# **TOSHIBA**

Preliminary

TMP92CW10F

**Specification**

## Revision 1.1 17 January 2001

### Histor

| Revision | Date         | Note                 |

|----------|--------------|----------------------|

| 1.0      | 28 Dec. 2000 | Initial draft        |

| 1.1      | 17 Jan. 2001 | A mistake correction |

#### CMOS 32-bit Micro-controller

#### TMP92CW10F

## Preliminary

#### 1. Outline and Device Characteristics

TMP92CW10 is high-function 32-bit microcontroller incorporating Toshiba's proprietary TLCS-900/H1 CPU. It is suitable for various embedded control equipment applications which require high-spped-processing data capability.

The product comes in a compact 100-pin flat package and tus help to meet user system requirements for high-density mounting.

(1) CPU: 32-bit CPU (900/H1 CPU)

Compatible with TLCS-900, 900/L, 900/H, 900/L1 and 900/H2's instruction code

16Mbytes of linear address space

General-purpose register and register banks

Micro DMA: 8channels. 250ns / 4bytes (when operating internally at fc = 20 MHz)

(2) Minimum instruction execution time: 50ns (when operating internally at fc = 20 MHz)

Internal data bus: 32-bit

(3) Internal memory

Internal RAM: 6Kbyte (can use for code section)

Internal ROM: 128Kbyte Mask ROM

(4) External memory expansion

16M-byte linear address space (memory mapped I/O)

External data bus: 8-bit

\* Can't use upper address bus when built-in I/Os are selected

(5) Memory controller

Chip select output: 1 channel

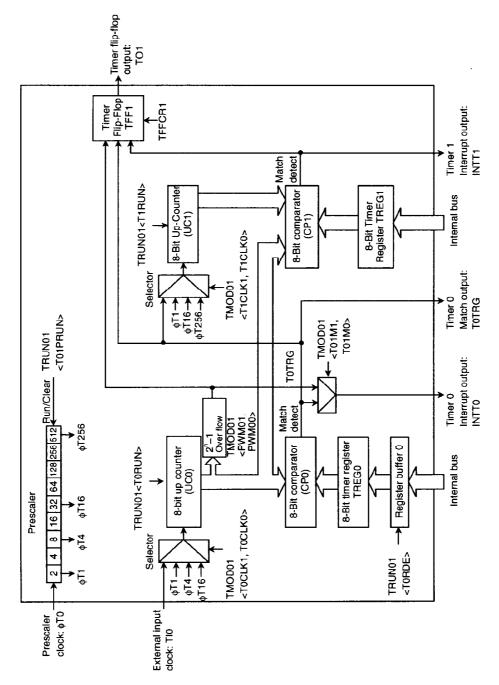

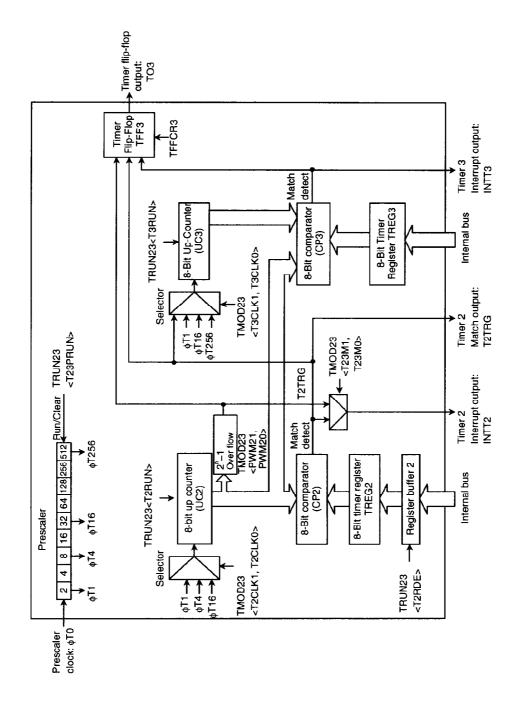

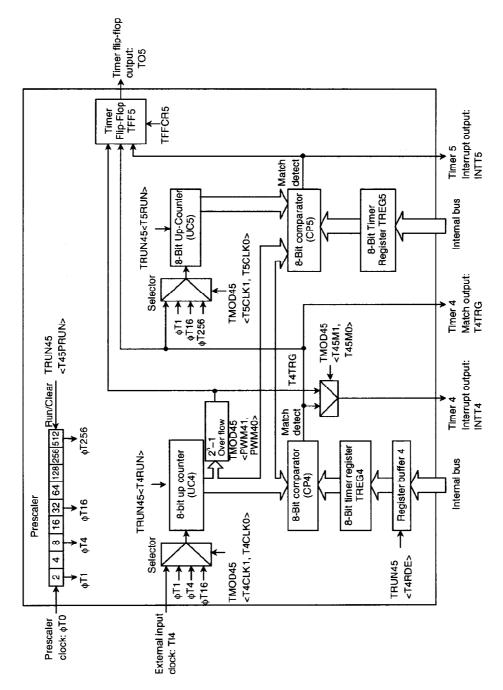

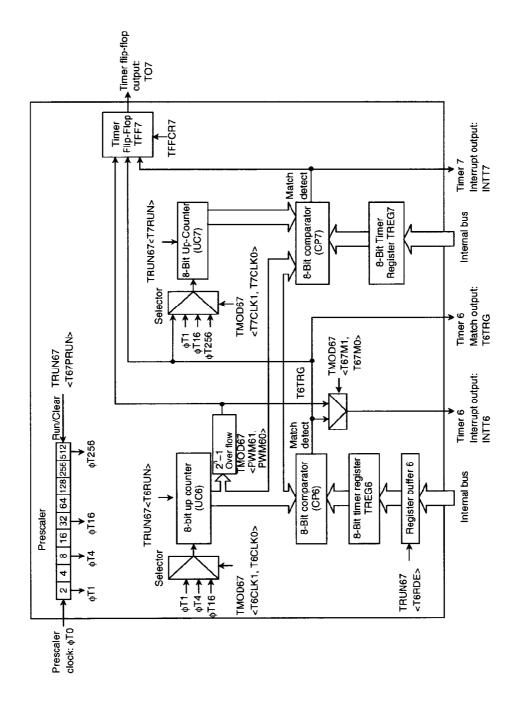

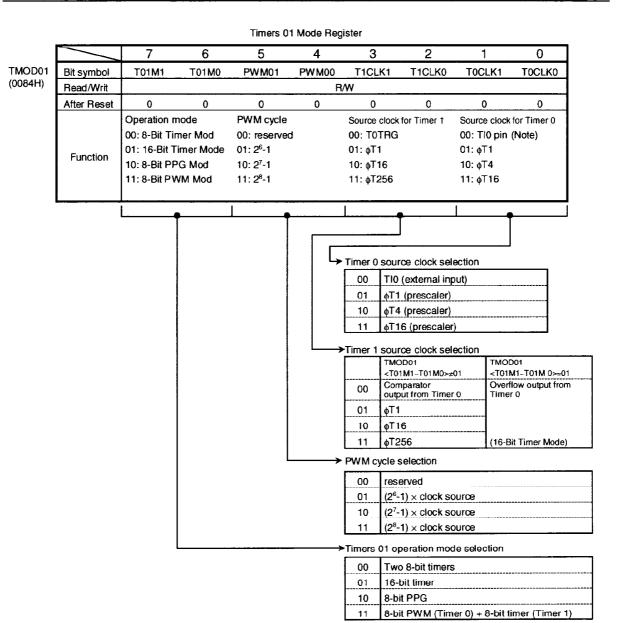

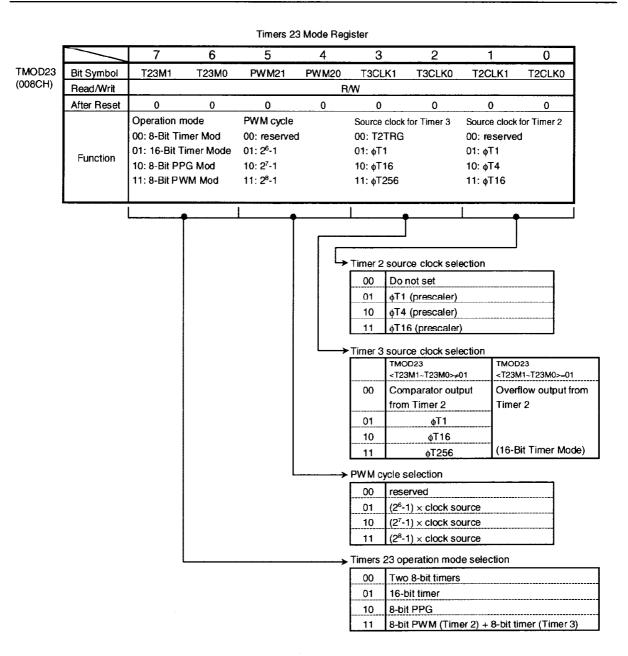

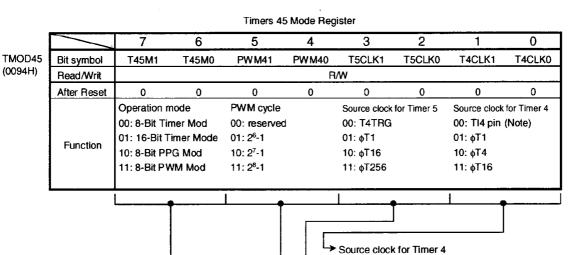

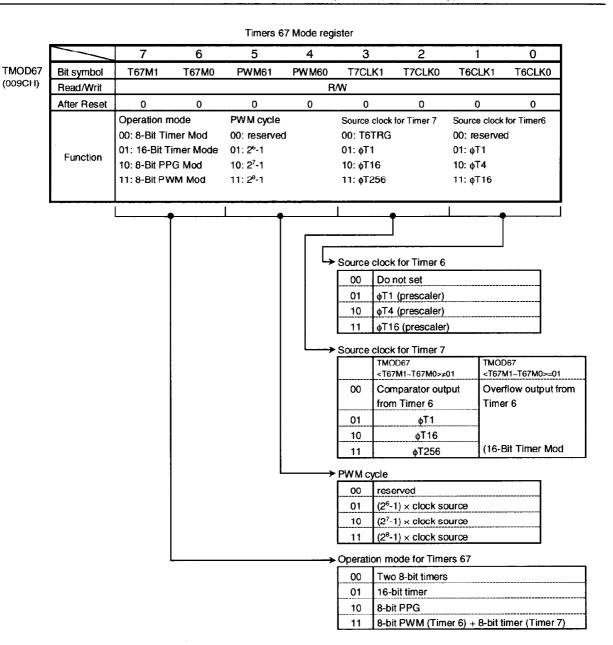

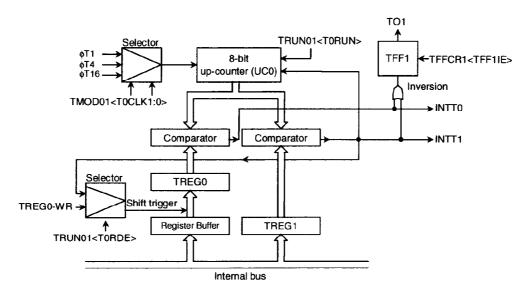

(6) 8-bit timer: 8 channels

8-bit interval timer mode (8 channels)

16-bit interval timer mode (4 channels)

8-bit programmable pulse generation (PPG) output mode (4 channels)

8-bit pulse width modulation (PWM) output mode (4 channels)

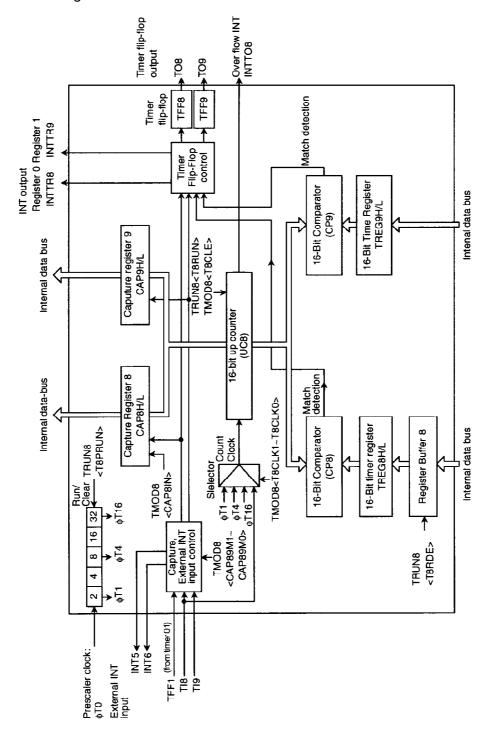

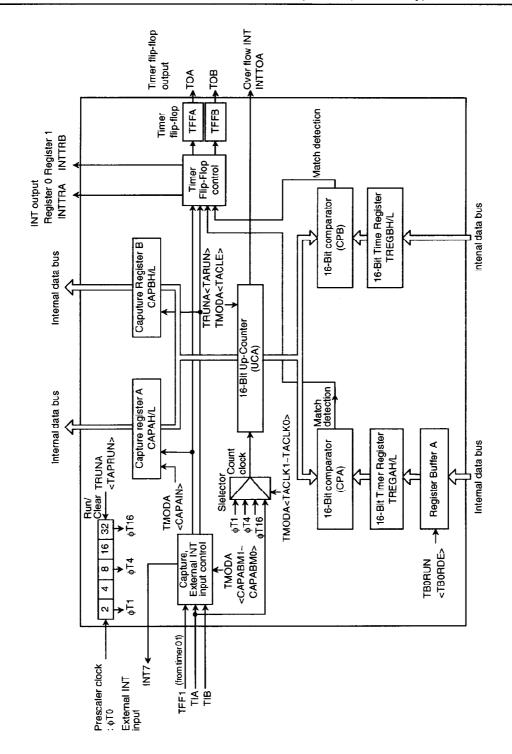

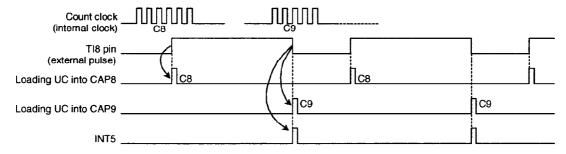

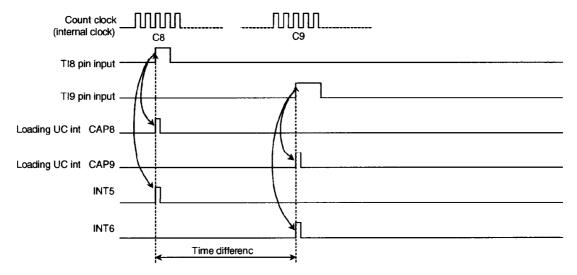

(7) 16-bit timer: 2 channels

16-bit interval timer mode

16-bit event counter mode

16-bit programmable pulse generation (PPG) output mode

Frequency measurement mode

Pulse width measurement (PWM) mode

Time differential measurement mode

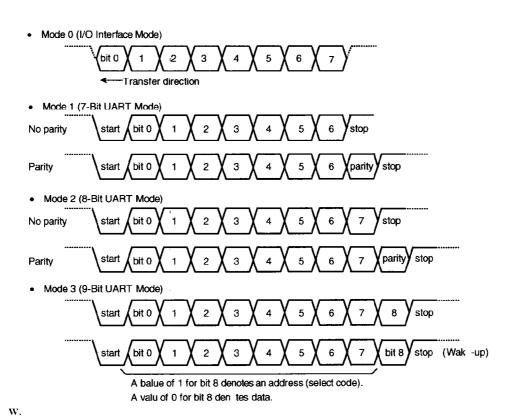

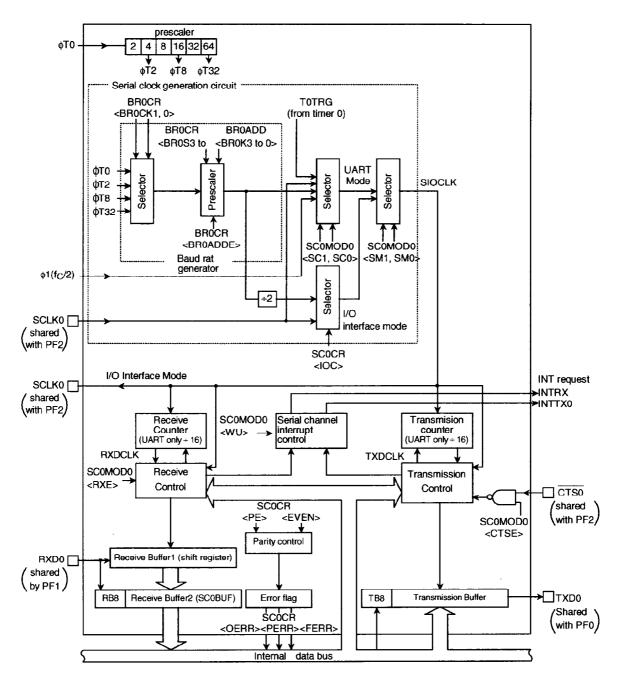

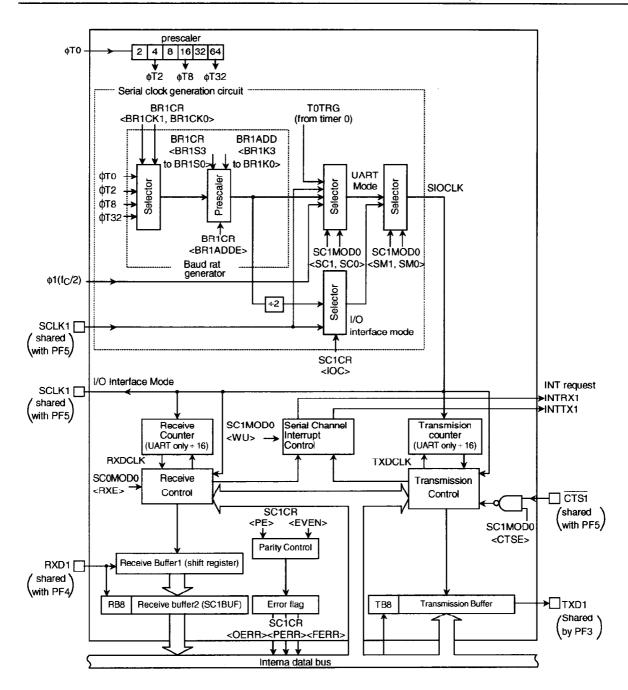

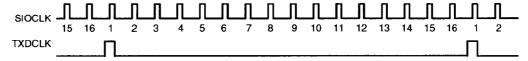

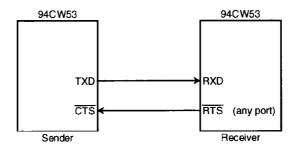

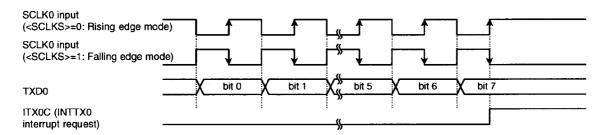

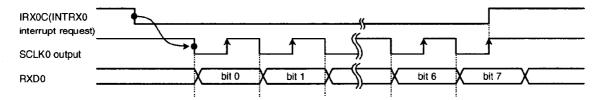

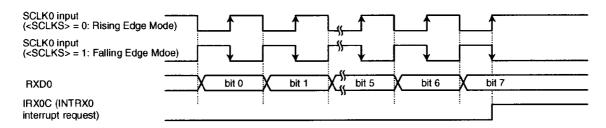

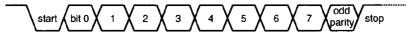

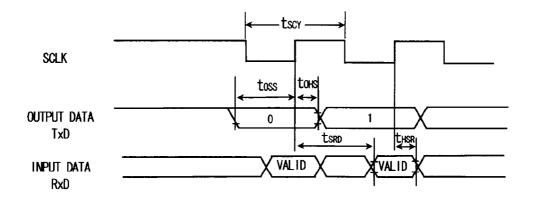

(8) Serial interface: 2 channels

I/O interface mode

Universal asynchronous receiver transmitter (UART) mode

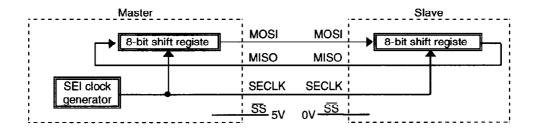

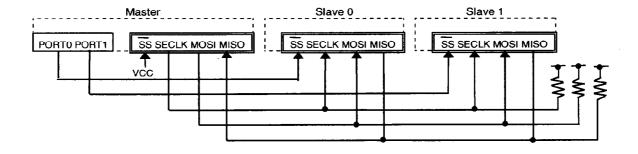

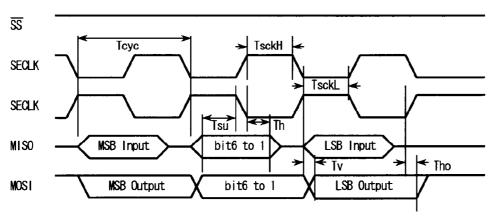

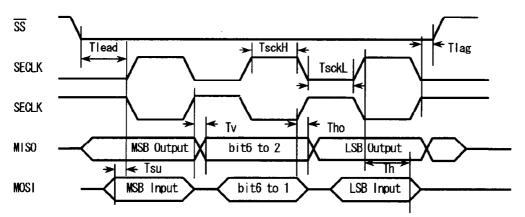

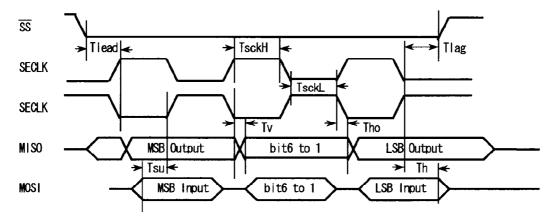

(9) Serial expansion interface: 2 channels

Baud rate 8/4/2/0.5Mbps at fc=20MHz.

(10) Serial bus interface: 2 channels

Clocked-synchronous mode

I<sup>2</sup>C bus mode

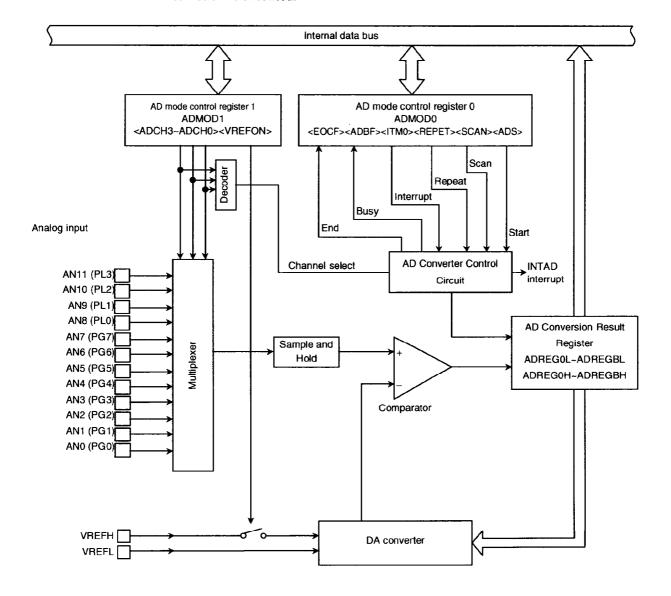

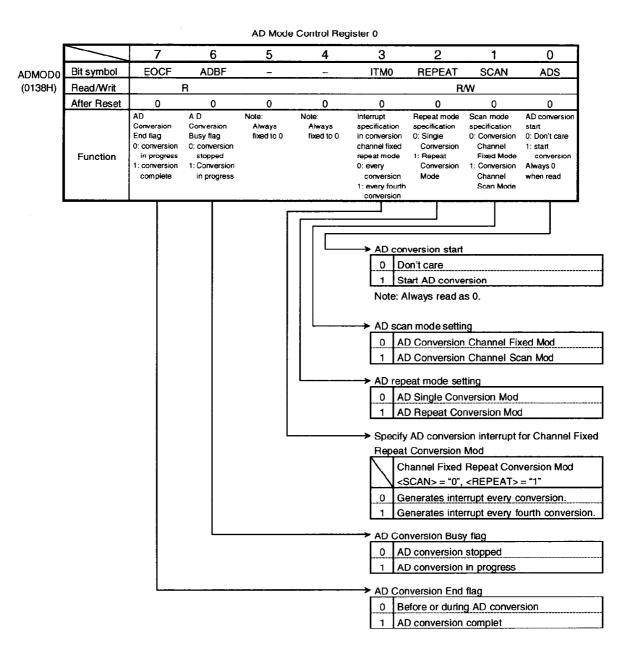

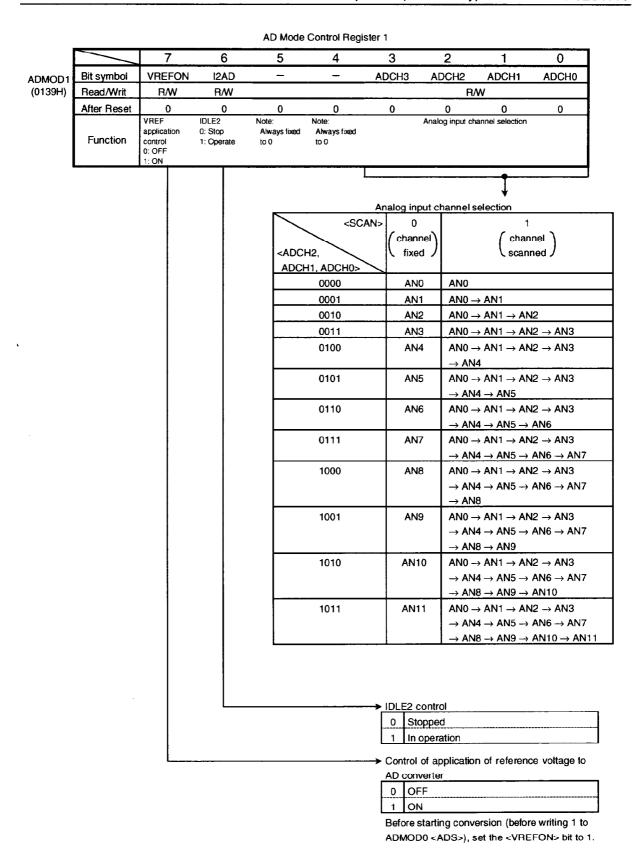

(11) 10-bit A/D converter: 12 channels

A/D conversion time 8µsec at fc=20MHz.

Total tolerance ±3LSB (excluding quantization error)

Scan mode for all 12channels

- (12) Watch dog timer

- (13) Interrupt controller

32 internal interrupts

Any one of 7 intrrupt priority lebels can be set (but not for NMI)

9 external interrupts

- (14) I/O Port: 70pins

- (15) Power supply voltage

$VCC5 = 5V \pm 10\%$  (4.5V to 5.5V)

$VCC3 = 3.3V \pm 0.3V$  (3V to 3.6V)

- (17) Operating temperature: -40 to 85 °C

- (18) Package: 100-pin LQFP (14×14×1.4 mm. 0.5 mm pitch)

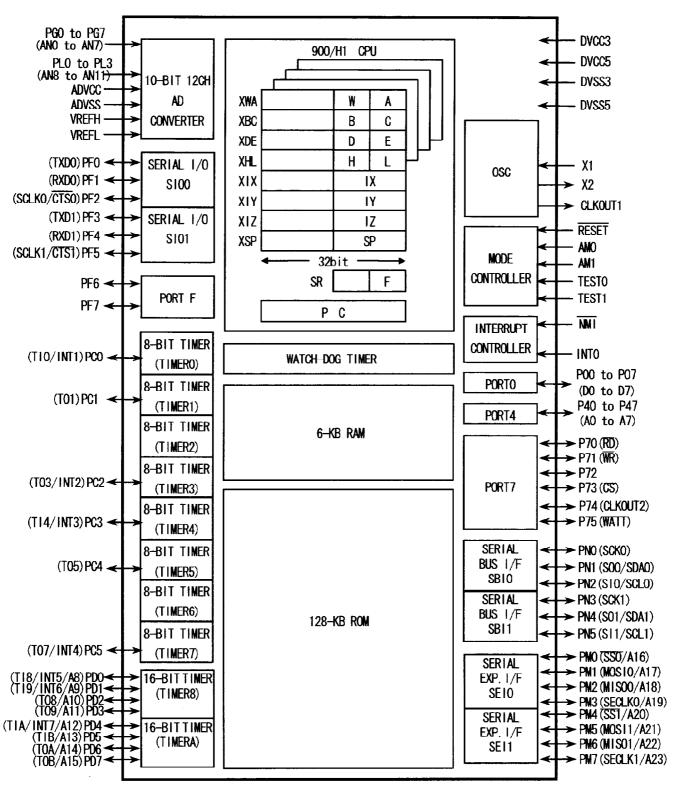

Figure 1 TMP92CW10 block diagram

### 2. Pin Assignment and Functions

#### 2.1 Pin Assignment

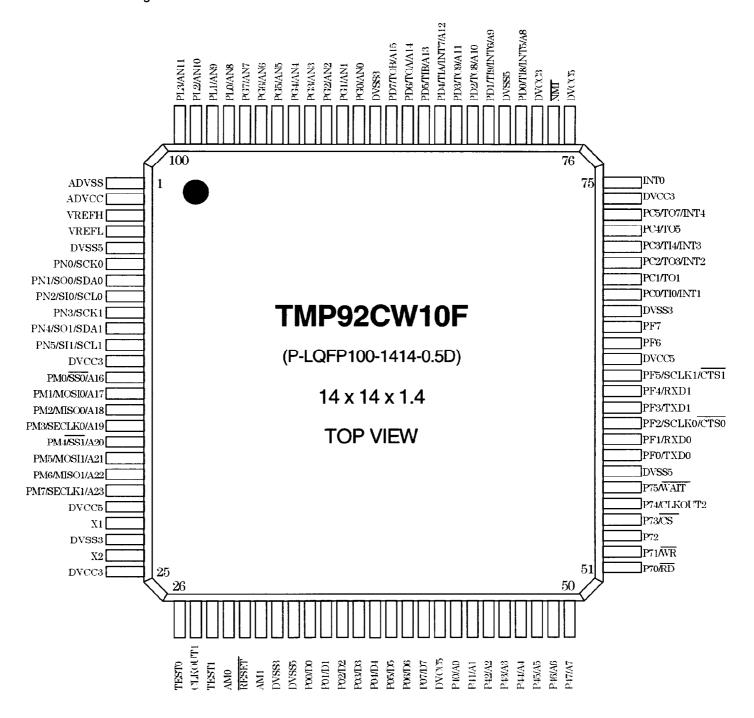

Figure 2.1 Pin Assignment

## 2.2 Pin names and functions

The following table shows the names and functions of the input/output pi

| Pin Name     | Number of pins | In/Out    |                                                                                                       |  |  |

|--------------|----------------|-----------|-------------------------------------------------------------------------------------------------------|--|--|

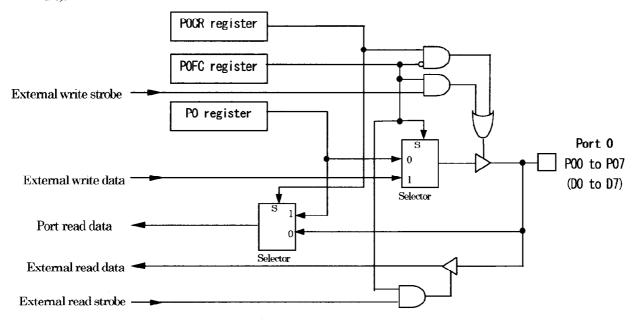

| P00P07       | 8 (CMOS)       |           | Port 0: I/O port. Input or output specifiable in units of bits.                                       |  |  |

| D0D7         | (TTL)          |           | Data: Data bus 0 to 7.                                                                                |  |  |

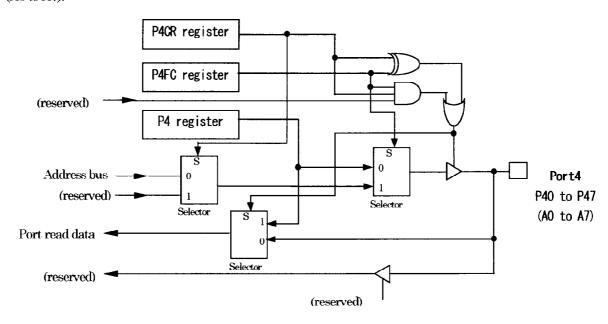

| P40P47       | 8 in/out       |           | Port4: I/O port. Input or output specifiable in units of bits.                                        |  |  |

| A0A7         |                | out       | Address: Address bus 0 to 7.                                                                          |  |  |

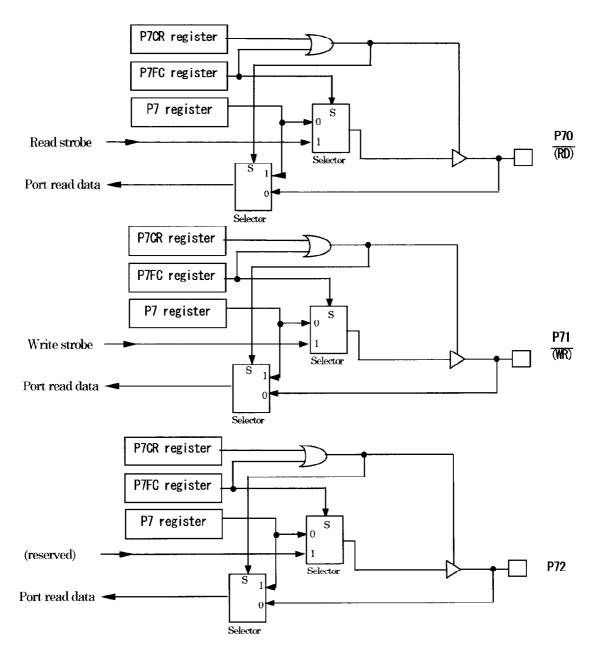

| P70          | 1              | in/out    | Port70: I/O port.                                                                                     |  |  |

| RD           |                | out       | Read: Outputs strobe signal to read external memory.                                                  |  |  |

| <u>P71</u>   | 1              | i         | Port 71: I/O port.                                                                                    |  |  |

| WR           | •              | out       | Write: Output strobe signal to write data on pins.                                                    |  |  |

| P72          | 1              | in/out    | Port 72: I/O port.                                                                                    |  |  |

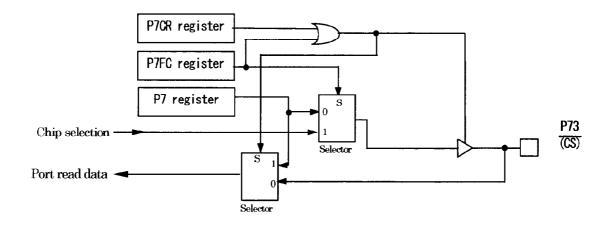

| P73          | 4              | in/out    | Port 73: I/O port.                                                                                    |  |  |

| CS           | 1              | out       | Chip select: Outputs "low" if address is within specified address area.                               |  |  |

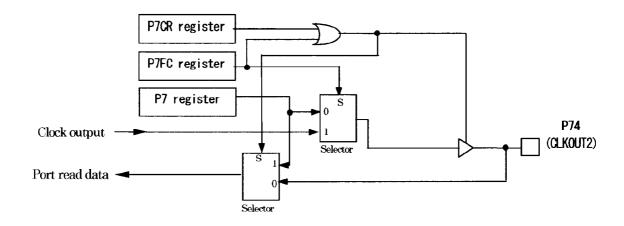

| P74          | -1             | in/out    | Port 74: I/O port.                                                                                    |  |  |

| CLKOUT2      | 1              | out       | Clock output 2: CLKOUT2 output 4 MHz clock at fc = 20 MHz.                                            |  |  |

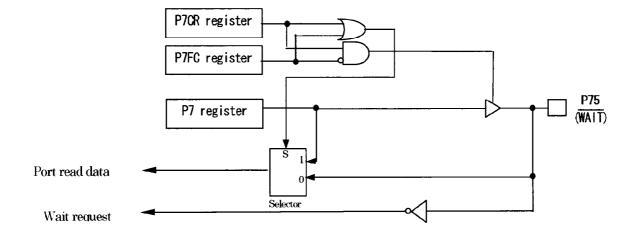

| P75          | 4              | in/out    | Port 75: I/O port.                                                                                    |  |  |

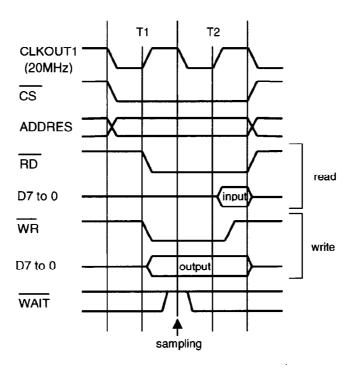

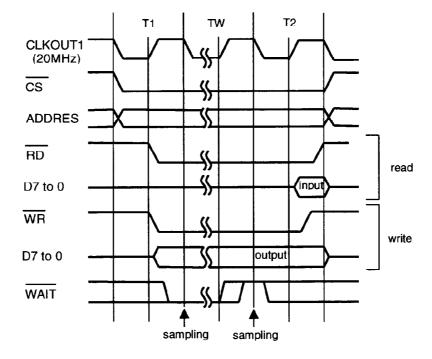

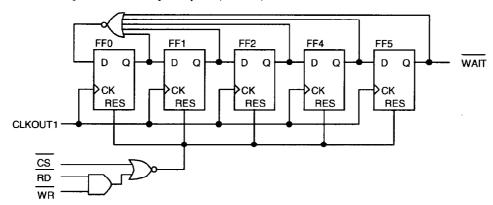

| WAIT         | 1              | in        | Wait: Signal used to request CPU bus wait.                                                            |  |  |

| PC0          |                | in/out    | Port C0: I/O port.                                                                                    |  |  |

| TIO          | 1              | in        | Timer input 0: Input pin for timer 0.                                                                 |  |  |

| INT1         | in In          |           | Interrupt request pin 1: Rising-edge interrupt request pin.                                           |  |  |

| PC1          | l in/out       |           | Port C1: I/O port.                                                                                    |  |  |

| TO1          |                |           | Timer output 1: Output pin for timer 1.                                                               |  |  |

| PC2          |                | in/out    | Port C2: I/O port.                                                                                    |  |  |

| TO3          | 1              | out       | Timer output 3: Output pin for timer 3.                                                               |  |  |

| INT2         |                | in        | Interrupt request pin 2: Rising-edge interrupt request pin.                                           |  |  |

| PC3          |                | ŀ         | Port C3: I/O port.                                                                                    |  |  |

| TI4          | 1              | in        | Timer input 4: Input pin for timer 4.                                                                 |  |  |

| INT3         |                | in        | Interrupt request pin 3: Rising-edge interrupt request pin.                                           |  |  |

| PC4          | 1              |           | Port C4: I/O port.                                                                                    |  |  |

| TO5          |                |           | Timer output 5: Output pin for timer 5.                                                               |  |  |

| PC5          | _              |           | Port C5: I/O port.                                                                                    |  |  |

| TO7          | 1              | Out       | Timer output 7: Output pin for timer 7.                                                               |  |  |

| INT4         |                | In        | Interrupt request pin 4: Rising-edge interrupt request pin.                                           |  |  |

| PD0          |                | In/out    | Port D0: I/O port.                                                                                    |  |  |

| TI8          | -1             | In        | Timer input 8: Input pin for timer 8.7                                                                |  |  |

| INT5         | 1              | In        | Interrupt request pin 5: Interrupt request pin with programmable rising/falling                       |  |  |

| 100          |                | l out     | edge.<br>Address: Address bus 8.                                                                      |  |  |

| A8           |                | out       |                                                                                                       |  |  |

| PD1          |                | in/out    | Port D1: I/O port. Timer input 9: Input pin for timer 9.                                              |  |  |

| T19<br> INT6 | 1              | in        | I imer input 9: input pin for timer 9:<br>Interrupt request pin 6: Rising-edge interrupt request pin. |  |  |

|              |                | in<br>out | Address: Address bus 9.                                                                               |  |  |

| A9           |                | Juui      | Audress. Audress bus &                                                                                |  |  |

| Pin Name         | Number of pins | In/Out |                                                                                 |  |  |  |

|------------------|----------------|--------|---------------------------------------------------------------------------------|--|--|--|

| PD2              |                | in/out | Port D2: I/O port.                                                              |  |  |  |

| TO8              | 1              | out    | Timer output 8: Output pin for timer 8                                          |  |  |  |

| A10              |                | out    | Address: Address bus 10.                                                        |  |  |  |

| PD3              |                | in/out | Port D3: I/O port.                                                              |  |  |  |

| TO9              | 1              | out    | Timer output 9: Output pin for timer 9                                          |  |  |  |

| A11              |                | out    | Address: Address bus 11.                                                        |  |  |  |

| PD4              |                | in/out | Port D4: I/O port.                                                              |  |  |  |

| TIA              |                | in     | Timer input A: Input pin for timer A                                            |  |  |  |

| INT7             | 1              | in     | Interrupt request pin 7: Interrupt request pin with programmable rising/falling |  |  |  |

|                  |                |        | edge.                                                                           |  |  |  |

| A12              |                | out    | Address: Address bus 12.                                                        |  |  |  |

| PD5              |                | in/out | Port D5: I/O port.                                                              |  |  |  |

| TIB              | 1              | in     | Timer input B: Input pin for timer B.                                           |  |  |  |

| A13              |                | out    | Address: Address bus 13.                                                        |  |  |  |

| PD6              |                | in/out | Port D6: I/O port.                                                              |  |  |  |

| TOA              | 1              | out    | Timer output A: Output pin for timer A.                                         |  |  |  |

| A14              |                | out    | Address: Address bus 14.                                                        |  |  |  |

| PD7              |                | in/out | Port D7: I/O port.                                                              |  |  |  |

| TOB              | 1              | out    | Timer output B: Output pin for timer B.                                         |  |  |  |

| A15              |                | out    | Address: Address bus 15.                                                        |  |  |  |

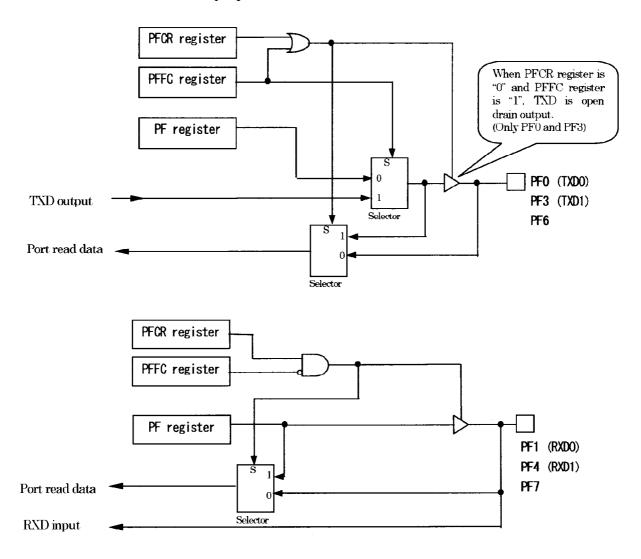

| PF0              | •              | in/out | Port F0: I/O port.                                                              |  |  |  |

| TXD0             | 1              | out    | Serial transmission data 0.                                                     |  |  |  |

| PF1              | 1              | in/out | Port F1: I/O port.                                                              |  |  |  |

| RXD0             | 1              | in     | Serial receive data 0.                                                          |  |  |  |

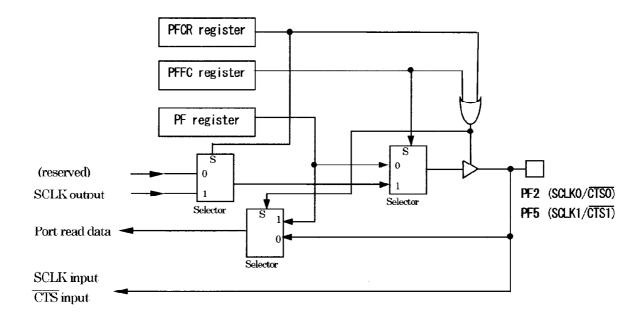

| PF2              |                | in/out | Port F2: I/O port.                                                              |  |  |  |

| SCLK0            | 1              | in/out | Serial clock input/output 0.                                                    |  |  |  |

| /CTS0            |                | in     | Serial data ready to send 0. (Clear-to-send)                                    |  |  |  |

| PF3              | 1              | in/out | Port F3: I/O port.                                                              |  |  |  |

| TXD1             | 1              | out    | Serial transmission data 1.                                                     |  |  |  |

| PF4              |                | in/out | Port F4: I/O port.                                                              |  |  |  |

| RXD1             | 1              | in     | Serial receive data 1.                                                          |  |  |  |

| PF5              |                | in/out | Port F5: I/O port.                                                              |  |  |  |

| SCLK1            | 1              | in/out | Serial clock input/output 1.                                                    |  |  |  |

| /CTS1            |                | in     | Serial data ready to send 0. (Clear-to-send)                                    |  |  |  |

| PF6              | 1              | in/out | Port F6: I/O port.                                                              |  |  |  |

| PF7              | 1              | in/out | Port F7: I/O port.                                                              |  |  |  |

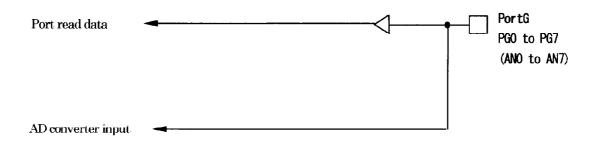

| PG0PG7           | 8              | in     | Port G: Input-only port.                                                        |  |  |  |

| ANOAN7           | 8              | in     | Analog input 0 to 7: AD converter input pins.                                   |  |  |  |

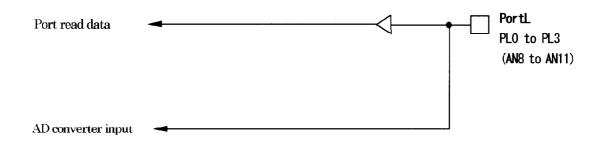

| PL0PL3           | 4              | in     | Port L0 to L3: Input-only port.                                                 |  |  |  |

| AN8AN11          | 4              | in     | Analog input 8 to 11: AD converter input pins.                                  |  |  |  |

| PM0              |                | in/out | Port M0: I/O port.                                                              |  |  |  |

| $\overline{SS0}$ | 1              | in     | SEI slave select input 0.                                                       |  |  |  |

| A16              |                | out    | Address: Address bus 16                                                         |  |  |  |

| PM1              |                | in/out | Port M1: I/O port.                                                              |  |  |  |

| MOSI0            | 1              | in/out | SEI master output. slave input 0.                                               |  |  |  |

| A17              |                | out    | Address: Address bus 17.                                                        |  |  |  |

| PM2              |                | in/out | Port M2: I/O port.                                                              |  |  |  |

| MISO0            | 1              | in/out | SEI master input. slave output 0.                                               |  |  |  |

| A18              |                | out    | Address: Address bus 18.                                                        |  |  |  |

| Pin Name     | Number of pins | In/Out        | Function                                                                                                 |  |  |

|--------------|----------------|---------------|----------------------------------------------------------------------------------------------------------|--|--|

| PM3          |                | in/out        | Port M3: I/O port.                                                                                       |  |  |

| SECLK0       | 1              | in/out        | SEI clock input/output 0.                                                                                |  |  |

| A19          |                | out           | Address: Address bus 19.                                                                                 |  |  |

| PM4          |                | in/out        | Port M4: I/O port.                                                                                       |  |  |

| SSI          | 1              | in            | SEI slave select input.                                                                                  |  |  |

| A20          |                | out           | Address: Address bus 20.                                                                                 |  |  |

| PM5          | _              |               | Port M5: I/O port.                                                                                       |  |  |

| MOSI1        | 1              |               | SEI master output. slave input 1.                                                                        |  |  |

| A21          |                | out           | Address: Address bus 21.                                                                                 |  |  |

| PM6          | •              |               | Port M6: I/O port.                                                                                       |  |  |

| MISO1<br>A22 | 1              | l I           | SEI master input, slave output 1.<br>Address: Address bus 22.                                            |  |  |

| PM7          |                | out<br>in/out |                                                                                                          |  |  |

| SECLK1       | 1              |               | Port M7: I/O port.<br>SEI clock input/output 1.                                                          |  |  |

| A23          | 1              | out           | Address: Address bus 23                                                                                  |  |  |

| PN0          |                |               | Port NO: I/O port.                                                                                       |  |  |

| SCK0         | 1              |               | SBI interface 0: clock during SIO mode                                                                   |  |  |

| PN1          |                | in/out        | Port N1: I/O port.                                                                                       |  |  |

| SOO          | 1              | out           | SBI interface 0: output data at SIO mode                                                                 |  |  |

| SDA0         | 1              |               | SBI interface 0: data at 1 <sup>2</sup> C mode                                                           |  |  |

| PN2          |                | in/out        | Port N2: I/O port.                                                                                       |  |  |

| SI0          | 1              | in            | SBI interface 0: input data at SIO mode                                                                  |  |  |

| SCL0         |                | in/out        | SBI interface 0: clock at I <sup>2</sup> C mode                                                          |  |  |

| PN3          | 1              | in/out        | Port N3: I/O port.                                                                                       |  |  |

| SCK1         | 1              | in/out        | SBI interface 1: clock during SIO mode                                                                   |  |  |

| PN4          |                | in/out        | Port N4: I/O port.                                                                                       |  |  |

| SO1          | 1              | out           | SBI interface 1: output data at SIO mode                                                                 |  |  |

| SDA1         |                |               | SBI interface 1: data at I <sup>2</sup> C mode                                                           |  |  |

| PN5          |                | in/out        | Port N5: I/O port.                                                                                       |  |  |

| SI1          | 1              | in            | SBI interface 1: input data at SIO mode                                                                  |  |  |

| SCL1         |                | in/out        | SBI interface 1: clock at I <sup>2</sup> C mode                                                          |  |  |

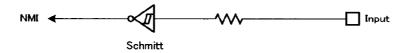

| NMI          | 1              | in            | Non-maskable interrupt: Interrupt request pin with programmable falling or both falling and rising edge. |  |  |

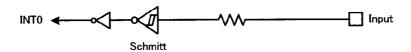

| INTO         | 1              | in            | Interrupt request pin 0: Interrupt request pin with programmable level/rising-edge.                      |  |  |

| AM0,1        | 2              | in            | Address Mode selection: Connect AM0 and AM1 pins to VCC.                                                 |  |  |

| TEST0.1      | 2              | in            | TEST mode pins :Input "low" when using                                                                   |  |  |

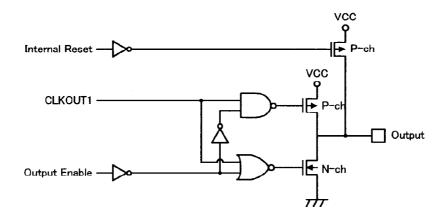

| CLKOUT1      | 1              | out           | Programmable clock output 1                                                                              |  |  |

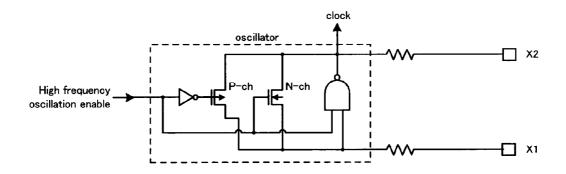

| X1/X2        | 2              | in/out        | Oscillator connecting pins. Input 3.3V clock signal using external clock.                                |  |  |

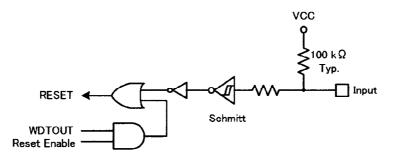

| RESET        | 1              | in            | Reset : Initializes the device.                                                                          |  |  |

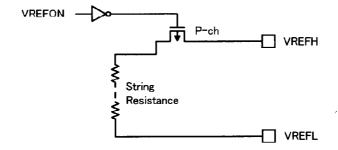

| VREFH        | 1              | in            | AD reference voltage high                                                                                |  |  |

| VREFL        | 1              | in            | AD reference voltage low                                                                                 |  |  |

| ADVCC        | 1              | -             | Power supply pin for AD converter                                                                        |  |  |

| ADVSS        | 1              |               | GND pin for AD converter                                                                                 |  |  |

| Pin Name | Number of pins | In/Out | Function                                                               |  |

|----------|----------------|--------|------------------------------------------------------------------------|--|

| DVCC5    | 4              | -      | Power supply pins (+5V): Conect all DVCC5 pins to 5V power supply.     |  |

| DVSS5    | 4              | -      | ND 5V: Connect all DVSS pins to GND (0V).                              |  |

| DVCC3    | 4              |        | Power supply pins (+3.3V): Connect all DVCC pins to 3.3V power supply. |  |

| DVSS3    | 4              | -      | GND 3.3V: Connect all DVSS3 pins to GND.(0V)                           |  |

#### 3. OPERATION

This section describes the functions and the basic operation of the TMP92CW10.

#### 3.1 CPU

The CPU functions exclusive to the TMP92CW10 are explained here.

#### 3.1.1 CPU Outline

TMP92CW10 devices have a built-in high-performance 32-bit CPU (the TLCS-900/H1 CPU). (For basics of the CPU for more information about the TLCS-900/H2 CPU, please refer to the previous chapter).

Details of the TMP92CW10 CPU are as follows:

| Table 3.1.1 | Outline of CPU |

|-------------|----------------|

| Pug         | 94 bit         |

| Width of CPU Address Bus     | 24-bit                                       |  |  |  |

|------------------------------|----------------------------------------------|--|--|--|

| Width of CPU Data Bus        | 32-bit                                       |  |  |  |

| Internal Operating Frequency | 20MHz                                        |  |  |  |

| Minimum Bus Cycle            | 1-clock access (50ns @20MHz)                 |  |  |  |

| Internal RAM                 | 32-bit 1-clock access                        |  |  |  |

| Internal ROM                 | 32-bit 1-clock access                        |  |  |  |

| Internal I/O                 | 8/16-bit 2-clock access TLCS-900/H1 I/O      |  |  |  |

|                              | 8/16-bit 5 to 6-clock access TLCS-900/L1 I/O |  |  |  |

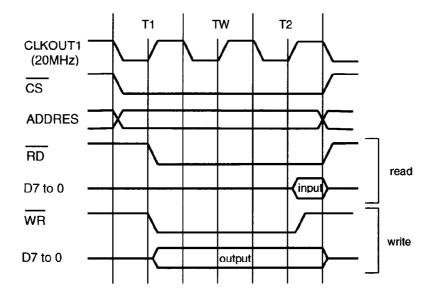

| External Device              | 8-bit 2-clock access                         |  |  |  |

|                              | (can insert some waits)                      |  |  |  |

| Minimum Instruction          | 1-clock(50ns @20MHz)                         |  |  |  |

| Execution Cycle              |                                              |  |  |  |

| Conditional Jump             | 2-clock(100ns@20MHz)                         |  |  |  |

| Instruction Queue Buffer     | 12-byte                                      |  |  |  |

| Instruction Set              | Compatible with TLCS-900/L1, TLCS-900/H2     |  |  |  |

|                              | (LDX instructions have been omitted.)        |  |  |  |

| CPU mode                     | Only maximum mode                            |  |  |  |

| Micro DMA                    | 8-channel                                    |  |  |  |

### 3.1.2 Reset Operation

When resetting the TMP92CW10 microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the RESET input Low for at least20 system clocks(  $4\,\mu$  s). At reset the clock doubler is bypassed and system clock operates at 5MHz(fc=20MHz).

When the Reset has been accepted, the CPU performs the following:

• Sets the Program Counter (PC) as follows in accordance with the Reset Vector stored at address FFFF00H~FFFF02H:

PC<0~7> ← data in location FFFF00H PC<8~15> ← data in location FFFF01H PC<16~23> ← data in location FFFF02H

- Sets the Stack Pointer (XSP) to 00000000H.

- Sets bits <IFF0~IFF2> of the Status Register (SR) to 111 (thereby setting the Interrupt Level Mask Register to level 7).

- Clears bits <RFP0~RFP1> of the Status Register to 00 (thereby selecting Register Bank 0).

When the Reset is released, the CPU starts executing instructions according to the

Program Counter settings. CPU internal registers not mentioned above do not change when the Reset is released.

When the Reset is accepted, the CPU sets internal I/O, ports and other pins as follows.

- Initializes the internal I/O registers as table of "Special Function Register" in Section 5.

- Sets the port pins, including the pins that also act as internal I/O, to General-Purpose Input or Output Port Mode.

When the RESET input pin is released High, the internal reset is released.

After a power-on reset, the operation of the memory controller cannot be guaranteed until the power supply becomes stable. External memory data receives befor e the TNP92CW10 was turned on may be corrupted since the control signals will be unstable until the power supply has stabilized after the power-on reset.

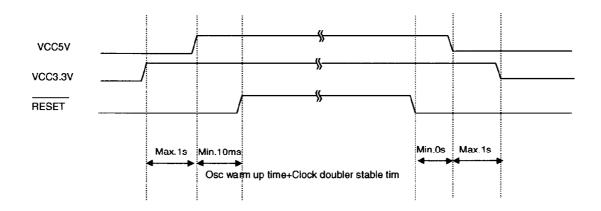

Figure 3.1.1 Power on Reset Timing Example

#### 3.1.3 Setting of TEST0, TEST1, AM0, AM1

Connect TEST0.TEST1 pin to "GND". set AM0.AM1 pin to "1" to use.

Table 3.1.2 Operation ModeSetup Table

| On anation Made | Input pin for mode setting |     |     |       |       |  |

|-----------------|----------------------------|-----|-----|-------|-------|--|

| Operation Mode  | RESET                      | AM1 | AM0 | TEST1 | TEST0 |  |

| Single-chip Mod | $\mathcal{I}$              | 1   | 1   | 0     | 0     |  |

#### 3.2 Memory Map

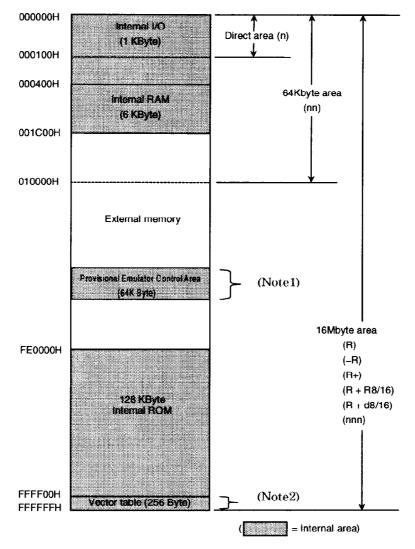

Figure 3.2.1 is a memory map of the TMP92CW10.

Figure 3.2.1 Memory Map

- Note1: Provisional emulator control area is for emulator, it is mapped F00000H to F10000H address after reset.

- Note2: Don't use the last 16-byte area (FFFFF0H to FFFFFFH). This area is reserved.

- Note3: When the provisional emulator control area is accessed, the WR and RD signals are output. For this reason, care should be exercised when the expanded memory area is used.

## 3.3 The Clock Function and Standby Function

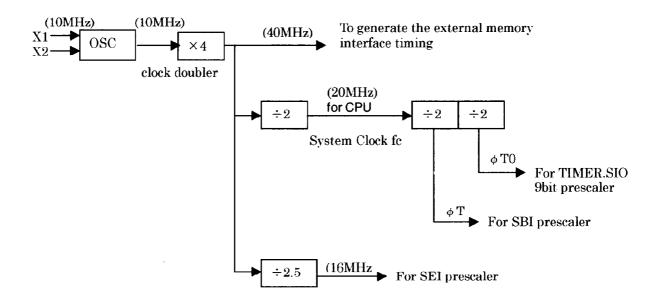

## 3.3.1 Block diagram of system clock

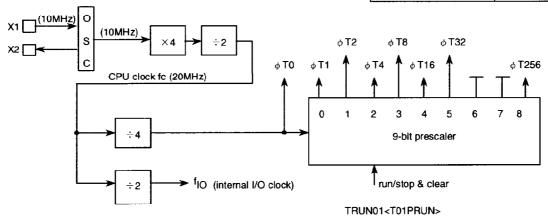

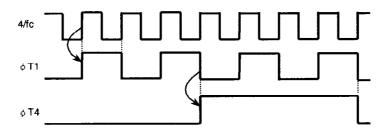

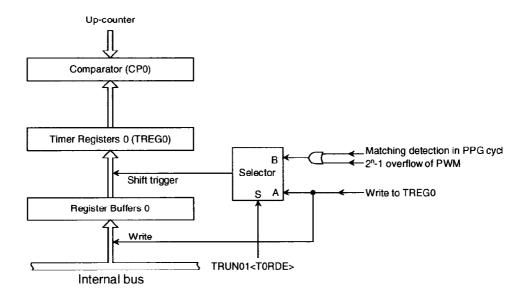

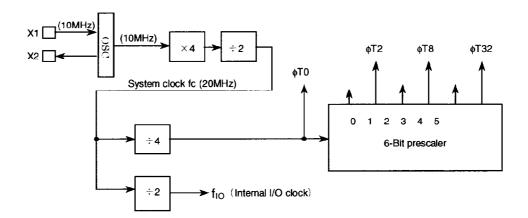

Figure 3.3.1 Block Diagram of System clock

### 3.3.2 Standby controller

#### (1) Halt Modes

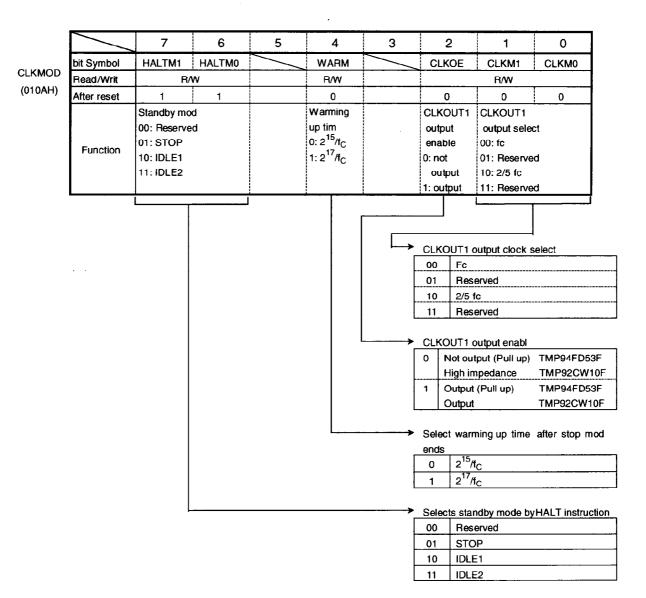

When the HALT instruction is executed, the operating mode switches to Idle2, Idle1 or Stop Mode, depending on the content s of th@LKMOD<HALTM1,HALTM0> register.

The subsequent actions performed in each mode are as follows:

① IDLE2: The CPU only is halted.

In Idle2 Mode internal I/O operations can be performed by setting the following registers.

Table 3.3.1 Shows the registers of setting operation during Idle2 Mode

Table 3.3.1 Shows the registers of setting operation during Idle2 Mode

|               | 3 1                       |

|---------------|---------------------------|

| Internal I/O  | SFR                       |

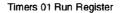

| TIMER0,TIMER1 | TRUN01 <i2t01></i2t01>    |

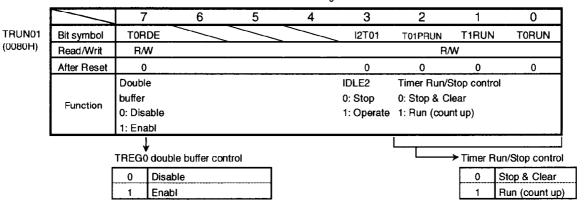

| TIMER2,TIMER3 | TRUN23 <i2t23></i2t23>    |

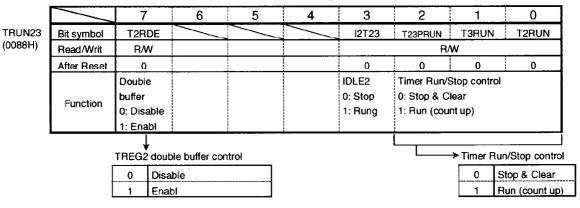

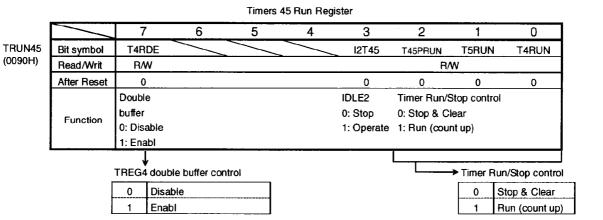

| TIMER4,TIMER5 | TRUN45 <i2t45></i2t45>    |

| TIMER6,TIMER7 | TRUN67 <i2t67></i2t67>    |

| TIMER8        | TRUN8 <i2t8></i2t8>       |

| TIMERA        | TRUNA <i2ta></i2ta>       |

| SIO0          | SC0MOD1 <i2s0></i2s0>     |

| SIO1          | SC1MOD1 <i2s1></i2s1>     |

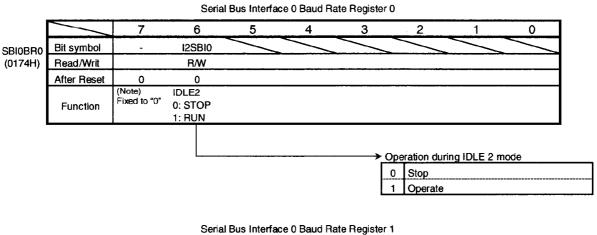

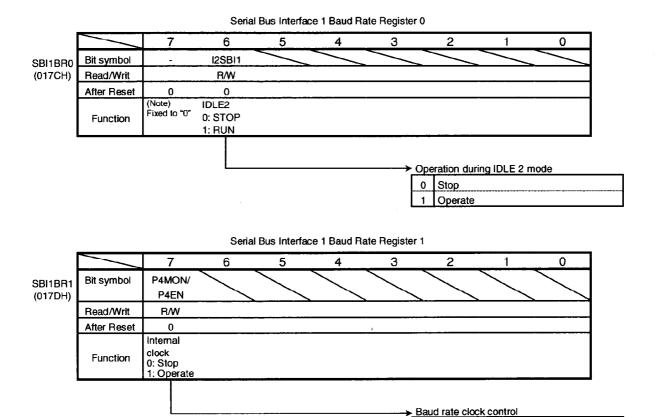

| SBI0          | SBI0BR0 <i2sbi0></i2sbi0> |

| SBI1          | SBI1BR0 <i2sbi1></i2sbi1> |

| A/D converter | ADMOD1 <i2ad></i2ad>      |

| WDT           | WDMOD <i2wdt></i2wdt>     |

- ② Idle1: Only the oscillator continue to operate.

- 3 Stop: All internal circuits stop operating.

The operation of each of the different Halt Modes is described in Table 3.3.2.

Table 3.3.2 I/O operation during Halt Modes

| Halt Mode                    |                       | ldle2                                                      | ldle1   | Stop            |  |  |

|------------------------------|-----------------------|------------------------------------------------------------|---------|-----------------|--|--|

| CLKMOD <haltm1:0></haltm1:0> |                       | 11                                                         | 10      | 01              |  |  |

|                              | CPU                   | Halt                                                       |         |                 |  |  |

|                              | I/O ports             | Maintain same state as when HALT instruction was executed. |         | See Table 3.3.5 |  |  |

|                              | 8-bit TMR, 16-bit TMR |                                                            | Stopped |                 |  |  |

| Disale                       | SIO, SBI              | Can be selected                                            |         |                 |  |  |

| Block                        | A/D converter         | Can be selected                                            |         |                 |  |  |

|                              | WDT                   |                                                            |         |                 |  |  |

|                              | CAN, SEI              | Operational                                                |         |                 |  |  |

| L                            | Interrupt controller  | Operational                                                |         |                 |  |  |

#### (2) How to clear a Halt mode

The Halt state can be cleared by a Reset or by an interrupt request. The combination of the value in <IFF0~IFF2> of the Interrupt Mask Register and the current Halt mode determine in which ways the Halt mode may be cleared. The details associated with each type of Halt state clearance are shown in Table 3.35.

#### · Clearance by interrupt request

Whether or not the Halt mode is cleared and subsequent operation depends on the status of the generated interrupt. If the interrupt request level set before execution of the HALT instruction is greater than or equal to the value in the Interrupt Mask Register, the following sequence takes place: the Halt mode is cleared, the interrupt is then processed, and the CPU then resumes execution starting from the instruction following the HALT instruction. If the interrupt request level set before execution of the HALT instruction is less than the value in the Interrupt Mask Register, the Halt mode is not cleared. (If a non-maskable interrupt is generated, the Halt mode is cleared and the interrupt processed, regardless of the value in the Interrupt Mask Register.)

However, for INTO only, even if the interrupt request level set before execution of the HALT instruction is less than the value in the Interrupt Mask Register, the Halt mode is cleared. In this case, the interrupt is not processed and the CPU resumes execution starting from the instruction following the HALT instruction. The interrupt request flag remains set to 1.

#### · Clearance by Reset

Any Halt state can be cleared by Reset.

When Stop Mode is cleared by RESET signal, sufficient time

(at least 10ms@20MHz) must be allowed after the Reset for the operation of the oscillator and clock doubler to stabilize.

When a Halt mode is cleared by resetting, the contents of the internal RAM remain the same as they were before execution of the HALT instruction. However, all other settings are re-initialized. (Clearance by an interrupt affects neither the RAM contents nor any other settings – the state which existed before the HALT instruction was executed is retained.)

|                | Status of Received Interrupt |                     | Interrupt Enabled (interrupt level) ≥ (interrupt mask) |          |             | Interrupt Disabled<br>(interrupt level) < (interrupt mask) |      |                 |

|----------------|------------------------------|---------------------|--------------------------------------------------------|----------|-------------|------------------------------------------------------------|------|-----------------|

|                |                              | Halt mode           | Idle2 Idle1 Stop                                       |          | Idle2       | Idle1                                                      | Stop |                 |

|                |                              | NMI                 | •                                                      | <b>Ø</b> | <b>©</b> *1 |                                                            | -    | -               |

| ø              |                              | INTWDT              | •                                                      | ×        | ×           | _                                                          | -    | -               |

| clearance      |                              | INTO                | •                                                      | •        | <b>⊚</b> "1 | 0                                                          | 0    | o <sup>*1</sup> |

| ä              |                              | INT1 to 7           | •                                                      | ×        | х           | ×                                                          | ×    | ×               |

| 용              |                              | INTTO to 7          | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

| ē              | igh                          | INTTR8 to B         | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

| Halt state     | Interrupt                    | INTTO8, INTTOA      | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

| l <del>≝</del> | <u>t</u>                     | INTRX0 to 1, TX0 to | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

|                |                              | INTCR, INTCT, INTCG | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

| ō              |                              | INTSEM0, E0, R0, T0 | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

| 8              |                              | INTSEM1, E1, R1, T1 | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

| Source         |                              | INTSBE0, S0, E1, S1 | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

| lo             | ν INTAD                      |                     | •                                                      | ×        | ×           | ×                                                          | ×    | ×               |

|                |                              | RESET               | •                                                      | 0        | •           | 8                                                          | 9    | 0               |

Table 3.3.3 Source of Halt state clearance and Halt clearance operation

- (RESET initializes the microcont.)

- O: After clearing the Halt mode, CPU resumes executing starting from instruction following the HALT instruction.

- ×: Cannot be used to clear the Halt mode.

- -: The priority level (interrupt request level) of non-maskable interrupts is fixed to 7, the highest priority level.

There is not this combination type.

- \*1: The Halt mode is cleared when the warm-up time has elapsed.

- Note 1: When the Halt mode is cleared by an INT0 interrupt of the level mode in the interrupt enabled status, hold level H until starting interrupt processing. If level L is set before holding level H, interrupt processing is not correctly started.

- Note 2: If one of the external interrupts INT5~INT7 is generated in Idle2 Mode, TRUN8<I2T8> and TRUNA<I2TA> are set to 1

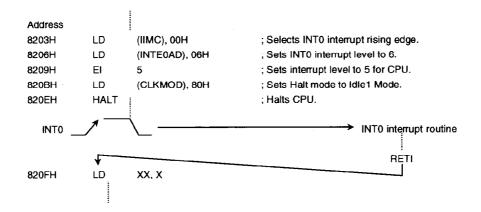

#### (Example - clearing Idle1 Mode)

An INTO interrupt clears the Halt state when the device is in Idle1 Mode.

#### (3) Operation

#### ① Idle2 Mode

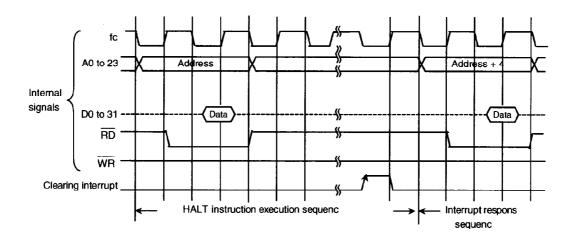

In Idle2 Mode only specific internal I/O operations, as designated by the Idle2 Setting Register, can take place. Instruction execution by the CPU stops.

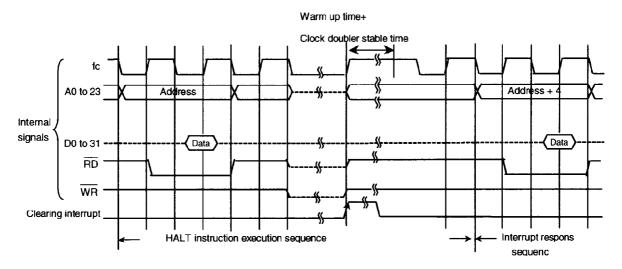

Figure 3.3.2 illustrates an example of the timing for clearance of the Idle2 Mode Halt state by an interrupt.

Figure 3.3.2 Timing chart for Idle2 Mode Halt state cleared by interrupt

#### ② Idle1 Mode

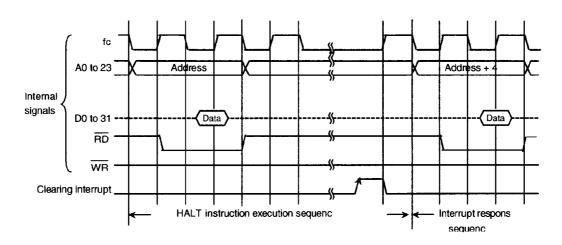

In Idle1 Mode, only the internal oscillator continue to operate. The system clock in the MCU stops.

In the Halt state, the interrupt request is sampled asynchronously with the system clock; however, clearance of the Halt state (i.e. restart of operation) is synchronous with it.

Figure 3.3.3 illustrates the timing for clearance of the Idle1 Mode Halt state by an interrupt.

Figure 3.3.3 Timing chart for Idle1 Mode Halt state cleared by interrupt

#### 3 Stop Mode

When Stop Mode is selected, all internal circuits stop, including the internal oscillator Pin status in Stop Mode depends on the settings in the WDMOD<DRVE> register. Table 3.3.5 summarizes the state of these pins in Stop Mode.

After Stop Mode has been cleared system clock output starts when the warm-up time and clock doubler stable time have elapsed, in order to allow oscillation and clock doubler to stabilize. Figure 3.3.4 illustrates the timing for clearance of the Stop Mode Halt state by an interrupt.

STOP mode can only be released by an NMI pin or INTO pin interrupt, or by reset.

When STOP mode is released by other than reset, the system clock starts its output after the time set by the warm-up counter for the internal oscillation to stabilize. When using reset to release stop mode, input reset signals long enough for stable oscillation and clock doubler stable time.

In systems with an external oscillator, the warm-up counter also operates when STOP mode is released. Therefore, such systems also require a warm-up time between input of release signals and system clock output.

Figure 3.3.4 Timing chart for Stop Mode Halt state cleared by interrupt

Table 3.3.4 Sample warm-up time and clock doubler stable time after clearance of Stop Mode fc=20MHz

|                          | CLKMOD <warm></warm>         |                              |  |

|--------------------------|------------------------------|------------------------------|--|

|                          | 0 1                          |                              |  |

| Warm-up tim              | 1.6 ms (2 <sup>15</sup> /fc) | 6.6 ms (2 <sup>17</sup> /fc) |  |

| Clock doubler stable tim | 1.6 ms (2 <sup>15</sup> /fc) | 1.6 ms (2 <sup>15</sup> /fc) |  |

Table 3.3.5 Pin states in Stop Mode

| Pin Names              | I/O         | <drve> = 0</drve> | <drve> = 1</drve>              |

|------------------------|-------------|-------------------|--------------------------------|

| P00 to 07              | Input Mode  | Invalid           | Invalid                        |

|                        | Output Mode | Output            | Output                         |

|                        | D0~D7       | High-z            | High-z                         |

| P40 to 47/A0 to 7      | Input Mode  | Invalid           | Invalid                        |

|                        | Output Mode | High-z            | Output                         |

| P70 to 75/ RD to WAIT  | Input Mode  | Invalid           | Invalid                        |

| *Except P74/CLKOUT2    | Output Mode | High-z            | Output                         |

| P74/CLKOUT2            | Input Mode  | Invalid           | Invalid                        |

|                        | Output Mode | High-z            | Output                         |

|                        | CLKOUT2     | Output            | Output                         |

| PC0 to PC5/TI0 to TO7  | Input Mode  | Invalid           | Invalid                        |

|                        | Output Mode | High-z            | Output                         |

| PD0 to PD7/TI8 to TOB  | Input Mode  | Invalid           | Invalid                        |

|                        | Output Mode | High-z            | Output                         |

| PF0 to PF7/TXD0 to RX  | Input Mode  | Invalid           | Invalid                        |

|                        | Output Mode | High-z            | Output                         |

| PG0 to PG7/AN0 to AN7  | Input Mode  | Invalid           | Invalid                        |

| PL0 to PL3/AN8 to AN11 | Input Mode  | Invalid           | Invalid                        |

| PM0 to PM7             | Input Mode  | invalid           | Invalid                        |

| /SS0 to SECLK1         | Output Mode | High-z            | Output                         |

| PN0 to PN5             | Input Mode  | Invalid           | Invalid                        |

| /SCK0 to SI1           | Output Mode | High-z            | Output                         |

| NMi                    | Input pin   | Input             | Input                          |

| INT0                   | Input pin   | Input             | Input                          |

| RESET                  | Input       | Input             | Input                          |

| AMO, AM1               | Input       | Input             | Input                          |

| TEST0, TEST1           | Input       | Input             | Input                          |

| X1                     | Input       | Invalid           | Invalid                        |

| X2                     | Output      | H Level Output    | H Level Output                 |

| CLKOUT1                | Output      | Output (PU)       | Output (PU) @TMP94FD53F (Note) |

|                        |             | Output            | Output @TMP92CW10F             |

Input: Input gate in operation. Input voltage should be fixed to L or H so that input pin stays constant.

Output: Output state

Invalid: Input pin invalid

High-z: Output pin High-Impedance

PU: A pull-up is always carried out.

Note: CLKOUT1 pin may be in the state of "Lo" level output at Stop mode.

Please set CLKMOD <CLKOE> bit to "0" and be sure to forbid CLKOUT1 output, before the

"HALT" instruction is executed.

#### 3.4 Interrupts

Interrupts are controlled by the CPU Interrupt Mask Register <IFF20> (reflected by bits 12 to 14 of the Status Register) and by the built-in interrupt controller.

The TMP92CW10 has a total of 58 interrupts divided into the following five types:

Interrupts generated by CPU: 9 sources

- Software interrupts: 8 sources

- Illegal Instruction interrupt: 1 source

Internal interrupts: 43 sources

- Internal I/O interrupts: 32 sources

- Micro DMA Transfer End interrupts: 8 sources

External interrupts: 9 sources

• Interrupts on external pins (NMI, INTO to INT7)

A fixed individual interrupt vector number is assigned to each interrupt source.

Any one of seven levels of priority can also be assigned to each maskable interrupt. Non-maskable interrupts have a fixed priority level of 7, the highest level.

When an interrupt is generated, the interrupt controller sends the priority of that interrupt to the CPU. When more than one interrupt are generated simultaneously, the interrupt controller sends the priority value of the interrupt with the highest priority to the CPU. (The highest priority level is 7, the level used for non-maskable interrupts.)

The CPU compares the interrupt priority level which it receives with the value held in the CPU Interrupt Mask Register <IFF2:0>. If the priority level of the interrupt is greater than or equal to the value in the Interrupt Mask Register, the CPU accepts the interrupt.

However, software interrupts and Illegal Instruction interrupts generated by the CPU are processed irrespective of the value in <IFF20>.

The value in the Interrupt Mask Register <IFF2:0> can be changed using the EI instruction (EI num sets <IFF2:0> to num). For example, the command EI 3 enables the acceptance of non-maskable interrupts and of maskable interrupts whose priority level, as set in the interrupt controller, is 3 or higher. The commands EI and EI 0 enable the acceptance of all non-maskable interrupts and of maskable interrupts with a priority level of 1 or above (hence both are equivalent to the command EI 1).

The DI instruction (sets <IFF2:0> to 7) is exactly equivalent to the EI 7 instruction. The DI instruction is used to disable all maskable interrupts (since the priority level for maskable interrupts ranges from 0 to 6). The EI instruction takes effect as soon as it is executed.

In addition to the general-purpose Interrupt Processing Mode described above, there is also a Micro DMA Processing Mode.

In Micro DMA Mode the CPU automatically transfers data in one-byte, two-byte or four-byte blocks; this mode allows high-speed data transfer to and from internal and external memory and internal I/O ports.

In addition, the TMP94FD53 also has a software start function in which micro DMA processing is requested in software rather than by an interrupt.

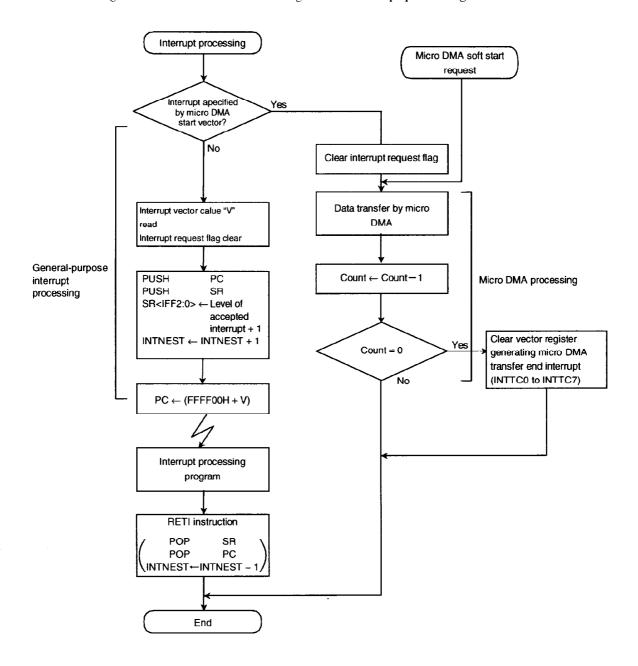

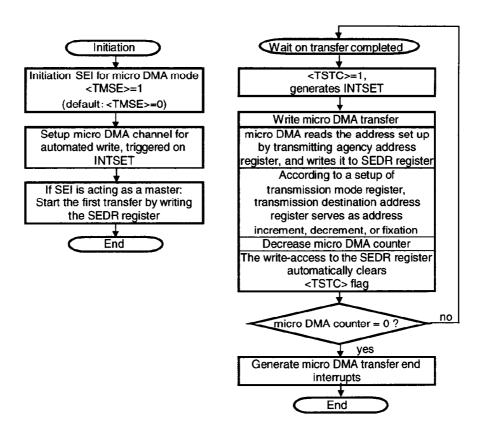

Figure 3.4.1 is a flowchart showing overall interrupt processing.

Figure 3.4.1 Interrupt and micro DMA processing sequence

#### 3.4.1 General-purpose interrupt processing

When the CPU accepts an interrupt, it usually performs the following sequence of operations. However, in the case of software interrupts and Illegal Instruction interrupts generated by the CPU, the CPU skips steps @ and @ and executes only steps @. @ and @.

- The CPU reads the interrupt vector from the interrupt controller. When more than one interrupt with the same priority level have been generated simultaneously, the interrupt controller generates an interrupt vector in accordance with the default priority and clears the interrupt requests. (The default priority is determined as follows: the smaller the vector value, the higher the priority.)

- The CPU pushes the Program Counter (PC) and Status Register (SR) onto the top of the stack (pointed to by XSP).

- The CPU sets the value of the CPUs Interrupt Mask Register <IFF2:0> to the priority level for the accepted interrupt plus 1. However, if the priority level for the accepted interrupt is 7, the register's value is set to 7.

- The CPU increments the interrupt nesting counter INTNEST by 1.

- The CPU jumps to the address given by adding the contents of address FFFF00H + the interrupt vector, then starts the interrupt processing routine.

On completion of interrupt processing, the RETI instruction is used to return control to the main routine. RETI restores the contents of the Program Counter and the Status Register from the stack and decrements the Interrupt Nesting counter INTNEST by 1. Non-maskable interrupts cannot be disabled by a user program. Maskable interrupts, however, can be enabled or disabled by a user program. A program can set the priority level for each interrupt source. (A priority level setting of 0 or 7 will disable an interrupt request.)

If an interrupt request is received for an interrupt with a priority level equal to or greater than the value set in the CPU Interrupt Mask Register <IFF20>. the CPU will accept the interrupt. The CPU Interrupt Mask Register <IFF20> is then set to the value of the priority level for the accepted interrupt plus 1.

If during interrupt processing, an interrupt is generated with a higher priority than the interrupt currently being processed, or if during the processing of a non-maskable interrupt processing, a non-maskable interrupt request is generated from another source, the CPU will suspend the routine which it is currently executing and accept the new interrupt. When processing of the new interrupt has been completed, the CPU will resume processing of the suspended interrupt.

If the CPU receives another interrupt request while performing processing steps ① to ⑤. the new interrupt will be sampled immediately after execution of the first instruction of its interrupt processing routine. Specifying DI as the start instruction disables nesting of maskable interrupts.

After a reset, initializes the Interrupt Mask Register <IFF20> to 111, disabling all maskable interrupts.

Table 3.4.1 shows the TMP92CW10 interrupt vectors and micro DMA start vectors. FFFF00H~FFFFFH (256 bytes) is designated as the interrupt vector area.

Table 3.4.1 TMP92CW10 interrupt vectors and micro DMA start vectors

| Default  | Туре     | Interrupt Source and Source of                     | Vector Value | Address refer to | Micro DMA    |

|----------|----------|----------------------------------------------------|--------------|------------------|--------------|

| Priority |          | Micro DMA Request                                  |              | Vector           | Start Vector |

| 1        |          | Reset or [SWI0] instruction                        | 0000H        | FFFF00H          |              |

| 2        |          | [SWI1] instruction                                 | 0004H        | FFFF04H          |              |

| 3        |          | Illegal instruction or [SWI2] instruction          | 0008H        | FFFF08H          |              |

| 4        |          | [SWI3] instruction                                 | 000CH        | FFFF0CH          |              |

| 5        | Non      | [SWI4] instruction                                 | 0010H        | FFFF10H          |              |

| 6        | maskable | [SWI5] instruction                                 | 0014H        | FFFF14H          |              |

| 7        |          | [SWI6] instruction                                 | 0018H        | FFFF18H          |              |

| 8        |          | [SW17] instruction                                 | 001CH        | FFFF1CH          |              |

| 9        |          | NMI: pin input                                     | 0020H        | FFFF20H          |              |

| 10       |          | INTWD: Watchdog Timer                              | 0024H        | FFFF24H          |              |

| 11       |          | INTO: INTO pin input                               | 0028H        | FFFF28H          | 0AH (Note1)  |

| 12       |          | INT1: INT1 pin input                               | 002CH        | FFFF2CH          | 0ВН          |

| 13       |          | INT2: INT2 pin input                               | 0030H        | FFFF30H          | 0CH          |

| 14       |          | INT3: INT3 pin input                               | 0034H        | FFFF34H          | ODH          |

| 15       |          | INT4: INT4 pin input                               | 0038H        | FFFF38H          | 0EH          |

| 16       |          | INT5: INT5 pin input                               | 003CH        | FFFF3CH          | 0FH          |

| 17       |          | INT6: INT6 pin input                               | 0040H        | FFFF40H          | 10H          |

| 18       |          | INT7: INT7 pin input                               | 0044H        | FFFF44H          | 11H          |

| 19       |          | INTT0: 8-bit timer 0                               | 0048H        | FFFF48H          | 12H          |

| 20       |          | INTT1: 8-bit timer 1                               | 004CH        | FFFF4CH          | 13H          |

| 21       |          | INTT2: 8-bit timer 2                               | 0050H        | FFFF50H          | 14H          |

| 22       |          | INTT3: 8-bit timer 3                               | 0054H        | FFFF54H          | 15H          |

| 23       |          | INTT4: 8-bit timer 4                               | 0058H        | FFFF58H          | 16H          |

| 24       |          | INTT5: 8-bit timer 5                               | 005CH        | FFFF5CH          | 17H          |

| 25       |          | INTT6: 8-bit timer 6                               | 0060H        | FFFF60H          | 18H          |

| 26       |          | INTT7: 8-bit timer 7                               | 0064H        | FFFF64H          | 19H          |

| 27       |          | INTTR8: 16-bit timer 8                             | 0068H        | FFFF68H          | 1AH          |

| 28       |          | INTTR9: 16-bit timer 8                             | 006CH        | FFFF6CH          | 1BH          |

| 29       |          | INTTRA: 16-bit timer A                             | 0070H        | FFFF70H          | 1CH          |

| 30       |          | INTTRB: 16-bit timer A                             | 0074H        | FFFF74H          | 1DH          |

| 31       | Maskable | INTTO8: 16-bit timer 8 (overflow)                  | 0078H        | FFFF78H          | 1EH          |

| 32       |          | INTTOA: 16-bit timer A (overflow)                  | 007CH        | FFFF7CH          | 1FH          |

| 33       |          | INTRX0: Serial receive (Channel 0)                 | 0080H        | FFFF80H          | -            |

| 34       |          | INTTX0: Serial transmission (Channel 0)            | 0084H_       | FFFF84H          | 21H          |

| 35       |          | INTRX1: Serial receive (Channel 1)                 | 0088H        | FFFF88H          |              |

| 36       |          | INTTX1: Serial transmission (Channel 1)            | 008CH        | FFFF8CH          | 23H          |

| 37       |          | (Reserved)                                         | 009011       | ГГГГ90Н          | -            |

| 38       |          | (Reserved)                                         | 0094H        | FFFF94H          | -            |

| 39       |          | (Reserved)                                         | 0098H        | FFFF98H          | -            |

| 40       |          | INTSEM0: SEI mode (Channel 0)                      | 009CH        | FFFF9CH          | -            |

| 41       |          | INTSEE0: SE transfer end / slave error (Channel 0) | 00A0H        | FFFFAOH          | -            |

| 42       |          | INTSER0: SEI receive (Channel 0)                   | 00A4H        | FFFFA4H          | 29H          |

| 43       |          | INTSET0: SEI transmission (Channel 0)              | 00A8H        | FFFFA8H          | 2AH          |

| 44       |          | INTSEM1: SEI mode (Channel 1)                      | 00ACH        | FFFFACH          | -            |

| 45       |          | INTSEE1: SE_transfer end / slave error (Channel 1) | 00В0Н        | FFFFB0H          | -            |

| 46       |          | INTSER1: SE_receive (Channel 1)                    | 00B4H        | FFFFB4H          | 2DH          |

| 47       |          | INTSET1: SEI transmission (Channel 1)              | 00B8H        | FFFFB8H          | 2EH          |

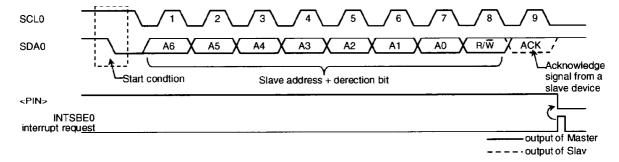

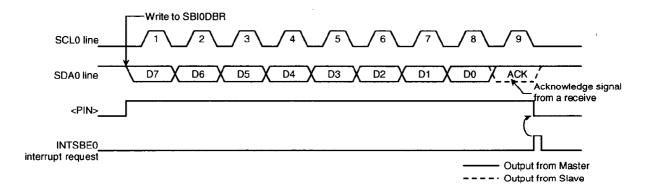

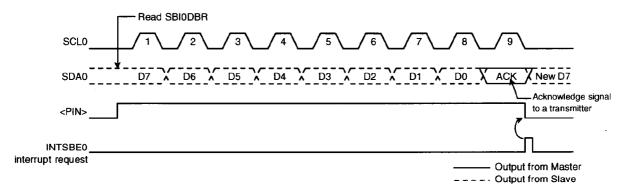

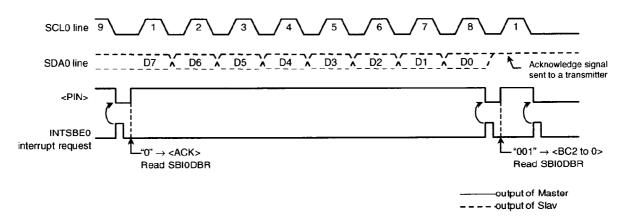

| 48       |          | INTSBE0: SB I2CBUS transfer end (Channel 0)        | 00BCH        | FFFFBCH          | 2FH          |

| 49       |          | INTSBS0: SBI I2CBUS stop condition (Channel 0)     | 00C0H        | FFFFC0H          | 30H          |

| 50       |          | INTSBE1: SBI I2CBUS transfer end (Channel 1)       | 00C4H        | FFFFC4H          | 31H          |

| 51 |          | INTSBS1: SBI I2CBUS stop condition (Channel 1) | 00C8H | FFFFC8H | 32H |

|----|----------|------------------------------------------------|-------|---------|-----|

| 52 | 7        | INTAD: AD conversion end                       | 00ССН | FFFFCCH | 33H |

| 53 |          | INTTC0: Micro DMA end (Channel 0)              | оорон | FFFFD0H | 34H |

| 54 | 7        | INTTC1: Micro DMA end (Channel 1)              | 00D4H | FFFFD4H | 35H |

| 55 |          | INTTC2: Micro DMA end (Channel 2)              | 00D8H | FFFFD8H | 36H |

| 56 |          | INTTC3: Micro DMA end (Channel 3)              | 00DCH | FFFFDCH | 37H |

| 57 | Maskable | INTTC4: Micro DMA end (Channel 4)              | 00E0H | FFFFE0H | 38H |

| 58 |          | INTTC5: Micro DMA end (Channel 5)              | 00E4H | FFFFE4H | 39H |

| 59 |          | INTTC6: Micro DMA end (Channel 6)              | 00E8H | FFFFE8H | зан |

| 60 |          | INTTC7: Micro DMA end (Channel 7)              | 00ECH | FFFFECH | звн |

| -  |          |                                                | оогон | FFFFF0H | -   |

| to |          | (reserved)                                     | :     | :       | to  |

| -  |          |                                                | 00FCH | FFFFFCH | -   |

Note1: When starting-up micro DMA, set at edge detect mode.

Note2: Micro DMA default priority

If an interrupt request is generated by micro DMA, the interrupt has a higher priority than any other maskable interrupt (irrespective of default channel priority).

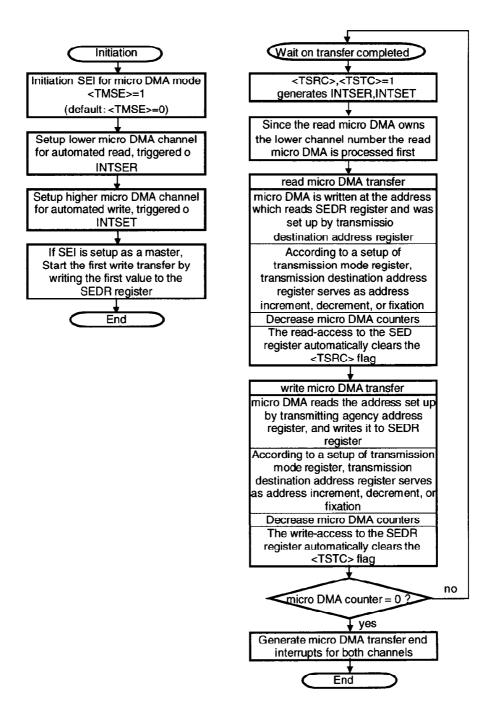

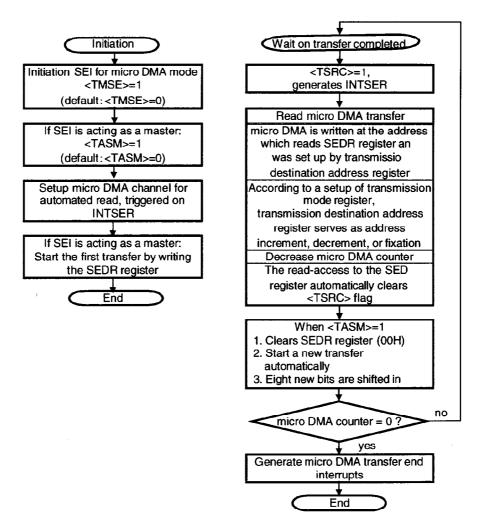

#### 3.4.2 Micro DMA processing

In addition to general-purpose interrupt processing, the TMP92CW10 also includes a micro DMA function. Micro DMA processing for interrupt requests set by micro DMA is performed at the highest priority level for maskable interrupts (level 6), regardless of the priority level of the interrupt source.

Micro DMA is suppoted 8 channels and can be transferred continuously by specifying the micro DMA burst function in the following.

#### (1) Micro DMA operation

When an interrupt request is generated by an interrupt source specified by the Micro DMA Start Vector Register, the micro DMA triggers a micro DMA request to the CPU at interrupt priority level 6 and starts processing the request. Theeight micro DMA channels allow micro DMA processing to be set for up to eight types of interrupt at once.

When micro DMA is accepted, the interrupt request flip-flop assigned to that channel is cleared. Data in one-byte or two-byte or four-byte blocks, is automatically transferred at once from the transfer source address to the transfer destination address set in the control register, and the transfer counter is decremented by 1. If the value of the counter after it has been decremented is not 0, DMA processing ends with no change in the value of the micro DMA start vector register. If the value of the decremented counter is 0, a Micro DMA Transfer End interrupt (INTTC0 to INTTC7) is sent from the CPU to the interrupt controller. In addition, the micro DMA start vector register is cleared to 0, the next micro DMA operation is disabled and micro DMA processing terminates.

If micro DMA requests are set simultaneously for more than one channel, priority is not based on the interrupt priority level but on the channel number: the lower the channel number, the higher the priority (Channel 0 thus has the highest priority and Channel the lowest).

If an interrupt request is triggered for the interrupt source in use during the interval between the time at which the micro DMA start vector is cleared and the next setting, general-purpose interrupt processing is performed at the interrupt level set. Therefore, if the interrupt is only being used to initiate micro DMA (and not as a general-purpose interrupt), the interrupt level should first be set to 0 (i.e. interrupt requests should be disabled).

If micro DMA and general-purpose interrupts are being used together as described above, the level of the interrupt which is being used to initiate micro DMA processing should first be set to a lower value than all the other interrupt levels. In this case, edge-triggered interrupts are the only kinds of general interrupts which can be accepted.

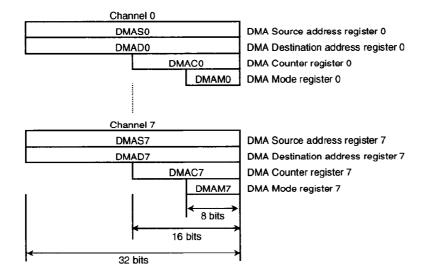

Although the control registers used for setting the transfer source and transfer destination addresses are 32 bits wide, this type of register can only output 24-bit addresses. Accordingly, micro DMA can only access 16 Mbytes (the upper eight bits of a 32-bit address are not valid).

Three micro DMA transfer modes are supported: one-byte transfers, two-byte (one-word) transfer and four-byte transfer. After a transfer in any mode, the transfer source and transfer destination addresses will either be incremented or decremented, or will remain unchanged. This simplifies the transfer of data from I/O to memory, from memory to I/O, and from I/O to I/O. For details of the various transfer modes, see Section 34.2 (1), Detailed description of the Transfer Mode Register.

Since a transfer counter is a 16-bit counter, up to 65536 micro DMA processing operations can be performed per interrupt source (provided that the transfer counter for the source is initially set to 0000H).

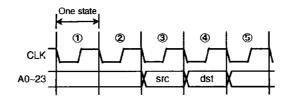

Micro DMA processing can be initiated by any one of 42 different interrupts—the 41 interrupts shown in the micro DMA start vectors in Table 34.1 and a micro DMA soft start. Figure 3.4.2 shows a 2-byte transfer carried out using a micro DMA cycle in Transfer Destination Address INC Mode (micro DMA transfers are the same in every mode except Counter Mode). (The conditions for this cycle are as follows: external 8-bit bus, 0 waits, and even-numbered transfer source and transfer destination addresses).

Figure 3.4.2 Timing for micro DMA cycle

States 1. 2: Instruction fetch cycle (prefetches the next instruction code)

State 3: Micro DMA read cycle

State 4: Micro DMA write cycle

State 5: (The same as in state 1. 2)

#### (2) Soft start function

The TMP92CW10 can initiate micro DMA either with an interrupt or by using the micro DMA soft start function, in which micro DMA is initiated by a Write cycle which writes to the register DMAR.

Writing 1 to any bit of the register DMAR causes micro DMA to be performed once. On completion of the transfer, the bits of DMAR which support the end channel are automatically cleared to 0.

When a burst is specified by the register DMAB, data is transferred continuously from the initiation of micro DMA until the value in the micro DMA transfer counter is 0.

| Symbol   | NAME    | Address | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0 |

|----------|---------|---------|-------|-------|-------|-------|-------|-------|-------|---|

| DMAR DMA | 109h    | DREQ7   | DREQ6 | DREQ5 | DREQ4 | DREQ3 | DREQ2 | DREQ1 | DREQ0 |   |

|          |         | R/W     |       |       |       |       |       |       |       |   |

|          | Request |         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0 |

DMAR must not be used any of the read-modify-write instructions.

#### (3) Transfer control registers

The transfer source address and the transfer destination address are set in the following registers. An instruction of the form LDC cr.r can be used to set these registers.

(4) Detailed description of the Transfer Mode Register

| DMAM[4:0] | Mode Description                                                                                    | Execution time |

|-----------|-----------------------------------------------------------------------------------------------------|----------------|

| 0 0 0 z z | Destination INC mode  (DMADn +) ← (DMASn)  DMACn ← DMACn − 1  if DMACn = 0 then INTTCn              | 5states        |

| 001zz     | Destination DEC mode  (DMADn →) ← (DMASn)  DMACn ← DMACn − 1  if DMACn = 0 then INTTCn              | 5states        |

| 0 1 0 z z | Source INC mode  (DMADn) ← (DMASn +)  DMACn ← DMACn − 1  if DMACn = 0 then INTTCn                   | 5states        |

| 011zz     | Source DEC mode  (DMADn) ← (DMASn -)  DMACn ← DMACn - 1  if DMACn = 0 then INTTCn                   | 5states        |

| 100zz     | Source and Destination INC mode  (DMADn +) ← (DMASn +)  DMACn ← DMACn − 1  If DMACn = 0 then INTTCn | 6states        |

| 101zz     | Source and Destination DEC mode  (DMADn →) ← (DMASn →)  DMACn ← DMACn − 1  If DMACn = 0 then INTTCn | 6states        |

| 1 1 0 z z | Destination and Fixed mode  (DMADn) ← (DMASn)  DMACn ← DMACn − 1  If DMACn = 0 then INTTCn          | 5states        |

| 1 1 1 z z | Gounter mode  DMASn ← DMASn + 1  DMACn ← DMACn − 1  if DMACn = 0 then INTTCn                        | 5states        |

ZZ: 00 = 1-byte transfer

01 = 2-byte transfer

10 = 4-byte transfer

11 = (reserved)

Note: The execution time is measured at 1states = 50ns operation @internal 20 MHz)

Note: n stands for the micro DMA channel number (0 to 7)

DMADn+/DMASn+: Post-increment (register value is incremented after transfer)

DMADn-/DMASn-: Post-decrement (register value is decremented after transfer)

#### 3.4.3 Interrupt controller operation

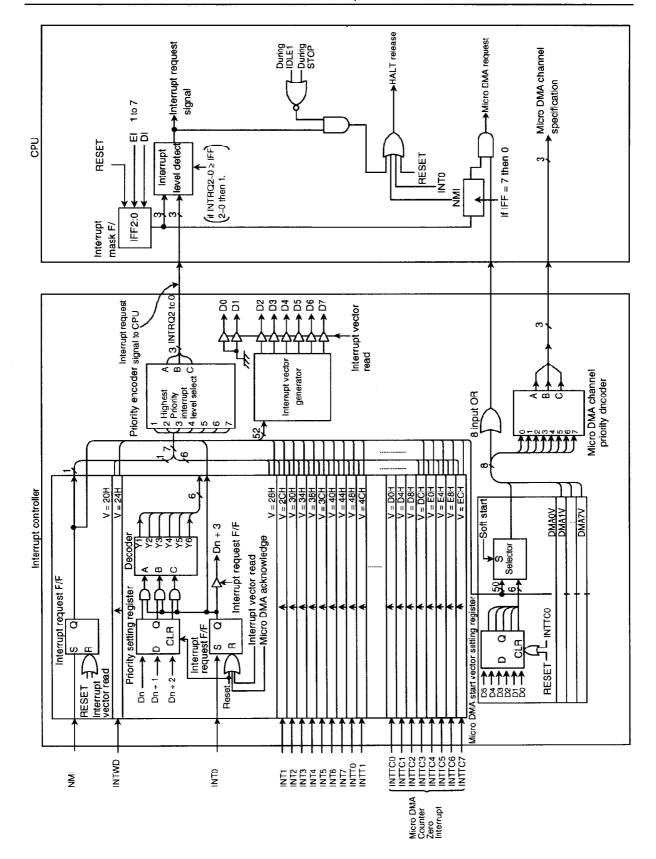

The block diagram in Figure 3.4.3 shows the interrupt circuits. The left-hand side of the diagram shows the interrupt controller circuit. The right-hand side shows the CPU interrupt request signal circuit and the halt release circuit.

For each of the 52 interrupt channels there is an interrupt request flag (consisting of a flip-flop), an interrupt priority setting register and a micro DMA start vector register. The interrupt request flag latches interrupt requests from the peripherals. The flag is cleared to zero in the following cases: when a Reset occurs, when the CPU reads the channel vector of an interrupt it has received, when the CPU receives a micro DMA request (when micro DMA is set), when a micro DMA burst transfer is terminated, and when an instruction that clears the interrupt for that channel is executed (by writting a micro DMA start vector to the INTCLR register).

An interrupt priority can be set independently for each interrupt source by writing the priority to the interrupt priority setting register (e.g. INTEOAD or INTE12). Six interrupt priorities levels (1 to 6) are provided. Setting an interrupt source's priority level to 0 (or 7) disables interrupt requests from that source. The priority of non-maskable interrupts (NMI pin interrupts and Watchdog Timer interrupts) is fixed at 7. If more than one interrupt request with a given priority level are generated simultaneously, the default priority (the interrupt with the lowest priority or, in other words, the interrupt with the lowest vector value) is used to determine which interrupt request is accepted first.

The 3rd and 7th bits of the interrupt priority setting register indicate the state of the interrupt request flag and thus whether an interrupt request for a given channel has occurred.

If several interrupts are generated simultaneously, the interrupt controller sends the interrupt request for the interrupt with the highest priority and the interrup's vector address to the CPU. The CPU compares the mask value set in <IFF2:0> of the Status Register (SR) with the priority level of the requested interrupt; if the latter is higher, the interrupt is accepted. Then the CPU sets SR <IFF20> to the priority level of the accepted interrupt, new interrupt requests with a priority value equal to or higher than the value set in SR <IFF2:0> (i.e. interrupts with a priority higher than the interrupt being processed) will be accepted.

When interrupt processing has been completed (i.e. after execution of a RETI instruction), the CPU restores to SR<IFF20> the priority value which was saved on the stack before the interrupt was generated.

The interrupt controller also includes eight registers which are used to store the micro DMA start vector. Writing the start vector of the interrupt source for the micro DMA processing (see Table 3.4.1), enables the corresponding interrupt to be processed by micro DMA processing. The values must be set in the micro DMA parameter registers (e.g. DMAS and DMAD) prior to micro DMA processing.

Figure 3.4.3 Block Diagram of Interrupt Controller

## (1) Interrupt priority setting registers

| Symbol   | NAME                    | Address | 7         | 6       | 5            | 4              | 3         | 2           | 1            | 0             |

|----------|-------------------------|---------|-----------|---------|--------------|----------------|-----------|-------------|--------------|---------------|

|          |                         |         |           | INT     | AD           |                |           | IN          | TO           |               |

| INTE0AD  | INTO & INTAD            | F0h     | IADC      | IADM2   | IADM1        | IADM0          | IOC       | IOM2        | [OM1         | IOMO          |

| INTEGAD  | Enable                  | FUII    | R         |         | R/W          |                | R         |             | R/W          |               |

|          |                         |         | 0         | 0       | 0            | 0              | 0         | 0           | 0            | 0             |

|          |                         |         |           | IN      | T2           |                |           | IN          | T1           |               |

| INTE12   | INT1 & INT2             | D0h     | I2C       | I2M2    | I2M1         | I2M0           | I1C       | I1M2        | I1M1         | I1M0          |

| 11112    | Enable                  | Duii    | R         |         | R/W          |                | R         |             | R/W          |               |

|          |                         |         | 0         | 0       | 0            | 0              | 0         | 0           | 0            | 0             |

|          |                         |         |           | IN      |              |                |           | IN          | Т3           |               |

| INTE34   | INT3 & INT4             | D1h     | I4C       | I4M2    | I4M1         | I4M0           | I3C       | I3M2        | I3M1         | I3M0          |

|          | Enable                  |         | R         |         | R/W          | y <del> </del> | R         |             | R/W          |               |

|          |                         |         | 0         | 0       | 0            | 0              | 0         | 0           | 0            | 0             |

|          |                         |         |           | ĮN'     | 1            |                |           | IN          |              |               |

| INTE56   | INT5 & INT6             | D2h     | I6C       | I6M2    | I6M1         | I6M0           | I5C       | I5M2        | I5M1         | I5M0          |

|          | Enable                  |         | R         |         | R/W          | T              | R         |             | R/W          |               |

|          |                         |         | 0         | 0       | 0            | 0              | 0         | 0           | 0            | 0             |

|          |                         |         |           |         | ,            |                |           | IN          |              |               |

| INTE7    | INT7                    | D3h     |           |         | -            | -              | I7C       | I7M2        | 17M1         | 17 <b>M</b> 0 |

|          | Enable                  |         |           |         |              |                | R         |             | R/W          |               |

|          |                         |         | -         | -<br>   | -<br>T:1\    |                | 0         | O<br>INTTO( | 0<br>Ti0)    | 0             |

|          | MITTO O MITTA           |         | IT10      | INTT1(  |              | TT1MO          | ITOO      | ITOM2       |              | ITOMO         |

| INTET01  | INTT0 & INTT1<br>Enable | D4h     | IT1C<br>R | IT1M2   | IT1M1<br>R/W | IT1M0          | ITOC<br>R | TTUMZ       | ITOM1<br>R/W | ІТОМО         |

|          |                         |         | 0         | 0       | 0            | 0              | 0         | 0           | 0            | 0             |

|          |                         |         | 0         | INTT3(  | _            |                |           | INTT2(      |              |               |

|          | INTT2 & INTT3           | D5h     | IT3C      | IT3M2   | IT3M1        | IT3M0          | IT2C      | IT2M2       | IT2M1        | IT2M0         |

| INTET23  | Enable                  |         | R         | 1131412 | R/W          | LIJIVIO        | R         | 1121412     | R/W          | 1121410       |

|          | Litable                 |         | 0         | 0       | 0            | 0              | 0         | 0           | 0            | 0             |

|          |                         |         |           | INTT5(  |              |                |           | INTT4(      |              |               |

|          | INTT4 & INTT5           |         | IT5C      | IT5M2   | IT5M1        | IT5M0          | IT4C      | IT4M2       | IT4M1        | IT4M0         |

| INTET45  | Enable                  | D6h     | R         | 1701112 | R/W          | 1101110        | R         |             | R/W          |               |

|          |                         |         | 0         | 0       | 0            | 0              | 0         | 0           | 0            | 0             |

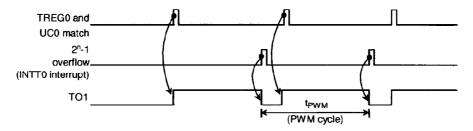

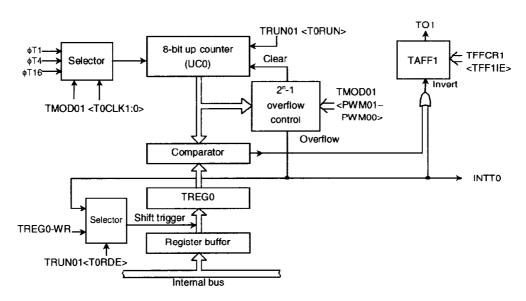

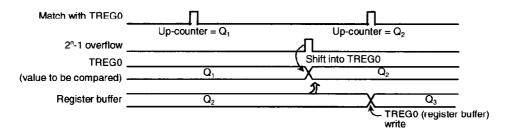

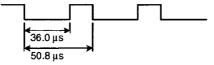

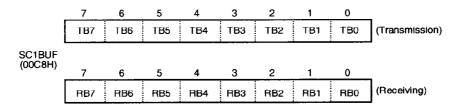

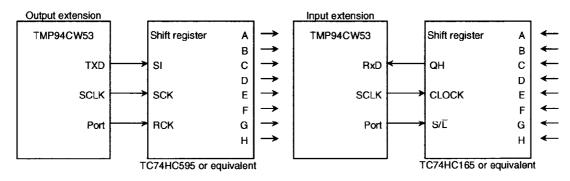

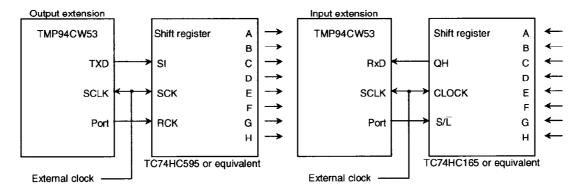

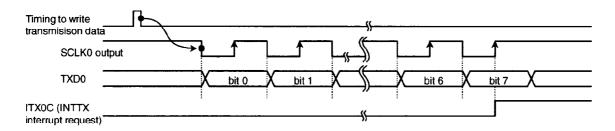

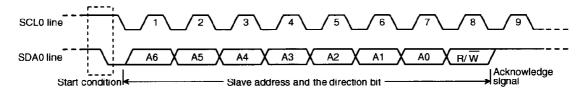

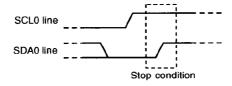

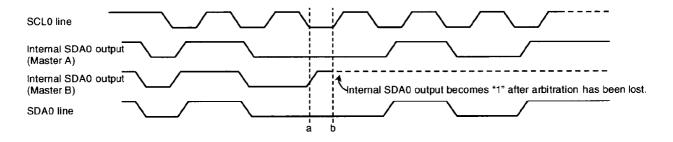

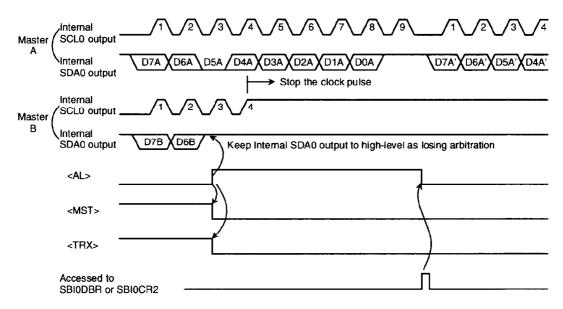

|          |                         |         |           | INTT7(  |              | <u> </u>       | Ť         | INTT6(      | Timer6)      | · · · · ·     |