80186

## 80186

## High Integration 16-Bit Microprocessor iAPX86 Family

## DISTINCTIVE CHARACTERISTICS

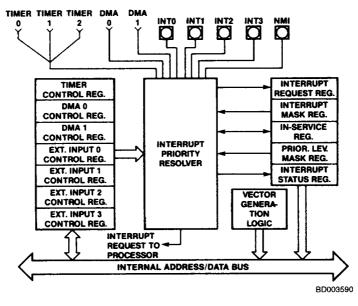

- Integrated feature set Enhanced 10 MHz 8086-1 CPU Clock generator Two independent, high-speed DMA channels Programmable interrupt controller Three programmable 16-bit timers Programmable memory and peripheral chip-select logic Programmable wait state generator

- Local bus controller

- Available in 10 MHz (80186-10), 8 MHz (80186)

- High performance processor Two times the performance of the standard 8086 4M byte/sec bus bandwidth interface

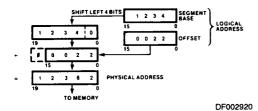

- Direct addressing capability to 1M byte of memory

- · Completely object code compatible with all existing iAPX 86, 88 software Ten new instruction types Compatible with 29843/45, 29833/63, 8284, and 8288 bus support components

- Optional numeric processor extension

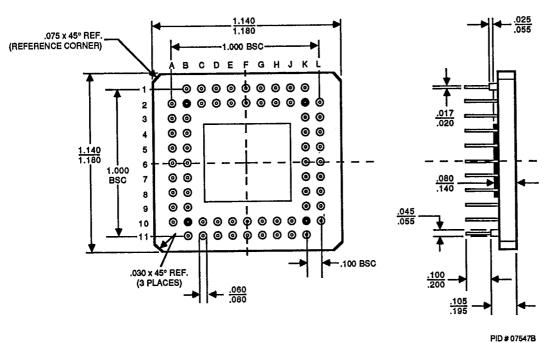

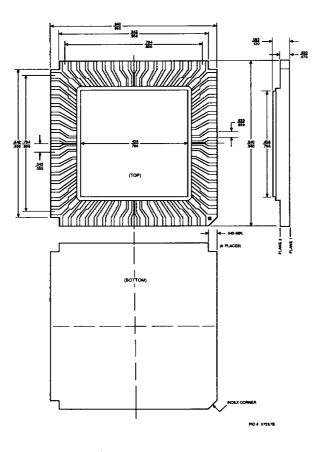

- Available in 68-pin Plastic Leaded Chip Carrier (PLCC), Ceramic Leadless Chip Carrier (LCC), and Pin Grid Array (PGA) packages.

## **GENERAL DESCRIPTION**

The 80186 is a highly integrated 16-bit microprocessor. It effectively combines 15-20 of the most common iAPX 86 system components onto one. The 80186 provides two times greater throughput than the standard 5 MHz 8086. The 80186 is upward compatible with 8086 and 8088 software and adds 10 new instruction types to the existing set.

The 80186 comes in a 68-pin package and requires a single +5 V power supply.

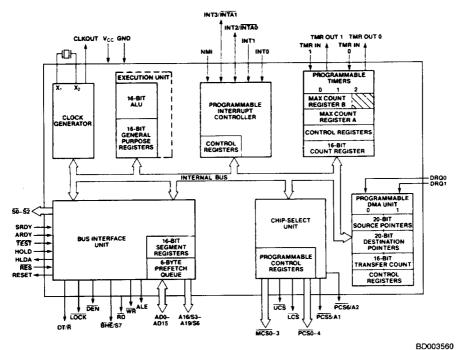

### **BLOCK DIAGRAM**

Figure 1.

Amendment Publication # Rev.

Issue Date: March 1989

Advanced Micro Devices

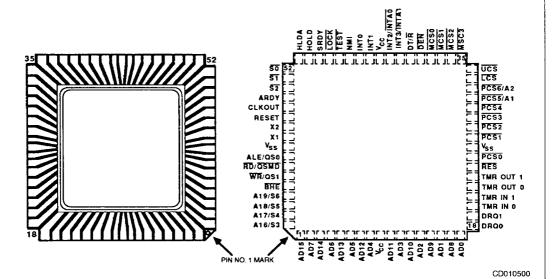

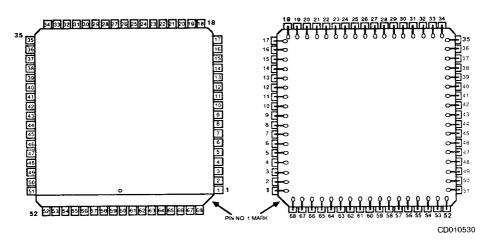

#### CONNECTION DIAGRAMS

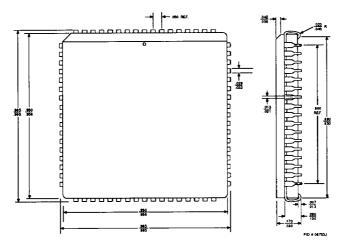

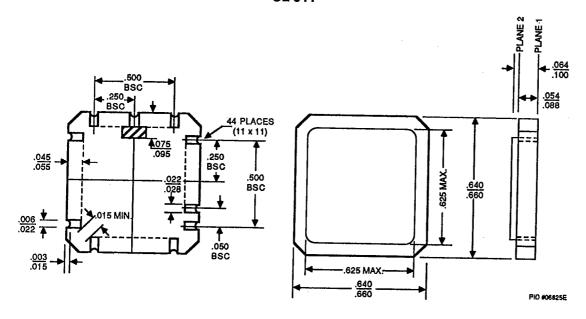

## Ceramic Leadless Chip Carrier (LCC\*)

Top

Bottom

\*LCC package placed in socket top down.

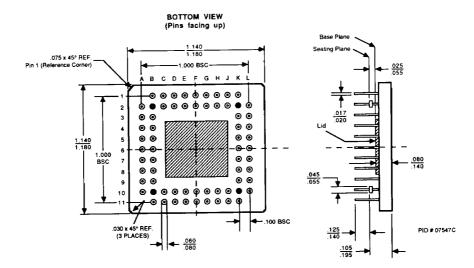

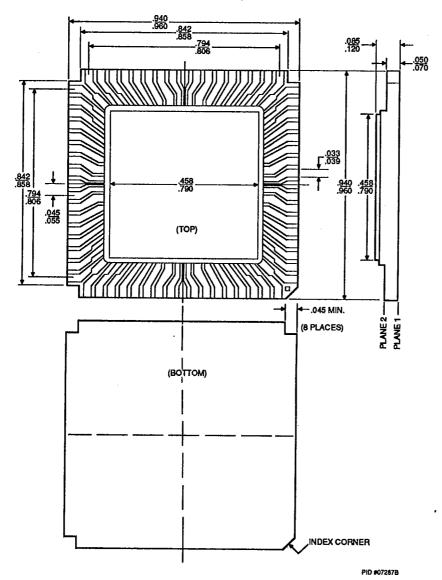

## Pin Grid Array (PGA)

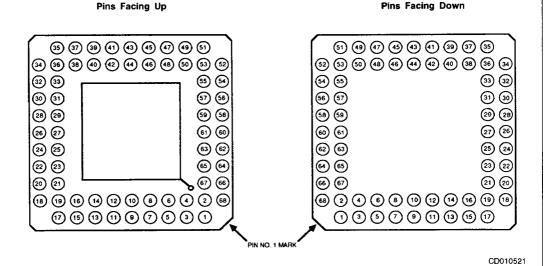

## CONNECTION DIAGRAMS (Cont'd.)

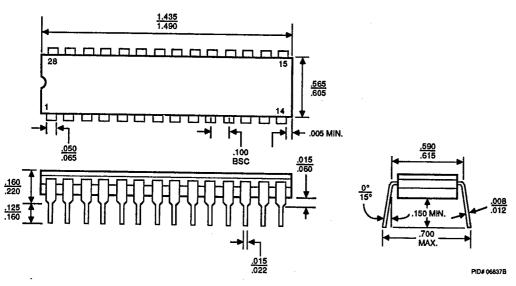

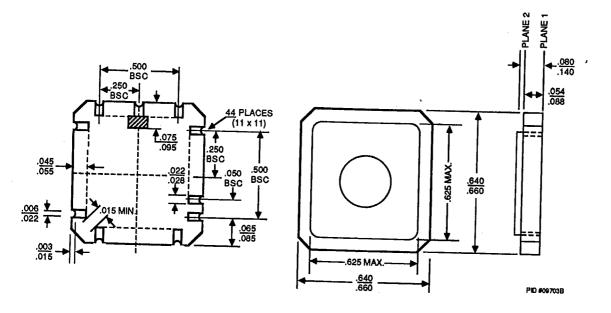

Plastic Leaded Chip Carrier (PLCC\*\*)

Тор

Bottom

\*\*PLCC package placed in socket top up. (PLCC pin-out same as LCC.)

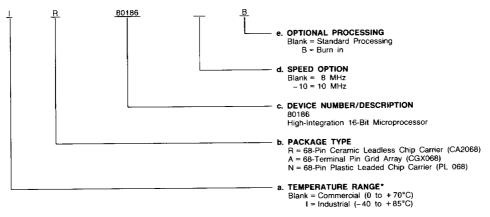

## ORDERING INFORMATION

## **Commodity Products**

AMD commodity products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Temperature Range

- b. Package Type

- c. Device Number

- d. Speed Option

- e. Optional Processing

| Valid Combinations |          |  |  |

|--------------------|----------|--|--|

|                    | 80186    |  |  |

| A, R, N            | 80186-10 |  |  |

| A, R, IA, IR       | 80186B   |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

## PIN DESCRIPTION

| Pin No.            | Name                                   | 1/0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description                                                       |                                                                                                         |  |

|--------------------|----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| 9, 43              | Vcc, Vcc                               | 1                | System Power: +5 v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | olt power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ٠,                                                                |                                                                                                         |  |

| 26, 60             | V <sub>SS</sub> , V <sub>SS</sub>      | 1 1              | System Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

| 57                 | RESET                                  | 0                | Reset Output indicates that the 80186 CPU is being reset; and can be used as a system reset. It is active HIGH, synchronized with the processor clock, and lasts an integer number of clock period corresponding to the length of the RES signal.                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

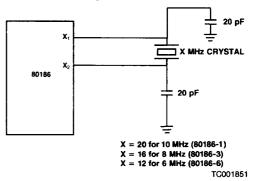

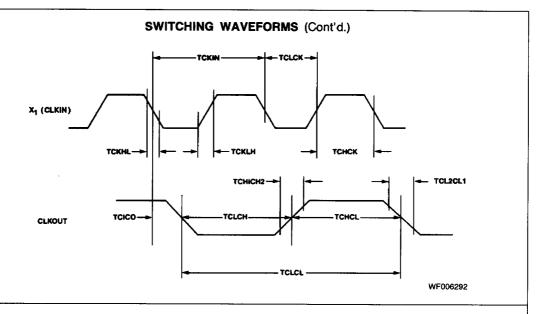

| 59, 58             | X1, X2                                 | 1                | Crystal inputs, X1 and X2, provide an external connection for a fundamental mode parallel resonal crystal for the internal crystal oscillator. X1 can interface to an external clock instead of a crystal. The input or oscillator frequency is internally divided by two to generate the clock signal (CLKOUT).                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

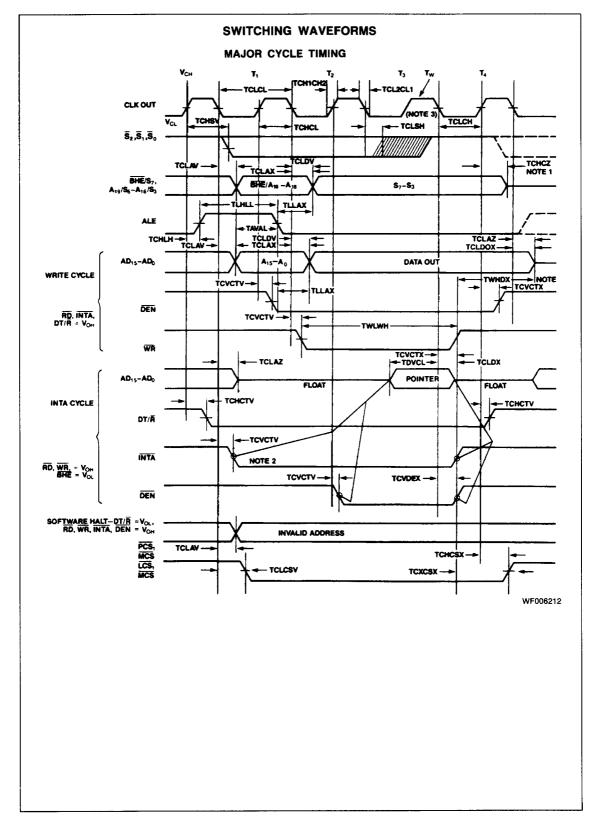

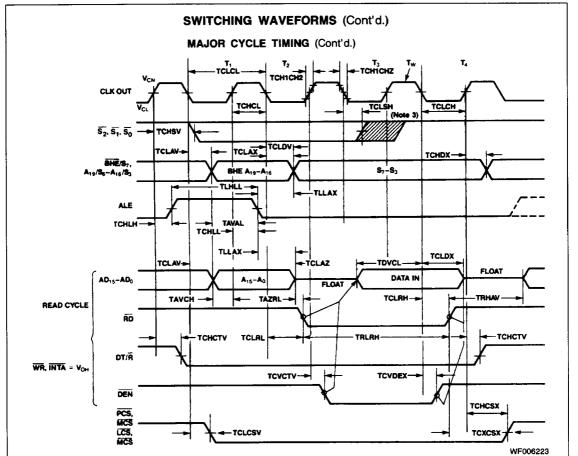

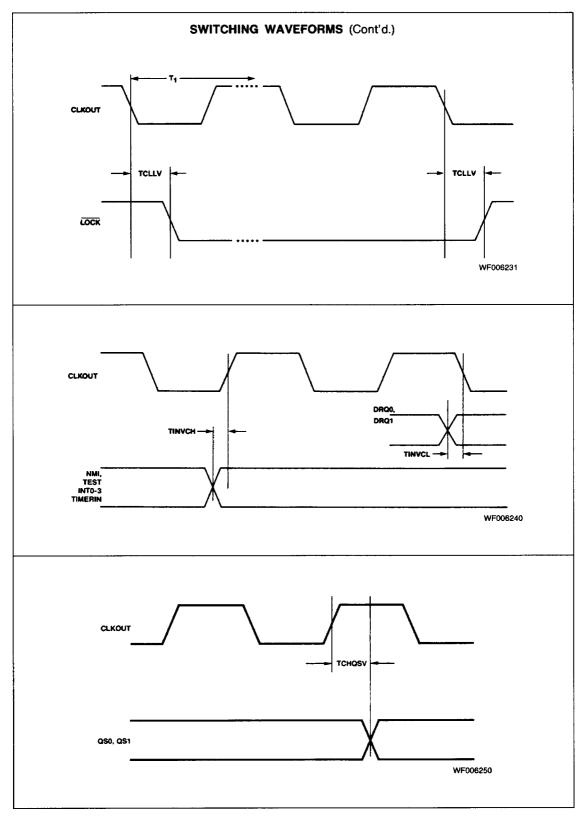

| 56                 | CLKOUT                                 | 0                | Clock Output provides the system with a 50% duty cycle waveform. All device pin timings are specifical relative to CLKOUT. CLKOUT has sufficient MOS drive capabilities for a numeric processor extension.                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

| 24                 | RES                                    | 1                | and enter a dormant fetching instructions a LOW for greater than HIGH transition of RI provided with a Schm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | System Reset causes the 80186 to immediately terminate its present activity, clear the internal logic and enter a dormant state. This signal may be asynchronous to the 80186 clock. The 80186 begin fetching instructions approximately 7 clock cycles after RES is returned HIGH. RES is required to be LOW for greater than 4 clock cycles and is internally synchronized. For proper initialization, the LOW-to HIGH transition of RES must occur no sooner than 50 microseconds after power up. This input i provided with a Schmitt-trigger to facilitate power-on RES generation via an RC network. When REs occurs, the 80186 will drive the status lines to an inactive level for one clock, and then tri-state them |                                                                   |                                                                                                         |  |

| 47                 | TEST                                   | l                | instruction execution will resume. If interruption the input is synchro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | will suspend. TES<br>ots are enabled w<br>nized internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | T will be resampled until it go<br>while the 80186 is waiting for | when "WAIT" execution begins,<br>bes LOW, at which time execution<br>TEST, interrupts will be serviced. |  |

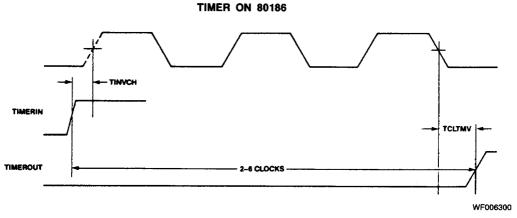

| 20<br>21           | TMR in 0,<br>TMR IN1                   | I<br>I           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   | pon the programmed timer mode.<br>nted) and internally synchronized.                                    |  |

| 22<br>23           | TMR OUT 0,<br>TMR OUT 1                | 0                | Timer outputs are use timer mode selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d to provide single                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | e pulse or continuous wavefor                                     | m generation, depending upon the                                                                        |  |

| 18<br>19           | DRQ0<br>DRQ1                           | I<br>I           | perform a transfer. T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | hese signals are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | active HIGH, level-triggered                                      | at a DMA channel (Channel 0 or 1)<br>l, and internally synchronized.                                    |  |

| 46                 | NMI                                    |                  | Non-Maskable Interrupt is an edge-triggered input which causes a type 2 interrupt. NMI is not maskable internally. A transition from a LOW to HIGH initiates the interrupt at the next instruction boundary. NMI is latched internally. An NMI duration of one clock or more will guarantee service. This input is internally synchronized.                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

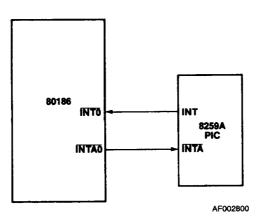

| 45, 44<br>42<br>41 | INTO, INT1<br>INT2/INTAO<br>INT3/INTA1 | <br>  1/0<br> /0 | Maskable Interrupt Requests can be requested by strobing one of these pins. When configured as inputs, these pins are active HIGH. Interrupt Requests are synchronized internally. INT2 and INT3 may be configured via software to provide active-LOW interrupt-acknowledge output signals. All interrupt inputs may be configured via software to be either edge- or level-triggereed. To ensure recognition, all interrupt requests must remain active until the interrupt is acknowledged. When iRMX mode is selected, the function of these pins changes (see Interrupt Controller section of this data sheet). |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

| 65-68              | A19/S6,<br>A18/S5,<br>A17/S4,          | 0 0 0            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | als are active HIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   | four most significant address bits, status information is available on                                  |  |

|                    | A16/S3                                 | "                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Low                                                               | High                                                                                                    |  |

|                    |                                        |                  | S6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Processor Cycle                                                   | DMA Cycle                                                                                               |  |

|                    |                                        |                  | S3, S4, and S5 are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | defined as LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | during T2-T4.                                                     |                                                                                                         |  |

| 10-17<br>1-8       | AD15-AD0                               | 1/0              | Address/Data Bus (0-15) signals constitute the time multiplexed memory or I/O address (T <sub>1</sub> ) and data (T <sub>2</sub> , T <sub>3</sub> , T <sub>W</sub> , and T <sub>4</sub> ) bus. The bus is active HIGH. A <sub>0</sub> is analogous to BHE for the lower byte of the data bus, pins D <sub>7</sub> through D <sub>0</sub> . It is LOW during T <sub>1</sub> when a byte is to be transferred onto the lower portion of the bus in memory or I/O operations.                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

| 64                 | BHE/S7                                 | 0                | During T <sub>1</sub> the Bus High Enable signal should be used to determine if data is to be enabled onto t most significant half of the data bus, pins D <sub>15</sub> -D <sub>8</sub> . BHE is LOW during T <sub>1</sub> for read, write, an intermacknowledge cycles when a byte is to be transferred on the higher half of the bus. The S <sub>7</sub> stat information is available during T <sub>2</sub> , T <sub>3</sub> , and T <sub>4</sub> . S <sub>7</sub> is logically equivalent to BHE. The signal is act LOW, and is tristated OFF during bus HOLD.                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

|                    |                                        |                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BHE and A0 Encodings                                              |                                                                                                         |  |

|                    |                                        |                  | BHE Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A0 Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                   | nction                                                                                                  |  |

|                    |                                        |                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Work Transfer                                                     | olf of data hue (D15 D9)                                                                                |  |

|                    |                                        |                  | 0 1 Byte Transfer on upper half of data but 1 0 Byte Transfer on lower half of data but                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

|                    |                                        |                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reserved                                                          | J. data 500 (D/-D(J)                                                                                    |  |

|                    | ļ                                      | <u> </u>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

| 61                 | ALE/QS0                                | 0                | Address Latch Enable/Queue Status 0 is provided by the 80186 to latch the address into the 8282/8283 address latches. ALE is active HIGH. Addresses are guaranteed to be valid on the trailing edge of ALE. The ALE rising edge is generated off the rising edge of the CLKOUT immediately preceding T1 of the associated bus cycle, effectively one-half clock cycle earlier than in the standard 8086. The trailing edge is generated off the CLKOUT rising edge in T1 as in the 8086. Note that ALE is never floated.                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                         |  |

| Pin No. | Name                          | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                               |

|---------|-------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3       | WR/QS1 0                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Write Strobe/Queue Status 1 indicates that the data on the bus is to be written into a memory or an I device. WR is active for T <sub>2</sub> , T <sub>3</sub> , and T <sub>W</sub> of any write cycle. It is active LOW, and floats during "HOLD, is driven HIGH for one clock during Reset, and then floated. When the 80186 is in queue status mo the ALE/QS0 and WR/QS1 pins provide information about processor/instruction queue interacti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | i "HOLD."<br>itatus mod                                                                                                                                       |

|         |                               |     | 1 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | QS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | QS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Queue Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                               |