# OMAP5912 Applications Processor Silicon Errata

SPRZ209K December 2003 – Revised December 2007

### **Contents**

| 1 Introduction |                                                                           |                                                               |               | . 7                                                                                         |      |  |

|----------------|---------------------------------------------------------------------------|---------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------|------|--|

|                | 1.1                                                                       | Device                                                        | and Develop   | ment-Support Tool Nomenclature                                                              | . 7  |  |

| 2              | Impo                                                                      | ortant Notices and Information About OMAP5912                 |               |                                                                                             |      |  |

|                | 2.1 Useful Information Regarding TMS320C55x Assembler Diagnostic Messages |                                                               |               | egarding TMS320C55x Assembler Diagnostic Messages                                           | 10   |  |

|                |                                                                           | 2.1.1                                                         | ERROR Diag    | nostics                                                                                     | 10   |  |

|                |                                                                           | 2.1.2                                                         | WARNING Di    | agnostics                                                                                   | 10   |  |

|                |                                                                           | 2.1.3                                                         |               | gnostics                                                                                    |      |  |

| 3              | Usa                                                                       | _                                                             |               |                                                                                             |      |  |

|                |                                                                           |                                                               |               | Bits Clear Procedure is not Correctly Documented in OMAP Reference Guide                    |      |  |

|                |                                                                           |                                                               |               | Speed on OMAP3.2                                                                            |      |  |

|                |                                                                           |                                                               |               | endation for Clock Gating clk16x                                                            |      |  |

|                |                                                                           |                                                               | •             | on Will Increase Power Consumption on CV <sub>DD</sub> Power                                |      |  |

|                |                                                                           |                                                               |               | ansmit Mode Definition                                                                      |      |  |

|                |                                                                           |                                                               |               | ansmit Mode Definition                                                                      |      |  |

|                |                                                                           |                                                               |               | ock Rules                                                                                   |      |  |

|                |                                                                           | Dynamic Switch Locked if DSP Reset Occurs During a DSP Access |               |                                                                                             |      |  |

|                |                                                                           | •                                                             |               | ved Between Production and Engineering OMAP5912                                             |      |  |

| 4              | DSP                                                                       |                                                               |               | es                                                                                          |      |  |

|                | 4.1                                                                       | •                                                             |               |                                                                                             |      |  |

|                |                                                                           |                                                               | CACHE_1       | DSP ICACHE is Servicing a Missed Program Bus Request During a                               |      |  |

|                |                                                                           |                                                               |               | RAMSET Preload                                                                              | . 14 |  |

|                | 4.2                                                                       | DSP Emulation Advisories                                      |               |                                                                                             | 16   |  |

|                |                                                                           | DSP_E                                                         | MU_1          | DSP IDLE Interrupt Not Serviced When Emulator is Connected                                  | 16   |  |

|                |                                                                           | DSP_E                                                         | MU_2          | Bad RTCK Clock Signal May Cause JTAG Communication Failure between the OMAP and an Emulator | . 17 |  |

|                | 4.3                                                                       | DSP S                                                         | ystem Advisoı | ries                                                                                        | 18   |  |

|                |                                                                           | DSP_S                                                         | SYS_1         | Use Caution When Reading Following a Configuration Change on the DSP                        | 18   |  |

|                |                                                                           | DSP_S                                                         | SYS_2         | Users of (JTAG) RTDX are Advised Not to Put the DSP Domain Into Idle                        | . 18 |  |

|                |                                                                           | DSP_S                                                         | SYS_3         | DSP IDLE Wakeup With Program Code in External Memory and EMIF Domain in IDLE Hangs          | . 19 |  |

|                |                                                                           | DSP_S                                                         | SYS_4         | DM Timer Incorrect Value Read During DSP Access and Value Change                            | . 19 |  |

|                |                                                                           | DSP_S                                                         | SYS_5         | DSP STIO Interrupt Generation is Not Possible                                               | 20   |  |

|                | 4.4                                                                       | DSP Direct Memory Access (DMA) Advisories                     |               |                                                                                             |      |  |

|                |                                                                           | DSP_D                                                         | DMA_1         | DSP DMA IDLE Prevents Transfer Completion                                                   | 21   |  |

|                |                                                                           | DSP_D                                                         | MA_2          | DSP EMIF/DMA Port Hangs During EMIF Bus Error                                               | 21   |  |

|                |                                                                           |                                                               |               |                                                                                             |      |  |

| 5 | MPU                               | U Subsystem Advisories                       |                                                                                                        |    |  |  |

|---|-----------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------|----|--|--|

|   | 5.1                               | System Direct Memory Access (DMA) Advisories |                                                                                                        |    |  |  |

|   |                                   | SYS_DMA_1                                    | System DMA CSAC and CDAC Not Showing Correct Value Consistently                                        | 22 |  |  |

|   |                                   | SYS_DMA_2                                    | Cannot Get SysDMA to Complete Data Transfer Out of UART                                                | 22 |  |  |

|   |                                   | SYS_DMA_3                                    | DMA Synchronized Transfers Can Be Stalled                                                              | 23 |  |  |

|   | 5.2 MPU Emulation Advisories      |                                              |                                                                                                        | 24 |  |  |

|   |                                   | MPU_EMU_1                                    | Emulation is Intrusive to ARM Idle Mode: Cannot Stop the CPU Clock With Code Composer Studio Connected | 24 |  |  |

|   | 5.3                               | MPU System Advisor                           | ries                                                                                                   | 25 |  |  |

|   |                                   | MPU_SYS_1<br>MPU_SYS_2                       | STANDBY Mode Not Entered After Execution of WFI Instruction                                            |    |  |  |

|   |                                   | MPU_SYS_3                                    | External Device Power Control is Broken                                                                | 25 |  |  |

|   |                                   | MPU_SYS_4                                    | Emulation Causes OMAP Not to Enter Deep Sleep                                                          | 26 |  |  |

|   |                                   | MPU_SYS_5                                    | Write Followed by Immediate Read not Supported on the Rhea Switch Peripheral $$ . $$                   |    |  |  |

|   |                                   | MPU_SYS_6                                    | When Absent, the OMAP Peripheral Clock Prevents Deep Sleep Entry                                       |    |  |  |

|   |                                   | MPU_SYS_7                                    | MPU IRQ122–127 Can Cause Spurious Interrupts                                                           |    |  |  |

|   |                                   | MPU_SYS_8                                    | If BVLZ is Not Configured, the Corresponding Interrupt Must be Masked                                  |    |  |  |

|   |                                   | MPU_SYS_9                                    | Access to the OMAP3.2 ARM_CLKM Registers                                                               |    |  |  |

|   |                                   | MPU_SYS_10                                   | WFI Instruction Loses 2–4 Instruction Fetches                                                          | 29 |  |  |

|   | 5.4                               | MPU/Watchdog Time                            | r Advisories                                                                                           | 31 |  |  |

|   |                                   | MPU_WATCHDOG_1                               | MPU Watchdog Does Not Reset DPLL                                                                       | 31 |  |  |

|   |                                   | MPU_WATCHDOG_2                               | The Secure Watchdog Register Reads Can Return Wrong Value Under Some Clock Configurations              | 32 |  |  |

| 6 | Traff                             | ffic Controller Subsystem Advisories3        |                                                                                                        |    |  |  |

|   | 6.1                               | EMIF Slow (EMIFS) Advisories                 |                                                                                                        |    |  |  |

|   |                                   | EMIFS_1                                      | Unexpected FCLK on EMIFS When Dynamic Wait State is Selected                                           | 33 |  |  |

|   |                                   | EMIFS_2                                      | Program Fetch From External Memory at Address 0x3C18 Results in Processor Reset                        | 33 |  |  |

|   | 6.2 EMIF Fast (EMIFF) Advisories  |                                              | dvisories                                                                                              | 34 |  |  |

|   |                                   | EMIFF_1                                      | MRS/EMRS Command Issued Twice SDRAM Interface                                                          | 34 |  |  |

|   |                                   | EMIFF_2                                      | Limitation of the EMIFF Not Mentioned in Reference Guide                                               | 34 |  |  |

|   |                                   | EMIFF_3                                      | Using EMIFF POM0 Mode May Result in Data Read Corruption                                               | 35 |  |  |

|   |                                   | EMIFF_4                                      | Only 725 DLL is Supported on the EMIFF                                                                 |    |  |  |

|   |                                   | EMIFF_5                                      | The EMIFF Autoclock Feature Affects the DLL Behavior                                                   | 36 |  |  |

|   | 6.3 Traffic Controller Advisories |                                              |                                                                                                        | 37 |  |  |

|   |                                   | TC_1                                         | OMAP5912 Global Software Reset Affects Traffic Controller Frequency                                    | 37 |  |  |

| 7 | OMA  | OMAP5912 Peripheral Advisories                     |                                                                                                                                        |      |  |  |  |

|---|------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

|   | 7.1  | Multimedia Card/Secure Digital (MMC/SD) Advisories |                                                                                                                                        |      |  |  |  |

|   |      | MMC_SD_1                                           | CMD12 Implementation in TI MMC/SDIO                                                                                                    | . 39 |  |  |  |

|   |      | MMC_SD_2                                           | SPI Mode Not Supported on the MMC/SD Peripheral                                                                                        | . 39 |  |  |  |

|   |      | MMC_SD_3                                           | MMC1 Internal Pullups are Not Software-Controllable                                                                                    |      |  |  |  |

|   |      | MMC_SD_4                                           | CMD1 Implementation in TI MMC/SDIO IP May Cause Missing EOC Interrupt                                                                  |      |  |  |  |

|   | 7.2  | MICROWIRE Adviso                                   | ories                                                                                                                                  | . 41 |  |  |  |

|   |      | UWIRE_1                                            | MICROWIRE Interface RX Data Failures Possible                                                                                          |      |  |  |  |

|   |      | UWIRE_2                                            | Bit 14 of CSR Not Reset                                                                                                                | . 43 |  |  |  |

|   | 7.3  | Inter-Integrated Circ                              | cuit (I <sup>2</sup> C) Advisories                                                                                                     | . 44 |  |  |  |

|   |      | I2C_1                                              | I <sup>2</sup> C Random Duplication of Byte When Sending Long Messages                                                                 | . 44 |  |  |  |

|   | 7.4  | Universal Serial Bus                               | Universal Serial Bus (USB) Host Advisories                                                                                             |      |  |  |  |

|   |      | USB_HOST_1                                         | USB Host Fails to Receive the First Packet Sent After Remote Wakeup                                                                    | . 49 |  |  |  |

|   |      | USB_HOST_2                                         | USB Device Controller Remote Wake-Up Feature May Fail                                                                                  | . 49 |  |  |  |

|   | 7.5  | Universal Serial Bus                               | Universal Serial Bus (USB) On-the-Go (OTG) Controller Advisories                                                                       |      |  |  |  |

|   |      | USB_OTG_1                                          | Specification for TA_WAIT_BCON                                                                                                         | . 50 |  |  |  |

|   |      | USB_OTG_2                                          | USB OTG TA_WAIT_VRISE is Set at 200 ms                                                                                                 |      |  |  |  |

|   |      | USB_OTG_3                                          | USB OTG Timings Do Not Comply With USB OTG Specifications Rev. 1.0a                                                                    |      |  |  |  |

|   |      | USB_OTG_4                                          | USB OTG DMA Requests Control Bits Cannot Be Read Back                                                                                  |      |  |  |  |

|   |      | USB_OTG_5<br>USB_OTG_6                             | USB OTG A-Device State Machine Does Not Comply With OTG Specification  USB OTG Registers are Set to 0x0 After UHOST_EN Bit is Set to 0 |      |  |  |  |

|   | 7.6  |                                                    | es                                                                                                                                     |      |  |  |  |

|   | 7.0  |                                                    |                                                                                                                                        |      |  |  |  |

|   |      | TIMER32K_1                                         | Timer32K Reload TRB Bit Does Not Work Properly                                                                                         |      |  |  |  |

|   | 7.7  | Microprocessor Unit I/O (MPUIO) Advisories         |                                                                                                                                        |      |  |  |  |

|   |      | MPUIO_1                                            | MPUIO Input Latch Register is Disabled During TIPB Read Access to it                                                                   |      |  |  |  |

|   |      | MPUIO_2                                            | MPUIO GPIO_INT is no Longer Generated                                                                                                  |      |  |  |  |

|   | 7.8  | Pulse-Width Tone (PWT) Advisories                  |                                                                                                                                        |      |  |  |  |

|   |      |                                                    | Write Followed by Immediate Read Not Supported on the PWT Peripheral                                                                   |      |  |  |  |

|   | 7.9  | Camera Interface Advisories                        |                                                                                                                                        |      |  |  |  |

|   |      | CAM_1                                              | Interrupt Observability on Camera Port                                                                                                 |      |  |  |  |

|   |      | CAM_2                                              | Peculiar Sequence Needed to Reset Camera FIFO Using the RAZ_FIFO Bit                                                                   | . 57 |  |  |  |

|   | 7.10 | Universal Asynchro                                 | nous Receiver/Transmitter (UART) Advisories                                                                                            | . 58 |  |  |  |

|   |      | UART_1                                             | NIRQ Can Stay Low for a Few OCP Clock Cycles After the IRQ is Serviced                                                                 |      |  |  |  |

|   |      | UART_2                                             | UART IrDA (MIR Mode) Sends an Additional Bit                                                                                           | . 58 |  |  |  |

|   |      | UART_3                                             | When in UART Sleep, Writes to the THR Wakes up the UART but No Data is Transmitted                                                     | . 59 |  |  |  |

|   |      |                                                    | - 10 TIGHOHIIGOU                                                                                                                       | . UJ |  |  |  |

|      | UART_4                      | Rx Overrun and TX_FIFO_FULL Bit Not Operational When FIFO is Disabled       | 59 |

|------|-----------------------------|-----------------------------------------------------------------------------|----|

|      | UART_5                      | Receive Overrun Not Reset on an Early Read of LSR                           | 60 |

|      | UART_6                      | Unexpected Pulse on UART.TX During Switch to SIR Mode                       | 60 |

|      | UART_7                      | UART3.TX3 Stuck in IrDA Mode                                                | 60 |

|      | UART_8                      | UART Auto Baud Status Register May Contain Invalid Speeds                   | 61 |

|      | UART_9                      | UART Fails to Transmit XON Character in Certain Conditions                  | 61 |

|      | UART_10                     | UART FIFO Pointers May be Shifted Upon FIFO Enable                          | 62 |

| 7.11 | <b>Emulation Advisories</b> | s                                                                           | 63 |

|      | EMU_1                       | Default TDO State During Reset is Unpredictable                             | 63 |

|      | EMU_2                       | Emulation Breakpoint Between Sequential 16-Bit Accesses to 32-Bit Registers | 63 |

| 7.12 | Specially Optimized         | Screen Interface (SoSSI) Advisories                                         | 64 |

|      | SOSSI_1                     | SoSSI CPriority                                                             | 64 |

| 7.13 | Oscillator Advisories       | ·<br>3                                                                      | 65 |

|      | OSC_1                       | 32-kHz Oscillator Does Not Power Down in Deep-Sleep Mode                    | 65 |

| 7.14 |                             | erface (SPI) Advisories                                                     | 66 |

|      | SPI_1                       | Emulation Reads of the SPI Peripheral are Intrusive                         |    |

|      | SPI 2                       | SPI Not Able to Receive the First Data While Waking Up From Sleep Mode      |    |

|      | SPI 3                       | SPI Peripheral Does Not Support 8-Bit Accesses                              |    |

|      | SPI_4                       | Problem With SPI Functionality After Wakeup From Deep Sleep                 |    |

|      | SPI_5                       | SPI CS Chosen Polarity Only Applies When the First SPI Transfer Begins      | 67 |

| 7.15 | Ultra Low-Power Dev         | rice (ULPD) Advisories                                                      | 68 |

|      | ULPD 1                      | Emulation Access to the ULPD IT_STATUS_REG are Instrusive                   | 68 |

|      | ULPD_2                      | ULPD Analog Cell Configuration are Reset After an MPU Peripheral Reset      |    |

|      | IULPD_3                     | DLECT1.WKUP_MODE Bit Must Be 0 for Proper Operation                         | 69 |

|      | ULPD_4                      | System May Hang if Idle/Awake Sequence Period is Too Short                  | 70 |

| 7.16 | Multichannel Serial I       | nterface (MCSI) Advisories                                                  | 71 |

|      | MCSI_1                      | MCSI2 DMA Requests are Not Mapped to the ARM                                | 71 |

|      | MCSI_2                      | Late Generation of TX DMA Request in the MCSI                               |    |

|      | MCSI_3                      | MCSI Does Not Support Multi-Master Mode                                     | 72 |

| 7.17 | Multichannel Buffere        | d Serial Port (McBSP) Advisories                                            | 73 |

|      | MCBSP_1                     | McBSP in ABIS Mode Does Not Receive Data Properly                           |    |

|      | MCBSP_2                     | Improper Behavior in McBSP ABIS Mode Transmit                               |    |

|      | MCBSP_3                     | McBSP 3-Pin Operation Versus 4-Pin Operation Configuration                  | 74 |

|     | 7.18 Dual-Mode Timers Advisories             |                      |                                                                                                            | 75 |

|-----|----------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------|----|

|     |                                              | DM_TIMER_1           | Consecutive Captures in Dual-Mode Timer                                                                    | 75 |

|     |                                              | DM_TIMER_2           | After Wakeup, the First Access to Any Dual-Mode Timer May Fail                                             | 75 |

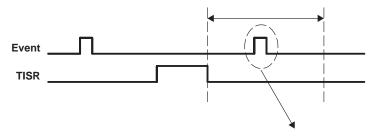

|     |                                              | DM_TIMER_3           | Dual-Mode Timer Peripheral May Not Detect Incoming Events                                                  | 76 |

|     |                                              | DM_TIMER_4           | Specific Sequence Needed to Restart the Dual-Mode Timer When One-Shot Mode is Used and Overflow Occurs     | 77 |

|     |                                              | DM_TIMER_5           | DM Timer Continuous Accesses in Non-Posted Mode Can Be Ignored                                             | 77 |

|     |                                              | DM_TIMER_6           | DM Timer Events May Get Ignored                                                                            | 78 |

|     | 7.19 Liquid Crystal Display (LCD) Advisories |                      | ay (LCD) Advisories                                                                                        | 79 |

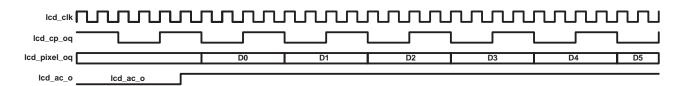

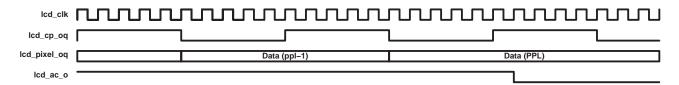

|     |                                              | LCD_1                | LCD AC Bias is not Aligned With Pixel Clock                                                                | 79 |

|     |                                              | LCD_2                | Pullups and Pulldowns Not Supported on LCD Pins P[0:15]                                                    |    |

|     |                                              | LCD_3                | The Dynamic Power-Saving Feature Changes the HSYNC and VSYNC Timings                                       | 80 |

|     | 7.20                                         | HDQ/1-Wire Advisori  | ies                                                                                                        | 81 |

|     |                                              | HDQ_1WIRE_1          | HDQ/1-Wire Peripheral Does Not Meet HDQ Standard Requirements                                              | 81 |

|     |                                              | HDQ_1WIRE_2          | HDQ/1-Wire Engine Does Not Meet 1-Wire Module Standard Requirements                                        |    |

| 8   | OMA                                          | AP5912 Device/Systen | n-Level Advisories                                                                                         | 34 |

|     | 8.1                                          | System Advisories    |                                                                                                            | 34 |

|     |                                              | SYS_1                | External Pulldown is Needed on Ball Y18 of ZZG Package                                                     | 84 |

|     |                                              | SYS_2                | UART1 and UART3 Must Be Configured to Force Idle Mode to Allow OMAP5912 to Go Into Deep Sleep              |    |

|     |                                              | SYS_3                | OMAP5912 Will Not Enter Deep Sleep Without OCPI_CK                                                         | 85 |

|     |                                              | SYS_4                | OMAP5912 Gated1/Gated2 Functionality Does Not Control I/O Direction                                        | 86 |

|     |                                              | SYS_5                | Dynamic Voltage Scaling (DVS) Implementation Requires Special Software Sequence to Properly Enter/Exit DVS | 86 |

|     |                                              | SYS_6                | Emulation is Broken When the DSP is in Isolation Mode                                                      | 87 |

|     |                                              | SYS_7                | Reset Mode Limitation                                                                                      | 87 |

|     |                                              | SYS_8                | Booting Mode Limitation                                                                                    |    |

|     |                                              | SYS_9                | High Security and Emulation Mode Limitation                                                                |    |

|     |                                              | SYS_10               | OMAP5912 USB Power Consumption                                                                             |    |

|     |                                              | SYS_11               | Peripherals That Are Not Supported on OMAP5912                                                             |    |

| 9   |                                              | • •                  |                                                                                                            |    |

| Rev | ision                                        | History              |                                                                                                            | 90 |

#### 1 Introduction

This document describes the silicon updates to the functional specifications for the OMAP5912, OMAP revision. Issues related to CPU operation are documented in the *TMS320C55x DSP CPU Programmer's Reference Supplement* (literature number SPRU652).

### 1.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all OMAP™ devices and support tools. Each OMAP™ commercial family member has one of three prefixes: X, P, or Null (e.g., XOMAP-DM270MGVL-B). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (X/TMDX) through fully qualified production devices/tools (Null/TMDS).

Device development evolutionary flow:

- X Experimental device that is not necessarily representative of the final device's electrical specifications

- P Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- Null Fully-qualified production device

Support tool development evolutionary flow:

**TMDX** Development support product that has not yet completed Texas Instruments internal qualification testing.

TMDS Fully qualified development support product

X and P devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Null devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. Tl's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

All trademarks are the property of their respective owners.

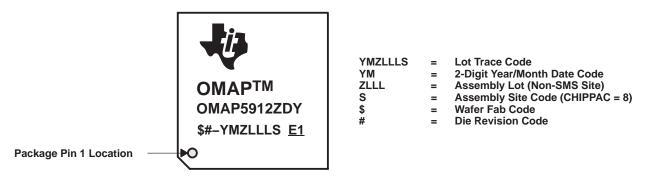

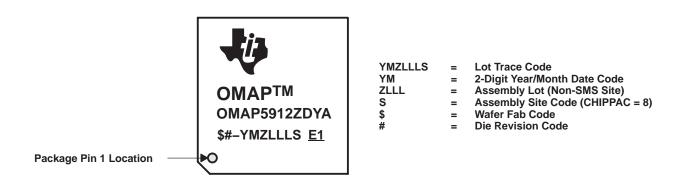

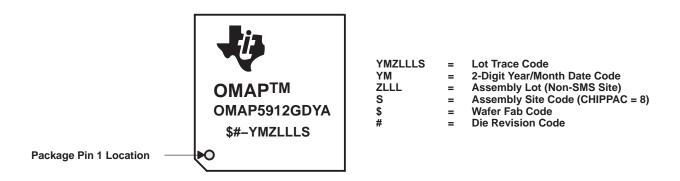

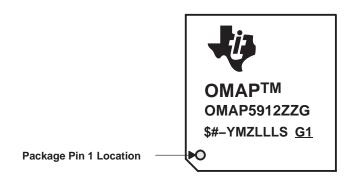

The device revision can be determined by the symbols marked on the top of each package. Example markings of the ZDY, GDY, and ZZG packages are shown in Figure 1 through Figure 4.

Figure 1. Example Markings for Catalog OMAP5912 ZDY Package

Figure 2. Example Markings for Extended Temperature OMAP5912 ZDY Package

Figure 3. Example Markings for Extended Temperature OMAP5912 GDY Package

YMZLLLS = Lot Trace Code

YM = 2-Digit Year/Month Date Code

ZLLL = Assembly Lot (Non-SMS Site)

S = Assembly Site Code (CHIPPAC = 8)

\$ = Wafer Fab Code # = Die Revision Code

Figure 4. Example Markings for OMAP5912 ZZG Package

### 2 Important Notices and Information About OMAP5912

#### 2.1 Useful Information Regarding TMS320C55x™ Assembler Diagnostic Messages

The TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP assembler generates three types of diagnostic messages when it detects a potential or probable Silicon Exception.

### 2.1.1 ERROR Diagnostics

The assembler generates ERROR diagnostics in cases where it can fully determine that the code will cause a silicon exception to occur on hardware.

### 2.1.2 WARNING Diagnostics

The assembler generates WARNING diagnostics in cases where it can fully determine that the code will cause a silicon exception to occur on hardware, but which, under certain circumstances, may not be an issue for the user.

### 2.1.3 REMARK Diagnostics

The assembler generates REMARK diagnostics in conditions where it can fully determine that the code may cause a silicon exception to occur on hardware, but the exception itself also depends on non-visible trigger conditions that the assembler has no knowledge of, such as whether interrupts are enabled.

Since the assembler cannot determine the state of these trigger conditions, it cannot know that the exception will affect this code. Therefore, it generates a REMARK to instruct the user to examine the code and evaluate whether this is a potential silicon exception situation. (Please see the following sections for how to suppress remarks in situations where you have determined that the other trigger conditions do not exist.)

#### **Intended Treatment of REMARK Diagnostics**

The intent of generating REMARK diagnostics is to inform the user that the code could potentially cause a silicon exception and that it should be reviewed by the user side by side with the trigger conditions and a determination be made whether the code is a potential silicon exception situation.

If the code is determined to be a potential silicon exception situation, users should modify their code to prevent that exception from occurring.

If users determine that their code will not cause a silicon exception based on the trigger conditions, then the REMARK that the assembler generates can be suppressed. There are two methods of doing so; please see the "Suppressing REMARK Diagnostics" section.

### **Suppressing REMARK Diagnostics**

Once the user determines that a silicon exception REMARK diagnostic is not appropriate for the code as written, the REMARK diagnostic can be suppressed in one of the following ways.

- REMARK directives

- REMARK command-line options

TMS320C55x and C55x are trademarks of Texas Instruments.

#### **REMARK Directives:**

The .noremark.remark directives can be used to suppress the generation of a REMARK diagnostic for particular regions of code. The .noremark directive turns off the generation of a particular REMARK diagnostic. The .remark directive re-enables the generation of a particular REMARK diagnostic.

A '.noremark ##' (where ## is the remark id) directive is placed at the beginning of the region, and a '.remark ##' directive is placed at the end of the region.

**NOTE:** The .noremark.remark directive combination should always be placed around the entire region of code that participates in the potential silicon exception. Otherwise, spurious diagnostics may still be generated.

Additionally, the user has the option of disabling a silicon exception diagnostic for the entire file by placing just the .noremark directive at the top of the assembly file. However, this may be dangerous if, during inevitable code maintenance, the code is modified by someone not familiar with all the exception conditions. Please take great care when using the directives in this manner.

### **REMARK Command-Line Options:**

The compiler shell (cl55) supports a command line option to suppress a particular REMARK diagnostic. The shell option –ar# (where # is the assembler's silicon exception id as described above) suppresses the named REMARK for the entire scope of all assembly files compiled with that command. Using the option –ar without a number suppresses all REMARK diagnostics.

Again, this may be dangerous if, during inevitable code maintenance, the code is modified by someone not familiar with all the silicon exception conditions. Please take great care when using the command-line REMARK options. Using the .noremark/.remark directives covering the shortest possible range of source lines is much safer.

### 3 Usage Notes

Usage Notes highlight and describe particular situations where the device's behavior may not match the presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### DMA xxxx IT COND Bits Clear Procedure is not Correctly Documented in OMAP Reference Guide

The OMAP5912 Multimedia Processor Direct Memory Access (DMA) Support Reference Guide (literature number SPRU755) states that user must write to the DMA\_LCD\_CTRL register to clear the interrupt status bits. This is not true. When receiving an interrupt, software must read the DMA\_LCD\_CTRL and then any write on the MPU Private TIPB will clear the register.

The recommended procedure to clear the DMA xxxx\_IT\_COND bits in DMA\_LCD\_CTRL register is to:

- Read DMA\_LCD\_CTRL\_REGISTER

- Write back to it as quickly as possible, clearing the required bits. The bits will only be cleared if a read to

this register occurred previously; this decreases the interrupt loss risk.

#### **DSP MMU Maximum Speed on OMAP3.2**

The DSP MMU clock must have the same maximum speed as the Traffic Controller clock. When using synchronous scalable mode, software must program the ARM\_CKCTL .DSPMMUDIV field accordingly.

#### UART IrDA Recommendation for Clock Gating clk16x

In the UART IrDA, clk16x is operational before the autobaud has acquired any lock status. This is power-inefficient; especially if a lock is not achieved quickly. It is recommended that the UART IrDA clk16x output be gated off until the autobaud functionality has accurately characterized the data settings, hence improving the power consumption of the peripheral.

#### Activating DSP Isolation Will Increase Power Consumption on CV<sub>DD</sub> Power

As soon as DSP isolation is activated, INITZ of the internal memory in OMAP MPU power domain will toggle low. This will cause additional power consumption. To save power, It is recommended that the user shut down  ${\rm CV_{DD3}}$  power as soon as possible after activating DSP isolation. Isolation is controlled by ULPD POWER\_CTRL\_REG.ISOLATION\_CONTROL bit.

### **ETM FIFO Overflow**

Frequent ETM FIFO overflows may prevent efficient tracing. For example, when running 32-bit code which contains lots of LDM/STM commands, overflows occur.

### MICROWIRE® Auto-Transmit Mode Definition

In autotransmit mode, the CS\_CMD and START bits of the control and status register (CSR) are not used. An internal hardware state machine detects a TXD write and automatically sets the programmed CS to its active value, and then starts the transmission. This behavior is only valid when both AUTO\_TX\_EN and CS\_TOGGLE\_TX\_EN bits are 1. If AUTO\_TX\_EN is 1 and CS\_TOGGLE\_TX\_EN is 0, then, the CS will not toggle automatically upon a TXD write. In this mode, CS\_CMD must be set for transmission to begin when writing a TXD.

MICROWIRE is a registered trademark of National Semiconductor Corporation.

### Set Address Request: Minor Violation of USB 2.0 Specification

If the host does not send an ACK in response to the device's empty DATA packet, the device will observe the proper 18-bit timeout. However, the device will be addressed at this point, and not respond to the host's retry SETUP token (using the old address).

This behavior occurs during FS20 testing and is isolated to the Status stage of a SetAddress request and will not be detected during compliance testing. Affects USB client (USB\_W2FC).

In general, most OS's will retry enumeration, but they are not required to do so by specification. As a result, the host will have to reset the device.

#### **OMAP5912 Global Clock Rules**

The following table lists the maximum allowable clock speeds for the various OMAP5912 clocks.

| MPU max clock                                      | 192 MHz |

|----------------------------------------------------|---------|

| DSP max clock                                      | 192 MHz |

| TC max clock                                       | 96 MHz  |

| DPLL1 max clock                                    | 192 MHz |

| Flash max clock                                    | 48 MHz  |

| DSP MMU max clock                                  | 96 MHz  |

| MPUPER max clock                                   | 96 MHz  |

| DSPPER max clock                                   | 96 MHz  |

| MPU TIPB (Public and Private) max strobe frequency | 48 MHz  |

| DSP TIPB (Public and Private) max strobe frequency | 32 MHz  |

| MPU interface max strobe frequency                 | 32 MHz  |

| LCD controller max clock                           | 48 MHz  |

#### Dynamic Switch Locked if DSP Reset Occurs During a DSP Access

In OMAP5912, four GPIO modules and the 32K synchronous counter are shared between DSP and ARM. If a DSP reset occurs while the DSP is performing an access to a dynamically shared peripheral, the dynamic switch will stay in a locked state and no access to the peripheral is possible anymore. The only way to recover from this locked state is to perform an ARM peripheral reset (set ARM\_RSTCT2.PER\_EN bit to 0).

#### Camera Interface Moved Between Production and Engineering OMAP5912

On OMAP5912, the camera interface is connected to the OCP – T1/T2 bus.

On XOMAP5912 or POMAP5912, the camera interface is connected to the TIPB bus.

### 4 DSP Subsystem Advisories

#### 4.1 DSP ICACHE Advisories

### Advisory DSP ICACHE 1

DSP ICACHE is Servicing a Missed Program Bus Request During a RAMSET Preload

Revision(s) Affected:

All revisions

Details:

The two ramset banks inside the DSP ICACHE are preloaded when the corresponding ramset tag registers' content are updated through I/O access. The ramset preload uses the same line-fill mechanism as the cache miss line-fill; therefore, there is a conflict of resource when the ramset refill happens while the I-cache miss line-fill is on-going. Although there is logic to arbitrate this conflict, a functional bug can corrupt the content of Tag ram under the following corner condition:

- I-cache is turned on with ramset(s) enabled.

- The instruction(s) for updating the ramset tag register(s) are embedded with other program code in external memory.

- The external memory space where the instruction(s) for updating the ramset tag(s) are not present in the ICACHE, e.g., will generate a cache miss.

### **Example:**

The following example shows assembly code that is likely to encounter this corner case:

```

Address

Instruction

Ext Mem

DSP code

DSP code

Ext Mem

. . . . . .

DSP code

Ext Mem

Ext Mem

DSP code

*port(#0x1400) = #0xc 2f ; Configure icache

Ext Mem

bit(ST3, #14) = #1

Ext Mem

; Turn on icache

*port(\#0x1406) = \#0x0800

Ext Mem

; Update ramset tag for bank1

*port(#0x1408) = #0x0801 ; Update ramset tag for bank2

Ext Mem

DSP code

Ext Mem

DSP coI.....

Ext Mem

. . . . . .

DSP code

Ext Mem

Ext Mem

DSP code

```

While the ramset tag is being updated by the I/O bus, the CPU IBQ is prefetching instructions not present in ICACHE. There are some latencies in completing I/O access to ramset tag registers, the exact time of when ramset update happens is not controllable.

DSP ICACHE is Servicing a Missed Program Bus Request During a RAMSET Preload (Continued)

#### Workaround:

- 1. I-cache must be turned on with ramset(s) enabled.

- 2. Branch from external memory program code to the ramset tag update code.

- 3. Continue polling the ramset tag valid bit to make sure the ramset preload has finished.

- Branch back to external memory for normal program execution after the preload has finished.

### **Example:**

```

Address

Instruction

Ext Mem

DSP code

Ext Mem

DSP code

DSP code

Ext Mem

Ext Mem

DSP code

*port(#0x1400) #0xce2f

; Configure icache

Ext Mem

Ext Mem

bit(ST3, #14) = #1

; Turn on icache

Ext Mem

goto Preload_ramsets

Preload_ramsets:

Int Mem

*port(\#0x1406) = \#0x0800

; Update ramset tag for bank1

Scan0:

Int Mem

TC1 = bit(*port(0x1405), #15)

; Read the Tag Valid

; bit of ramset bank 0

nop 16

Int Mem

Int Mem

if (!TC1) goto Scan0

; Continue polling if the

; Tag Valid bit is not 1.

Int Mem

*port(\#0x1408) = \#0x0801

; Update ramset tag for bank1

Scan1:

Int Mem

TC1 = bit(*port(0x1407), #15)

; Read the Tag Valid

; bit of ramset bank 1

Int Mem

nop 16

Int Mem

if (!TC1) goto Scan1

; Continue polling if the

; Tag Valid bit is not 1.

Int Mem

goto Back_from_ramset_preload

Back_from_ramset_preload:

DSP code

Ext Mem

I Ie

Ext Mem

. . . . . .

DSP code

Ext Mem

DSP code

Ext Mem

```

#### 4.2 DSP Emulation Advisories

# Advisory DSP EMU 1

DSP IDLE Interrupt Not Serviced When Emulator is Connected

Revision(s) Affected:

All revisions

Details:

At the JTAG interface level, an emulator device generates the TCK signal, which can be an adaptive or fixed clock signal. Inside the OMAP16xx devices, this TCK is re–synchronized by the ARM926 in order to create the RTCK signal provided to the emulator. This RTCK signal is so used by the emulator to send and receive data to OMAP synchronously with the OMAP internal clock.

This mechanism creates some limitations for the used TCK frequency, when the ARM/MPU clock runs at low frequency (which is the case when the DPLL is not running). Indeed, if we have fast TCK (5 🗵 12 MHz) and low MPU clock, the 2 clock frequencies are too near. So the re–synchronization machine will provide a very bad and polluted RTCK at a frequency around 1 or 2 MHz.

With such an RTCK clock, the communication between OMAP and the emulator will fail most of the time.

Workaround:

Slow down the TCK at 2 MHz: it will always works, regardless the state of the DPLL (anyway, when the DPLL is not enabled, the badly generated RTCK is never higher than 3 MHz). Yet, if you want use the fast TCK capability, we recommend using the following high–level sequence:

- 1. Use first slow TCK (<2 MHz) to debog boot process.

- (Once the boot process is debugged, have boot code in non-volatile memory that programs DPLL for ARM clock >>12 MHz (noting that this clock can raise up to 192 MHz).

- 3. Use faster TCK (5-12 MHz).

# Advisory DSP\_EMU\_2

Bad RTCK Clock Signal May Cause JTAG Communication Failure between the OMAP and an Emulator

Revision(s) Affected:

All revisions

Details:

A DSP IDLE interrupt is not serviced when an emulator is connected as shown in the following sequence:

- 1. Emulator is connected

- 2. RT mode is set

- 3. Test code is run

- ASM code sets INTM

- ASM code clears all pending interrupts in IFR

- ASM code configures timers, but does not enable

- ASM code sets ICR to 0x3F

- 4. Emulator halts CPU

- PC indicates halted at IDLE instruction

- DBGSTAT = 0x805F (IDLE, DSUSP, and FXWOK)

- ISR = 0x3F

- No interrupts pending in IFR

- 5. Single interrupt is provided

- 6. RT int by emulation write to DBIER0 is enabled

- Halted background code immediately comes out of idle

- ISR = 0x3F (interrupt not taken)

Workaround:

There is no workaround.

The emulator result is different from the functional mode (which will service the ISR). This only affects the debugger mode. Therefore, do not use IDLE when the emulator is connected.

### 4.3 DSP System Advisories

# Advisory DSP SYS 1

Use Caution When Reading Following a Configuration Change on the DSP

Revision(s) Affected: All revisions

**Details**: Within the C55x CPU, writes occur later in the pipeline than reads do. This allows reads from a

later instruction to sometimes occur prior to the write of an earlier instruction. This can be a problem when the write is to a configuration register in a peripheral that affects the read. If the user intends to read memory that can be affected by the new configuration, it is recommended that the user read from the configuration register being programmed prior to memory reads.

Reads from the TIPB interface are pipeline-protected, so writes and reads of peripheral

registers are not affected. Also, sequential writes to peripherals work correctly.

Workaround: After configuring a peripheral, the software should ensure that the writes have completed prior

to using that configuration. This can be done with a read from the last register written or waiting 3 cycles. This configuration constraint is common to pipeline architectures.

This exception will not be fixed in future silicon revisions.

Advisory

DSP SYS 2

Users of (JTAG) RTDX are Advised Not to Put the DSP Domain Into Idle

Revision(s) Affected: All revisions

**Details**: When the DSP is idled, ALL interrupts generated external to the DSP core are latched into a

register within the OMAP subsystem. In this subsystem, the logic tied to the CLEAR input signal for the latch will erroneously cause the latch to be cleared upon emulation accesses,

including CMSG/DMSG/DT-DMA.

This interrupt will cause the DSP to be awakened from Idle, but once it is awakened it will not find any interrupts flagged in IFR which require servicing. Thus, the interrupt will appear to have been lost. This latch is only used when the DSP domain is in idle. Thus, this issue may

be avoided if the DSP domain is never idled.

**Workaround**: There is no workaround.

# Advisory DSP SYS 3

DSP IDLE Wakeup With Program Code in External Memory and EMIF Domain in IDLE Hangs

Revision(s) Affected: All revisions

**Details**: If the EMIF domain and DSP domain are set to IDLE, and the IDLE instruction is executed, it

is not possible for the wakeup ISR to be located in EMIF. The program counter will hang since

the EMIF domain will not come out of IDLE.

**Workaround**: Ensure that wakeup ISR is executing from internal memory.

This exception will not be fixed in future silicon revisions.

Advisory DSP\_SYS\_4

DM Timer Incorrect Value Read During DSP Access and Value Change

Revision(s) Affected: All revisions

**Details**: The DM timer supports OCP accesses from both the ARM<sup>®</sup> and DSP. The timer registers are

32 bits wide, so two 16-bit accesses must be performed from the DSP side in order to read/write the full data. The correct procedure is to read the 16 LSBs first, then the 16 MSBs. However, when accessing TCRR or TCAR registers, there is no hardware mechanism to ensure that the 16 MSBs of the register will not change between the LSB reading and MSB

reading.

**Example:** DSP reads TCRR as its value is 0x0001FFFF. LSB read returns 0xFFFF. TCRR value changes before MSB read (TCRR is now 0x0002 0000). MSB read will return 0x0002

instead of 0x0001.

Workaround: A read LSB-MSB while loop can be implemented in the DSP software in order to ensure

correct data is provided by reading two consecutive identical MSB values.

# Advisory DSP\_SYS\_5

DSP STIO Interrupt Generation is Not Possible

Revision(s) Affected:

All revisions

Details:

The DSP EMIF is a DSP subsystem module that gives the DSP access to the shared system memory managed by the traffic controller (bus wide is 32 bits). It supports interface to a variety of external devices, including:

- Asynchronous devices (asynchronous SRAM, ROM and Flash). The external memory interface provides highly programmable timing to these interfaces.

- Synchronous burst SRAM (SBSRAM) running at either 1x or 1/2x the CPU clock rate.

- Synchronous DRAM (SDRAM) running at either 1x or 1/2x the CPU clock rate.

- Synchronous STIO interface for OMAP applications.

The interrupt for the STIO interface is linked to the DSP Level 1 interrupt handler (SINT16/INT16: peripheral interrupt #14). The problem is that at OMAP level, this STIO interrupt input is connected by hardware to an inactive state instead coming from the EMIF module; thus it is impossible to generate a STIO interrupt.

Workaround:

No existing workaround.

### 4.4 DSP Direct Memory Access (DMA) Advisories

# Advisory DSP DMA 1

DSP DMA IDLE Prevents Transfer Completion

Revision(s) Affected: All revisions

**Details**: When DSP peripherals are placed in IDLE, there is an internal hardware handshaking

mechanism between the DSP and its peripherals that ensures the IDLE can occur. If a DMA transfer is occurring, this handshaking is supposed to prevent IDLEing until after the transfer is complete. The DSP DMA, however, can go into IDLE during the middle of a transfer, resulting

in the transfer not completing.

Workaround: In order to enforce that all DMA transfers be complete before attempting to IDLE the DMA, the

DMA status first needs to be checked. Afterwards, the DMA channels need to be disabled

from which the IDLE instruction can then be safely executed.

This exception will not be fixed in future silicon revisions.

Advisory DSP\_DMA\_2

DSP EMIF/DMA Port Hangs During EMIF Bus Error

Revision(s) Affected: All revisions

**Details**: If the EMIF times out on an access, the DSP will get a time-out bus-error interrupt. The

time-out condition may also cause a DMA interrupt. During this DMA interrupt, the DMA will

not time out and go into an unknown state.

Workaround: Whenever an EMIF bus error interrupt occurs, the software needs to RESET the DMA and

reschedule the transfer

### 5 MPU Subsystem Advisories

### 5.1 System Direct Memory Access (DMA) Advisories

| Advis | sory |   |

|-------|------|---|

| SYS   | DMA  | • |

System DMA CSAC and CDAC Not Showing Correct Value Consistently

Revision(s) Affected: All revisions

**Details**: Due to a malfunction of the CDAC/CSAC registers, software may read 0000 or incorrect data

during large transfers and may not be able to judge the progress of transfers correctly.

These registers show incorrect values of address, for interleaving enabled, synchronized transfers, when read 7 cycles after the generation of a hardware request. At that time, the registers will be read as 0000. Similarly, incorrect data is read 8 cycles after the generation of

the first hardware request.

Workaround: The workaround is to synchronize hardware requests and counter reads. After giving a

hardware request, read the value after 8 clock cycles.

Normally the CSAC/CDAC registers will not give a value of zero (except when the starting address is 0000 and in constant address mode). Software should read the register(s) until the

0000 disappears.

This exception will not be fixed in future silicon revisions.

### Advisory SYS DMA 2

Cannot Get SysDMA to Complete Data Transfer Out of UART

Revision(s) Affected: All revisions

**Details**: The UART FIFO can interrupt the DMA channel upon setting register bits [2:0] in the

supplementary control register (SCR), even if the UART is disabled (MDR1 = 0x7). This can

cause problems if the SCR[2:0] bits are set prior to setting the trigger thresholds.

Workaround: Set the DMA just before setting the mode select in the MDR1 register to avoid filling the FIFO

in disable mode.

### Advisory SYS DMA 3

DMA Synchronized Transfers Can Be Stalled

Revision(s) Affected:

All revisions

Details:

When request pipelining is enabled, synchronized DMA transfers can get stalled. (In order to allow a faster response of the DMA, a new request can start while a previous one is stil under processing.) The request pipelining is a DMA feature, automatically chosen when interleaving mode is disabled (DMA\_LCH\_CTRL[LID]=1).

The affected transfers are:

- Synchronized element transfers

- Synchronized frame transfers

- Synchronized block transfers

This problem is independent of:

- Transfer size

- Channel priority

- Used physical channel

The consequences/symptoms of this issue depend on the DMA request initiator and on the type of synchronized transfer (element/frame/block). For example:

- Event missed in element synchronized:

If the exception occurs during a frame of N single elements, by a chain effect, halt will be moved on the last request. Thus, the last element of the frame will not be returned to the destination and a frame interrupt will not be generated.

- Transfer stalled in Frame synchronized:

Some peripherals generate a new request only when a full frame has been read.

Consequently, if this exception occurs, transfers will be stalled, as no more requests will be issued from the peripheral.

Workaround:

This hardware issue is a corner case of the request pipelining mode and never occurs in interleaving mode. So, software must enable the interleaving mode:

DMA LCH CTRL[LID] = 0.

### 5.2 MPU Emulation Advisories

| Advisory  | Emulation is Intrusive to ARM Idle Mode:                      |

|-----------|---------------------------------------------------------------|

| MPU_EMU_1 | Cannot Stop the CPU Clock With Code Composer Studio Connected |

Revision(s) Affected: All revisions

**Details**: JTAG on the ARM926EJ-S™ does not work if the functional clock is halted. However, the

processor can still enter the IDLE state when an emulator is attached.

Emulation is detected based on TCK activity. When emulation is disconnected, a power up is required to switch back to the no emulation attached default state. If the emulation is connected during a power-down state, then TCK detection will trigger a wakeup without

interrupt generation.

**Workaround**: There is no workaround.

### 5.3 MPU System Advisories

# Advisory MPU SYS 1

STANDBY Mode Not Entered After Execution of WFI Instruction

Revision(s) Affected: All revisions

**Details**: STANDBY mode is not entered after execution of WFI instruction.

**Workaround**: There is no workaround.

This exception will not be fixed in future silicon revisions.

Advisory MPU\_SYS\_2

Inefficient Fill of Instruction Prefetch Buffer

Revision(s) Affected: All revisions

**Details**: Inefficient fill of instruction prefetch buffer.

**Workaround**: There is no workaround.

This exception will not be fixed in future silicon revisions.

Advisory MPU\_SYS\_3

External Device Power Control is Broken

Revision(s) Affected: All revisions

**Details**: If an external device power control is enabled (by setting EWUPCT.REPWR EN bit to 0), the

OMAP3.2 clock and reset manager might in some conditions shut down the ARM clock even

when the ARM is not in standby mode.

The following sequence will cause this exception. Note that this is only a high-level sequence

given for illustration purposes: there is no way to ensure proper operation of the system if the

EWUPCT.REPWR\_EN bit is set to 0.

External Device Power Control is Broken (Continued)

- 1. WFI instruction is executed. ARM goes into idle.

- 2. Clock and reset manager shuts down ARM clock and begins the OMAP3.2 idle entry procedure. This implies making sure that the Traffic Controller is idle.

- Before the clock and reset manager asserts the idle request to the traffic controller, a wake-up event occurs and wakes up the system. Clock and reset manager activates ARM and TC clock. ARM begins fetching code.

- 4. Since the REPWR\_EN is set, the clock and reset manager shuts down the ARM clock while TC clock stays active, and begins counting up until EWUPCT.EXTPWR cycles have elapsed. Then, the ARM clock is restored. This has two effects:

- a) Shutting down ARM clock while it is active and fetching code.

- b) Asserting FLASH.RP signal while the ARM is fetching code.

Workaround:

Set REPWR\_EN bit inside EWUPCT register (0xFFFE CE0C) to 1. This disables the external device power control feature, and prevents the exception from occurring.

This exception will not be fixed in future silicon revisions.

# Advisory MPU SYS 4

Emulation Causes OMAP Not to Enter Deep Sleep

Revision(s) Affected:

All revisions

Details:

Rising edge on TCK causes OMAP not to enter Deep Sleep.

Workaround:

Make sure that daisy-chaining other devices onto the OMAP5912 JTAG will not prevent OMAP from entering deep sleep by ensuring other JTAG device do not glitch TCK or provide a rising edge on TCK upon power up.

If a glitch propagates, either apply a power-up reset or a JTAG reset.

### Advisory MPU SYS 5

Write Followed by Immediate Read not Supported on the Rhea Switch Peripheral

Revision(s) Affected:

All revisions

Details:

A write followed by an immediate read does not work on the ARM address space defined below. If a read occurs immediately after the write to the same address, then the read will not be the data that was written. The affected address spaces are:

Rhea Switch module: Address FFFB:C800 to End Address FFFB:CFFF

Workaround:

When an immediate read is required after a write to any register in the above address space, make two consecutive writes to the same address prior to the read. Using this procedure ensures that the first write completes and the read data will be correct.

This exception will not be fixed in future silicon revisions.

Advisory MPU SYS 6 When Absent, the OMAP Peripheral Clock Prevents Deep Sleep Entry

Revision(s) Affected:

All revisions

Details:

If the peripheral clock is disabled, OMAP5912 cannot go into deep sleep when executing the ARM Idle instruction. If the peripheral clock is enabled prior to the execution of the ARM Idle instruction, the chip goes into deep sleep properly.

Workaround:

If the ARMPER peripheral clock is enabled (via EN PERCK of ARM IDLECT2) prior to the execution of the ARM Idle instruction, the chip goes in deep sleep correctly.

If the ARMPER peripheral clock is disabled, make sure that the TC1 clock is disabled as well.

### Advisory MPU SYS 7

MPU IRQ122-127 Can Cause Spurious Interrupts

Revision(s) Affected: All revisions

**Details**: On the MPU, IRQ122 through IRQ127 are tied low and therefore, capable of interrupting the

system if their corresponding ILR registers (from address 0xFFFE:0384 for IRQ122 to

0xFFFE:0398 for IRQ127) are programmed such as a level interrupt.

A level interrupt is configured if the SENS\_EDGE bit is set to 1 (bit 1 of the ILR register).

Workaround: Make sure SENS\_EDGE is cleared to 0 for IRQ122–IRQ127's IRL registers (from address

0xFFFE:0384 for IRQ122 to 0xFFFE:0398 for IRQ127).

This exception will not be fixed in future silicon revisions.

Advisory MPU SYS 8

If BVLZ is Not Configured, the Corresponding Interrupt Must be Masked

Revision(s) Affected: All revisions

**Details**: On OMAP5912, the UART3.CTS, UART1.DSR, and the MMC/SDIO2's MMC.DATDIR1

signals have been multiplexed with BVLZ (battery low-level external interrupt).

If BVLZ is not used, make sure that the corresponding interrupt mask is set (MPU Level 1 Interrupt Mapping, IRQ\_3) and masked or controlled accordingly the RST\_HOST\_OUT

(modem shutdown output) on ball W13 (ZZG package).

Workaround: Case 1:

Use W19 (ZZG package) as EXT FIQ (battery fail), use W13 as modem shutdown.

Case 2:

Use W19 as anything, provided the corresponding interrupt is masked. Use W13 as something that is not modem shutdown.

Case 3:

Use W19 as something different from EXT\_FIQ, provided that the corresponding interrupt is masked. Use W13 as modem shutdown.

In Case 3, the workaround is to pull W13 high externally and configure it by software to be in mode 7 (GPIO55). This will prevent activity on W19 from propagating to W13.

Then, when software wants to assert W13, set the ULPD POWER\_CTRL\_REG[3] bit to 0, and reconfigure pin muxing for W13 to be modem shutdown. When software wants to

deassert W13, reconfigure pin muxing to have W19 be GPIO55. Pullup should revert the line to high (inactive) state.

If using a pullup on Ball W13 is impossible, then configure the GPIO55 as an output driving 1.

# Advisory MPU SYS 9

Access to the OMAP3.2 ARM\_CLKM Registers

Revision(s) Affected:

All revisions

Details:

The ARM\_CLKM has 32-bit width registers. Make sure that the ARM\_CLKM registers are accessed with 32-bit access widths. If the ARM CLKM registers are accessed in 16 bits, the access will be correctly performed, but a TIPB abort will be generated.

Workaround:

Do not access the ARM CLK registers with 16 bit access width (or mask TIPB aborts).

This exception will not be fixed in future silicon revisions.

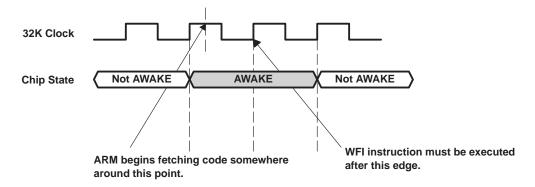

### Advisory MPU\_SYS\_10

WFI Instruction Loses 2-4 Instruction Fetches

Revision(s) Affected:

All revisions

Details:

When the ARM tries to wake up immediately after execution of the WFI instruction or a few cycles later, it may miss some instruction fetches. The number of instructions missed depends on the time of the wake-up interrupt. This problem does not depend on the EMIFS configuration and can occur with any configuration of the EMIFS.

The problem occurs as follows:

- ARM goes to idle after execution WFI instruction.

- 2. OMAP clock and Reset module cuts clock to the ARM.

- 3. At the same time, Clock and Reset module asserts TCIDLE Reg to the Traffic controller.

- 4. TC acknowledges the idle request from clock and reset module.

- 5. Meanwhile, a wake-up interrupt comes to OMAP.

- 6. After a few synchronization cycles, the ARM clock cycles wake up.

- 7. In parallel, the clock and reset module synchronizes the TC idle acknowledge and cuts the clock to the TC.

- 8. Because the ARM clock is active and IRQ/FIQ is present, the ARM tries to fetch instructions from the EMIFS (TC).

- 9. This results in the following two cases:

- a) Request comes before the Clock and Reset module cutting the clock to the TC. . . . . . Because the Idle acknowledge is present, the Clock and Reset module will cut the . . . . . . clock to TC. [If the clock cut in the middle of request, ARM has the possibility of . . . . . . . missing some instructions (9a).]

- b) TC clock already cut and request from ARM waits until TC clock is active. . . . . . . . . . . (No problem to any instruction fetch.)

WFI Instruction Loses 2–4 Instruction Fetches (Continued)

#### Workaround:

The software workaround is to make sure the that ARM will only execute NOPs when it wakes up, inserting NOPs after the WFI instruction, and making sure interrupts are disabled for ARM when the WFI instruction is executed. See below:

- 1. Disable interrupts, by setting I and F bits in ARM CPSR register. This ensures that the ARM will not jump to interrupt routine when it wakes up.

- 2. WFI instruction

- 3. NOP instructions

- 4. Enable interrupts by resetting I and F bits in the ARM CPSR. The number of NOPs to insert after the WFI instruction is given by the following formula:

$$X = 2 + (4*DPLL MULT)/DPLL DIV/ARMDIV$$

### 5.4 MPU/Watchdog Timer Advisories

# Advisory MPU WATCHDOG 1

MPU Watchdog Does Not Reset DPLL

Revision(s) Affected:

All revisions

Details:

If the MPU watchdog timer expires, a reset is provided to the ARMCK\_CTL registers (resetting the clock divisors) but not to the DPLL.

This means that when OMAP5912 is operating at 192 MHz with SDRAM at 96 MHz (/2) and a WD timer reset occurs, the ARM will begin executing code at the reset vector with the DPLL remaining at 192 MHz and all clock divisors set at /1. See below:

- Before reset:

- DPLL register (0xFFFE CF00) = 0x2813 (DPLL Lock mode, 16 x multiplier)

- ARM\_SYSST register (0xFFFE CE18) = 0x1000 (Synchronous scalable mode)

- ARM\_CKCTL register (0xFFFE CE00) = 0x5101 (ARMINTH, TC. PER clocks div/2; clkref = CLKGen1)

- After reset:

- DPLL register (0xFFFE CF00) = 0x2813 No change

- ARM\_SYSST register (0xFFFE CE18) = 0x000C (Full synchronous mode, WD + MPU reset)

- ARM\_CKCTL register (0xFFFE CE00) = 0x3000 (No div; clkref = CLKGen1)

Workaround:

Use the 32k watchdog timer. It properly resets the DPLL when it expires; however, the 32k WD Timer has less precision on the timer value (it counts 30.5  $\mu$ s ticks instead of ~0.1  $\mu$ s ticks) and cannot cause a WD reset to occur in less than 30.5  $\mu$ s.

# Advisory MPU\_WATCHDOG\_2

The Secure Watchdog Register Reads Can Return Wrong Value Under Some Clock Configurations

Revision(s) Affected: All revisions

**Details**: All the OMAP16xx Watchdog timers (32 KHz watchdog and secure watchdog) support only

POSTED internal synchronization mode. There is no capability to change the internal

synchronization scheme to NON-POSTED by software; therefore, their OCP clock must be at least 4 times faster than their functional clock (system clock or 32K clock).

In OMAP16xx clock configurations where this condition is not met (interface clock is

ARMPER\_CK i.e. CK\_GEN1 divided by 1, 2, 4 or 8 as per ARM\_CKCTL.PERDIV[1:0] setting), met stability can occur and cause erroneous value to be read from WCLR, WCRR, WLDR, WTGR and WSPR registers. This can cause problems with the secure WD, since its functional clock frequency is 12MHz/13MHz or 19.2MHz (ARMXOR\_CK). The 32 KHz watchdog is not impacted, as its functional clock is 32 KHz. Interface clock frequency is always greater than 4

times the functional clock.

Workaround: Software must perform several read accesses in order to detect and discard possible

erroneous values.

### 6 Traffic Controller Subsystem Advisories

### 6.1 EMIF Slow (EMIFS) Advisories

| Adv | /iso | ry |

|-----|------|----|

| EMI | FS   | 1  |

Unexpected FCLK on EMIFS When Dynamic Wait State is Selected

Revision(s) Affected:

All revisions

Details:

When the EMIFS\_DWS register is configured to select dynamic wait states, an unexpected FCLK is generated after an access to the CS which is configured to dynamic wait state mode.

Workaround:

Avoid dynamic wait ready mode. If the dynamic wait ready mode has to be used, insert a

dummy write/read cycle.

This exception will not be fixed in future silicon revisions.

# Advisory EMIFS 2

Program Fetch From External Memory at Address 0x3C18 Results in Processor Reset

Revision(s) Affected:

All revisions

Details:

If the EMIFS\_CONFIG.BM bit is set to 1, software must make sure no code is ever executed in the address range centered on  $0x0000~3C18\pm10~32$ -bit words. When the EMIFS\_CONFIG.BM bit is set, this address range is located in external memory (EMIFS) connected to FLASH.CS3. Depending on the device type, executing code in the forbidden area will have different consequences:

- On emulation devices, the processor will hang up

- On production devices (general-purpose), the processor will reset (warm reset generated).

This behavior will only affect devices where the BM bit is set. Emulation devices booting externally and GP devices using Fast Boot mode have this bit set by default.

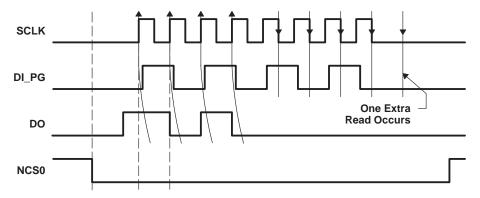

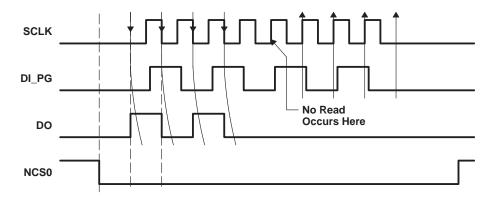

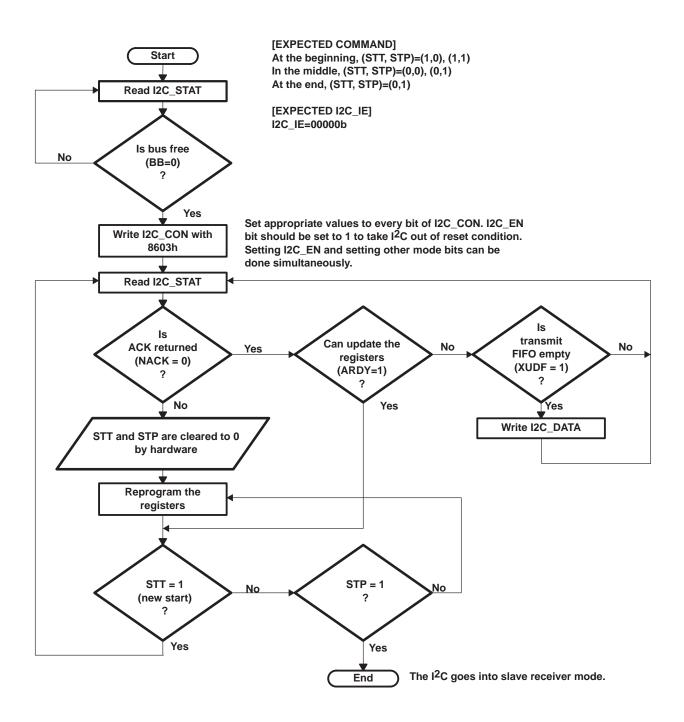

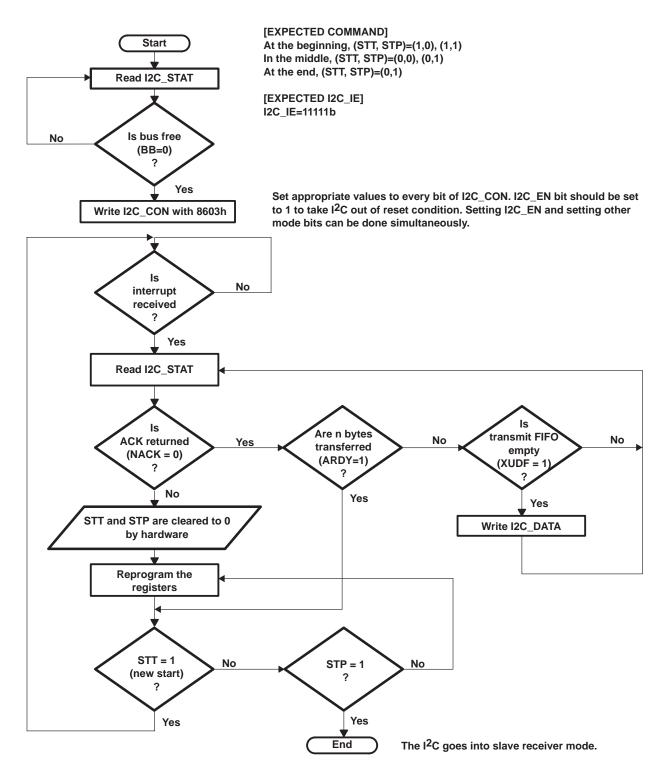

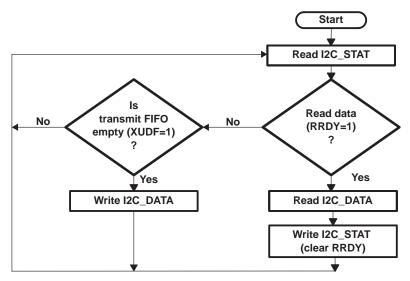

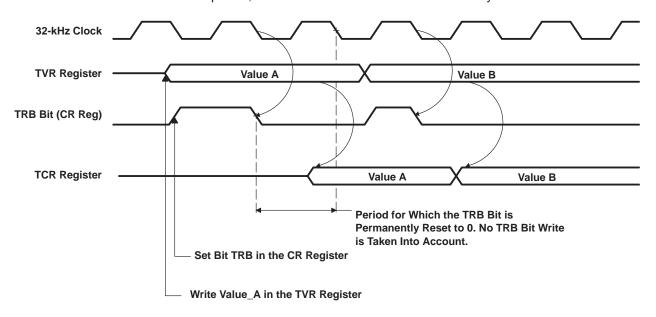

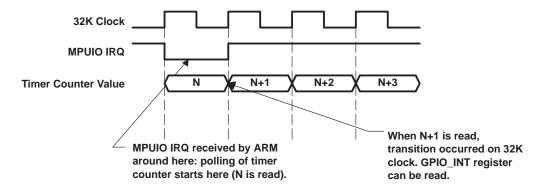

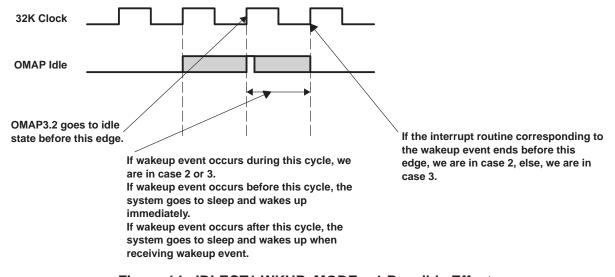

Workaround: