TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

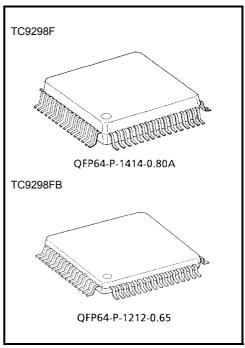

# TC9298F,TC9298FB

# LCD Driver with On-Chip Key Input

TC9298F and TC9298FB is an LCD driver with on-chip key input, which is controlled using serial data.

#### **Features**

- Supports switching between 1/4 and 1/8 duty and 1/3 and 1/4 hias

- Displays up to 176 segments in 1/4 duty mode; up to 320 segments in 1/8 duty mode.

- All display segments can be turned on or off. Outputs from the S40 to S43 pins can be switched between segment output and LED driver output.

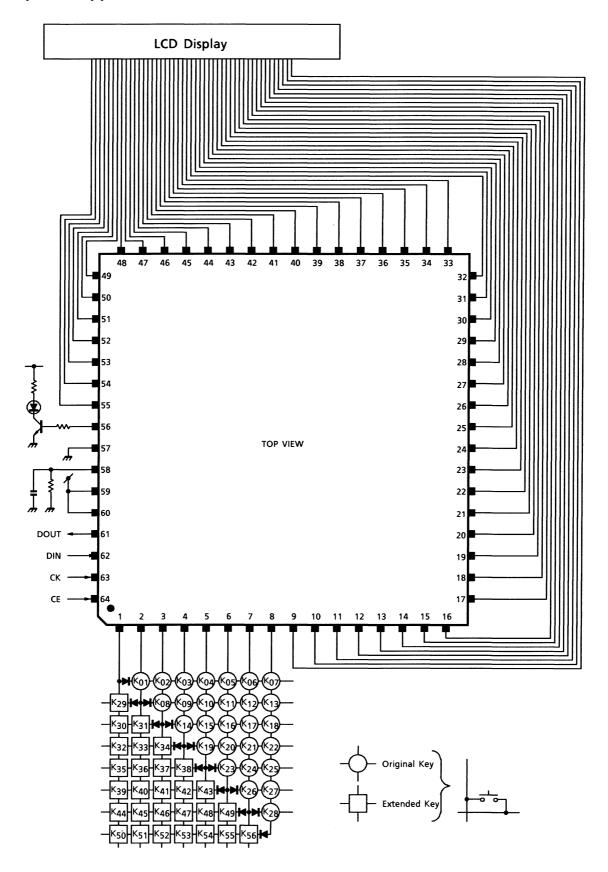

- Supports input from 28 keys as standard. Externally connecting diodes supports input from up to 56 keys.

- Four-wire configuration employed for connecting to the controller.

Weight

QFP64-P-1414-0.80A: 1.10 g (typ.) QFP64-P-1212-0.65: 0.45 g (typ.)

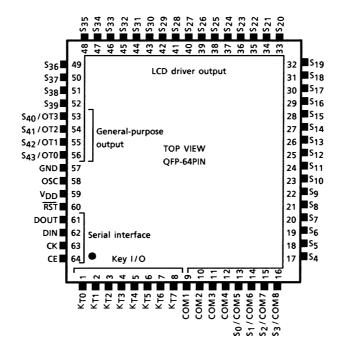

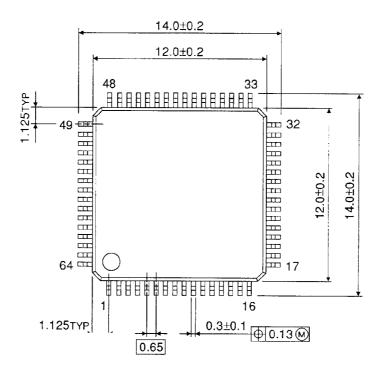

# Pin Assignment (top view)

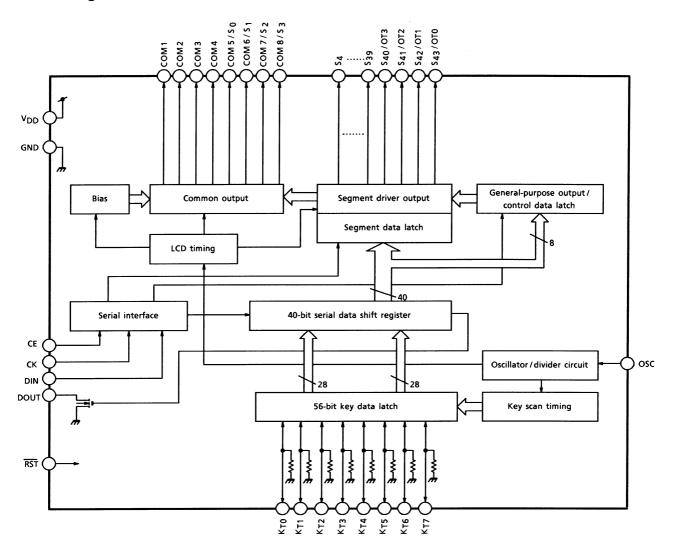

# **Block Diagram**

2

2003-06-04

# **Pin Functions**

| Pin No. | Symbol                                        | Pin Name                                               | Function                                                                                                                                                                                                                                                                                                                                                                                    | Remarks                         |  |  |

|---------|-----------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|

| 59      | $V_{DD}$                                      | Power pin                                              | Power is applied to these pins. Normally 5 V is                                                                                                                                                                                                                                                                                                                                             |                                 |  |  |

| 57      | GND                                           | Ground pin                                             | supplied. Power-on reset resets system at power on or $V_{DD}$ < 2.0 V (typical).                                                                                                                                                                                                                                                                                                           | _                               |  |  |

| 1~8     | KT <sub>0</sub> ∼KT <sub>7</sub>              | Key scan I/O pins                                      | Key scan signal I/O pins. Data can be input from 28 keys (standard) by a key matrix with other key scan I/O pins. Connecting external diodes enables data to be input from up to 56 keys.  At a fixed cycle, a pin is set to output and the other pins are set to input. The pin set to output outputs high level; the others are pulled down to low level by built-in pull-down resistors. | V <sub>DD</sub> V <sub>DD</sub> |  |  |

| 9~12    | COM1~<br>COM4                                 | Common output pins                                     | segments by a key matrix of COM1 to COM4 and $S_0$ to $S_{43}$ ; when set to 1/8 duty, can display up to                                                                                                                                                                                                                                                                                    |                                 |  |  |

| 13~16   | S <sub>0</sub> /COM5~<br>S <sub>3</sub> /COM8 | Segment output pins /common output pins                | 320 segments by a key matrix of COM1 to COM8 and $S_4$ to $S_{43}$ . When set to 1/8 duty, $S_0$ to $S_3$ are used as COM5 to COM8.                                                                                                                                                                                                                                                         | <b>∜</b> VDD                    |  |  |

| 17~52   | S <sub>4</sub> ~S <sub>39</sub>               | Segment output pins                                    | Segment signal output pins for LCD.  When set to 1/4 duty, can display up to 176 segments by a key matrix of COM1 to COM4 and S <sub>0</sub> to S <sub>43</sub> ; when set to 1/8 duty, can display up to 320 segments by a key matrix of COM1 to COM8 and S <sub>4</sub> to S <sub>43</sub> .                                                                                              |                                 |  |  |

| 53~56   | S <sub>40</sub> /OT3~<br>S <sub>43</sub> /OT0 | Segment output pins<br>/general-purpose<br>output pins | S <sub>40</sub> to S <sub>43</sub> are also used as general-purpose output pins.  When set to general-purpose output, S <sub>40</sub> to S <sub>43</sub> output CMOS outputs.                                                                                                                                                                                                               |                                 |  |  |

| 58      | osc                                           | CR oscillator pin                                      | Connecting C and R generates the system clock. The oscillation frequency is expressed as follows: $f_{\text{OSC}} \simeq 1.41/(\text{C} \cdot \text{R}) \text{ [Hz]}$ For example, where C = 0.01 $\mu\text{F}$ and R = 27 k $\Omega$ $f_{\text{OSC}} \simeq 5.22 \text{ kHz}$                                                                                                              | V DD R                          |  |  |

| 60      | RST                                           | Reset input pin                                        | Reset signal input pin for device system reset.  While the RST input is at low level, stops the oscillator, resetting all internal data. At the same time, fixes the LCD output pins to low level.  Since the power-on reset circuit is incorporated, for normal use, connect the RST pin to V <sub>DD</sub> .                                                                              | VDD VDD                         |  |  |

| 61      | DOUT                                          | Data output pin                                        | Serial interface pins.  Used to transfer to and from the controller, display data, key input data, and data for controlling these data.  While the CE pin is at low level, disables data transfer. Setting the CE pin to high level inputs or                                                                                                                                               |                                 |  |  |

| 62      | DIN                                           | Data input pin                                         | outputs data to or from the DIN/DOUT pin in sync with the clock input to the CK pin.                                                                                                                                                                                                                                                                                                        |                                 |  |  |

| 63      | CK                                            | Clock input pin                                        | All input pins incorporate Schmitt circuits.                                                                                                                                                                                                                                                                                                                                                | <b>○</b>                        |  |  |

|         |                                               | Chip enable input                                      | pat pino moorporato commit officiale.                                                                                                                                                                                                                                                                                                                                                       |                                 |  |  |

# **The Contents of Address Data**

| Duty | (                 | Can be | Omitte | d | A0 | A1 | A2 | A3 | Address (HEX) | D <sub>0</sub>                                  | D <sub>1</sub>                           | D <sub>2</sub>  | D <sub>3</sub>  | D <sub>4</sub>       | D <sub>5</sub>             | D <sub>6</sub>                          | D <sub>7</sub>       | D <sub>8</sub> ~D <sub>11</sub>  | D <sub>12</sub> ~D <sub>15</sub> | D <sub>16</sub> ~D <sub>28</sub> | D <sub>29</sub> ~D <sub>39</sub> |     |  |  |  |  |

|------|-------------------|--------|--------|---|----|----|----|----|---------------|-------------------------------------------------|------------------------------------------|-----------------|-----------------|----------------------|----------------------------|-----------------------------------------|----------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-----|--|--|--|--|

|      |                   |        |        |   |    |    |    |    |               |                                                 |                                          |                 |                 | 1                    | :                          | S <sub>9</sub> to S <sub>0</sub> displa | I <u> </u>           |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 0  | 0  | 0  | 0  | 0             |                                                 | 5                                        | S <sub>9</sub>  |                 |                      | (                          | S <sub>8</sub>                          |                      | S <sub>7</sub>                   | S <sub>6</sub>                   | S <sub>5</sub>                   | ~S <sub>0</sub>                  |     |  |  |  |  |

|      |                   |        |        |   |    |    |    |    |               | COM4                                            | СОМЗ                                     | COM2            | COM1            | COM4                 | COM3                       | COM2                                    | COM1                 | COM4, 3, 2, 1                    | COM4, 3, 2, 1                    | COM4                             | , 3, 2, 1                        |     |  |  |  |  |

|      |                   |        |        |   |    |    |    |    |               |                                                 | I.                                       | I.              | I.              |                      | S                          | <sub>19</sub> to S <sub>10</sub> disp   | lay data             |                                  | l                                | - I                              |                                  |     |  |  |  |  |

| 1/4  | *                 | *      | *      | * | 1  | 0  | 0  | 0  | 1             |                                                 | S                                        | 19              |                 |                      | S                          | 18                                      |                      | S <sub>17</sub>                  | S <sub>16</sub>                  | S <sub>15</sub>                  | ~S <sub>10</sub>                 |     |  |  |  |  |

|      |                   |        |        |   |    |    |    |    |               | COM4                                            | COM3                                     | COM2            | COM1            | COM4                 | COM3                       | COM2                                    | COM1                 | COM4, 3, 2, 1                    | COM4, 3, 2, 1                    | COM4                             | , 3, 2, 1                        |     |  |  |  |  |

|      | *                 | *      | *      | * | 0  | 1  | 0  | 0  | 2             |                                                 |                                          |                 |                 | •                    | S                          | <sub>29</sub> to S <sub>20</sub> disp   | lay data             |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 1  | 1  | 0  | 0  | 3             |                                                 |                                          |                 |                 |                      | S                          | <sub>39</sub> to S <sub>30</sub> disp   | lay data             |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 0  | 0  | 1  | 0  | 4             |                                                 |                                          |                 |                 | S                    | 43 to S <sub>40</sub> disp | olay data                               |                      |                                  |                                  | Input pi                         | rohibited                        |     |  |  |  |  |

|      |                   |        |        |   |    |    |    |    |               |                                                 |                                          |                 |                 |                      | ;                          | S <sub>8</sub> to S <sub>4</sub> displa | ay data              |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | * * * * * 0 0 0 0 |        |        |   | 0  |    |    |    |               | S <sub>8</sub>                                  |                                          |                 |                 | S <sub>7</sub>       |                            | S <sub>6</sub> ~S <sub>4</sub>          |                      |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      |                   |        |        |   |    |    |    |    |               | COM8                                            | COM7                                     | COM6            | COM5            | COM4                 | COM3                       | COM2                                    | COM1                 | COM8, 7, 6                       | , 5, 4, 3, 2, 1                  | COM8                             | ~COM1                            |     |  |  |  |  |

|      |                   |        |        |   |    |    |    |    |               |                                                 |                                          | l .             | l .             |                      | 5                          | S <sub>13</sub> to S <sub>9</sub> disp  | ay data              |                                  |                                  | 1                                |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 1  | 0  | 0  | 0  | 1             |                                                 | S <sub>13</sub> S <sub>12</sub>          |                 |                 |                      |                            |                                         | 12                   | S <sub>11</sub>                  | <sub>1</sub> ~S <sub>9</sub>     |                                  |                                  |     |  |  |  |  |

| 4/0  |                   |        |        |   |    |    |    |    |               | COM8                                            | COM7                                     | COM6            | COM5            | COM4                 | COM3                       | COM2                                    | COM1                 | COM8, 7, 6                       | , 5, 4, 3, 2, 1                  | COM8                             | ~COM1                            |     |  |  |  |  |

| 1/8  | *                 | *      | *      | * | 0  | 1  | 0  | 0  | 2             |                                                 |                                          |                 |                 | •                    | S                          | <sub>18</sub> to S <sub>14</sub> disp   | lay data             |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 1  | 1  | 0  | 0  | 3             |                                                 |                                          |                 |                 |                      | S                          | <sub>23</sub> to S <sub>19</sub> disp   | lay data             |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 0  | 0  | 1  | 0  | 4             |                                                 |                                          |                 |                 |                      | S                          | <sub>28</sub> to S <sub>24</sub> disp   | lay data             |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 1  | 0  | 1  | 0  | 5             | S <sub>33</sub> to S <sub>29</sub> display data |                                          |                 |                 |                      |                            |                                         |                      |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 0  | 1  | 1  | 0  | 6             |                                                 |                                          |                 |                 |                      | S                          | <sub>38</sub> to S <sub>34</sub> disp   | lay data             |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 1  | 1  | 1  | 0  | 7             |                                                 |                                          |                 |                 |                      | S                          | 43 to S <sub>39</sub> disp              | lay data             |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | ų.     | •      |   |    |    | _  |    |               | EV 000                                          | Segment/general-purpose output switching |                 |                 | witching             |                            | land of an analysis is a                |                      |                                  |                                  |                                  |                                  |     |  |  |  |  |

|      | *                 | *      | *      | * | 0  | 0  | 0  | 1  | 8             | EX-OSC                                          | 0                                        | 0               | DUTY            | S <sub>43</sub> /OT0 | S <sub>42</sub> /OT1       | S <sub>41</sub> /OT2                    | S <sub>40</sub> /OT3 |                                  | Input prohibited                 | 1                                |                                  |     |  |  |  |  |

|      | *                 |        |        |   | _  |    |    |    |               |                                                 |                                          | <u> </u>        |                 |                      | DDIAG                      | [                                       | Display contro       | ol                               | Ge                               | eneral-purpos                    | se output cont                   | rol |  |  |  |  |

|      | *                 | *      | *      | * | 1  | 0  | 0  | 1  | 9             | RBIAS LT BL OP OT0 OT1 OT2 OT3                  |                                          |                 |                 |                      |                            | 1                                       |                      |                                  |                                  |                                  |                                  |     |  |  |  |  |

| _    | *                 | *      | *      | * | 0  | 1  | 0  | 1  | ^             |                                                 | •                                        | •               | •               |                      | Key                        | data output                             | •                    |                                  |                                  |                                  | Undefined                        |     |  |  |  |  |

|      |                   |        |        |   |    | 1  | 0  | '  | Α             | K <sub>ON</sub>                                 | K <sub>01</sub>                          | K <sub>02</sub> | K <sub>03</sub> | K <sub>04</sub>      | K <sub>05</sub>            | K <sub>06</sub>                         | K <sub>07</sub>      | K <sub>08~</sub> K <sub>11</sub> | K <sub>12~</sub> K <sub>15</sub> | K <sub>12~</sub> K <sub>15</sub> | Unidenned                        |     |  |  |  |  |

|      | *                 | *      | *      | * | 1  | 1  | 0  | 1  | ь             |                                                 | •                                        |                 |                 | •                    | Expanded                   | key data out                            | put                  |                                  |                                  | •                                | Undefined                        |     |  |  |  |  |

|      |                   | -      |        |   | '  | '  | 0  | '  | В             | K <sub>ON</sub>                                 | K <sub>29</sub>                          | K <sub>30</sub> | K <sub>31</sub> | K <sub>32</sub>      | K <sub>33</sub>            | K <sub>34</sub>                         | K <sub>35</sub>      | K <sub>36~</sub> K <sub>39</sub> | K <sub>40~</sub> K <sub>43</sub> | K <sub>44~</sub> K <sub>56</sub> | Unidenned                        |     |  |  |  |  |

### **Description of Operation**

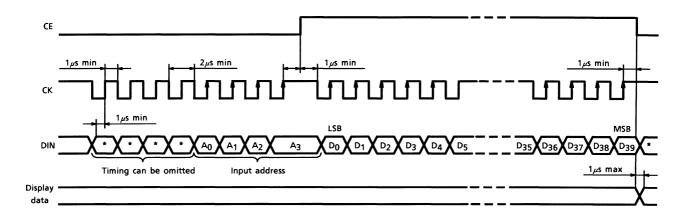

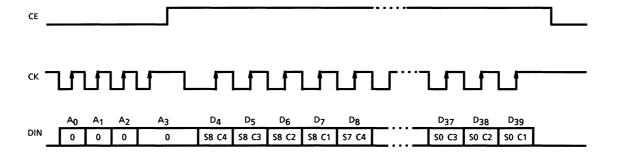

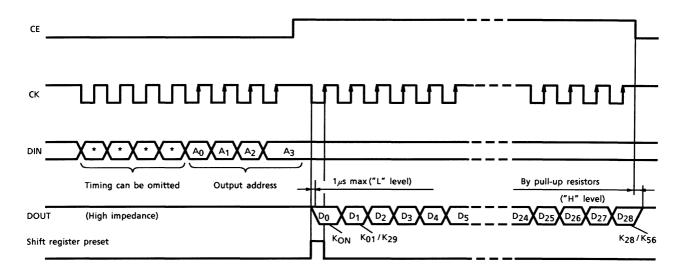

### 1. Display and Control Data Input Format

• The display and control data input timing is as follows.

- \*: Don't care

- Set all display data bits for outputting the segments to be used.

- The display data for outputting unused segments need not be set, but only on the LSB side.

- At input the DOUT pin goes to high impedance.

(example) At 1/4 duty, if the address for setting the data is set to 0H, segment output pins from S0 to S8 are used and S9 is not, the S9 display data can be omitted as shown below.

#### (1) Display control data bit

This bit sets the display on/off. In accordance with the setting, the waveform corresponding to display on/off is output to a segment output pin. Setting the bit to 1 outputs display on waveform; setting the bit to 0, display off waveform.

First specify an address from  $0H\sim4H$  at 1/4 duty or an address from  $0H\sim7H$  at 1/8 duty, then set the data for each segment in sequence, starting from the segment's upper bit.

If any segments remain unused, the data settings can be omitted from the highest segment output pins.

| 0 | Display off |

|---|-------------|

| 1 | Display on  |

Note 1: After a reset these data are undefined.

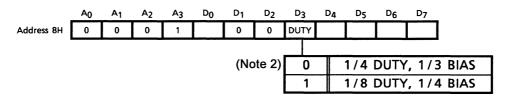

### (2) Duty control bit (DUTY)

The DUTY bit controls the switching between 1/4 and 1/8 duty. Setting this bit to 0 selects 1/4 duty; to 1 selects 1/8 duty.

Selecting 1/4 duty switches the S0/COM5~S3/COM8 pins to segment output pins S0~S3. Selecting 1/8 duty switches the S0/COM5~S3/COM8 pins to common output pins COM5~COM8.

To set the data, specify the address as 8H.

Note 2: After a reset these data are cleared to 0.

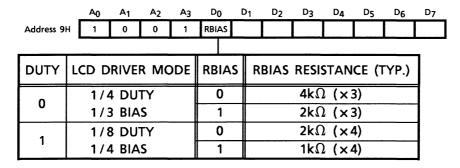

#### (3) Bias resistance control bit (RBIAS)

This bit controls the resistance (RBIAS) value for generating the bias voltage.

At 1/4 duty and 1/3 bias, writing 0 to the bit sets RBIAS = 4 k $\Omega$ , while writing 1 to the bit sets RBIAS = 2 k $\Omega$ .

At 1/8 duty and 1/4 bias, writing 0 to the bit sets RBIAS = 2 k $\Omega$ , while writing 1 to the bit sets RBIAS = 1 k $\Omega$ .

To set the data, specify the address as 9H.

If setting RBIAS to 0 increases the noise on the LCD driver output waveform and adversely affects the display, set RBIAS to 1 to reduce the noise.

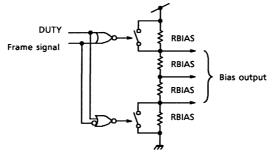

### (configuration of bias circuit)

Note 3: After a reset these data are cleared to 0.

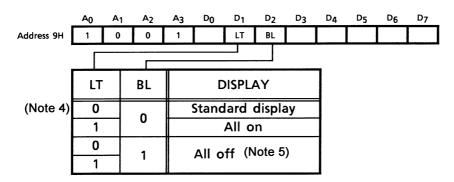

#### (4) All-on/all-off control bits (BL/LT)

The BL/LT bits turn each display to all-on or all-off. Setting both bits to 0 outputs standard display data to each segment output pin. Setting BL to 1 outputs the display off waveform to all the segment output pins. Setting BL to 1 outputs the display on waveform to all the segment output pins.

When all-on or all-off is set, the previous display data are held. There is no need to set the display data again. New data can also be set during the all-on or all-off states.

To set the data, specify the address as 9H.

Note 4: After a reset these data are cleared to 0.

Note 5: When BL and LT are both set to 1, BL takes priority.

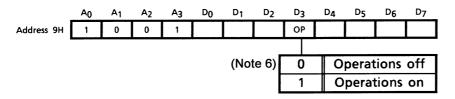

#### (5) Operation control bit (OP)

The OP bit starts/stops the LCD driver and key scan functions.

Setting OP to 0 stops the oscillation and fixes the LCD driver output pins and the key scan input/output pins to Low.

After operations are turned off, the previous data of all data bits are held. New data can also be set while the operations are off.

A reset clears the OP bit to 0 and turns off the LCD driver and key scanner operations. While the operations are off, initialize the control data and display data.

To set the data, specify the address as 9H.

Note 6: After a reset these data are cleared to 0.

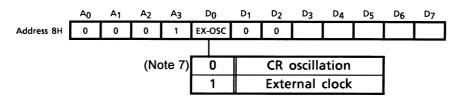

#### (6) External clock input control bit (EX-OSC)

The EX-OSC bit selects oscillator operation or external clock input.

Setting this bit to 0 operates the oscillator circuit with external CR.

Setting the bit to 1 sets the OSC pin as a CMOS input pin with Schmitt circuit and inputs an external clock as the system clock. Use this pin at such times as when using an output clock from a microcontroller.

To set the data, specify the address as 8H.

Note 7: After a reset these data are cleared to 0.

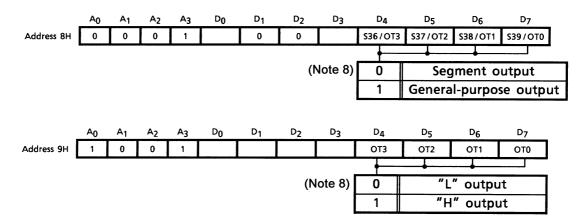

(7) Segment/general-purpose output switching bits (S43/OT0~S40/OT3) and general-purpose output control bits (OT0~OT3)

The segment/general-purpose output switching bits switch between segment output and general-purpose output. Setting 0 selects segment output; setting 1 selects general-purpose output. When segment output is selected, a display on/off waveform corresponding to the display data is output. When general-purpose output is selected, the general-purpose output control bit sets the output status.

Setting the general-purpose output control bit to 0 outputs Low. Setting the bit to 1 outputs High.

When segment output is selected, the corresponding general-purpose output control data are invalid. When general-purpose output is selected, the corresponding segment output display data are invalid.

To set the segment/general-purpose output switching bits, specify the address as 8H.

To set the general-purpose output control bits, specify the address as 9H.

Note 8: After a reset these data are cleared to 0.

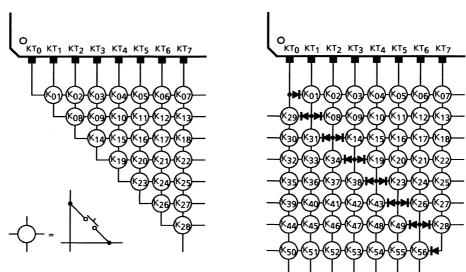

#### (8) Key data bits (Kon, Ko1~K56)

These are the key data bits of the key matrix. The  $K_{ON}$  bit shows whether the key input is on or off. The  $K_{01}$ ~ $K_{56}$  bits, each corresponding to a key, show which key is being pressed.

Key input sets KON to 1. No key input sets KON to 0. A key input corresponding to  $K_{01}\sim K_{56}$  sets the relevant  $K_{01}\sim K_{56}$  bit to 1. No key input corresponding to  $K_{01}\sim K_{56}$  sets the relevant  $K_{01}\sim K_{56}$  bit to 0.

### **KON Bit**

| 0 | No key input |

|---|--------------|

| 1 | Key input    |

### K<sub>0</sub>~K<sub>56</sub> Bits

| 0 | No key input |

|---|--------------|

| 1 | Key input    |

Note 9: After a reset these data are undefined.

### 2. Data Output Mode (key data)

(1) The key data are output at the following timing.

#### (2) Structure of key matrix

One of two matrices can be selected for the key matrix: a matrix with up to 28 keys without any external components, or a matrix with up to 56 keys with external diodes.

# **Structure of Key Matrix**

Note 10: When a key is input, KON is set to 1.

- Note 11: Setting the CE pin to 1 then to 0 after address input sets the DOUT pin to output. With DOUT in an output state, the K<sub>ON</sub> bit can be monitored by halting the timing.

- Note 12: If there are any unnecessary key data, the key data output can be stopped by setting the CE pin to 0.

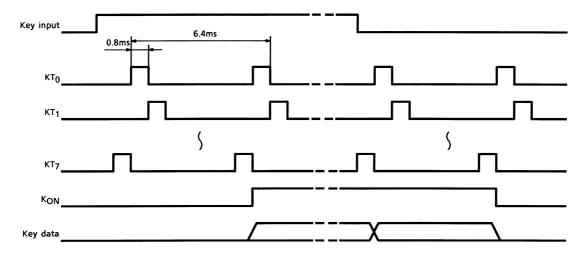

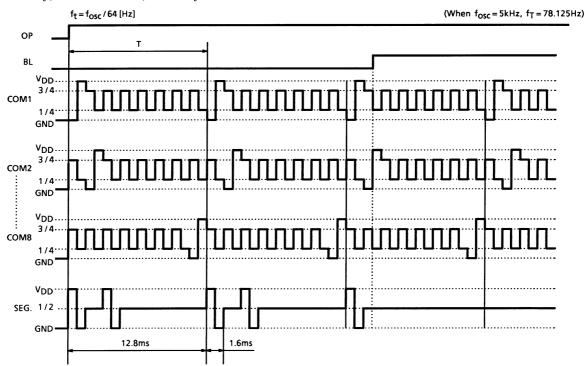

(3) The keys are scanned at the following timing.

Note 13: When  $f_{\text{OSC}} = 5 \text{ kHz}$

When OP is set to 1, the keys are scanned. The key scan cycle is 32 times the oscillation cycle (6.4 ms @ $f_{OSC} = 5 kHz$ ). The key data are also updated at this timing. The actual data become valid and updated one cycle after each key scan cycle.

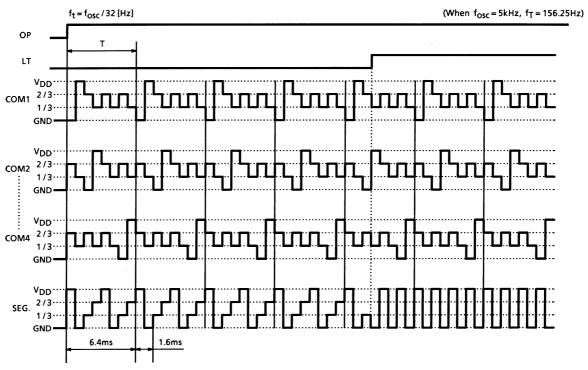

### 3. The Output Waveforms of the LCD Driver are as Shown Below.

• 1/4 duty, 1/3 bias (COM1, COM3 system on)

• 1/8 duty, 1/4 bias (COM1, COM3 system on)

# Maximum Ratings (Ta = 25°C)

| Characteristics       | Symbol           | Rating                     | Unit |

|-----------------------|------------------|----------------------------|------|

| Supply voltage        | $V_{DD}$         | -0.3~6.0                   | V    |

| Input voltage 1       | V <sub>IN1</sub> | -0.3~V <sub>DD</sub> + 0.3 | V    |

| Input voltage 2       | V <sub>IN2</sub> | -0.3~6.0 (Note 14)         | V    |

| Power dissipation     | $P_{D}$          | 300                        | mW   |

| Operating temperature | T <sub>opr</sub> | -40~85                     | °C   |

| Storage temperature   | T <sub>stg</sub> | −65 <b>~</b> 150           | °C   |

Note 14: DIN, CK, CE pins

# Electrical Characteristics (unless otherwise specified, $V_{DD} = 2.7$ to 5.5 V, Ta = -40 to 85°C)

| Characteristics          |           | Symbol           | Test<br>Circuit | Test Condition                                                                                  | Min                   | Тур. | Max                   | Unit |  |

|--------------------------|-----------|------------------|-----------------|-------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|--|

| Operating supply         | voltage   | $V_{DD}$         | _               | _                                                                                               | 2.7                   | 5.0  | 5.5                   | V    |  |

| Power-on reset v         | oltage    | V <sub>RST</sub> | _               | _                                                                                               | 1.5                   | 2.0  | 2.5                   | V    |  |

|                          |           |                  | _               | $V_{DD} = 5 \text{ V}, f_{OSC} = 5 \text{ kHz},$ No load  1/3 BIAS, RBIAS = 4 k $\Omega$ (typ.) | _                     | 0.7  | 1.5                   |      |  |

|                          |           |                  | _               | V <sub>DD</sub> = 5 V, f <sub>osc</sub> = 5 kHz,<br>No load                                     | _                     | 1.1  | 2.0                   |      |  |

| Operating supply current |           | I <sub>DD1</sub> |                 | 1/3 BIAS, RBIAS = $2 \text{ k}\Omega$ (typ.)                                                    |                       |      |                       | · mA |  |

|                          |           | 551              | _               | $V_{DD} = 5 \text{ V}, f_{OSC} = 5 \text{ kHz},$<br>No load                                     | _                     | 0.9  | 2.0                   |      |  |

|                          |           |                  |                 | 1/4 BIAS, RBIAS = 2 kΩ (typ.)                                                                   |                       |      |                       |      |  |

|                          |           |                  | _               | $V_{DD} = 5 \text{ V}, f_{OSC} = 5 \text{ kHz},$<br>No load                                     | _                     | 1.5  | 2.5                   |      |  |

|                          |           |                  |                 | 1/4 BIAS, RBIAS = 1 kΩ (typ.)                                                                   |                       |      |                       |      |  |

| Stand-by current         |           | I <sub>DD2</sub> | _               | V <sub>DD</sub> = 5 V, OP = "0"                                                                 |                       | 150  | 300                   | μΑ   |  |

|                          |           | V <sub>IH1</sub> | _               | КТ <sub>0</sub> -КТ <sub>3</sub>                                                                | V <sub>DD</sub> × 0.6 | ~    | V <sub>DD</sub>       |      |  |

|                          | "H" level | V <sub>IH2</sub> | _               | RST                                                                                             | V <sub>DD</sub> × 0.8 | ~    | V <sub>DD</sub>       |      |  |

| Input voltage            |           | V <sub>IH3</sub> | _               | DIN, CK, CE                                                                                     | V <sub>DD</sub> × 0.8 | ~    | 5.5                   | V    |  |

|                          | "L" level | V <sub>IL1</sub> | _               | K <sub>T0</sub> -K <sub>T3</sub>                                                                | 0                     | ~    | V <sub>DD</sub> × 0.1 |      |  |

|                          | Lievei    | V <sub>IL2</sub> | _               | RST , DIN, CK, CE                                                                               | 0                     | ~    | V <sub>DD</sub> × 0.2 |      |  |

| Schmitt voltage          |           | V <sub>SCH</sub> | _               | V <sub>DD</sub> = 5 V, DIN, CK, CE                                                              |                       | 1.0  | _                     | ٧    |  |

| Input leakage            | "H" level | I <sub>IH</sub>  | _               | $V_{IN} = V_{DD}, \ \overline{RST}$ , DIN, CK, CE                                               | _                     | _    | ±1.0                  | μΑ   |  |

| current                  | "L" level | I <sub>IL</sub>  | _               | V <sub>IN</sub> = 0 V, RST, DIN, CK, CE                                                         | _                     | _    | ±1.0                  |      |  |

# **TOSHIBA**

| Chara                 | Characteristics |                  | Test<br>Circuit | Test Condition                                                                                                                | Min                             | Тур.                   | Max                             | Unit |

|-----------------------|-----------------|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|---------------------------------|------|

| Output voltage        | 1/4 level       | V <sub>1/4</sub> | _               | V <sub>DD</sub> = 5 V, COM1-COM8                                                                                              | 1/4<br>V <sub>DD</sub> –<br>0.3 | 1/4<br>V <sub>DD</sub> | 1/4<br>V <sub>DD</sub> +<br>0.3 |      |

|                       | 1/3 level       | V <sub>1/3</sub> | _               | V <sub>DD</sub> = 5 V, COM1-COM4,<br>S <sub>0</sub> -S <sub>43</sub>                                                          | 1/3<br>V <sub>DD</sub> –<br>0.3 | 1/3<br>V <sub>DD</sub> | 1/3<br>V <sub>DD</sub> +<br>0.3 |      |

|                       | 1/2 level       | V <sub>1/2</sub> | _               | V <sub>DD</sub> = 5 V, S <sub>4</sub> -S <sub>43</sub>                                                                        | 1/2<br>V <sub>DD</sub> –<br>0.3 | 1/2<br>V <sub>DD</sub> | 1/2<br>V <sub>DD</sub> +<br>0.3 | V    |

|                       | 2/3 level       | V <sub>2/3</sub> | _               | V <sub>DD</sub> = 5 V, COM1-COM4,<br>S <sub>0</sub> -S <sub>43</sub>                                                          | 2/3<br>V <sub>DD</sub> –<br>0.3 | 2/3<br>V <sub>DD</sub> | 2/3<br>V <sub>DD</sub> +<br>0.3 |      |

|                       | 3/4 level       | V <sub>3/4</sub> | _               | V <sub>DD</sub> = 5 V, COM1-COM8                                                                                              | 3/4<br>V <sub>DD</sub> –<br>0.3 | 3/4<br>V <sub>DD</sub> | 3/4<br>V <sub>DD</sub> +<br>0.3 |      |

| Output current        | "H" level       | Іон              | _               | $V_{DD} = 5 \text{ V}, V_{OH} = 4.5 \text{ V}, KT_0\text{-KT}_7, COM1\text{-COM8}, S_0\text{-S}_{43}, OT_0\text{-OT}_3$       | -0.5                            | -3.0                   | _                               | mA   |

|                       | "L" level       | l <sub>OL</sub>  | _               | $V_{DD} = 5 \text{ V}, V_{OL} = 0.5 \text{ V}, KT_0\text{-KT}_7, COM1\text{-COM8}, S_0\text{-S}_{43}, OT_0\text{-OT}_3, DOUT$ | 0.5                             | 3.0                    | _                               | IIIA |

| Off leakage current   |                 | I <sub>LO</sub>  | _               | V <sub>OUT</sub> = 5.5 V, DOUT                                                                                                | _                               | _                      | ±1.0                            | μА   |

| Pull-down resista     | nce             | R <sub>IN</sub>  | _               | KT <sub>0</sub> -KT <sub>7</sub>                                                                                              | 75                              | 150                    | 300                             | kΩ   |

| Oscillation frequency |                 | f <sub>osc</sub> | _               | _                                                                                                                             | _                               | 5                      | 20                              | kHz  |

# **Example for Application Circuit**

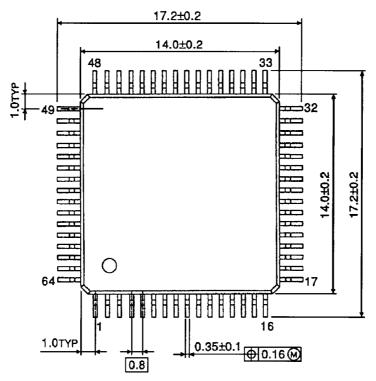

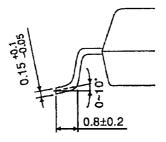

# **Package Dimensions**

QFP64-P-1414-0.80A

15

Weight: 1.10 g (typ.)

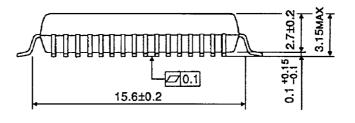

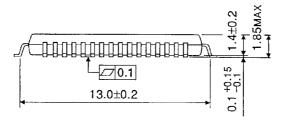

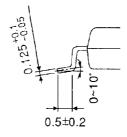

# **Package Dimensions**

QFP64-P-1212-0.65 Unit: mm

Weight: 0.45 g (typ.)

### **RESTRICTIONS ON PRODUCT USE**

Handbook" etc..

030519EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.