# **Quad IEEE 802.3at Power-Over-Ethernet PSE Controller**

Check for Samples: TPS23851

## **FEATURES**

- INDUSTRY STANDARD PSE

- Fully IEEE Std 802.3at-2009 Compliant

- Four Independent PSE Ports

- PD Detection and Classification

- Current Limit Output Protection with Foldback for Reduced Cost FET

- AC and DC Disconnect Detection

- I<sup>2</sup>C<sup>™</sup> Communication

- 4 Bit Address for 64-Port Systems

- Flexible Operation Modes

- Automatic

- Semi Automatic

- Processor Controlled

- Pin Compatible with LTC4259A and MAX5952, MAX5945, MAX5935

- **ENHANCED FEATURES**

- **Never Fooled 4-Point Detection**

- Onboard Precision 110-Hz AC Disconnect **Sine Wave Oscillator**

- I<sup>2</sup>C Watchdog for Failsafe Operation

- Individual and Multiplexed Port Shutdown **Modes**

- Per Port A/D Converters

- 14-Bit Resolution for Precision Measurements

- Real-time Voltage Monitoring

- Real-time Current Monitoring

- Inherent Filtering

- Extended -20°C to 125°C Temperature Operation

- 802.3at Type 2 Mode

- High-Power Mode

- Classification through Link Laver **Discovery Protocol (LLDP)**

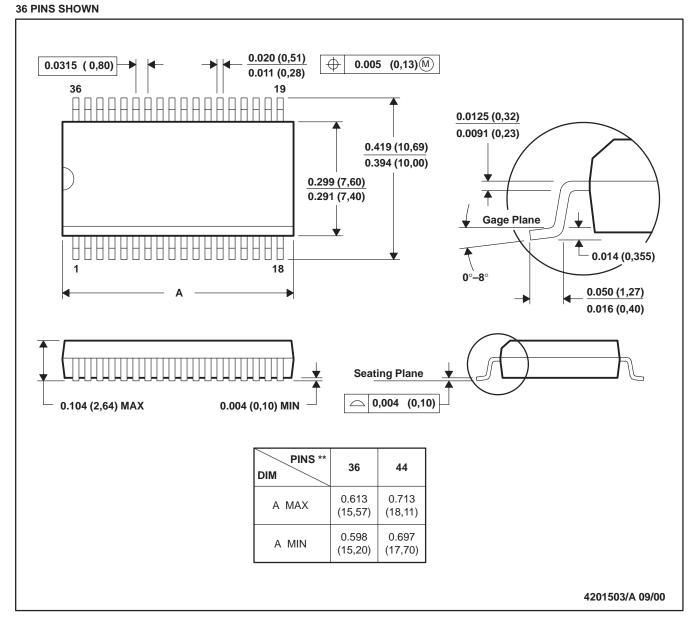

- Available in 36-lead SSOP Package

#### **APPLICATIONS**

**Ethernet Switches and Routers**

#### DESCRIPTION

The TPS23851 is a quad-power controller engineered to insert power onto Ethernet cable according to IEEE Std 802.3at-2009 (or 802.3at) for Power Sourcing Equipment (PSE). The PSE controller can detect Powered devices (PDs) that have a valid signature, determine the power requirements of the devices according to the classification, and apply power to the devices, limited per 802.3at. Based on an industry standard register set, the PSE controller is software compatible with other PSE controllers for basic functionality

Beyond the industry standard operation, the TPS23851 operates with enhanced features. Port current trip point can be set to all classification thresholds of IEEE Std 802.3-2005 (or 802.3af) and can be programmed up to more than 720 mA when used with a LLDP classification stack, complying with 802.3at. The TPS23851 supports AC and DC disconnection with a precision on-chip, 110-Hz oscillator for AC waveform generation. The PSE also contains four 14-bit A/D converters that constantly monitor voltage and current on each port. This information is available on the I2C bus for power management. The unique converter integrating topology used in the TPS23851 provides inherent filtering for a robust solution.

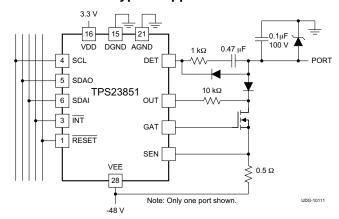

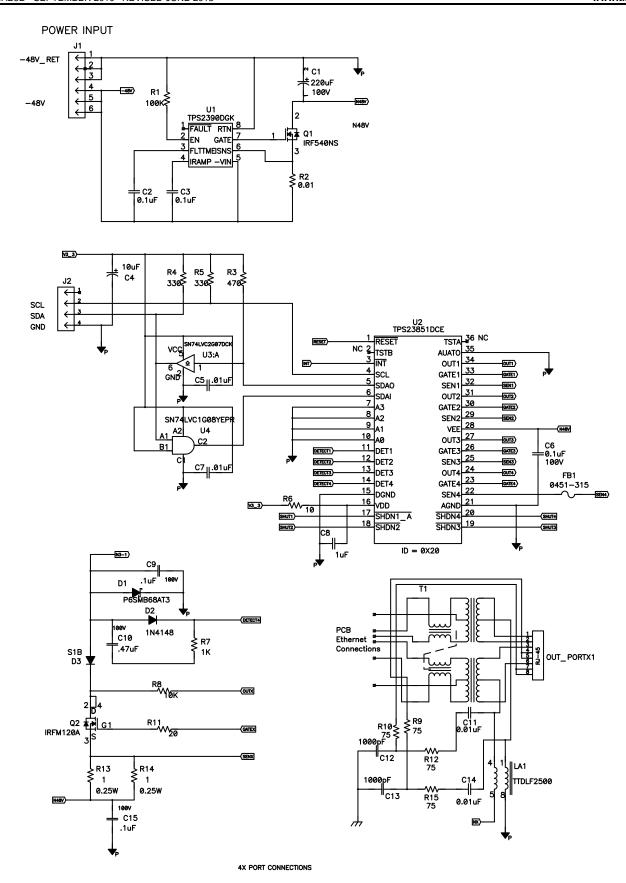

## **Typical Application**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. I<sup>2</sup>C is a trademark of Royal Philips Electronics.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## PRODUCT INFORMATION(1)

| T <sub>J</sub> | PACKAGE      | ORDERING CODE | MARKING  |

|----------------|--------------|---------------|----------|

| -20°C to 125°C | DCE36 (SSOP) | TPS23851DCE   | TPS23851 |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder on www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**(1)

voltages are referenced to DGND (unless otherwise noted)

|                                      | PARAMETER                                                                    | MIN                | MAX | UNIT |

|--------------------------------------|------------------------------------------------------------------------------|--------------------|-----|------|

| Input voltage                        | VEE to AGND                                                                  | -70                | 0.3 |      |

| Input voltage                        | VDD                                                                          | -0.3               | 3.6 |      |

| Voltage range                        | AGND                                                                         | -1                 | 1   |      |

| Voltage range                        | SDAI, SDAO (2), SCL, A0 (3), A1 (3), A2 (3), A3 (3), SHDN1-4, RESET, INT (2) | -0.3               | 3.6 |      |

| Output voltage                       | GATE1-4 to VEE (4)                                                           | -0.3               | 12  | V    |

| Input voltage range                  | SEN1-4 to VEE                                                                | -0.3               | 3   |      |

| Input voltage range                  | OUT1-4 to VEE                                                                | -3                 | 70  |      |

| Voltage range                        | DET1-4 to VEE <sup>(2)</sup>                                                 | -0.3               | 70  |      |

| Voltage range                        | TSTA, TSTB (2)                                                               | VEE                | VDD |      |

| Voltage slew rate                    | VEE                                                                          |                    | 1   | V/µs |

| Sinking current,                     | ĪNT, SDAO                                                                    |                    | 20  | mA   |

| ESD – human body model               |                                                                              |                    | 2   | kV   |

| ESD – charged device mod             | el                                                                           |                    | 500 | V    |

| Operating junction temperature range | T <sub>J</sub>                                                               | Internally limited |     |      |

| Storage temperature                  | T <sub>ST</sub>                                                              | -65                | 125 | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Product Folder Links: TPS23851

Submit Documentation Feedback

<sup>(2)</sup> Do not apply external voltage sources directly.

<sup>(3)</sup> A3-A0 can be directly tied to DGND but a resistor (at least 2 kΩ) must be used if pulled up. Do not tie directly to a positive voltage source

<sup>(4)</sup> Application of voltage is not implied – these are internally driven pins.

## THERMAL INFORMATION

|                  |                                                             | TPS23851 |       |

|------------------|-------------------------------------------------------------|----------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | DCE      | UNITS |

|                  |                                                             | 36 PINS  |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 52.4     |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 25.1     |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 29.0     | 9000  |

| ΨЈТ              | Junction-to-top characterization parameter <sup>(5)</sup>   | 3.4      | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 26.4     |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | n/a      |       |

- For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted

- from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### RECOMMENDED OPERATING CONDITIONS

voltages are referenced to DGND (unless otherwise noted)

|                  | PARAMETER                      | MIN | NOM | MAX | UNIT |

|------------------|--------------------------------|-----|-----|-----|------|

| V <sub>VDD</sub> |                                | 3   | 3.3 | 3.5 |      |

| V <sub>VEE</sub> | To AGND                        | -44 | -48 | -57 | V    |

| V <sub>VEE</sub> | Slew rate                      |     |     | 1   | V/µs |

| TJ               | Operating junction temperature | -20 |     | 125 | °C   |

| T <sub>A</sub>   | Operating free-air temperature | -20 |     | 85  | *C   |

## **ELECTRICAL CHARACTERISTICS**

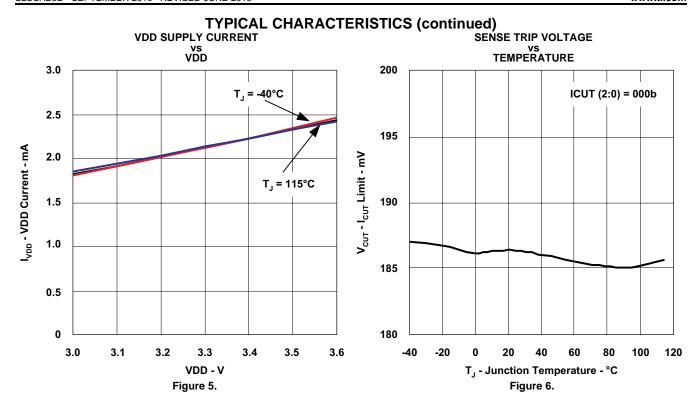

Conditions are  $-20 \le TJ \le 125^{\circ}C$  unless otherwise noted.  $V_{VDD} = 3.3 \text{ V}$ ,  $V_{VEE} = -48 \text{ V}$ ,  $V_{DGND} = V_{AGND}$ , and all outputs are unloaded, unless otherwise noted. Positive currents are into pins. Current sense resistor = 0.5  $\Omega$ . Typical values are at 25°C. All voltages are with respect to DGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                        | PARAMETER                                             | TEST CONDITIONS                                                              | MIN  | TYP    | MAX   | UNIT |

|------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|------|--------|-------|------|

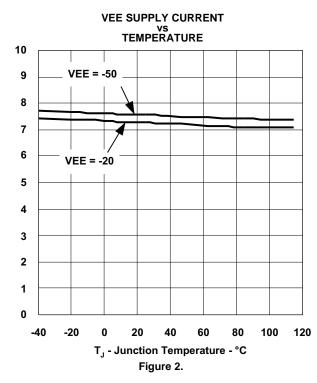

| Input Suppl            | у                                                     |                                                                              |      |        |       |      |

| $I_{VDD}$              | VDD current consumption                               |                                                                              |      | 2      | 5     | A    |

| I <sub>VEE</sub>       | VEE current consumption                               |                                                                              |      | -7     | -10   | mA   |

| Detection              |                                                       |                                                                              |      |        |       |      |

|                        | Data dia any any ant                                  | First detection point, DET = 0 V                                             | 145  | 165    | 190   | ^    |

| I <sub>DISC</sub>      | Detection current                                     | Second detection point, DET = 0 V                                            | 245  | 275    | 310   | μΑ   |

| V <sub>DETECT</sub>    | Open circuit detection voltage                        |                                                                              | -25  | -18.11 | -17   | V    |

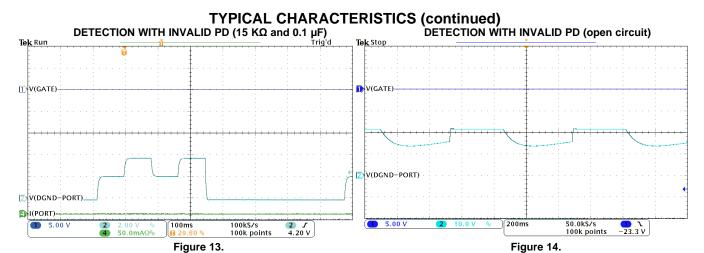

| R <sub>REJ_LOW</sub>   | Rejected resistance low range                         |                                                                              | 2.8  |        | 15    |      |

| R <sub>REJ_HI</sub>    | Rejected resistance high range                        |                                                                              | 33   |        | 55    | ΚΩ   |

| R <sub>ACCEPT</sub>    | Accepted resistance range                             |                                                                              | 19   | 25     | 26.5  | 1132 |

| R <sub>SHORT</sub>     | Shorted port threshold                                |                                                                              |      |        | 1.5   |      |

| R <sub>OPEN</sub>      | Open port threshold                                   |                                                                              | 55   |        |       |      |

| Classification         | on                                                    |                                                                              | '    | •      | '     |      |

| V <sub>CLASS</sub>     | Classification voltage                                | At DET pin                                                                   | -21  | -18.5  | -16.4 | V    |

| I <sub>CLASS_Lim</sub> | Classification current limit                          | At 0 V                                                                       | 52.5 | 70     | 95    | mA   |

| Gate                   |                                                       |                                                                              |      |        |       |      |

| $V_{GOH}$              | Gate drive voltage                                    | $V_{GATEn-VEE}$ , $I_{GATE} = -1 \mu A$                                      | 8    |        | 10.5  | V    |

| I <sub>GO-</sub>       | Gate sinking current with port short-circuit detected | V <sub>GATEn-VEE</sub> = 5 V                                                 | 70   | 100    | 120   | mA   |

| I <sub>GO+</sub>       | Gate sourcing current                                 | $V_{GATEn} = V_{VEE}$                                                        | 0.05 |        | 1.5   |      |

| t <sub>D_off</sub>     | Gate turn off time with /SHDNn                        | From SHDNn to V <sub>GATEn-VEE</sub> < 1 V, SENn connected to VEE            |      |        | 900   |      |

| t <sub>P_off_CMD</sub> | Gate turn off time from port off command              | From port off command to V <sub>GATEn-VEE</sub> < 1 V, SENn connected to VEE |      |        | 900   |      |

| t <sub>P_off_RST</sub> | Gate turn off time with RESET                         | From RESET low to V <sub>GATEn-VEE</sub> < 1V, SENn connected to VEE         | 1    |        | 5     | μs   |

| t <sub>P_didt</sub>    | Gate turn on and turn off di/dt control period        | From port turn on/off command or from SHDN input                             |      | 150    |       |      |

| OUT Pin Se             | nse                                                   | -                                                                            |      |        |       |      |

| V <sub>PGT</sub>       | Power good threshold                                  | Measured at V <sub>OUT</sub>                                                 | 1.5  | 2.13   | 3     | V    |

|                        | Resistance from OUT to AGND                           |                                                                              |      | 2.5    |       | МΩ   |

|                        |                                                       | V <sub>OUT</sub> = 0 V                                                       | -6   |        | 5     |      |

| I <sub>OUT</sub>       | OUT pin bias current                                  | -10 V > V <sub>OUT</sub> > -30 V                                             | -18  |        | 0     | μΑ   |

|                        |                                                       | V <sub>OUT</sub> = -48                                                       | -30  | -20    | -10   |      |

Product Folder Links: TPS23851

Submit Documentation Feedback

Conditions are  $-20 \le TJ \le 125^{\circ}C$  unless otherwise noted.  $V_{VDD} = 3.3 \text{ V}$ ,  $V_{VEE} = -48 \text{ V}$ ,  $V_{DGND} = V_{AGND}$ , and all outputs are unloaded, unless otherwise noted. Positive currents are into pins. Current sense resistor = 0.5  $\Omega$ . Typical values are at 25°C. All voltages are with respect to DGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                     | PARAMETER                                                                 | TEST CONDITIONS                                                | MIN   | TYP   | MAX   | UNIT   |

|---------------------|---------------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|--------|

| AC Discon           | nect                                                                      |                                                                |       |       |       |        |

| I <sub>ACDMAX</sub> | Absolute magnitude of AC disconnect DET pin drive current                 | Port powered, $V_{VEE} < V_{DET} < V_{DGND}$ , relative to VEE | -5    |       | 15    | mA     |

| I <sub>ACDMIN</sub> | AC Disconnect DET pin drive current. Minimum current to remain connected. | Port powered                                                   | 150   | 205   | 260   | μΑ     |

| V <sub>ACD</sub>    | Peak-to-peak DET pin output level                                         | Port on, PD not present. Ports 1 – 4.                          | 3.5   | 4     | 4.5   | V      |

| f <sub>sin</sub>    | sine wave frequency                                                       |                                                                | 100   | 110   | 125   | Hz     |

| A/D Conve           | rter                                                                      |                                                                |       |       |       |        |

| T <sub>CONV</sub>   | Conversion time                                                           | All ranges, each port                                          | 15    | 20    | 27.5  | ms     |

|                     | Powered port voltage                                                      | OUT = -66 V                                                    | 10800 | 11147 | 11400 |        |

|                     | conversion scale factor and accuracy                                      | OUT = -44 V                                                    | 7200  | 7432  | 7600  | Counts |

|                     | Powered port current                                                      | Port current = 770 mA                                          | 12288 | 12616 | 12944 | Counts |

|                     | conversion scale factor and accuracy                                      | Port current = 10 mA                                           | 100   | 163.8 | 220   |        |

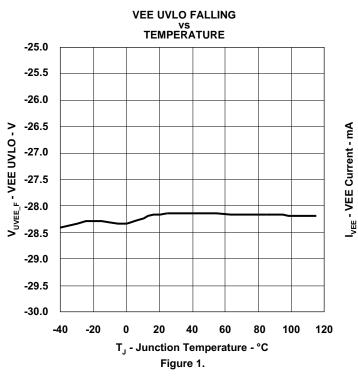

| Input Supp          | bly UVLO                                                                  |                                                                |       |       |       |        |

| V <sub>UVEE_F</sub> | VEE UVLO falling threshold                                                | VEUV threshold (supply event register) for port deassertion    | 25    | 31    | 34    |        |

| V <sub>UVP_F</sub>  | VDD UVLO falling threshold                                                | For port deassertion                                           | 1.9   | 2.3   | 2.6   | V      |

| V <sub>DD_I2C</sub> | Required VDD supply for I <sup>2</sup> C operation                        |                                                                | 2.9   |       |       |        |

Conditions are -20  $\leq$  TJ  $\leq$  125°C unless otherwise noted.  $V_{VDD} = 3.3 \text{ V}$ ,  $V_{VEE} = -48 \text{ V}$ ,  $V_{DGND} = V_{AGND}$ , and all outputs are unloaded, unless otherwise noted. Positive currents are into pins. Current sense resistor = 0.5  $\Omega$ . Typical values are at 25°C. All voltages are with respect to DGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                      | PARAMETER                               | TEST CONDITIONS                                    | MIN  | TYP | MAX | UNIT |

|----------------------|-----------------------------------------|----------------------------------------------------|------|-----|-----|------|

| Port Curre           | nt Sense                                |                                                    |      | ,   |     |      |

|                      |                                         | OUT = VEE, ICUT(2:0) = 000b                        | 175  | 187 | 200 |      |

|                      |                                         | OUT = VEE, ICUT(2:0) = 001b                        | 45   | 55  | 65  |      |

| V <sub>СИТ</sub>     |                                         | OUT = VEE, ICUT(2:0) = 010b                        | 90   | 102 | 115 |      |

|                      | 1 12-24                                 | OUT = VEE, ICUT(2:0) = 011b                        | 175  | 187 | 200 |      |

|                      | I <sub>CUT</sub> limit                  | OUT = VEE, ICUT(2:0) = 100b                        | 350  | 377 | 400 |      |

|                      |                                         | OUT = VEE, ICUT(2:0) = 101b                        | 276  | 296 | 316 |      |

|                      |                                         | OUT = VEE, ICUT(2:0) = 110b                        | 318  | 343 | 365 |      |

|                      |                                         | OUT = VEE, ICUT(2:0) = 111b                        | 385  | 408 | 430 | \/   |

|                      |                                         | OUT = - 47 V                                       | 200  |     | 225 | mV   |

| $V_{LIM}$            | I <sub>LIM</sub> limit                  | OUT = - 30 V                                       | 200  |     | 225 |      |

|                      |                                         | OUT = - 10 V                                       | 90   |     | 175 |      |

|                      |                                         | OUT = - 47 V                                       | 409  | 431 | 452 |      |

| $V_{LIM2X}$          | I <sub>LIM</sub> limit in 2X mode       | OUT = - 40 V                                       | 409  | 431 | 452 |      |

|                      |                                         | OUT = - 10 V                                       | 150  |     | 300 |      |

| V <sub>short</sub>   | I <sub>short</sub> threshold            | Threshold for GATE to be less than 1 V, 2 µs after | 275  | 290 | 335 |      |

| V <sub>short2X</sub> | I <sub>short</sub> threshold in 2X mode | application of pulse                               | 525  | 562 | 625 |      |

| I <sub>bias</sub>    | Sense pin bias current                  |                                                    | -100 |     | 100 | μΑ   |

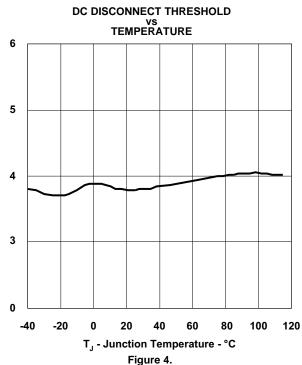

| I <sub>MIN</sub>     | DC disconnect threshold                 |                                                    | 2.5  |     | 5   | mV   |

Product Folder Links: TPS23851

Submit Documentation Feedback

Conditions are  $-20 \le TJ \le 125^{\circ}C$  unless otherwise noted.  $V_{VDD} = 3.3 \text{ V}$ ,  $V_{VEE} = -48 \text{ V}$ ,  $V_{DGND} = V_{AGND}$ , and all outputs are unloaded, unless otherwise noted. Positive currents are into pins. Current sense resistor = 0.5  $\Omega$ . Typical values are at 25°C. All voltages are with respect to DGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                       | PARAMETER                                     | TEST CONDITIONS                                                                          | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Timings               |                                               |                                                                                          |     |     |     |      |

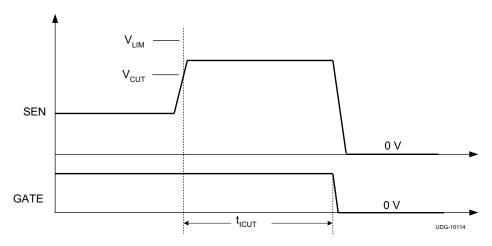

|                       |                                               | TICUT = 00                                                                               | 50  |     | 70  |      |

|                       |                                               | TICUT = 01                                                                               | 25  |     | 35  |      |

| t <sub>ICUT</sub>     | I <sub>CUT</sub> time limit                   | TICUT = 10                                                                               | 100 |     | 140 |      |

|                       |                                               | TICUT = 11                                                                               | 200 |     | 280 |      |

|                       |                                               | TSTART = 00                                                                              | 50  |     | 70  |      |

| i                     | Maximum current limit                         | TSTART = 01                                                                              | 25  |     | 35  |      |

| t <sub>START</sub>    | duration in port start-up                     | TSTART = 10                                                                              | 100 |     | 140 |      |

|                       |                                               | TSTART = 11                                                                              | 200 |     | 280 |      |

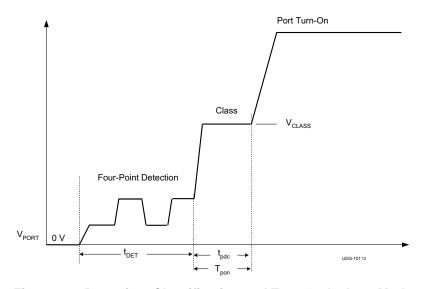

| t <sub>DET</sub>      | Detection duration with 4-<br>point discovery | Time to complete a detection                                                             | 275 |     | 425 | ms   |

|                       | Classification devention                      | Auto or semi-auto mode. From detection complete                                          |     |     | 50  |      |

| t <sub>pdc</sub>      | Classification duration                       | Manual mode. From class command                                                          |     |     | 50  |      |

|                       |                                               | Auto mode from end of detection to port turn on                                          |     |     | 200 |      |

| T <sub>pon</sub>      | Port power on delay                           | Manual mode from port turn on command to $I_{GATE}$ = $I_{GO+}$                          |     |     | 4   |      |

| t <sub>ed</sub>       | Error delay timing                            | Delay before next attempt to power a port following power removal due to error condition | 750 |     |     |      |

| T <sub>RESET</sub>    | Reset time duration from RESET pin            |                                                                                          | 3   |     | 6   | μs   |

| T <sub>RDG</sub>      | RESET input deglitch time                     |                                                                                          | 1   |     | 5   | •    |

|                       |                                               | TDIS = 00                                                                                | 300 |     | 400 |      |

|                       | PD Maintain Power signature                   | TDIS = 01                                                                                | 75  |     | 100 |      |

| t <sub>MPDO</sub>     | dropout time limit                            | TDIS = 10                                                                                | 150 |     | 200 | ms   |

|                       |                                               | TDIS = 11                                                                                | 600 |     | 800 |      |

| t <sub>SHDG</sub>     | SHDNn input deglitch time                     | SHDNx pin assertion threshold                                                            | 1   |     | 5   | μs   |

| t <sub>POR</sub>      | device power-on reset delay                   |                                                                                          |     |     | 20  | ms   |

| Digital Inte          | erface                                        |                                                                                          |     |     |     |      |

| V <sub>IH</sub>       | Digital input High                            |                                                                                          | 2.4 |     |     |      |

| V <sub>IL</sub>       | Digital input Low                             |                                                                                          |     |     | 0.8 | V    |

| \/                    | Digital output Low                            | at 3 mA                                                                                  |     |     | 0.4 | V    |

| V <sub>OL</sub>       | Digital output Low                            | SDAO at 5 mA                                                                             |     |     | 0.7 |      |

| R <sub>pullup</sub>   | Pullup resistor to VDD                        | RESET, A[3:0], /SHDN[4:1]                                                                | 30  | 50  | 80  | kΩ   |

| R <sub>pulldown</sub> | Pulldown resistor to DGND                     | esistor to DGND AUTO pin                                                                 |     | 50  | 80  | K12  |

Conditions are  $-20 \le TJ \le 125^{\circ}C$  unless otherwise noted.  $V_{VDD} = 3.3 \text{ V}$ ,  $V_{VEE} = -48 \text{ V}$ ,  $V_{DGND} = V_{AGND}$ , and all outputs are unloaded, unless otherwise noted. Positive currents are into pins. Current sense resistor = 0.5  $\Omega$ . Typical values are at 25°C. All voltages are with respect to DGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                                  | PARAMETER                                        | TEST CONDITIONS                                                       | MIN | TYP | MAX | UNIT |  |

|----------------------------------|--------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|--|

| I <sup>2</sup> C Interface       | e Timing Requirements at 0 ≤ T                   | 」≤ 100°C                                                              |     |     |     |      |  |

| 4                                | CCI aloak fraguenay                              |                                                                       |     |     | 400 | kHz  |  |

| f <sub>SCL</sub>                 | SCL clock frequency                              | -20 ≤ T <sub>J</sub> ≤ 100°C                                          |     |     | 100 | KHZ  |  |

| t <sub>LOW</sub>                 | LOW period of the clock                          |                                                                       | 1.3 |     |     |      |  |

| t <sub>HIGH</sub>                | HIGH period of the clock                         |                                                                       | 0.6 |     |     | μs   |  |

|                                  |                                                  | SDA, 2.3 V $-$ 1.0 V, $C_b$ = 10 pF, 10 k $\Omega$ pull-up to 3.3 V   | 21  |     | 250 |      |  |

| t <sub>fo</sub>                  | SDAO output fall time                            | SDA, 2.3 V $-$ 1.0 V, $C_b$ = 400 pF, 1.3 k $\Omega$ pull-up to 3.3 V | 60  |     | 250 |      |  |

| t <sub>SU,DAT</sub>              | Data set-up time                                 |                                                                       | 200 |     |     | ns   |  |

| t <sub>HD,DAT</sub>              | Data hold time                                   |                                                                       | 150 | 50  |     | 110  |  |

| t <sub>rfSDA</sub>               | Input rise/fall times of SDAI                    |                                                                       | 20  |     | 120 |      |  |

| t <sub>r</sub>                   | Input rise time of SCL                           |                                                                       | 20  |     | 300 |      |  |

| t <sub>f</sub>                   | Input fall time of SCL                           |                                                                       | 20  |     | 150 |      |  |

| t <sub>BUF</sub>                 | Bus free time between a STOP and START condition |                                                                       | 1.3 |     |     |      |  |

| t <sub>HD</sub> , <sub>STA</sub> | Hold time after (repeated) start condition       |                                                                       | 0.6 |     |     |      |  |

| t <sub>SU,STA</sub>              | Repeated start condition set-<br>up time         |                                                                       | 0.6 |     |     | μs   |  |

| t <sub>SU,STO</sub>              | Stop condition set-up time                       |                                                                       | 0.6 |     |     |      |  |

| t <sub>FLT_INT</sub>             | Fault to INT assertion                           | Time to internally register an Interrupt fault                        |     | 100 |     |      |  |

| t <sub>STOP_INT</sub>            | STOP to INT assertion                            |                                                                       |     | 140 |     |      |  |

| t <sub>ARA_INT</sub>             | ARA to INT de-assertion                          |                                                                       |     |     | 500 | ns   |  |

| Thermal Sh                       | utdown                                           |                                                                       | '   | 1   |     |      |  |

|                                  | Shutdown temperature                             | Temperature rising                                                    | 143 | 154 | 161 | 90   |  |

|                                  | Hysteresis                                       |                                                                       |     | 8   |     | °C   |  |

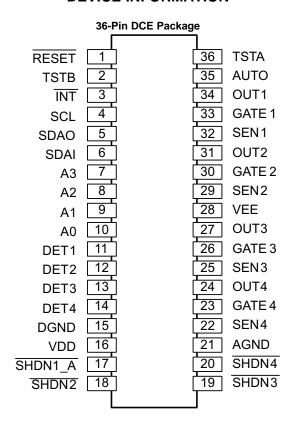

#### **DEVICE INFORMATION**

## **PIN FUNCTIONS**

|                |         |     | PIN FUNCTIONS                                                                                                                                                                 |

|----------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN            | NAME    | I/O | DESCRIPTION                                                                                                                                                                   |

| 1              | RESET   | I   | Reset input. When asserted low, the TPS23851 will reset. This pin is internally pulled up to VDD.                                                                             |

| 2              | TSTB    |     | Used for internal test modes only. Negative high voltage may appear if test mode is enabled. Leave this pin open.                                                             |

| 36             | TSTA    |     | Used for internal test modes only. Negative high voltage may appear if test mode is enabled. Leave this pin open                                                              |

| 3              | ĪNT     | 0   | Interrupt output. This pin asserts low when a bit in the interrupt register is asserted. This pin is updated between I <sup>2</sup> C transactions. This output is opendrain. |

| 4              | SCL     | 1   | Serial clock input for I <sup>2</sup> C bus.                                                                                                                                  |

| 5              | SDAO    | 0   | Serial data output for I <sup>2</sup> C bus. This pin can be connected to SDAI for non-isolated systems. This output is open-drain.                                           |

| 6              | SDAI    | I   | Serial data input for I <sup>2</sup> C bus. This pin can be connected to SDAO for non-isolated systems.                                                                       |

| 7              | А3      | I   |                                                                                                                                                                               |

| 8              | A2      | 1   | I <sup>2</sup> C A3-A0 Address lines. These pins are internally pulled up to VDD. Do not tie                                                                                  |

| 9              | 9 A1    |     | directly to a positive voltage source. (1)(2)                                                                                                                                 |

| 10             | A0      | 1   |                                                                                                                                                                               |

| 11, 12, 13, 14 | DET1-4  | 1   | Port 1-4 detect sense.                                                                                                                                                        |

| 15             | DGND    |     | Digital ground.                                                                                                                                                               |

| 16             | VDD     |     | Digital supply. Bypass VDD to DGND using 0.1 $\mu$ F and 1 $\mu$ F capacitors in parallel. Connect VDD to the 3.3V digital supply using a 10 $\Omega$ resistor.               |

| 17             | SHDN1_A | ı   | Port 1 manual shutdown input or Port 1-4 multiplexed shutdown. This pin is internally pulled up to VDD.                                                                       |

| 18,19,20       | SHDN2-4 | 1   | Port 2-4 manual shutdown logic input. These pins are internally pulled up to VDD.                                                                                             |

| 21             | AGND    |     | Analog ground.                                                                                                                                                                |

| 32, 29, 25     | SEN1-3  | 1   | Port 1-3 current sense input. Connect to current sense resistor.                                                                                                              |

| 22             | SEN4    | 1_  | Port 4 current sense input. Connect to current sense resistor.                                                                                                                |

| 33, 30, 26, 23 | GAT1-4  | 0   | Port 1-4 gate drive output.                                                                                                                                                   |

| 34, 31, 27, 24 | OUT1-4  | 1   | Port 1-4 output voltage monitor. Connect to output port through a 10-kΩ resistor.                                                                                             |

| 28             | VEE     |     | Analog supply. Bypass VEE to AGND using 0.1 μF and 1 μF capacitors in parallel.                                                                                               |

| 35             | AUTO    | ı   | Mode select input. Asserting high on power-up puts the TPS23851 into auto mode. This pin is internally pulled down to DGND.                                                   |

<sup>(1)</sup> Can be directly tied to DGND but a resistor (at least 2 k $\Omega$ ) must be used if pulled up. (2) A6, A5, A4 are factory set to 010.

## **Detailed Pin Description**

The following descriptions refer to the pinout and the functional block diagram.

**RESET:** Reset input, active low. When asserted, the TPS23851 will reset, turning off all ports and forcing the registers to their power-up state. This pin is internally pulled up to VDD, with internal 1-µs to 5-µs deglitch filter. External RC network can be used to delay the turn on. There is also an internal power-on reset which is independent of the RESET input.

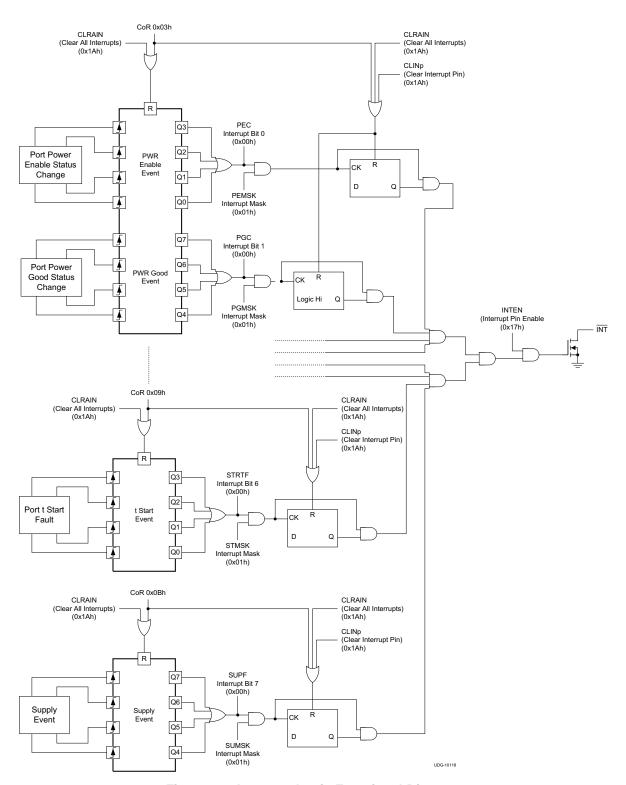

**INT**: Interrupt output. This pin asserts low when a bit in the interrupt register is asserted. This pin is updated between I<sup>2</sup>C transactions. This output is open-drain. Interrupt functional diagram is shown in Figure 31.

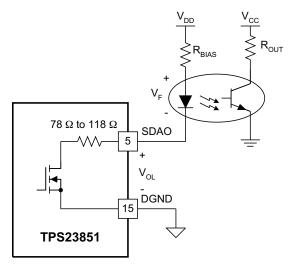

**SDAO:** Open-drain I<sup>2</sup>C bus output data line requiring an external resistive pullup. The TPS23851 uses separate SDAO and SDAI lines to allow optoisolated I<sup>2</sup>C interface. SDAO can be connected to SDAI for non-isolated systems.

**SCL:** Serial clock input for I<sup>2</sup>C bus.

**SDAI:** Serial data input for I<sup>2</sup>C bus. This pin can be connected to SDAO for non-isolated systems. Note that the data sent by the TPS23851 on SDAO must be mirrored on its SDAI line for correct operation. See Figure 35.

**A3-A0:**  $I^2C$  bus address inputs. Can be directly tied to DGND but a resistor (at least 2  $k\Omega$ ) must be used if pulled up. These pins are internally pulled up to VDD. See the Pin Status Register for more details.

**SHDN1\_A:** Port 1 Manual Shutdown Input or Port 1-4 Multiplexed Shutdown, active low. This pin is internally pulled up to VDD, with internal 1-µs to 5-µs deglitch filter.

When Multiplexed Shutdown is disabled, pulling low SHDN1\_A turns off port 1, regardless of the state of registers except the Multiplexed Shutdown Configuration Register.

When Multiplexed Shutdown is Enabled, pulling low SHDN1\_A turns off the ports selected in the Multiplexed Shutdown Configuration Register. This turn off action is triggered regardless of the state of registers except the Multiplexed Shutdown Configuration Register.

SHDN2-4: Port 2-4 Manual Shutdown Logic Input, active low. These pins are internally <u>pulled</u> up to VDD, with internal 1-µs to 5-µs deglitch filter. When Multiplexed Shutdown is disabled, pulling low SHDNn turns off port n, regardless of the state of registers except the Multiplexed Shutdown Configuration Register.

#### NOTE

If the Multiplexed Shutdown function is Enabled, the  $\overline{SHDN2}$  to  $\overline{SHDN4}$  inputs must be at logic High.

**DET1-DET4:** Port 1-4 detect sense.

Used during AC disconnect detection and powered device discovery. Connect to output port through a 1 k $\Omega$  in series with a 0.47  $\mu$ F, both in parallel with a diode. AC disconnect consists in sensing the load impedance by injecting an AC voltage at DETn pin and measuring the resultant current through the same pin. If the impedance is higher than a defined threshold, the port will automatically be turned off. The DET pin sine wave output voltage typically has a 2.5-V offset above the VEE supply, with a 2 V peak-to-peak amplitude under a no load condition.

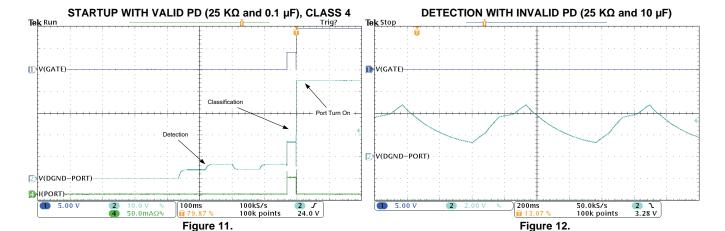

The TPS23851 uses an innovative 4-point technique in order to provide a reliable PD detection. The discovery is performed by sinking two different current levels via the DETn pin, while the PD voltage is measured from DGND to DET. The 4-point measurement provides the capability to avoid powering a capacitive or legacy load.

The resistor and capacitor are not needed if AC disconnect is not used. If the port is not used, the DETn pin can be floated or tied to VEE.

**GAT1-GAT4:** Port 1-4 gate drive output used for external N channel MOSFET gate control. At port turn on, it is driven positive by a low current charge pump to turn the MOSFET on. Note that the MOSFET turn on is done with di/dt control, which means that an internal amplifier forces the load current to track an internally defined voltage ramp. GATn is pulled low whenever any of the input supplies are low or if an over-current timeout has occurred. GATn will also be pulled low if its port is turned off by use of manual shutdown inputs. Leave floating if unused.

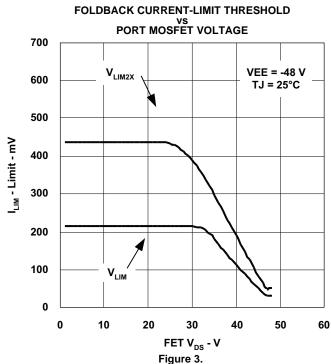

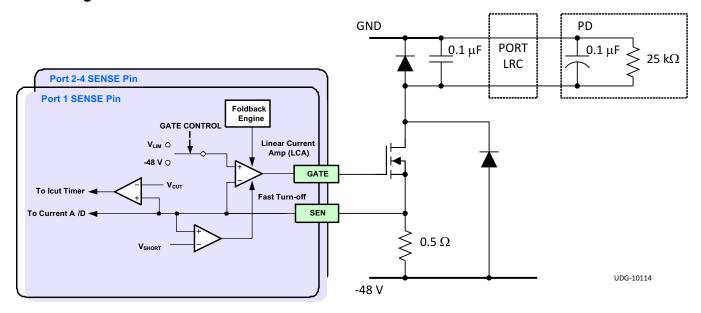

For a robust design, a current foldback function limits the power dissipation of the MOSFET during low resistance load or a short circuit event. The foldback mechanism measures the port voltage across AGND and OUTn to reduce the current limit threshold from 100% at 18 V (28 V if in 2X mode) down to around 14% at a port voltage of 0 V.

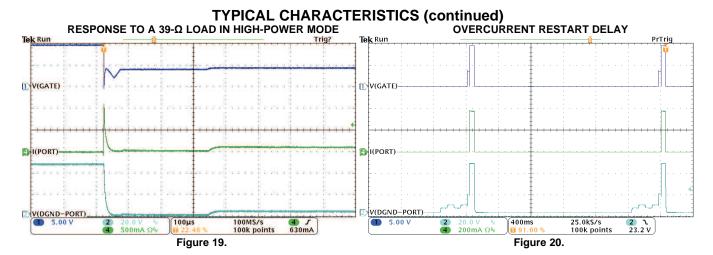

When  $I_{CUT}$  threshold is exceeded while a port is on, a timer starts. During that time, linear current limiting makes sure the current will not exceed  $I_{LIM}$  combined with current foldback action. When the timer reaches its  $t_{ICUT}$  (or  $t_{START}$  if at port turn on) limit, the port shuts off. When the port current goes below  $I_{CUT}$ , while there is no foldback action, the counter counts down at a rate  $1/16^{th}$  of the increment rate and it must reach a count of zero before the port can be turned on again.

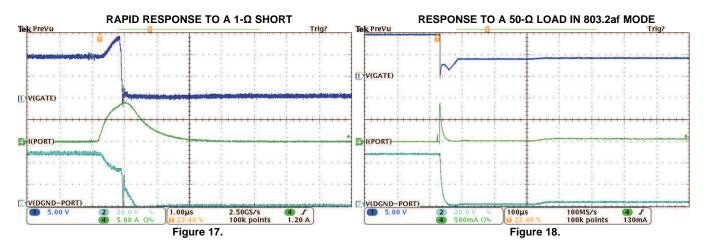

The fast overload protection is for major faults like a direct short. This turns off the MOSFET in less than a microsecond, for a period of 100  $\mu$ s, after which the gate is slowly turned back on with controlled di/dt. If the port is not used, tie SENn to VEE.

**OUT1-OUT4:** Port 1-4 output voltage monitor. Used to measure the port output voltage, for port voltage monitoring, port power good detection and foldback action. Should be connected to output port through a  $10-k\Omega$  resistor. There is an internal resistor between each OUTn pin and AGND. If the port n is not used, OUTn can be left floating or tied to AGND.

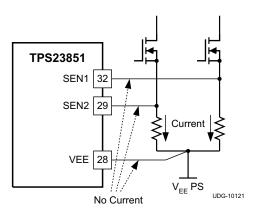

**SEN1-4:** Port 1-4 current sense input, relative to VEE. Monitors the external MOSFET current by use of a  $0.5-\Omega$  current sense resistor connected to VEE. Used by current foldback engine and also during classification. Can be used to perform load current monitoring via A/D conversion.

A classification is done while using the external MOSFET so that doing a classification on more than one port at same time is possible without overdissipation in the TPS23851.

For the DC disconnect function, there is an internal 2-µs analog filter on the SEN1-4 pins to provide glitch filtering.

SENn is a single ended measurement for all four ports and any voltage drop on the VEE path between the sense resistor and the VEE pin of TPS23851 can introduce errors, particularly during classification. Consequently, the PCB layout must be done in order to mitigate any such error, for example by using a copper plane, a star return point at the VEE pin for all four current sense resistors, or both. Connect to VEE if the port is unused.

#### NOTE

In order to meet clearance safety regulations, a fuse or an equivalent component should be inserted in series between the SEN4 pin and its corresponding current sense resistor.

**AUTO:** Auto mode input. A logic high state at POR means the TPS23851 will operate autonomously in auto mode even in the absence of a host controller. The state of that pin is measured only immediately following a Power-on-Reset or after the RESET input has been activated.

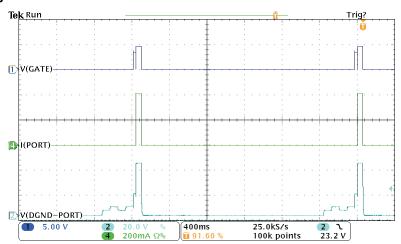

## **TYPICAL CHARACTERISTICS**

Submit Documentation Feedback

MIN - DC Disconnect - mV

Figure 21. OVERCURRENT RESTART DELAY WITH CURRENT LIMIT

Figure 22.

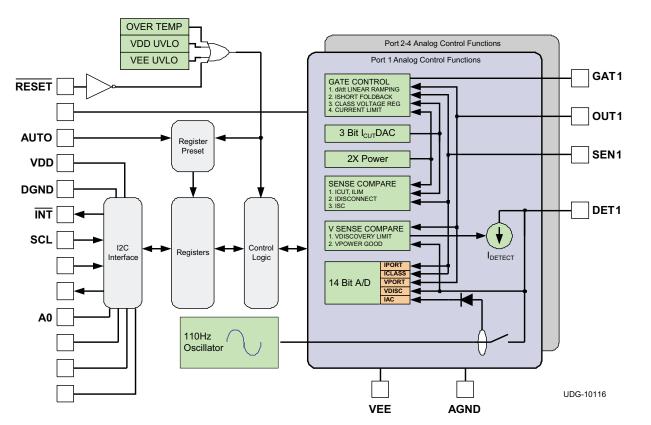

## **Block Diagrams**

Figure 23. Port Current Sense Circuitry

Figure 24. Block Diagram

Submit Documentation Feedback

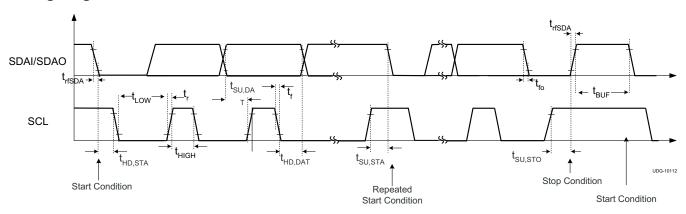

## **Timing Diagrams**

Figure 25. I<sup>2</sup>C Timings

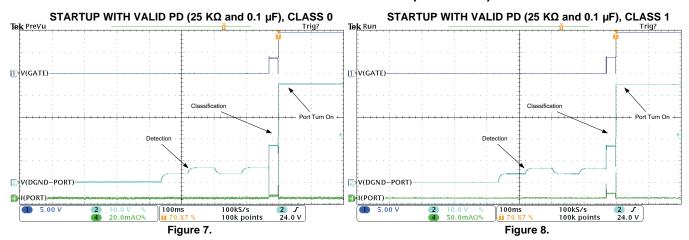

Figure 26. Detection, Classification and Turn On In Auto Mode

Figure 27. Overcurrent Fault Timing

#### **DETAILED DESCRIPTION**

#### A/D Converters

The TPS23851 features one 14-bit multi-slope integrating converter per port, for a total of four converters. Each converter is operated independently to perform measurements in any of the following modes: discovery, classification, port powered (current, voltage and AC disconnect).

The A/D converter type used in the TPS23851 differs from other similar types of converters in that it converts while the input signal is being sampled by the integrator, resulting in reduced conversion time and providing inherent filtering over the conversion period. The typical conversion time of this converter is 20 ms with 17.5-ms sampling window, providing significant rejection of noise at 50-Hz to 60-Hz line frequency.

#### NOTE

- 1. During AC disconnect measurement, the converter integration is synchronized with the sinewave generator for rejection of the excitation signal.

- Note that during port powered mode, voltage conversions are interleaved with port current conversions. If AC disconnect is Enabled, DC current, DC voltage and AC current measurements are interleaved.

When a port is on, its voltage and current results are stored in the Port n Voltage and Port n Current Registers.

The content of the Port #n Current and Voltage Registers is not updated when the port is off.

Any port reading should be qualified with the PGn bit of the Power Status Register (10h). If the port bit is a 1, then the reading should be accepted. If zero, the A/D reading should be considered corrupt as it may represent a port that experienced a power fault event or was disabled midway through a conversion.

Also, in port powered mode, the t<sub>START</sub> timer must expire before any current or voltage A/D conversion can begin. Each 14-bit result can be read via a 2-byte read cycle, as shown in Figure 5.

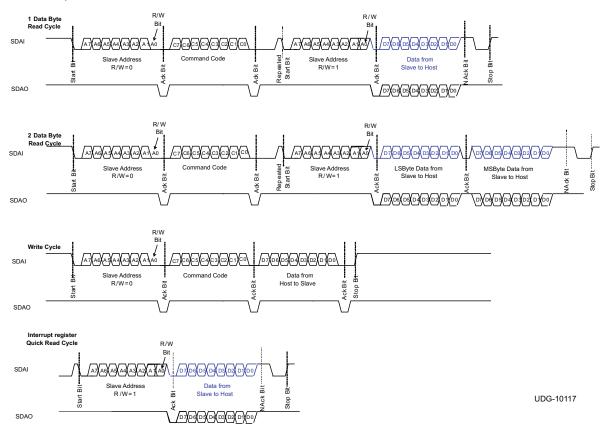

#### I<sup>2</sup>C Serial Interface

The TPS23851 features a 3-wire I<sup>2</sup>C interface, using SDAI, SDAO and SCL. Each transmission includes a Start condition sent by the master, followed by the device address (7-bit) with R/W bit, a register address byte, then one or two data bytes, and a Stop condition. There is also an acknowledge bit sent by the recipient following each byte transmitted. Also, SDAI/SDAO is stable while SCL is high except during a Start or Stop condition. Figure 28 illustrates read and write operations through I<sup>2</sup>C interface. The 2 data bytes read operation is applicable to A/D conversion results. Note that the data sent by the TPS23851 on SDAO must be mirrored on its SDAI line for correct operation, as shown.

The TPS23851 features a quick access to the Interrupt Register through I<sup>2</sup>C bus. See Figure 28.

#### NOTE

This means that when a Stop Bit is received, the register pointer is automatically reset. This means that there must not be any Stop Bit before a Repeated Start Bit, as shown.

It is also possible to perform a write operation to many TPS23851 devices at same time. The slave address during this broadcast access is 0x30, as shown in the Pin Status Register description.

The TPS23851, using the INT line, supports the SMBALERT protocol.

When  $\overline{\text{INT}}$  is asserted low, if the bus master controller sends the Alert response address, the TPS23851 responds providing its device address on the SDA line and releases the  $\overline{\text{INT}}$  line. If there is a collision between two TPS23851 devices responding simultaneously, then the device with the lower address wins arbitration and responds first, by use of SDAI and SDAO lines.

Figure 28. I<sup>2</sup>C/SMBus Interface Read And Write Protocol

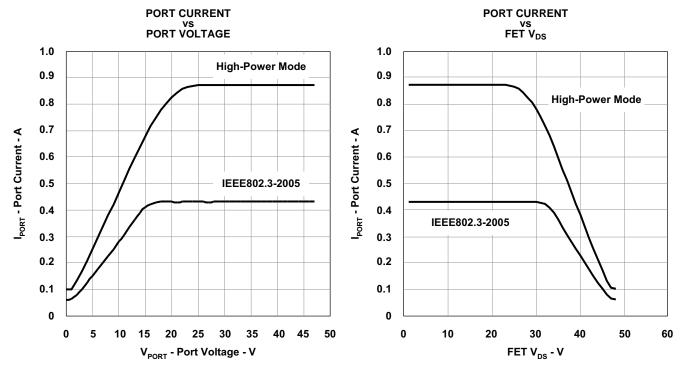

## Foldback and High Power Mode

For a robust design, a current foldback function limits the power dissipation of the MOSFET during low resistance load or a short circuit event. Using the TPS23851, it is possible to select one of two foldback profiles. The first one is for 802.3af applications, while the second one (2X mode) is for higher power applications as defined in the 802.3at standard. See Figure 29 and Figure 30.

The HPWn bit of the High Power and Sine Disable Register needs to be set to select the High Power Mode.

The linear foldback mechanism measures the port voltage across AGND and OUTn to reduce the current limit threshold from 100% at 18 V (28 V if in 2X mode) down to around 14% at a port voltage of 0 V.

Figure 29. Output Current Foldback Function (In IEEE Std 802.3at-2009 Mode and High-Power Mode)

Figure 30. Output Current Foldback Function (With VEE = -48 V, in IEEE Std 802.3at-2009 Mode and High-Power Mode)

#### Inrush Control, ICUT Fault Control

During a port turn on, the port MOSFET is turned on with di/dt control, which means that an internal current limiting amplifier forces the load current to track an internally defined voltage ramp. The  $t_{START}$  fault timer is also started at port turn on. If at the end of  $t_{START}$  time period the port is still in current limit, the port shuts off and its STRTn fault bit is set (Start Event Register).

#### NOTE

During inrush period, the regular (1x) current foldback is used, regardless of the state of the HPWn bit in High Power and Sine Disable Register.

Once the  $t_{START}$  fault timer has expired without a fault, the  $t_{ICUT}$  timer becomes effective. It starts when  $I_{CUT}$  threshold is exceeded while a port is on. During that time, linear current limiting makes sure the current will not exceed  $I_{LIM}$  combined with current foldback action. When the timer reaches its  $t_{ICUT}$  limit, the port shuts off and its ICUTn bit is set (Fault Event Register). When the port current goes below  $I_{CUT}$ , while there is no foldback action, the counter counts down at a rate  $1/16^{th}$  of the increment rate and it must reach a count of zero before the port can be turned on again.

Figure 31. Interrupt Logic Functional Diagram

#### **APPLICATION INFORMATION**

#### Introduction to POE

Power-Over-Ethernet (POE) is a means of distributing power to Ethernet devices over the Ethernet cable using either data or spare pairs. POE eliminates the need for power supplies at the Ethernet device. Common applications of POE are security cameras, IP Phones and PDA chargers. The host or mid-span equipment that supplies power is the Power Source Equipment (PSE). The load at the Ethernet connector is the Powered device (PD). POE protocol between PSE and PD controlling power to the load is specified by IEEE Std 802.3at-2009.

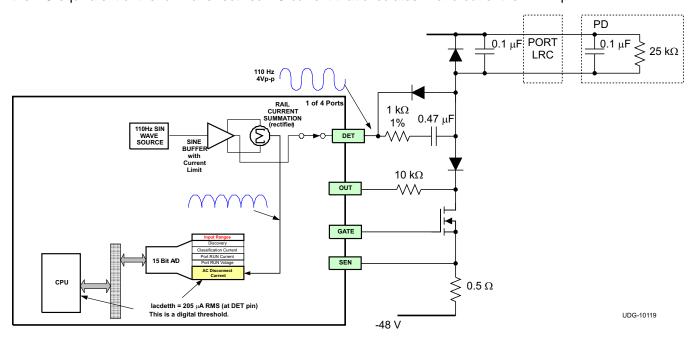

Transformers are used at Ethernet host ports, mid-spans and hubs, to interface data to the cable. A DC voltage can be applied to the center tap of the transformer with no effect on the data signals. As in any power transmission line, a relatively high 48 V is used to keep current low, minimize the effect of IR drops in the line and preserve power to the load. Standard POE delivers approximately 13 W to the PD. Figure 35 shows the overview schematic of a POE port.

## **POE States Introduction**

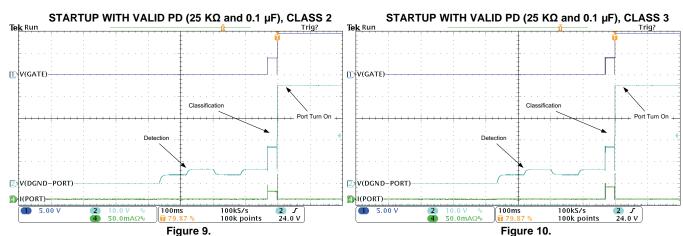

The PSE and PD operate under a three state protocol to complete the power connection. At initialization or when the port is disconnected, the PSE controller enters the detection state. In detection, the PD places a 25-k $\Omega$  signature resistor across the wire pair. The TPS23851 controller outputs a small current and checks the voltage to determine a valid PD signature. When a valid PD is found, the PSE controller enters the classification state to find out how much current the device requires. The PSE outputs a fixed 17.5 V and reads the current taken by the PD at this level. The current is converted to a device class. The PSE then enters the power on state. The PSE powers the port and continuously monitors the current supplied to the PD. See Figure 26.

The port remains on as long as the port load is less than  $I_{CUT}$ , which is the maximum current allowed. Once a port load is above  $I_{CUT}$  or is disconnected or faulted, the port is powered down.

#### **Detection**

To eliminate the possibility of false detection, the TPS23851 uses a TI proprietary 4-point detection method to determine the signature resistance of the PD device. False detection of a  $25-k\Omega$  signature can occur with 2-point detection type PSE's in noisy environments or if the load is highly capacitive.

Both detection 1 and detection 2 are merged into a single detection function which is repeated. Detection 1 applies I1 (165  $\mu$ A) to a port, waits 80 ms and then measures the port voltage V1 with the integrating ADC. Detection 2 applies I2 (275  $\mu$ A) to a port, waits 80 ms and measures the port voltage V2. The process is repeated a second time. Multiple comparisons and calculations are performed on all four measurement point combinations to eliminate the effects of a non-linear or hysteretic PD signature. The resulting port signature is then sorted into the appropriate category.

#### Classification

802.3af (or 802.3at Type 1) classification (class) is performed by supplying a voltage and sampling the resulting current. To eliminate the high power of a classification event from occurring in the power controller chip, the TPS23851 makes use of the external power FET for classification.

During classification, the voltage on the gate node of the external MOSFET is part of a linear control loop. The control loop applies the appropriate MOSFET drive to maintain a differential voltage between GND and OUT of 17.5 V. During classification the voltage across the sense resistor in the source of the MOSFET is measured and converted to a Class level within the TPS23851. If a load short occurs during classification the MOSFET gate voltage is quickly reduced to a linearly controlled, short circuit value for the duration of the class event.

Classification results may be read through the I<sup>2</sup>C Detection Event and Port n Status Registers.

Product Folder Links: TPS23851

Copyright © 2010-2013, Texas Instruments Incorporated

#### **Power On**

Once the port has met the requirements of a valid POE load, the port is powered on.

## **Port Operating Modes**

Each port may operate in one of four modes:

- 1. Auto: The port operates autonomously. It performs detection continuously until a valid PD is detected. Once a PD is found, classification is performed and the port is powered up as specified within its registers. Classification has no effect on the power-on step. When the AUTO pin is pulled high on power-up, the TPS23851 operates the four ports in auto mode. If the AUTO pin is pulled low, the operation is controlled by the system software through the I<sup>2</sup>C interface. The power on setting of the AUTO pin can be changed at any time by the I<sup>2</sup>C Operating Mode Registers. If the AUTO Mode is to be selected through I<sup>2</sup>C while the AUTO pin voltage is low, additional registers also need to be changed accordingly. This includes the Interrupt Mask Register, Disconnect Enable Register, Detect/Class Enable Register.

- 2. **SemiAuto:** The port performs detection and classification (if valid detection occurs) continuously. Registers are updated each time a detection or classification occurs. The port power is not automatically turned on.

- 3. **Manual:** The port performs the functions indicated by its registers one time when Commanded. There is no automatic state change.

- 4. **Power Off:** The port is powered off and will not autonomously perform a detection, classification or poweron. In this mode, Status and Enable Bits for the associated port are reset.

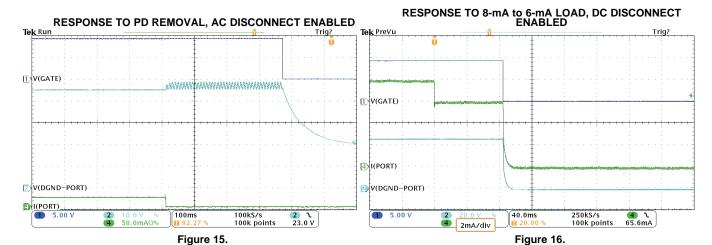

#### **Disconnect**

Disconnect is the automated process of turning off power to the port. When the port is unloaded or at least falls below minimum load it is necessary to turn off power to the port and restart detection. Two methods of determining the port is below minimum load are AC disconnect and DC disconnect.

#### **DC** Disconnect

In DC disconnect, the voltage across the sense resistors is measured. When enabled, the DC disconnect function monitors the sense resistor voltage of a powered port to verify the port is drawing at least the minimum current to remain active. The  $T_{DIS}$  timer will count up whenever the port current is below a 7.5-mA threshold. If a timeout occurs, the port will be shut down and the corresponding disconnect bit in the Fault Event Register will be set. The  $T_{DIS}$  counter is reset each time the current goes continuously higher than the disconnect threshold for 17% of  $T_{MPDO}$ .

The timer will start counting from the beginning if an undercurrent condition occurs again. An internal 2- $\mu$ s analog filter on the SENSE pin provides glitch filtering. The  $T_{DIS}$  duration is set by the  $T_{DIS}$  Bits of the Timing Configuration Register (0x16).

#### **AC Disconnect**

The TPS23851 can detect a PD disconnect using AC or DC measurement.

AC disconnect consists in sensing the load impedance by injecting an AC voltage (110-Hz sinewave) at DETn pin and measuring the resultant current through the same pin. If the impedance is higher than a defined threshold, a timer  $(T_{DIS})$  is started and if a time-out occurs the port is turned off.

Also, the corresponding disconnect bit (DISFn) in the Fault Event Register is set accordingly. The T<sub>DIS</sub> counter is reset each time the impedance goes lower than the disconnect threshold.

Referring to Figure 32, each DETn pin is connected to its output port through a 1 k $\Omega$  in series with a 0.47  $\mu$ F, both in parallel with a low leakage diode. The AC disconnect technique requires a diode to be inserted in series with the power MOSFET as shown in Figure 32. This diode must be a S1B or equivalent. Also, the capacitance across the port on PSE is critical for accurate detection and must be close to 0.1  $\mu$ F. Also consider that ceramic capacitors are strongly dependent on DC bias voltage, capacitance going down substantially at higher voltage. For these reasons, using X7R type with 100-V rating or equivalent is required.

The A/D converter is used to perform AC disconnect detection. A port's AC disconnect current is measured as the DC equivalent of the full-wave rectified AC current that circulates in and out of the DETn pin.

Figure 32. AC Disconnect Block Diagram

Submit Documentation Feedback

## I<sup>2</sup>C Timing While Using Isolators

The data communications used by TPS23851 is I<sup>2</sup>C fast mode to a maximum of 400 kHz. Repeated start is supported; there may not be a Stop bit before a repeated Start. Clock stretching is not supported. The TPS23851 is always a slave device. One of sixteen devices may be selected by a hex digit. Starting address is 20h.

Because of the high voltage for POE and the low-voltage computer communication systems, it is good practice to use isolation on I<sup>2</sup>C signals. Texas Instruments ISO724X galvanic isolation is recommended because of their 20-ns propagation delay and 2-ns rise and fall times.

Optical isolation may be used but careful device selection is needed to maintain proper transmission timing. The master provides SCLK for the slave devices. The TPS23851 respond with SDAO which is aligned to an SCLK delayed from the master by the isolators. The master receives SDAO after an isolation propagation delay time relative to the TPS23851 SDAO. With slower isolation devices it becomes difficult to maintain I<sup>2</sup>C setup and hold times over DATA, ACK, START and STOP conditions. An opto-isolator with less than 200-ns total propagation delay is required.

Other factors can have an effect on the propagation delay. For opto-isolation, set the input bias current to meet the desired propagation delay for the maximum forward current of the diode using the minimum input voltage. Then check the maximum power of the diode is not violated for minimum  $V_F$  and maximum supply voltage conditions.

The output side of the opto-isolator has a secondary delay because the signal rise/fall time is effected by the output pull-up resistor. The range of values for the output resistor used with an opto-isolator may be listed in its datasheet. Many factors including test result are needed to determine the best choice. The lower values are bounded by the maximum power dissipation of the device and managing the  $V_{OL}$ . As the output resistor value increases, the rise and fall time of the signal increase. The total propagation delay of the device is also increased. In this example the resistor range is 350  $\Omega$  to 4000  $\Omega$ . Signal rise and fall time with a 1-k $\Omega$  resistor is about 60 ns and is nearly 300 ns for 4 k $\Omega$ . Similarly, the propagation delay with a 1-k $\Omega$  resistor is about 50 ns and is about 85 ns for 1 k $\Omega$ . Based on other system conditions such as nominal voltage and temperature, a 2-k $\Omega$  output resistor is selected for test.

TPS23851 uses separate SDAI and SDAO lines to allow isolated  $I^2C$  interface. SDAI can be connected to SDAO for non-isolated systems. Isolated or not, the SDAO must be mirrored on its SDAI for correct  $I^2C$  operation. SDAO and SDAI are usually ORed on the  $I^2C$  host side to become SDA, the single wire  $I^2C$  host data signal. The  $I^2C$  data integrity is best when the SDAI signal to TPS23851 has edges faster than 120 ns. The SDAO signal is an open drain output. It is rated for 5-mA output to meet a 0.7-V maximum  $V_{OL}$  The SDAO signal can sink higher current at increased  $V_{OL}$ .  $V_{OL}$  is not critical for receivers that do not have threshold inputs, the usual case for opto-isolators

Figure 33 shows the open drain output at SDAO with equivalent series impedance 78  $\Omega$  to 118  $\Omega$ .

Figure 33. I<sup>2</sup>C Optocoupler Interface

## **Biasing Opto-Isolators**

A worst case design for opto-isolators ensures operation over input voltage and temperature range. The following design example can be applied to any opto or system specifications. This example uses HCPL0631.

The bias on the isolator should meet minimum current specifications when the input voltage is minimum (3.0 V) and the temperature is high (85°C). The bias is then checked when the the applied voltage is high (3.5 V) and the temperature is minimum (-20°C). The result is that the maximum forward current is within isolator specifications. Different vendors HCPL-0631 datasheets show minimum  $I_F$  from 5 mA to 6.7 mA. Allowing for specifiations and aging of the isolator, choose 6.3-mA minimum current. Next, use the isolator datasheet graphs to determine  $V_F$  at -20°C as 1.46 V and  $V_F$  at 85°C as 1.67 V.

#### NOTE

The Vf goes down at high temperature, while the Rdson of SDAO FET goes up, so that a worst case 1.67V at high temperature is a good assumption.

Minimum bias, low input voltage.

$$V_{SDAO} = 6.3 \text{ mA} \times 118 \Omega = 0.74 \text{ V}$$

(1)

$$V_R = V_{DD} - V_{SDAO} - V_F = 3.0 - 0.74 - 1.67 = 0.59 V$$

(2)

$$\frac{V_R}{V_F} = \frac{0.59 \,\text{V}}{0.0063} = 93.6 \,\Omega, \text{ use } 95.3 \,\Omega$$

(3)

After setting low voltage bias, check for safe high voltage bias.

$$V = V_{DD} - V_{F} = 3.5 V - 1.47 V = 2.03 V$$

(4)

$$I_{F} = \frac{V}{(R_{BIAS} + R_{SDAO})} = \frac{2.03}{(95.3 + 78)} = 11.7 \text{ mA}$$

(5)

Isolator data sheet specs 15 mA max.

## I<sup>2</sup>C Watchdog

An I<sup>2</sup>C Watchdog time is available on the Texas Instruments TPS23851 device. When enabled, the timer will monitor the I<sup>2</sup>C, SCL line for clock edges. A timeout of the watchdog will reset the I<sup>2</sup>C interface along with any active ports. This feature provides protection in the event of rogue system software or I<sup>2</sup>C bus hang-up by slave devices. In the latter case, if a slave is attempting to send a data bit of "0" when the master stops sending clocks, then the slave could get stuck driving the data line low indefinitely. Since the data line is being driven low, the master cannot send a STOP to clean up the bus. Activating the I<sup>2</sup>C watchdog feature of the TPS23851 would clear this deadlocked condition. If the timer of 2 seconds expires, the ports will latch off and WD Status bit will be set. WD Status can only be cleared by a reset or writing a 0 to the WDS status bit location. The 4-bit watchdog disable field will shutdown this feature when a code of 1011b is loaded. This field is preset to 1011b whenever the TPS23851 is initially powered. The Watchdog Timer is divided from the main 7.4-MHz clock. Also see the I<sup>2</sup>C Watchdog Register for more details on the subject.

#### **Port Output Construction and Component Selection**

Port output components can be seen in the applications schematic lower left, Figure 35. The output port has a TVS (D1) for protection against voltage transients. The TVS shown was selected for 68-V breakdown, unidirectional, 600 W with less than 5- $\mu$ A leakage. A 0.1  $\mu$ F, X7R capacitor (C9) rated at 100 V provides minimal filtering and stability to the output.

The series RC (R7, C10) with parallel diode (D2) and Diode D3 are needed for AC disconnect only. These components are described in the AC disconnect section. If DC disconnect is used, they are omitted. MOSFET, Q2 is the port power switch controlled by the TPS23851. The MOSFET is used to power to the port connected device and also during classification.

TPS23851 reads the voltage at sense resistors (R13 and R14) to determine the port current. Port current is measured as the voltage drop across the external  $0.5-\Omega$  sense resistor. Two  $1-\Omega$  resistors wired in parallel are recommended. Two resistors improve the overall resistor tolerance and spread out the heat dissipation minimizing the effects of self heating.

## Layout

Sense readback should be wired in a Kelvin connection to the sense resistors. It is important to read voltage directly across the sense resistor to get a true measure of the current to the port load. Do not use other sense or GND points that may be electrical equivalents to these signals in the design layout tool. Read errors will occur because of stray current from other sources. Similarly, care must be taken to keep the flow of port current direct from the power source, through the pass FET to the sense resistors and to the return. This will minimize crosstalk between port loads and provide accurate current sense.

Accurate current readings are essential because they are used for sensitive measurements such as DC disconnect, classification, port loading and output faults.

#### NOTE

For more details on TPS23851 layout recommendations, see TI document SLUU451.

Figure 34. Current Sensing Resistor Layout

## **MOSFET Selection**

MOSFET selection is based on a number of key parameters listed in the MOSFET datasheet. An N-channel MOSFET is used. The IRFM120A or equivalent is recommended.

- **V**<sub>DS</sub>: The system voltage is 48 V and could operate as high as 53V. There must be some allowance for transients in inductive cables. Use 100-V parts as a good safety factor for 48-V systems.

- $R_{DS(on)}$ : The on resistance of the MOSFET determines the power to be dissipated at a given load. The commonly used parts have about a 0.2- $\Omega$  on resistance

- ID: The current capability of the device, while important, is not sufficient for device selection. The maximum safe operating area curve gives the drain current (ID) vs drain-to-source voltage (VDS) curve. This is usually a family of curves for an on time duration. This data is given for 25°C. It must therefore be de-rated by the thermal response for pulse duration.

Figure 35. TPS23851 Application Schematic With AC Disconnect Detection

Submit Documentation Feedback

# Table 1. Summary of Main Registers (1)

| CMD<br>CODE | REGISTER OR COMMAND NAME | R/W | DATA<br>BYTE | RST State       |            |              | E          | BITS DE          | SCRIPTIO  | ON            |             |           |

|-------------|--------------------------|-----|--------------|-----------------|------------|--------------|------------|------------------|-----------|---------------|-------------|-----------|

| 00h         | Interrupt                | RO  | 1            | 1000,0000b      | SUPF       | STRTF        | ICUTF      | CLAS<br>C        | DETC      | DISF          | PGC         | PEC       |

| 01h         | Interrupt mask           | R/W | 1            | 1AA0,0A00b      | SUMSK      | STMSK        | ICMS<br>K  | CLMS<br>K        | DEMSK     | DIMSK         | PGMS<br>K   | PEMSK     |

| 02h         | Power status             | RO  | 1            | 0000,0000b      | Powe       | er Good st   | tatus cha  | inge             | Pow       | er Enable     | status cha  | ange      |

| 03h         | Power status             | CoR | 1            | 0000,0000       | PGC4       | PGC3         | PGC2       | PGC1             | PEC4      | PEC3          | PEC2        | PEC1      |

| 04h         |                          | RO  | 1            |                 | Cla        | assificatio  | n occure   | d                |           | Detection     | occurred    |           |

| 05h         | Detection status         | CoR | 1            | 0000,0000b      | CLSC4      | CLSC3        | CLSC<br>2  | CLSC<br>1        | DETC4     | DETC3         | DETC2       | DETC1     |

| 06h         | Foult status             | RO  | 1            | 0000 00006      | Di         | isconnect    | occurred   | t                |           | ICUT faul     | t occurred  |           |

| 07h         | Fault status             | CoR | 1            | 0000,0000b      | DISF4      | DISF3        | DISF2      | DISF1            | ICUT4     | ICUT3         | ICUT2       | ICUT1     |

| 08h         | Ctowt status             | RO  | 1            | 0000 0000       |            |              |            |                  | S         | TART fau      | ılt occurre | d         |

| 09h         | Start status             | CoR | 1            | 0000,0000b      | -          | -            | -          | -                | STRT4     | STRT3         | STRT2       | STRT1     |

| 0Ah         | Commission               | RO  | 1            | 0040 0040       | TOD        |              | VDUV       | \/ <b>E</b> LI\/ |           |               | 0005        |           |

| 0Bh         | Supply event             | CoR | 1            | 0010,0010b      | TSD        | - VDUV VEUV  |            | -                | -         | OSCF          | -           |           |

| 0Ch         | Port 1 status            | RO  | 1            | 0000,0000b      | -          | CLASS Port 1 |            | -                | DE        | DETECT Port 1 |             |           |

| 0Dh         | Port 2 status            | RO  | 1            | 0000,0000b      | -          | CL           | ASS Por    | t 2              | -         | DETECT Port 2 |             |           |

| 0Eh         | Port 3 status            | RO  | 1            | 0000,0000b      | -          | CL           | ASS Por    | t 3              | -         | DETECT Port 3 |             |           |

| 0Fh         | Port 4 status            | RO  | 1            | 0000,0000b      | -          | CL           | ASS Por    | t 4              | -         | DETECT Port 4 |             | rt 4      |

| 10h         | Power status             | RO  | 1            | 0000,0000b      | PG4        | PG3          | PG2        | PG1              | PE4       | PE3           | PE2         | PE1       |

| 11h         | Pin status               | RO  | 1            | 00,A[3:0],0,A   | -          | -            | SLA3       | SLA2             | SLA1      | SLA0          | -           | AUTO      |

| 12h         | Operating mode           | R/W | 1            | AAAA,AAAAb      | Port 4     | Mode         | Port 3     | Mode             | Port 2    | Mode          | Port 1      | Mode      |

| 13h         | Disconnect enable        | R/W | 1            | AAAA,0000b      | ACDE4      | ACDE3        | ACDE<br>2  | ACDE<br>1        | DCDE4     | DCDE3         | DCDE2       | DCDE1     |

| 14h         | Detect/class enable      | R/W | 1            | AAAA,AAAAb      | CLE4       | CLE3         | CLE2       | CLE1             | DETE4     | DETE3         | DETE2       | DETE1     |

| 16h         | Timing configuration     | R/W | 1            | 0000,0000b      | -          |              | TST        | ART              | TIC       | UT            | TD          | DIS       |