TLCS-90 Series TMP90C802A/803A

#### **CMOS 8–Bit Microcontrollers**

#### TMP90C802AP/TMP90C802AM

### TMP90C803AP/TMP90C803AM

#### 1. Outline and Characteristics

The TMP90C802A is a high-speed advanced 8-bit microcontroller applicable to a variety of equipment.

With its 8-bit CPU, ROM, RAM, timer/event counter and general-purpose serial interface integrated into a single CMOS chip, the TMP90C802A allows the expansion of external memories (up to 56K byte). The TMP90C803A is the same as the TMP90C802A but without the ROM

The TMP90C802AP/803AP is in a DIP product. The TMP90C802AM/8803AM is in a SOP (Small Outline Package).

The characteristics of the TMP90C802A include:

Powerful instructions: 163 basic instructions, including Multiplication, division, 16-bit arithmetic operations, bit manipulation instructions

- (2) Minimum instruction executing time: 320ns (at 12.5MHz oscillation frequency)

- (3) Internal ROM: 8K byte (The TMP90C803A does not have a built-in ROM.)

- (4) Internal RAM: 256 byte

- (5) Memory expansion External memory: 56K byte

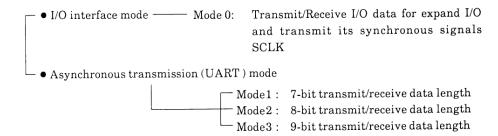

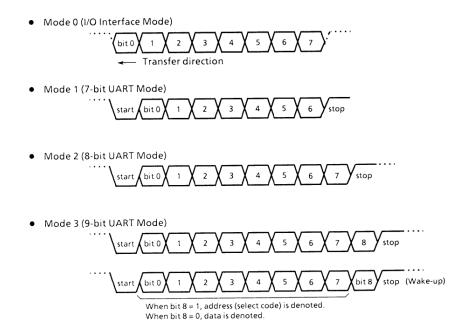

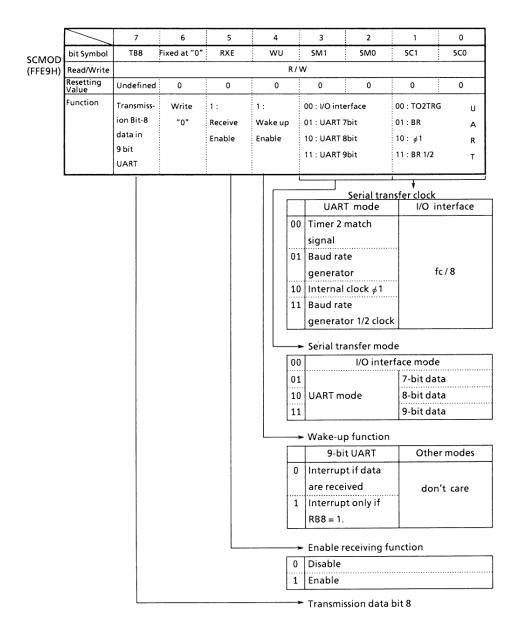

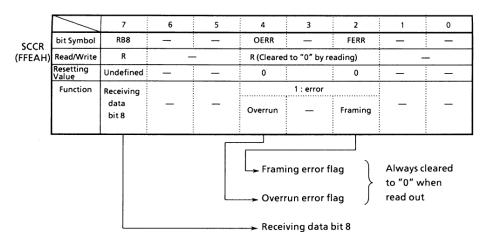

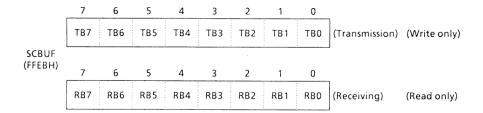

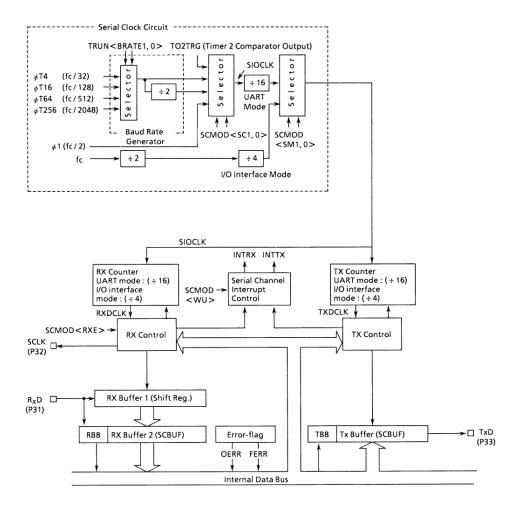

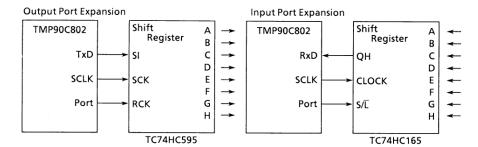

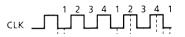

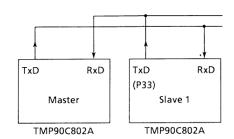

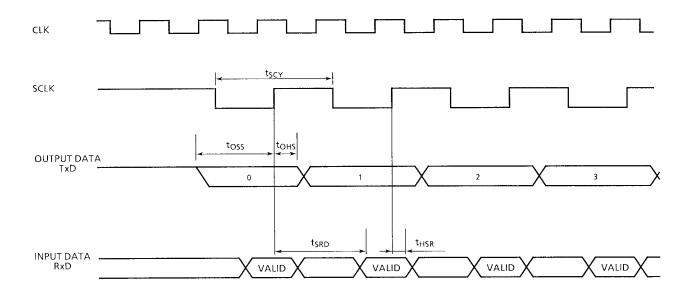

- (6) General-purpose serial interface (1 channel) Asynchronous mode, I/O interface mode

- (7) 8-bit timers (4 channels): (1 external clock input)

- (8) Port with zero cross detection circuit (1 input)

- (9) Input/Output ports (TMP90C802A: 32 pins, 90C803A: 6 pins)

- (10) Interrupt function: 8 internal interrupts and 3 external interrupts

- (11) Micro Direct Memory Access (DMA) function (4 channels)

- (12) Watchdog timer

- (13) Standby function (4 HALT modes)

The information contained herein is presented only as guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. These TOSHIBA products are intended for usage in general electronic equipments (office equipment, communication equipment, measuring equipment, domestic electrification, etc.) Please make sure that you consult with us before you use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which could have major impact to the welfare of human life (atomic energy control, spaceship, traffic signal, combustion control, all types of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may occur in case these TOSHIBA products were used in the mentioned equipments without prior consultation with TOSHIBA.

TOSHIBA CORPORATION 1/86

The information contained here is subject to change without notice

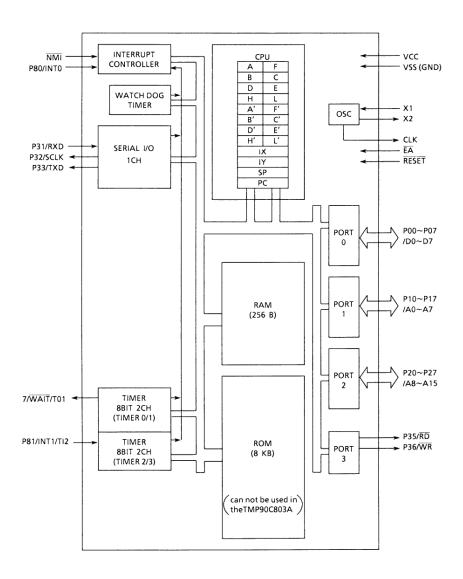

Figure 1. TMP90C802A Block Diagram

2/86 TOSHIBA CORPORATION

# 2. Pin Assignment and Functions

# 2.1 Pin Assignment

The assignment of input/output pins, their names and functions are described below.

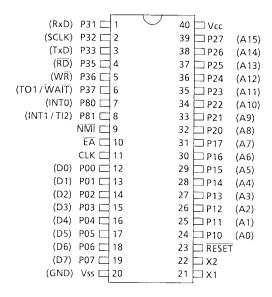

Figure 2.1 shows pin assignment of the TMP90C802A/803A.

Figure 2.1. Pin Assignment

# 2.2 Pin Names and Functions

The names of input/output pins and their functions are summarized in Table 2.2.

Table 2.2 Pin Names and Functions (1/2)

| Pin Name              | No. of pins | I/O 3 states | Function                                                                                                                                |

|-----------------------|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| P00 ~ P07             | 0           | 1/0          | Port 0: 8-bit I/O port that allows selection of input/output on byte basis                                                              |

| /D0 ~ D7              | 8           | 3 states     | Data bus: Also functions as 8-bit bidirectional data bus for external memory                                                            |

| D40 D47               |             | 1/0          | Port 1: 8-bit I/O port that allows selection on byte basis                                                                              |

| P10 ~P17<br>/A0 ~ A7  | 8           | Output       | Address bus: The lower 8 bits address bus for external memory                                                                           |

| P20 ~ P27             | 8           | 1/0          | Port 2: 8-bit I/O port that allows selection on bit basis                                                                               |

| /A8 ~ A15             | 0           | Output       | Address bus: The upper 8 bits address bus for external memory                                                                           |

| P31                   | 1           | Input        | Port 31: 1-bit input port                                                                                                               |

| /RxD                  | l           |              | Receives Serial Data                                                                                                                    |

| P32                   | 1           | Output       | Port 32: 1-bit output port                                                                                                              |

| /SCLK                 | l           |              | Serial clock output                                                                                                                     |

| P33                   | 1           | Output       | Port 33: 1-bit output port                                                                                                              |

| /TxD                  | l           |              | Transmitter Serial Data                                                                                                                 |

| P35                   | 1           | Output       | Port 35: 1-bit output port                                                                                                              |

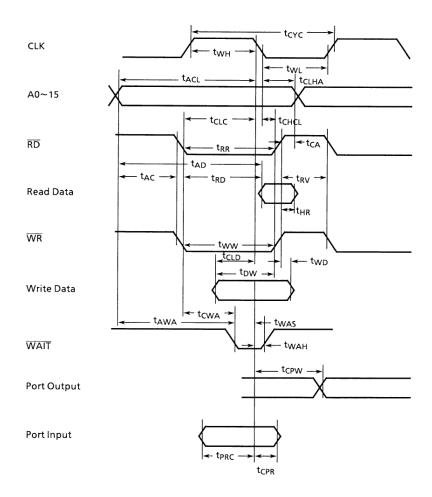

| /RD                   | '           | Output       | Read: Generates strobe signal for reading external memory                                                                               |

| P36                   | 1           | Output       | Port 36: 1-bit output port                                                                                                              |

| /WR                   | '           | Output       | Write: Generates strobe signal for writing into external memory                                                                         |

| P37                   | 1           | Innut        | Port 37: 1-bit input port                                                                                                               |

| /WAIT                 |             | Input        | Wait: Input pin for connecting slow speed memory or peripheral LSI                                                                      |

| /T01                  |             | Output       | Timer output 1: Output of Timer 0 or 1                                                                                                  |

|                       |             |              | Port 80: 1-bit input port                                                                                                               |

| P80                   | 1           | Input        | Interrupt request pin 0: Interrupt request pin (Level/rising edge is programmable)                                                      |

| /INTO                 |             | ,            |                                                                                                                                         |

|                       |             |              | Port 81: 1-bit input port                                                                                                               |

| P81                   |             | land         | Interrupt request pin 1: Interrupt request pin (Rising edge)                                                                            |

| /INT1<br>/TI2         | 1           | Input        |                                                                                                                                         |

| ,                     |             |              | Timer input 2: Counter/capture trigger signal for Timer 2                                                                               |

|                       |             |              | Non-maskable interrupt request pin: Falling edge interrupt request pin                                                                  |

| NMI                   | 1           | Input        |                                                                                                                                         |

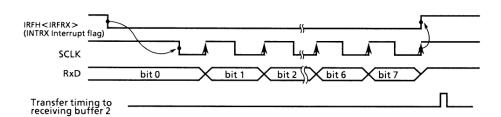

| CLK                   | 1           | Output       | Clock output: Generates clock pulse at 1/4 frequency of clock oscillation. It is pulled up internally during resetting.                 |

| ĒĀ                    | 1           | Input        | External access: Connects with $V_{CC}$ pin in the TMP90C802A using internal ROM, and with GND pin the TMP90C803A with no internal ROM. |

| RESET                 | 1           | Input        | Reset: Initializes the TMP90C802A/803A. (Built-in pull-up resister)                                                                     |

| X1/X2                 | 2           | Input/Output | Pin for quartz crystal or ceramic resonator (1 ~ 12.5MHz)                                                                               |

| V <sub>CC</sub>       | 1           | -            | Power supply (+5V)                                                                                                                      |

| V <sub>SS</sub> (GND) | 1           | -            | Ground (OV)                                                                                                                             |

# 3. Operation

This chapter describes the functions and the basic operations of the TMP90C802A in every block.

#### 3.1 CPU

TMP90C802A includes a high performance 8-bit CPU. For the function of the CPU, see the book TLCS Series CPU Core Architecture concerning CPU operation. This chapter explains exclusively the functions of the CPU of TMP90C802A which are not described in that book.

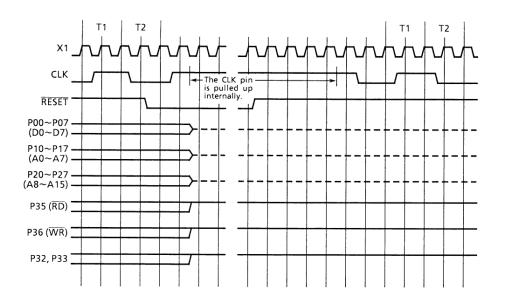

#### 3.1.1 Reset

The basic timing of the reset operation is indicated in Figure 3.1. In order to reset the TMP90C802A, the RESET input must be maintained at the "0" level for at least ten system clock cycles (10 stated: 2µsec at 10MHz) within an operating voltage band and with a stable oscillation. When a reset request is accepted, all I/O ports (Port 0/data bus D0  $\sim$  D7, Port 1/ address bus A0 to A7, Port 2/address bus A8 to A15) function as input ports (high impedance state). Output ports (P32, P33, P35 (RD) and P36 (WR) and CLK turn to "1". Input ports remain unchanged.

The registers of the CPU also remain unchanged. Note, however, that the program counter "PC" and the interrupt enable flag IFF are cleared to "0". Register A shows an undefined status.

When the reset is cleared, the CPU starts executing instructions from the address 0000H.

Figure 3.1. Reset Timing

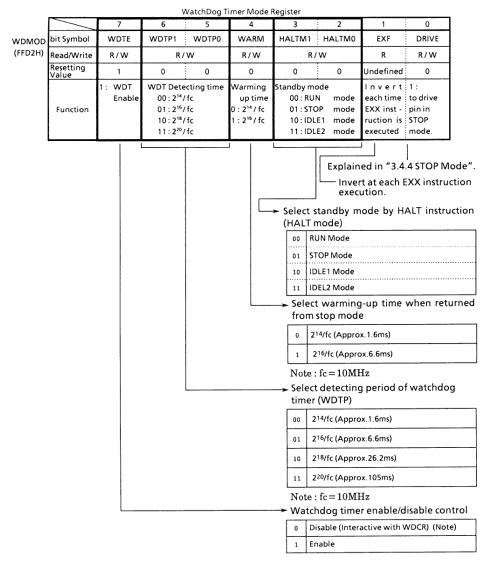

#### 3.1.2 EXF (Exchange Flag)

For TMP90C802A, "EXF", which is inverted when the command "EXX" is executed to transfer data between the main

W

register and the auxiliary register, is allocated to the first bit of memory address FFD2H.

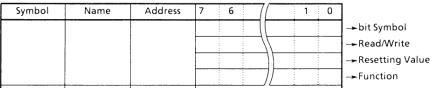

|       |                    | 7                 | 6                                                                                                            | 5              | 4                                                                        | 3                                                        | 2                           | 1                                                          | 0                                         |

|-------|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------|------------------------------------------------------------|-------------------------------------------|

| DMOD  | bit Symbol         | WDTE              | WDTP1                                                                                                        | WDTP0          | WARM                                                                     | HALTM1                                                   | HALTM0                      | EXF                                                        | DRIVE                                     |

| FD2H) | Read/Write         | R/W               | R/                                                                                                           | w              | R/W                                                                      | R/                                                       | W                           | R                                                          | R/W                                       |

|       | Resetting<br>Value | 1                 | 0                                                                                                            | 0              | 0                                                                        | 0                                                        | 0                           | Undefined                                                  | 0                                         |

|       | Function           | 1 : WDT<br>Enable | WDT Dete<br>00: 2 <sup>14</sup> /<br>01: 2 <sup>16</sup> /<br>10: 2 <sup>18</sup> /<br>11: 2 <sup>20</sup> / | fc<br>fc<br>fc | Warming<br>up time<br>0: 2 <sup>14</sup> / fc<br>1: 2 <sup>16</sup> / fc | Standby mo<br>00: RUN<br>01: STO<br>10: IDLE<br>11: IDLE | M mode<br>P mode<br>E1 mode | Invert<br>each time<br>EXX inst-<br>ruction is<br>executed | 1:<br>to drive<br>pins in<br>STOP<br>mode |

#### 3.1.3 Wait Control

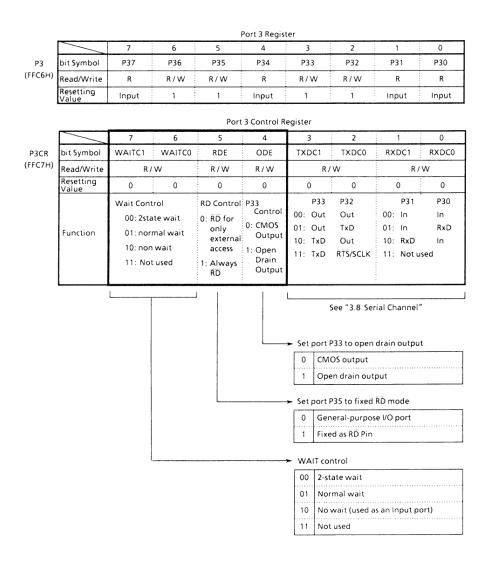

For TMP90C802A, a wait control register (WAITC) is allocated

to the 6th and 7th bits of memory address FFC7H.

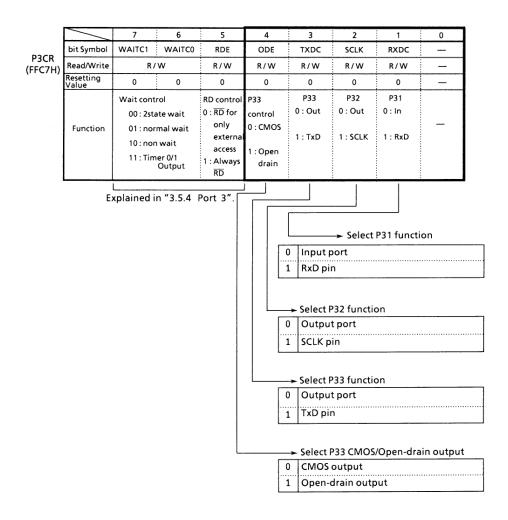

P3CR (FFC7H)

|                    | 7      | 6                              | 5                                                        | 4                             | 3                                               | 2                                    | 1                                                | 0                      |

|--------------------|--------|--------------------------------|----------------------------------------------------------|-------------------------------|-------------------------------------------------|--------------------------------------|--------------------------------------------------|------------------------|

| bit Symbol         | WAITC1 | WAITC0                         | RDE                                                      | ODE                           | TXDC1                                           | TXDC0                                | RXDC1                                            | RXDC0                  |

| Read/Write         | R      | / W                            | R/W                                                      | R/W                           | R                                               | / W                                  | R/                                               | w .                    |

| Resetting<br>Value | 0      | 0                              | 0                                                        | 0                             | 0                                               | 0                                    | 0                                                | 0                      |

| Function           |        | ate wait<br>mal wait<br>n wait | RD control  0: RD for only external access  1: Always RD | control<br>0: CMOS<br>1: Open | P33<br>00: Out<br>01: Out<br>10: TxD<br>11: TxD | P32<br>Out<br>TxD<br>Out<br>RTS/SCLK | P31<br>00: In<br>01: In<br>10: RxD<br>11: Not us | P30<br>In<br>RxD<br>In |

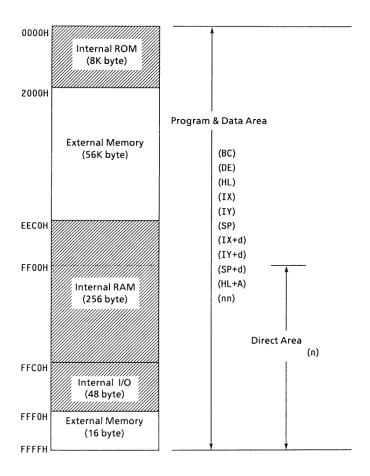

# 3.2 Memory Map

The TMP90C802A supports a program memory of up to 64K bytes.

The program/data memory may be assigned to the address space from 0000H to FFFFH.

## (1) Internal ROM

The TMP90C802A internally contains an 8K byte ROM. The address space from 0000H  $\sim$  1FFFH is provided to the ROM. The CPU starts executing a program from 0000H by resetting.

The addresses 0010H  $\sim$  007FH in this internal ROM area are used for the entry area for the interrupt processing. The TMP90C803A does not have a built-in ROM; therefore, the address space 0000H  $\sim$  1FFFFH is used as external memory space.

## (2) Internal RAM

The TMP90C802A also contains a 256 byte RAM, which is allocated to the address space from FFC0H ~ FFBFH. The CPU allows the access to the whole RAM area (FF00H ~ FFBFH, 192 bytes) by a short operation code (opcode) in a "direct addressing mode".

The addresses from FF30H  $\sim$  FF7FH in this RAM area can be used as parameter area for micro DMA processing (and for any other purposes when the micro DMA function is not used).

## (3) Internal I/O

The TMP90C802A provides a 48-byte address space as an internal I/O area, whose addresses range from FFC0H ~ FFEFH. This I/O area can be accessed by the CPU using a short opcode in the "direct addressing mode". Figure 3.2 is a memory map indicating the area accessible by the CPU in the respective addressing mode.

Figure 3.2. Memory Map

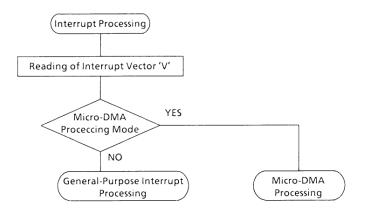

# 3.3 Interrupt Functions

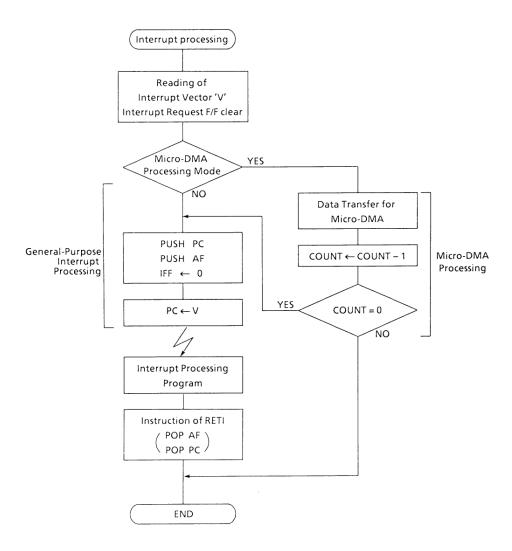

The TMP90C802A supports a general purpose interrupt processing mode and a micro DMA processing mode that enables automatic data transfer by the CPU for internal and external interrupt requests.

After the reset state is released, all interrupt requests are

processed in the general purpose interrupt processing mode. However, they can be processed in the micro DMA processing mode by using a MDA enable register to be described later.

Figure 3.3 (1) is a flow chart of the interrupt response sequence.

TOSHIBA CORPORATION

Figure 3.3 (1). Interrupt Response Flowchart

When an interrupt is requested, the source of the interrupt transmits the request to the CPU via an internal interrupt controller. The CPU starts the interrupt processing if it is a non-maskable or maskable interrupt requested in the EI state. However, a maskable interrupt requested in the DI state (IFF = "0") is ignored.

Having acknowledged an interrupt, the "CPU" reads out the interrupt vector from the internal interrupt controller to find out the interrupt source.

Then, the CPU checks if the interrupt requests the general purpose interrupt processing or the micro DMA processing, and proceeds to each processing.

As the reading of an interrupt vectors is performed in the internal operating cycles, the bus cycle results in dummy cycles.

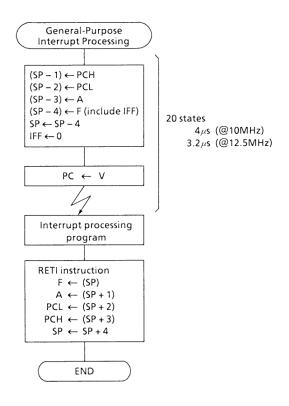

## 3.3.1 General Purpose Interrupt Processing

A general purpose interrupt is processed as shown in Figure 3.3 (2).

The CPU stores the contents of the program counter PC and the register pair AF (including the interrupt enable flag (IFF) before the interrupt) into the stack, and resets the interrupt enable flag IFF to "0" (disable interrupts). In then transfers the value of the interrupt vector "V" to the program counter, and the processing jumps to an interrupt processing program.

The overhead for the entire process from accepting an interrupt to jumping to an interrupt processing program is 20 states.

Figure 3.3 (2). General Purpose Interrupt Processing Flowchart

An interrupt (Maskable and Non-maskable) processing program ends with a RETI instruction.

When this instruction is executed, the data previously stacked from the program counter PC and the register pair AF are restored.

After the CPU reads out the interrupt vector, the interrupt source acknowledges that the CPU accepts the request, and clears the request.

A non-maskable interrupt cannot be disabled by programming. A

maskable interrupt, on the other hand, can be enabled or disabled by programming. An interrupt enable flip-flop (IFF) is provided on the bit 5 of Register F in the CPU. The interrupt is enabled or disabled by setting IFF to "1" by the El instruction or to "0" by the DI instruction, respectively. IF is reset to "0" by the reset operation or the acceptance of any interrupt (including non-maskable interrupt). the interrupt can be enabled after the subsequent instruction of El instruction is executed.

Table 3.3 (1) lists the possible interrupt sources.

| Table 3.3 | (1) Interrupt | Sources |

|-----------|---------------|---------|

|-----------|---------------|---------|

| Priority<br>order | Туре     | Interrupt source                   | Vector<br>Value<br>÷ 8 | Vector<br>Value | Start<br>address of general<br>purpose interrupt<br>processing | Start<br>address of<br>Micro DMA<br>processing<br>parameter |

|-------------------|----------|------------------------------------|------------------------|-----------------|----------------------------------------------------------------|-------------------------------------------------------------|

| 1                 | Non      | SWI instruction                    | 02H                    | 10H             | 0010H                                                          | _                                                           |

| 2                 | maskable | NMI (Input from NMI pin)           | 03H                    | 18H             | 018H                                                           | -                                                           |

| 3                 | maskabio | INTWD (watchdog)                   | 04H                    | 20H             | 0020H                                                          | _                                                           |

| 4                 |          | INTO (External input 0)            | 05H                    | 28H             | 0028H                                                          | _                                                           |

| 5                 |          | INTTO (Timer 0)                    | 06H                    | 30H             | 0030H                                                          | FF30H                                                       |

| 6                 |          | INTT1 (Timer 1)                    | 07H                    | 38H             | 0038H                                                          | FF38H                                                       |

| 7                 | Maakabla | INTT2 (Timer 2)                    | 08H                    | 40H             | 0040H                                                          | _                                                           |

| 8                 | Maskable | INTT3 (Timer 3)                    | 09H                    | 48H             | 0048H                                                          | _                                                           |

| 9                 |          | INT1 (External input 1)            | 0AH                    | 58H             | 0058H                                                          | _                                                           |

| 10                |          | INTRX (End of serial receiving)    | 0EH                    | 70H             | 0070H                                                          | FF70H                                                       |

| 11                |          | INTTX (End of serial transmission) | 0FH                    | 78H             | 0078H                                                          | FF78H                                                       |

The "priority order" in the table shows the order of the interrupt source to be acknowledge by the CPU when more than one interrupt are requested at one time.

In interrupt of fourth and fifth orders are requested simultaneously, for example, an interrupt of the "5th" priority is acknowledged after a "4th" priority interrupt processing has been completed by a RETI instruction. However, a lower priority interrupt can be acknowledged immediately by executing an El instruction in a program that processes a higher priority interrupt.

The internal interrupt controller merely determines the priority of the sources of interrupts to be acknowledged by the CPU when more than one interrupt are requested at a time. It is, therefore, unable to compare the priority of interrupt being executed with the one being requested.

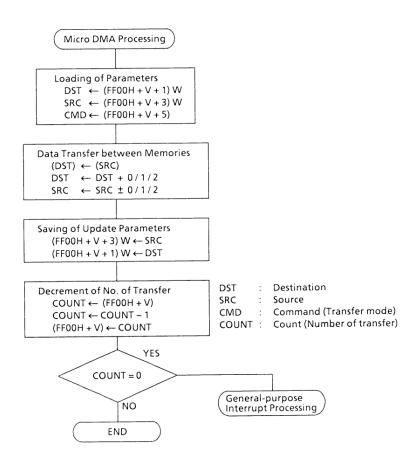

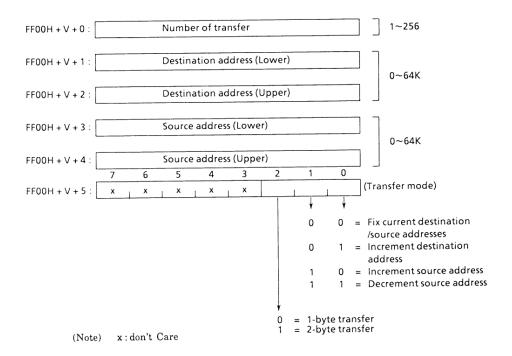

## 3.3.2 Micro DMA Processing

Figure 3.3 (3) is a flow chart of the micro DMA processing. Parameters (addresses of source and destination, and transfer mode) for the data transfer between memories are loaded by the CPU from an address modified by an interrupt vector value. After the data transfer between memories according to these parameter, these parameters are updated and saved into the original locations. The CPU then decrements the number of transfers, and completes the micro DMA processing unless the result is "O".

If the number of transfer becomes "0", the CPU proceeds to the general purpose interrupt handling described in the previous chapter.

10/86 TOSHIBA CORPORATION

Figure 3.3 (3). Micro DMA Processing Flowchart

The micro DMA processing is performed by using only hardware to process interrupts mostly completed by simple data transfer. The use of hardware allows the micro DMA processing to handle the interrupt in a higher speed that the conventional

methods using software. the CPU registers are not affected by the micro DMA processing.

Figure 3.3 (4). Parameters for Micro DMA Processing

Parameters for the micro DMA processing are located in the internal RAM area (See Table 3.3 (1) Interrupt Sources). The start address of each parameter is "FF00H + interrupt vector value", from which a six bytes' space is used for the parameter. This space can be used for any other memory purposes if the micro DMA processing is not used.

The parameters normally consist of the number of transfer, addresses of destination and source, and transfer mode. The number of transfer indicates the number of data transfer accepted in the micro DMA processing.

The amount of data transferred by a single micro DMA

processing is one or two bytes. The number of transfers is 256 when the number of transfers value is "00H". Both the destination and source addresses are specified by 2-byte data. The address space available for the micro DMA processing ranges from 0000H to FFFFH.

Bits 0 and 1 of the transfer mode indicates the mode updating the source and/or destination, and the bit 2 indicates the data length (one byte or two bytes).

Table 3.3 (2) shows the relation between the transfer mode and the result of updating the destination/source addresses.

| Table 3.3 (2) Addresses I | Jpda  | ited k | y Micro |

|---------------------------|-------|--------|---------|

| DMA Proces                | ssing | J      |         |

| Transfer<br>Mode | Function                                                      | Destination address | Source<br>address |

|------------------|---------------------------------------------------------------|---------------------|-------------------|

| 000              | 1-byte transfer: Fix the current source/destination addresses | 0                   | 0                 |

| 001              | 1-byte transfer: Increment the destination address            | +1                  | 0                 |

| 010              | 1-byte transfer: Increment the source address                 | 0                   | +1                |

| 011              | 1-byte transfer: Decrement the source address                 | 0                   | -1                |

| 100              | 2-byte transfer: Fix the current source/destination addresses | 0                   | 0                 |

| 101              | 2-byte transfer: Increment the destination address            | +2                  | 0                 |

| 110              | 2-byte transfer: Increment the source address                 | 0                   | +2                |

| 111              | 2-byte transfer: Decrement the source address                 | 0                   | -2                |

12/86 TOSHIBA CORPORATION

In the 2 byte transfer mode, data are transferred as follows:

(Destination address)  $\leftarrow$  (Source address) (Destination address + 1)  $\leftarrow$  (Source address + 1)

Similar data transfers are made in the modes that "decrement the source address", but the updated address are different as shown in the Table 3.3 (2).

Figure 3.3 (5) shows an example of the micro DMA processing that handles data receiving of internal serial I/O.

This is an example of executing "an interrupt processing program after serial data receiving" after receiving 7-frame data (Assume 1 frame = 1 byte for this example) and saving them into the memory addresses from FF00H to FF06H.

CALL SIOINIT; Initial setting for serial addressing. SET 1, (0FFE6H); Enable an interrupt for serial data

H) ; Enable an interrupt for serial data

receiving.

SET 1, (0FFE8H); Set the micro DMA processing

mode for the interrupt.

LD (0FF70H),7; Set the number of transfer = 7 LDW (0FF71H),

OFFOOH ; Set FFOOH for the destination

address.

LDW (OFF73H),

OFFEBH; Set FFEBH for the source (serial

receiving buffer) address.

LD (0FF75H),1; Set the transfer mode (1-byte

transfer:Increment destination

address.)

EI :

: ORG 0070H

Interrupt processing program after serial data receiving

**RETI**

Figure 3.3 (5). Example of Micro DMA Processing

The bus operation in the general- purpose interrupt processing and the micro DMA processing is shown in "Table 1.4 (2) Bus Operation for Executing Instructions" in the previous section.

The micro DMA processing time (when the number of

transfer is not decremented to 0) is 46 states (9.2 $\mu$ s at 10MHz oscillation frequency) without regard to the 1-byte/2-byte transfer mode.

Figure 3.3 (6) shows the interrupt processing flowchart.

Figure 3.3 (6). Interrupt Processing Flowchart

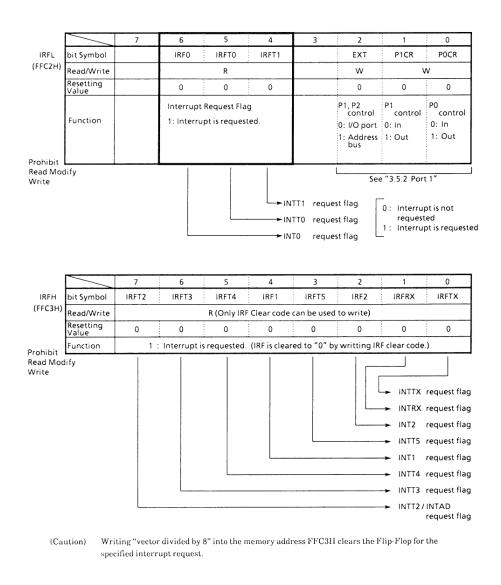

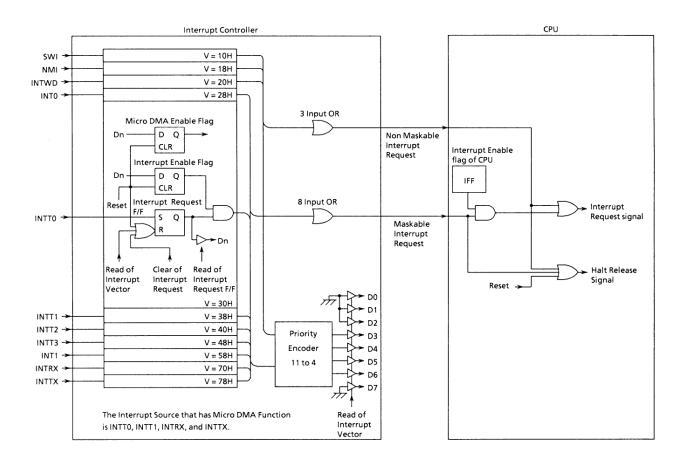

#### 3.3.3 Interrupt Controller

Figure 3.3 (8) outlines the interrupt circuit. The left side of this figure represents an interrupt controller, and the right side comprises the CPU's interrupt request signal circuit and HALT release signal circuit.

The interrupt controller consists of Interrupt Request Flipflops, Interrupt Enable flags, and micro DMA enable flags allocated to each of 14 channels. The Interrupt Request Flip-flops serve to latch interrupt requests from peripherals. Each Flipflop is reset to "0" when a reset or interrupt is acknowledged by the CPU and the vector of the interrupt channel is read into the CPU, or when the CPU executes an instruction that clears

an Interrupt Request Flip-flop for the specified channel (write "vector divided by 8" in the memory address FFC3H). For example, by executing.

LD (FFC3H), 58H/8,

The Interrupt Request Flip-flops for the interrupt channel "INT1" whose vector is 58H is reset to "0". The status of an Interrupt Request Flip-flops is found out by reading the memory address FFC2H or FFC3H. "0" denotes

there is not interrupt request, and "1" denotes that an interrupt is requested. Figure 3.3 (7) illustrates the bit configuration indicating the status of Interrupt Request Flip-flops.

Figure 3.3 (7). Configuration of Interrupt Request Flip-Flops

Figure 3.3 (8). Block Diagram of Interrupt Controller

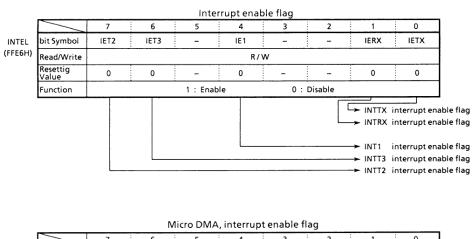

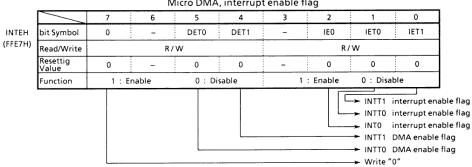

The interrupt enable flags provided for all interrupt request channels are assigned to the memory address FFE6H to FFE7H. Setting any of these flags to "1" enables an interrupt of the respective channel. These flags are initialized to "0" by resetting.

Clear the interrupt enable flag in the DI status.

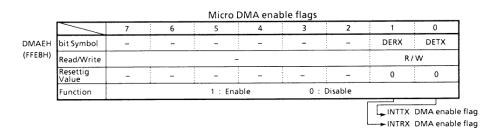

The micro DMA enable flag also provided for each interrupt request channel is assigned to the memory address FFE7H to

FFE8H. The interrupt processing for each channel is placed in the micro DMA processing mode by setting this flag to "1". This flag is initialized to "0" (general purpose interrupt processing mode) by resetting.

Figure 3.3 (9) shows the bit configuration of the interrupt enable flags and micro DMA enable flags.

The external interrupt functions are shown below.

16/86 TOSHIBA CORPORATION

| Interrupt | Common Terminal | Mode         | How to set             |

|-----------|-----------------|--------------|------------------------|

| NMI       | -               | Falling edge | _                      |

| INTO      | P80             | Level        | P8CR < EDGE> = 0       |

| 0         |                 | Rising edge  | P8CR <edge> = 1</edge> |

| INT1      | P81             | Rising edge  | _                      |

For the pulse width for the external interrupts, see section 4.7 "Interrupt Operation".

Attention should be paid to the following three modes having special circuits:

| INTO Level mode  | IF INTO is not an edge-based interrupt, the function of Interrupt Request Flip-flop is cancelled. Therefore, the interrupt request signal must be held until the interrupt request is acknowledged by the CPU. A change in the mode (edge to level) automatically clears the interrupt request flag. When the CPU has been put in the interrupt response sequence with INTO level mode, it is necessary to leave INTO at "1" until the second bus cycle of the interrupt response sequence is completed. Also, "1" must always be held until HALT is cleared when using the INTO level mode to clear HALT. (USE care to prevent noise changing "1" back to "0".)  When switching from the level mode to the edge mode, the interrupt request flag set in the level mode is not cleared; therefore, use the following sequence to clear the interrupt request flag.  DI  LD (0FFD1H), 01H: switch from level to edge  LD (0FFC3H), 05H: clear interrupt request flag  EI |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRX level mode | The Interrupt Request Flip-flop is cleared only by resetting or reading the serial channel receiving buffer, and not by an instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

TOSHIBA CORPORATION 17/86

Figure 3.3 (9). Interrupt/Micro DMA Enable Flags

### 3.4 Standby Function

When a HALT instruction is executed, the TMP90C802 selects one of the following modes as determined by the halt mode set register:

(1) RUN: Suspends only the CPU operation. The power

consumption remains unchanged.

(2) IDLE1: Suspends all internal circuits except the inter

nal oscillator. In this mode, the power con sumption is less than 1/10 of that in the

normal operation.

(3) IDLE2: Operate only the internal oscillator and

specific internal I/O devices. The power consumption is about 1/3 of that in the normal

operation.

(4) STOP: Suspends all internal circuits including the

internal oscillator. In this mode, the power consumption is considerably reduced.

The HALT mode set register WDMOD <HALTM 1, 0> is assigned too the bits 2 and 3 of the memory address FFD2H in the internal I/O register area (other bits are used to control other functions). The register is reset to "00" (RUN mode) by resetting.

These HALT state can be released by resetting or requesting an interrupt. The methods for releasing the HALT status are shown in Table 3.4 (2).

Either a non-maskable or maskable interrupt with EI (enable interrupt) condition is acknowledged and interrupt processing is processed. A maskable interrupt with DI instruction that follows the HALT instruction, but the interrupt request flag is held at "1".

But if interrupt request occur before MPU practices "HALT" command in the state of DI and it latches interrupt request flag, it causes to release HALT state and to do state will be released as soon as after MPU practices "HALT" command. (MPU doesn't HALT state.)

Therefore clear interrupt request flag or disable interrupt enable flag before MPU practices "HALT" command.

ex) MPU becomes STOP mode in the state of DI and release it byINT0 interrupt.

(But "built-in I/O" uses only Tomer 0")

DI SET 2, (INTEH) ; INTO interrupt enable RES 1, (INTEH) ; INTO interrupt disable

LD (WDMOD), 04H; STOP mode HALT

After release "HALT"

Practice Program

When the halt status is released by a reset, the status in effect before entering the halt status (including built-in RAM) is held. The RAM contents may not be held, however, if the HALT instruction is executed within the built-in RAM.

0 WDMOD WDTE WDTP1 WARM HALTM1 HALTM0 DRIVE bit Symbol WDTP0 EXF (FFD2H) Read/Write R/W R/W R/W R/W R/W Resetting Value 0 0 0 0 Undefined WDT Detecting time 1 · WDT Standby mode Invert Warming to drive 00: RUŃ 00: 214/fc up time 0: 214/ fc mode each time Enable Function 01: 216/fc 01: STOP EXX instmode pin in 10: 218/fc 1: 216/ fc 10: IDLE1 ruction is STOP 11: 220/fc 11: IDLE2 executed mode Explained in Explained in "3.8 Watchdog Timer" Exchange flag "3.4.4 STOP mode" Explained in "3.1.2 Registers"

Figure 3.4 (1). HALT Mode Set Register

# **3.4.1 RUN Mode**

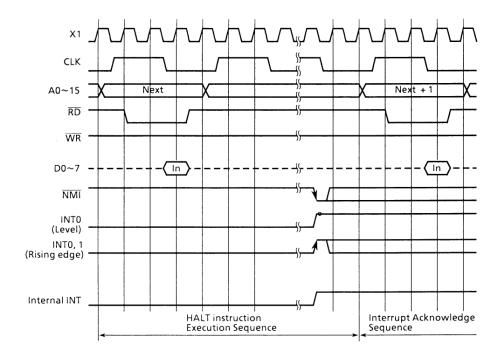

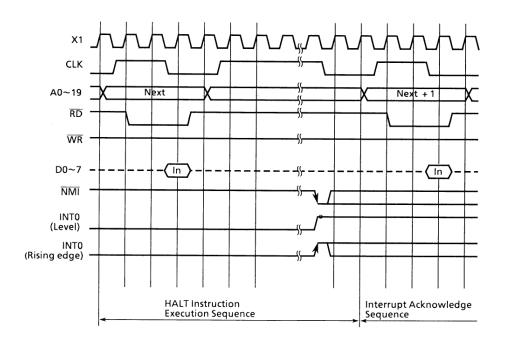

Figure 3.4 (2) shows the timing for releasing the HALT state by interrupts in the RUN/IDLE 2 mode.

In the RUN mode, the system clock in the MCU continues to operate even after a HALT instruction is executed. Only the

CPU stops executing the instruction. Until the HALT state is released, the CPU repeats dummy cycles. In the HALT state, an interrupt request is sampled with the rising edge of the "CLK" signal.

Figure 3.4 (2). Timing Chart for Releasing the HALT State by Interrupts in RUN/IDLE 2 Modes

20/86 TOSHIBA CORPORATION

#### 3.4.2 IDLE 1 Mode

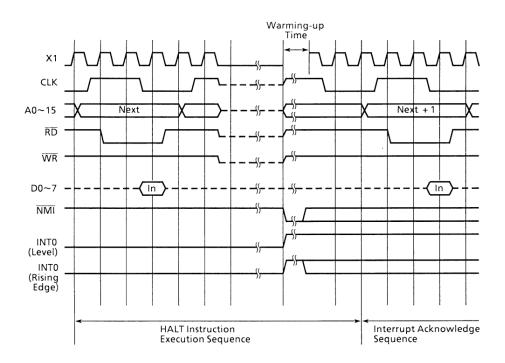

Figure 3.4 (3) illustrates the timing for releasing the HALT state by interrupts in the IDLE 1 mode.

In the IDLE 1 mode, only the internal oscillator and the watchdog timer operate. The system clock in the MCU stops, and the CLK signal is fixed at the "1" level.

In the HALT state, an interrupt request is sampled asynchronously with the system clock, however the HALT release (restart of operating) is performed synchronously with it.

Note: An interrupt requested by the watchdog timer is prohibited through the HALT period in this mode.

Figure 3.4 (3). Timing chart of HALT Released by Interrupts in IDLE1 Mode

### 3.4.3 IDLE 2 Mode

Figure 3.4 (2) shows the timing of HALT release caused by interrupts in the RUN/IDLE 2 mode.

In the IDLE 2 mode, the HALT state is released by an interrupt with the same timing as in the RUN mode, except the internal operation of the MCU. In the RUN mode, only the CPU stops executing the current instruction, and the system clock is supplied to all internal devices. In the IDLE 2 mode, however, the system clock is supplied to only specific internal I/O devices. As a result, the HALT state in the IDLE 2 mode requires only a 1/3 of the power consumed in the RUN mode. In the IDLE 2 mode, the system clock is supplied to the following I/O devices:

- 8-bit timer

- Serial interface

- Watchdog timer

### 3.4.4 STOP Mode

Figure 3.4 (4) is a timing chart for releasing the HALT state by interrupts in the STOP mode.

The STOP mode is selected to stop all internal circuits including the internal oscillator. In this mode, all pins except special ones are put in the high-impedance state, independent of the internal operation of the MCU. Table 3.4 (1) summarizes the state of these pins in the STOP mode. Note, however, that the pre-halt state (The status prior to execution of HALT instruction) of all output pins can be retained by setting the internal I/O register WDMOD<DRVE (Drive enable: Bit 0 of memory address FFD2H) to "1". The content of this register is initialized to "0" by resetting.

When the CPU accepts an interrupt request, the internal oscillator is restarted immediately. However, to get the stabilized oscillation, the system clock starts its output after the time set by the warming up counter WDMOD<WARM> (Warming up: Bit 4 of memory address FFD2H). A warming-up time of either the clock oscillation time x  $2^{14}$  or x  $2^{16}$  can be set by setting this bit to either "0" or "1". This bit is initialized to "0" by resetting.

Figure 3.4 (4). Timing Chart of HALT Released by Interrupt in STOP Mode

The internal oscillator can be also restarted by the input of the RESET signal at "0" the CPU. In the Reset restart mode, however, the warming-up counter remains inactive in order to get the quick response of MCU when the power is turned on (Power on Reset). As a result, the normal operation may not be

performed due to the unstable clock supplied immediately after restarting the internal oscillator. To avoid this, it is necessary to keep the RESET signal at "0" long enough too release the HALT state in the STOP mode.

| Table 3.4  | (1)         | State | of | Pins in    | STOP                                             | Mode   |

|------------|-------------|-------|----|------------|--------------------------------------------------|--------|

| I abic o.T | ۱: <i>,</i> | Otate | v  | 1 1113 111 | $\mathbf{o}_{\mathbf{i}}\mathbf{o}_{\mathbf{i}}$ | IVIOUC |

|                          | In/Out                               | DRVE = 0 | DRVE = 1  |

|--------------------------|--------------------------------------|----------|-----------|

| PO                       | Input mode<br>Output mode            | -<br>OUT | –<br>OUT  |

| P1                       | Input mode<br>Output mode            | -        | IN<br>OUT |

| P2                       | Input mode<br>Output mode            | -        | IN<br>OUT |

| P3                       | Input pin<br>Output pin              | -        | IN<br>OUT |

| P80 (INT0)<br>P81 (INT1) | Input pin<br>Input pin               | -        | IN*       |

| NMI<br>CLK<br>RESET      | Input pin<br>Output pin<br>Input pin | -        | "1"       |

| X1<br>X2                 | Input pin<br>Output pin              | <br>"1"  | _<br>"1"  |

- \*: Intermediate bias is still applied to this pin in the zero cross detect mode.

- Indicates that input mode/input pin cannot be used for input and that the output mode/output pin have been set to high impedance.

- IN: The input enable status.

- IN: The input gate is operating. Fix the input voltage at either "0" or "1" to prevent the pin floating.

- OUT: The output status.

It is necessary to leave INTO at "1" until the second bus cycle of the interrupt response sequence is completed, when the STOP mode is released by the level mode of INTO.

Table 3.4 (2) I/O Operation During Halt and How to Release the Halt Command

|           | Halt mode                      |           | RUN                           | IDLE2                 | IDLE1 | STOP              |  |  |

|-----------|--------------------------------|-----------|-------------------------------|-----------------------|-------|-------------------|--|--|

|           | WDMOD <haltm1, 0=""></haltm1,> |           |                               | 11                    | 10    | 01                |  |  |

|           | CPU                            |           | Halt                          |                       |       |                   |  |  |

|           | I/O port                       |           | Keeps the state when the halt | command was executed. |       | See Table 3.4 (1) |  |  |

|           | 8-bit timer                    |           |                               |                       |       |                   |  |  |

| Operation | 16-bit timer                   |           |                               |                       | Ц     | alt               |  |  |

| Block     | Stepping motor of              | ontroller | 0                             | ation                 | Halt  |                   |  |  |

|           | Serial interface               |           | Орег                          | ation                 |       |                   |  |  |

|           | Watchdog timer                 |           |                               |                       |       |                   |  |  |

|           | Interrupt controller           |           |                               |                       |       |                   |  |  |

|           |                                | NMI       | 0                             | 0                     | 0     | 0                 |  |  |

|           |                                | INTWD     | 0                             | 0                     | -     | -                 |  |  |

|           |                                | INT0      | 0                             | 0                     | 0     | 0                 |  |  |

|           |                                | INTT0     | 0                             | 0                     | _     | _                 |  |  |

| Halt      | Interrupt                      | INTT1     | 0                             | 0                     | _     | _                 |  |  |

| Releasing | ппстирі                        | INTT2     | 0                             | 0                     | _     | _                 |  |  |

| Source    |                                | INTT3     | 0                             | 0                     | _     | _                 |  |  |

|           |                                | INT1      | 0                             | 0                     | _     | _                 |  |  |

|           |                                | INTRX     | 0                             | 0                     | _     | _                 |  |  |

|           |                                | INTTX     | 0                             | 0                     | _     | _                 |  |  |

|           | RESET                          |           | 0                             | 0                     | 0     | 0                 |  |  |

O: Can be used to release the halt command.

<sup>-:</sup> Cannot be used to release the halt command.

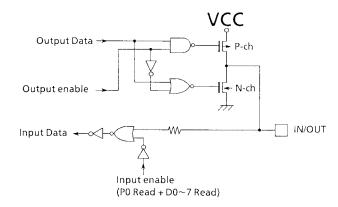

#### 3.5 Function of Ports

The TMP90C802 contains total 32 pins input/output ports. These ports function not only for the general-purpose I/O but

also for the input/output of the internal CPU and I/O. Table 3.5 describes the functions of these ports.

**Table 3.5 Functions of Ports**

| Port<br>name | Pin name                               | No. of pins           | Direction                                              | Direction<br>set unit | Resetting<br>Value                             | Pin name<br>for internal<br>function       |

|--------------|----------------------------------------|-----------------------|--------------------------------------------------------|-----------------------|------------------------------------------------|--------------------------------------------|

| Port 0       | P00 ~ P07                              | 8                     | 1/0                                                    | Byte                  | Input                                          | D0 ~ D7                                    |

| Port 1       | P10 ~ P17                              | 8                     | 1/0                                                    | Byte                  | Input                                          | A0 ~ A7                                    |

| Port 2       | P20 ~ P27                              | 8                     | 1/0                                                    | Bit                   | Input                                          | A8 ~ A15                                   |

| Port 3       | P31<br>P32<br>P33<br>P35<br>P36<br>P37 | 1<br>1<br>1<br>1<br>1 | Input<br>Output<br>Output<br>Output<br>Output<br>Input | -<br>-<br>-<br>-<br>- | Input Output Output Output Output Output Input | RxD<br>SCLK<br>TxD<br>RD<br>WR<br>WAIT/T01 |

| Port 8       | P80<br>P81                             | 1<br>1                | Input<br>Input                                         | -<br>-                | Input<br>Input                                 | INTO<br>INT1/TI2                           |

These port pins function as the general-purpose input/output ports by resetting. The port pins, for which input or output is programmably selectable, function as input ports by resetting.

A separate program is required to use them for an internal function.

- Port 0 always functions as data bus (D0 to D7)

- Port 0 always functions as address bus (A0 to A7)

- Port 0 always functions as address bus (A8 to A15)

- P35 and P36 of always functions as data RD and WR pins, respectively.

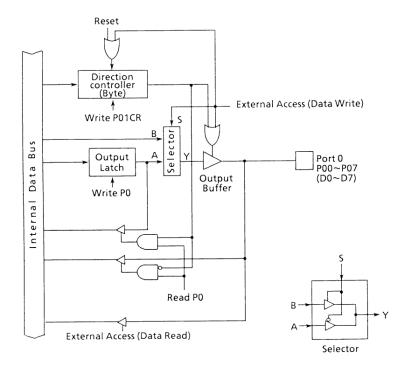

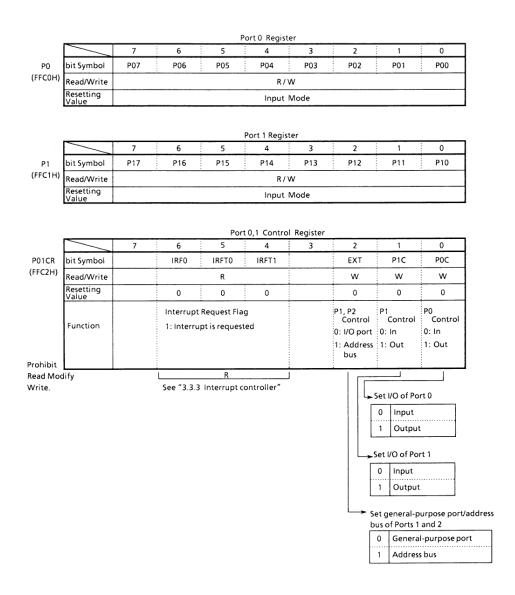

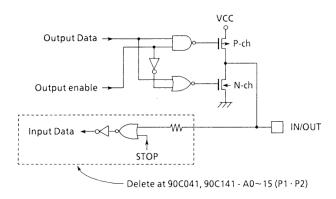

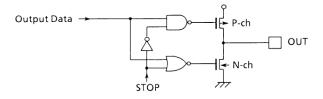

# 3.5.1 Port 0 (P00 ~ P07)

Port 0 is an 8-bit general-purpose I/O port P0 whose I/O function is specified by the control register P01CR <P0C> in byte. By resetting all bits of the control register are initialized to "0", whereby, Port 0 turns to the input mode, and the contents of

the output latch register are undefined.

In addition to the general-purpose I/O port function, it functions as a data bus (D0 ~ D7). Access of an external memory makes it automatically function as a data bus and <POC> are cleared to "0".

Figure 3.5 (1). Port 0

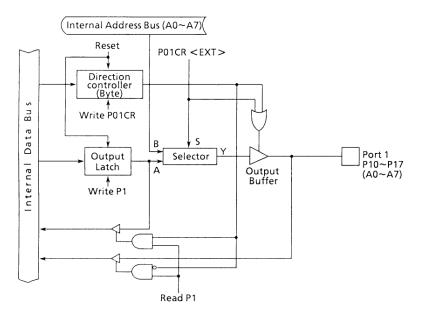

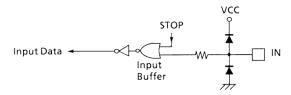

# 3.5.2 Port 1 (P10 ~ P17)

Port 1 is an 8-bit general-purpose I/O port P1 whose I/O function is specified by the control register P01CR<P1C> in byte. All bits of the output latch and the control register are initialized to "0" by resetting, whereby Port 1 is put in the input mode. In addition to the general-purpose I/O port function, it

functions as an address but (A0  $\sim$  A7). The address bus function can be selected by setting only the external extension control register P01CR<EXT> to "1" regardless of the status of the above control register <P1C>. The register <EXT> is reset to "0" whereby Port 1 and Port 2 turn to the general-purpose I/O mode.

Figure 3.5 (2). Port 1

Figure 3.5 (3). Registers for Port 0 and 1

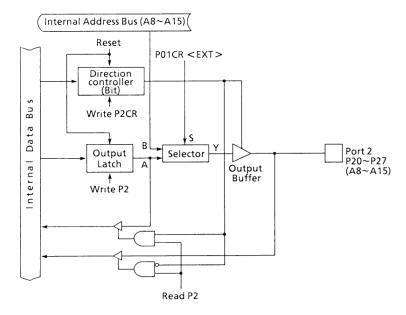

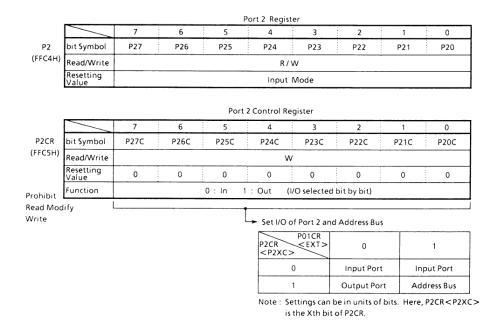

# 3.5.3 Port 2 (P20 ~ P27)

Port 2 is an 8-bit general-purpose I/O port P2 whose I/O functions are specified by the control register P2CR for each bit. All bits of the output latch and the control register are initialized to "0" by resetting, where by Port 2 turns to the input mode.

In addition to the general-purpose I/O port function, it

functions as an address bus (A8  $\sim$  A15). The address bus function can be selected by setting the register P01CR <EXT> (shared with port 1) to "1" and setting the Port 2 control register P2CR to the output mode. When the Port 2 control register P2CR is set to "0", Port 2 functions as an input port, regardless of the status of the <EXT> register.

Figure 3.5 (4). Port 2

Figure 3.5 (5). Registers for Port 2

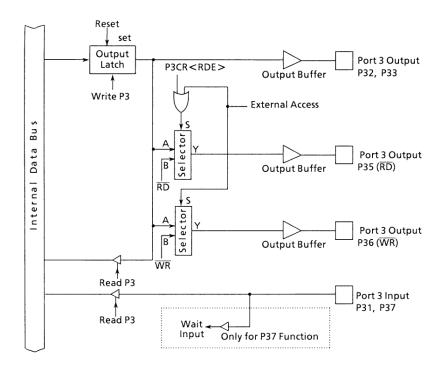

### 3.5.4 Port 3 (P30 ~ P33, P35 ~ P37)

Port 3 is an 6-bit general-purpose I/O port P3 with fixed I/O function. All bits of the output latch are initialized to "1" by resetting, and "High level" is generated to the output port.

In addition to the I/O port function, P31 ~ P31 have the I/O function for the internal serial interface, while P35 ~ P37 have the external memory control function. The additional functions can be selected by the control register P3CR. All bits of the control register are initialized by "0" by resetting, and the port turns to the general-purpose I/O Ports mode.

However, P37 is placed in the input mode after resetting, and turns to the TO1 output port mode after writing

P3C < WAIT1, 0 > = 1, 1.

Further, access of an external memory makes P35 and P36 automatically function as the memory control pins ( $\overline{RD}$  and  $\overline{WR}$ ), and access of an internal memory makes them function as general-purpose I/O ports.

When an external memory is accessed, therefore, the output latch registers P35 ( $\overline{\text{RD}}$ ) and P36 ( $\overline{\text{WR}}$ ) should be kept at "1" which is the initial value after the reset.

The P3CR <RDE> of the control register is intended for a pseudostatic RAM. When set to "1", it always functions as an RD pin. Therefore the RD pin outputs "0" (Enable) when it is an internal memory read and internal I/O read cycle.

Figure 3.5 (6). Port 3

Figure 3.5 (7). Register for Ports 3

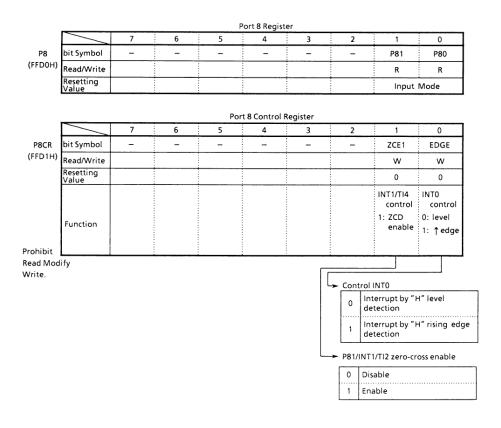

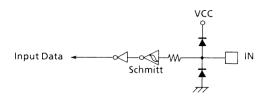

# 3.5.5 Port 8 (P80 ~ P81)

Port 8 is a 2-bit general-purpose INPUT port P8.

Port 8 also has the functions of interrupt request input, clock input for a timer/event counter.

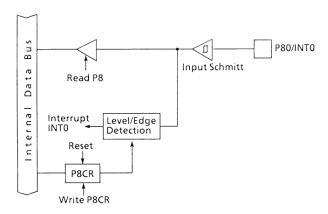

# (1) P80/INT0

P80 is a general-purpose input port, also used as the external interrupt request input pin INTO. INTO allows the selection of either an "H" level interrupt or rising edge interrupt by using the control register P8CR<EDGE>.

Figure 3.5 (8). Port P80/INT0

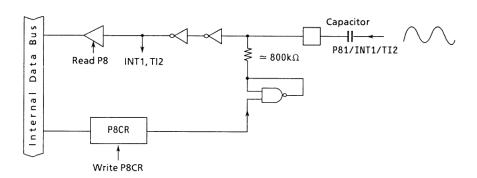

#### (2) P81/INT1/TI2

P81 is a general-purpose input port, also used as the external request input pin INT1 and the clock input pin Tl2 for the timer/event counter.

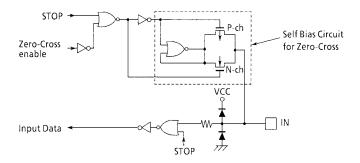

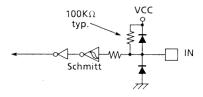

This port incorporates a zero-cross detection circuit, and enables zero-cross detection by connecting an external capacitor. The zero-cross detection can be disable/enabled by using the control register P8CT<ZCE1>. This control register is reset to "0", making the zero-cross detection disabled by resetting.

Figure 3.5 (9). Port 81/INT1/TI2

Figure 3.5 (10). Registers for Port 8

#### 3.6 Timers

The TMP90C802A incorporates four 8-bit timers.

The four 8-bit timers can be operated independently, and can also be functioned as two 16-bit timer by mode setting: Timer 2 has an event counter function, so that it can also be used as an 8-bit counter. Furthermore, it can be used as a 16-bit counter cascaded with Timer 3.

- 8-bit interval timer mode (4 timers)

- 16-bit interval timer mode (2 timers)

- 8-bit programmable pulse generation (PPG) output mode (Timer 0 and Timer 1)

- 8-bit PWM output mode (Timer 1) Possible arrangements:

8-bit x 2 and 16-bit x 1

- 8-bit event counter mode (Timer 2)

- 16-bit event counter mode (Timer 2 and Timer 3)

- Software counter latch function (Timer 2 and Timer 3)

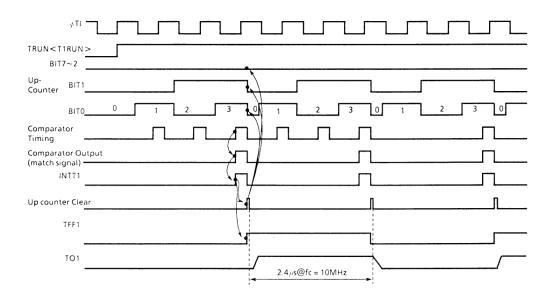

#### 3.6.1 8-bit Timers

The TMP90C802A incorporates four 8-bit interval timers (Timers 0, 1, 2 and 3), each of which can be operated independently. The cascade connection of Timer 0 and 1, or Timer 2 and 3 allows these timers used as 16-bit internal timers.

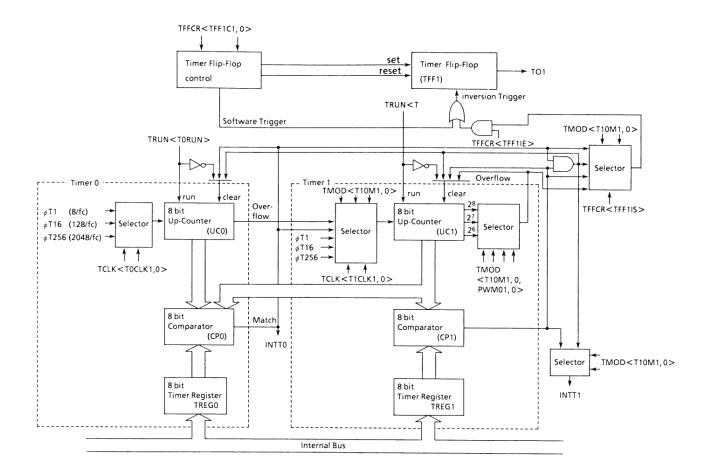

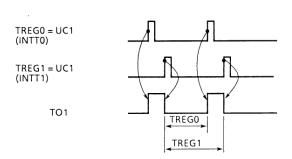

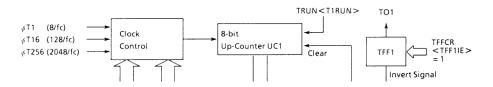

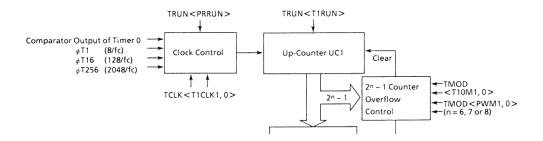

Figure 3.6 (1) is a block diagram of the 8-bit timers (Timer 0 and Timer 1).

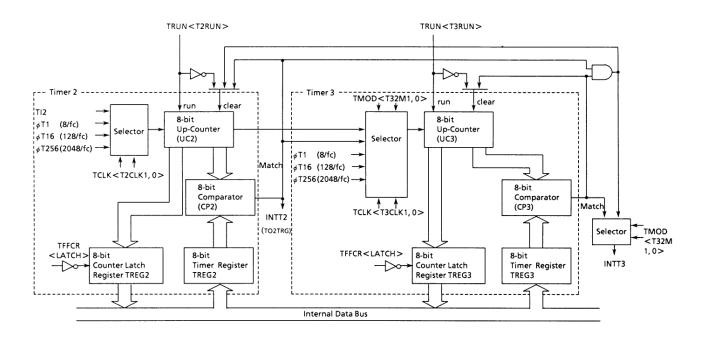

Figure 3.6 (2) is a block diagram of the 8-bit timer/event counters (Timer 2 and Timer 3).

Each interval timer is composed of an 8-bit up-counter, an 8-bit comparator and an 8-bit timer register, with a Timer Flipflop (TFF1) provided to each pair of Timer 0/1.

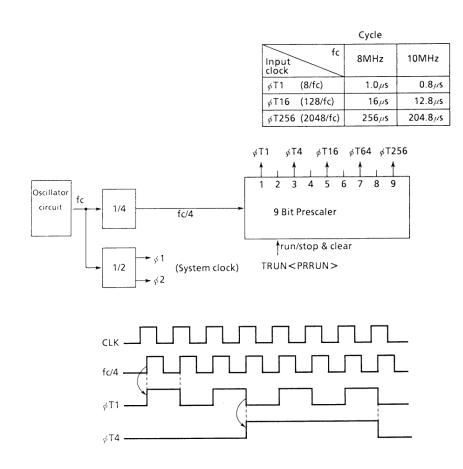

Internal clocks (øT1, øT16 and øT256), some of the input clock sources for the interval timers, are generated by the 9-bit prescaler shown in Figure 3.6 (3).

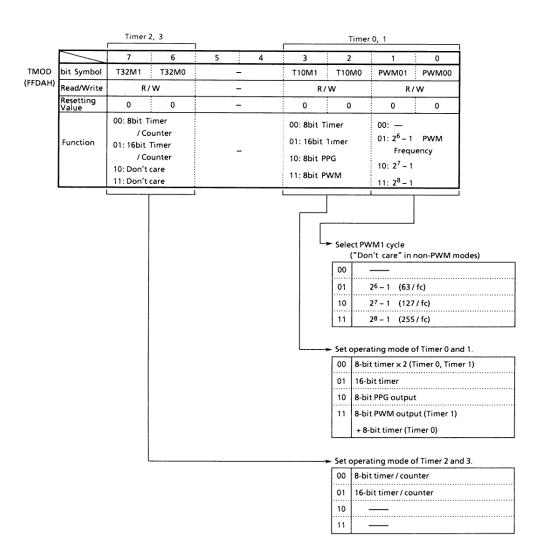

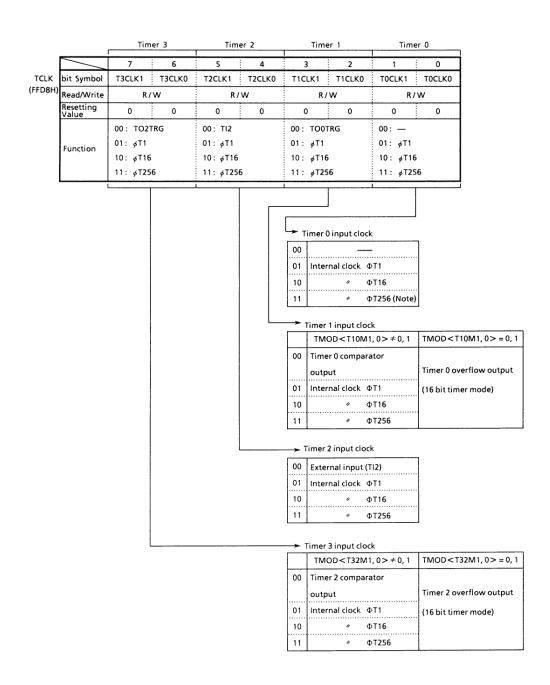

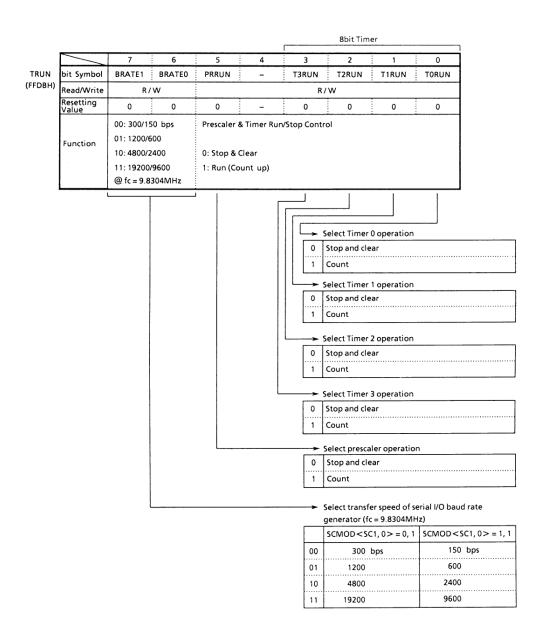

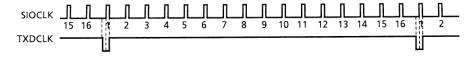

Their operating modes of the 8-bit timers and flip-flops are controlled by four control registers (TCLK, TFFCR, TMOD and TRUN).

Figure 3.6 (1). Block Diagram of 8-bit Timers (Timer 0 and 1)

Figure 3.6 (2). Block Diagram of 8-bit Timer/Counter (Timer 2 and Timer 3)

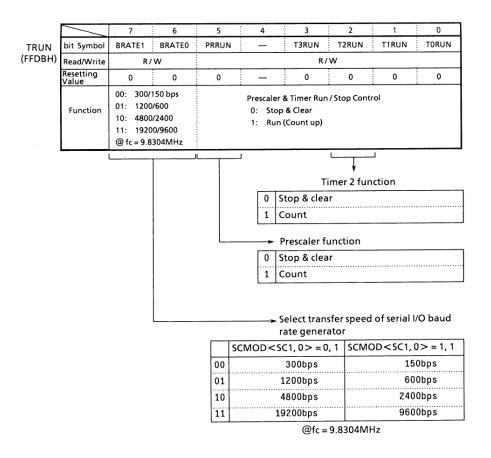

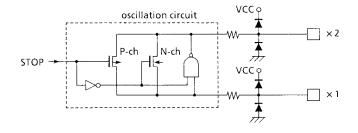

#### ① Prescaler

An 9-bit prescaler is provided to further devide the clock frequency already divided to a 1/4 of the frequency of the source clock (fc).

It generates an input clock pulse for the 8-bit timers, 16-bit timer/event counter, the baud-rate generator, etc.

For the 8-bit timers, three types of clock are generated ( $\phi$ T1,  $\phi$ T16 and  $\phi$ T256).

The prescaler can be run or stopped by using the 5th bit TRUN <PRRUN> of the timer control register TRUN. Setting <PRRUN> to "1" makes the prescaler count, and setting it to "0" clears the prescaler to stop.

By resetting, <PRRUN> is initialized to "0", making the prescaler clear and stop.

Figure 3.6 (3). Prescaler

#### 2 Up-counter

This is an 8-bit binary counter that counts up by an input clock pulse specified by an 8-bit timer clock control register TCLK and an 8-bit timer mode register (TMOD).

The input clock pulse for Timer 0 and 2 is selected from  $\emptyset$ T1,  $\emptyset$ T16 and  $\emptyset$ T256 according to the setting of the TCLK register. When using Timer 2 as the counter, set bit 4 and bit 5 of TCLK to "0".

Example: When setting TCLK <TOCLK1, 0> = 0,1, ØT1 is selected as the input clock pulse for Timer 0.

The input clock pulse to Timer 1 and 3 is selected according to the operating mode. In the 16-bit timer mode, the overflow output of Timer 0 and 2 is automatically selected as the input clock pulse, regardless of the setting of the TCLK register.

In the other operating modes, the clock pulse is selected among the internal clocks øT1, øT16 and øT256, and the output

of the Timer 0 and 2 comparator (match signal).

Example: If TMOD <T10M1, 0> = 0, 1, the overflow output of Timer 0 is selected as the input clock to Timer 1. (16 bit timer mode)

If TMOD <T10M10> = 0, 0 and TCLK <T1CLK1, 0> = 0, 1,  $\emptyset$ T1 is selected as the input clock to Timer 1. (8-bit timer mode)

The operating mode is selected by the TMOD register. This register is initialized to TMOD <T10M1, 0> = 0, 0/TMOD <T32M1, 0> = 0, 0 by resetting, whereby the up-counter is place in the 8-bit timer mode.

Functions, count, stop or clear of the up-counter can be controlled for each interval timer by the timer control register TRUN.

By resetting, all up-counters are cleared to stop the timers.

Figure 3.6 (4). 8-bit Timer Mode Register TMOD

Figure 3.6 (5). 8-bit Timer Clock Control Register TCLK

Figure 3.6 (6). Timer/Serial Channel Control Registers TRUN

Figure 3.6 (7). 8-bit Timer Flip-Flop Control Register (TFFCR)

#### 3 Timer registers

Note: Only for writing.

8-bit registers are provided to set the interval time. When the set value of a timer register matches that of an up-counter, the match signal of their comparators turn to the active mode. If "00H" is set, this signal becomes active when the up-counter overflows.

The values of the timer register 0 and timer register 1 cannot be read. The values of the timer register 2 and timer register 3, however, can be read because these registers are assigned same address with the counter latch registers. When the values of these registers are read, they become the values of the counter latch registers (Read only registers). When the values of these registers are written, they become the values of the values of the values of the values of the timer registers (Write only register).

# 4 Comparators

A comparator compares the values in an up-counter and a timer register. When they matches, the up-counter is cleared to "0", and an interrupt signal (INTTn) is generated. If the Timer Flip-flop inversion is enabled by the Timer Flip-flop control register, the Timer Flip-flop is inverted.

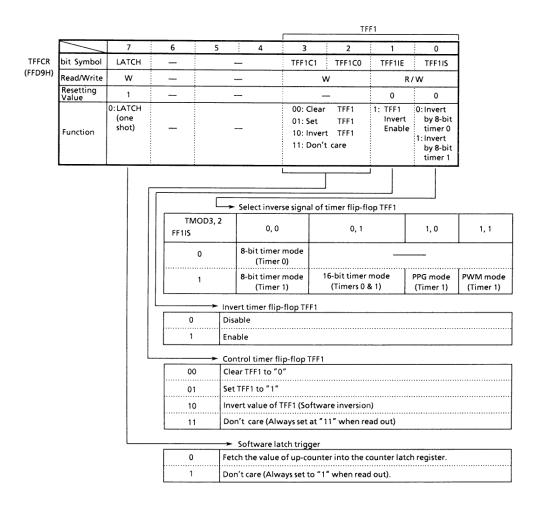

#### **5** Timer Flip-flop (Timer F/F)

The status of the Timer Flip-flop is inverted by the match signal (output by comparator) of each interval timer. Its status can be output to the timer output pin TO1 (also used as P37).

This Timer F/F is provided to the timer pair, Timer 0 - Timer 1 is called TFF1. The status of TFF1 is output to TO1.

The Timer F/F are controlled by a Timer Flip-flop control register (TFFCR).

• TFFCR<FF1IS> is a timer selection bit for inversion of TFF1. In the 8-bit timer mode, inversion is enabled by the match signal from Timer 0 if this bit is set to "0", or by the signal from Timer 1 is set to "1".

In any other mode, <FF1IS> must be always set to "1". It is initialized to "0" by resetting.

• TFFCR <FF1IE> controls the inversion of TFF1. Setting this bit to "1" enables the inversion and setting it to "0" disable.

<FF1IE> is initialized to "0" by resetting.

The bits TFFCR are used to set/reset TFF1 or enable its inversion by software. TFF1 is reset by writing "0, 0", set by "0, 1" and inverted by "1, 0".

The 8-bit timers operate as follows:

#### (1) 8-bit Timer Mode

The four interval timers, Timer 0, Timer 1, Timer 2 and Timer 3 can operate independently as an 8-bit interval timer. Only the operation of Timer 1 is described because their operations are the same.

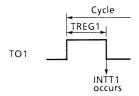

#### ① Generating interrupts at specified intervals

Periodic interrupts can be generated by using Timer 1 (INTT1) in the following procedure: Stop Timer 1, set the desired operating mode, input clock and cycle time in, the registers TMOD, TCLK and TREG1 enable INTT1, and start the counting of Timer 1.

Example: To generate Timer 1 interrupt every  $4.0\mu s$  at fc = 10MHz, the registers should be set as follows:

```

MSB

LSB

7 6 5 4 3 2 1 0

TRUN

- - - 0 -

Stop Timer 1, and clear it to "0".

TMOD ←

- 0 0 X X

Set the 8-bit timer mode.

- - 0 1 - -

Select \phi T1 (0.8\mus @fc = 10 MHz) as the input clock.

TREG1 ←

0 0 1 1 0 0 1 0

Set the timer register at 40\mu\text{s}/\phi\text{T1} = 32\text{H}.

INTEH ←

Enable INTT1.

TRUN ←

Start Timer 1.

```

(Note) X: Don't care -: No change

Use the following table for selecting the input clock:

Table 3.6 (1) 8-bit timer interrupt cycle and input clock

| Interrupt cycle<br>@fc = 10MHz | Resolution | Input clock     |

|--------------------------------|------------|-----------------|

| 0.8µs ~ 204µs                  | 0.8µs      | øT1 (8/fc)      |

| 12.8µs ~ 3.264ms               | 12.8µs     | øT16 (128/fc)   |

| 204.8μs ~ 52.429ms             | 204.8µs    | øT256 (2048/fc) |

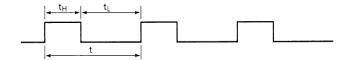

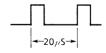

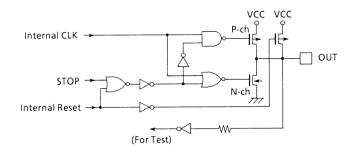

# ② Generating pulse at 50% duty

The Timer Flip-flop is inverted at specified intervals, and its status is output to a timer output pin TO1 (only Timer 0, Timer 1).

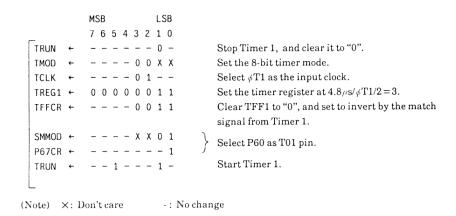

Example: To output pulse from TO1 at fc = 10MHz every  $4.8\mu s$ , the registers should be set as follows:

This example uses Timer 1, but the same operation can be effected by using Timer 0.

Figure 3.6 (8). Pulse Output (50% duty) Timing Chart

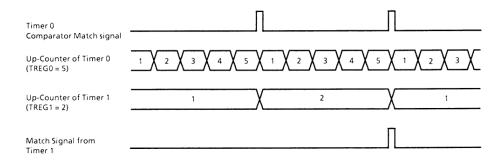

# Making Timer 1 count up by match signal from Timer 0 comparator.

Select the 8-bit timer mode, and set the comparator output of Timer 0 as the input clock to Timer 1.

Figure 3.6 (9)

#### 4 Software inversion

The Timer Flip-flops can be inverted by software independent of the timer operation.

Writing "1, 0" into the bits TFFCR <TFF1C1, 0> inverts TFF1.

#### ⑤ Initial setting of Timer Flip-flops

The Timer Flip-flops can be initialized to either "0" or "1" without regard to the timer operation.

TFF1 is initialized to "0" by writing "0, 0" into TFFCR <TFF1C1, 0>, and "1" by writing "0, 1" into these bits

Note: Reading the data from the Timer Flip-flops and timer registers is prohibited.

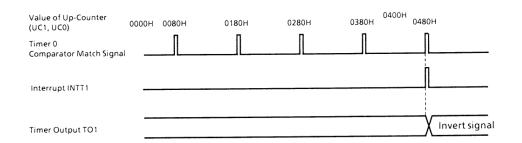

# (2) 16-bit Timer Mode

The Timer 0 and Timer 1 or Timer 2 and Timer 3 can be used as one 16-bit interval timer.

Only operation of Timer 0 and Timer 1 is described in this section since the operation of Timer 2 and Timer 3 is identical with that of Timer 0 and Timer 1 except a pair of Timer 2 and 3 does not have Timer Output function. Cascade connection of Timer 0 and Timer 1 to use them as a 16-bit interval timer requires to set the <T10M1, 0> of the mode register TMOD to "0, 1".

By selecting the 16-bit timer mode, the overflow output of Timer 0 is automatically selected as the input clock to Timer 1, regardless of the set value of the clock control register TCLK. The input clock to Timer 0 is selected by TCLK. Table 3.6 (2) shows the combinations of timer (interrupt) cycle and input clock.

# Table 3.6 (2) 16-bit Timer (Interrupt) Cycle and Input Clock

| Timer (interrupt) cycle<br>@fc = 10MHz | Resolution | Input clock to<br>Timer O |

|----------------------------------------|------------|---------------------------|

| 0.8 <b>µs</b> ~ 52.43ms                | 0.8µs      | øT1 (8/fc)                |

| 12.8µs ~ 838.86ms                      | 12.8µs     | øT16 (128/fc)             |

| 204.8μs ~ 13.42s                       | 204.8µs    | øT256 (256/fc)            |

TOSHIBA CORPORATION 43/86

The lower eight bits of the timer (interrupt) cycle is set by TREG0 and the upper eight bits of that is set by TREG1. Note that TREG0 must be always set first (Writing data into TREG0 disables the comparator temporarily, which is restarted by writing data into TREG1).

Example: To generate interrupts INTT1 at fc = 8MHz every 1 second, the timer registers TREG0 and TREG1 should be set as follows:

As  $\emptyset$ T16 (= 16 $\mu$ s @ 8MHz) is selected as the input clock, 1 sec/16 $\mu$ s = 62500 = F424H

Therefore, TREG1 = F4H TREG0 = 24H

The match signal is generated by Timer 0 comparator each time the up-counter UC0 matches TREG0. In this case, the up-counter UCO is not cleared, but the interrupt INTT0 is generated.

Timer 1 comparator also generates the match signal each timer the up-counter UC1 match TREG1. When the match signal is generated simultaneously from comparators of Timer 0 and Timer 1, the up-counters UC0 and UC1 are cleared to "0", and the interrupt INTT1 is generated. If the Timer Flip-flop inversion is enabled by the Timer Flip-flop control register, the Timer Flip-flop TFF1 is inverted at the same time.

|                                                                  |                         | Timer 0                                                             |                                            |                         | Timer 1                                                        |                                                                                          |

|------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------|--------------------------------------------|-------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------|

|                                                                  | INTTO                   | T01                                                                 | match                                      | INTT1                   | T01                                                            | match                                                                                    |

| 16-bit Timer Mode<br>(Count-up Timer 1 by<br>verflow of TImer 0) | Interrupt is generated. | Can't output<br>(TO1 can't be output<br>the matching with<br>TREGO) | TREGO<br>(Continue counting<br>when match) | Interrupt is generated. | Can output *Can output the matching with both TREG0 and TREG1) | TREG1 * 2 <sup>8</sup> + TREG0 (16 bit)<br>(Cleared by<br>matching with both registers.) |

| 8-bit Timer Mode<br>(Count-up Timer 1 by<br>matching of Timer 0) | Interrupt is generated. | Can output<br>(Timer 0 or Timer 1)                                  | TREGO<br>(Clear when match)                | Interrupt is generated. | Can output<br>(Timer 0 or Timer 1)                             | TREG1*TREG0<br>(Multiplied Valve)<br>(Cleared by matching)                               |

Example: Given TREG1 = 04H and TREG0 = 80H,

Figure 3.6 (10)

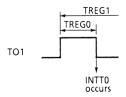

(3) 8-bit PPG (Programmable Pulse Generation) Mode

Pulse can be generated at any frequency and duty rate by Timer 1 or Timer 3. The output pulse may be either low-or high-active. In this mode, Timers 0 cannot be used. Pulse is output to TO1 (shared with P37).

# Following is the timing of Timer 1

In the 8-bit PPG mode, programmable pulse is generated by the inversion of the timer output put each time the 8 bit upcounter 1 (UC1) matches the timer register TREG0 or TREG1.

Note that the set value of TREG0 must be smaller than that of TREG1.

In this mode, the up-counter UC0 of Timer 0 cannot be used (Set TRUN < TORUN> = 1, and count the Timer 0).

The block diagram of the PPG mode can be illustrated as follows:

# Figure 3.6 (11). Block Diagram of 8-bit PPG Mode

Example: Generate pulse at 50kHz and 1/4 duty rate (@fc = 8MHz)

• Calculate the set value of the timer registers.

To obtain the frequency of 50kHz, the pulse cycle should be:  $1/50kHz = 20\mu s$ .

Given  $\varphi T1 = 1\mu s$  (@ 8MHz),

$20\mu s/1\mu s = 20$

Consequently, the timer register 1 (TREG1) should be set to 20 =14H.

Given a 1/4 duty, t x 1/4 = 20 x  $1/4 = 5\mu$ s

$5\mu s/1\mu s = 5$

As a result, the timer register 0 (TREG0) should be set to 5 = 05H.

```

Stop Timer 0 and Timer 1, and clear them to "0".

TRUN ← - - - - - 0 0

Select &T1 as the input clock.

TCLK ← - - - - 0 1 x x

Set 8-bit PPG mode.

← - - - - 1 0 x x

Set the output "H", and enable the inversion by Timer 1.

Writing "00" provides negative logic pulse

Write "5H".

TREG0 ← 0 0 0 0 0 1 0 1

Write "14H".

TREG1 \leftarrow 0 0 0 1 0 1 0 0

SMMOD \leftarrow - - - x x 0 1

Select P60 as the T01 pin.

P67CR ← - - - - - 1

Start Timer 1.

```

#### **Precautions for PPG Output**

By rewriting the content of the TREG (timer register), it is possible to make TMP90C802 output PPG. However, be careful, since the timing to rewrite TREG differs depending on the pulse width of PPG to be set. This problem is explained below by an example.

Example: To output PPG through 8 bit timers 0 and 1

TREG0: Pulse width TREG1: Cycle

The pulse width is normally changed by the interrupt (INTT1) process routine in each cycle. However, when the pulse width to be set (the value to be written in TREG0) is small, trouble may occur, in that the timer counter exceeds the value of TREG0 before the interrupt process routine is set. Therefore, it is recommended to make the following decisions in INTT0 and INTT1 interrupt processes.

INTTO process routine: The value of TREGO is rewritten

only when the value to be written in TREG0 is smaller than the

current value of TREGO.

INTT1 process routine: On the contrary to INTT0, TREG0 is written only when the value to

be written in TREGO is larger than the current value of TREGO.

TMP90C802 cannot read the content of TREG, so it is necessary to buffer the content of TREG in a RAM (or the like)

for making the above judgement.

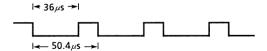

4) 8-bit PWM (pulse width modulation) Mode

This mode is only available for Timer 1 and can output 8-bit resolution PWM. It is output to TO1 (also used as P37). Timer 0 can be used as 8-bit timers.

The inversion of the timer output occurs when the up-counter (UC1) matches the set value of the timer register TREG1, as well as when an overflow of  $2^n$  - 1 (n = 6, 7 or 8 selected by TMOD <PWM01, 00> occurred at the counter. The up-counter UC1 is cleared by the occurrence of an overflow of  $2^n$  - 1. For example, 6 bit PWM is selected when n = 6, and 7-bit PWM is selected when n = 7.

The following condition must be obtained in the PWM mode:

(Set value of timer register) < (set overflow value of  $2^n$  - 1 counter)

(Set value of timer register)  $\neq 0$

Match signal from comparator (INTT1)

2<sup>n</sup> – 1 Overflow

TO1

The PWM mode can be illustrated as follows:

# Figure 3.6 (12). Block Diagram of 8-bit PWM Mode

Example: Generate the following PWM to the TO1 pin at fc = 10MHz.

Assuming the PWM cycle is  $50.4\mu s$  when  $\phi T1 = 0.8\mu s$  and  $\phi C1 = 10 MHz$ ,  $50.4\mu s/0.8\mu s = 63 = 2^6 - 1 Consequently, n should be set at 6 (TMOD1<PWM01, <math>00>=0$ , 1).

Given the "L" level period of  $36\mu s$ , setting  $\phi T1 = 0.8\mu s$

results:  $36\mu s/0.8\mu s = 45 = 2DH$

As result, TREG1 should be set at 2DH.

(Note): X: Don't care -: No change

# Table 3.6 (3) PWM Cycle and Selection of 2<sup>n</sup> - 1 counter

|                    |                            |               | PWM cycle (@fc = 10Mhz) |                    |

|--------------------|----------------------------|---------------|-------------------------|--------------------|

|                    | Expression                 | øT1<br>(8/fc) | øT16<br>(128/fc)        | øT256<br>(2048/fc) |

| 2 <sup>6</sup> - 1 | (2 <sup>6</sup> - 1) x øTn | 50.4µs        | 8064µs                  | 12.9ms             |

| 2 <sup>7</sup> - 1 | (2 <sup>7</sup> - 1) x øTn | 101.6µs       | 1625.6µs                | 26.0ms             |

| 2 <sup>8</sup> - 1 | (2 <sup>8</sup> - 1) x øTn | 204.0µs       | 3264.0µs                | 52.2ms             |

# **Precautions for PWM output**

TMP90C802 can output PWM by the 8-bit timer. However, changing the pulse width of PWM requires special care. This problem is explained by the following example.

Example: To output PWM by 8-bit timer

TREG1: Pulse width

Cycle: Flxed  $(2^6 - 1, 2^7 - 1, 2^8 - 1)$

TOSHIBA CORPORATION 49/86

In the PWM mode, INTT1 occurs at the coincidence with TREG1. However, the pulse width cannot be changed directly using the interrupt. (Depending on the value of TREG1 to be set, coincidence with TREG1 may be detected again in a single cycle, inverting the timer output.)

To eliminate this problem in changing the pulse width, it is effective the halt the timer with the INTT1 process, modify the value of TREG1, set the timer output to "1", and restart the timer. In the mean time, the output waveform loses shape when the pulse width is changed. This method is valid for a system that allows a deformed output waveform.

(5) A Table of All Timer Mode

# Table 3.6 (4) Timer Mode

| Register          | TMOD        |             | TCLK          |                              | TFFCR            |

|-------------------|-------------|-------------|---------------|------------------------------|------------------|

| bit Symbol        | T10M (T32M) | PWM1 (PWM1) | T1CLK (T3CLK) | TOCLK (T2CLK)                | FF1IS (FF1IS)    |

| Function          | Timer mode  | PWM cycle   | Upper input   | Lower input                  | Inversion select |

| 16-bit Timer mode | 01          | -           | -             | øT1, 16, 256<br>(01, 10, 11) | 1(*)             |

#### Table 3.6 (4) Timer Mode

Table 3.6 (4) Timer

| Register          | Т           | MOD                                                                        | Register TC                                                                        | CLK                          | TMOD TFFCR                       |     |

|-------------------|-------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------|----------------------------------|-----|

| bit Symbol        | T10M (T32M) | PWM1 (PWM1)                                                                | T1CLIKit(183)(01116)                                                               | TOCLIO(MZCBKM)               | FIPMSV(FI(PMS)V11)               | T10 |

| Function          | Timer mode  | PWM cycle                                                                  | Upp <b>€</b> ai <b>rcþid</b> n                                                     | Lowieneinprode               | Inver®1M/Mseyebt                 | U   |

| 8-bit Timer x 2ch | 00          | Table 3.6 (4)                                                              | Comparator output<br>8-bit P G X 1ch<br>From Wer Timer,<br>Timer, Mede<br>T M 6 de | øT1, 16, 256<br>(01, 10, 11) | 0: Lower timer<br>1: Upper timer | ķ   |

| Register          | Т           | MOD                                                                        | (00 01 10 11)                                                                      | LK                           | TFFCR                            |     |