## **TPPM0302** 400-mA LOW-DROPOUT REGULATOR WITH AUXILIARY POWER MANAGEMENT AND POK

SLVS316 - NOVEMBER 2000

- **Automatic Input Voltage Source Selection**

- **Glitch-Free Regulated Output**

- 5-V Input Voltage Source Detector With **Hysteresis**

- 400-mA Load Current Capability With 5-V or 3.3-V Input Source

- **Power OK Feature Based on Voltage** Supervisor of 3.3VOUT

- Low r<sub>DS(on)</sub> Auxiliary Switch

- Thermally Enhanced PowerPAD™ **Packaging Concept for Efficient Heat** Management

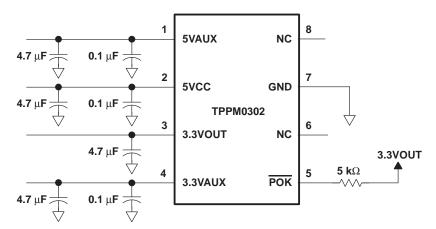

#### **DGN PACKAGE** (TOP VIEW) 5VAUX [ oxdot NC 5VCC [ ☐ GND 2 7 3.3VOUT [ 3 6 NC POK 3.3VAUX [ 5

NC - No connect

### description

The TPPM0302 is a low-dropout regulator with auxiliary power management that provides a constant 3.3-V supply at the output capable of driving a 400-mA load.

The TPPM0302 provides a regulated power output for systems that have multiple input sources and require a constant voltage source with a low-dropout voltage. This is a single output, multiple input, intelligent power source selection device with a low-dropout regulator for either 5VCC or 5VAUX inputs, and a low-resistance bypass switch for the 3.3VAUX input.

Transitions may occur from one input supply to another without generating a glitch, outside of the specification range, on the 3.3-V output. The device has an incorporated reverse blocking scheme to prevent excess leakage from the input terminals in the event that the output voltage is greater than the input voltage. The output voltage is continually monitored for constant output, and any deviation from the internal set limit (≈2.8 V) is reported by a low signal on the POK output.

The input voltage is prioritized in the following order: 5VCC, 5VAUX, and 3.3VAUX.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

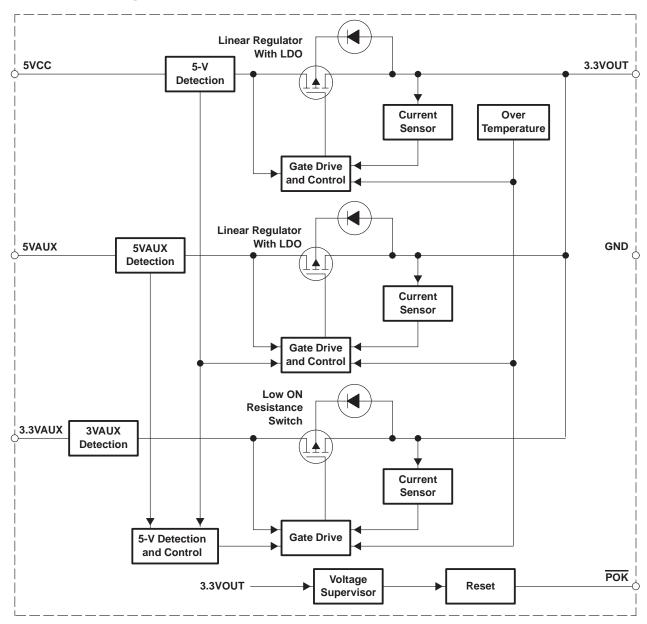

## functional block diagram

### **Terminal Functions**

| TERMI   | NAL  | 1/0 | DESCRIPTION                                            |

|---------|------|-----|--------------------------------------------------------|

| NAME    | NO.  | "0  | DESCRIPTION                                            |

| 3.3VAUX | 4    | ı   | 3.3-V auxiliary input                                  |

| 3.3VOUT | 3    | 0   | 3.3-V output with a typical capacitance load of 4.7 μF |

| 5VAUX   | 1    | ı   | 5-V auxiliary input                                    |

| 5VCC    | 2    | ı   | 5-V main input                                         |

| GND     | 7    | ı   | Ground                                                 |

| NC      | 6, 8 | I   | No internal connection                                 |

| POK     | 5    | 0   | Power OK                                               |

#### **Table 1. Input Selection**

| INPUT | VOLTAGI<br>(V) | E STATUS | INPUT SELECTED     | OUTPUT<br>(V) | OUTPUT<br>(I) |

|-------|----------------|----------|--------------------|---------------|---------------|

| 5VCC  | 5VAUX          | 3.3VAUX  | 5VCC/5VAUX/3.3VAUX | 3.3VOUT       | IL (mA)       |

| 0     | 0              | 0        | None               | 0             | 0             |

| 0     | 0              | 3.3      | 3.3VAUX            | 3.3           | 375           |

| 0     | 5              | 0        | 5VAUX              | 3.3           | 400           |

| 0     | 5              | 3.3      | 5VAUX              | 3.3           | 400           |

| 5     | 0              | 0        | 5VCC               | 3.3           | 400           |

| 5     | 0              | 3.3      | 5VCC               | 3.3           | 400           |

| 5     | 5              | 0        | 5VCC               | 3.3           | 400           |

| 5     | 5              | 3.3      | 5VCC               | 3.3           | 400           |

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage, 5-V main input, V <sub>(5VCC)</sub> (see Notes 1 and 2)         | 7 V            |

|---------------------------------------------------------------------------------|----------------|

| Auxiliary voltage, 5-V input, V <sub>(5VAUX)</sub> (see Notes 1 and 2)          | 7 V            |

| Auxiliary voltage, 3.3-V input, $V_{(3.3VAUX)}$ (see Notes 1 and 2)             | 5 V            |

| 3.3-V output current limit, I <sub>(LIMIT)</sub>                                | 1.5 A          |

| Continuous power dissipation, P <sub>D</sub> (see Note 3)                       | 1.36 W         |

| Electrostatic discharge susceptibility, human body model, V <sub>(HBMESD)</sub> | 2 kV           |

| Operating ambient temperature range, T <sub>A</sub>                             |                |

| Storage temperature range, T <sub>stq</sub>                                     | –55°C to 150°C |

| Operating junction temperature range, T <sub>J</sub>                            |                |

| Lead temperature (soldering, 10 second), T <sub>(LEAD)</sub>                    | 260°C          |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All voltage values are with respect to GND.

- 2. Absolute negative voltage on these terminal should not be below -0.5 V.

- 3. Refer to the Thermal Information Section.

#### recommended operating conditions

|                                               | MIN  | TYP | MAX  | UNIT |

|-----------------------------------------------|------|-----|------|------|

| 5-V main input, V <sub>(5VCC)</sub>           | 4.5  |     | 5.5  | V    |

| 5-V auxiliary input, V <sub>(5VAUX)</sub>     | 4.5  |     | 5.5  | V    |

| 3.3-V auxiliary input, V <sub>(3.3VAUX)</sub> | 3    |     | 3.6  | V    |

| Load capacitance, C <sub>L</sub>              | 4.23 | 4.7 | 5.17 | μF   |

| Load current, IL                              | 0    |     | 400  | mA   |

| Ambient temperature, T <sub>A</sub>           | 0    |     | 70   | °C   |

## **TPPM0302** 400-mA LOW-DROPOUT REGULATOR WITH AUXILIARY POWER MANAGEMENT AND POK

SLVS316 - NOVEMBER 2000

## electrical characteristics over recommended operating free-air temperature range, $T_A = 0$ °C to 70°C, $C_L$ = 4.7 $\mu F$ (unless otherwise noted)

|                                  | PARAMETER                      | TEST CONDITIONS                                                                      | MIN   | TYP | MAX   | UNIT |

|----------------------------------|--------------------------------|--------------------------------------------------------------------------------------|-------|-----|-------|------|

| V(5VCC) <sup>/</sup><br>V(5VAUX) | 5-V inputs                     |                                                                                      | 4.5   | 5   | 5.5   | ٧    |

| l.s.                             | Outageant aupply aurrent       | From 5VCC or 5VAUX terminals, I <sub>L</sub> = 0 mA to 400 mA                        |       | 2.5 | 5     | mA   |

| <sup>1</sup> (Q)                 | Quiescent supply current       | From 3.3VAUX terminal, I <sub>L</sub> = 0 A                                          |       | 250 | 500   | μΑ   |

| IL                               | Output load current            |                                                                                      | 0.4   |     |       | Α    |

| I <sub>(LIMIT)</sub>             | Output current limit           | 3.3VOUT = 0 V                                                                        |       | 1   | 1.5   | Α    |

| T <sub>(TSD)</sub> †             | Thermal shutdown               | 2.2VOLT subsuit shorted to 0.V                                                       | 150   |     | 180   | °C   |

| T <sub>hys</sub> †               | Thermal hysteresis             | 3.3VOUT output shorted to 0 V                                                        |       | 15  |       | -0   |

| V(3.3VOUT)                       | 3.3-V output                   | I <sub>L</sub> = 400 mA                                                              | 3.135 | 3.3 | 3.465 | V    |

| CL                               | Load capacitance               | Minimal ESR to insure stability of regulated output                                  |       | 4.7 |       | μF   |

| I <sub>lkg(REV)</sub>            | Reverse leakage output current | Tested for input that is grounded.<br>3.3VAUX, 5VAUX, or 5VCC = GND, 3.3VOUT = 3.3 V |       |     | 50    | μА   |

<sup>†</sup> Design targets only. Not tested in production.

#### 5-V detect

|                      | PARAMETER               | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|----------------------|-------------------------|-----------------|------|------|------|------|

| V(TO_LO)             | Threshold voltage, low  | 5VAUX or 5VCC↓  | 3.85 | 4.05 | 4.25 | V    |

| V <sub>(TO_HI)</sub> | Threshold voltage, high | 5VAUX or 5VCC↑  | 4.1  | 4.3  | 4.5  | V    |

#### auxiliary switch

|                                 | PARAMETER                   | TEST CONDITIONS                                  | MIN | TYP | MAX | UNIT |

|---------------------------------|-----------------------------|--------------------------------------------------|-----|-----|-----|------|

| R(SWITCH)                       | Auxiliary switch resistance | 5VAUX = 5VCC = 0 V, 3.3VAUX = 3.3 V, IL = 150 mA |     |     | 0.4 | Ω    |

| $\Delta V_{O(\Delta VI)}$       | Line regulation voltage     | 5VAUX or 5VCC = 4.5 V to 5.5 V                   |     | 2   |     | mV   |

| ΔV <sub>O</sub> (ΔIO)           | Load regulation voltage     | 20 mA < I <sub>L</sub> < 400 mA                  |     | 40  |     | mV   |

| V <sub>I</sub> – V <sub>O</sub> | Dropout voltage             | I <sub>L</sub> < 400 mA                          |     |     | 1   | V    |

## Power OK (POK)

|           | PARAMETER             | TEST CONDITIONS                                                                | MIN  | TYP | MAX  | UNIT |

|-----------|-----------------------|--------------------------------------------------------------------------------|------|-----|------|------|

| V(TO_POK) | POK threshold voltage |                                                                                | 2.67 | 2.8 | 2.93 | W    |

| VOL       | Output low voltage    | 3.3VOUT = 0 $\rightarrow$ 3.3 V and starts $\overline{\text{POK}}$ delay timer |      |     | 0.4  | V    |

| IOH       | Output high current   |                                                                                |      |     | 200  | μΑ   |

| VOH       | Output high voltage   | 5K pullup to 3.3VOUT                                                           |      | 3.3 |      | V    |

# timing characteristics, T\_A = 0°C to 70°C, C\_L = 4.7 $\mu\text{F}$ (unless otherwise noted)†

|                | PARAMETER      | TEST CONDITIONS                                      | MIN | TYP | MAX | UNIT |

|----------------|----------------|------------------------------------------------------|-----|-----|-----|------|

| t <sub>d</sub> | Power OK delay | 5VCC or 5VAUX or 3.3VAUX > V <sub>TO</sub> and POK ↑ |     | 5   | 10  | ms   |

<sup>†</sup> Design targets only. Not tested in production.

## thermal characteristics‡

|                 | PARAMETER                              | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------------|-----|-----|-----|------|

| $R_{\theta JC}$ | Thermal impedance, junction-to-case    |     | 4.7 |     | °C/W |

| $R_{\theta JA}$ | Thermal impedance, junction-to-ambient |     | 59  |     | °C/W |

<sup>‡</sup> Based on Texas Instrument recommended board for PowerPAD package.

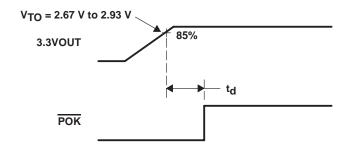

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Power OK Timing Diagram

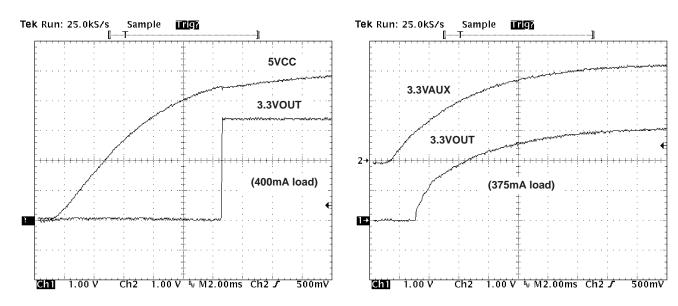

#### TYPICAL CHARACTERISTICS

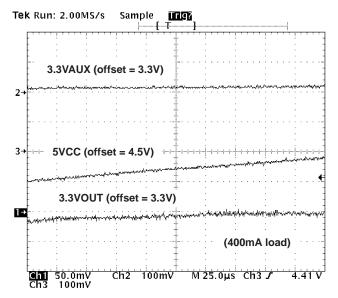

Figure 2. 5VCC Cold Start

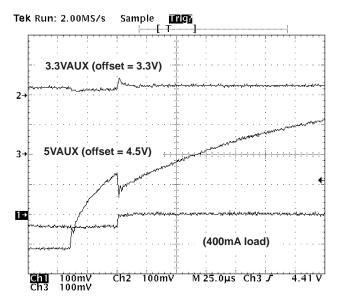

Figure 3. 3.3VAUX Cold Start

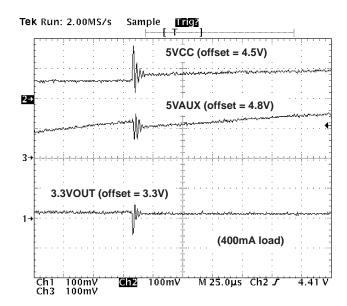

#### TYPICAL CHARACTERISTICS

Figure 4. 5VCC Power Up (5VAUX = 5 V)

Figure 5. 5VCC Power Up (3.3VAUX = 3.3 V)

Figure 6. 5VAUX Power Up (3.3VAUX = 3.3 V)

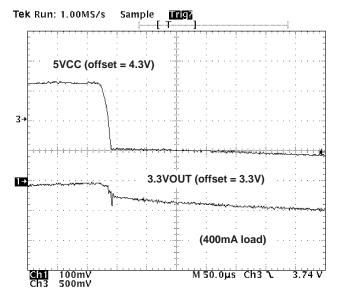

Figure 7. 5VCC Power Down (3.3VAUX = 3.3 V)

#### TYPICAL CHARACTERISTICS

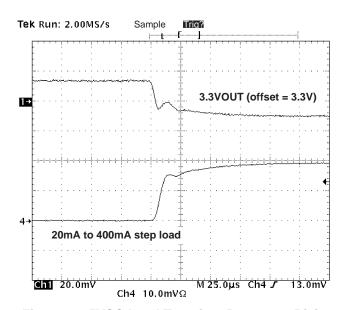

3.3VOUT (offset = 3.3V)

400mA to 20mA step load

41

Ch1 20.0mV

Ch4 10.0mVΩ

M 25.0μs Ch4 13.0mV

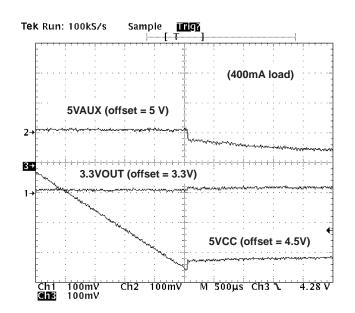

Figure 8. 5VCC Power Down (5VAUX = 5 V)

Figure 9. 5VCC Load Transient Responses Falling

Figure 10. 5VCC Load Transient Response Rising

Figure 11. 5VCC Cold Start, POK Released

#### THERMAL INFORMATION

To ensure reliable operation of the device, the junction temperature of the output device must be within the safe operating area (SOA). This is achieved by having a means to dissipate the heat generated from the junction of the output structure. There are two components that contribute to thermal resistance. They consist of two paths in series. The first is the junction to case thermal resistance,  $R_{\theta JC}$ ; the second is the case to ambient thermal resistance,  $R_{\theta JA}$ , is determined by:

$$R_{\theta,JA} = R_{\theta,JC} + R_{\theta,CA}$$

SLVS316 - NOVEMBER 2000

The ability to efficiently dissipate the heat from the junction is a function of the package style and board layout incorporated in the application. The operating junction temperature is determined by the operating ambient temperature,  $T_A$ , and the junction power dissipation,  $P_J$ .

The junction temperature, T<sub>J</sub>, is equal to the following thermal equation:

$$T_J = T_A + P_J (R_{\theta JC}) + P_J (R_{\theta CA})$$

$T_{.J} = T_A + P_{.J} (R_{\theta .JA})$

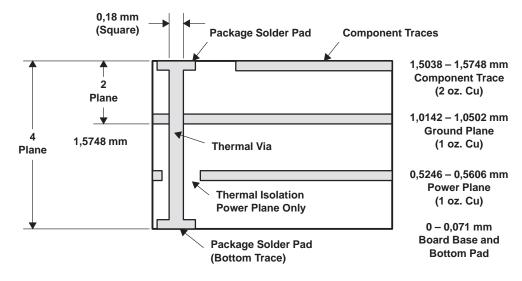

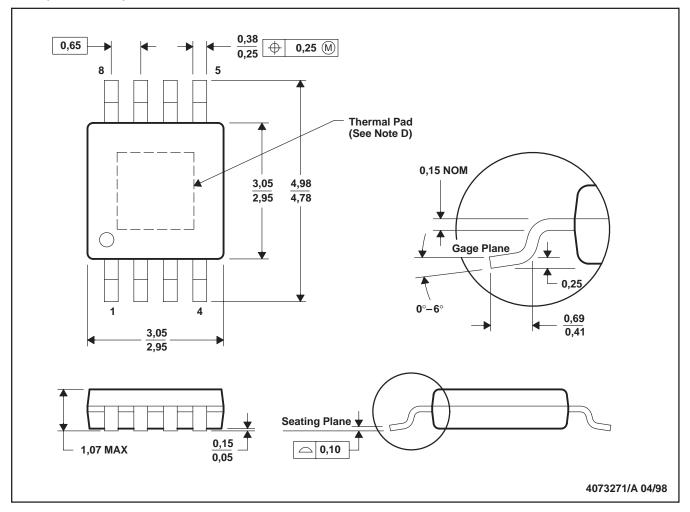

This particular application uses the 8-pin DGN PowerPAD package with a standard lead frame with dedicated ground terminal. Using a multilayer printed-circuit board (PCB), the power pad is mounted as recommended in the TI packaging application. The power pad is electrically connected to the ground plane of the circuit board through the dedicated ground pin and the die mount power pad. This will provide a means for heat spreading through the copper plane associated within the PCB (GND Layer). This concept could provide a thermal resistance from junction to ambient,  $R_{\theta JA}$ , of 59°C/W if implemented correctly.

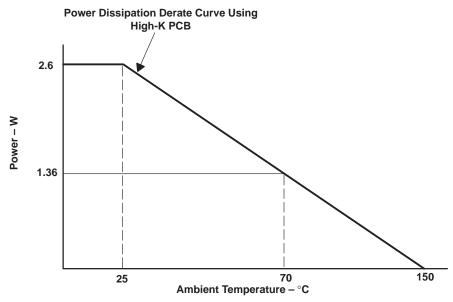

Hence, maximum power dissipation allowable for an operating ambient temperature of 70°C, and a maximum junction temperature of 150°C is determined as:

$$P_J = (T_J - T_A) / R_{\theta JA}$$

$P_J = (150 - 70) / 59 = 1.36 W$

Using a multilayer board and utilizing the ground plane for heat spreading.

NOTE: This curve is to be used for guideline purposes only. For a particular application, a more specific thermal characterization is required.

Figure 12. Power Dissipation Derating Curve

#### APPLICATION INFORMATION

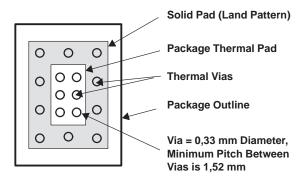

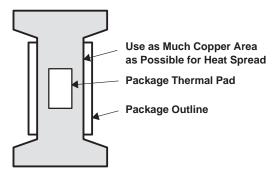

### packaging

To maximize the efficiency of this package for application on a single layer or multilayer PCB, certain guidelines must be followed.

The following information is to be used as a guideline only. For further information, refer to the PowerPAD concept implementation document.

### multilayer PCB

Guidelines for mounting the PowerPAD IC on a multilayer PCB with a ground plane.

Figure 13. Package and Land Configuration for a Multilayer PCB

Figure 14. Multilayer Board (Side View)

#### APPLICATION INFORMATION

In a multilayer board application, the thermal vias are the primary method of heat transfer from the package thermal pad to the internal ground plane. The efficiency of this method depends on several factors (die area, number of thermal vias, thickness of copper) Consult the *PowerPAD Thermally Enhanced Package Technical Brief.*

#### single-layer PCB

SLVS316 - NOVEMBER 2000

Figure 15. Land Configuration for Single-layer PCB

Layout recommendations for a single-layer PCB utilize as much copper area as possible for power management.

In a single layer board application, the thermal pad is attached to a heat spreader (copper area) by using low thermal impedance attachment method (solder paste or thermal conductive epoxy).

In both of the methods mentioned above, it is advisable to use as many copper traces as possible to dissipate the heat.

#### **IMPORTANT**

If the attachment method is NOT implemented correctly, the functionality of the product is not efficient. Power dissipation capability will be adversely affected if the device is incorrectly mounted onto the circuit board.

Figure 16. Typical Application Schematic

#### **MECHANICAL DATA**

### DGN (S-PDSO-G8)

### PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions include mold flash or protrusions.

- D. The package thermal performance may be enhanced by attaching an external heat sink to the thermal pad. This pad is electrically and thermally connected to the backside of the die and possibly to selected leads.

- E. Falls within JEDEC MO-187

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated