#### CMOS 4-BIT MICROCONTROLLER

#### TMP47P885F

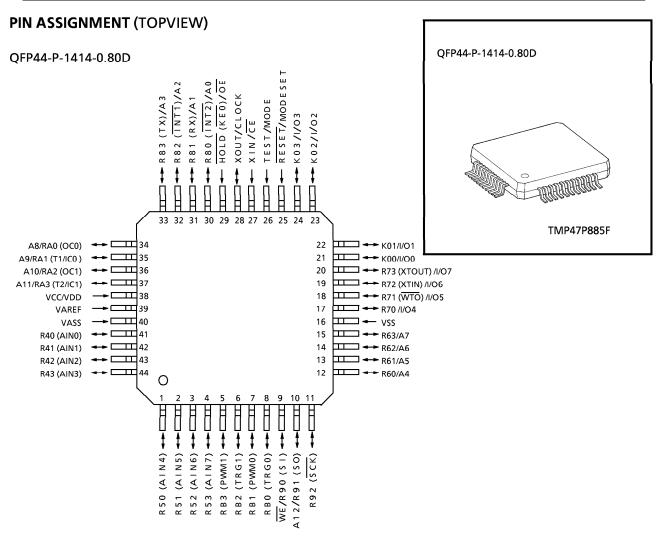

Designed for testing TMP47E885F-based systems, TMP47P885F is an LSI microcontroller with a built-in 8Kbyte E2PROM as ROM. Using a PROM writer connecting adaptor socket, TMP47P885F can write/verify the same as MBM28C64.

TMP47P885F is pin-compatible with the mask-ROM TMP47E885F. The internal E<sup>2</sup>PROM of TMP47P885F can be programmed for the same operations as TMP47E885F.

| PART No.   | ROM                              | RAM         | E <sup>2</sup> PROM | PACKAGE            | ADAPTOR SOCKET |

|------------|----------------------------------|-------------|---------------------|--------------------|----------------|

| TMP47P885F | E <sup>2</sup> PROM 8192 × 8-bit | 512 × 4-bit | 64 × 8-bit          | QFP44-P-1414-0.80D | BM1197         |

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Kehaptire Assurance/Handling Precautions.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

# **PIN FUNCTION**

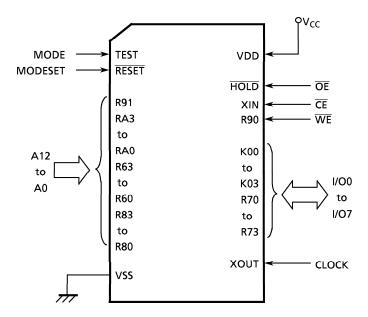

TMP47P885F supports MCU mode and E<sup>2</sup>PROM mode.

(1) MCU mode

This mode is pin-compatible with TMP47E885F. (Fix the TEST pin at low level.)

### (2) E<sup>2</sup>PROM mode

| PIN NAME     | Input/Output      | FUNCTION                                                      | Pin name (In MCU mode) |  |  |

|--------------|-------------------|---------------------------------------------------------------|------------------------|--|--|

| A12          |                   |                                                               | R91                    |  |  |

| A11 to A8    | la acce           | Decrees as a second distance in sect                          | RA3 to RA0             |  |  |

| A7 to A4     | Input             | Program memory address input                                  | R63 to R60             |  |  |

| A3 to A0     |                   |                                                               | R83 to R80             |  |  |

| I/O7 to I/O4 | Input/output      | Program moment data input/output                              | R73 to R70             |  |  |

| I/O3 to I/O0 | πρασσατρατ        | Program memory data input/output                              | K03 to K00             |  |  |

| OE           |                   | Output enable signal input                                    | HOLD                   |  |  |

| CE           | Input             | Chip enable signal input                                      | XIN                    |  |  |

| WE           |                   | Write enable signal input                                     | R90                    |  |  |

| MODE         | Input             | E <sup>2</sup> PROM mode setting pin. Fix MODE at high level; | TEST                   |  |  |

| MODESET      | input             | MODESET at low level                                          | RESET                  |  |  |

| CLOCK        | Input             | External oscillator connecting pin                            | хоит                   |  |  |

| vcc          | Power supply      | + 5V                                                          | VDD                    |  |  |

| VSS          | Power supply      | 0V (GND)                                                      | VSS                    |  |  |

| R43 to R40   |                   |                                                               |                        |  |  |

| R53 to R50   | Input/output      | For input processing, fix at low level.                       |                        |  |  |

| R92          | πιρασσατρατ       | i or input processing, nx acrow level.                        |                        |  |  |

| RB3 to RB0   | RB0               |                                                               |                        |  |  |

| VAREF        | Davisan avisanti: | To protect ladder resistors, fix at VSS level.                |                        |  |  |

| VASS         | Power supply      | To protect lauder resistors, fix at voo level.                |                        |  |  |

#### **OPERATIONAL DESCRIPTION**

The following sections describe the hardware configuration and operation for TMP47P885F. The internal mask ROM of TMP47E885F is used as E<sup>2</sup>PROM in TMP47P885F. Otherwise, structurally and functionally, TMP47P885F is identical to TMP47E885F.

### 1. Operating Mode

TMP47P885F supports MCU mode and E<sup>2</sup>PROM mode.

| Pin<br>Mode         | MODE<br>(TEST) | MODESET<br>(RESET) |         |

|---------------------|----------------|--------------------|---------|

| мси                 | L              | *                  | Ĺ       |

| E <sup>2</sup> PROM | Н              | L                  | [#<br>* |

0V 5V

Table 1-1. Operating Mode Setting

### 1.1 MCU Mode

Fixing the TEST pin at low level enters MCU mode.

The MCU mode operation is identical to TMP47E885F MCU mode operation. (As the TEST pin does not incorporate a pull-down resistor, TMP47P885F cannot be used with the TEST pin open.)

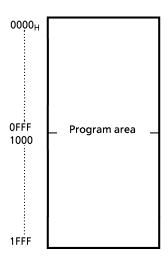

# 1.1.1 Program Memory

The program is stored in the same area as in TMP47E885F.

Figure 1-1. Program Area

#### 1.1.2 Data Memory

TMP47P885F incorporates 512 x 4 bits of RAM data memory (equivalent to TMP47E885F).

### 1.1.3 Pin Input/Output Circuits

### (1) Control pins

Apart from the TEST pin, which does not have a built-in pull-down resistor, all control pins are the same as those for TMP47E88F.

#### (2) Input/output ports

The input/output circuits for the I/O ports are the same as those for TMP47E885F.

# 1.2 E<sup>2</sup>PROM Mode (Used only for 8K byte E<sup>2</sup>PROM access)

Setting the MODE (TEST) pin to high level and the MODESET (RESET) pin to low level enters E<sup>2</sup>PROM mode. Using a general-purpose PROM writer, in E<sup>2</sup>PROM mode data are written or verified. (Set the ROM type as equal to MBM28C64.)

Figure 1-2. E<sup>2</sup>PROM Mode Settings

# 1.2.1 Operating Mode in E<sup>2</sup>PROM Mode

| Mod              | Pin              | CE<br>(XIN) | OE<br>(HOLD) | WE<br>(R90) | 1/0                      | А       | Operating state |

|------------------|------------------|-------------|--------------|-------------|--------------------------|---------|-----------------|

|                  | Data             |             |              |             | D <sub>OUT</sub>         | A.1.1   | Operate         |

| Read             | Data polling     | ]           | L            | Н           | O7 = 17, O0 to O6 = Hi-Z | Address | Write           |

| Standby          |                  | Н           | *            | *           | 11' 7                    | _       | Standby         |

| Outpu            | Output disable   |             | Н            | Н           | Hi-Z                     | *       | Operate         |

| Write            | (single byte)    | L           | Н            | L           | D <sub>IN</sub>          | Address | Write           |

| Write            | inhibit (No.1)   | *           | L            | *           | _                        | _       | _               |

| Write            | inhibit (No.2)   | *           | *            | Н           | _                        | _       | _               |

| Write (all-byte) |                  |             |              |             | all L                    |         |                 |

| Batch            | Chip erase       | L           | HV           | L           | all H                    | H *     |                 |

|                  | Security program |             |              |             | "FE <sub>H</sub> "       |         |                 |

L : 0

H : 5V

HV : 12 to 15V

Hi-Z : High impedance

D<sub>IN</sub> : Data input

D<sub>OUT</sub> : Data output

\* : don't care

Table 1-2. Operating Mode Settings (In E<sup>2</sup>PROM mode)

#### 1.2.1.1 Read Mode ( $\overline{CE} = \overline{OE} = "L", \overline{WE} = "H"$ )

Setting the  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  pins to low level and the  $\overline{\text{WE}}$  pin to high level enters read mode. Read mode has two functions: a data function to read internal data and a data polling function to detect termination of data write.

(1) Data function (Read data during normal operation)

When data are read during normal operation (except writing), the data at addresses specified by pins A0 to A12 are output to the I/O pins.

#### (2) Data polling function (Read data while writing data)

When data are read while writing data, the data being written  $(\overline{17})$  are output in inverted form to I/O pin 7. I/O pins 0 - 6 become high impedance.

This function enables detection of the termination of data write without using any additional external circuits.

Setting the  $\overline{CE}$  or  $\overline{OE}$  pin to high level sets the internal data bus and I/O pin to high impedance.

### **1.2.1.2 Standby Mode** (CE = "H")

Setting the  $\overline{\text{CE}}$  pin to high level enters standby mode. This mode disables the E<sup>2</sup>PROM and sets the I/O pins to high level.

### 1.2.1.3 Output Disable Mode ( $\overline{CE} = "L", \overline{OE} = \overline{WE} = "H"$ )

Setting the  $\overline{CE}$  pin to low level and the  $\overline{OE}$  and  $\overline{WE}$  pins to high level enters output disable mode. In this mode, E<sup>2</sup>PROM operates but the I/O ports are at high impedance.

#### 1.2.1.4 Write (Single Byte) Mode ( $\overline{CE} = \overline{WE} = "L", \overline{OE} = "H"$ )

Setting the  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  pins to low level and the  $\overline{\text{OE}}$  pin to high level enters write (single byte) mode. In this mode, only a single byte of the I/O pin data is written to the address specified by pins A0 - A12. Address input is latched at the falling edge of pins  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ . Conversely, data input is latched at the rising edge of pins  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ . Therefore, there is no need to save the address or data during write. The write timing is determined by the timing for setting the  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  pin to low level ( $\overline{\text{CE}}$  control or  $\overline{\text{WE}}$  control).

#### (1) $\overline{CE}$ control

When the  $\overline{OE}$  pin at high level and the  $\overline{WE}$  pin at low level, set the  $\overline{CE}$  pin to low level (data write at  $\overline{CE} = L$ ).

#### (2) WE control

When the  $\overline{OE}$  pin at high level and the  $\overline{CE}$  pin at low level, set the  $\overline{WE}$  pin to low level (data write at  $\overline{WE} = L$ ).

# 1.2.1.5 Write (all-byte) function (No.1 : $\overline{OE} = "L"$ , No.2 : $\overline{WE} = "H"$ )

Setting the  $\overline{OE}$  pin to low level enters write inhibit No.1 mode. Setting the  $\overline{WE}$  pin to high level enters write inhibit No.2 mode. Data are not written in either of the write inhibit modes.

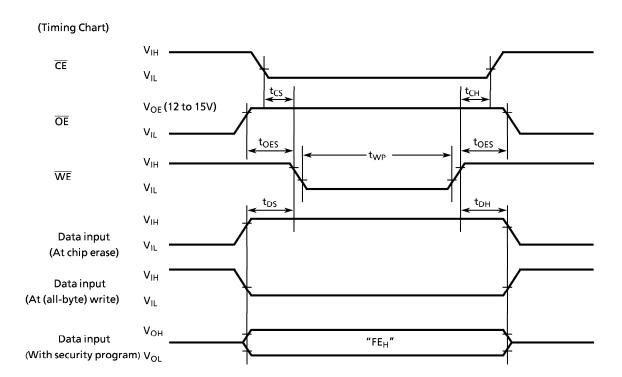

#### 1.2.1.6 Batch Mode ( $\overline{CE} = \overline{WE} = "L", \overline{OE} = "HV"$ )

Setting the  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  pins to low level, and the  $\overline{\text{OE}}$  pin to high voltage (12 - 15V) enters batch mode. Batch mode includes three functions: write (all-byte) function, chip erase function, which simultaneously erases all bytes, and security program function, which maintains data confidentiality by preventing data from being read after they are written.

- (1) Write (all-byte) function (I/O0 to I/O7 = "L")

In batch mode, setting all the I/O pins set to low level and applying a low pulse to the WE pin writes all bytes at a time.

- (2) Chip erase function (I/O0 to I/O7 = "H")

In batch mode, setting all the I/O pins set to high level and applying a low pulse to the WE pin erases all bytes at a time.

- (3) Security program function (I/O0 to I/O7 = "FEH") In batch mode, applying a low pulse to the  $\overline{WE}$  pin while outputting FEH to the I/O pins disables subsequent data reads. After security program execution, only the chip erase function can be used. This function preserves data confidentiality.

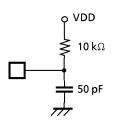

# 1.2.2 E<sup>2</sup>PROM Data Protection

E<sup>2</sup>PROM has no data protection. To access the E<sup>2</sup>PROM, set the registers of E<sup>2</sup>PROM by the instruction. If TMP47P885F is operated out of the guaranteed range, data in the E<sup>2</sup>PROM may be changed by the runaways of the CPU. Under the condition out of the guaranteed range, such as power on or power off, please use the power-on-reset circuit and reset IC to reset the MCU certainly.

- 1. After power on, keep active Reset until Vcc stabilized.

- 2. Do not power off during E2PROM access.

# **ELECTRICAL CHARACTERISTICS**

**ABSOLUTE MAXIMUM RATINGS**

$(V_{SS} = 0V)$

| PARA                                 | METER                    | SYMBOL             | PIN                           | SPECIFI                       | CATION                | UNIT |

|--------------------------------------|--------------------------|--------------------|-------------------------------|-------------------------------|-----------------------|------|

| Power supply vol                     | tage                     | V <sub>DD</sub>    |                               | – 0.3 to                      | 6.5                   | V    |

| Input voltage                        |                          | V <sub>IN</sub>    |                               | – 0.3 to                      | √ <sub>DD</sub> + 0.3 | V    |

|                                      |                          | V <sub>OUT1</sub>  | Ports R4, R5, R6, R7, R8, RA  | – 0.3 to '                    | V <sub>DD</sub> + 0.3 | .,   |

| Output voltage                       |                          | V <sub>OUT2</sub>  | Ports R9, RB                  | – 0.3 to                      | V <sub>DD</sub> + 0.3 | V    |

|                                      |                          | I <sub>OUT1</sub>  | Ports R4, R5, R6, R7, R8, RA  | 3                             | .2                    |      |

| Output current                       | Output current (per pin) |                    | Ports R9, RB (sink current)   | 3.2                           |                       | mA   |

|                                      |                          | I <sub>OUT3</sub>  | Ports R9, RB (source current) |                               | Ì                     |      |

|                                      |                          | ΣΙ <sub>ΟUT1</sub> | Ports R4, R5, R6, R7, R8, RA  | 4                             | 0                     |      |

| Output current                       | (total for all pins)     | Σl <sub>OUT2</sub> | Ports R9, RB                  | 2                             | 0                     | mA   |

| Power dissipation<br>[Topr = +85°C/+ |                          | PD                 |                               | 30                            | 00                    | mW   |

| Soldering temperature (time)         |                          | Tsld               |                               | 260 (10s)                     |                       | °C   |

| Storage temperature                  |                          | Tstg               |                               | – 55 to 1                     | 50                    | °C   |

| Operating                            | Product version          | Tana               |                               | T <sub>L</sub> T <sub>H</sub> |                       | °C   |

| temperature                          | Standard product         | Topr               |                               | - 40                          | + 85                  | ٠٠   |

RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0V, Topr = T_L to T_H)$

| PARAMETER                | Symbol           | PIN                         | CONDITION              | Min.                   | Max.                   | UNIT |

|--------------------------|------------------|-----------------------------|------------------------|------------------------|------------------------|------|

|                          |                  |                             | At normal operation    | 4.5                    |                        |      |

| Power supply voltage     | $V_{DD}$         |                             | At slow operation      | 2.7                    | 5.5                    | V    |

| High-level input voltage |                  |                             | At hold operation      | 2.0                    |                        |      |

|                          | V <sub>IH1</sub> |                             |                        | V <sub>DD</sub> × 0.7  |                        |      |

| High-level input voltage | V <sub>IH2</sub> | Hysteresis input            | V <sub>DD</sub> ≧ 4.5V | V <sub>DD</sub> × 0.75 | V <sub>DD</sub>        | V    |

| V <sub>IH3</sub>         |                  | At slow and hold operations | V <sub>DD</sub> <4.5V  | V <sub>DD</sub> × 0.9  |                        |      |

|                          | V <sub>IL1</sub> | Excluding hysteresis input  |                        |                        | $V_{DD} \times 0.3$    |      |

| Low-level input voltage  | V <sub>IL2</sub> | Hysteresis input            | V <sub>DD</sub> ≧ 4.5V | 0                      | V <sub>DD</sub> × 0.25 | v    |

| V <sub>IL3</sub>         |                  | At slow and hold operations | V <sub>DD</sub> <4.5V  |                        | V <sub>DD</sub> × 0.1  |      |

| Clock frequency          | fc               | XIN, XOUT                   |                        | 0.4                    | 6.0                    | MHz  |

|                          | fs               | XTIN, XTOUT                 |                        | 30                     | 34                     | kHz  |

D.C. CHARACTERISTICS

( $V_{SS} = 0V$ , Topr =  $T_L$  to  $T_H$ )

| PARAMETER                              | SYMBOL           | PINS                                         | COND                                                 | ITIONS           | Min. | Тур. | Max. | UNIT |

|----------------------------------------|------------------|----------------------------------------------|------------------------------------------------------|------------------|------|------|------|------|

| Hysteresis voltage                     | $V_{HS}$         | Hysteresis Input                             | ysteresis Input                                      |                  | -    | 0.7  | _    | V    |

| Input current                          | I <sub>IN1</sub> | Ports RESET, HOLD, TEST, K0 Ports R4 to RB   | V <sub>DD</sub> = 5.5V,<br>V <sub>IN</sub> = 5.5V/0V |                  | -    | _    | ± 10 | μΑ   |

|                                        | R <sub>IN1</sub> | RESET                                        |                                                      |                  | 80   | 220  | 450  | 1.0  |

| resistance                             | $R_P$            | Ports R9, RB                                 |                                                      |                  | 3    | 10   | 35   | kΩ   |

| Output leak current                    | $I_{LO}$         | Ports R4 to R8, RA                           | $V_{DD} = 5.5V, V_{OUT} = 5.5V$                      |                  | -    | _    | + 10 | μΑ   |

| High-level output voltage              | V <sub>OH</sub>  | Ports R9, RB                                 |                                                      |                  | 2.4  | _    | _    | V    |

| Low-level output voltage               | V <sub>OL</sub>  | Ports R4 to RB                               | $V_{DD} = 4.5V$ , $I_{OL} = 1.6$ mA                  |                  | 1    | _    | 0.4  | V    |

| Low-level output                       | I <sub>OL1</sub> | Ports R4 to R8, RA                           | \                                                    | 1.0\/            | 2.4  | _    | _    |      |

| current                                | I <sub>OL2</sub> | Ports R9, RB                                 | $V_{DD} = 4.5V, V_{OI}$                              | _= 1.00          | 2.4  | -    | _    | mA   |

| Power supply current at                | l                | Except for E <sup>2</sup> PROM Erase / write | V <sub>DD</sub> = 5.5V, fc =                         | 4 MHz            | -    | 3    | 6    |      |

| normal operation                       | I <sub>DD</sub>  | During E <sup>2</sup> PROM Erase / write     | V <sub>DD</sub> = 5.5V, fc =                         | 4 MHz            | -    | 6    | 10   | mA   |

| Power supply current at slow operation | I <sub>DDS</sub> |                                              | $V_{DD} = 3.0V$ ,<br>fs = 32.768 kHz                 | Standard product | -    | 30   | 60   | μA   |

| Power supply current at hold operation | I <sub>DDH</sub> |                                              | V <sub>DD</sub> = 5.5V                               | Standard product | _    | 0.5  | 20   | μΑ   |

Note 1: Typ. values are based on Topr = 25 °C,  $V_{DD}$  = 5V

Note 2 : Input current :  $I_{IN1}$ ,  $I_{IN2}$  : Excludes current due to built-in input (pull-up or pull-down) resistors.

Note 3: Input current:  $I_{DD}$ ,  $I_{DDH}$  :  $V_{IN} = 5.3V/0.2V$

Port R voltage level is assumed to be valid.

$I_{DDS}$ :  $V_{IN} = 2.8 V / 0.2 V$ , low-frequency clock (XTIN, XTOUT connected) only oscillates.

A.C. CHARACTERISTICS

$(V_{SS} = 0V, V_{DD} = 4.5V \text{ to } 5.5V, Topr = T_L \text{ to } T_H)$

| PARAMETER                      | SYMBOL             | CONDITIONS               | Min. | Max. | UNIT            |  |

|--------------------------------|--------------------|--------------------------|------|------|-----------------|--|

| Instruction and ations         |                    | At normal operation      | 1.3  | 20   |                 |  |

| Instruction cycle time         | t <sub>cy</sub>    | At slow operation        | 235  | 267  | μS              |  |

| High-level clock pulse width   | t <sub>WCH</sub>   |                          | 00   |      |                 |  |

| Low-level clock pulse width    | t <sub>WCL</sub>   | External clock operation | 80   | _    | ns              |  |

| Reset pulse width              | PW <sub>RSTL</sub> | With stable oscillation  | 3    | _    | t <sub>cy</sub> |  |

| External interrupt pulse width | PW <sub>EINT</sub> |                          | 2    | -    | t <sub>cy</sub> |  |

### A / D CONVERSION CHARACTERISTICS

(

$$V_{SS} = 0V$$

,  $V_{DD} = 4.5V$  to 5.5V,  $Topr = T_L$  to  $T_H$ )

| PARAMETER                                     | SYMBOL               | CONDITION                            | Min.                  | Тур. | Max.              | UNIT            |

|-----------------------------------------------|----------------------|--------------------------------------|-----------------------|------|-------------------|-----------------|

| Analog reference power supply                 | V <sub>AREF</sub>    |                                      | V <sub>DD</sub> – 1.5 | 1    | $V_{DD}$          | v               |

| voltage                                       | V <sub>ASS</sub>     |                                      | V <sub>SS</sub>       | -    | 1.5               | V               |

| Analog reference power supply voltage range   | $\triangle V_{AREF}$ | V <sub>AREF</sub> - V <sub>ASS</sub> | 2.5                   | -    | -                 | ٧               |

| Analog input voltage range                    | V <sub>AIN</sub>     |                                      | V <sub>ASS</sub>      | -    | V <sub>AREF</sub> | V               |

| Analog reference voltage power supply current | I <sub>REF</sub>     |                                      | _                     | 0.5  | 1.0               | mA              |

| Non-linear error                              |                      |                                      | _                     | -    | ± 1.5             |                 |

| Non-linear error                              |                      | $V_{DD} = 5.0V, V_{SS} = 0.0V$       | _                     | _    | ± 1.5             | LSB             |

| Zero error                                    |                      | V <sub>AREF</sub> = 5.000V           | _                     | -    | ± 1.5             |                 |

| Full-scale error                              |                      | V <sub>ASS</sub> = 0.000V            | _                     | -    | ± 2               |                 |

| Total error                                   | t <sub>ADC</sub>     |                                      | -                     | 26   | _                 | t <sub>cy</sub> |

| A/D conversion time                           | t <sub>AIN</sub>     | At fc = 4 MHz                        | _                     | 4    | _                 | μ\$             |

# SIO CHARACTERISTICS

(

$$V_{SS} = 0V$$

,  $V_{DD} = 4.5$  to 5.5V,  $Topr = T_L$  to  $T_H$ )

| PARAMETER                      | SYMBOL             | CONDITION                                 | Min.                      | Max.  | UNIT            |

|--------------------------------|--------------------|-------------------------------------------|---------------------------|-------|-----------------|

| Data transfer rate             |                    | When fc = 6 MHz, internal clock operates. | -                         | 93750 | bps             |

| Shift data hold time           | t <sub>SDH</sub>   |                                           | 0.5 t <sub>cy</sub> – 300 | _     | ns              |

| Futomost algebrasicas scientis | PW <sub>SCKH</sub> | Fire and alone an anaton                  | 2                         |       |                 |

| External clock pulse width     | PW <sub>SCKL</sub> | External clock operates.                  | 2                         | _     | t <sub>cy</sub> |

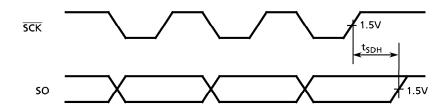

Note: Shift data hold time:

SCK, SO pin External circuit

Serial port (end of transmission)

TIMER/COUNTER CHARACTERISTICS

$(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 5.5V, Topr = T_L \text{ to } T_H)$

| PARAMETER                         | SYMBOL             | CONDITION           | Min. | Max.  | UNIT |  |

|-----------------------------------|--------------------|---------------------|------|-------|------|--|

| External count clock from one     | f                  | At normal operation | -    | fc/16 | Hz   |  |

| External count clock frequency    | † <sub>CNT</sub>   | At slow operation   | -    | fs/16 | 112  |  |

|                                   | D)A/               | At normal operation | 4/fc | -     | ,    |  |

| External input signal pulse width | PW <sub>TCIN</sub> | At slow operation   | 4/fs | -     | 5    |  |

PWM OUTPUT CHARACTERISTICS

$(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 5.5V, Topr = T_L \text{ to } T_H)$

| PARAMETER                        | SYMBOL            | CONDITION | Min. | Тур. | Max.    | UNIT |

|----------------------------------|-------------------|-----------|------|------|---------|------|

| PWM signal output frequency      | f <sub>PWM</sub>  |           | -    | -    | fc/8192 | Hz   |

| Trigger signal input pulse width | PW <sub>TRG</sub> |           | 4/fc | _    | _       | s    |

64 byte E<sup>2</sup>PROM characteristics

$(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 5.5V, Topr = T_L \text{ to } T_H)$

| PARAMETER                 | SYMBOL          | CONDITION                                                                     |                 |        | UNIT  |

|---------------------------|-----------------|-------------------------------------------------------------------------------|-----------------|--------|-------|

| Write time                | t <sub>PW</sub> |                                                                               | 4.1             | (Typ.) | ms    |

| Erase time                | t <sub>EW</sub> |                                                                               | 4.1             | (Typ.) | ms    |

| Number of overwrites      |                 | Topr = T <sub>H</sub>                                                         | 10 <sup>4</sup> | (Min.) | Times |

| Data hold characteristics |                 | After executing 10 <sup>4</sup> rewrites,<br>Ta = 55 °C (average temperature) | 10              | (Min.) | Year  |

Note: Number of rewrites and data retention characteristics are intended as a guide to product capability.

$(V_{SS} = 0V)$

# D. C. CHARACTERISTICS (IN E<sup>2</sup>PROM MODE)

| PARAMETER                                          | SYMBOL           | PINS                 | CONDITIONS                                                       | Min.                 | Тур. | Max.                  | UNIT           |

|----------------------------------------------------|------------------|----------------------|------------------------------------------------------------------|----------------------|------|-----------------------|----------------|

| Input leak current                                 | ILI              | TEST, RESET, HOLD    | $V_{CC} = 5.5V, V_{IN} = 5.5V$                                   | - 10                 | -    | 10                    |                |

| Output leak current                                | I <sub>LO</sub>  | Sink open drain port | $V_{CC} = 5.5V, V_{OUT} = 5.5V$                                  | - 10                 | -    | 10                    | μΑ             |

| V <sub>CC</sub> power supply current (standby)     | I <sub>SB1</sub> |                      | CE = V <sub>IH</sub> , I/O = OPEN                                | -                    | 0.2  | 1                     | mA             |

| V <sub>CC</sub> power supply current (standby)     | I <sub>SB2</sub> |                      | $\overline{CE} = V_{CC} \pm 0.3V$ , I/O = OPEN                   | -                    | 10   | 100                   | μΑ             |

| V <sub>CC</sub> power supply current (operation)   | I <sub>CC1</sub> |                      | $\overline{CE} = V_{IL}$ , I/O = OPEN                            | -                    | 20   | 30                    |                |

| V <sub>CC</sub> power supply current (operation)   | I <sub>CC2</sub> |                      | Cycle = Min., I/O = OPEN                                         | _                    | 20   | 30                    | mA             |

| V <sub>CC</sub> power supply current (write)       | I <sub>CCW</sub> |                      | WE = ¬∟r , CE = V <sub>IL</sub>                                  | -                    | 20   | 30                    |                |

| High-level input voltage                           | V <sub>IH</sub>  |                      | V <sub>CC</sub> = 4.5~5.5V                                       | V <sub>CC</sub> ×0.7 | -    | V <sub>CC</sub> + 0.3 |                |

| Low-level input voltage                            | V <sub>IL</sub>  |                      | V <sub>CC</sub> = 4.5~5.5V                                       | - 0.1                | _    | V <sub>CC</sub> ×0.3  |                |

| High-level output voltage                          | V <sub>OH</sub>  |                      | $I_{OH} = -400 \mu A$ , $V_{CC} = 4.5 V$                         | 2.4                  | 1    | _                     | ] <sub>v</sub> |

| Low-level output<br>voltage                        | V <sub>OL</sub>  | Excluding XOUT       | I <sub>OL</sub> = 2.1mA                                          | -                    | -    | 0.45                  |                |

| Program inhibit V <sub>CC</sub><br>voltage         | V <sub>INH</sub> |                      |                                                                  | 2.0                  | _    | _                     |                |

| Output enable pin voltage at chip erase            | V <sub>OE</sub>  |                      | V <sub>CC</sub> = 4.5V~5.5V                                      | 12                   | -    | 15                    |                |

| V <sub>CC</sub> power supply current at chip erase | I <sub>CCE</sub> |                      | $\overline{OE} = V_{OE}, \overline{CE} = \overline{WE} = V_{IL}$ | -                    | -    | 60                    | mA             |

| High potential detect input voltage                | V <sub>IHP</sub> |                      | V <sub>CC</sub> = 4.5V to 5.5V                                   | 8.0                  | -    | -                     | V              |

# A . C characteristics (In E<sup>2</sup>PROM mode)

$$(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 5.5V)$$

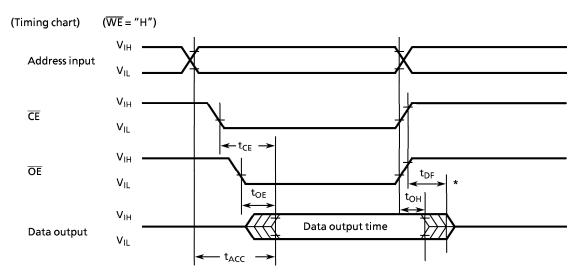

# (1) Read Cycle

| PARAMETER                                | SYMBOL           | CONDITIONS                                                  | Min. | Тур. | Max. | UNIT |

|------------------------------------------|------------------|-------------------------------------------------------------|------|------|------|------|

| Address access time                      | t <sub>ACC</sub> | $\overline{CE} = \overline{OE} = V_{IL}$                    | -    | _    | 350  |      |

| From $\overline{CE} = L$ to data output  | t <sub>CE</sub>  | $\overline{OE} = V_{IL}$                                    | -    | -    | 350  |      |

| From $\overline{OE}$ = L to data output  | t <sub>OE</sub>  | $\overline{CE} = V_{IL}$                                    | -    | -    | 120  | ns   |

| From CE = H or OE = H to output floating | t <sub>DF</sub>  | $\overline{CE} = V_{IH} \text{ or } \overline{OE} = V_{IH}$ | -    | -    | 60   |      |

| Previous cycle data output hold          | t <sub>OH</sub>  | $\overline{CE} = \overline{OE} = V_{IL}$                    | 0    | _    | _    |      |

\* t<sub>DF</sub> is determined by whichever of the rising edges of <del>OE</del> or <del>CE</del> is faster. The level is determined when the output becomes high impedance.

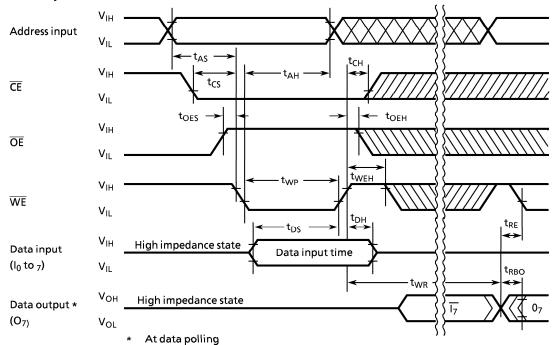

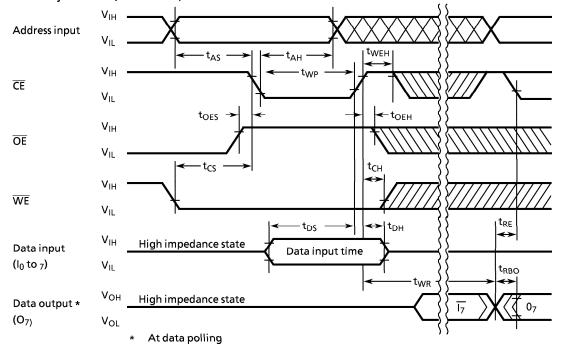

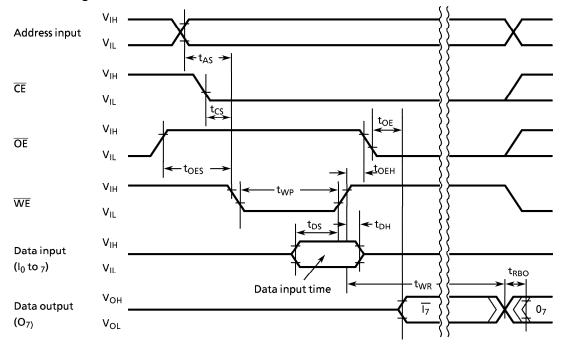

# (2) Write cycle (single byte)

| PARAMETER                          | SYMBOL           | Min. | Тур. | Max. | UNIT |

|------------------------------------|------------------|------|------|------|------|

| Address set-up time                | t <sub>AS</sub>  | 20   | -    | -    |      |

| Write set-up time                  | t <sub>CS</sub>  | 0    | ı    | -    |      |

| OE set-up time                     | t <sub>OES</sub> | 20   | -    | -    |      |

| Write pulse width                  | t <sub>WP</sub>  | 100  | -    | -    |      |

| Address hold time                  | t <sub>AH</sub>  | 50   | -    | -    | ns   |

| Data set-up time                   | t <sub>DS</sub>  | 50   | -    | -    |      |

| Data hold time                     | t <sub>DH</sub>  | 20   | -    | -    |      |

| Write hold time                    | t <sub>CH</sub>  | 0    | ı    | -    |      |

| OE hold time                       | t <sub>OEH</sub> | 20   | ı    | -    |      |

| Write time                         | t <sub>WR</sub>  | ı    | ı    | 10   | ms   |

| Write recover time                 | t <sub>RE</sub>  | 50   | -    | -    | ns   |

| From program termination to output | t <sub>RBO</sub> |      | -    | 100  | 115  |

| WE hold time                       | t <sub>WEH</sub> | 10   | ı    | -    | ns   |

### (Timing chart)

# 1. Write cycle No.1 (WE control)

### 2. Write cycle No.2 (CE control)

# 3. Data Polling

# (3) Chip erase/write (all-byte)/ security program cycle

| PARAMETER         | SYMBOL           | Min. | Тур. | Max. | UNIT |

|-------------------|------------------|------|------|------|------|

| Write set-up time | t <sub>CS</sub>  | 150  | -    | -    |      |

| OE set-up time    | t <sub>OES</sub> | 150  | -    | -    | ns   |

| Data set-up time  | t <sub>D\$</sub> | 150  | -    | _    |      |

| Data hold time    | t <sub>DH</sub>  | 100  | ı    | ı    |      |

| Write pulse width | t <sub>WP</sub>  | 5    | ı    | 20   | ms   |

| Write hold time   | t <sub>CH</sub>  | 100  | -    | _    | ns   |

| OE hold time      | t <sub>OEH</sub> | 100  | -    | _    | 113  |

### **CAUTIONS**

TMP47E885F and TMP47P885F are covered by a patent agreement between Toshiba Corporation and Bull CP8. These products cannot be used with IC cards and other portable devices (as defined below).

### "PORTABLE DEVICE"

- (I) A portable piece of equipment with a length or breadth ± 10 mm, and a thickness ± 3 mm of the dimensions defined under ISO standard 7816, or

- (II) A portable device conforming to the electrical connection layout and shape specified under ISO standard 7816, part 2, or

- (III) A portable and pocket-size device for the identification of the carrier of the device or of the device itself, and for the accumulation of information relating to the carrier of the device or the device itself.