#### **CMOS 8-Bit Microcontroller**

## TMP86CH06N/TMP86CH06U

The TMP86CH06 is the 8-bit single chip microcomputer, which contains ROM, RAM, multi-function timer/counters, serial interface (UART/SIO) with high speed, high performance and low power consumption.

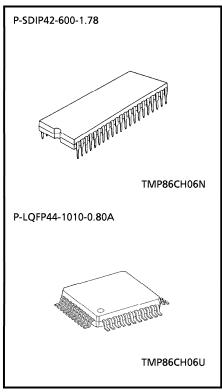

| Product No. | ROM         | RAM         | Package             | OTP MCU    |

|-------------|-------------|-------------|---------------------|------------|

| TMP86CH06N  | 16K × 8-bit | E120 hit    | P-SDIP42-600-1.78   | TMP86PH06N |

| TMP86CH06U  | 10K X 0-DIL | 512 × 8-bit | P-LQFP44-1010-0.80A | TMP86PH06U |

#### **Features**

- ♦ 8-bit single chip microcomputer TLCS-870/C Series

- Minimum Instruction execution time:  $0.25 \mu s$  (at 16.0 MHz)

- Power consumption is reducible by means of conversion of instruction execution time 0.25  $\mu$ s, 0.50  $\mu$ s, 1.0  $\mu$ s, 2.0  $\mu$ s, 4.0  $\mu$ s, 8.0  $\mu$ s, 122  $\mu$ s (at 16.0 MHz, 32.768 kHz operation)

- ◆ External Bus Interface

- up to 64 Kbytes (for both Program and Data memory)

- Multiplexed between Lower Address-bus and Data-bus

- ♦ 21 Interrupt factors (6 for External, 15 for Internal)

- ◆ Input/Output Ports: 35 pins

- High-Current Output (Typ. 20 mA, LED direct drive): 8 pins

- ◆ 16-bit Timer/Counter: 1 channel

- Timer, Event counter, Pulse Width measurement and External-triggered timer

000707EBP1

• For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer,

● The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

86CH06-1 2002-10-08

- ◆ 8-bit Timer/Counter: 2 channels

- Available for 16-bit timer by cascade connection

- Timer, Event counter, Pulse Width Modulation, Programmed Pulse Generator and Programmable Divider Output, Warming-up Counter

- ♦ Serial Interface

- 8-bit UART: 2 channels

- 8-bit SIO (synchronized): 1 channel

- ◆ Clock Oscillation circuit: 2 units

- For Single or Dual clock mode

- ◆ Nine power saving operating modes

- STOP mode: Oscillation stops. Battery/Capacitor back-up. Port output hold/High-impedance.

- SLOW 1, 2 mode: Low power consumption operation using low-frequency clock (32.768 kHz)

- IDLE 0 mode: CPU stops, and peripherals operate using high-frequency clock of Time-Base-

- Timer. Release by falling edge of TBTCR < TBTCK > setting.

- IDLE 1 mode: CPU stops, and peripherals operate using high-frequency clock. Release by

- interruputs.

- IDLE 2 mode: CPU stops, and peripherals operate using high and low frequency clock. Release

- by interruputs.

- SLEEP 0 mode: CPU stops, and peripherals operate using low-frequency clock of Time-Base-

- Timer. Release by falling edge of TBTCR < TBTCK > setting.

- SLEEP 1 mode: CPU stops, and peripherals operate using low-frequency clock. Release by

- interrupts.

- SLEEP 2 mode: CPU stops, and peripherals operate using high and low frequency clock. Release

- by interrupts.

- ◆ Operating Voltage: 4.5 to 5.5 V at 16.0 MHz/32.768 kHz, 2.7 to 5.5 V at 8 MHz/32.768 kHz,

- 1.8 to 5.5 V at 4.2 MHz/32.768 kHz.

86CH06-2 2002-10-08

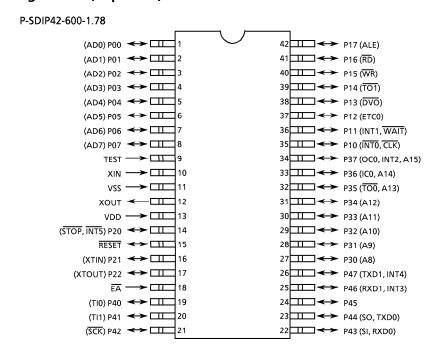

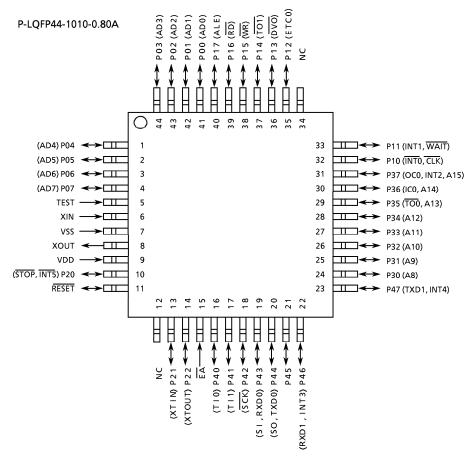

## Pin Assignments (Top View)

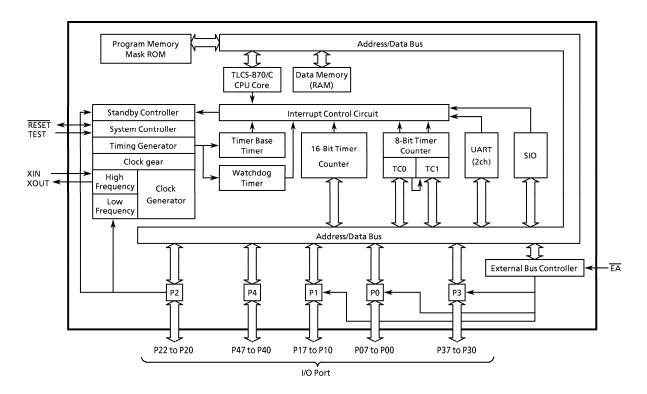

# **Block Diagram**

# Pin Names And Functions (1/3)

| Pin Name                 | No. of Pins | Input/Output           | Functions                                                                                                                                                                        |

|--------------------------|-------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00 to P07<br>AD0 to AD7 | 8           | I/O<br>3-states        | Port 0: 8-bit I/O port that allows selection of input/output on bit basis.  Address/Data bus: Functions as 8-bit bidirectional address/data bus for external memory (TTL input). |

| P10 INTO CLK             | 1           | I/O<br>Input<br>Output | Port 10: I/O port that allows selection of input/output on bit basis.  External Interrupt Request 0  Clock: Clock output  (Schmidt Input)                                        |

| P11 INT1 WAIT            | 1           | I/O<br>Input<br>Input  | Port 11: I/O port that allows selection of input/output on bit basis.  External Interrupt Request 1  Wait: Wait request from external Memory  (Schmidt Input)                    |

| P12<br>ETC0              | 1           | I/O<br>Input           | Port 12: I/O port that allows selection of input/output on bit basis.  Extended Timer Input 0  (Schmidt Input)                                                                   |

| P13                      | 1           | I/O<br>Output          | Port 13: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)  Divider Output                                                                           |

| P14                      | 1           | 1/0                    | Port 14: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)                                                                                           |

| P15                      | 1           | Output<br>I/O          | 8-bit Timer 1 Output  Port 15: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)                                                                     |

| P16                      | 1           | Output<br>I/O          | Write: Generates strobe signal to write data on External Memory.  Port 16: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)                         |

| RD<br>P17                |             | Output<br>I/O          | Read: Generates strobe signal to read data from External Memory.  Port 17: I/O port that allows selection of input/output on bit basis.                                          |

| ALE                      | 1           | Output                 | (Schmidt Input)  Address Latch Enable: The negative edge of ALE supplies an address latch timing on AD0 to AD7 for External Memory.                                              |

| P20<br>STOP              | 1           | I/O<br>Input           | Port 20: I/O port that allows selection of input/output on bit basis. Open-Drain Output.  STOP Releasing: The rising edge or High Level (Schmidt Input)                          |

| ĪNT5                     |             | Input                  | Releases STOP mode. External Interrupt Request 5                                                                                                                                 |

| P21                      | 1           | I/O                    | Port 21: I/O port that allows selection of input/output on bit basis. Open-Drain Output. (Schmidt Input)                                                                         |

| P22                      | 1           | Input<br>I/O           | Port 22: I/O port that allows selection of input/output on bit basis. Open-Drain Output. (Schmidt Input)                                                                         |

| хтоит                    |             | Output                 | Low Frequency Clock Output                                                                                                                                                       |

| P30 to P34               | 5           | 1/0                    | Port 30 to 34: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)                                                                                     |

| A8 to A12                |             | Output                 | Address Bus 8 to 12                                                                                                                                                              |

# Pin Names And Functions (2/3)

| Pin Name           | No. of Pins | Input/Output              | Functions                                                                                                                                                                                             |

|--------------------|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P35                |             | I/O                       | Port 35: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)                                                                                                                |

| TO0<br>A13         | 1           | Output<br>Output          | 8-bit Timer Output 0 Address Bus 13                                                                                                                                                                   |

| P36<br>IC0<br>A14  | 1           | I/O<br>Input<br>Output    | Port 36: I/O port that allows selection of input/output on bit basis.  Capture Input 0 for Extended Timer  Address Bus 14                                                                             |

| P37                |             | 1/0                       | Port 37: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)                                                                                                                |

| OC0<br>INT2<br>A15 | 1           | Output<br>Input<br>Output | Output Compare 0 for Extended Timer  External Interrupt Request 2 (Schmidt Input)  Address Bus 15                                                                                                     |

| P40                | 1           | I/O                       | Port 40: I/O port that allows selection of input/output on bit basis. Programmable Open-Drain Output. 8-bit Timer Input 0  (Schmidt Input)                                                            |

| P41                | 1           | I/O                       | Port 41: I/O port that allows selection of input/output on bit basis. Programmable Open-Drain Output. 8-bit Timer Input 1                                                                             |

| P42                | 1           | 1/0                       | Port 42: I/O port that allows selection of input/output on bit basis. Programmable Open-Drain Output. Clock input/output for SIO (Schmidt Input)                                                      |

| P43<br>SI, RXD0    | 1           | I/O<br>Input              | Port 43: I/O port that allows selection of input/output on bit basis. Programmable Open-Drain Output. Data Input for UART/SIO channel 0                                                               |

| P44                | 1           | I/O                       | Port 44: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)                                                                                                                |

| SO, TXD0<br>P45    | 1           | Output<br>I/O             | Data Output for UART/SIO channel 0. Programmable Open-Drain Output.  Port 45: I/O port that allows selection of input/output on bit basis. Programmable Open-Drain Output.                            |

| P46 RXD1 INT3      | 1           | I/O<br>Input<br>Input     | Port 46: I/O port that allows selection of input/output on bit basis. Programmable Open-Drain Output. Data Input for UART channel 1 External Interrupt Request 3                                      |

| P47 TXD1 INT4      | 1           | I/O Output Input          | Port 47: I/O port that allows selection of input/output on bit basis.  (Schmidt Input)  Data Output for UART channel 1. Programmable Open-Drain Output.  External Interrupt Request 4 (Schmidt Input) |

# Pin Names And Functions (3/3)

| Pin Name | No. of Pins | Input/Output | Functions                                                                                                |

|----------|-------------|--------------|----------------------------------------------------------------------------------------------------------|

| ĒĀ       | 1           | Input        | External Access: Fix to HIGH level to utilize internal ROM. Fix to LOW level to utilize external memory. |

| TEST     | 1           | Input        | to be fixed to LOW level                                                                                 |

| RESET    | 1           | I/O          | RESET signal input or watchdog timer output/address trap output/system-clock-reset-output                |

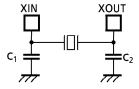

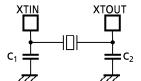

| XIN/XOUT | 2           | 1/0          | High-frequency resonator is to be connected.                                                             |

| VSS      | 1           | Input        | Ground                                                                                                   |

| VDD      | 1           | Input        | Power Supply                                                                                             |

### **Operational Description**

#### 1. CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller.

This section provides a description of the CPU core, the program memory, the data memory, the external memory interface, and the reset circuit.

#### 1.1 Memory Address Maps

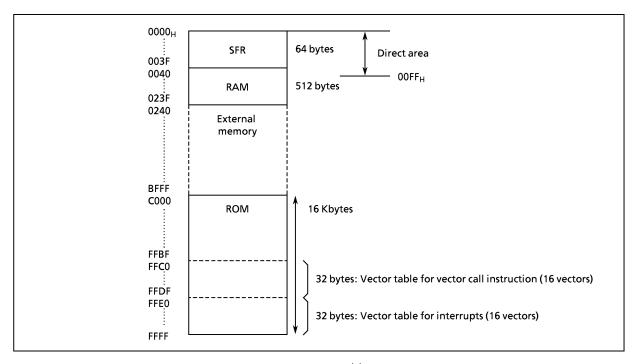

The TMP86CH06 memory consists of 3 blocks: ROM, RAM and SFR (Special Function Register). They are all mapped in 64K-byte address space. Figure 1-1 shows the TMP86CH06 memory address maps. The general-purpose register banks are not assigned to the RAM address space.

Figure 1-1. Memory Address Maps

## 1.2 Program Memory (ROM)

The TMP86CH06 can address up to 64 Kbytes of external program memory space except the SFR area and the internal RAM. However, placing program memory on the internal RAM is deregulated if a certain procedure is executed (See 2.4.5 Address trap). The TMP86CH06 contains a 16-Kbyte program memory (mask ROM) at addresses from  $C000_{\rm H}$  to  $FFFF_{\rm H}$ .

## 1.3 Data Memory (RAM)

The TMP86CH06 is available up to 64 Kbytes of data memory area. Data memory consists of internal data memory (internal ROM or RAM) and external data memory (ROM or RAM). The TMP86CH06 has 512 bytes of internal RAM. The first 192 bytes ( $0040_{\rm H}$  to  $00FF_{\rm H}$ ) of the internal RAM are located in the direct area; instructions with shorten operations are available against such an area.

# **Electrical Characteristics**

Absolute Maximum Rating (V<sub>ss</sub> = 0 V)

| Parameter                               | Symbol              | Pins       | Rating                         | Unit  |

|-----------------------------------------|---------------------|------------|--------------------------------|-------|

| Supply Voltage                          | $V_{DD}$            |            | – 0.3 to 6.5                   |       |

| Input Voltage                           | $V_{IN}$            |            | – 0.3 to V <sub>DD</sub> + 0.3 | V     |

| Output Voltage                          | V <sub>OUT</sub>    |            | – 0.3 to V <sub>DD</sub> + 0.3 |       |

|                                         | I <sub>OUT1</sub>   | P1 to P4   | 3.2                            |       |

| Output Current                          | I <sub>OUT3</sub>   | P0         | 30                             | mA    |

|                                         | Σ l <sub>OUT1</sub> |            | 80                             | ] ''" |

| Output Current                          | Σ I <sub>OUT3</sub> |            | 120                            |       |

| 2 2 4 4 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |                     | TMP86CH06N | 600                            |       |

| Power Dissipation (Topr = 85°C)         | PD                  | тмр86сн060 | 350                            | mW    |

| Soldering Temperature (Time)            | Tsld                |            | 260 (10 s)                     |       |

| Storage Temperature                     | Tstg                |            | – 55 to 125                    | °c    |

| Operating Temperature                   | Topr                |            | - 40 to 85                     |       |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

**Recommended Operating Conditions**

$(V_{SS} = 0 \text{ V, Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter          | Symbol            | Pins                            |                                  | Conditions                                 | Min                   | Max                  | Unit             |

|--------------------|-------------------|---------------------------------|----------------------------------|--------------------------------------------|-----------------------|----------------------|------------------|

|                    |                   |                                 | fc = 16                          | NORMAL1, 2 mode                            |                       |                      |                  |

|                    |                   |                                 | MHz                              | IDLE0, 1, 2 mode                           | 4.5                   |                      |                  |

|                    |                   |                                 | fc = 8                           | NORMAL1, 2 mode                            |                       |                      |                  |

|                    |                   |                                 | MHz                              | IDLE0, 1, 2 mode                           | 2.7                   |                      |                  |

| Supply Voltage     | $V_{\mathrm{DD}}$ |                                 | fc = 4.2                         | NORMAL1, 2 mode                            |                       | 5.5                  | l <sub>v</sub> l |

|                    | - 55              |                                 | MHz                              | IDLE0, 1, 2 mode                           | 1.8                   |                      |                  |

|                    |                   |                                 | fs = 32.768                      | SLOW1, 2 mode                              | ] "                   |                      |                  |

|                    |                   |                                 | kHz                              | SLEEP0, 1, 2 mode                          |                       |                      |                  |

|                    |                   |                                 |                                  | STOP mode                                  | 1.8                   |                      |                  |

|                    | V <sub>IH1</sub>  | Except hysteresis and TTL input | - V <sub>DD</sub> ≧ 4.5 V        |                                            | $V_{DD} \times 0.70$  |                      |                  |

|                    | V <sub>IH2</sub>  | Hysteresis input                |                                  |                                            | $V_{DD} \times 0.75$  |                      |                  |

| Input High Voltage | V <sub>IH3</sub>  | Except TTL input                |                                  | $V_{DD}$ < 4.5 V                           | $V_{DD} \times 0.90$  | $V_{DD}$             | V                |

|                    | $V_{IH4}$         | TTL input (Data bus)            | V <sub>DD</sub> = 5 V            |                                            | 2.2                   | ]                    |                  |

|                    | $V_{\text{IH}5}$  |                                 |                                  | $V_{DD} = 1.8 V$                           | V <sub>DD</sub> – 0.2 |                      |                  |

|                    | $V_{IL1}$         | Except hysteresis and TTL input |                                  | $V_{DD} \ge 4.5 V$                         |                       | $V_{DD} \times 0.30$ |                  |

|                    | $V_{IL2}$         | Hysteresis input                |                                  | V DD = 4.5 V                               |                       | $V_{DD} \times 0.25$ |                  |

| Input Low Voltage  | $V_{IL3}$         | Except TLL input                |                                  | V <sub>DD</sub> < 4.5 V                    | 0                     | $V_{DD} \times 0.10$ | V                |

|                    | $V_{IL4}$         | TTL input (Data bus)            |                                  | $V_{DD} = 5 V$                             |                       | 0.8                  |                  |

|                    | $V_{IL5}$         |                                 |                                  | V <sub>DD</sub> = 1.8 V                    |                       | 0.2                  |                  |

|                    |                   |                                 |                                  | $V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}$ |                       | 16                   |                  |

| Clock Frequency    | fc                | XIN, XOUT                       |                                  | V <sub>DD</sub> = 2.7 V to 5.5 V           |                       | 8                    | MHz              |

| Clock Frequency    |                   |                                 | V <sub>DD</sub> = 1.8 V to 5.5 V |                                            |                       | 4.2                  |                  |

|                    | fs                | XTIN, XTOUT                     |                                  |                                            | 30.0                  | 34.0                 | kHz              |

Note 1: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

Note 2: Clock Frequency fc; The condition of supply voltage range is the value under NORMAL1/2 and IDLE0/1/2 mode.

Note 3: The minimum fc with clock gear is calculated as following formula with the ratio on divider n.

(Min fc) = (ratio on divider n)  $\times$  1 [MHz]

DC Characteristics

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter            | Symbol           | Pins                            | Conditions                                                      | Min  | Тур. | Max | Unit |

|----------------------|------------------|---------------------------------|-----------------------------------------------------------------|------|------|-----|------|

| Hysteresis Voltage   | V <sub>HS</sub>  | Hysteresis input                |                                                                 | _    | 0.9  | -   | ٧    |

|                      | I <sub>IN1</sub> | TEST, EA                        | V 55V                                                           |      |      |     |      |

| Input Current        | I <sub>IN2</sub> | Sink Open Drain, Tri-state Port | $V_{DD} = 5.5 V$                                                | _    | _    | ± 2 | μΑ   |

|                      | I <sub>IN3</sub> | RESET, STOP                     | $V_{IN} = 5.5 \text{ V/0 V}$                                    |      |      |     |      |

| Input Resistance     | R <sub>IN2</sub> | RESET                           |                                                                 | 100  | 220  | 450 | kΩ   |

| input Resistance     | R <sub>IN3</sub> | TEST                            |                                                                 | _    | 70   | -   | K22  |

| OSC. Feedback        | Rfx              | XIN-XOUT                        |                                                                 | _    | 1.2  | -   |      |

| Resistance           | Rfxt             | XTIN-XTOUT                      |                                                                 | _    | 6    | -   | ΜΩ   |

| Output Leakage       | I <sub>LO1</sub> | Sink Open Drain Port            | $V_{DD} = 5.5 \text{ V}, V_{OUT} = 5.5 \text{ V}$               | _    | -    | 2   |      |

| Current              | I <sub>LO2</sub> | Tri-state Port                  | $V_{DD} = 5.5 \text{ V}, \ V_{OUT} = 5.5 \text{ V}/0 \text{ V}$ | _    | -    | ± 2 | μΑ   |

| "H" Output Voltage   | V <sub>OH2</sub> | Tri-state Port                  | $V_{DD} = 4.5 \text{ V}, I_{OH} = -0.7 \text{ mA}$              | 4.1  | -    | -   | V    |

| "L" Output Voltage   | V <sub>OL3</sub> | Except P0 and XOUT              | $V_{DD} = 4.5 \text{ V}, I_{OL} = 1.6 \text{ mA}$               | _    | -    | 0.4 | V    |

| #U# Q :              | I <sub>OL1</sub> | Except P0 and XOUT              | $V_{DD} = 4.5 \text{ V}, V_{OL} = 0.4 \text{ V}$                | 1.6  | -    | -   | mA   |

| "L" Output Current   | I <sub>OL3</sub> | P0                              | $V_{DD} = 4.5 \text{ V}, V_{OL} = 1.0 \text{ V}$                | - 20 |      | _   | IIIA |

| Supply Current under |                  |                                 | V <sub>DD</sub> = 5.5 V                                         |      | 5.5  | 7.0 |      |

| NORMAL1, 2 mode      |                  |                                 | V <sub>IN</sub> = 5.3 V/0.2 V                                   | _    | 3.5  | 7.0 |      |

| Supply Current under |                  |                                 | fc = 16 MHz                                                     |      | 2.8  | 3.5 | mA   |

| IDLE1, 2 mode        |                  |                                 | fs = 32.768 kHz                                                 | -    | 2.8  | 3.3 |      |

| Supply Current under |                  |                                 | V <sub>DD</sub> = 5.5 V                                         |      | 4.0  | 5.0 |      |

| NORMAL1, 2 mode      |                  |                                 | V <sub>IN</sub> = 5.3 V/0.2 V                                   | _    | 4.0  | 3.0 |      |

| Supply Current under |                  |                                 | fc = 8 MHz                                                      |      | 2.0  | 2.5 | mA   |

| IDLE1, 2 mode        | ] ,              |                                 | fs = 32.768 kHz                                                 | _    | 2.0  | 2.5 |      |

| Supply Current under | I <sub>DD</sub>  |                                 |                                                                 |      | 14   | 25  | _    |

| SLOW1 mode           |                  |                                 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                           | _    | 14   | 25  | μΑ   |

| Supply Current under |                  |                                 | $V_{DD} = 3.0 \text{ V}$                                        |      | 7.0  | 4.5 |      |

| SLEEP1 mode          |                  |                                 | $V_{IN} = 2.8 \text{ V}/0.2 \text{ V}$<br>fs = 32.768 kHz       |      | 7.0  | 15  | μΑ   |

| Supply Current under | ]                |                                 | 15 = 32./08 KHZ                                                 |      | 6.0  | 15  |      |

| SLEEP0 mode          |                  |                                 |                                                                 | -    | 6.0  | 15  | μA   |

| Supply Current under |                  |                                 | V <sub>DD</sub> = 5.5 V                                         |      | ۸.   | 10  |      |

| STOP mode            |                  |                                 | V <sub>IN</sub> = 5.3 V/0.2 V                                   | -    | 0.5  | 10  | μA   |

Note 1: Typical values are shown under  $T_{opr} = 25$ °C,  $V_{DD} = 5$  V, while conditions are not stated. Note 2: Input current  $I_{IN1}$ ,  $I_{IN3}$ : The current through pull-up or pull-down resistor is not included.

AC Characteristics

(1)  $(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

# ① CLOCK

| Parameter                    | Symbol           | Conditions                               | Min   | Тур. | Max   | Unit    |

|------------------------------|------------------|------------------------------------------|-------|------|-------|---------|

|                              |                  | NORMAL1, 2 mode                          | 0.25  |      | 4     |         |

| Machine Cycle Time           | +0.4             | IDLE0, 1, 2 mode                         | 0.25  | 1    | 4     |         |

| Machine Cycle Time           | tcy              | SLOW1, 2 mode                            | 117.6 |      | 122.2 | $\mu$ S |

|                              |                  | SLEEP0, 1, 2 mode                        | 117.6 | _    | 133.3 |         |

| High Level Clock Pulse Width | t <sub>WCH</sub> | External clock operation<br>(XIN input)  | 25    |      |       | 200     |

| Low Level Clock Pulse Width  | t <sub>WCL</sub> | fc = 16 MHz                              | 25    | ı    | 1     | ns      |

| High Level Clock Pulse Width | t <sub>WSH</sub> | External clock operation<br>(XTIN input) | 14.7  |      |       |         |

| Low Level Clock Pulse Width  | t <sub>WSL</sub> | fs = 32.768 kHz                          | 14.7  | -    | _     | μS      |

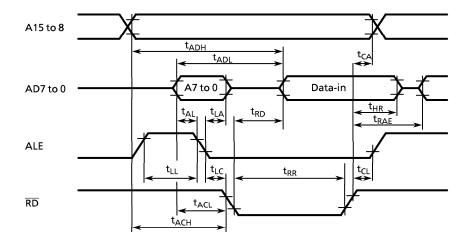

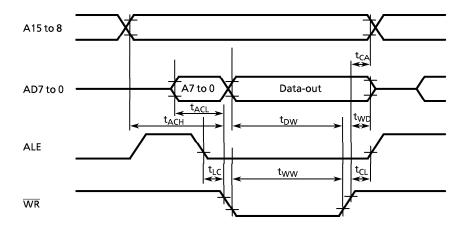

② External Memory Interface (Multiplexed Bus) at  $V_{DD} = 4.5$  to 5.5

| Na  | Cumple of        | Do no monto n                                                         | Vari                                                                        | able      | 16 N | ЛHz | Unit |

|-----|------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------|------|-----|------|

| No. | Symbol           | Parameter                                                             | Min                                                                         | Max       | Min  | Max | Unit |

| 1   | t <sub>AL</sub>  | A7 to 0 effective → ALE                                               | 0.5t – 15                                                                   |           | 16   |     | ns   |

| 2   | t <sub>LA</sub>  | ALE fall → A7 to 0 hold                                               | 0.5t – 20                                                                   |           | 11   |     | ns   |

| 3   | t <sub>LL</sub>  | ALE pulse width                                                       | t – 40                                                                      |           | 22   |     | ns   |

| 4   | t <sub>LC</sub>  | ALE fall → RD, WR fall                                                | 0.5t – 25                                                                   |           | 6    |     | ns   |

| 5   | t <sub>CL</sub>  | RD, WR rise → ALE rise                                                | 0.5t – 20                                                                   |           | 11   |     | ns   |

| 6   | t <sub>ACL</sub> | A7 to 0 effective $\rightarrow \overline{RD}$ , $\overline{WR}$ fall  | A7 to 0 effective $\rightarrow \overline{RD}$ , $\overline{WR}$ fall $t-25$ |           | 37   |     | ns   |

| 7   | t <sub>ACH</sub> | A15 to 8 effective $\rightarrow \overline{RD}$ , $\overline{WR}$ fall | 1.5t – 25                                                                   |           | 68   |     | ns   |

| 8   | t <sub>CA</sub>  | $\overline{RD}$ , $\overline{WR}$ rise $\rightarrow$ A15 to 8 hold    | 0.5t – 20                                                                   |           | 11   |     | ns   |

| 9   | t <sub>ADL</sub> | A7 to 0 effective $\rightarrow$ D7 to 0 input                         |                                                                             | 3t – 55   |      | 132 | ns   |

| 10  | t <sub>ADH</sub> | A15 to 8 effective $\rightarrow$ D7 to 0 input                        |                                                                             | 3.5t – 65 |      | 153 | ns   |

| 11  | t <sub>RD</sub>  | $\overline{RD}$ fall $\rightarrow$ D7 to 0 input                      |                                                                             | 2t – 60   |      | 65  | ns   |

| 12  | t <sub>RR</sub>  | RD pulse width                                                        | 2t – 40                                                                     |           | 85   |     | ns   |

| 13  | t <sub>HR</sub>  | $\overline{RD}$ rise $\rightarrow$ D7 to 0 hold                       | 0                                                                           |           | 0    |     | ns   |

| 14  | t <sub>RAE</sub> | $\overline{RD}$ rise $\rightarrow$ A7 to 0 effective                  | t – 15                                                                      |           | 47   |     | ns   |

| 15  | t <sub>WW</sub>  | WR pulse width                                                        | 2t – 40                                                                     |           | 85   |     | ns   |

| 16  | t <sub>DW</sub>  | D7 to 0 effective → WR rise                                           | 2t – 40                                                                     |           | 85   |     | ns   |

| 17  | t <sub>WD</sub>  | $\overline{\text{WR}}$ rise $\rightarrow$ D7 to 0 hold                | 0.5t – 15                                                                   |           | 16   |     | ns   |

Note: t = tcy/4 (t = 62.5 ns at fcgck = 16 MHz)

### A.C.Measurement Condition

Output Level: High 2.2 V/Low 0.8 V, CL = 50 pFHigh 2.4 V/Low 0.4 V (D7 to D0)

High 0.8 VDD/Low 0.2 VDD (Except D7 to D0) Input Level:

# Read Cycle

# Write Cycle

### **Recommended Oscillating Conditions - 1**

$$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$$

| Danamatan                  | 0 ''' '            | Oscillation |        |                   | Recommended Constant |                  |  |

|----------------------------|--------------------|-------------|--------|-------------------|----------------------|------------------|--|

| Parameter                  | Oscillator         | Frequency   | Recom  | mended Oscillator | C <sub>1</sub>       | C <sub>2</sub>   |  |

|                            |                    |             | MURATA | CSA16.00MXZ040    | 10 pF                | 10 pF            |  |

| Lieb francis               |                    | 8 MHz       | MURATA | CSA8.00MTZ        | 30 pF                | 30 pF            |  |

| High-frequency Oscillation | Ceramic Resonator  | 8 IVITIZ    |        | CST8.00MTW        | 30 pF (built-in)     | 30 pF (built-in) |  |

| Oscillation                |                    | 4.19 MHz    | MURATA | CSA4.19MG         | 30 pF                | 30 pF            |  |

|                            |                    | 4.19 WITZ   |        | CST4.19MGW        | 30 pF (built-in)     | 30 pF (built-in) |  |

| Low-frequency              | Crystal Oscillator | 32.768 kHz  | SII    | VT-200            | 6 pF                 | 6 pF             |  |

| Oscillation                | Crystal Oscillator | 32.700 KHZ  | ווכ    | V 1-200           | o pr                 | o pi             |  |

# Recommended Oscillating Conditions - 2

$$(V_{SS} = 0 \text{ V}, V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$$

| Davamatas      | 0 111 /           | Oscillation |                        |            | Recommended Constant |                  |  |

|----------------|-------------------|-------------|------------------------|------------|----------------------|------------------|--|

| Parameter      | Oscillator        | Frequency   | Recommended Oscillator |            | C <sub>1</sub>       | C <sub>2</sub>   |  |

|                | Ceramic Resonator | 8 MHz       | MURATA                 | CSA8.00MTZ | 30 pF                | 30 pF            |  |

| High-frequency |                   | OIVITZ      |                        | CST8.00MTW | 30 pF (built-in)     | 30 pF (built-in) |  |

| Oscillation    |                   | 4.40 8.411  | MURATA                 | CSA4.19MG  | 30 pF                | 30 pF            |  |

|                |                   | 4.19 MHz    |                        | CST4.19MGW | 30 pF (built-in)     | 30 pF (built-in) |  |

## Recommended Oscillating Conditions - 3

$$(V_{SS} = 0 \text{ V}, V_{DD} = 1.8 \text{ to } 5.5 \text{ V}, Topr = -40 \text{ to } 85^{\circ}\text{C})$$

| Donomoton      | 0 ''' 1           | Oscillation | Recommended Oscillator |            | Recommend        | ed Constant      |

|----------------|-------------------|-------------|------------------------|------------|------------------|------------------|

| Parameter      | Oscillator        | Frequency   |                        |            | C <sub>1</sub>   | C <sub>2</sub>   |

| High-frequency | Caramia Basanatar | 4 10 1411-  | MURATA                 | CSA4.19MG  | 30 pF            | 30 pF            |

| Oscillation    | Ceramic Resonator | 4.19 MHz    |                        | CST4.19MGW | 30 pF (built-in) | 30 pF (built-in) |

(1) High-frequency Oscillation

(2) Low-frequency Oscillation

- Note 1: An electrical shield by metal shield plate on the surface of IC package is recommended in order to protect the device from the high electric field stress applied from CRT (Cathodic Ray Tube) for continuous reliable operation.

- Note 2: The product numbers and specifications of the resonators by Murata Manufacturing Co., Ltd. are subject to change. For up-to-date information, please refer to the following URL;

http://www.murata.co.jp/search/index.html