# TPS6131x 1.5-A Multiple LED Camera Flash and Video Light Driver With I<sup>2</sup>C Compatible Interface

## 1 Features

- Operational Modes:

- Video Light and Flash Strobe

- Voltage Regulated Converter: 3.8 V to 5.7 V With Down Mode

- Standby: 2  $\mu$ A (Typical)

- LED V<sub>F</sub> Measurement

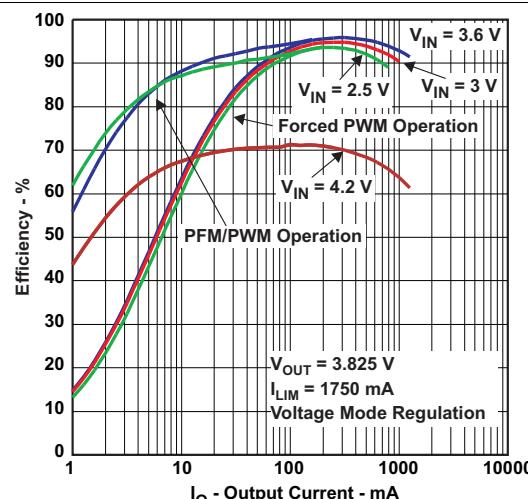

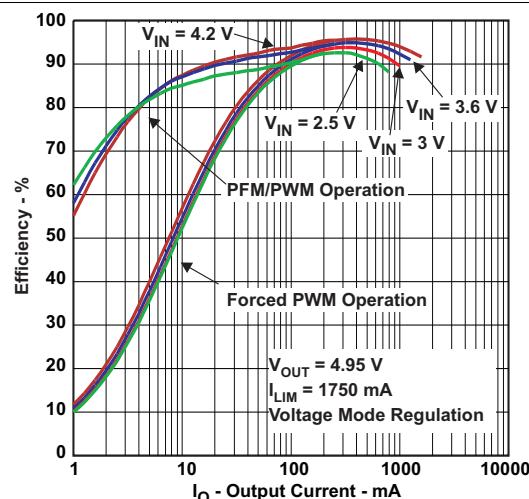

- Power-Save Mode for Improved Efficiency at Low Output Power, Up to 95% Efficiency

- I<sup>2</sup>C Compatible Interface up to 3.4 Mbps

- Dual Wire Camera Module Interface

- Zero Latency Tx-Masking Input

- Hardware Reset Input

- Privacy Indicator LED Output

- GPIO and Power Good Output

- Various Safe Operation and Robust Handling Features:

- LED Temperature Monitoring

- Open and Shorted LED Detection and Protection

- Integrated LED Safety Timer

- Automatic Battery Voltage Droop Monitoring and Protection

- Smooth LED Current Ramp-Up and Ramp-Down

- Undervoltage Lockout

- Total Solution Size of Less Than 25 mm<sup>2</sup>

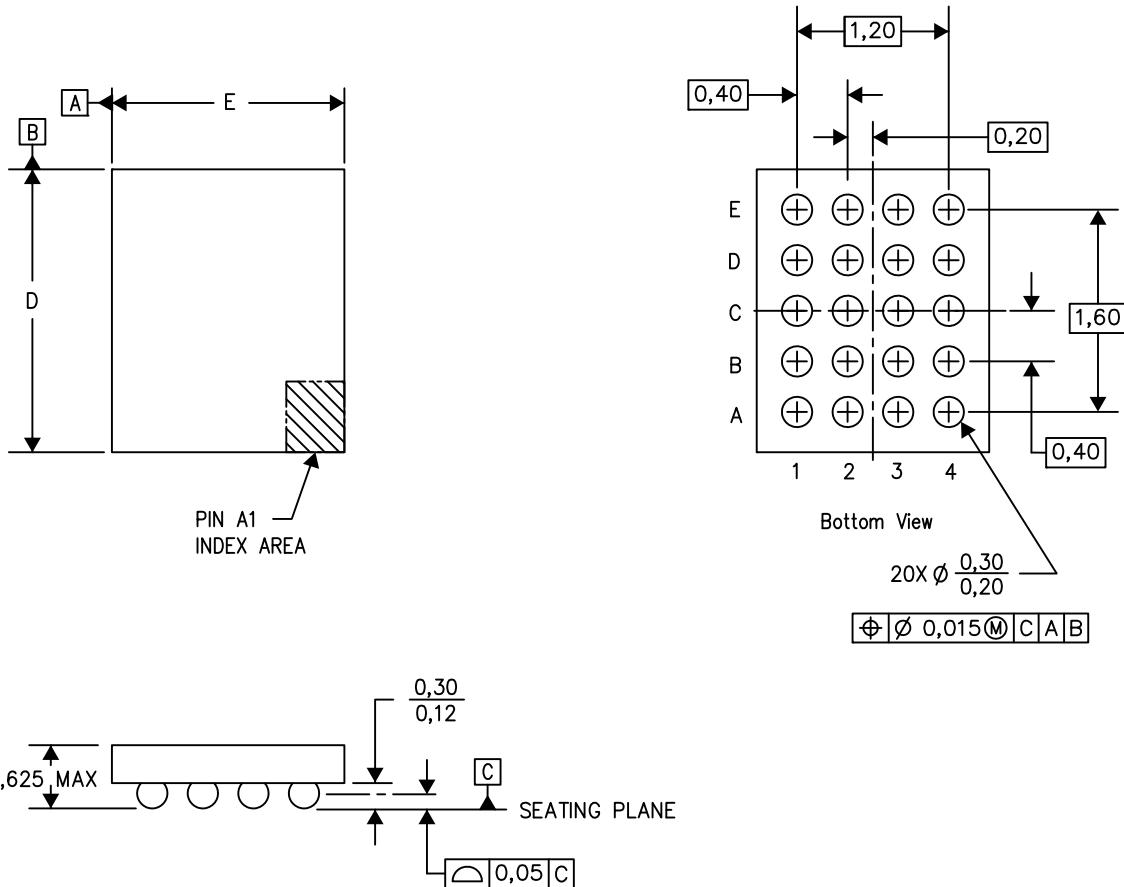

- Available in a 20-Pin NanoFree™ DSBGA Package

## 2 Applications

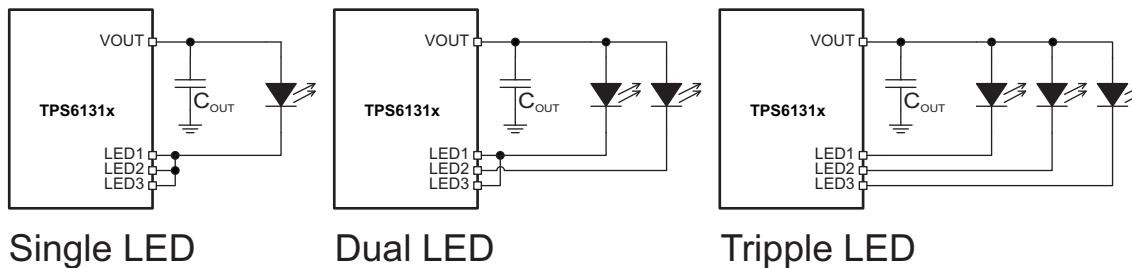

- Single, Dual, or Triple White LED Flash Supply for Cell Phones and Smart-Phones

- Video Lighting for Digital Video Applications

- General Lighting Applications

- Audio Amplifier Power Supply

## 3 Description

The TPS6131x family is an integrated solution with a wide feature set for driving up to three LEDs for still-camera flash strobe and video-camera lighting applications. It is based on a high efficiency synchronous boost topology with combinable current sinks to drive up to three white LEDs in parallel. The 2-MHz switching frequency allows the use of small and low-profile 2.2- $\mu$ H inductors. To optimize overall efficiency, the device operates with a low LED-feedback voltage and regulated output-voltage adaptation.

The device integrates a control scheme that automatically optimizes the LED current flash budget as a function of the battery voltage condition.

The TPS6131x not only operates as a regulated current source, but also as a standard voltage boost regulator. The device enters power-save mode operation at light load currents to maintain high efficiency over the entire load current range. These operating modes can be useful to supply other high power devices in the system (for example, a hands-free audio PA).

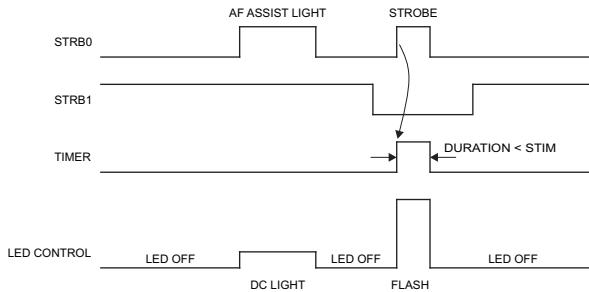

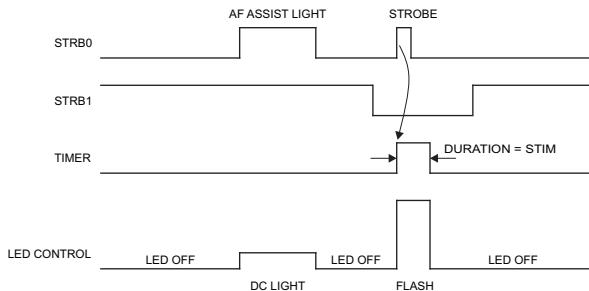

To simplify video light and flash synchronization with the camera module, the device offers a dedicated control interface (STRB0, STRB1) for zero latency LED turnon time.

### Device Information<sup>(1)</sup>

| PART NUMBER           | PACKAGE    | BODY SIZE (NOM)   |

|-----------------------|------------|-------------------|

| TPS61310,<br>TPS61311 | DSBGA (20) | 2.20 mm x 1.90 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

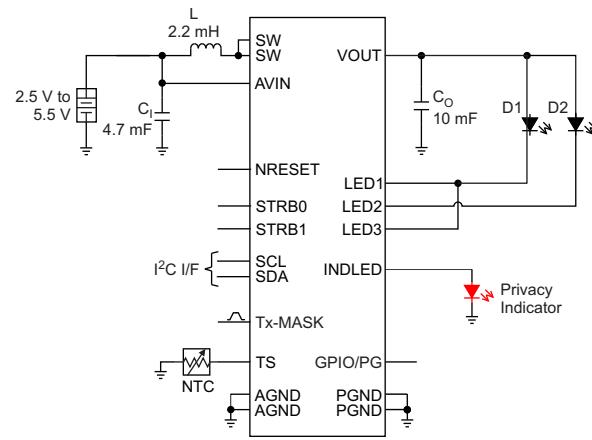

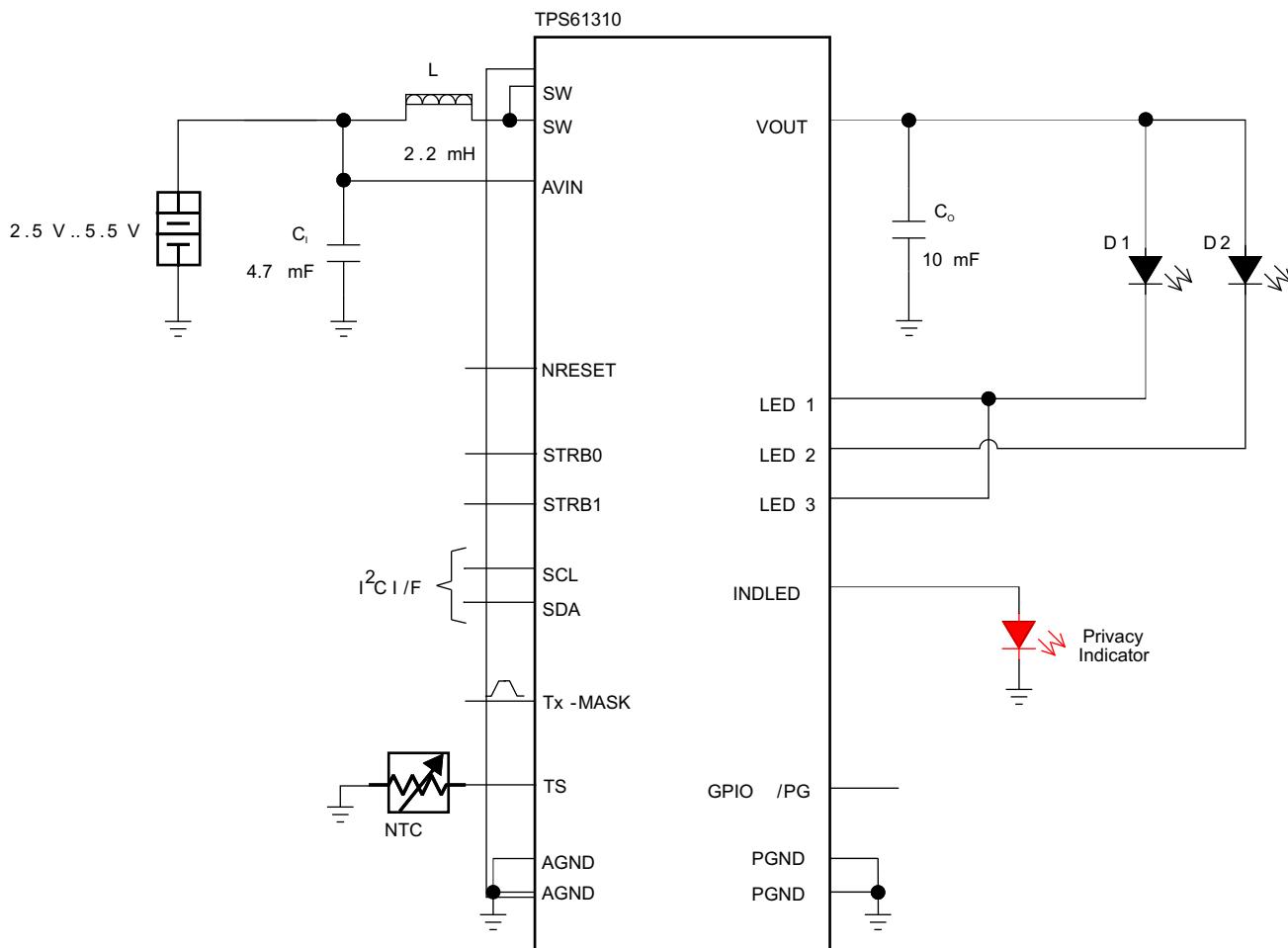

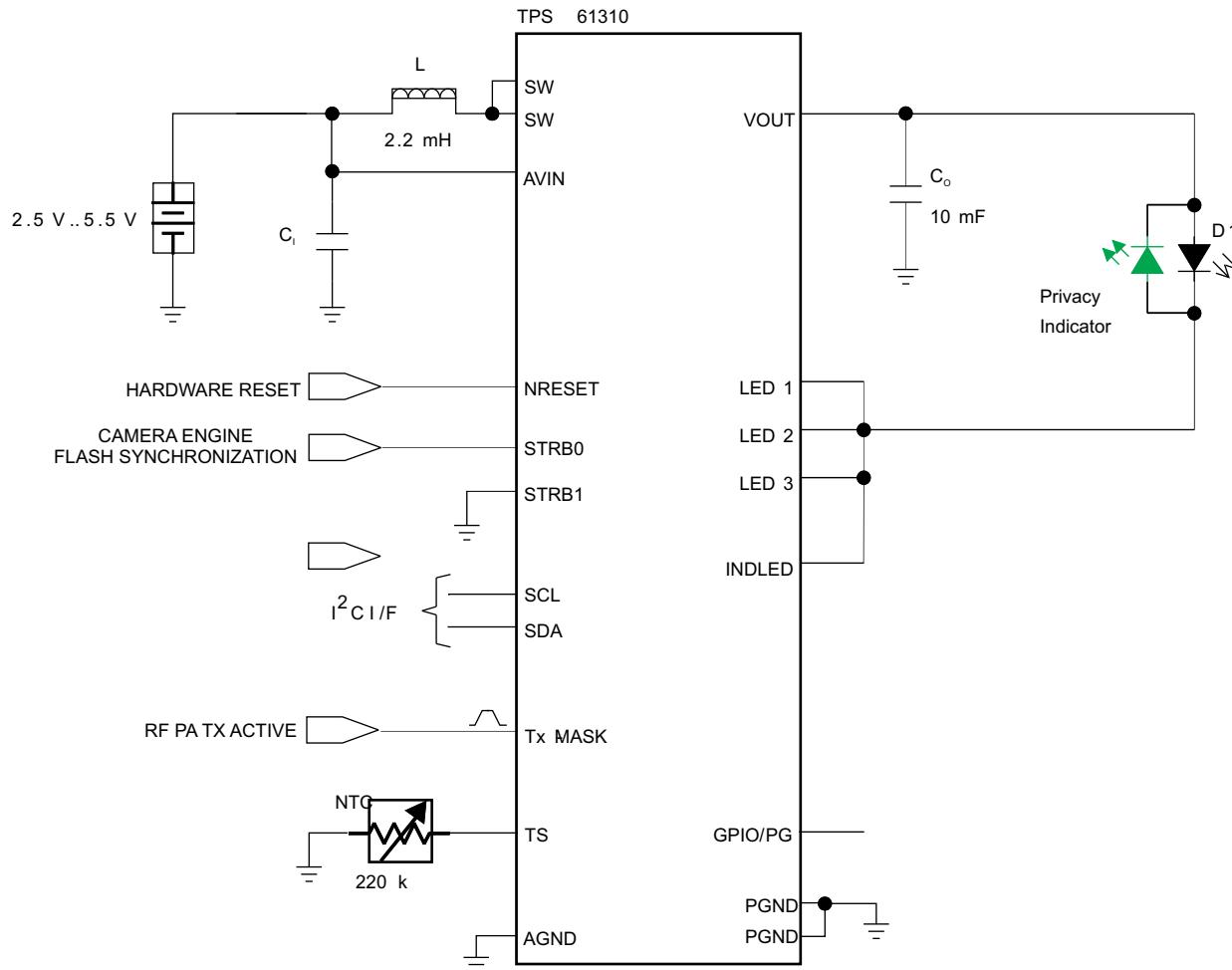

## Typical Application

Copyright © 2016, Texas Instruments Incorporated

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|          |                                                         |           |           |                                                                         |           |

|----------|---------------------------------------------------------|-----------|-----------|-------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Features</b> .....                                   | <b>1</b>  | 9.4       | Device Functional Modes.....                                            | 25        |

| <b>2</b> | <b>Applications</b> .....                               | <b>1</b>  | 9.5       | Register Maps.....                                                      | 30        |

| <b>3</b> | <b>Description</b> .....                                | <b>1</b>  | <b>10</b> | <b>Application and Implementation</b> .....                             | <b>38</b> |

| <b>4</b> | <b>Revision History</b> .....                           | <b>2</b>  | 10.1      | Application Information.....                                            | 38        |

| <b>5</b> | <b>Device Comparison Table</b> .....                    | <b>3</b>  | 10.2      | Typical Applications .....                                              | 38        |

| <b>6</b> | <b>Pin Configuration and Functions</b> .....            | <b>3</b>  | <b>11</b> | <b>Power Supply Recommendations</b> .....                               | <b>45</b> |

| <b>7</b> | <b>Specifications</b> .....                             | <b>4</b>  | <b>12</b> | <b>Layout</b> .....                                                     | <b>45</b> |

|          | 7.1 Absolute Maximum Ratings .....                      | 4         | 12.1      | Layout Guidelines .....                                                 | 45        |

|          | 7.2 ESD Ratings.....                                    | 4         | 12.2      | Layout Example .....                                                    | 46        |

|          | 7.3 Recommended Operating Conditions.....               | 4         | 12.3      | Thermal Considerations.....                                             | 46        |

|          | 7.4 Thermal Information .....                           | 5         | <b>13</b> | <b>Device and Documentation Support</b> .....                           | <b>48</b> |

|          | 7.5 Electrical Characteristics.....                     | 5         | 13.1      | Documentation Support .....                                             | 48        |

|          | 7.6 I <sup>2</sup> C Interface Timing Requirements..... | 7         | 13.2      | Related Links .....                                                     | 48        |

|          | 7.7 Dissipation Ratings .....                           | 8         | 13.3      | Receiving Notification of Documentation Updates                         | 48        |

|          | 7.8 Typical Characteristics.....                        | 9         | 13.4      | Community Resources.....                                                | 48        |

| <b>8</b> | <b>Parameter Measurement Information</b> .....          | <b>13</b> | 13.5      | Trademarks .....                                                        | 48        |

| <b>9</b> | <b>Detailed Description</b> .....                       | <b>14</b> | 13.6      | Electrostatic Discharge Caution .....                                   | 48        |

|          | 9.1 Overview .....                                      | 14        | 13.7      | Glossary .....                                                          | 48        |

|          | 9.2 Functional Block Diagram .....                      | 15        | <b>14</b> | <b>Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>48</b> |

|          | 9.3 Feature Description.....                            | 16        |           |                                                                         |           |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision C (November 2012) to Revision D                                                                                                                                                                                                                         | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • Added <i>Device Information</i> table, <i>ESD Ratings</i> table, <i>Recommended Operating Conditions</i> table, <i>Thermal Information</i> table, <i>Device and Documentation Support</i> section, and <i>Mechanical, Packaging, and Orderable Information</i> section..... | 1    |

| • Deleted <i>Ordering Information</i> table; see POA at the end of the data sheet.....                                                                                                                                                                                        | 1    |

| Changes from Revision B (September 2011) to Revision C          | Page |

|-----------------------------------------------------------------|------|

| • Added revision letter C to literature number.....             | 1    |

| • Added TPS61311 to ordering table .....                        | 3    |

| • Added Current Limit Setting for TPS61311 .....                | 21   |

| • Added current limit setting for TPS61311 in register map..... | 34   |

| Changes from Revision A (October 2010) to Revision B                | Page |

|---------------------------------------------------------------------|------|

| • Changed V <sub>UVLO</sub> to max value from 2.35 V to 2.4 V ..... | 5    |

| • Updated LED forward voltage calibration description. .....        | 24   |

| • Updated SFT bit description .....                                 | 33   |

## 5 Device Comparison Table

| PACKAGE  | DEVICE SPECIFIC FEATURES <sup>(1)</sup>      |

|----------|----------------------------------------------|

| TPS61310 | up to 1750-mA (typical) input valley current |

| TPS61311 | up to 2480-mA (typical) input valley current |

(1) For more details, see [Detailed Description](#) and [Application and Implementation](#).

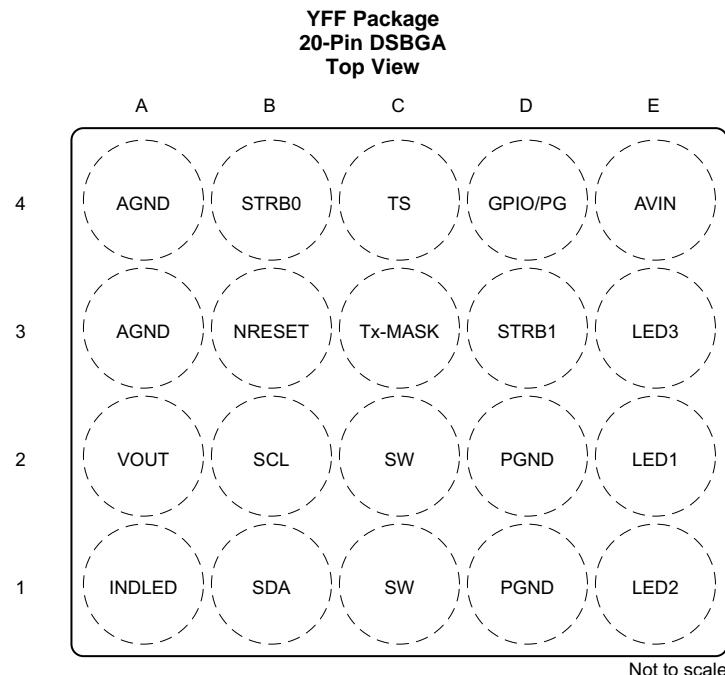

## 6 Pin Configuration and Functions

### Pin Functions

| PIN    |         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|--------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME    |     |                                                                                                                                                                                                                                                                                                                                                                                |

| A1     | INDLED  | O   | This pin provides a constant current source to drive low $V_F$ LEDs. Connect to LED anode.                                                                                                                                                                                                                                                                                     |

| A2     | VOUT    | O   | This is the output voltage pin of the converter.                                                                                                                                                                                                                                                                                                                               |

| A3, A4 | AGND    | —   | Analog ground.                                                                                                                                                                                                                                                                                                                                                                 |

| B1     | SDA     | I/O | Serial interface address and data line. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                             |

| B2     | SCL     | I   | Serial interface clock line. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                                        |

| B3     | NRESET  | I   | Master hardware reset input.<br>NRESET = LOW: The device is forced in shutdown mode and the I <sup>2</sup> C control I/F and all internal control registers are reset.<br>NRESET = HIGH: The device is operating normally under the control of the I <sup>2</sup> C interface.                                                                                                 |

| B4     | STRB0   | I   | LED1, LED2, and LED3 enable logic input. This pin can be used to enable or disable the high-power LEDs connected to the device.<br>STRB0 = LOW: LED1, LED2 and LED3 current regulators are turned off.<br>STRB0 = HIGH: LED2, LED2 and LED3 current regulators are active. The LED current level (video light or flash current) is defined according to the STRB1 logic level. |

| C1, C2 | SW      | I/O | Inductor connection. Drain of the internal power MOSFET. Connect to the switched side of the inductor. SW is high impedance during shutdown.                                                                                                                                                                                                                                   |

| C3     | Tx-MASK | I   | RF PA synchronization control input. Pulling this pin high turns the LED from flash to video light operation, thereby reducing almost instantaneously the peak current loading from the battery.                                                                                                                                                                               |

### Pin Functions (continued)

| PIN    |         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                      |

|--------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME    |     |                                                                                                                                                                                                                                                                                  |

| C4     | TS      | I   | NTC resistor connection. This pin can be used to monitor the LED temperature. Connect a 220-k $\Omega$ NTC resistor from the TS input to ground. In case this functionality is not desired, the TS input must be tied to AVIN or left floating.                                  |

| D1, D2 | PGND    | —   | Power ground. Connect to AGND underneath IC.                                                                                                                                                                                                                                     |

| D3     | STRB1   | I   | LED current level selection input. Pulling this input high disables the video light watchdog timer.<br>STRB1 = LOW: flash mode is enabled.<br>STRB1 = HIGH: video light mode is enabled.                                                                                         |

| D4     | GPIO/PG | I/O | This pin can either be configured as a general purpose I/O pin (GPIO) or either as an open-drain or a push-pull output to signal when the converters output voltage is within the regulation limits (PG). Per default, the pin is configured as an open-drain Power Good output. |

| E1     | LED2    | I   |                                                                                                                                                                                                                                                                                  |

| E2     | LED1    | I   | LED return input (current sinks). This feedback pin regulates the LED current through the internal sense resistor by regulating the voltage across it. Connect to the cathode of the white LEDs.                                                                                 |

| E3     | LED3    | I   |                                                                                                                                                                                                                                                                                  |

| E4     | AVIN    | I   | This is the input voltage pin of the device. Connect directly to the input bypass capacitor.                                                                                                                                                                                     |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

see <sup>(1)</sup>

|                                                              |                                                                                        | MIN                | MAX | UNIT |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------|-----|------|

| Voltage                                                      | AVIN, VOUT, SW, LED1, LED2, LED3, SCL, SDA, STRB0, STRB1, NRESET, GPIO/PG, Tx-MASK, TS | -0.3               | 7   | V    |

| Current on GPIO/PG                                           |                                                                                        | ±25                |     | mA   |

| Power dissipation                                            |                                                                                        | Internally limited |     |      |

| Operating ambient temperature, $T_A$ <sup>(2)</sup>          |                                                                                        | -40                | 85  | °C   |

| Maximum operating junction temperature, $T_J$ <sup>(2)</sup> |                                                                                        | 150                |     | °C   |

| Storage temperature, $T_{stg}$                               |                                                                                        | -65                | 150 | °C   |

- (1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

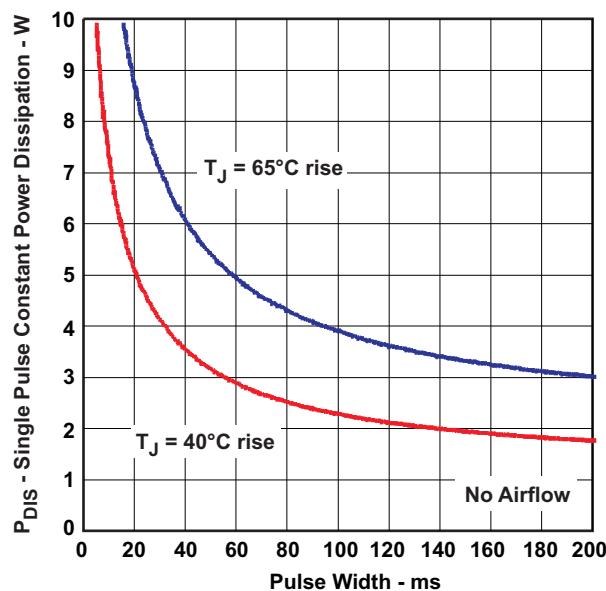

- (2) In applications where high power dissipation or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature [ $T_{A(max)}$ ] is dependent on the maximum operating junction temperature [ $T_{J(max)}$ ], the maximum power dissipation of the device in the application [ $P_{D(max)}$ ], and the junction-to-ambient thermal resistance of the part in the application ( $R_{\theta JA}$ ), as given by:  $T_{A(max)} = T_{J(max)} - (R_{\theta JA} \times P_{D(max)})$

### 7.2 ESD Ratings

|             |                         | VALUE                                                                          | UNIT  |

|-------------|-------------------------|--------------------------------------------------------------------------------|-------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |

|             |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |       |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|       |                                | MIN | MAX | UNIT |

|-------|--------------------------------|-----|-----|------|

| $T_J$ | Operating junction temperature | -40 | 125 | °C   |

## 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | TPS6131x    | UNIT |

|-------------------------------|----------------------------------------------|-------------|------|

|                               |                                              | YFF (DSBGA) |      |

|                               |                                              | 20 PINS     |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 71          | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 0.4         | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 21          | °C/W |

| $\psi_{JT}$                   | Junction-to-top characterization parameter   | 1.9         | °C/W |

| $\psi_{JB}$                   | Junction-to-board characterization parameter | 11.2        | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 7.5 Electrical Characteristics

Specification applies for  $V_{IN} = 3.6$  V over an operating junction temperature  $T_J = -40^\circ\text{C}$  to  $125^\circ\text{C}$ ; see [Figure 24](#) (unless otherwise noted). Typical values are for  $T_J = 25^\circ\text{C}$ .

| PARAMETER                                     | TEST CONDITIONS                                                                                    | MIN                                                                                               | TYP                    | MAX  | UNIT             |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------|------|------------------|

| <b>SUPPLY CURRENT</b>                         |                                                                                                    |                                                                                                   |                        |      |                  |

| $V_{IN}$                                      | Input voltage                                                                                      | 2.5                                                                                               | 5.5                    |      | V                |

| $I_Q$                                         | Operating quiescent current into AVIN                                                              | 590                                                                                               | 700                    |      | µA               |

|                                               | $I_{OUT(DC)} = 0$ mA, PWM operation $V_{OUT} = 4.95$ V, voltage regulation mode                    | 11.3                                                                                              |                        |      | mA               |

| $I_{SD}$                                      | Shutdown current                                                                                   | -40°C $\leq T_J \leq$ 85°C                                                                        | 1                      | 5    | µA               |

| $V_{UVLO}$                                    | Undervoltage lockout threshold (analog circuitry)                                                  | $V_{IN}$ falling                                                                                  | 2.3                    | 2.4  | V                |

| <b>OUTPUT</b>                                 |                                                                                                    |                                                                                                   |                        |      |                  |

| $V_{OUT}$                                     | Output voltage                                                                                     | Current regulation mode                                                                           | $V_{IN}$               | 5.5  | V                |

|                                               |                                                                                                    | Voltage regulation mode                                                                           | 3.825                  | 5.7  |                  |

|                                               | Internal feedback voltage accuracy                                                                 | 2.5 V $\leq V_{IN} \leq$ 4.8 V, -20°C $\leq T_J \leq$ 125°C, Boost mode, PWM voltage regulation   | -2%                    | 2%   |                  |

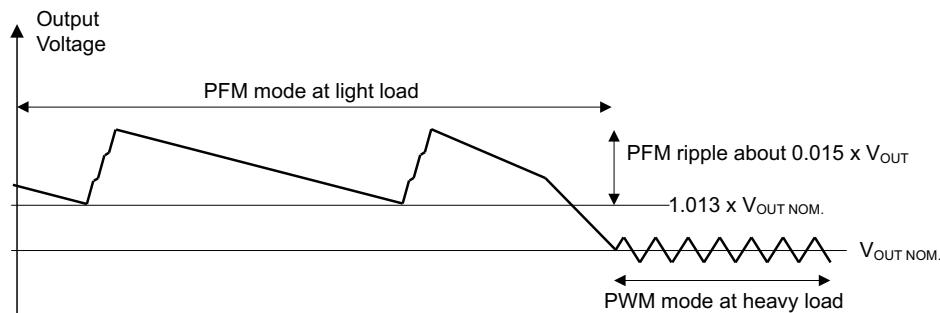

|                                               | Power-save mode ripple voltage                                                                     | $I_{OUT} = 10$ mA                                                                                 | $0.015 \times V_{OUT}$ |      | $V_{P-P}$        |

| $OVP$                                         | Output overvoltage protection                                                                      | $V_{OUT}$ rising, 0000 $\leq OV[3:0] \leq$ 0100                                                   | 4.5                    | 4.65 | 4.8              |

|                                               |                                                                                                    | $V_{OUT}$ rising, 0101 $\leq OV[3:0] \leq$ 1111                                                   | 5.8                    | 6    | 6.2              |

|                                               | Output overvoltage protection hysteresis                                                           | $V_{OUT}$ falling                                                                                 | 0.15                   |      |                  |

| <b>POWER SWITCH</b>                           |                                                                                                    |                                                                                                   |                        |      |                  |

| $r_{DS(on)}$                                  | Switch MOSFET ON-resistance                                                                        | $V_{OUT} = V_{GS} = 3.6$ V                                                                        | 90                     |      | $\text{m}\Omega$ |

|                                               | Rectifier MOSFET ON-resistance                                                                     | $V_{OUT} = V_{GS} = 3.6$ V                                                                        | 135                    |      | $\text{m}\Omega$ |

| $I_{lkg(SW)}$                                 | Leakage into SW                                                                                    | $V_{OUT} = 0$ V, SW = 3.6 V, -40°C $\leq T_J \leq$ 85°C                                           | 0.3                    | 4    | µA               |

| $I_{lim}$                                     | Rectifier valley current limit (open loop)                                                         | $V_{OUT} = 4.95$ V, -20°C $\leq T_J \leq$ 85°C, PWM operation, relative to selected ILIM          | -15%                   | 15%  |                  |

| <b>OSCILLATOR</b>                             |                                                                                                    |                                                                                                   |                        |      |                  |

| $f_{OSC}$                                     | Oscillator frequency                                                                               |                                                                                                   | 1.92                   |      | MHz              |

| $f_{ACC}$                                     | Oscillator frequency                                                                               |                                                                                                   | -10%                   | 7%   |                  |

| <b>THERMAL SHUTDOWN, HOT DIE DETECTOR</b>     |                                                                                                    |                                                                                                   |                        |      |                  |

| Thermal shutdown <sup>(1)</sup>               |                                                                                                    | 140                                                                                               | 160                    |      | °C               |

| Thermal shutdown hysteresis <sup>(1)</sup>    |                                                                                                    | 20                                                                                                |                        |      | °C               |

| Hot die detector accuracy <sup>(1)</sup>      |                                                                                                    | -8                                                                                                | 8                      |      | °C               |

| <b>LED CURRENT REGULATOR</b>                  |                                                                                                    |                                                                                                   |                        |      |                  |

| LED1 and LED3 current accuracy <sup>(2)</sup> | 0.4 V $\leq V_{LED[1,3]} \leq$ 2 V, 0 mA $\leq I_{LED[1,3]} \leq$ 100 mA, $T_J = 85^\circ\text{C}$ | -10%                                                                                              | 10%                    | 7.5% |                  |

|                                               |                                                                                                    | 0.4 V $\leq V_{LED[1,3]} \leq$ 2 V, 100 mA $< I_{LED[1,3]} \leq$ 400 mA, $T_J = 85^\circ\text{C}$ | -7.5%                  |      |                  |

(1) Verified by characterization. Not tested in production.

(2) Verified by characterization. Not tested in production.

## Electrical Characteristics (continued)

Specification applies for  $V_{IN} = 3.6$  V over an operating junction temperature  $T_J = -40^\circ\text{C}$  to  $125^\circ\text{C}$ ; see [Figure 24](#) (unless otherwise noted). Typical values are for  $T_J = 25^\circ\text{C}$ .

| PARAMETER                                               | TEST CONDITIONS                                                                                                  | MIN                                                                                    | TYP            | MAX  | UNIT |    |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------|------|------|----|

| LED2 current accuracy <sup>(2)</sup>                    | 0.4 V $\leq V_{LED2} \leq 2$ V,<br>0 mA $\leq I_{LED2} \leq 250$ mA, $T_J = 85^\circ\text{C}$                    | -10%                                                                                   | 10%            |      |      |    |

|                                                         | 0.4 V $\leq V_{LED2} \leq 2$ V,<br>250 mA $\leq I_{LED2} \leq 800$ mA, $T_J = 85^\circ\text{C}$                  | -7.5%                                                                                  | 7.5%           |      |      |    |

| LED1 and LED3 current matching <sup>(2)</sup>           |                                                                                                                  | -10%                                                                                   | 10%            |      |      |    |

| LED1, LED2, and LED3 current temperature coefficient    |                                                                                                                  |                                                                                        | 0.05           |      | %/°C |    |

| INDLED current accuracy                                 | 1.5 V $\leq (V_{IN} - V_{INDLED}) \leq 2.5$ V<br>2.6 mA $\leq I_{INDLED} \leq 15.8$ mA, $T_J = 25^\circ\text{C}$ | -20%                                                                                   | 20%            |      |      |    |

| INDLED current temperature coefficient                  |                                                                                                                  |                                                                                        | 0.05           |      | %/°C |    |

| LED1, LED2, and LED3 sense voltage                      | $I_{LED[1,2,3]} = \text{full-scale current}$                                                                     | 400                                                                                    |                |      | mV   |    |

| $V_{DO}$ VOUT dropout voltage                           | $I_{OUT} = -15.8$ mA, $T_J = 25^\circ\text{C}$ , device not switching                                            |                                                                                        | 250            |      | mV   |    |

| LED1, LED2, and LED3 input leakage current              | $V_{LED[1,2,3]} = V_{OUT} = 5$ V, $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$                             | 0.1                                                                                    | 4              |      | μA   |    |

| INDLED input leakage current                            | $V_{INDLED} = 0$ V, $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$                                           | 0.1                                                                                    | 1              |      | μA   |    |

| <b>LED TEMPERATURE MONITORING</b>                       |                                                                                                                  |                                                                                        |                |      |      |    |

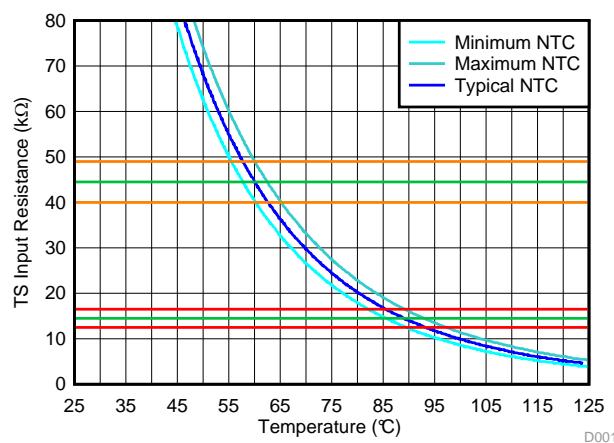

| $I_{O(TS)}$                                             | Temperature Sense Current Source                                                                                 | Thermistor bias current                                                                | 23.8           |      | μA   |    |

|                                                         | TS Resistance (Warning Temperature)                                                                              | LEDWARN bit = 1                                                                        | 39             | 44.5 | 50   | kΩ |

|                                                         | TS Resistance (Hot Temperature)                                                                                  | LEDHOT bit = 1                                                                         | 12.5           | 14.5 | 16.5 | kΩ |

| <b>SDA, SCL, GPIO/PG, Tx-MASK, STRB0, STRB1, NRESET</b> |                                                                                                                  |                                                                                        |                |      |      |    |

| $V_{(IH)}$                                              | High-level input voltage                                                                                         |                                                                                        | 1.2            |      | V    |    |

| $V_{(IL)}$                                              | Low-level input voltage                                                                                          |                                                                                        |                | 0.4  | V    |    |

| $V_{(OL)}$                                              | Low-level output voltage (SDA)                                                                                   | $I_{OL} = 8$ mA                                                                        |                | 0.3  | V    |    |

|                                                         | Low-level output voltage (GPIO)                                                                                  | DIR = 1, $I_{OL} = 5$ mA                                                               |                | 0.3  |      |    |

| $V_{(OH)}$                                              | High-level output voltage (GPIO)                                                                                 | DIR = 1, GPIOTYPE = 0, $I_{OH} = 8$ mA                                                 | $V_{IN} - 0.4$ |      | V    |    |

| $I_{(LKG)}$                                             | Logic input leakage current                                                                                      | Input connected to $V_{IN}$ or GND, $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ | 0.01           | 0.1  | μA   |    |

| $R_{PD}$                                                | STRB0, STRB1 pulldown resistance                                                                                 | STRB0, STRB1 $\leq 0.4$ V                                                              | 400            |      | kΩ   |    |

|                                                         | NRESET pulldown resistance                                                                                       | NRESET $\leq 0.4$ V                                                                    | 400            |      |      |    |

|                                                         | Tx-MASK pulldown resistance                                                                                      | Tx-MASK $\leq 0.4$ V                                                                   | 400            |      |      |    |

| $C_{(IN)}$                                              | SDA Input Capacitance                                                                                            | $SDA = V_{IN}$ or GND                                                                  | 9              |      | pF   |    |

|                                                         | SCL Input Capacitance                                                                                            | $SCL = V_{IN}$ or GND                                                                  | 4              |      |      |    |

|                                                         | GPIO/PG Input Capacitance                                                                                        | DIR = 0, GPIO/PG = $V_{IN}$ or GND                                                     | 9              |      |      |    |

|                                                         | STRB0 Input Capacitance                                                                                          | STRB0 = $V_{IN}$ or GND                                                                | 3              |      |      |    |

|                                                         | STRB1 Input Capacitance                                                                                          | STRB1 = $V_{IN}$ or GND                                                                | 3              |      |      |    |

|                                                         | NRESET Input Capacitance                                                                                         | NRESET = $V_{IN}$ or GND                                                               | 3.5            |      |      |    |

|                                                         | Tx-MASK Input Capacitance                                                                                        | Tx-MASK = $V_{IN}$ or GND                                                              | 4              |      |      |    |

| <b>TIMING</b>                                           |                                                                                                                  |                                                                                        |                |      |      |    |

| $t_{NRESET}$                                            | Reset pulse width                                                                                                |                                                                                        | 10             |      | μs   |    |

|                                                         | Start-up time                                                                                                    | From shutdown into video light mode<br>$I_{LED} = 150$ mA                              | 1.2            |      | ms   |    |

|                                                         | LED current settling time <sup>(3)</sup> triggered by a rising edge on STRB0                                     | MODE_CTRL[1:0] = 10, $I_{LED2}$ = from 0 mA to 950 mA                                  | 500            |      | μs   |    |

|                                                         | LED current settling time <sup>(3)</sup> triggered by Tx-MASK                                                    | MODE_CTRL[1:0] = 10, $I_{LED2}$ = from 950 mA to 150 mA                                | 20             |      | μs   |    |

(3) Settling time to  $\pm 15\%$  of the target value.

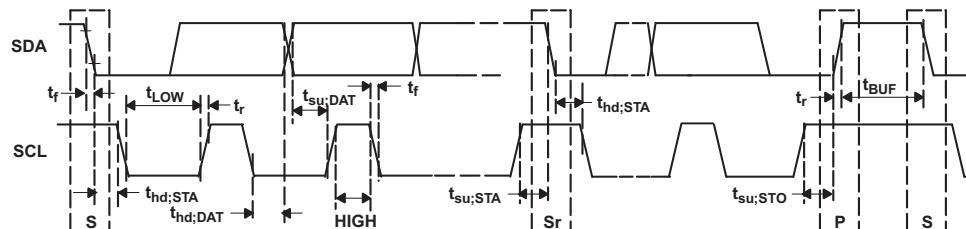

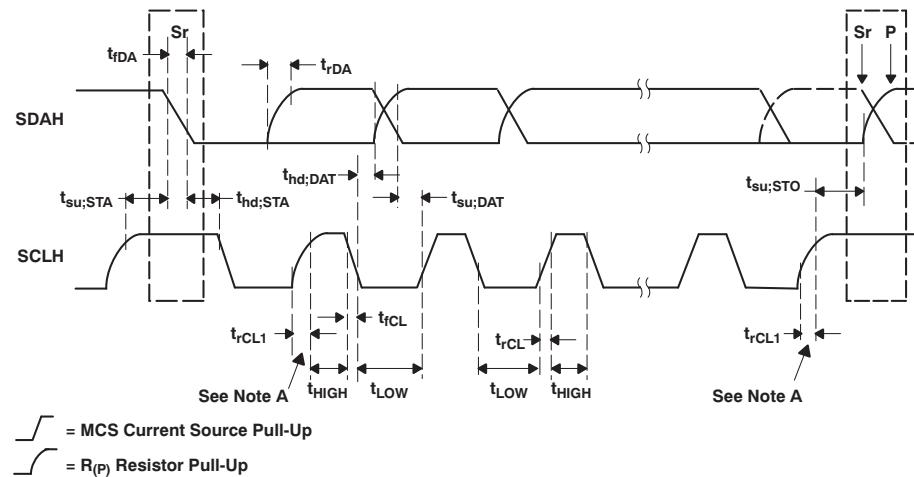

## 7.6 I<sup>2</sup>C Interface Timing Requirements

see <sup>(1)</sup>

|                   |                                                                                       |                                                               | MIN                   | MAX  | UNIT          |

|-------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------|------|---------------|

| $f_{SCL}$         | SCL Clock Frequency                                                                   | Standard mode                                                 |                       | 100  | kHz           |

|                   |                                                                                       | Fast mode                                                     |                       | 400  |               |

|                   |                                                                                       | High-speed mode (write operation), $C_B = 100 \text{ pF}$ max |                       | 3.4  | MHz           |

|                   |                                                                                       | High-speed mode (read operation), $C_B = 100 \text{ pF}$ max  |                       | 3.4  |               |

|                   |                                                                                       | High-speed mode (write operation), $C_B = 400 \text{ pF}$ max |                       | 1.7  |               |

|                   |                                                                                       | High-speed mode (read operation), $C_B = 400 \text{ pF}$ max  |                       | 1.7  |               |

| $t_{BUF}$         | Bus Free Time Between a STOP and START Condition                                      | Standard mode                                                 | 4.7                   |      | $\mu\text{s}$ |

|                   |                                                                                       | Fast mode                                                     | 1.3                   |      |               |

| $t_{HD}, t_{STA}$ | Hold Time (Repeated) START Condition                                                  | Standard mode                                                 | 4                     |      | $\mu\text{s}$ |

|                   |                                                                                       | Fast mode                                                     | 600                   |      | ns            |

|                   |                                                                                       | High-speed mode                                               | 160                   |      |               |

| $t_{LOW}$         | LOW Period of the SCL Clock                                                           | Standard mode                                                 | 4.7                   |      | $\mu\text{s}$ |

|                   |                                                                                       | Fast mode                                                     | 1.3                   |      |               |

|                   |                                                                                       | High-speed mode, $C_B = 100 \text{ pF}$ max                   | 160                   |      | ns            |

|                   |                                                                                       | High-speed mode, $C_B = 400 \text{ pF}$ max                   | 320                   |      |               |

| $t_{HIGH}$        | HIGH Period of the SCL Clock                                                          | Standard mode                                                 | 4                     |      | $\mu\text{s}$ |

|                   |                                                                                       | Fast mode                                                     | 600                   |      | ns            |

|                   |                                                                                       | High-speed mode, $C_B = 100 \text{ pF}$ max                   | 60                    |      |               |

|                   |                                                                                       | High-speed mode, $C_B = 400 \text{ pF}$ max                   | 120                   |      |               |

| $t_{SU}, t_{STA}$ | Setup Time for a Repeated START Condition                                             | Standard mode                                                 | 4.7                   |      | $\mu\text{s}$ |

|                   |                                                                                       | Fast mode                                                     | 600                   |      | ns            |

|                   |                                                                                       | High-speed mode                                               | 160                   |      |               |

| $t_{SU}, t_{DAT}$ | Data Setup Time                                                                       | Standard mode                                                 | 250                   |      | ns            |

|                   |                                                                                       | Fast mode                                                     | 100                   |      |               |

|                   |                                                                                       | High-speed mode                                               | 10                    |      |               |

| $t_{HD}, t_{DAT}$ | Data Hold Time                                                                        | Standard mode                                                 | 0                     | 3.45 | $\mu\text{s}$ |

|                   |                                                                                       | Fast mode                                                     | 0                     | 0.9  |               |

|                   |                                                                                       | High-speed mode, $C_B = 100 \text{ pF}$ max                   | 0                     | 70   | ns            |

|                   |                                                                                       | High-speed mode, $C_B = 400 \text{ pF}$ max                   | 0                     | 150  |               |

| $t_{RCL}$         | Rise Time of SCL Signal                                                               | Standard mode                                                 | 20 + 0.1 $\times C_B$ | 1000 | ns            |

|                   |                                                                                       | Fast mode                                                     | 20 + 0.1 $\times C_B$ | 300  |               |

|                   |                                                                                       | High-speed mode, $C_B = 100 \text{ pF}$ max                   | 10                    | 40   |               |

|                   |                                                                                       | High-speed mode, $C_B = 400 \text{ pF}$ max                   | 20                    | 80   |               |

| $t_{RCL1}$        | Rise Time of SCL Signal After a Repeated START Condition and After an Acknowledge BIT | Standard mode                                                 | 20 + 0.1 $\times C_B$ | 1000 | ns            |

|                   |                                                                                       | Fast mode                                                     | 20 + 0.1 $\times C_B$ | 300  |               |

|                   |                                                                                       | High-speed mode, $C_B = 100 \text{ pF}$ max                   | 10                    | 80   |               |

|                   |                                                                                       | High-speed mode, $C_B = 400 \text{ pF}$ max                   | 20                    | 160  |               |

| $t_{FCL}$         | Fall Time of SCL Signal                                                               | Standard mode                                                 | 20 + 0.1 $\times C_B$ | 300  | ns            |

|                   |                                                                                       | Fast mode                                                     | 20 + 0.1 $\times C_B$ | 300  |               |

|                   |                                                                                       | High-speed mode, $C_B = 100 \text{ pF}$ max                   | 10                    | 40   |               |

|                   |                                                                                       | High-speed mode, $C_B = 400 \text{ pF}$ max                   | 20                    | 80   |               |

| $t_{RDA}$         | Rise Time of SDA Signal                                                               | Standard mode                                                 | 20 + 0.1 $\times C_B$ | 1000 | ns            |

|                   |                                                                                       | Fast mode                                                     | 20 + 0.1 $\times C_B$ | 300  |               |

|                   |                                                                                       | High-speed mode, $C_B = 100 \text{ pF}$ max                   | 10                    | 80   |               |

|                   |                                                                                       | High-speed mode, $C_B = 400 \text{ pF}$ max                   | 20                    | 160  |               |

(1) Specified by design. Not tested in production.

## I<sup>2</sup>C Interface Timing Requirements (continued)

see (1)

|                   |                                 | MIN                                         | MAX                   | UNIT          |    |

|-------------------|---------------------------------|---------------------------------------------|-----------------------|---------------|----|

| $t_{FDA}$         | Fall Time of SDA Signal         | Standard mode                               | $20 + 0.1 \times C_B$ | 300           | ns |

|                   |                                 | Fast mode                                   | $20 + 0.1 \times C_B$ | 300           |    |

|                   |                                 | High-speed mode, $C_B = 100 \text{ pF}$ max | 10                    | 80            |    |

|                   |                                 | High-speed mode, $C_B = 400 \text{ pF}$ max | 20                    | 160           |    |

| $t_{SU}, t_{STO}$ | Setup Time for STOP Condition   | Standard mode                               | 4                     | $\mu\text{s}$ | ns |

|                   |                                 | Fast mode                                   | 600                   |               |    |

|                   |                                 | High-speed mode                             | 160                   |               |    |

| $C_B$             | Capacitive Load for SDA and SCL |                                             | 400                   | $\text{pF}$   |    |

## 7.7 Dissipation Ratings

| PACKAGE | POWER RATING ( $T_A = 25^\circ\text{C}$ ) | DERATING FACTOR ABOVE $T_A = 25^\circ\text{C}^{(1)}$ |

|---------|-------------------------------------------|------------------------------------------------------|

| YFF     | 1.4 W                                     | 14 mW/°C                                             |

(1) Maximum power dissipation is a function of  $T_{J(max)}$ ,  $R_{\theta JA}$  and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = (T_{J(max)} - T_A) / R_{\theta JA}$ .

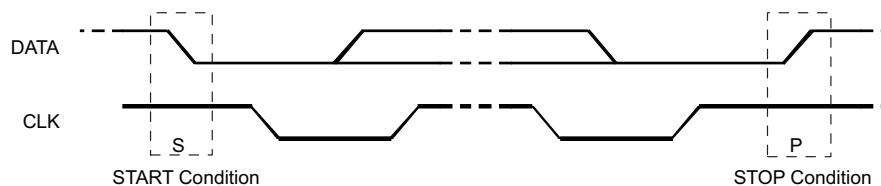

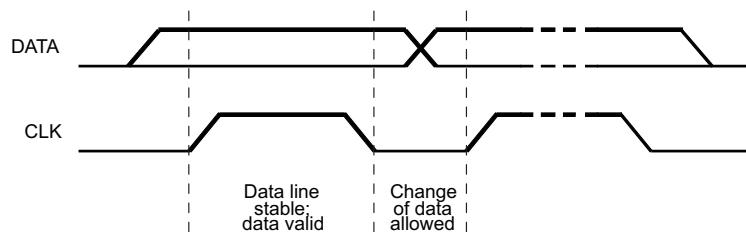

**Figure 1. Serial Interface Timing For F/S-Mode**

Note A: First rising edge of the SCLH signal after Sr and after each acknowledge bit.

**Figure 2. Serial Interface Timing For H/S-Mode**

## 7.8 Typical Characteristics

**Table 1. Table of Graphs**

| CAPTION                         |                             | FIGURE                                                   |

|---------------------------------|-----------------------------|----------------------------------------------------------|

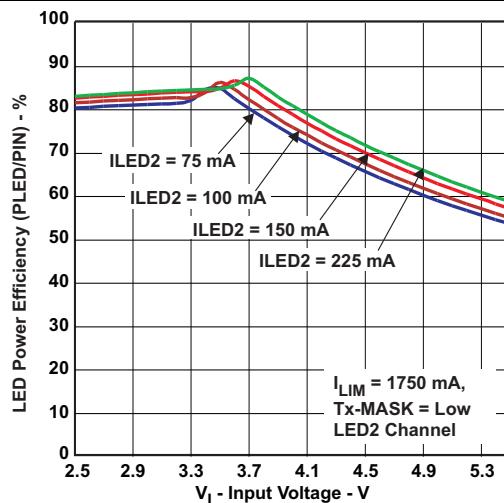

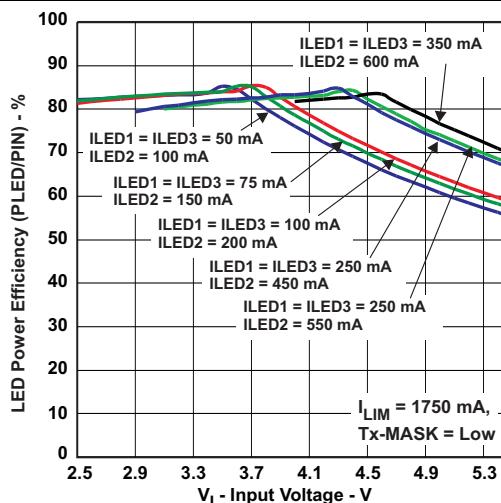

| LED Power Efficiency            | Input Voltage               | <a href="#">Figure 3, Figure 4</a>                       |

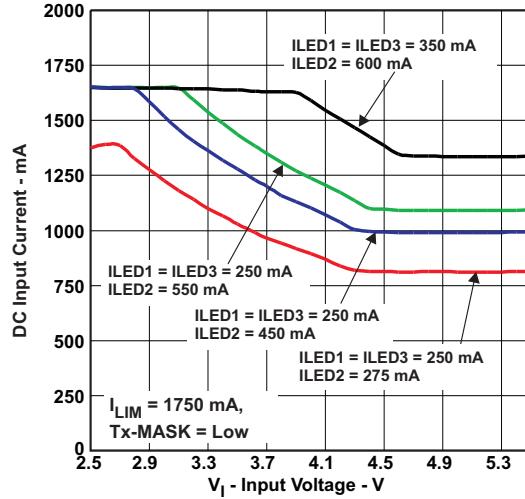

| DC Input Current                | Input Voltage               | <a href="#">Figure 5</a>                                 |

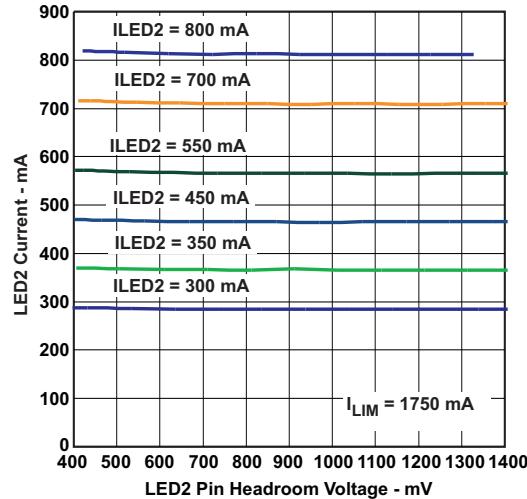

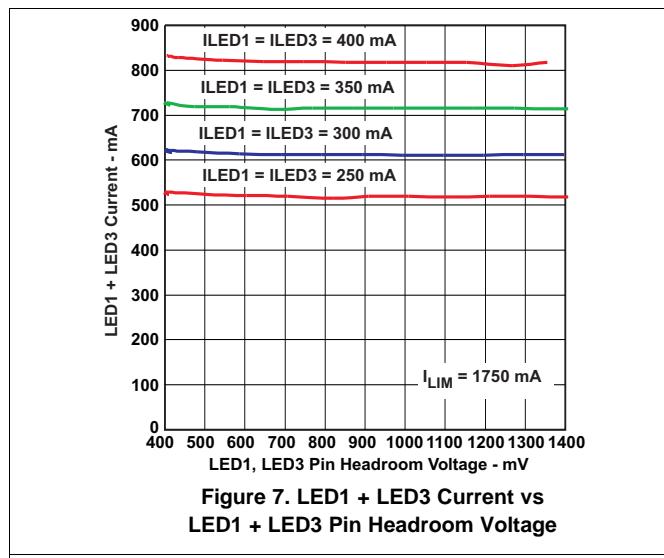

| LED Current                     | LED Pin Headroom Voltage    | <a href="#">Figure 6, Figure 7</a>                       |

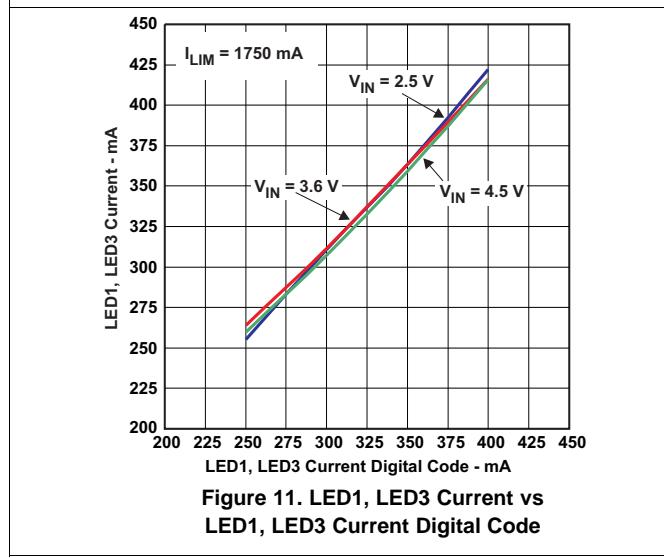

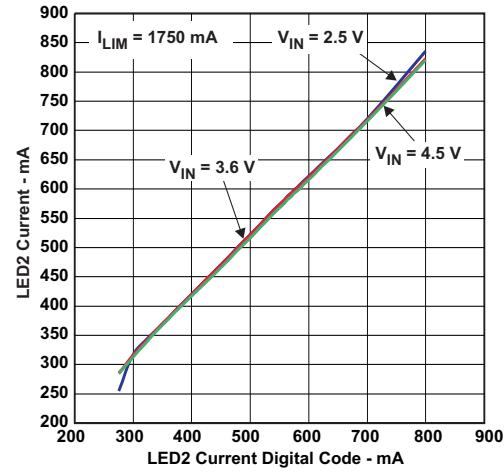

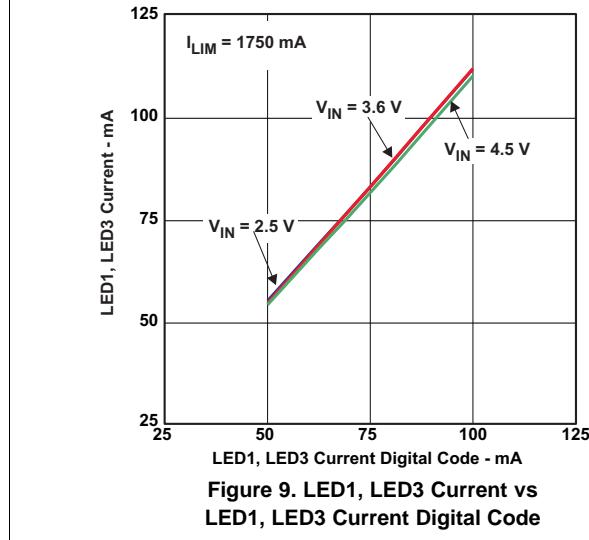

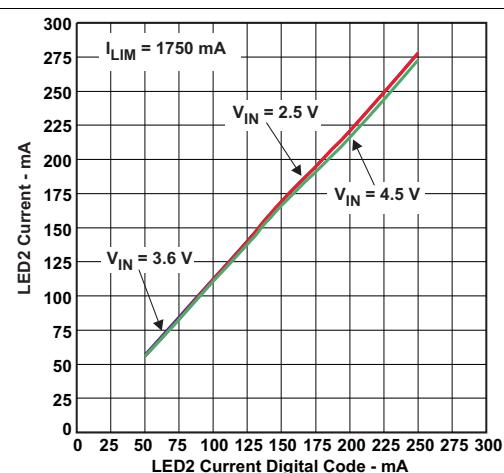

| LED Current                     | LED Current Digital Code    | <a href="#">Figure 8, Figure 9, Figure 10, Figure 11</a> |

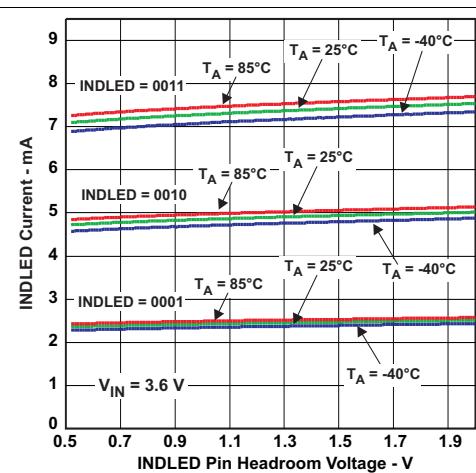

| INDLED Current                  | INDLED Pin Headroom Voltage | <a href="#">Figure 12</a>                                |

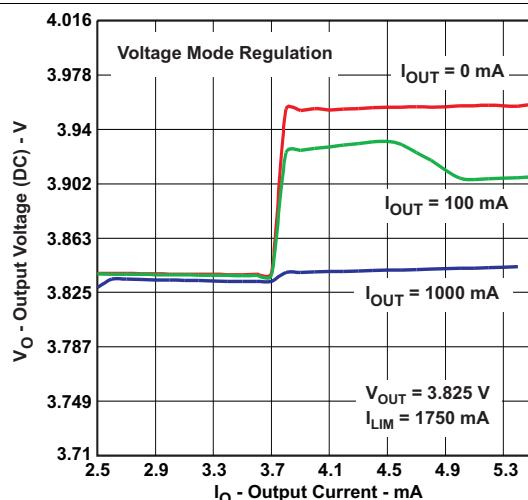

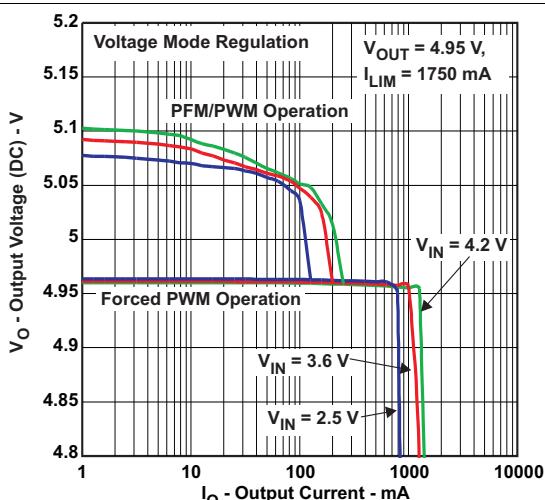

| Efficiency                      | Output Current              | <a href="#">Figure 13, Figure 14</a>                     |

| DC Output Voltage               | Load Current                | <a href="#">Figure 15, Figure 16</a>                     |

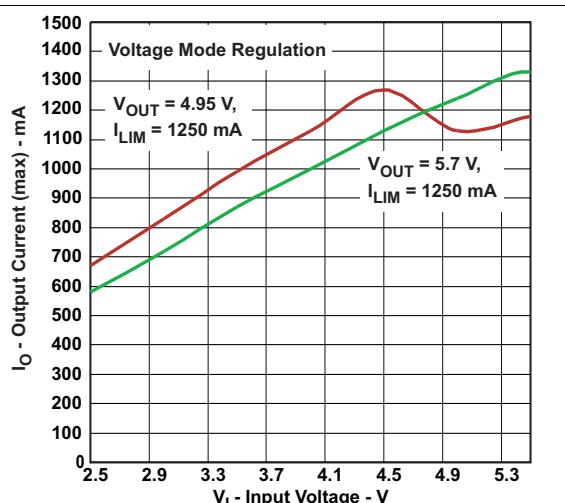

| Maximum Output Current          | Input Voltage               | <a href="#">Figure 17</a>                                |

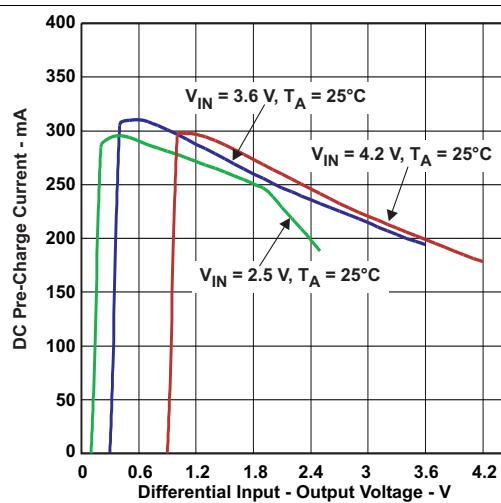

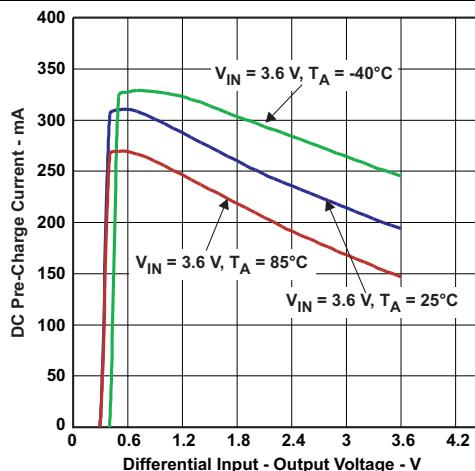

| DC Precharge Current            | Differential I/O Voltage    | <a href="#">Figure 18, Figure 19</a>                     |

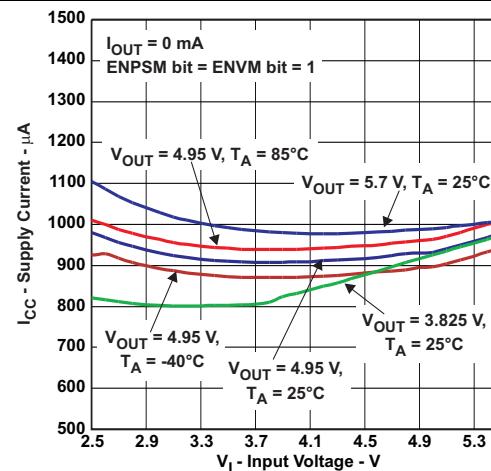

| Supply Current                  | Input Voltage               | <a href="#">Figure 20</a>                                |

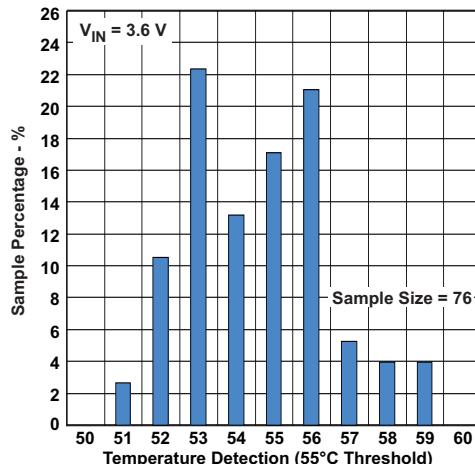

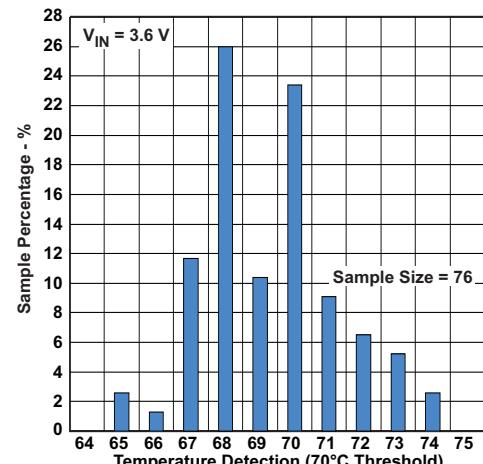

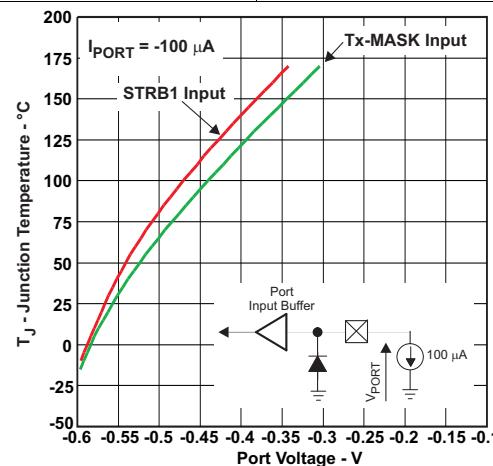

| Temperature Detection Threshold |                             | <a href="#">Figure 21, Figure 22</a>                     |

| Junction Temperature            | Port Voltage                | <a href="#">Figure 23</a>                                |

**Figure 3. LED Power Efficiency vs Input Voltage**

**Figure 4. LED Power Efficiency vs Input Voltage**

**Figure 5. DC Input Current vs Input Voltage**

**Figure 6. LED2 Current vs LED2 Pin Headroom Voltage**

## Typical Characteristics (continued)

## Typical Characteristics (continued)

## Typical Characteristics (continued)

**Figure 19. DC Pre-charge Current vs Differential I/O Voltage**

**Figure 20. Supply Current vs Input Voltage**

**Figure 21. Temperature Detection Threshold**

**Figure 22. Temperature Detection Threshold**

**Figure 23. Junction Temperature vs Port Voltage**

## 8 Parameter Measurement Information

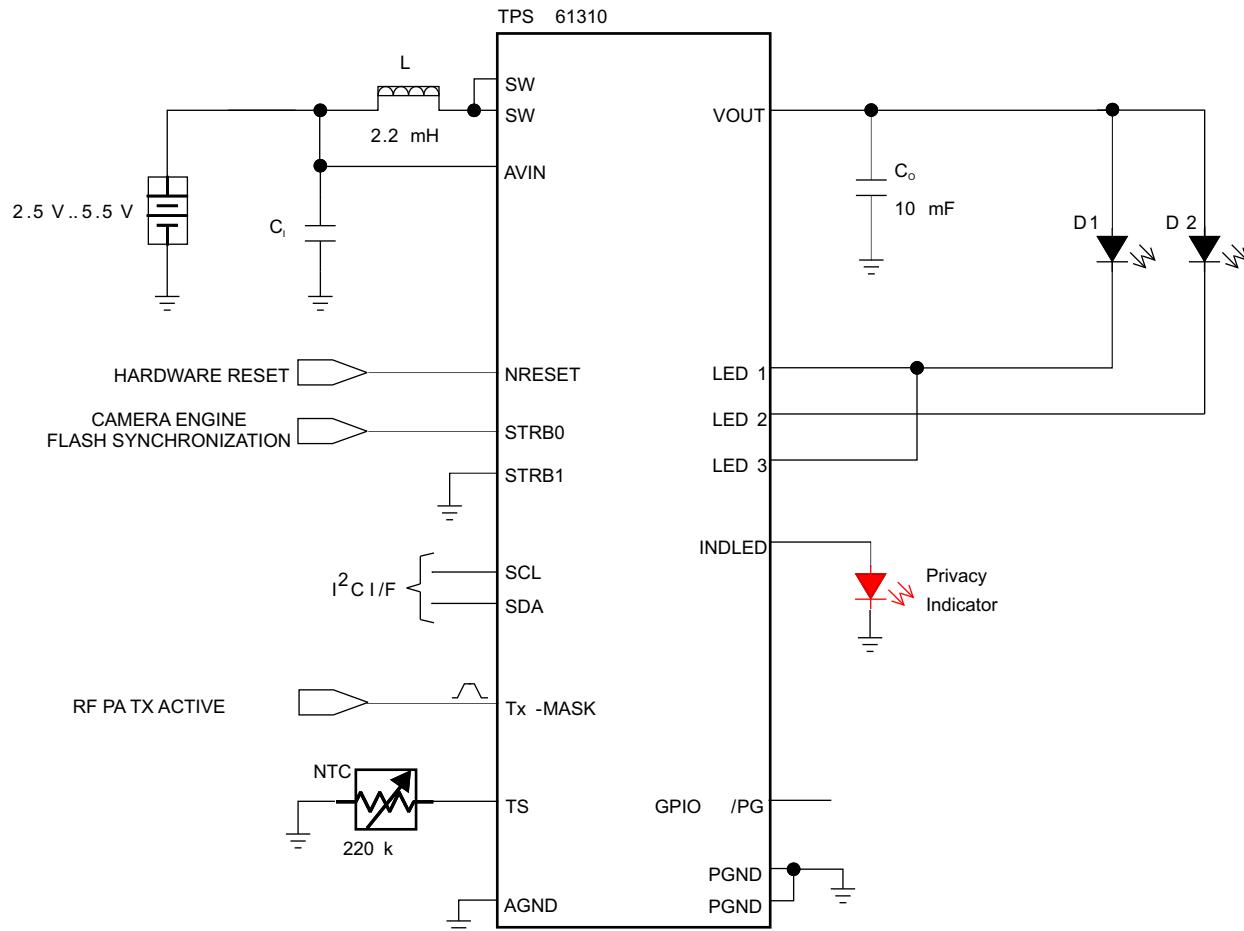

Copyright © 2016, Texas Instruments Incorporated

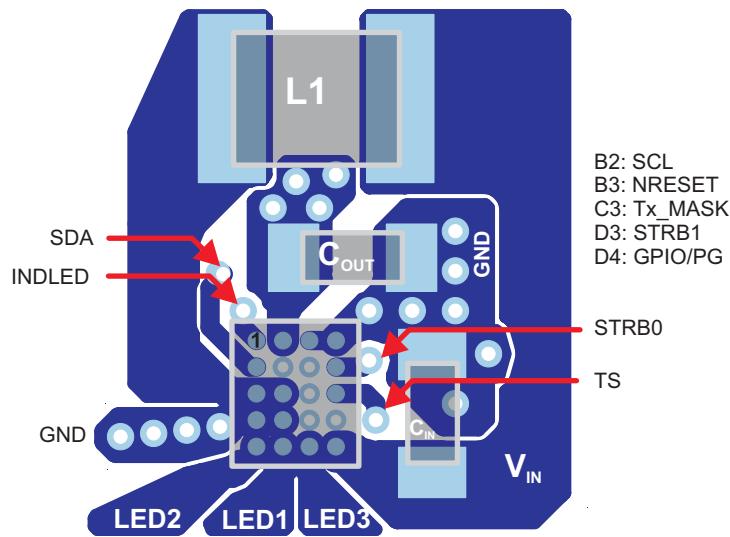

L = 2.2- $\mu$ H

C<sub>i</sub>, C<sub>o</sub> = 10- $\mu$ F, 6.3-V X5R 0603

NTC = 220-k $\Omega$

**Figure 24. TPS61310 Typical Application Circuit**

## 9 Detailed Description

### 9.1 Overview

The TPS6131x family is an integrated solution with a wide feature set for driving up to three LEDs for still-camera flash and video-camera lighting applications. It employs a 2-MHz fixed on-time, PWM current-mode converter to generate the output voltage required to drive up to three high-power LEDs in parallel. The device integrates an NMOS-switch power stage and a synchronous PMOS rectifier. The device also implements a set of linear low-side current regulators to control the LED current when the battery voltage is higher than the diode forward voltage.

The high-efficiency boost converter stage and LED forward voltage adoption ensure lowest device input current for a given LED output current.

A special circuit disconnects the load from the battery during shutdown of the converter. In conventional synchronous-rectifier circuits, the back-gate diode of the high-side PMOS is forward biased in shutdown, allowing current to flow from the battery to the output. The TPS6131x prevents this by disconnecting the cathode of the back-gate diode of the high-side PMOS from the source when the regulator is in shutdown.

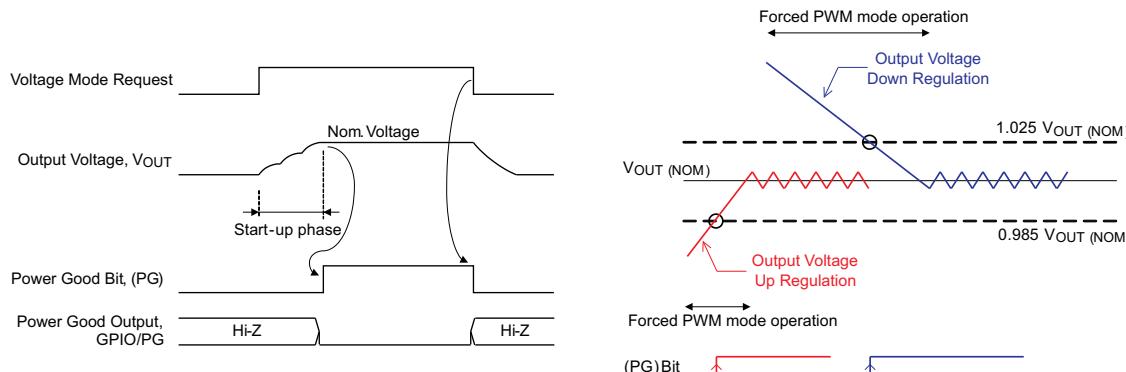

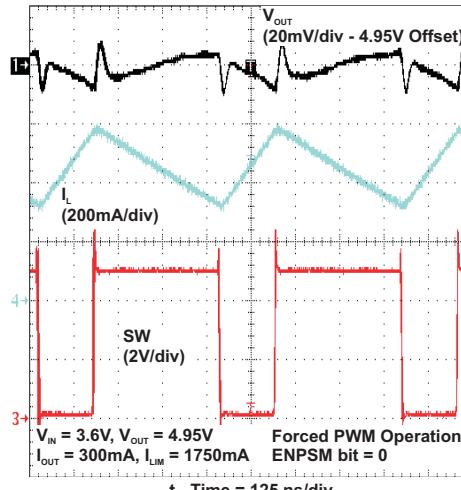

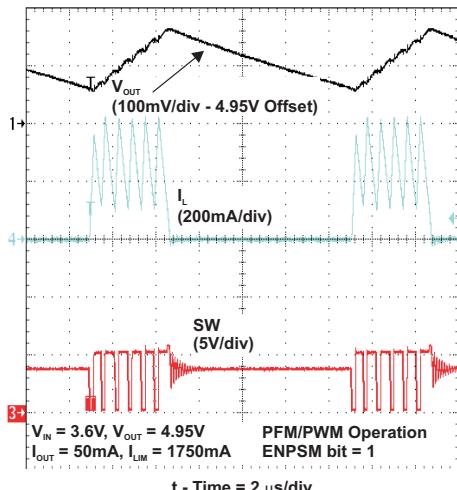

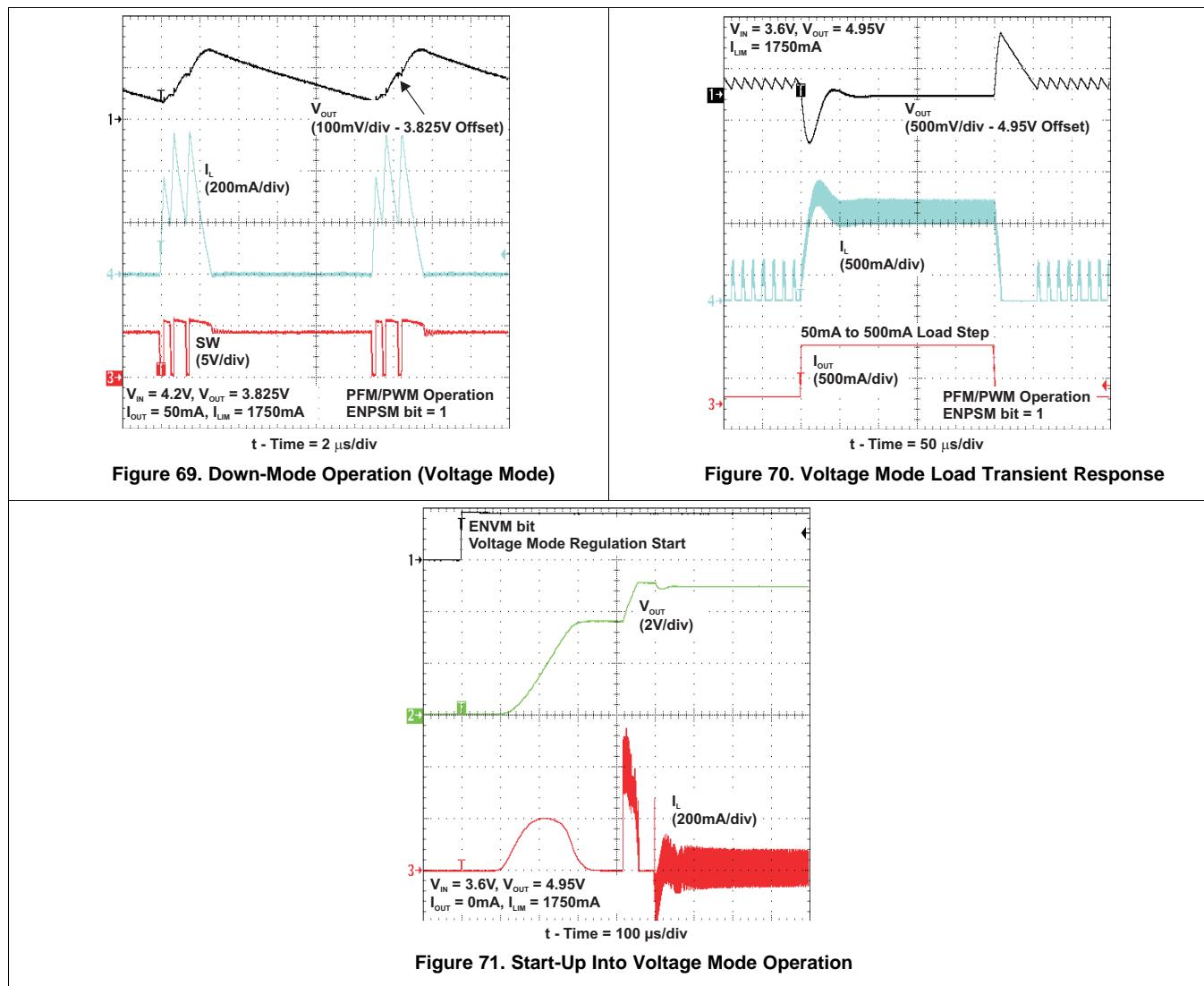

The TPS6131x device not only operates as a regulated current source, but also as a standard voltage-boost regulator featuring a power-save mode for improved efficiency at light loads. If the input voltage is higher than the programmed output voltage, a down mode is implemented that acts similarly to an LDO.

The power stage is capable of supplying a maximum total current of roughly 1500 mA. The TPS6131x provides three constant-current sinks, capable of sinking up to  $2 \times 400$  mA (LED1 and LED3) and 800 mA (LED2) in flash mode.

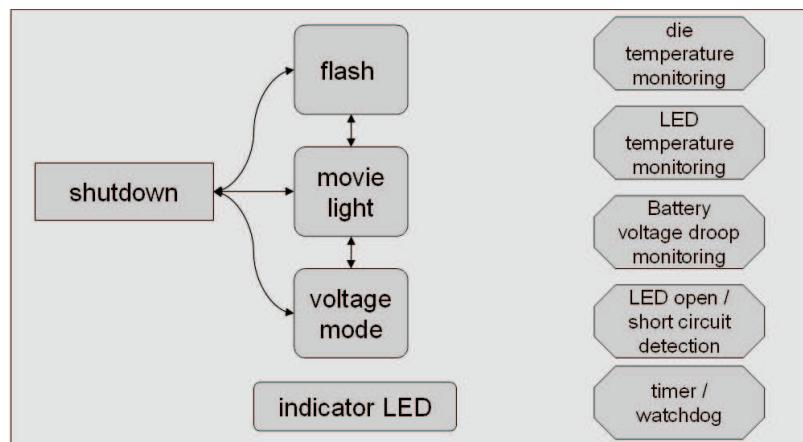

**Figure 25. TPS6131x States**

Special effort is taken for safe operation and robust system integration. The battery voltage can be monitored so that the flash current is not increased if the battery voltage drops by a programmable threshold. Internal timers limit the flash ON time to prevent potential camera-engine software errors, and a video light watchdog acts in a similar fashion. Multiple monitoring features (LED and die temperature, input voltage droop and so forth) keep the device and LEDs operating properly.

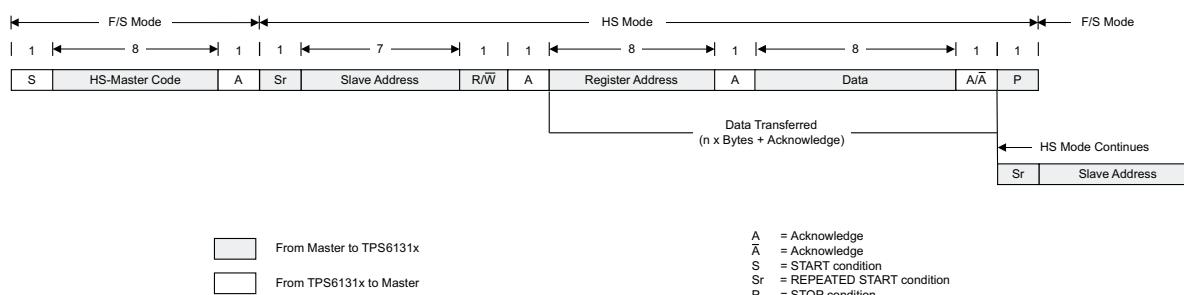

The TPS6131x integrates an I<sup>2</sup>C compatible interface allowing transfers up to 3.4 Mbps for controlling the device, featuring low-speed mode, standard mode and high-speed mode compatible operation. Additionally, basic functions can be triggered by dedicated hardware input signals, such as STRB0 and STRB1 for triggering the flash or video lighting with zero latency.

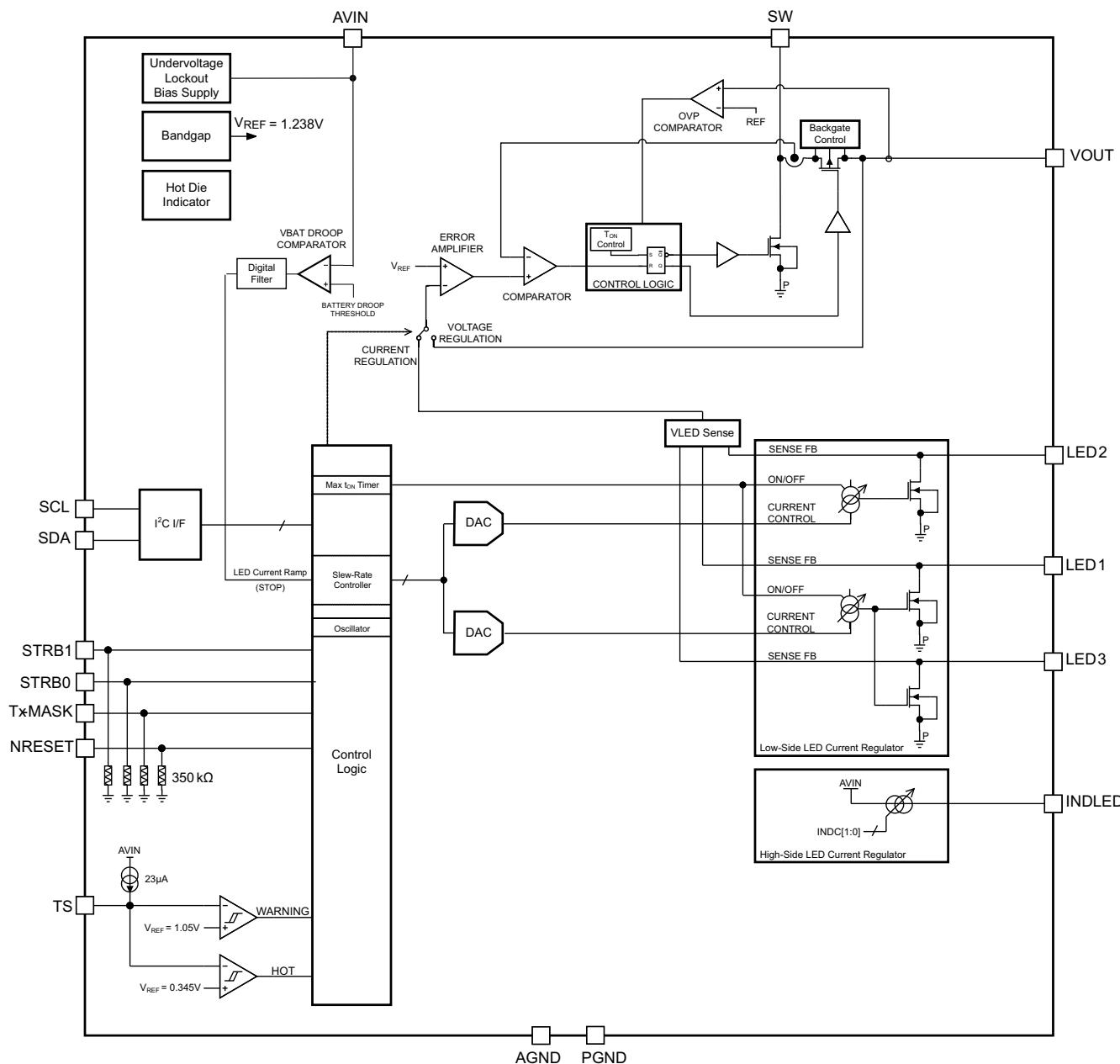

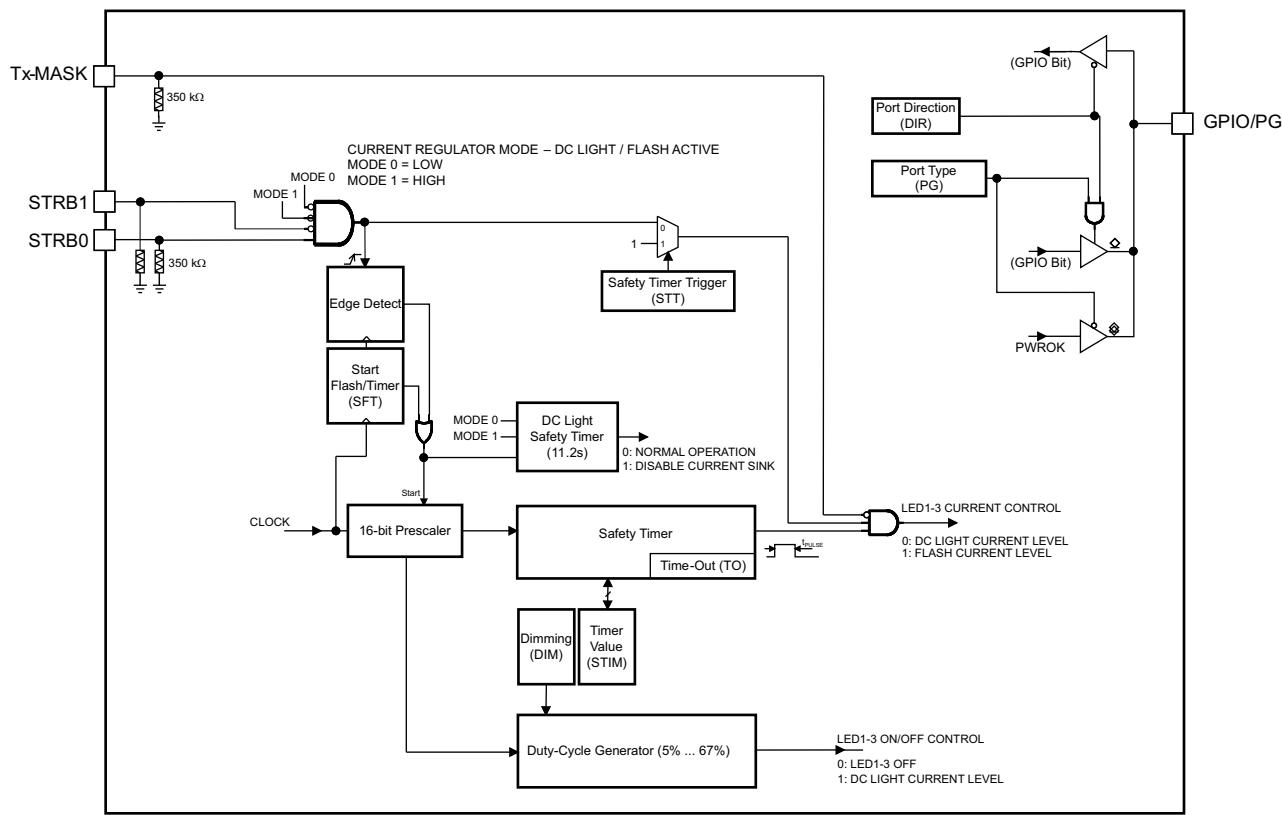

## 9.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

**Figure 26. TPS6131x**

## Functional Block Diagram (continued)

Copyright © 2016, Texas Instruments Incorporated

**Figure 27. Timer Block**

## 9.3 Feature Description

### 9.3.1 Privacy Indicator

The privacy indicator functionality can be used to indicate when a person is being photographed or filmed. The TPS6131x device offers two options of privacy indication: A dedicated pin driving an additional privacy indicator LED or using the white LEDs with pulse width modulation.

#### 9.3.1.1 Dedicated LED Privacy Indicator

The TPS6131x device provides a high-side linear constant current source to drive low  $V_F$  LEDs. The LED current is directly regulated off the battery and can be controlled through the INDC[3:0] bits, from 2.6 mA to 15.8 mA in 7 programmable current steps.

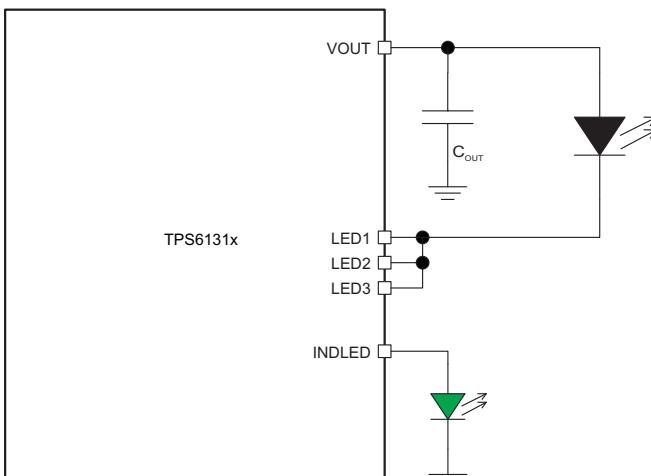

The device can drive two possible hardware configurations shown in [Figure 28](#) and [Figure 29](#). In [Figure 28](#) the TPS6131x device drives a privacy indicator LED towards ground.

## Feature Description (continued)

Copyright © 2016, Texas Instruments Incorporated

**Figure 28. Configuration 1**

Copyright © 2016, Texas Instruments Incorporated

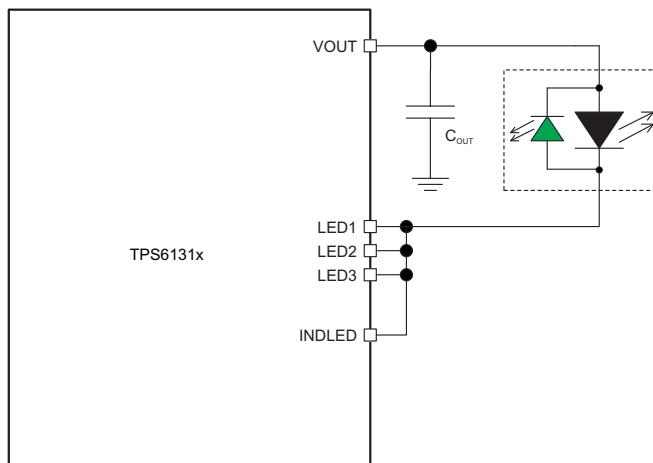

**Figure 29. Configuration 2**

The TPS6131x device also allows a path for driving a privacy indicator LED that is reverse biased to the white flash LED, see [Figure 29](#). To do so, the output of the converter (VOUT) is pulled to ground thus allowing a reverse current to flow. This mode of operation is only possible when the converter's power stage is in shutdown (MODE\_CTRL[1:0] = 00, ENVM = 0).

### 9.3.1.2 White LED Privacy Indicator

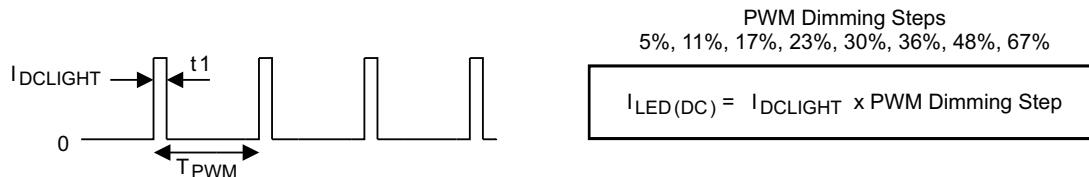

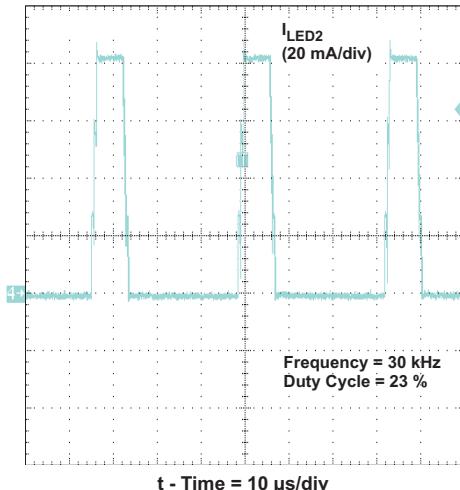

The TPS6131x device features white LED drive capability at very low light intensity. To generate a reduced LED average current, the device employs a 30-kHz fixed-frequency PWM modulation scheme. The PWM timer uses the internal oscillator as reference clock, therefore the PWM modulating frequency shows the same accuracy as the internal reference clock. Operation is shown in [Figure 27](#).

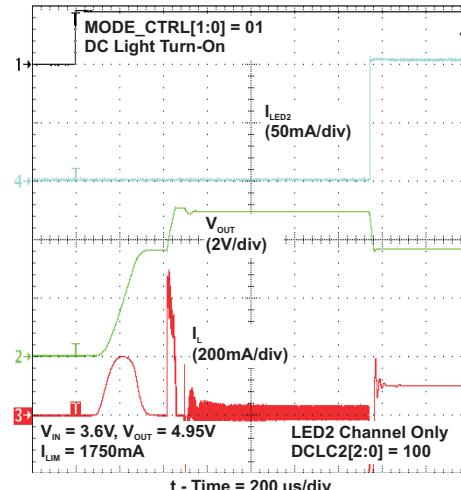

The video light current is modulated with a duty cycle defined by the INDC[3:0] bits. The low light dimming mode can only be activated in the software-controlled video-light-only mode (MODE\_CTRL[1:0] = 01, ENVM = 1), and applies to the LEDs selected through ENLED[3:1] bits. In this mode, the video light safety-timeout feature is disabled.

**Figure 30. PWM Dimming Principle**

### 9.3.2 Safe Operation and Protection Features

#### 9.3.2.1 LED Temperature Monitoring (Finger-Burn Protection)

The TPS6131x device optionally monitors the LED temperature. Critical temperatures are handled in two stages reflected by two bits: LEDWARN provides an early warning to the camera engine, LEDHOT immediately suspends the flash operation.

The LED temperature is sensed by measuring the voltage drop of a negative-temperature-coefficient resistor connected between the TS and AGND pins. An internal current source provides the bias (approximately 24  $\mu$ A) for the NTC, and the TS pin voltage is compared to internal thresholds (1.05 V and 0.345 V) to protect the LEDs against overheating. See [NTC Selection](#).

The temperature-monitoring blocks are explicitly active in video light or flash modes. In voltage-mode operation [MODE\_CTRL[1:0] = 11], the device only activates the TS input when the ENTS bit is set high.

## Feature Description (continued)

The LEDWARN and LEDHOT bits reflect the LED temperature. The LEDWARN bit is set when the voltage at the TS pin is lower than 1.05 V. This threshold corresponds to an LED warning temperature value; device operation is still permitted. While regulating LED current, video light or flash modes, the LEDHOT bit is latched when the voltage at the TS pin is lower than 0.345 V. This threshold corresponds to an excessive LED temperature value; device operation is immediately suspended, (MODE\_CTRL[1:0] bits are reset, and the HOTDIE[1:0] bits are set).

### 9.3.2.2 LED Failure Modes (Open and Short Detection) and Overvoltage Protection

The TPS6131x devices incorporate protection features to indicate if the connected LEDs are failing. These protections cover overvoltage conditions, which are caused by a failing LED showing open circuit behavior, as well as short-circuit conditions caused by a failing LED or further reasons causing a short-circuit condition. If such failure conditions occur, these are indicated by setting a failure detection flag. Furthermore, the maximum current drawn from the output is limited and can be programmed by the current-limit setting.

#### 9.3.2.2.1 LED Open Circuit Detection and Overvoltage Protection

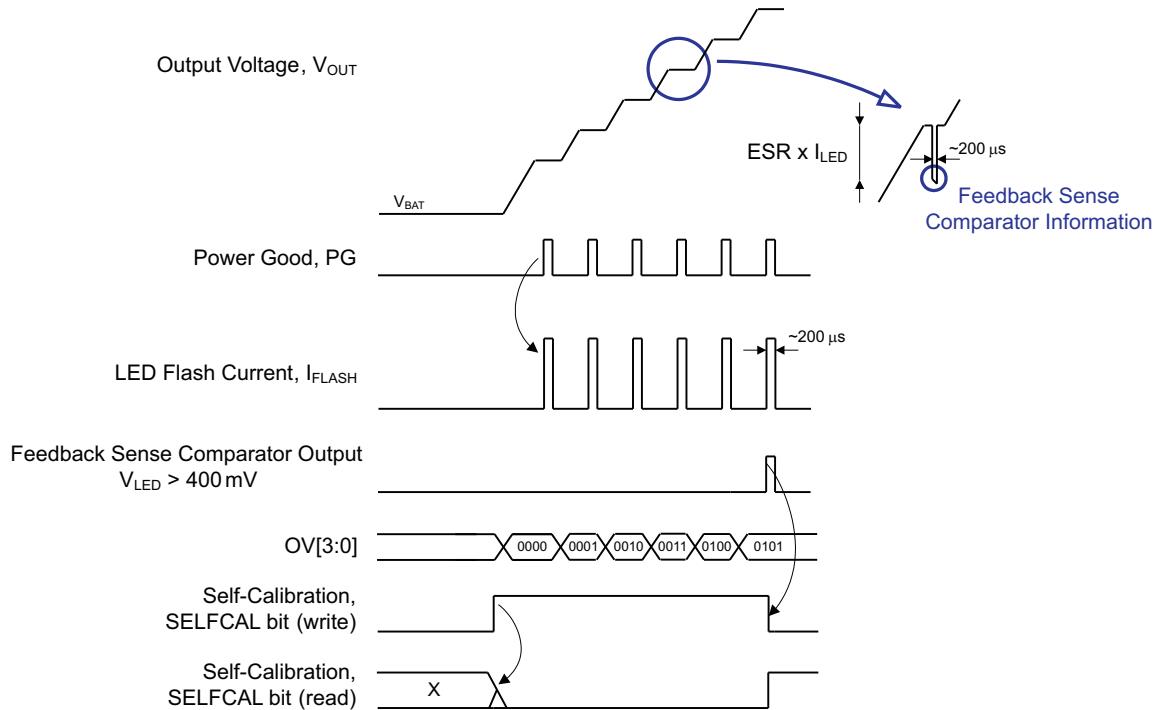

If the connected LED(s) fail showing an open circuit behavior or are disconnected, the VOUT output voltage must be limited to prevent the step-up converter from exceeding critical values. An overvoltage protection is implemented to avoid the output voltage exceeding critical values for the device and possibly for the system it is supplying. For this protection the TPS6131x output voltage is monitored internally. The TPS6131x device limits  $V_{OUT}$  according to the overvoltage protection settings (see [Table 2](#)). In this failure mode,  $V_{OUT}$  is either limited to 4.65 V (typical) or 6 V (typical) and the HIGH-POWER LED FAILURE (HPLF) flag is set. The OVP threshold depends on the programmed output voltage (OV).

**Table 2. OVP Specification**

| OVP THRESHOLD  | OPERATING CONDITIONS  |

|----------------|-----------------------|

| 4.65 V typical | 0000 ≤ OV[3:0] ≤ 0100 |

| 6 V typical    | 0101 ≤ OV[3:0] ≤ 1111 |

#### 9.3.2.2.2 Short-Circuit Protection

The TPS6131x devices incorporate double protection to protect the device and application circuit from short-circuit conditions occurring between VOUT and the current sinks LED1, LED2, and LED3.

If a short-circuit condition occurs while the LEDs are operated, the low side current sinks LED1, LED2, LED3 limit the maximum output current as programmed for the video-light mode or flash mode respectively. If a short-circuit condition occurs, the current sinks increase their input resistance to prevent excessive current to be drawn. Furthermore, the HIGH-POWER LED FAILURE flag (HPLF) is set to indicate the short circuit condition. (HPLF) is triggered if the LED forward voltage drops below 1.23 V typically. The second protection is the current limit, which generally limits the current drawn from VOUT. See [Current Limit](#).

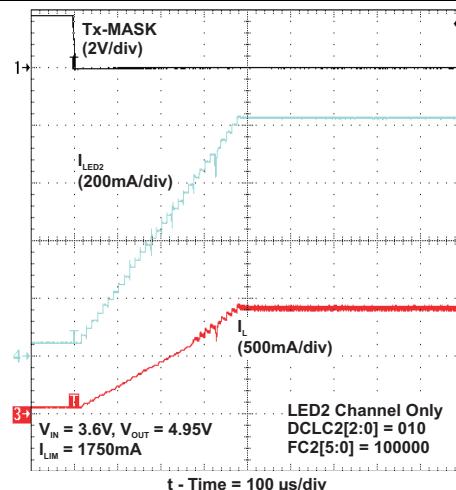

#### 9.3.2.3 LED Current Ramp-Up and Ramp-Down

To achieve smooth LED current waveforms and avoid excessive battery voltage drop, the TPS6131x device actively controls the LED current ramp-up and ramp-down sequence.

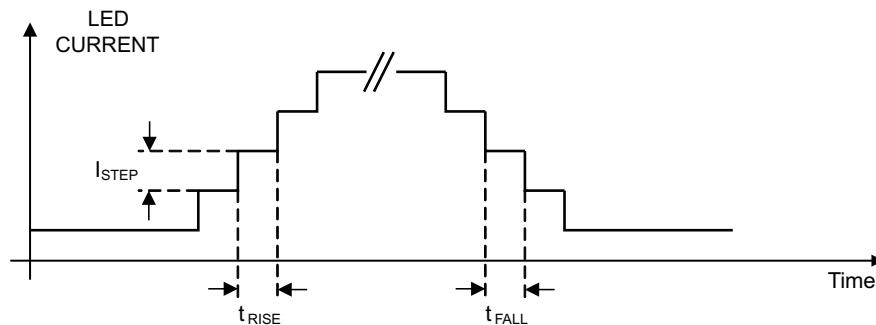

**Table 3. LED Current Ramp-Up and Ramp-Down Control vs Operating Mode**

| LED CURRENT | OPERATING MODE                                |

|-------------|-----------------------------------------------|

| Ramp-up     | $I_{STEP} = 25 \text{ mA}$                    |

|             | $t_{RISE} = 12 \mu\text{s}$                   |

|             | Slew rate $\times 2.1 \text{ mA}/\mu\text{s}$ |

| Ramp-down   | $I_{STEP} = 25 \text{ mA}$                    |

|             | $t_{FALL} = 0.5 \mu\text{s}$                  |

|             | Slew rate $\times 50 \text{ mA}/\mu\text{s}$  |

**Figure 31. LED Current Slew Rate Control**

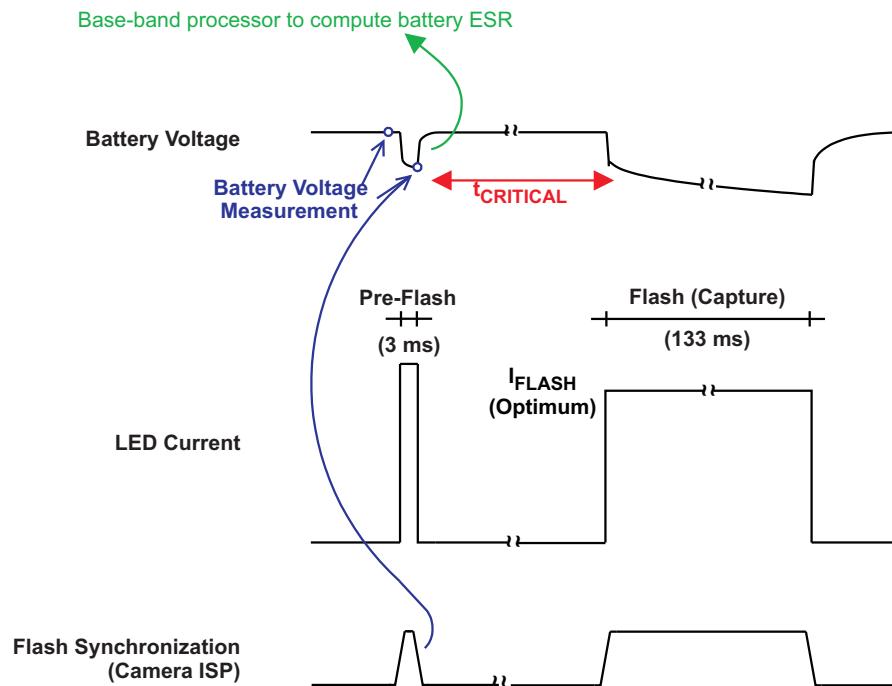

#### 9.3.2.4 Battery Voltage Droop Monitoring and Protection

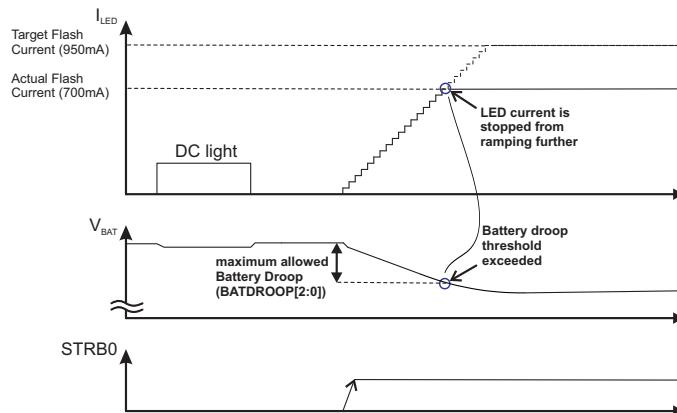

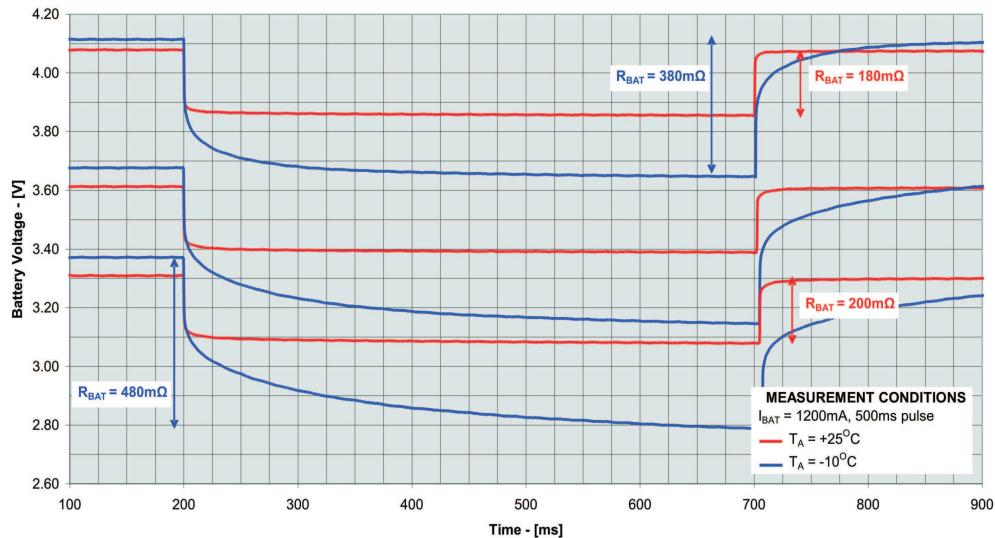

During a high-power flash strobe, the battery voltage usually drops by a few hundred millivolts. To prevent the battery voltage from collapsing too much, the TPS6131x devices integrates a battery voltage droop monitoring feature to automatically limit the flash current if the battery voltage drops more than a programmable threshold.

The battery voltage droop monitoring feature can be enabled or disabled through the ENBATMON bit.

At the very beginning of the flash strobe, the device measures the battery voltage and sets a minimum battery voltage threshold based on the tolerable droop (see [REGISTER7 \(address = 0x07\)](#) for BATDROOP[2:0] bits). While the LED current is increasing to the target flash current (see [REGISTER1 \(address = 0x01\)](#) and [REGISTER2 \(address = 0x02\)](#) for FC13[4:0] and FC2[5:0] bits), a comparator monitors the actual battery voltage and stops the ramp-up sequence when the droop exceeds the limit. See [Functional Block Diagram](#) and Figure 32.

The battery voltage droop monitor feature is automatically disabled during a Tx-MASK event.

**Figure 32. Battery Voltage Droop Monitoring and LED Current Control Principle (STRB1 = 0, Tx-Base = 1)**

#### 9.3.2.5 Undervoltage Lockout

The undervoltage lockout circuit prevents the device from error conditions at low input voltages. It prevents the converter from turning on the switch MOSFET, or rectifier MOSFET for battery voltages below 2.3 V. The I<sup>2</sup>C compatible interface is fully functional down to 2.1-V input voltage.

#### 9.3.2.6 Hot Die Detection and Thermal Shutdown

The TPS6131x device offers two levels of die temperature monitoring and protection, which are hot die detection and thermal shutdown functionality. The hot die detector (HOTDIE[1:0] bits) reflects the instantaneous junction temperature. This functionality is always enabled except when the device is in shutdown mode.

The hot die detector monitors the junction temperature but does not shut down the device. It provides an early warning to the camera engine to avoid excessive power dissipation thus preventing from thermal shutdown during the next high-power flash strobe.

As soon as the junction temperature  $T_J$  exceeds 160°C typical, the device goes into thermal shutdown. In this mode, the power stage and the low-side current regulators are turned off, the HOTDIE[1:0] bits are set and can only be reset by a read access. In the voltage mode operation (MODE\_CTRL[1:0] = 11 or ENVM = 1), the device continues its operation when the junction temperature falls below 140°C typical again. In the current regulation mode, video light or flash modes, device operation is suspended.

**Table 4. Die Temperature Bits**

| HOTDIE[1:0] | JUNCTION TEMPERATURE                                         |

|-------------|--------------------------------------------------------------|

| 00          | <55°C                                                        |

| 01          | 55°C ≤ $T_J$ ≤ 70°C                                          |

| 10          | >70°C                                                        |

| 11          | Thermal shutdown tripped. The bit is reset after read access |

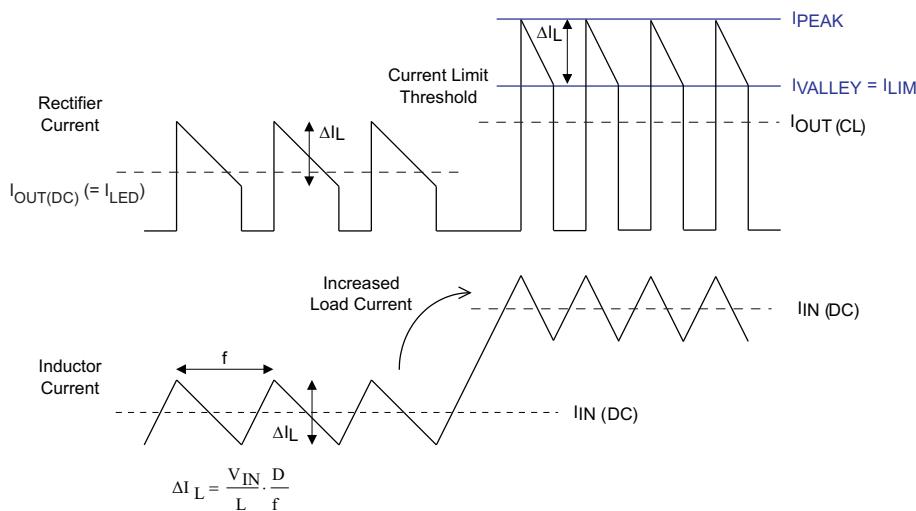

### 9.3.2.7 Current Limit

The TPS6131x devices employ a programmable inductor current limit. This allows choosing inductors with different saturation current ratings. Furthermore, this provides protection against a shorted inductor, or if the inductance value dramatically drops. This protects the battery from excessively high current drain.

The current limit circuit employs a valley current sensing scheme. The detection threshold is user selectable through the ILIM bit. The ILIM bit can only be set before entering operation, during initial shutdown state.

Figure 33 illustrates the inductor and rectifier current waveforms during current limit operation. The output current,  $I_{OUT}$ , is the average of the rectifier ripple current waveform. When the load current is increased such that the lower peak is above the current limit threshold, the off time is lengthened to allow the current to decrease to this threshold before the next ON time begins (so called frequency foldback mechanism).

Both the output voltage and the switching frequency are reduced as the power stage of the device operates in a constant current mode. The maximum continuous output current ( $I_{OUT(CL)}$ ), before entering current limit operation, can be defined as:

$$I_{OUT(CL)} = (1 - D) \times (I_{VALLEY} + \frac{1}{2} \Delta I_L) \text{ with } \Delta I_L = \frac{V_{IN}}{L} \times \frac{D}{f} \text{ and } D \approx \frac{V_{OUT} - V_{IN}}{V_{OUT}} \quad (1)$$

The TPS6131x device also provides a negative current limit ( $\approx 300$  mA) to prevent an excessive reverse inductor current when the power stage sinks current from the output in the forced continuous conduction mode.

**Figure 33. Inductor and Rectifier Currents in Current Limit Operation**

**Table 5. Inductor Current Limit Operation**

| CURRENT LIMIT SETTING |          | ILIM BIT |

|-----------------------|----------|----------|

| TPS61310              | TPS61311 |          |

| 1250 mA               | 1800 mA  | Low      |

| 1750 mA               | 2480 mA  | High     |

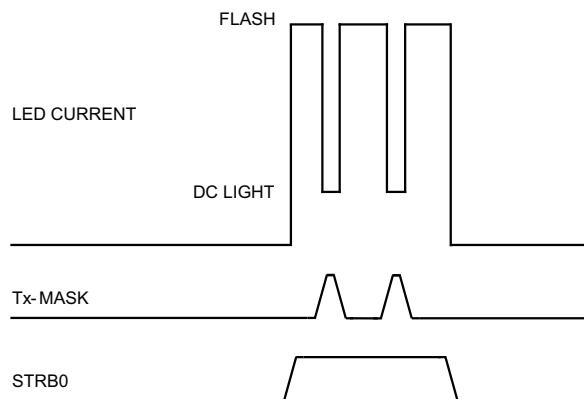

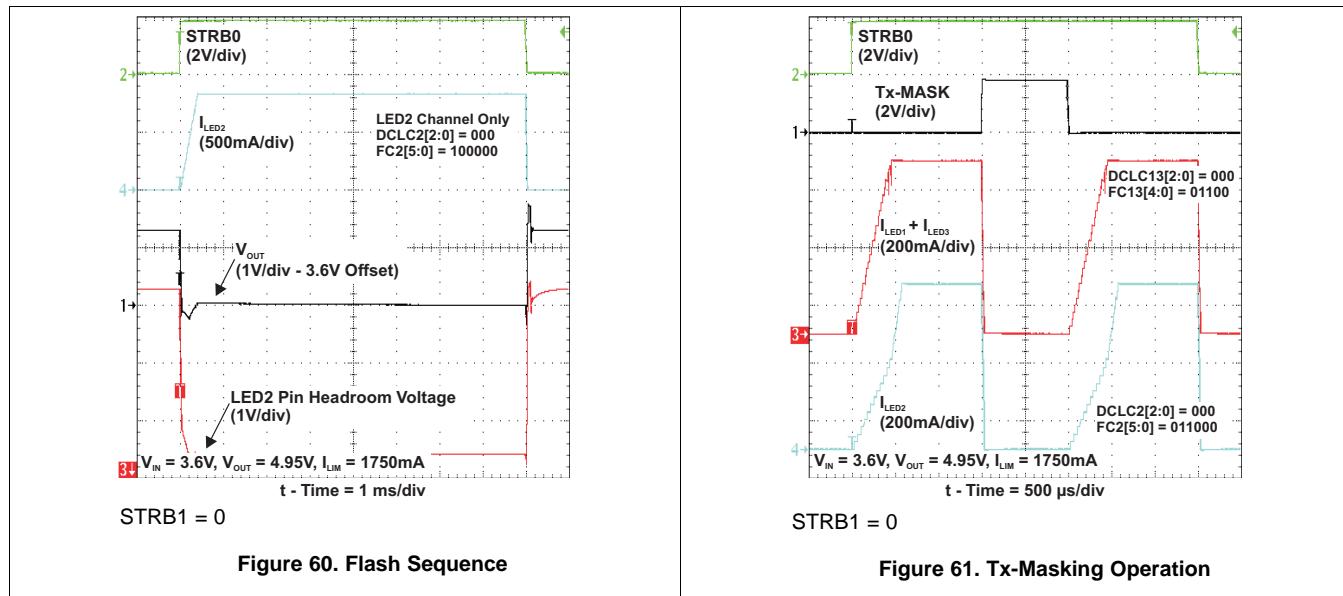

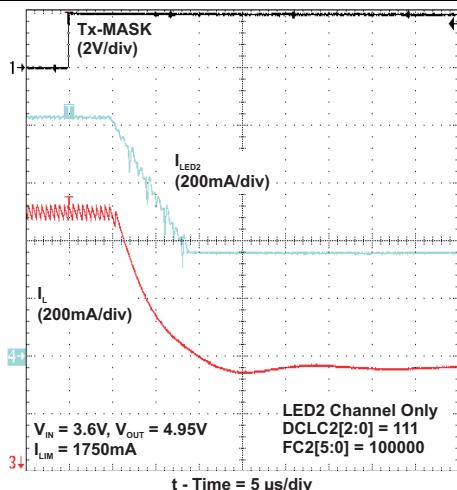

### 9.3.2.8 Flash Blanking (Tx-Mask) for Instantaneous Flash Current Reduction

The TPS6131x devices offer a dedicated hardware signal input (Tx-Mask) that can be used to reduce the flash current to the programmed video light level instantaneously.

This feature can be used to reduce the overall current drawn from the battery if other system components require high energy simultaneously, such as during a RF PA transmission pulse.

The Tx-MASK function has no influence on the safety timer duration.

**Figure 34. Synchronized Flash With Blanking Periods (STRB1 = 0)**

### 9.3.3 Start-Up Sequence

To avoid high inrush current during start-up, control the inrush current. When the device enables, the internal start-up cycle starts with the first step, the precharge phase.

During precharge, the rectifying switch is turned on until the output capacitor is either charged to a value close to the input voltage or  $\approx 3.3$  V, whichever occurs first. The rectifying switch is current limited during that phase. The current limit increases with decreasing input-to-output voltage difference. This circuit also limits the output current under output short-circuit conditions.

After precharging the output capacitor, the device starts switching, and increases its current limit in three steps of typically 25 mA, 250 mA and full current limit (ILIM setting). The current limit transition from the first to the second step occurs after 1 ms of operation. Full current limit operation is set once the output voltage reaches its regulation limits. In this mode, the active balancing circuit is disabled.

### 9.3.4 NRESET Input: Hardware Enable or Disable

The TPS6131x family features a hardware reset pin (NRESET). This reset pin allows the device to be disabled by an external controller without requiring an I<sup>2</sup>C write command. Under normal operation, the NRESET pin must be held high to prevent an unwanted reset. When the NRESET is driven low, the I<sup>2</sup>C control interface and all internal control registers are reset to the default states and the part enters shutdown mode.

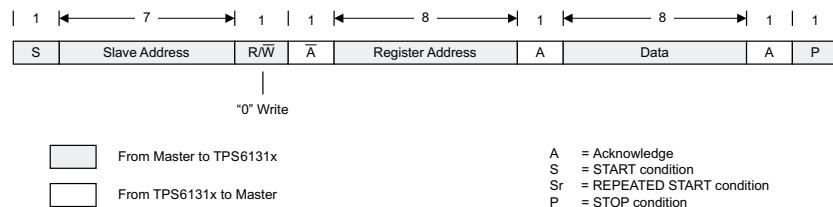

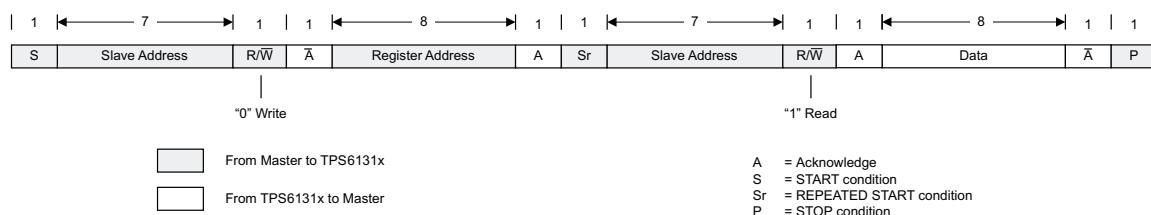

### 9.3.5 Serial Interface Description

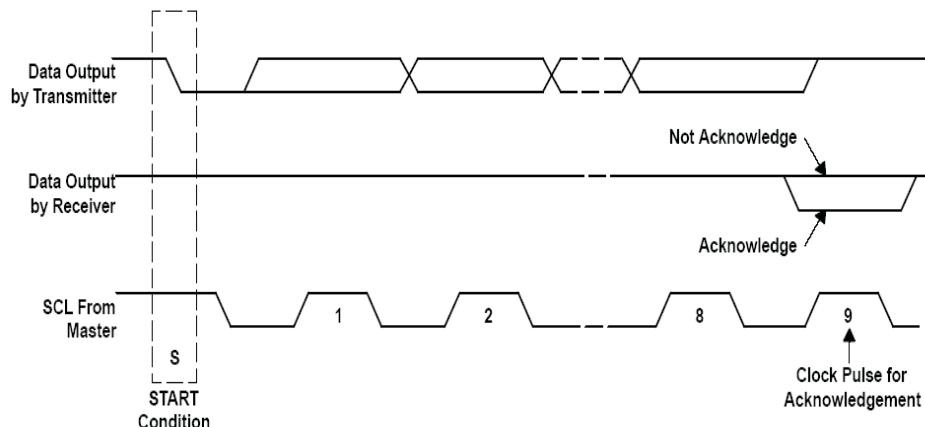

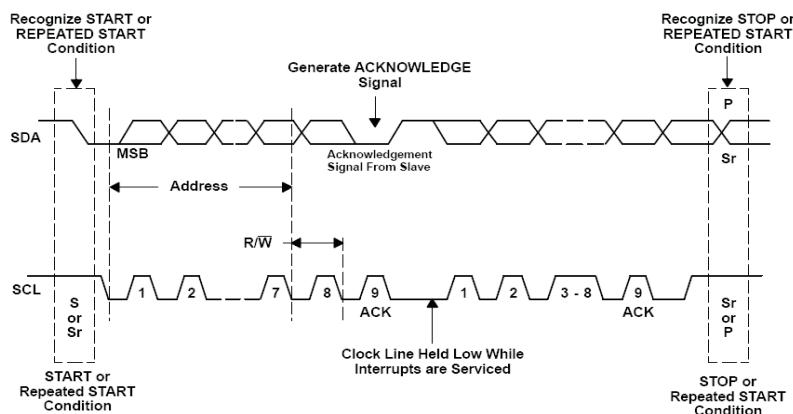

$\text{I}^2\text{C}$ ™ is a 2-wire serial interface developed by Philips Semiconductor, now NXP Semiconductors [1]. The bus consists of a data line (SDA) and a clock line (SCL) with pullup structures. When the bus is *idle*, both SDA and SCL lines are pulled high. All the  $\text{I}^2\text{C}$  compatible devices connect to the  $\text{I}^2\text{C}$  bus through open drain I/O pins, SDA and SCL. A *master* device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A *slave* device receives or transmits data on the bus under control of the master device.