# HEXFET® Power MOSFET

# **Applications**

**Benefits**

Lead-Free

- High Frequency Synchronous Buck Converters for Computer Processor Power

- High Frequency Isolated DC-DC Converters with Synchronous Rectification for Telecom and Industrial Use

Fully Characterized Avalanche Voltage and Current

| V <sub>DSS</sub>        | 30V           |

|-------------------------|---------------|

| R <sub>DS(on)</sub> max | 9.5m $\Omega$ |

| Qg                      | 9.6nC         |

| G    | D     | S      |

|------|-------|--------|

| Gate | Drain | Source |

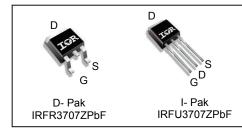

|                  | B. J         | Standard Pack      |          | Out of the Boat North |

|------------------|--------------|--------------------|----------|-----------------------|

| Base part number | Package Type | Form               | Quantity | Orderable Part Number |

| IRFU3707ZPbF     | I-Pak        | Tube               | 75       | IRFU3707ZPbF          |

|                  |              | Tube               | 75       | IRFR3707ZPbF          |

| IRFR3707ZPbF     | D-Pak        | Tape and Reel Left | 3000     | IRFR3707ZTRLPbF       |

Absolute Maximum Ratings

• Very Low R<sub>DS(on)</sub> at 4.5V V<sub>GS</sub> Ultra - Low Gate Impedance

| Symbol                                  | Parameter                                               | Max.         | Units |

|-----------------------------------------|---------------------------------------------------------|--------------|-------|

| V <sub>DS</sub>                         | Drain -to-Source Voltage                                | 30           | V     |

| $V_{GS}$                                | Gate-to-Source Voltage                                  | ± 20         | V     |

| I <sub>D</sub> @ T <sub>C</sub> = 25°C  | Continuous Drain Current, V <sub>GS</sub> @ 10V         | 564          |       |

| I <sub>D</sub> @ T <sub>C</sub> = 100°C | Continuous Drain Current, V <sub>GS</sub> @ 10V         | 394          | Α     |

| I <sub>DM</sub>                         | Pulsed Drain Current ①                                  | 220          |       |

| P <sub>D</sub> @T <sub>C</sub> = 25°C   | Maximum Power Dissipation                               | 50           | W     |

| P <sub>D</sub> @T <sub>C</sub> = 100°C  | Maximum Power Dissipation                               | 25           | W     |

|                                         | Linear Derating Factor                                  | 0.33         | W/°C  |

| TJ                                      | Operating Junction and                                  | -55 to + 175 |       |

| $T_{STG}$                               | Storage Temperature Range                               |              | °C    |

|                                         | Soldering Temperature, for 10 seconds (1.6mm from case) | 300          |       |

## **Thermal Resistance**

| Symbol          | Parameter                          | Тур. | Max. | Units |

|-----------------|------------------------------------|------|------|-------|

| $R_{	heta JC}$  | Junction-to-Case                   |      | 3.0  |       |

| $R_{	heta JA}$  | Junction-to-Ambient ( PCB Mount) ® |      | 50   | °C/W  |

| $R_{\theta JA}$ | Junction-to-Ambient                |      | 110  |       |

Notes ① through ⑤ are on page 2.

2016-5-31

# Static @ T<sub>J</sub> = 25°C (unless otherwise specified)

|                                 | Parameter                                           | Min. | Тур.  | Max. | Units | Conditions                                        |

|---------------------------------|-----------------------------------------------------|------|-------|------|-------|---------------------------------------------------|

| $V_{(BR)DSS}$                   | Drain-to-Source Breakdown Voltage                   | 30   |       |      | V     | $V_{GS} = 0V, I_D = 250\mu A$                     |

| $\Delta V_{(BR)DSS}/\Delta T_J$ | Breakdown Voltage Temp. Coefficient                 |      | 0.023 |      | V/°C  | Reference to 25°C, I <sub>D</sub> = 1mA           |

| Б                               | Otatia Duain ta Cauraa On Dagiatanaa                |      | 7.5   | 9.5  |       | V <sub>GS</sub> = 10V, I <sub>D</sub> = 15A ③     |

| $R_{DS(on)}$                    | Static Drain-to-Source On-Resistance                |      | 10    | 12.5 | mΩ    | V <sub>GS</sub> = 4.5V, I <sub>D</sub> = 12A ③    |

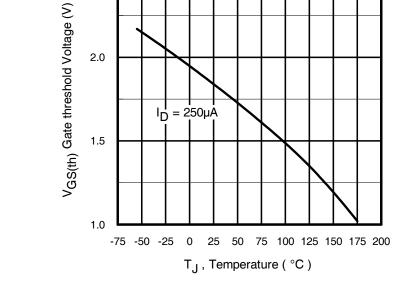

| $V_{GS(th)}$                    | Gate Threshold Voltage                              | 1.35 | 1.80  | 2.25 | V     | )/ )/ L 05::A                                     |

| $\Delta V_{GS(th)}/\Delta T_J$  | Gate Threshold Voltage Temp. Coefficient            |      | -5.0  |      | mV/°C | $V_{DS} = V_{GS}$ , $I_D = 25\mu A$               |

| I <sub>DSS</sub>                | Drain-to-Source Leakage Current                     |      |       | 1.0  | μA    | V <sub>DS</sub> = 24V, V <sub>GS</sub> = 0V       |

| פטי                             | Brain-to-course Leakage Carrent                     |      |       | 150  | μΛ    | $V_{DS} = 24V, V_{GS} = 0V, T_{J} = 125^{\circ}C$ |

| 1                               | Gate-to-Source Forward Leakage                      |      |       | 100  | nA    | $V_{GS} = 20V$                                    |

| I <sub>GSS</sub>                | Gate-to-Source Reverse Leakage                      |      |       | -100 | II/   | $V_{GS} = -20V$                                   |

| gfs                             | Forward Trans conductance                           | 71   |       |      | S     | $V_{DS} = 15V, I_{D} = 12A$                       |

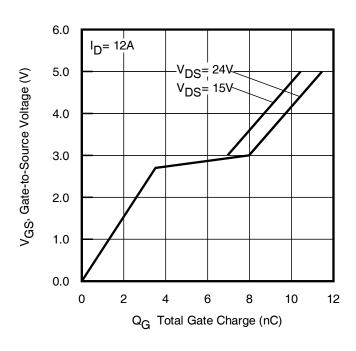

| $Q_g$                           | Total Gate Charge                                   |      | 9.6   | 14   |       |                                                   |

| $Q_{gs1}$                       | Pre-Vth Gate-to-Source Charge                       |      | 2.6   |      |       | V <sub>DS</sub> = 15V                             |

| $Q_{gs2}$                       | Post-Vth Gate-to-Source Charge                      |      | 0.90  |      | nC    | $V_{GS} = 4.5V$                                   |

| $Q_{gd}$                        | Gate-to-Drain Charge                                |      | 3.5   |      | IIC   | I <sub>D</sub> = 12A                              |

| $Q_{godr}$                      | Gate Charge Overdrive                               |      | 2.6   |      |       | See Fig. 16                                       |

| $Q_{sw}$                        | Switch Charge (Q <sub>gs2</sub> + Q <sub>gd</sub> ) |      | 4.4   |      |       |                                                   |

| $Q_{oss}$                       | Output Charge                                       |      | 5.8   |      | nC    | $V_{DS} = 15V, V_{GS} = 0V$                       |

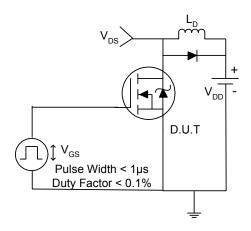

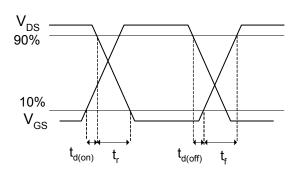

| $t_{d(on)}$                     | Turn-On Delay Time                                  |      | 8.0   |      |       | V <sub>DD</sub> = 16V,V <sub>GS</sub> = 4.5V ③    |

| t <sub>r</sub>                  | Rise Time                                           |      | 11    |      | ]     | I <sub>D</sub> = 12A                              |

| $t_{d(off)}$                    | Turn-Off Delay Time                                 |      | 12    |      | ns    | Clamped Inductive Load                            |

| t <sub>f</sub>                  | Fall Time                                           |      | 3.3   |      |       |                                                   |

| C <sub>iss</sub>                | Input Capacitance                                   |      | 1150  |      |       | $V_{GS} = 0V$                                     |

| Coss                            | Output Capacitance                                  |      | 260   |      | pF    | V <sub>DS</sub> = 15V                             |

| C <sub>rss</sub>                | Reverse Transfer Capacitance                        |      | 120   |      |       | f = 1.0MHz                                        |

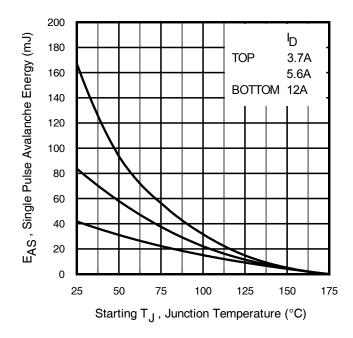

## **Avalanche Characteristics**

|                 | Parameter                       | Max. | Units |

|-----------------|---------------------------------|------|-------|

| E <sub>AS</sub> | Single Pulse Avalanche Energy ② | 42   | mJ    |

| I <sub>AR</sub> | Avalanche Current ①             | 12   | Α     |

| E <sub>AR</sub> | Repetitive Avalanche Energy ①   | 5.0  | mJ    |

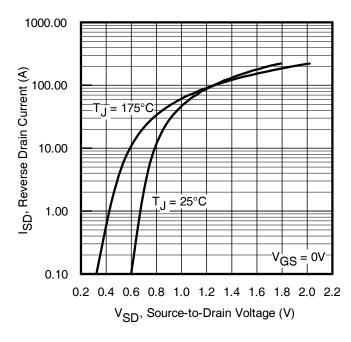

## **Diode Characteristics**

|                 | Parameter                               | Min.      | Тур.    | Max.    | Units     | Conditions                                                   |

|-----------------|-----------------------------------------|-----------|---------|---------|-----------|--------------------------------------------------------------|

| I <sub>S</sub>  | Continuous Source Current (Body Diode)  |           |         | 56④     |           | MOSFET symbol showing the                                    |

| I <sub>SM</sub> | Pulsed Source Current<br>(Body Diode) ① |           |         | 220     |           | integral reverse p-n junction diode.                         |

| $V_{SD}$        | Diode Forward Voltage                   |           |         | 1.0     | V         | $T_J = 25^{\circ}C, I_S = 12A, V_{GS} = 0V$ 3                |

| t <sub>rr</sub> | Reverse Recovery Time                   |           | 25      | 38      | ns        | $T_J = 25^{\circ}C$ , $I_F = 12A$ , $V_{DS} = 15V$           |

| Qrr             | Reverse Recovery Charge                 |           | 17      | 26      | nC        | di/dt = 100A/µs ③                                            |

| $t_{on}$        | Forward Turn-On Time                    | Intrinsio | turn-or | time is | negligibl | le (turn-on is dominated by L <sub>S</sub> +L <sub>D</sub> ) |

#### Notes:

- ① Repetitive rating; pulse width limited by max. junction temperature

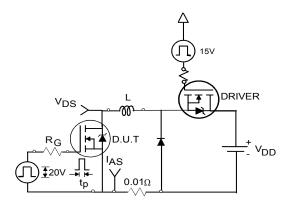

- ② starting  $T_J = 25^{\circ}C$ , L = 0.58mH,  $R_G = 25\Omega$ ,  $I_{AS} = 12A$ .

- 3 Pulse width  $\leq 400 \mu s$ ; duty cycle  $\leq 2\%$ .

- ④ Calculated continuous current based on maximum allowable junction temperature. Package limitation current is 30A.

- (§) When mounted on 1" square PCB (FR-4 or G-10 Material). For recommended footprint and soldering techniques refer to application note #AN-994.

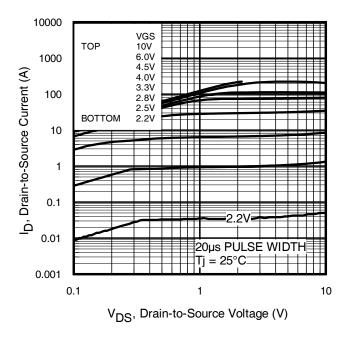

Fig. 1 Typical Output Characteristics

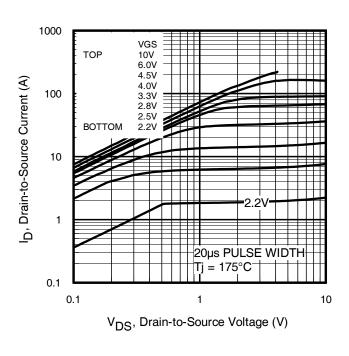

Fig. 2 Typical Output Characteristics

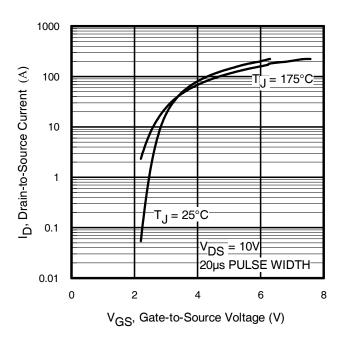

Fig. 3 Typical Transfer Characteristics

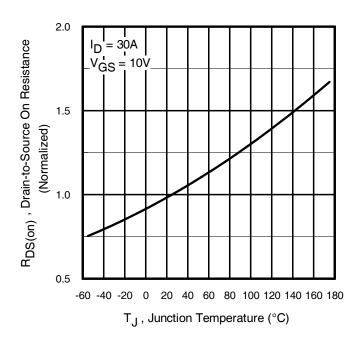

**Fig. 4** Normalized On-Resistance vs. Temperature

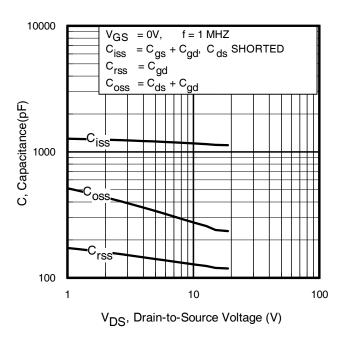

**Fig 5.** Typical Capacitance vs. Drain-to-Source Voltage

**Fig 6.** Typical Gate Charge vs. Gate-to-Source Voltage

Fig. 7 Typical Source-to-Drain Diode Forward Voltage

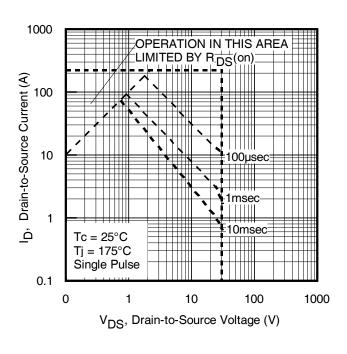

Fig 8. Maximum Safe Operating Area

4

2.5

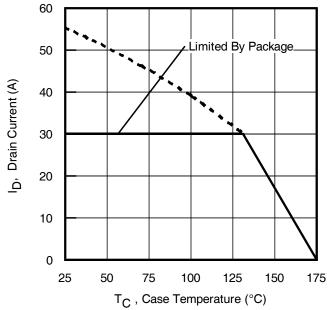

Fig 9. Maximum Drain Current vs. Case Temperature

Fig 10. Threshold Voltage vs. Temperature

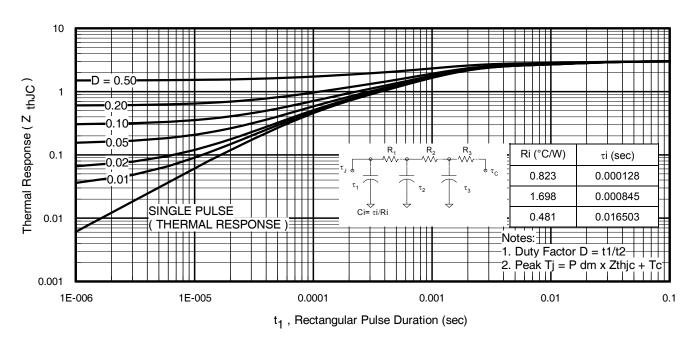

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

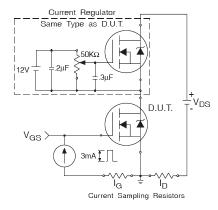

Fig 12a. Unclamped Inductive Test Circuit

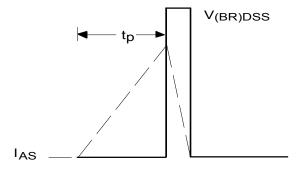

Fig 12b. Unclamped Inductive Waveforms

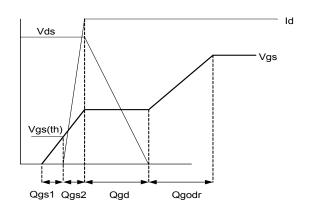

Fig 13a. Gate Charge Waveform

Fig 13b. Gate Charge Test Circuit

**Fig 12c.** Maximum Avalanche Energy vs. Drain Current

Fig 14a. Switching Time Test Circuit

Fig 14b. Switching Time Waveforms

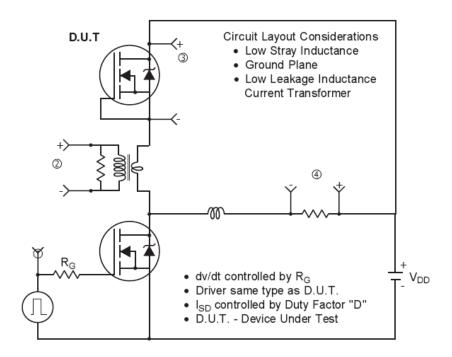

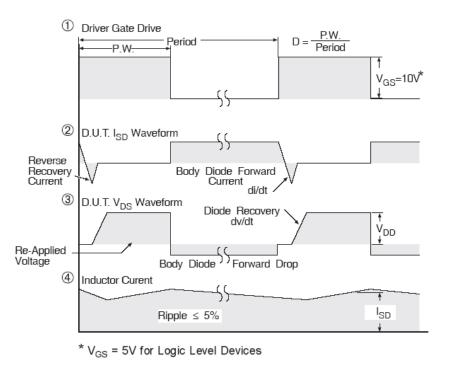

# Peak Diode Recovery dv/dt Test Circuit

Fig 15. Peak Diode Recovery dv/dt Test Circuit for N-Channel HEXFET® Power MOSFETs

2016-5-31

## Power MOSFET Selection for Non-Isolated DC/DC Converters

## **Control FET**

Special attention has been given to the power losses in the switching elements of the circuit - Q1 and Q2. Power losses in the high side switch Q1, also called the Control FET, are impacted by the  $R_{\text{ds(on)}}$  of the MOSFET, but these conduction losses are only about one half of the total losses.

Power losses in the control switch Q1 are given by;

$$P_{loss} = P_{conduction} + P_{switching} + P_{drive} + P_{output}$$

This can be expanded and approximated by;

$$\begin{split} P_{loss} &= \left(I_{rms}^{2} \times R_{ds(on)}\right) \\ &+ \left(I \times \frac{Q_{gd}}{i_{g}} \times V_{in} \times f\right) + \left(I \times \frac{Q_{gs2}}{i_{g}} \times V_{in} \times f\right) \\ &+ \left(Q_{g} \times V_{g} \times f\right) \\ &+ \left(\frac{Q_{oss}}{2} \times V_{in} \times f\right) \end{split}$$

This simplified loss equation includes the terms  $Q_{gs2}$  and  $Q_{oss}$  which are new to Power MOSFET data sheets.

$Q_{gs2}$  is a subelement of traditional gate-source charge that is included in all MOSFET data sheets. The importance of splitting this gate-source charge into two sub elements,  $Q_{gs1}$  and  $Q_{gs2}$ , can be seen from Fig 16.

$Q_{gs2}$  indicates the charge that must be supplied by the gate driver between the time that the threshold voltage has been reached and the time the drain current rises to Id max at which time the drain voltage begins to change. Minimizing  $Q_{gs2}$  is a critical factor in reducing switching losses in Q1.

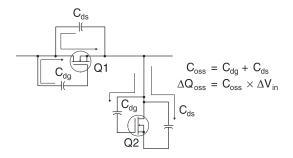

$Q_{\text{oss}}$  is the charge that must be supplied to the output capacitance of the MOSFET during every switching cycle. Figure A shows how  $Q_{\text{oss}}$  is formed by the parallel combination of the voltage dependent (non-linear) capacitance's  $C_{\text{ds}}$  and  $C_{\text{dg}}$  when multiplied by the power supply input buss voltage.

## **Synchronous FET**

The power loss equation for Q2 is approximated by;

$$\begin{split} P_{loss} &= P_{conduction} + P_{drive} + P_{output}^* \\ P_{loss} &= \left(I_{rms}^2 \times R_{ds(on)}\right) \\ &+ \left(Q_g \times V_g \times f\right) \\ &+ \left(\frac{Q_{oss}}{2} \times V_{in} \times f\right) + \left(Q_{rr} \times V_{in} \times f\right) \end{split}$$

\*dissipated primarily in Q1

For the synchronous MOSFET Q2, R<sub>ds(on)</sub> is an important characteristic; however, once again the importance of gate charge must not be overlooked since it impacts three critical areas. Under light load the MOSFET must still be turned on and off by the control I<sub>C</sub> so the gate drive losses become much more significant. Secondly, the output charge Qoss and reverse recovery charge Qr both generate losses that are transferred to Q1 and increase the dissipation in that device. Thirdly, gate charge will impact the MOSFETs' susceptibility to C<sub>dv/dt</sub> turn on. The drain of Q2 is connected to the switching node of the converter and therefore sees transitions between ground and Vin. As Q1 turns on and off there is a rate of change of drain voltage dV/dt which is capacitive coupled to the gate of Q2 and can induce a voltage spike on the gate that is sufficient to turn the MOSFET on, resulting in shoot-through current . The ratio of Q<sub>ad</sub>/Q<sub>as1</sub> must be min-

imized to reduce the potential for C<sub>dv/dt</sub> turn on.

Figure A: Qoss Characteristic

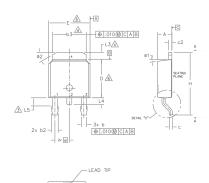

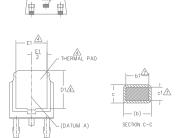

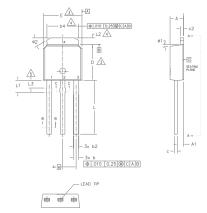

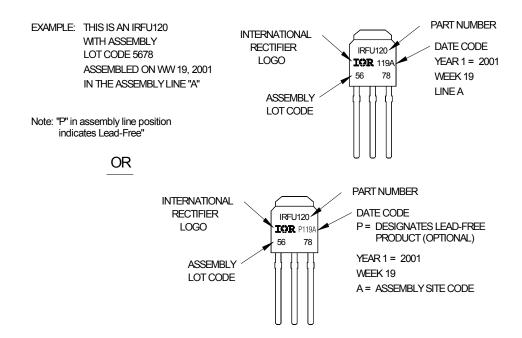

## D-Pak (TO-252AA) Package Outline (Dimensions are shown in millimeters (inches))

VIEW A-A

- 1.- DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

- 2.- DIMENSION ARE SHOWN IN INCHES [MILLIMETERS].

- A. LEAD DIMENSION UNCONTROLLED IN L5.

- A- DIMENSION D1, E1, L3 & b3 ESTABLISH A MINIMUM MOUNTING SURFACE FOR THERMAL PAD.

- 5.— SECTION C-C DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .005 AND 0.10 [0.13 AND 0.25] FROM THE LEAD TIP.

- DIMENSION D & E DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED .006 [0.15] PER SIDE. THESE DIMENSIONS ARE MEASURED AT THE OUTMOST EXTREMES OF THE PLASTIC BODY.

- ♠ DATUM A & B TO BE DETERMINED AT DATUM PLANE H.

- 9.- OUTLINE CONFORMS TO JEDEC OUTLINE TO-252AA

| S      |        | DIMEN | SIONS |      | Ŋ      |

|--------|--------|-------|-------|------|--------|

| M<br>B | MILLIM | ETERS | INC   | HES  | O<br>T |

| 0<br>L | MIN.   | MAX.  | MIN.  | MAX. | E<br>S |

| Α      | 2.18   | 2.39  | .086  | .094 |        |

| A1     | -      | 0.13  | -     | .005 |        |

| ь      | 0.64   | 0.89  | .025  | .035 |        |

| ь1     | 0.64   | 0.79  | .025  | .031 | 7      |

| b2     | 0.76   | 1,14  | .030  | .045 |        |

| b3     | 4.95   | 5.46  | .195  | .215 | 4      |

| С      | 0.46   | 0.61  | .018  | .024 |        |

| c1     | 0.41   | 0.56  | .016  | .022 | 7      |

| c2     | 0.46   | 0.89  | .018  | .035 |        |

| D      | 5.97   | 6.22  | .235  | .245 | 6      |

| D1     | 5.21   | -     | .205  | -    | 4      |

| Ε      | 6.35   | 6.73  | .250  | .265 | 6      |

| E1     | 4.32   | -     | .170  | -    | 4      |

| е      | 2.29   | BSC   | .090  | BSC  |        |

| Н      | 9.40   | 10.41 | .370  | .410 |        |

| L      | 1.40   | 1.78  | .055  | .070 |        |

| L1     | 2.74   | BSC   | .108  | REF. |        |

| L2     | 0.51   | BSC   | .020  | BSC  |        |

| L3     | 0.89   | 1.27  | .035  | .050 | 4      |

| L4     | -      | 1.02  | -     | .040 |        |

| L5     | 1.14   | 1.52  | .045  | .060 | 3      |

| Ø      | 0,     | 10°   | 0,    | 10°  |        |

| ø1     | 0,     | 15°   | 0,    | 15°  |        |

| ø2     | 25°    | 35°   | 25°   | 35°  |        |

|        |        |       |       |      |        |

#### LEAD ASSIGNMENTS

#### <u>HEXFET</u>

- 1.- GATE 2.- DRAIN 3.- SOURCE 4.- DRAIN

## IGBT & CoPAK

- 1.- GATE 2.- COLLECTOR

- 3.- EMITTER

- 4.- COLLECTOR

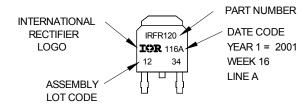

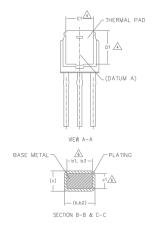

# D-Pak (TO-252AA) Part Marking Information

EXAMPLE: THIS IS AN IRFR120 WITH ASSEMBLY LOT CODE 1234

> ASSEMBLED ON WW 16, 2001 IN THE ASSEMBLY LINE "A"

Note: "P" in assembly line position indicates "Lead-Free"

> "P" in assembly line position indicates "Lead-Free" qualification to the consumer-level

Note: For the most current drawing please refer to Infineon's web site www.infineon.com

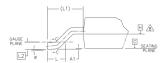

# I-Pak (TO-251AA) Package Outline Dimensions are shown in millimeters (inches)

#### OTES:

- 1.- DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

- 2.- DIMENSION ARE SHOWN IN INCHES [MILLIMETERS].

- ⚠ DIMENSION D & E DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED .005 [0.18] PER SIDE. THESE DIMENSIONS ARE MEASURED AT THE OUTMOST EXTREMES OF THE PLASTIC BODY.

- A- THERMAL PAD CONTOUR OPTION WITHIN DIMENSION 64, L2, E1 & D1.

- ⚠- LEAD DIMENSION UNCONTROLLED IN L3.

- ⚠- DIMENSION 61, 63 & c1 APPLY TO BASE METAL ONLY.

- 7.- OUTLINE CONFORMS TO JEDEC OUTLINE TO-251AA (Date 06/02).

- 8.- CONTROLLING DIMENSION: INCHES.

| S<br>Y<br>M | DIMENSIONS |       |      |      |        |

|-------------|------------|-------|------|------|--------|

| В           | MILLIM     | ETERS | INC  | HES  | 0      |

| 0           | MIN.       | MAX.  | MIN. | MAX. | E<br>S |

| Α           | 2.18       | 2.39  | .086 | .094 |        |

| A1          | 0.89       | 1.14  | .035 | .045 |        |

| b           | 0.64       | 0.89  | .025 | .035 |        |

| ь1          | 0.65       | 0.79  | .025 | .031 | 6      |

| ь2          | 0.76       | 1.14  | .030 | .045 |        |

| Ь3          | 0.76       | 1.04  | .030 | .041 | 6      |

| b4          | 4.95       | 5.46  | .195 | .215 | 4      |

| С           | 0.46       | 0.61  | .018 | .024 |        |

| c1          | 0.41       | 0.56  | .016 | .022 | 6      |

| c2          | 0.46       | 0.89  | .018 | .035 |        |

| D           | 5.97       | 6.22  | .235 | .245 | 3      |

| D1          | 5.21       | -     | .205 | _    | 4      |

| Ε           | 6.35       | 6.73  | .250 | .265 | 3      |

| E1          | 4.32       | -     | .170 | -    | 4      |

| е           | 2.29       | BSC   | .090 | BSC  |        |

| L           | 8.89       | 9.65  | .350 | .380 |        |

| L1          | 1.91       | 2.29  | .045 | .090 |        |

| L2          | 0.89       | 1.27  | .035 | .050 | 4      |

| L3          | 0.89       | 1.52  | .035 | .060 | 5      |

| ø1          | 0.         | 15°   | 0,   | 15*  |        |

| ø2          | 25°        | 35°   | 25*  | 35*  |        |

|             |            |       |      |      |        |

#### LEAD ASSIGNMENTS

#### **HEXFET**

- 1.- GATE

- 2.- DRAIN

- 3.- SOURCE 4.- DRAIN

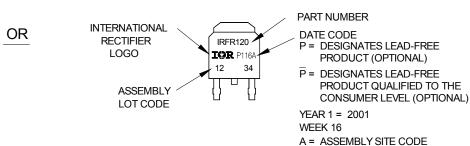

## I-Pak (TO-251AA) Part Marking Information

Note: For the most current drawing please refer to Infineon's web site www.infineon.com

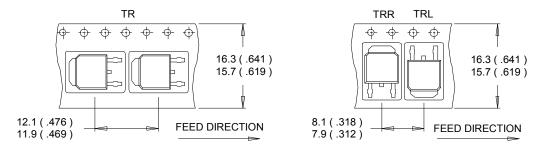

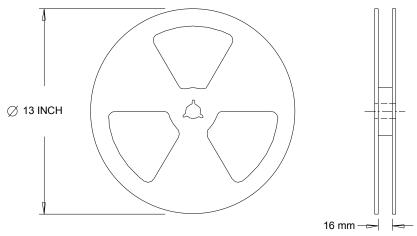

# D-Pak (TO-252AA) Tape & Reel Information Dimensions are shown in millimeters (inches)

### NOTES:

- CONTROLLING DIMENSION : MILLIMETER.

ALL DIMENSIONS ARE SHOWN IN MILLIMETERS ( INCHES ).

- 3. OUTLINE CONFORMS TO EIA-481 & EIA-541.

## NOTES:

1. OUTLINE CONFORMS TO EIA-481.

Note: For the most current drawing please refer to Infineon's web site www.infineon.com

2016-5-31

## Qualification Information<sup>†</sup>

| Qualification Level        | Industrial (per JEDEC JESD47F) †† |                           |  |  |

|----------------------------|-----------------------------------|---------------------------|--|--|

| Moisture Sensitivity Level | D-Pak                             | MSL1                      |  |  |

| Moisture Sensitivity Level | I-Pak                             | (per JEDEC J-STD-020D) †† |  |  |

| RoHS Compliant             | Yes                               |                           |  |  |

- † Qualification standards can be found at Infineon's web site <a href="www.infineon.com">www.infineon.com</a>

- †† Applicable version of JEDEC standard at the time of product release.

## **Revision History**

| Date      | Comments                                   |  |  |

|-----------|--------------------------------------------|--|--|

| 5/31/2016 | Updated datasheet with corporate template. |  |  |

| 3/31/2010 | Added disclaimer on last page.             |  |  |

#### **Trademarks of Infineon Technologies AG**

µHVIC™, µIPM™, µPFC™, AU-ConvertIR™, AURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, CoolDP™, CoolGaN™, COOLIR™, CoolMOS™, CoolSiC™, DAVE™, DI-POL™, DirectFET™, DrBlade™, EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPACK™, EconoPIM™, EiceDRIVER™, eupec™, FCOS™, GaNpowiR™, HEXFET™, HITFET™, HybridPACK™, iMOTION™, IRAM™, ISOFACE™, IsoPACK™, LEDrivIR™, LITIX™, MIPAQ™, ModSTACK™, my-d™, NovalithIC™, OPTIGA™, OptiMOS™, ORIGA™, PowIRaudio™, PowIRStage™, PrimePACK™, PrimeSTACK™, PROFET™, PRO-SIL™, RASIC™, REAL3™, SmartLEWIS™, SOLID FLASH™, SPOC™, StrongIRFET™, SupIRBuck™, TEMPFET™, TRENCHSTOP™, TriCore™, UHVIC™, XHP™, XMC™

Trademarks updated November 2015

### **Other Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2016-04-19

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2016 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference ifx1

### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

Please note that this product is not qualified according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

## WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.