# 8/16-BIT MCU FOR 3-PHASE AC MOTOR CONTROL

- Register File based 8/16 bit Core Architecture with RUN, WFI, SLOW, HALT and STOP modes

- 0-25 MHz Operation (internal clock) @ 5V±10% voltage range

- -40°C to +85°C Operating Temperature Range

- Fully Programmable PLL Clock Generator, with Frequency Multiplication and low frequency, low cost external crystal (3-5 MHz)

- Minimum Instruction Cycle time: 160 ns (@ 25 MHz internal clock frequency)

- Internal Memory:

- EPROM/OTP/FASTROM 16K bytes

- RAM 512 bytes

- 224 general purpose registers available as RAM, accumulators or index pointers (register file)

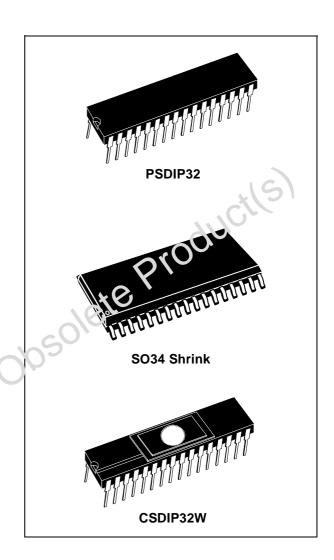

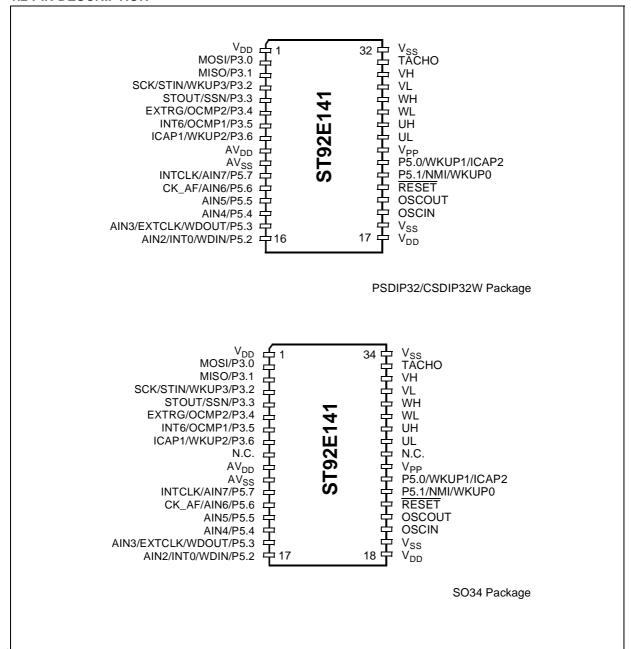

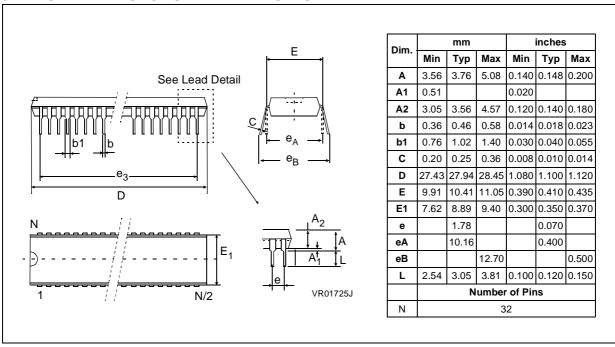

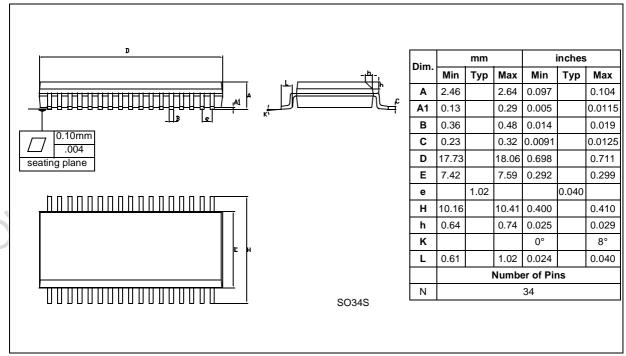

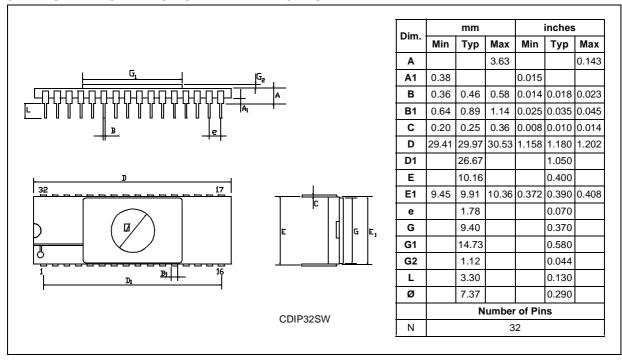

- 32-pin Dual Inline and 34-pin Small Outline Packages

- 15 programmable I/O pins with Schmitt Trigger input, including 4 high sink outputs (20mA @ V<sub>OL</sub>=3V)

- 4 Wake-up Interrupts (one usable as Non-Maskable Interrupt) for emergency event management

- 3-phase Induction Motor Controlle: (IMC) Peripheral with 3 pairs of PWM outputs and asynchronous emergency stop

- Serial Peripheral Interface (S.P.I) with Master/ Slave Mode capability

- 16-bit Timer with 8-bit Prescaler usable as a Watchdog Timer

- 16-bit Standard Timer with 8-bit Prescaler

- 16-bit ፲ኣ⁺er aed Function Timer with Prescaler, 2 Input Captures and 2 Output Compares

- ຈ -ວາ. Analog to Digital Converter allowing up to 6 input channels with autoscan and watchdog capability

- Low Voltage Detector Reset

- Rich Instruction Set with 14 Addressing Modes

- Division-by-Zero trap generation

- Versatile Development Tools, including Assembler, Linker, C-compiler, Archiver, Source Level Debugger and Hardware Emulators with Real-Time Operating System available from Third Parties

#### **DEVICE SUMMARY**

| DEVICE   | CE Program RAM (Bytes) |     | PACKAGE          |

|----------|------------------------|-----|------------------|

| ST92P141 | 16K FASTROM            | 512 | PSDIP32/<br>SO34 |

| ST92E141 | 16K EPROM              | 512 | CSDIP32W         |

| ST92T141 | 16K OTP                | 512 | PSDIP32/<br>SO34 |

Rev. 1.7

October 2001 1/179

# Table of Contents

| 1 GE   | NERA                                          | L DESCRIPTION                         | 6 |

|--------|-----------------------------------------------|---------------------------------------|---|

| 1.     | 1 INT                                         | RODUCTION (                           | 6 |

|        | 1.1.                                          | 1 ST9+ Core                           | 6 |

|        | 1.1.                                          | 2 Power Saving Modes                  | 6 |

|        | 1.1.                                          | · · · · · · · · · · · · · · · · · · · |   |

|        | 1.1.                                          | ·                                     |   |

|        | 1.1.                                          |                                       |   |

|        | 1.1.                                          | 6 3-phase Induction Motor Controller  | 7 |

|        | 1.1.                                          |                                       |   |

|        | 1.1.                                          | 8 Standard Timer                      | 7 |

|        | 1.1.                                          | 9 Extended Function Timer             | 7 |

|        | 1.1.                                          | 10 Serial Peripheral Interface (SPI)  | 7 |

|        | 1.1.                                          | 11 Analog/Digital Converter (ADC)     | 7 |

| 1.     | 2 PIN                                         | DESCRIPTION                           | 9 |

|        | 1.2.                                          | 1 I/O Port Configuration              | 1 |

|        | 1.2.                                          | 2 I/O Port Reset State                | 1 |

| 1.     | 3 MEI                                         | MORY MAP 14                           | 4 |

|        | 1.3.                                          | 1 Memory Configuration                | 4 |

|        | 1.3.                                          | 2 EPROM Programming 14                |   |

| 1.     |                                               | GISTER MAP                            |   |

| 2 DE   | VICE A                                        | ARCHITECTURE 20                       | 0 |

| 2.     | 1 CO                                          | RE ARCHITECTURE 20                    | ი |

| 2.     |                                               | MORY SPACES                           |   |

|        | 2.2.                                          |                                       |   |

|        | 2.2.                                          | · ·                                   |   |

| 2      |                                               | STEM REGISTERS                        |   |

| ۷.     |                                               | 1 Central Interrupt Control Register  |   |

|        | 2.3.                                          |                                       |   |

|        | 2.3.                                          | 5 5                                   |   |

|        | 2.3.                                          | · ·                                   |   |

|        | 2.3.                                          |                                       |   |

|        | 2.3.                                          |                                       |   |

| 2      |                                               | MORY ORGANIZATION                     |   |

| 2.     |                                               | MORY MANAGEMENT UNIT                  |   |

|        |                                               | DRESS SPACE EXTENSION                 |   |

| ۷.     | 0 ADI<br>2.6.                                 |                                       |   |

|        | 2.6.<br>2.6.                                  | • •                                   |   |

| 2.     | _                                             | U REGISTERS                           |   |

| ۷.     |                                               |                                       |   |

| 1      | 2.7.<br>2.7.                                  |                                       |   |

|        | 2.7.<br>2.7.                                  |                                       |   |

|        |                                               |                                       |   |

| 2      | 2.7.<br>• • • • • • • • • • • • • • • • • • • | - 3 - 3 3 3                           |   |

| ۷.     |                                               | U USAGE                               |   |

|        | 2.8.                                          |                                       |   |

|        | 2.8.                                          |                                       |   |

| 2 1817 | 2.8.<br>EDDII                                 | 3 DMA                                 |   |

|        |                                               | RODUCTION 39                          |   |

|        | 1 1171                                        | KUDUCHUN -4                           | ч |

# Table of Contents —

|     | 3.2  | INTERRUPT VECTORING                               | 39 |

|-----|------|---------------------------------------------------|----|

|     |      | 3.2.1 Divide by Zero trap                         | 39 |

|     |      | 3.2.2 Segment Paging During Interrupt Routines    | 40 |

|     | 3.3  | INTERRUPT PRIORITY LEVELS                         |    |

|     | 3.4  | PRIORITY LEVEL ARBITRATION                        | 40 |

|     |      | 3.4.1 Priority level 7 (Lowest)                   | 40 |

|     |      | 3.4.2 Maximum depth of nesting                    |    |

|     |      | 3.4.3 Simultaneous Interrupts                     |    |

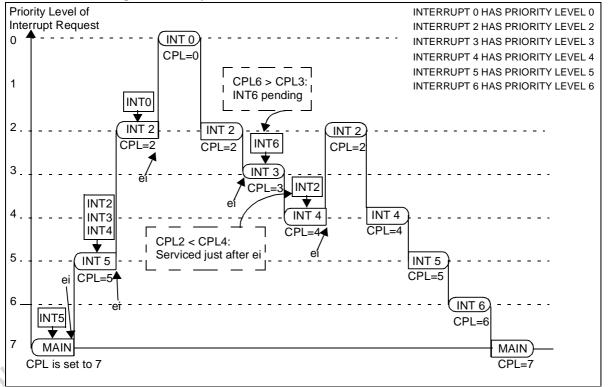

|     |      | 3.4.4 Dynamic Priority Level Modification         | 41 |

|     | 3.5  | ARBITRATION MODES                                 | 41 |

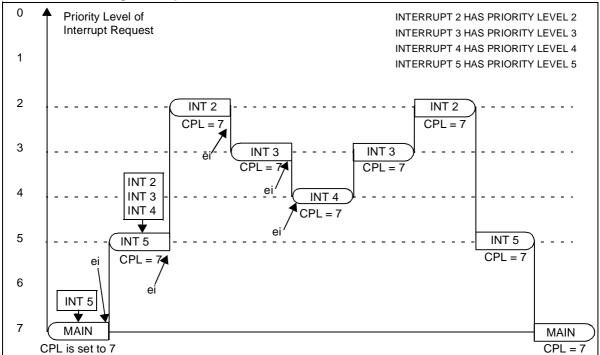

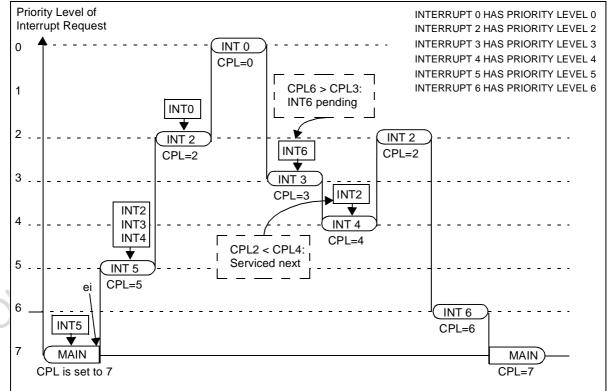

|     |      | 3.5.1 Concurrent Mode                             | 41 |

|     |      | 3.5.2 Nested Mode                                 | 44 |

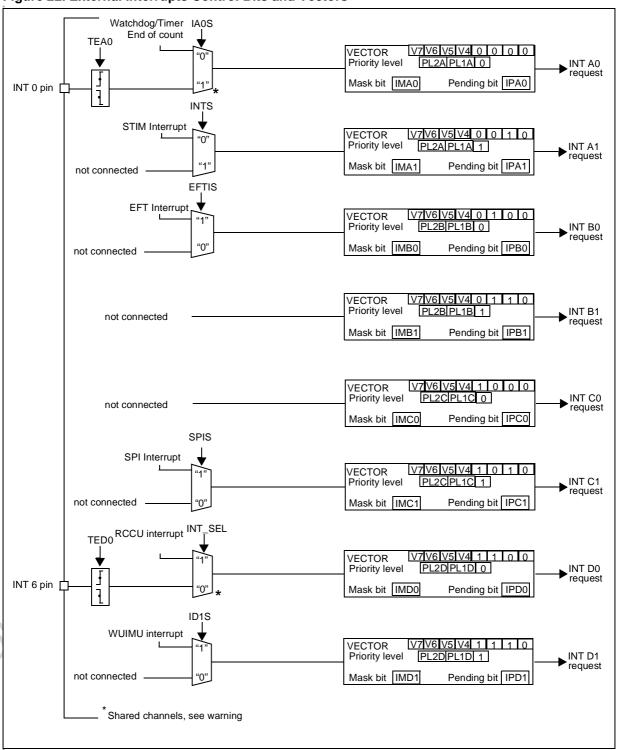

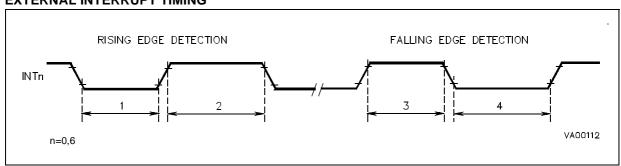

|     | 3.6  | EXTERNAL INTERRUPTS                               | 46 |

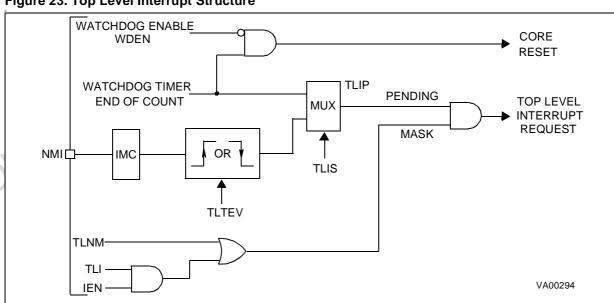

|     | 3.7  | TOP LEVEL INTERRUPT                               | 48 |

|     | 3.8  | ON-CHIP PERIPHERAL INTERRUPTS                     | 48 |

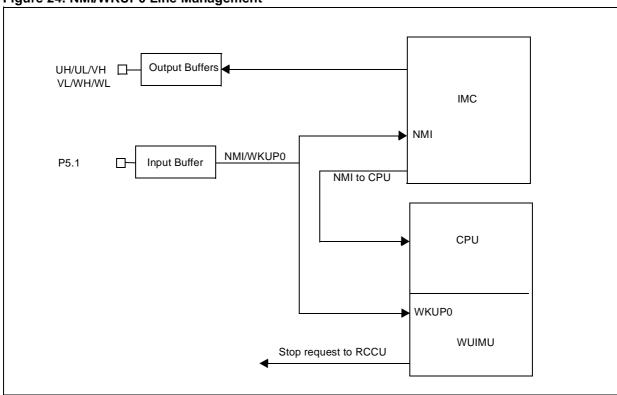

|     | 3.9  | NMI/WKP0 LINE MANAGEMENT                          | 49 |

|     |      | 3.9.1 NMI/Wake-Up Event Handling in Run mode      | 50 |

|     |      | 3.9.2 NMI/Wake-Up Event Handling in STOP mode     |    |

|     |      | 3.9.3 Unused Wake Up Management Unit lines        | 50 |

|     | 3.10 | INTERRUPT RESPONSE TIME                           | 51 |

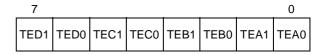

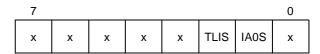

|     | 3.11 | INTERRUPT REGISTERS                               | 52 |

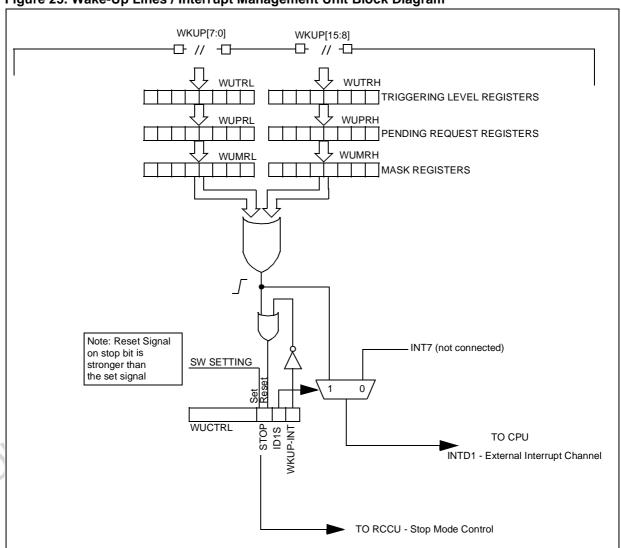

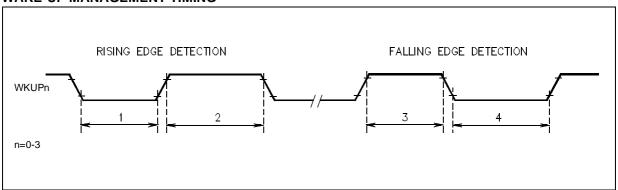

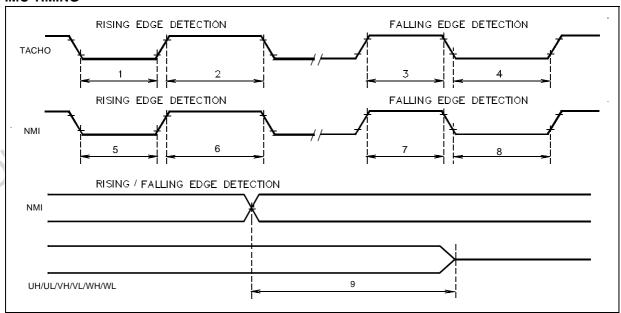

|     | 3.12 | WAKE-UP / INTERRUPT LINES MANAGEMENT UNIT (WUIMU) | 55 |

|     |      | 3.12.1 Introduction                               | 55 |

|     |      | 3.12.2 Main Features                              | 55 |

|     |      | 3.12.3 Functional Description                     | 56 |

|     |      | 3.12.4 Programming Considerations                 | 57 |

|     |      | 3.12.5 Register Description                       | 59 |

|     |      | CONFIGURATION REGISTERS (EM)                      |    |

| 5 F | RESE | ET AND CLOCK CONTROL UNIT (RCCU)                  | 63 |

|     | 5.1  | INTRODUCTION                                      | 63 |

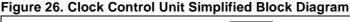

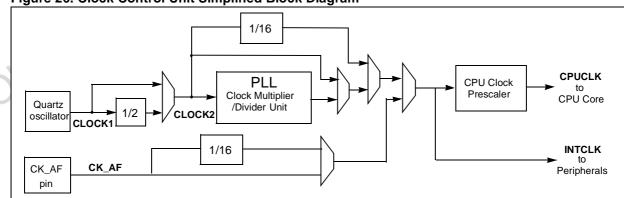

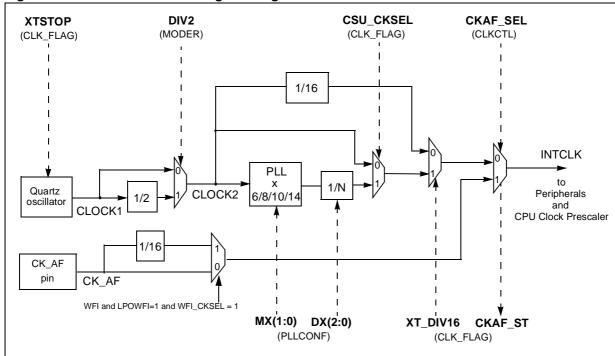

|     | 5.2  | CLOCK CONTROL UNIT                                | 63 |

|     |      | 5.2.1 Clock Control Unit Overview                 | 63 |

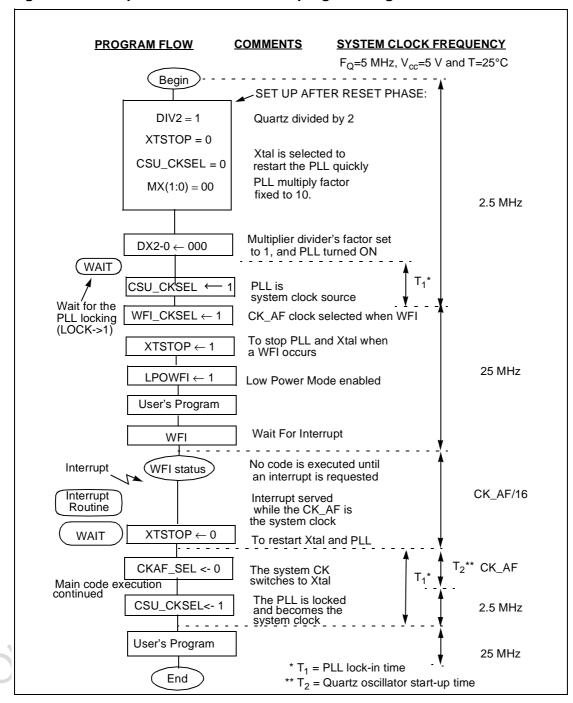

|     | 5.3  | CLOCK MANAGEMENT                                  | 65 |

|     |      | 5.3.1 PLL Clock Multiplier Programming            | 66 |

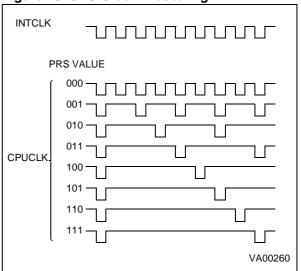

|     |      | 5.3.2 CPU Clock Prescaling                        | 66 |

|     |      | 5.3.3 Peripheral Clock                            |    |

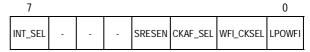

|     |      | 5.3.4 Low Power Modes                             | 67 |

|     |      | 5.3.5 Interrupt Generation                        |    |

|     |      | CLOCK CONTROL REGISTERS                           |    |

|     | 5.5  | OSCILLATOR CHARACTERISTICS                        | 73 |

|     | 5.6  | RESET/STOP MANAGER                                | 74 |

|     |      | 5.6.1 Reset Pin Timing                            | 75 |

|     | 5.7  | STOP MODE                                         | 76 |

|     | 5.8  | LOW VOLTAGE DETECTOR (LVD)                        | 78 |

| 6 I | /O P | ORTS                                              | 79 |

|     | 6.1  | INTRODUCTION                                      | 79 |

|     | 6.2  | SPECIFIC PORT CONFIGURATIONS                      | 79 |

# Table of Contents

| 6.3      | PORT CONTROL REGISTERS                             | 79  |

|----------|----------------------------------------------------|-----|

| 6.4      | INPUT/OUTPUT BIT CONFIGURATION                     | 80  |

| 6.5      | ALTERNATE FUNCTION ARCHITECTURE                    | 84  |

|          | 6.5.1 Pin Declared as I/O                          | 84  |

|          | 6.5.2 Pin Declared as an Alternate Function Input  | 84  |

|          | 6.5.3 Pin Declared as an Alternate Function Output | 84  |

| 6.6      | I/O STATUS AFTER WFI, HALT AND RESET               | 84  |

| 7 ON-C   | CHIP PERIPHERALS                                   | 85  |

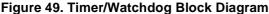

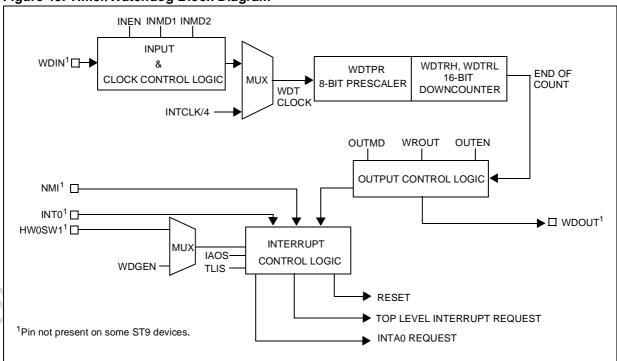

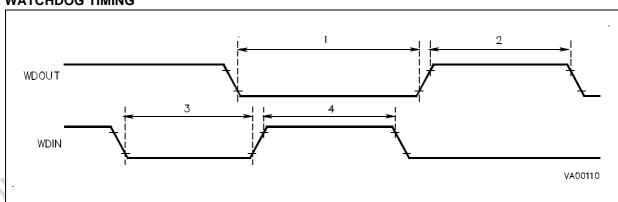

| 7.1      | TIMER/WATCHDOG (WDT)                               | 85  |

|          | 7.1.1 Introduction                                 | 85  |

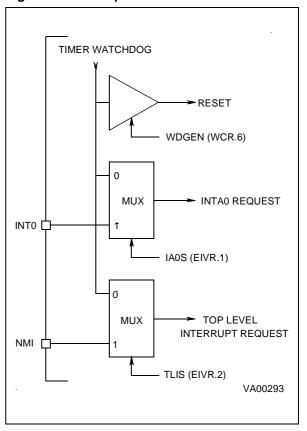

|          | 7.1.2 Functional Description                       | 86  |

|          | 7.1.3 Watchdog Timer Operation                     | 87  |

|          | 7.1.4 WDT Interrupts                               | 89  |

|          | 7.1.5 Register Description                         | 90  |

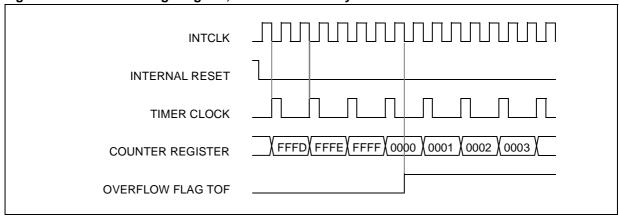

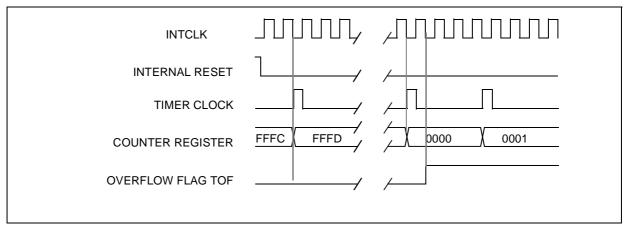

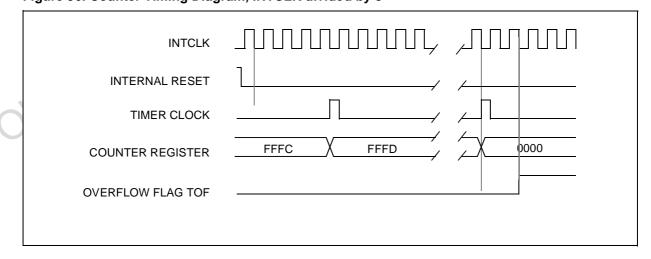

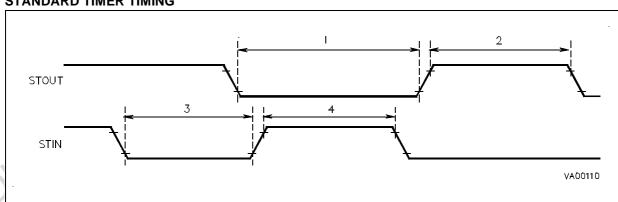

| 7.2      | STANDARD TIMER (STIM)                              | 92  |

|          | 7.2.1 Introduction                                 | 92  |

|          | 7.2.2 Functional Description                       | 93  |

|          | 7.2.3 Interrupt Selection                          | 94  |

|          | 7.2.4 Register Mapping                             | 94  |

|          | 7.2.5 Register Description                         | 95  |

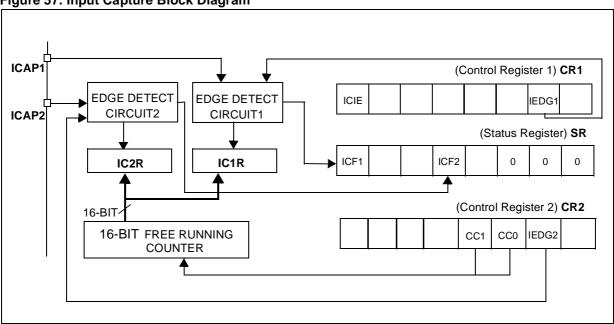

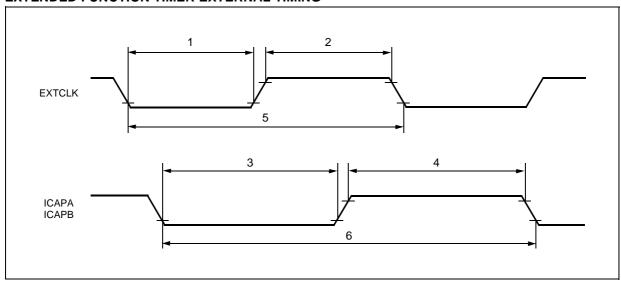

| 7.3      | EXTENDED FUNCTION TIMER (EFT)                      | 96  |

|          | 7.3.1 Introduction                                 | 96  |

|          | 7.3.2 Main Features                                | 96  |

|          | 7.3.3 Functional Description                       | 96  |

|          | 7.3.4 Interrupt Management                         |     |

|          | 7.3.5 Register Description                         | 108 |

| 7.4      | 3-PHASE INDUCTION MOTOR CONTROLLER (IMC)           | 116 |

|          | 7.4.1 Introduction                                 | 116 |

|          | 7.4.2 Main Features                                | 116 |

|          | 7.4.3 Functional Description                       |     |

|          | 7.4.4 Tacho Counter Operating mode                 |     |

|          | 7.4.5 IMC Operating mode                           |     |

|          | 7.4.6 IMC Output selection                         |     |

|          | 7.4.7 NMI management                               |     |

|          | 7.4.8 Register Description                         |     |

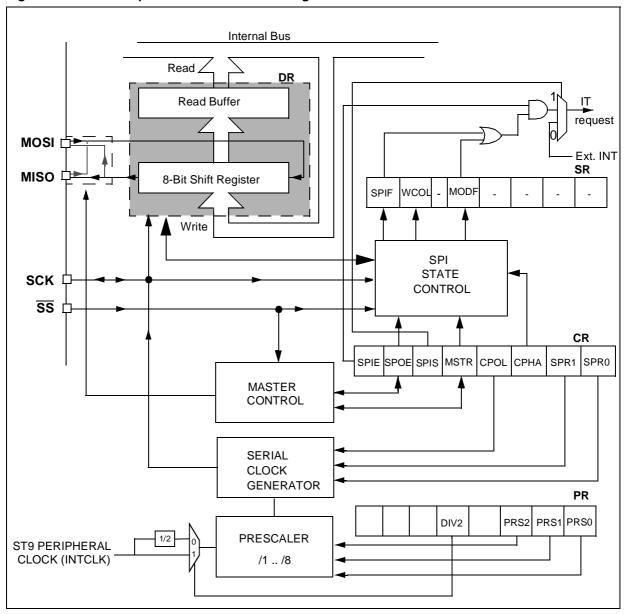

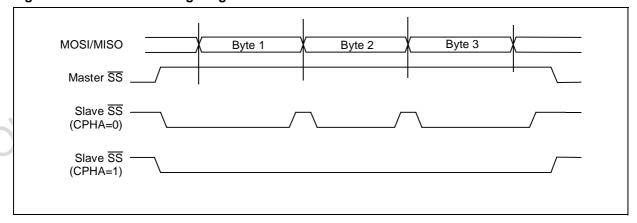

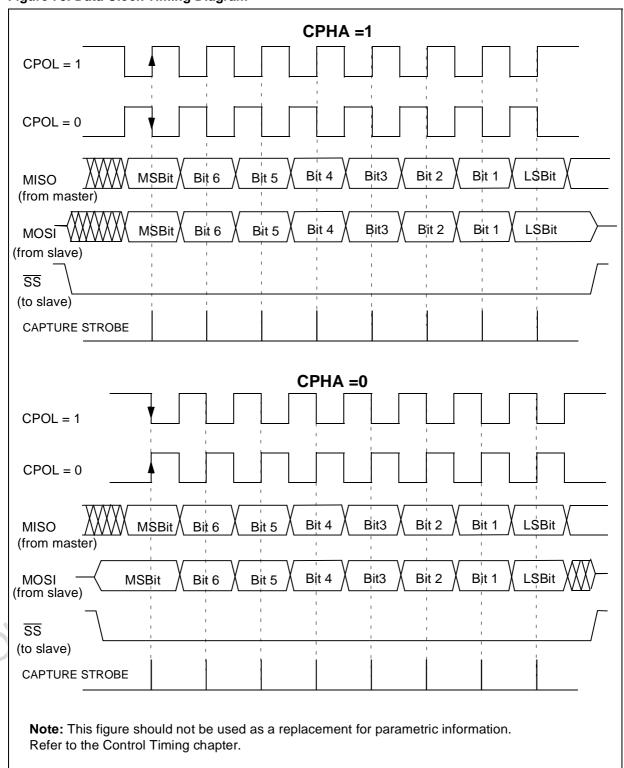

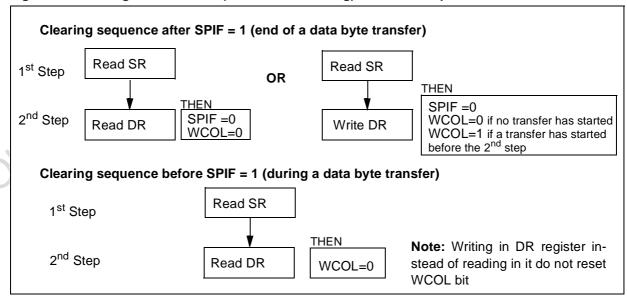

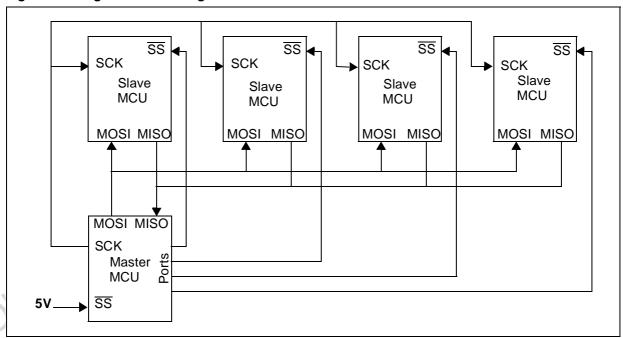

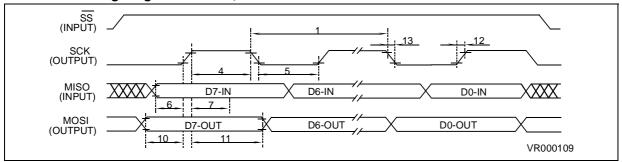

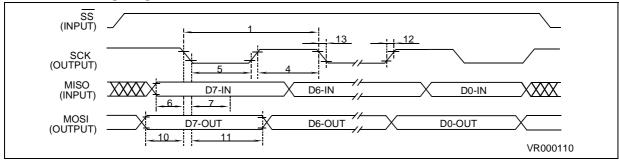

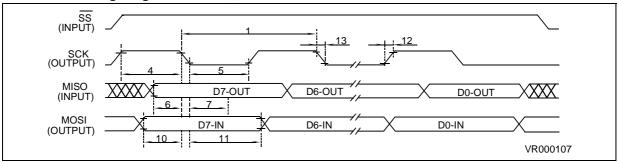

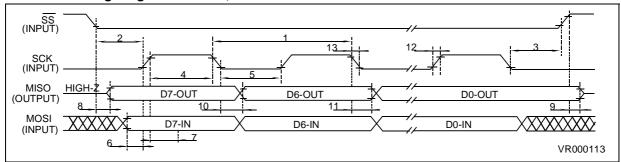

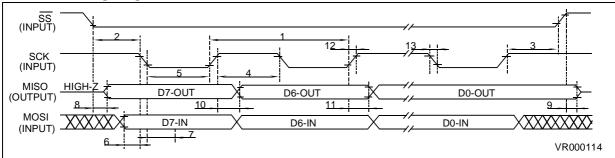

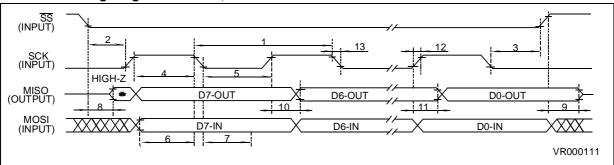

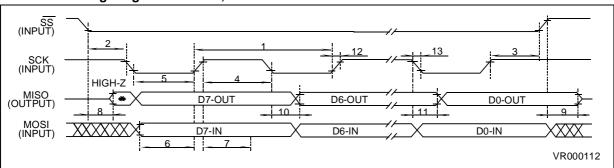

| 7.5      | SERIAL PERIPHERAL INTERFACE (SPI)                  |     |

|          | 7.5.1 Introduction                                 |     |

|          | 7.5.2 Main Features                                |     |

| 1        | 7.5.3 General Description                          |     |

|          | 7.5.4 Functional Description                       |     |

|          | 7.5.5 Interrupt Management                         |     |

|          | 7.5.6 Register Description                         |     |

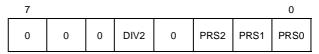

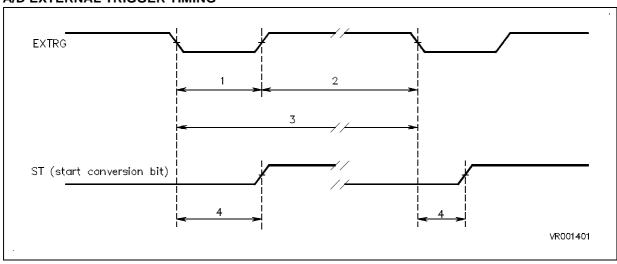

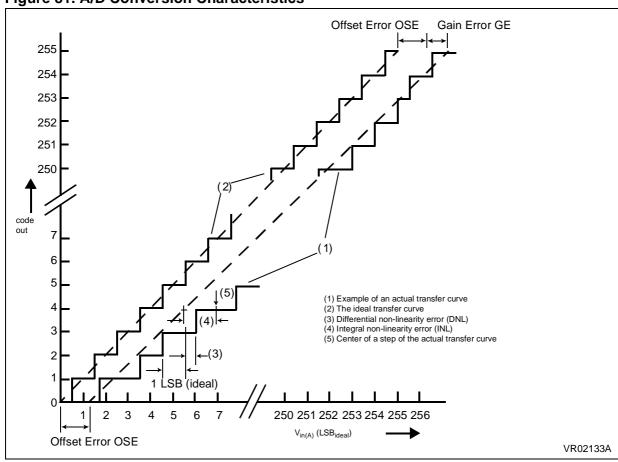

| 7.6      | ANALOG TO DIGITAL CONVERTER (ADC)                  |     |

|          | 7.6.1 Introduction                                 |     |

|          | 7.6.2 Functional Description                       |     |

|          | 7.6.3 Interrupts                                   |     |

| o =: = - | 7.6.4 Register Description                         |     |

| 8 ELEC   | CTRICAL CHARACTERISTICS                            | 156 |

# ——— Table of Contents ——

| 9 ( | SENE | ERAL INFORMATION          | 174 |

|-----|------|---------------------------|-----|

|     | 9.1  | PACKAGE MECHANICAL DATA   | 174 |

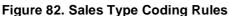

|     | 9.2  | ORDERING INFORMATION      | 176 |

|     | 9.3  | TRANSFER OF CUSTOMER CODE | 176 |

| 10  | SHIN | MMARY OF CHANGES          | 178 |

# 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

The ST92141 microcontroller is developed and manufactured by STMicroelectronics using a proprietary n-well HCMOS process. Its performance derives from the use of a flexible 256-register programming model for ultra-fast context switching and real-time event response. The intelligent onchip peripherals offload the ST9 core from I/O and data management processing tasks allowing critical application tasks to get the maximum use of core resources. The new-generation ST9 MCU devices now also support low power consumption and low voltage operation for power-efficient and low-cost embedded systems.

#### 1.1.1 ST9+ Core

The advanced Core consists of the Central Processing Unit (CPU), the Register File, the Interrupt controller, and the Memory Management Unit. The MMU allows addressing of up to 4 Megabytes of program and data mapped into a single linear space.

Four independent buses are controlled by the Core: a 16-bit memory bus, an 8-bit register data bus, an 8-bit register address bus and a 6-bit interrupt bus which connects the interrupt controllers in the on-chip peripherals with the core.

**Note:** The DMA features of the ST9+ core are not used by the on-chip peripherals of the ST92141.

This multiple bus architecture makes the ST9 family devices highly efficient for accessing on and offchip memory and fast exchange of data with the on-chip peripherals.

The general-purpose registers can be used as accumulators, index registers, or address pointers. Adjacent register pairs make up 16-bit registers for addressing or 16-bit processing. Although the ST9 has an 8-bit ALU, the chip handles 16-bit operations, including arithmetic, loads/stores, and memory/register and memory/memory exchanges.

# 1.1.2 Power Saving Modes

To optimize performance versus power consumption, a range of operating modes can be dynamically selected by software according to the requirements of the application.

**Run Mode.** This is the full speed execution mode with CPU and peripherals running at the maximum clock speed delivered either by the Phase Locked Loop controlled by the RCCU (Reset and Clock Control Unit), directly by the oscillator or by an ex-

ternal source (dedicated Pin or Alternate Function).

**Slow Mode**. Power consumption can be significantly reduced by running the CPU and the peripherals at reduced clock speed using the CPU Prescaler and RCCU Clock Divider.

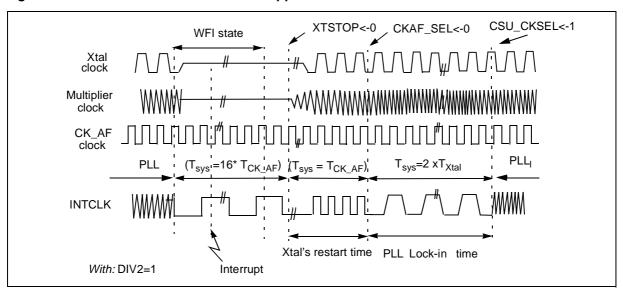

Wait For Interrupt Mode. The Wait For Interrupt (WFI) instruction suspends program execution until an interrupt request is acknowledged. During WFI, the CPU clock is halted while the peripheral with interrupt capability and interrupt controller are kept running at a frequency that can be programmed by software in the RCCU registers. In this mode, the power consumption of the device can be reduced by more than 95% (Low Power WFI).

Halt Mode. When executing the HALT instruction, and if the Watchdog is not enabled, the CPU and its peripherals stop operating. If however the Watchdog is enabled, the HALT instruction has no effect. The main difference between Halt mode and Stop mode is that a reset is necessary to exit from Halt mode which causes the system to be reinitialized.

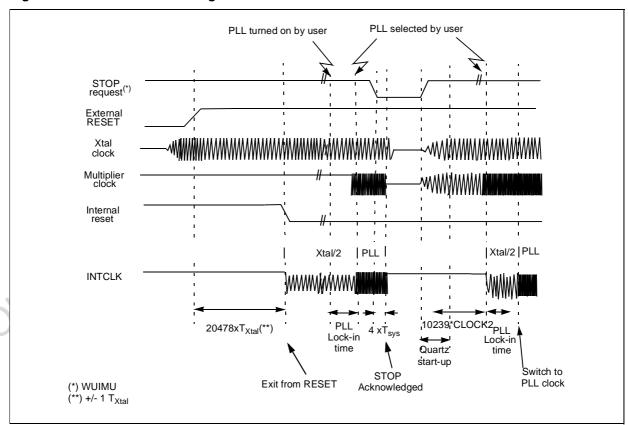

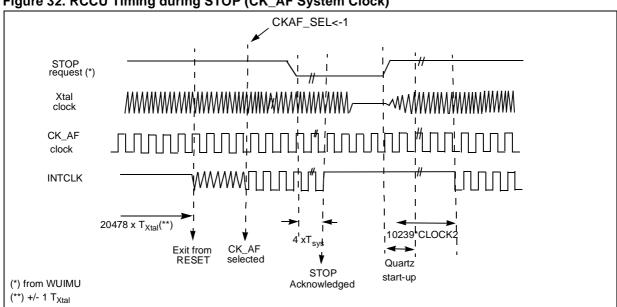

**Stop Mode.** When Stop mode is requested by executing the STOP sequence (see Wake-up Management Unit section), the CPU and the peripherals stop operating. Operations resume after a wake-up line is activated. The difference between Stop mode and Halt mode is in the way the CPU exits each state: when the STOP sequence is executed, the status of the registers is recorded, and when the system exits from Stop mode the CPU continues execution with the same status, without a system reset.

The Watchdog counter, if enabled, is stopped. After exiting Stop mode it restarts counting from where it left off.

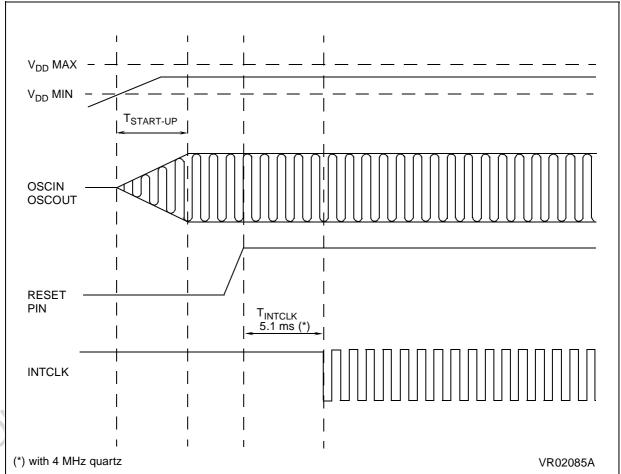

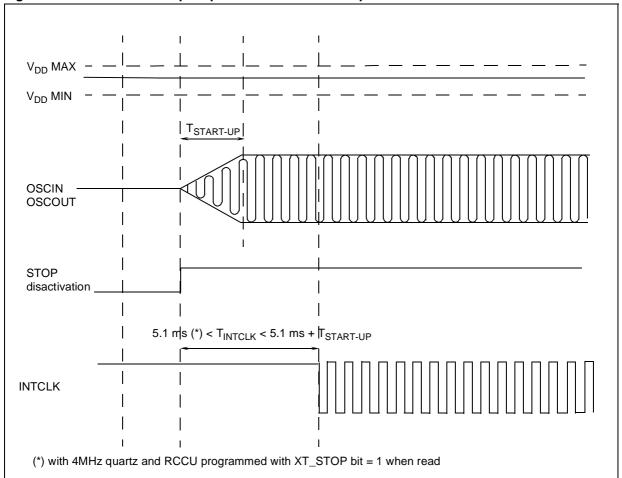

When the MCU exits from STOP mode, the oscillator, which was also sleeping, requires a start-up time to restart working properly. An internal counter is present to guarantee that, after exiting Stop Mode, all operations take place with the clock stabilised.

# 1.1.3 System Clock

A programmable PLL Clock Generator allows standard 3 to 5 MHz crystals to be used to obtain a large range of internal frequencies up to 25MHz.

#### 1.1.4 Low Voltage Reset

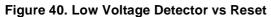

The on-chip Low Voltage Detector (LVD) generates a static reset when the supply voltage is below a reference value. The LVD works both during power-on as well as when the power supply drops (brown-out). The reference value for the voltage drop is lower than the reference value for power-on in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

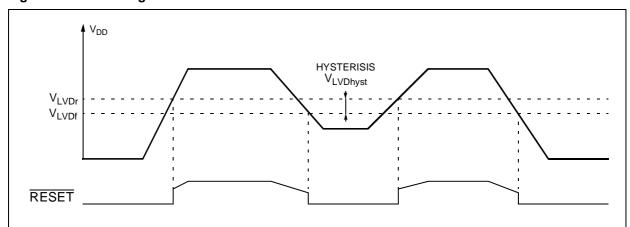

#### 1.1.5 I/O Ports

The I/O lines are grouped into two I/O Ports and can be configured on a bit basis to provide timing, status signals, an address/data bus for timer inputs and outputs, analog inputs, external wake-up lines and serial or parallel I/O.

#### 1.1.6 3-phase Induction Motor Controller

The IMC controller is designed for variable speed motor control applications. Three pairs of PWM outputs are available for controlling a three-phase motor drive. Rotor speed feedback is provided by capturing a tachogenerator input signal. Emergency stop is provided by putting the PWM outputs in high impedance mode upon asynchronous faulty event on NMI pin.

#### 1.1.7 Watchdog Timer (WDT)

The Watchdog timer can be used to monitor system integrity. When enabled, it generates a reset after a timeout period unless the counter is refreshed by the application software. For additional security, watchdog function can be enabled by hardware using a specific pin.

#### 1.1.8 Standard Timer

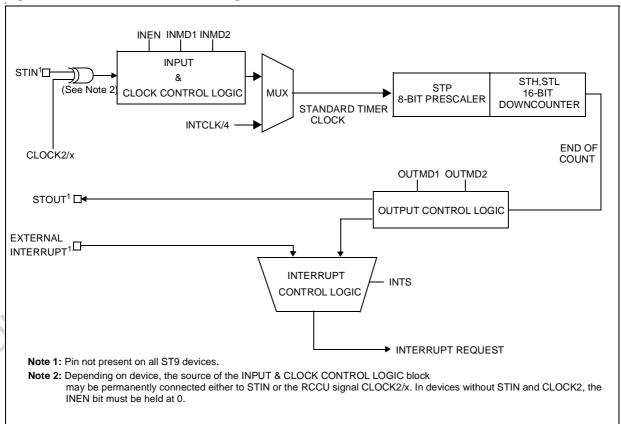

The standard timer includes a programmable 16-bit down-counter and an associated 8-bit prescaler with Single and Continuous counting modes.

#### 1.1.9 Extended Function Timer

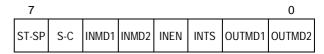

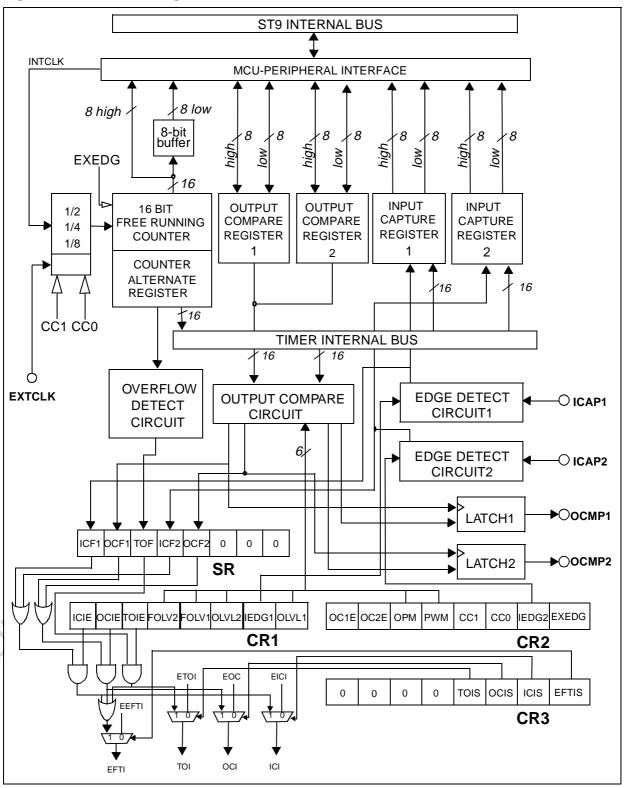

The Extended Function Timer can be used for a wide range of standard timing tasks. It has a 16-bit free running counter with programmable prescaler. Each timer can have up to 2 input capture and 2 output compare pins with associated registers. This allows applications to measure pulse intervals or generate pulse waveforms. Timer overflow and other events are flagged in a status register with optional interrupt generation.

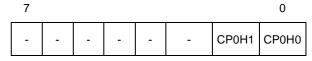

# 1.1.10 Serial Peripheral Interface (SPI)

The SPI bus is used to communicate with external devices via the SPI, or I<sup>2</sup>C bus communication standards.

#### 1.1.11 Analog/Digital Converter (ADC)

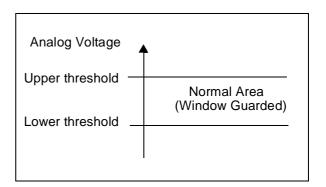

The ADC provides up to 6 analog inputs with onchip sample and hold. The analog watchdog generates an interrupt when the input voltage moves out of a preset threshold.

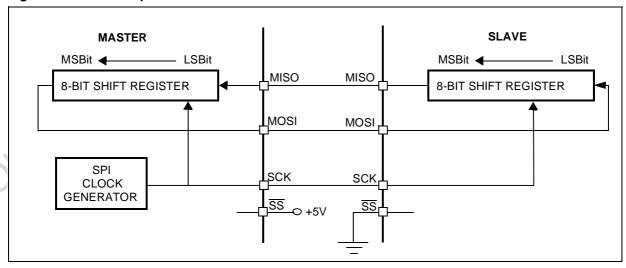

EPROM/ **FASTROM** 16K BUS  $\mathsf{RAM}$ P3[6:0] ully Prog. P5[7:0] 512 bytes I/Os MEMORY Register File 256 bytes WATCHDOG WDIN 8/16-bit **WDOUT** CPU NMI WKUP[3:0] ÎNTÔ Interrupt REGISTER BUS MISO Management INT6 MOSI SPI SCK ST9+ CORE SSN A/D Converter **OSCIN** AIN[7:2] with analog OSCOUT EXTRG RCCU + LVD RESET watchdog **INTCLK** CK\_AF **TACHO** UH UL ICAP1 IMC ٧H OCMP1 ٧L **EF TIMER** ICAP2 WH OCMP2 WL **EXTCLK** STIN STIM TIMER STOUT

Figure 1. ST92141 Block Diagram

8/179

All alternate functions (Italic characters) are mapped on Port3 and Port5

# 1.2 PIN DESCRIPTION

**Table 1. Power Supply Pins**

| Name             | Function                                                                                      | SDIP32 | <b>SO34</b> |

|------------------|-----------------------------------------------------------------------------------------------|--------|-------------|

| V <sub>PP</sub>  | Programming voltage for EPROM/OTP devices. Must be connected to V <sub>SS</sub> in user mode. | 24     | 25          |

| Vas              | Main power supply voltage (5V ±                                                               | 17     | 18          |

| $V_{DD}$         | 10% (2 pins internally connected)                                                             | 1      | 1           |

| $V_{SS}$         | Digital Circuit Ground (2 pins in-                                                            |        | 19          |

| VSS              | ternally connected)                                                                           | 32     | 34          |

| AV <sub>DD</sub> | Analog $V_{DD}$ of the Analog to Digital Converter                                            | 9      | 10          |

| AV <sub>SS</sub> | Analog V <sub>SS</sub> of the Analog to Digital Converter                                     | 10     | 11          |

**Table 2. Primary Function pins**

| Name   | Function                                                                                                                                                                                                                     | SDIP32 | 8034 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| TACHO  | Signal input from a tachogenera-<br>tor to the IMC controller for<br>measuring the rotor speed                                                                                                                               | 31     | 33   |

| UH     | U-phase PWM output signal                                                                                                                                                                                                    | 26     | 28   |

| VH     | V-phase PWM output signal                                                                                                                                                                                                    | 30     | 32   |

| WH     | W-phase PWM output signal                                                                                                                                                                                                    | 28     | 30   |

| UL     | The complemented UH, VH, WH                                                                                                                                                                                                  | 25     | 27   |

| VL     | output signals with added dead time to avoid crossover conduc-                                                                                                                                                               | 29     | 31   |

| WL     | tion from the power driver                                                                                                                                                                                                   | 27     | 29   |

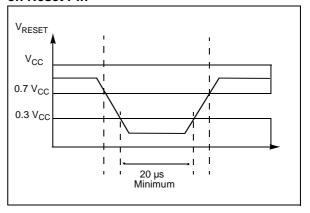

| RESET  | Reset (input, active low). The ST9+ is initialised by the Reset signal. With the deactivation of RESET, program execution begins from the memory location pointed to by the vector contained in memory locations 00h and 01h | 21     | 22   |

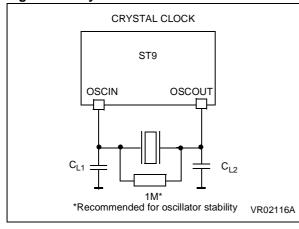

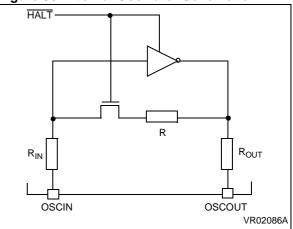

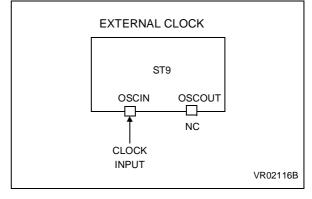

| OSCIN  | OSCIN is the input of the oscillator inverter and internal clock generator. OSCIN and OSCOUT connect a parallel-resonant crystal (3 to 5 MHz), or an external source to the on-chip clock oscillator and buffer              | 19     | 20   |

| OSCOUT | OSCOUT is the output of the oscillator inverter                                                                                                                                                                              | 20     | 21   |

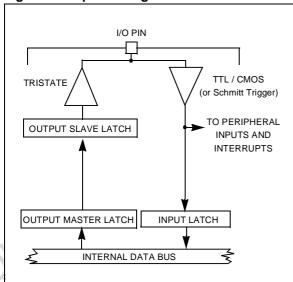

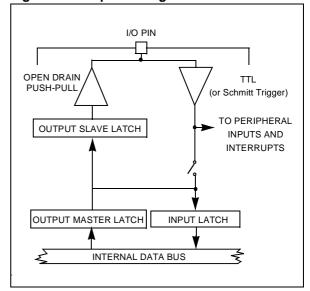

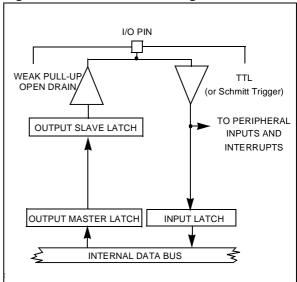

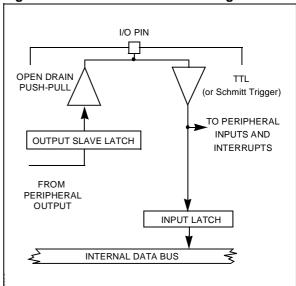

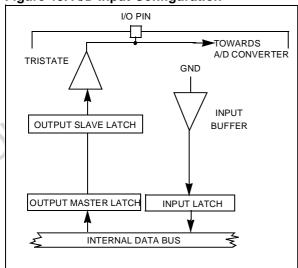

# 1.2.1 I/O Port Configuration

All ports can be individually configured as input, bidirectional, output, or alternate function. Refer to the Port Bit Configuration Table in the I/O Port Chapter.

All I/Os are implemented with a High Hysteresis or Standard Hysteresis Schmitt trigger function (See Electrical Characteristics).

**Weak Pull-Up** = This column indicates if a weak pull-up is present or not (refer to Table 3).

- If WPU = yes, then the WPU can be enabled/disable by software

- If WPU = no, then enabling the WPU by software has no effect

All port output configurations can be software selected on a bit basis to provide push-pull or open drain driving capabilities. For all ports, when configured as open-drain, the voltage on the pin must never exceed the V<sub>DD</sub> power line value (refer to Electrical characteristics section).

#### 1.2.2 I/O Port Reset State

$\overline{\text{I/Os}}$  are reset asynchronously as soon as the  $\overline{\text{RE-}}$  pin is asserted low.

All I/Os are forced by the Reset in "floating input" configuration mode.

#### WARNING

When a common pin is declared to be connected to an alternate function input and to an alternate function output, the user must be aware of the fact that the alternate function output signal always inputs to the alternate function module declared as input.

When any given pin is declared to be connected to a digital alternate function input, the user must be aware of the fact that the alternate function input is always connected to the pin. When a given pin is declared to be connected to an analog alternate function input (ADC input for example) and if this pin is programmed in the "AF-OD" mode, the digital input path is disconnected from the pin to prevent any DC consumption.

Table 3. I/O Port Characteristics

|             | Input                                 | Output            | Weak Pull-Up | Reset State    |

|-------------|---------------------------------------|-------------------|--------------|----------------|

| Port 3[4:0] | Schmitt trigger (High Hysteresis)     | Push-Pull/OD      | Yes          | Floating input |

| Port 3[6:5] | Schmitt trigger (High Hysteresis)     | Push-Pull/OD (HC) | Yes          | Floating input |

| Port 5.0    | Schmitt trigger (High Hysteresis)     | Push-Pull/OD (HC) | Yes          | Floating input |

| Port 5.1    | Schmitt trigger (High Hysteresis)     | Push-Pull/OD      | Yes          | Floating input |

| Port 5.2    | Schmitt trigger (Standard Hysteresis) | Push-Pull/OD (HC) | Yes          | Floating input |

| Port 5[7:3] | Schmitt trigger (Standard Hysteresis) | Push-Pull/OD      | Yes          | Floating input |

Legend: OD = Open Drain; HC= High current

Table 4. ST92141 Alternate functions

| Port  | General                            | Pin    | No.   |                                  |                                                        | Alternate Functions                |  |

|-------|------------------------------------|--------|-------|----------------------------------|--------------------------------------------------------|------------------------------------|--|

| Name  | Purpose I/O                        | SDIP32 | PSO34 |                                  |                                                        | Alternate Functions                |  |

| P3.0  |                                    | 2      | 2     | MOSI                             | I/O                                                    | SPI Master Output/Slave Input Data |  |

| P3.1  |                                    | 3      | 3     | MISO                             | I/O                                                    | SPI Master Input/Slave Output Data |  |

|       |                                    |        |       | WKUP3                            | ı                                                      | Wake-up line 3                     |  |

| P3.2  |                                    | 4      | 4     | STIN                             | ı                                                      | Standard Timer Input               |  |

|       |                                    |        |       | SCK                              | I/O                                                    | SPI Serial Clock Input/Output      |  |

| P3.3  |                                    | 5      | 5     | SSN                              | ı                                                      | SPI Slave Select                   |  |

| P3.3  |                                    | 5      | 5     | STOUT                            | 0                                                      | Standard Timer Output              |  |

| P3.4  |                                    | 6      | 6     | EXTRG                            | ı                                                      | A/D External trigger               |  |

| P3.4  |                                    | 6      | 0     | OCPM2                            | 0                                                      | Ext. Timer Output Compare 2        |  |

| P3.5  |                                    | 7      | 7     | INT6                             | ı                                                      | External Interrupt 6               |  |

| F3.5  |                                    | ,      | ,     | OCMP1                            | 0                                                      | Ext. Timer - Output Compare 1      |  |

| P3.6  |                                    | 8      | 8     | ICAP1                            | ı                                                      | Ext. Timer - Input Capture 1       |  |

| F3.0  | A II                               | 0      |       | WKUP2                            | ı                                                      | Wake-up line 2                     |  |

| P5.0  | All ports useable for general pur- | 23 24  |       | ICAP2                            | ı                                                      | Ext. Timer - Input Capture 2       |  |

| F 3.0 | pose I/O (input,                   | 23     | 24    | WKUP1                            | ı                                                      | Wake-up line 1                     |  |

| P5.1  | output or bidi-<br>rectional)      | 22     | 23    | NMI                              | ı                                                      | Not maskable Int.                  |  |

| F 3.1 | , rodional,                        | 22     |       | WKUP0                            | ı                                                      | Wake-up line 0                     |  |

|       |                                    |        |       | AIN2                             | ı                                                      | Analog Data Input 2                |  |

| P5.2  |                                    | 16     | 17    | INT0                             | ı                                                      | External Interrupt 0               |  |

|       |                                    |        |       | WDIN                             | ı                                                      | Watchdog input                     |  |

|       |                                    |        |       | AIN3                             | ı                                                      | Analog Data Input 3                |  |

| P5.3  |                                    | 15     | 16    | EXTCLK                           | ı                                                      | Ext. Timer - Input Clock           |  |

|       |                                    |        |       | WDOUT                            | 0                                                      | Watchdog Output                    |  |

| P5.4  |                                    | 14     | 15    | AIN4                             | AIN4 I Analog Data Input 4  AIN5 I Analog Data Input 5 |                                    |  |

| P5.5  |                                    | 13     | 14    | AIN5                             |                                                        |                                    |  |

| P5.6  |                                    | 12     | 13    | AIN6                             | ı                                                      | Analog Data Input 6                |  |

| 1 3.0 |                                    | 12     |       | CK_AF I Clock Alternative Source |                                                        | Clock Alternative Source           |  |

| P5.7  |                                    | 11     | 12    | AIN7                             | ı                                                      | Analog Data Input 7                |  |

|       |                                    | 11     | 12    | INTCLK                           | 0                                                      | Internal Main Clock                |  |

# How to configure the I/O ports

To configure the I/O ports, use the information in Table 3 and Table 4 and the Port Bit Configuration Table in the I/O Ports Chapter on page 81.

**I/O note** = The hardware characteristics fixed for each port line in Table 3.

All I/O inputs have Schmitt trigger fixed by hardware so selecting CMOS or TTL input by software

has no effect, the input will always be Schmitt Trigger. In particular, the Schmitt Triggers present on the P5[7:2] pins have a standard hysteresis whereas the remaining pins have Schmitt Triggers with High Hysteresis (refer to Electrical Specifications).

Alternate Functions (AF) = More than one AF cannot be assigned to an external pin at the same time:

An alternate function can be selected as follows. AF Inputs:

AF is selected implicitly by enabling the corresponding peripheral. Exceptions to this are ADC analog inputs which must be explicitly selected as AF by software.

AF Outputs or Bidirectional Lines:

In the case of Outputs or I/Os, AF is selected explicitly by software.

# **Example 1: Standard Timer input**

AF: STIN, Port: P3.2, I/O Note: Schmitt trigger. Write the port configuration bits:

P3C2.2=1

P3C1.2=0

P3C0.2=1

or P3C2.2=0

P3C1.2=0

P3C0.2=1

Enable the Standard Timer input by software as described in the STIM chapter.

# **Example 2: Standard Timer output**

AF: STOUT, Port: P3.3

Write the port configuration bits (for AF output push-pull):

P3C2.3=0

P3C1.3=1

P3C0.3=1

# **Example 3: ADC analog input**

AF: AIN2, Port: P5.2, I/O Note: does not apply to analog inputs

Write the port configuration bits:

P5C2.2=1

P5C1.2=1

P5C0.2=1

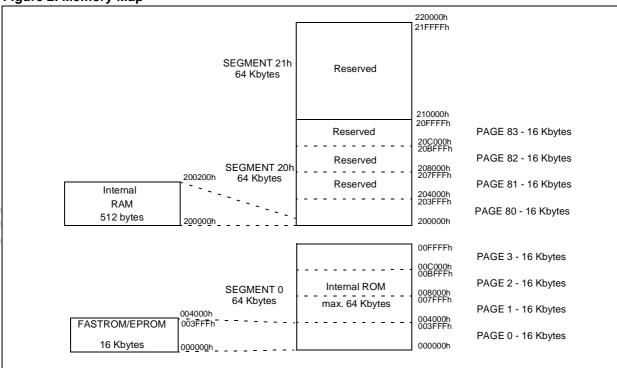

#### 1.3 MEMORY MAP

#### 1.3.1 Memory Configuration

The Program memory space of the ST92141, 16K bytes of directly addressable on-chip memory, is fully available to the user.

The first 256 memory locations from address 0 to FFh hold the Reset Vector, the Top-Level (Pseudo Non-Maskable) interrupt, the Divide by Zero Trap Routine vector and, optionally, the interrupt vector table for use with the on-chip peripherals and the external interrupt sources. Apart from this case no other part of the Program memory has a predetermined function except segment 21h which is reserved for use by STMicroelectronics.

# 1.3.2 EPROM Programming

The 16K bytes of EPROM memory of the ST92E141 may be programmed by using the EPROM Programming Boards (EPB) or gang programmers available from STMicroelectronics.

#### **EPROM Erasing**

The EPROM of the windowed package of the ST92E141 may be erased by exposure to Ultra-Violet light.

The erasure characteristic of the ST92E141 is such that erasure begins when the memory is exposed to light with a wave lengths shorter than approximately 4000Å. It should be noted that sunlight

and some types of fluorescent lamps have wavelengths in the range 3000-4000Å. It is thus recommended that the window of the ST92E141 packages be covered by an opaque label to prevent unintentional erasure problems when testing the application in such an environment.

The recommended erasure procedure of the EPROM is the exposure to short wave ultraviolet light which have a wave-length 2537Å. The integrated dose (i.e. U.V. intensity x exposure time) for erasure should be a minimum of 15W-sec/cm2. The erasure time with this dosage is approximately 30 minutes using an ultraviolet lamp with 12000mW/cm2 power rating. The ST92E141 should be placed within 2.5cm (1 inch) of the lamp tubes during erasure.

Table 5. First 6 Bytes of Program Space

| 0 | Address high of Power on Reset routine         |

|---|------------------------------------------------|

| 1 | Address low of Power on Reset routine          |

| 2 | Address high of Divide by zero trap Subroutine |

| 3 | Address low of Divide by zero trap Subroutine  |

| 4 | Address high of Top Level Interrupt routine    |

| 5 | Address low of Top Level Interrupt routine     |

# 1.4 REGISTER MAP

The following pages contain a list of ST92141 registers, grouped by peripheral or function.

Be very careful to correctly program both:

- The set of registers dedicated to a particular function or peripheral.

- Registers common to other functions.

- In particular, double-check that any registers with "undefined" reset values have been correctly initialised.

**WARNING**: Note that in the **EIVR** and each **IVR** register, all bits are significant. Take care when defining base vector addresses that entries in the Interrupt Vector table do not overlap.

**Table 6. Common Registers**

| Function or Peripheral | Common Registers                                                |

|------------------------|-----------------------------------------------------------------|

| ADC                    | CICR + NICR + I/O PORT REGISTERS                                |

| WDT                    | CICR + NICR + EXTERNAL INTERRUPT REGISTERS + I/O PORT REGISTERS |

| I/O PORTS              | I/O PORT REGISTERS + MODER                                      |

| EXTERNAL INTERRUPT     | INTERRUPT REGISTERS + I/O PORT REGISTERS                        |

| RCCU                   | INTERRUPT REGISTERS + MODER                                     |

Table 7. Group F Pages

Resources available on the ST92141 devices:

| Register |         | Page      |       |           |       |         |      |       |     |      |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

|----------|---------|-----------|-------|-----------|-------|---------|------|-------|-----|------|------|------|--|--|--|--|--|--|------|------|--|-------|--|--|------|

|          | 0       | 2         | 3     | 7         | 11    | 21      | 28   | 48    | 51  | 55   | 57   | 63   |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R255     |         | Res.      |       |           |       |         |      |       |     |      |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R254     | Res.    |           |       |           |       |         |      |       |     |      |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R253     |         | PORT<br>3 |       |           |       | Res.    |      |       |     |      |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R252     | WCR     |           |       |           |       | Res.    |      | IMC   |     |      | WU   |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R251     |         |           | Res.  |           |       |         |      | IIVIC |     | Res. |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R250     | EXT INT | WDT       |       |           | Res.  | Res.    |      |       |     |      |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R249     |         |           |       |           | 1103. | 1103.   | MMU  |       |     |      |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R248     |         |           |       |           |       | IVIIVIO | EFT0 |       | IMC |      |      | A/D0 |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R247     |         |           |       |           |       |         |      |       |     |      |      |      |  |  |  |  |  |  | Res. | LITO |  | livio |  |  | 7,00 |

| R246     |         |           |       | Res.      |       |         |      | EM    |     |      |      | RCCU |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R245     |         |           | 1103. | PORT<br>5 |       |         |      |       |     |      |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R244     |         |           |       |           |       |         |      | Res.  |     | Res. | Res. |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R243     |         |           |       |           |       |         |      | 1163. |     |      |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R242     |         |           | Res.  | SPI0      | STIM0 | мми     |      |       |     |      |      | RCCU |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R241     |         |           | 1165. | JF IU     | STINO |         |      |       |     | Res. |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

| R240     | Nes.    |           |       |           |       |         |      |       |     | RCCU |      |      |  |  |  |  |  |  |      |      |  |       |  |  |      |

**Table 8. Detailed Register Map**

| Page<br>(Decimal) | -   Block   3 |                       | -                       | Description                            | Reset<br>Value<br>Hex. | Doc.<br>Page |  |

|-------------------|---------------|-----------------------|-------------------------|----------------------------------------|------------------------|--------------|--|

|                   |               | R230                  | CICR                    | Central Interrupt Control Register     | 87                     | 52           |  |

|                   |               | R231                  | FLAGR                   | Flag Register                          | 00                     | 24           |  |

|                   |               | R232                  | RP0                     | Pointer 0 Register                     | xx                     | 26           |  |

|                   |               | R233                  | RP1                     | Pointer 1 Register                     | xx                     | 26           |  |

|                   | 0             | R234 PPR Page Pointer |                         | Page Pointer Register                  | xx                     | 28           |  |

|                   | Core          | R235                  | 235 MODER Mode Register |                                        | E0                     | 28           |  |

|                   |               | R236                  | USPHR                   | User Stack Pointer High Register       | xx                     | 30           |  |

| N/A               |               | R237                  | USPLR                   | User Stack Pointer Low Register        | xx                     | 30           |  |

|                   |               | R238                  | SSPHR                   | System Stack Pointer High Reg.         | xx                     | 30           |  |

|                   |               | R239                  | SSPLR                   | System Stack Pointer Low Reg.          | xx                     | 30           |  |

|                   |               | R224                  | P0DR                    | Port 0 Data Register                   | FF                     |              |  |

|                   | I/O           | R225                  | P1DR                    | Port 1 Data Register                   | FF                     |              |  |

|                   | Port          | R226                  | P2DR                    | Port 2 Data Register                   | FF                     | 79           |  |

|                   | 5:4,2:0       | R228                  | P4DR                    | Port 4 Data Register                   | FF                     |              |  |

|                   |               | R229                  | P5DR                    | Port 5 Data Register                   | FF                     |              |  |

|                   |               | R242                  | EITR                    | External Interrupt Trigger Register    | 00                     | 52           |  |

|                   |               | R243                  | EIPR                    | External Interrupt Pending Reg.        | 00                     | 53           |  |

|                   | INIT          | R244                  | EIMR                    | External Interrupt Mask-bit Reg.       | 00                     | 53           |  |

|                   | INT           | R245                  | EIPLR                   | External Interrupt Priority Level Reg. | FF                     | 53           |  |

|                   |               | R246                  | EIVR                    | External Interrupt Vector Register     | х6                     | 54           |  |

| 0                 |               | R247                  | NICR                    | Nested Interrupt Control               | 00                     | 54           |  |

|                   |               | R248                  | WDTHR                   | Watchdog Timer High Register           | FF                     | 90           |  |

|                   |               | R249                  | WDTLR                   | Watchdog Timer Low Register            | FF                     | 90           |  |

|                   | WDT           | R250                  | WDTPR                   | Watchdog Timer Prescaler Reg.          | FF                     | 90           |  |

|                   |               | R251                  | WDTCR                   | Watchdog Timer Control Register        | 12                     | 90           |  |

|                   |               | R252                  | WCR                     | Wait Control Register                  | 7F                     | 91           |  |

|                   | I/O           | R252                  | P3C0                    | Port 3 Configuration Register 0        | 00                     |              |  |

| 2                 | Port          | R253                  | P3C1                    | Port 3 Configuration Register 1        | 00                     |              |  |

|                   | 3             | R254                  | P3C2                    | Port 3 Configuration Register 2        | 00                     | 70           |  |

|                   | I/O           | R244                  | P5C0                    | Port 5 Configuration Register 0        | FF                     | 79           |  |

| 3                 | Port          | R245                  | P5C1                    | Port 5 Configuration Register 1        | 00                     |              |  |

|                   | 5             | R246                  | P5C2                    | Port 5 Configuration Register 2        | 00                     |              |  |

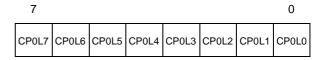

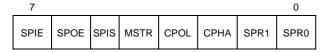

|                   |               | R240                  | SPDR                    | SPI Data Register                      | 00                     | 145          |  |

| 7                 | SPI           | R241                  | SPCR                    | SPI Control Register                   | 00                     | 145          |  |

| ,                 | 351           | R242                  | SPSR                    | SPI Status Register                    | 00                     | 146          |  |

|                   |               | R243                  | SPPR                    | SPI Prescaler Register                 | 00                     | 146          |  |

|                   |               | R240                  | STH                     | Counter High Byte Register             | FF                     | 95           |  |

| 11                | STIM          | R241                  | STL                     | Counter Low Byte Register              | FF                     | 95           |  |

| 11                | STIIVI        | R242                  | STP                     | Standard Timer Prescaler Register      | FF                     | 95           |  |

|                   |               | R243                  | STC                     | Standard Timer Control Register        | 14                     | 95           |  |

| Page<br>(Decimal) | Block      | Reg.<br>No. | Register<br>Name          | Description                     | Reset<br>Value<br>Hex. | Doc.<br>Page |

|-------------------|------------|-------------|---------------------------|---------------------------------|------------------------|--------------|

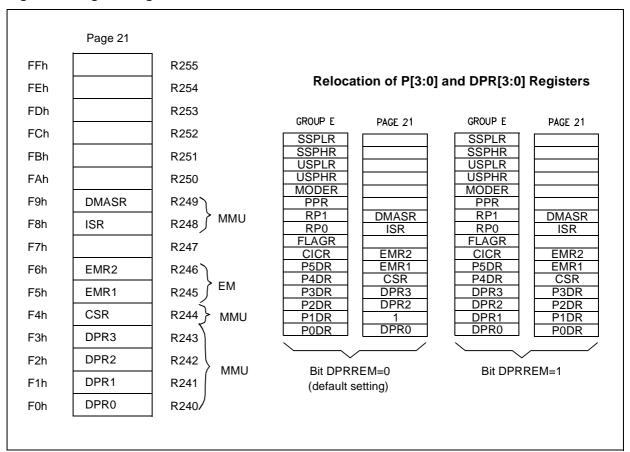

|                   |            | R240        | DPR0                      | Data Page Register 0            | xx                     | 35           |

|                   |            | R241        | DPR1                      | Data Page Register 1            | XX                     | 35           |

|                   |            | R242        | DPR2 Data Page Register 2 |                                 | xx                     | 35           |

|                   | MMU        | R243        | DPR3                      | Data Page Register 3            | XX                     | 35           |

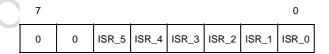

| 21                |            | R244        | CSR                       | Code Segment Register           | 00                     | 36           |

|                   |            | R248        | ISR                       | Interrupt Segment Register      | xx                     | 36           |

|                   |            | R249        | DMASR                     | DMA Segment Register            | xx                     | 36           |

|                   | <b>514</b> | R245        | EMR1                      | EM Register 1                   | 80                     | 62           |

|                   | EM         | R246        | EMR2                      | EM Register 2                   | 0F                     | 62           |

|                   |            | R240        | IC1HR                     | Input Capture 1 High Register   | XX                     | 108          |

|                   |            | R241        | IC1LR                     | Input Capture 1 Low Register    | xx                     | 108          |

|                   |            | R242        | IC2HR                     | Input Capture 2 High Register   | xx                     | 108          |

|                   |            | R243        | IC2LR                     | Input Capture 2 Low Register    | XX                     | 108          |

|                   |            | R244        | CHR                       | Counter High Register           | FF                     | 109          |

|                   |            | R245        | CLR                       | Counter Low Register            | FC                     | 109          |

|                   |            | R246        | ACHR                      | Alternate Counter High Register | FF                     | 109          |

| 28                | EFT        | R247        | ACLR                      | Alternate Counter Low Register  | FC                     | 109          |

| 20                |            | R248        | OC1HR                     | Output Compare 1 High Register  | 80                     | 110          |

|                   |            | R249        | OC1LR                     | Output Compare 1 Low Register   | 00                     | 110          |

|                   |            | R250        | OC2HR                     | Output Compare 2 High Register  | 80                     | 110          |

|                   |            | R251        | OC2LR                     | Output Compare 2 Low Register   | 00                     | 110          |

|                   |            | R252        | CR1                       | Control Register 1              | 00                     | 111          |

|                   |            | R253        | CR2                       | Control Register 2              | 00                     | 112          |

|                   |            | R254        | SR                        | Status Register                 | 00                     | 113          |

|                   |            | R255        | CR3                       | Control Register 3              | 00                     | 113          |

|                   |            | R248        | PCR0                      | Peripheral Control Register 0   | 80                     | 130          |

|                   |            | R249        | PCR1                      | Peripheral Control Register 1   | 00                     | 130          |

|                   |            | R250        | PCR2                      | Peripheral Control Register 2   | 00                     | 131          |

| 48                | IMC        | R251        | PSR                       | Polarity Selection Register     | 00                     | 131          |

| 40                | IIVIC      | R252        | OPR                       | Output Peripheral Register      | 00                     | 132          |

|                   |            | R253        | IMR                       | Interrupt Mask Register         | 00                     | 132          |

|                   |            | R254        | DTG                       | Dead Time Generator Register    | 00                     | 133          |

|                   |            | R255        | IMCIVR                    | IMC Interrupt Vector Register   | XX                     | 133          |

| Page<br>(Decimal) Block |       | Reg. Register Description            |                                     | Description                           | Reset<br>Value<br>Hex. | Doc.<br>Page |

|-------------------------|-------|--------------------------------------|-------------------------------------|---------------------------------------|------------------------|--------------|

|                         |       | R240                                 | TCPTH                               | Tacho Capture Register High           | xx                     | 125          |

|                         |       | R241                                 | TCPTL                               | Tacho Capture Register Low            | xx                     | 125          |

|                         |       | R242                                 | TCMP                                | Tacho Compare Register                | XX                     | 125          |

|                         |       | R243                                 | ISR                                 | Interrupt Status Register             | 3F                     | 36           |

|                         |       | R244                                 | TPRSH                               | Tacho Prescaler Register High         | 00                     | 127          |

|                         |       | R245                                 | TPRSL                               | Tacho Prescaler Register Low          | 00                     | 127          |

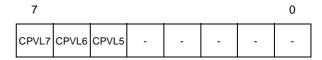

|                         |       | R246                                 | CPRS                                | PWM Counter Prescaler Register        | 00                     | 127          |

| -4                      | 11.40 | R247                                 | REP                                 | Repetition Counter Register           | 00                     | 127          |

| 51                      | IMC   | R248                                 | CPWH                                | Compare Phase W Preload Register High | 00                     | 128          |

|                         |       | R249                                 | CPWL                                | Compare Phase W Preload Register Low  | 00                     | 128          |

|                         |       | R250                                 | CPVH                                | Compare Phase V Preload Register High | 00                     | 128          |

|                         |       | R251                                 | CPVL                                | Compare Phase V Preload Register Low  | 00                     | 128          |

|                         |       | R252                                 | CPUH                                | Compare Phase U Preload Register High | 00                     | 129          |

|                         |       | R253                                 | CPUL                                | Compare Phase U Preload Register Low  | 00                     | 129          |

|                         |       | R254                                 | CP0H                                | Compare 0 Preload Register High       | 00                     | 129          |

|                         |       | R255                                 | CP0L                                | Compare 0 Preload Register Low        | 00                     | 129          |

|                         |       | R240                                 | CLKCTL                              | Clock Control Register                | 00                     | 69           |

| 55                      | RCCU  | R242                                 | CLK_FLAG                            | Clock Flag Register                   | 48, 28                 | 70           |

|                         |       | R246                                 | PLLCONF                             | PLL Configuration Register            | XX                     | 71           |

|                         |       | R249                                 | WUCTRL                              | Wake-Up Control Register              | 00                     | 59           |

|                         |       | R250                                 | 50 WUMRH Wake-Up Mask Register High |                                       | 00                     | 60           |

|                         |       | R251 WUMRL Wake-Up Mask Register Low |                                     | 00                                    | 60                     |              |

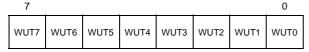

| 57                      | WUIMU | R252                                 | WUTRH                               | Wake-Up Trigger Register High         | 00                     | 61           |

|                         |       | R253                                 | WUTRL                               | Wake-Up Trigger Register Low          | 00                     | 61           |

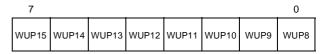

|                         |       | R254                                 | WUPRH                               | Wake-Up Pending Register High         | 00                     | 61           |

|                         |       | R255                                 | WUPRL                               | Wake-Up Pending Register Low          | 00                     | 61           |

|                         |       | R240                                 | D0R                                 | Channel 0 Data Register               | XX                     | 151          |

|                         |       | R241                                 | D1R                                 | Channel 1 Data Register               | XX                     | 151          |

|                         |       | R242                                 | D2R                                 | Channel 2 Data Register               | XX                     | 151          |

|                         |       | R243                                 | D3R                                 | Channel 3 Data Register               | XX                     | 151          |

|                         |       | R244                                 | D4R                                 | Channel 4 Data Register               | XX                     | 151          |

|                         |       | R245                                 | D5R                                 | Channel 5 Data Register               | XX                     | 151          |

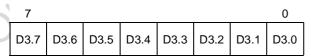

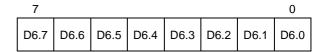

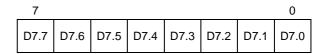

|                         |       | R246                                 | D6R                                 | Channel 6 Data Register               | XX                     | 151          |

| 63                      | ADC   | R247                                 | D7R                                 | Channel 7 Data Register               | XX                     | 151          |

| 03                      | ADC   | R248                                 | LT6R                                | Channel 6 Lower Threshold Reg.        | XX                     | 152          |

|                         |       | R249                                 | LT7R                                | Channel 7 Lower Threshold Reg.        | XX                     | 152          |

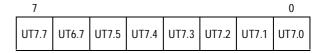

|                         |       | R250                                 | UT6R                                | Channel 6 Upper Threshold Reg.        | XX                     | 152          |

|                         |       | R251                                 | UT7R                                | Channel 7 Upper Threshold Reg.        | xx                     | 152          |

|                         |       | R252                                 | CRR                                 | Compare Result Register               | 0F                     | 153          |

|                         |       | R253                                 | CLR                                 | Control Logic Register                | 00                     | 154          |

|                         |       | R254                                 | ICR                                 | Interrupt Control Register            | 0F                     | 155          |

|                         |       | R255                                 | IVR                                 | Interrupt Vector Register             | x2                     | 155          |

Note: xx denotes a byte with an undefined value, however some of the bits may have defined values. Refer to register description for details.

#### 2 DEVICE ARCHITECTURE

#### 2.1 CORE ARCHITECTURE

The ST9 Core or Central Processing Unit (CPU) features a highly optimised instruction set, capable of handling bit, byte (8-bit) and word (16-bit) data, as well as BCD and Boolean formats; 14 addressing modes are available.

Four independent buses are controlled by the Core: a 16-bit Memory bus, an 8-bit Register data bus, an 8-bit Register address bus and a 6-bit Interrupt/DMA bus which connects the interrupt and DMA controllers in the on-chip peripherals with the Core.

This multiple bus architecture affords a high degree of pipelining and parallel operation, thus making the ST9 family devices highly efficient, both for numerical calculation, data handling and with regard to communication with on-chip peripheral resources.

#### 2.2 MEMORY SPACES

There are two separate memory spaces:

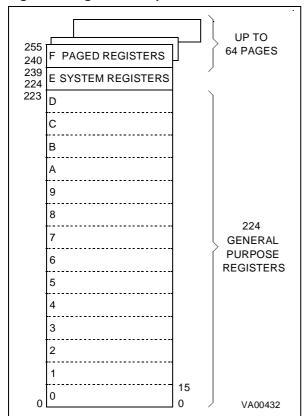

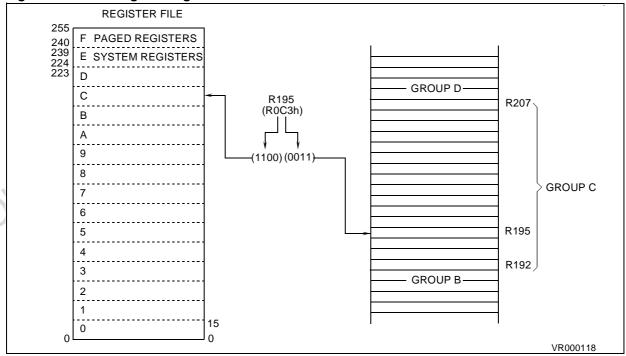

The Register File, which comprises 240 8-bit registers, arranged as 15 groups (Group 0 to E), each containing sixteen 8-bit registers plus up to 64 pages of 16 registers mapped in Group F, which hold data and control bits for the on-chip peripherals and I/Os.

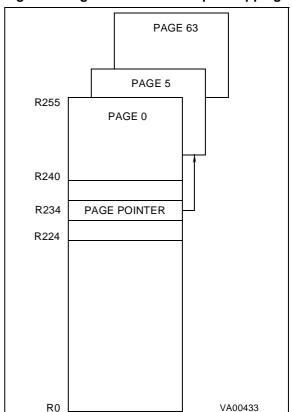

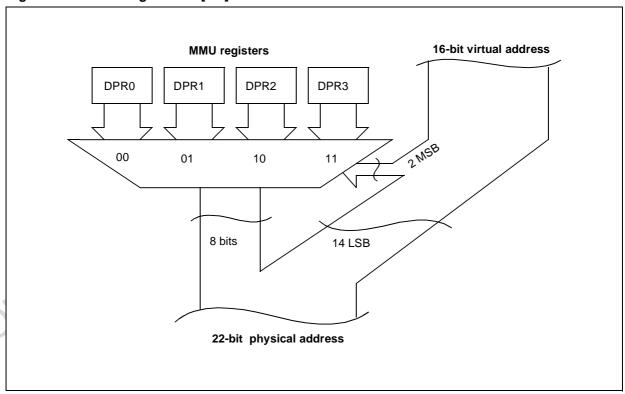

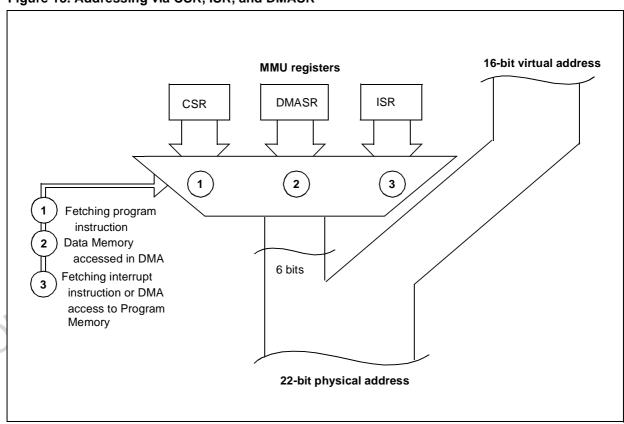

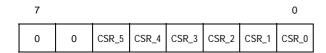

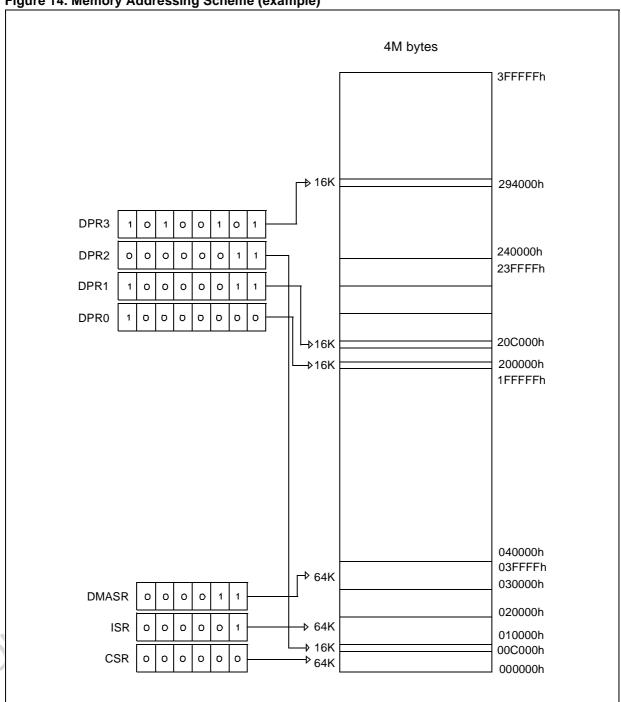

A single linear memory space accommodating both program and data. All of the physically separate memory areas, including the internal ROM, internal RAM and external memory are mapped in this common address space. The total addressable memory space of 4 Mbytes (limited by the size of on-chip memory and the number of external address pins) is arranged as 64 segments of 64 Kbytes. Each segment is further subdivided into four pages of 16 Kbytes, as illustrated in Figure 3. A Memory Management Unit uses a set of pointer registers to address a 22-bit memory field using 16-bit address-based instructions.

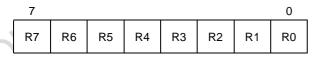

#### 2.2.1 Register File

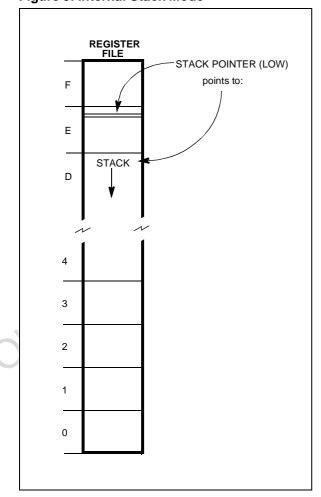

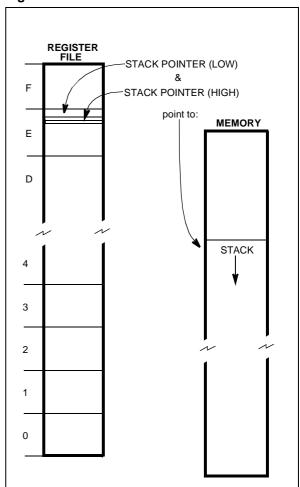

The Register File consists of (see Figure 4):

- 224 general purpose registers (Group 0 to D, registers R0 to R223)

- 6 system registers in the System Group (Group E, registers R224 to R239)

- Up to 64 pages, depending on device configuration, each containing up to 16 registers, mapped to Group F (R240 to R255), see Figure 5.

Data Code **Address** 16K Pages 64K Segments 3FFFFFh 254 63 3F0000h 3EFFFFh 250 62 249 3E0000h 248 247 up to 4 Mbytes 135 21FFFFh 134 Reserved 33 210000h 20FFFFh 11 02FFFFh 10 2 020000h 01FFFFh 010000h 00FFFFh 0 000000h

Figure 3. Single Program and Data Memory Address Space

# **MEMORY SPACES** (Cont'd)

Figure 4. Register Groups

Figure 5. Page Pointer for Group F mapping

Figure 6. Addressing the Register File

#### **MEMORY SPACES** (Cont'd)

#### 2.2.2 Register Addressing

Register File registers, including Group F paged registers (but excluding Group D), may be addressed explicitly by means of a decimal, hexadecimal or binary address; thus R231, RE7h and R11100111b represent the same register (see Figure 6). Group D registers can only be addressed in Working Register mode.

Note that an upper case "R" is used to denote this direct addressing mode.

#### **Working Registers**

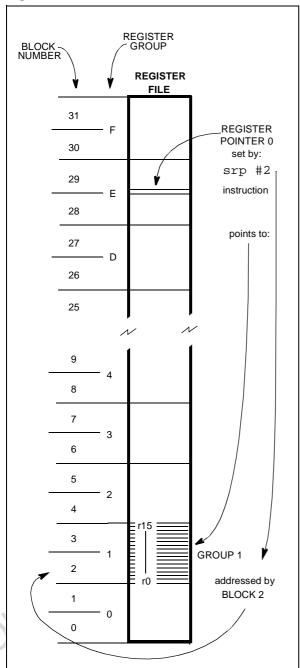

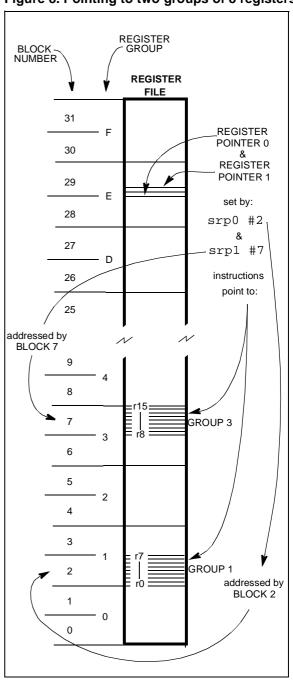

Certain types of instruction require that registers be specified in the form "rx", where x is in the range 0 to 15: these are known as Working Registers.

Note that a lower case "r" is used to denote this indirect addressing mode.

Two addressing schemes are available: a single group of 16 working registers, or two separately mapped groups, each consisting of 8 working registers. These groups may be mapped starting at any 8 or 16 byte boundary in the register file by means of dedicated pointer registers. This technique is described in more detail in Section 2.3.3 Register Pointing Techniques, and illustrated in Figure 7 and in Figure 8.

# **System Registers**

The 16 registers in Group E (R224 to R239) are System registers and may be addressed using any of the register addressing modes. These registers are described in greater detail in Section 2.3 SYSTEM REGISTERS.

#### **Paged Registers**

Up to 64 pages, each containing 16 registers, may be mapped to Group F. These are addressed using any register addressing mode, in conjunction with the Page Pointer register, R234, which is one of the System registers. This register selects the page to be mapped to Group F and, once set, does not need to be changed if two or more registers on the same page are to be addressed in succession.

Therefore if the Page Pointer, R234, is set to 5, the instructions:

will load the contents of working register r4 into the third register of page 5 (R242).

These paged registers hold data and control information relating to the on-chip peripherals, each peripheral always being associated with the same pages and registers to ensure code compatibility between ST9 devices. The number of these registers therefore depends on the peripherals which are present in the specific ST9 family device. In other words, pages only exist if the relevant peripheral is present.

**Table 9. Register File Organization**

| Hex.<br>Address | Decimal<br>Address | Function            | Register<br>File Group |

|-----------------|--------------------|---------------------|------------------------|

| F0-FF           | 240-255            | Paged<br>Registers  | Group F                |

| E0-EF           | 224-239            | System<br>Registers | Group E                |

| D0-DF           | 208-223            |                     | Group D                |

| C0-CF           | 192-207            |                     | Group C                |

| B0-BF           | 176-191            |                     | Group B                |

| A0-AF           | 160-175            |                     | Group A                |

| 90-9F           | 144-159            |                     | Group 9                |

| 80-8F           | 128-143            | _                   | Group 8                |

| 70-7F           | 112-127            | General<br>Purpose  | Group 7                |

| 60-6F           | 96-111             | Registers           | Group 6                |

| 50-5F           | 80-95              | 3                   | Group 5                |

| 40-4F           | 64-79              |                     | Group 4                |

| 30-3F           | 48-63              |                     | Group 3                |

| 20-2F           | 32-47              |                     | Group 2                |

| 10-1F           | 16-31              |                     | Group 1                |

| 00-0F           | 00-15              |                     | Group 0                |

#### 2.3 SYSTEM REGISTERS

The System registers are listed in Table 10 System Registers (Group E). They are used to perform all the important system settings. Their purpose is described in the following pages. Refer to the chapter dealing with I/O for a description of the PORT[5:0] Data registers.

Table 10. System Registers (Group E)

| R239 (EFh) | SSPLR                 |

|------------|-----------------------|

| R238 (EEh) | SSPHR                 |

| R237 (EDh) | USPLR                 |

| R236 (ECh) | USPHR                 |

| R235 (EBh) | MODE REGISTER         |

| R234 (EAh) | PAGE POINTER REGISTER |

| R233 (E9h) | REGISTER POINTER 1    |

| R232 (E8h) | REGISTER POINTER 0    |

| R231 (E7h) | FLAG REGISTER         |

| R230 (E6h) | CENTRAL INT. CNTL REG |

| R229 (E5h) | PORT5 DATA REG.       |

| R228 (E4h) | PORT4 DATA REG.       |

| R227 (E3h) | PORT3 DATA REG.       |

| R226 (E2h) | PORT2 DATA REG.       |

| R225 (E1h) | PORT1 DATA REG.       |

| R224 (E0h) | PORT0 DATA REG.       |

# 2.3.1 Central Interrupt Control Register

Please refer to the "INTERRUPT" chapter for a detailed description of the ST9 interrupt philosophy.

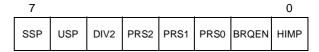

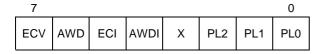

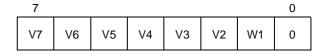

# CENTRAL INTERRUPT CONTROL REGISTER (CICR)

R230 - Read/Write

Register Group: E (System) Reset Value: 1000 0111 (87h)

| 7    |      |     |     |     |      |      | 0    |

|------|------|-----|-----|-----|------|------|------|

| GCEN | TLIP | TLI | IEN | IAM | CPL2 | CPL1 | CPL0 |

Bit 7 = GCEN: Global Counter Enable.

This bit is the Global Counter Enable of the Multifunction Timers. The GCEN bit is ANDed with the CE bit in the TCR Register (only in devices featuring the MFT Multifunction Timer) in order to enable the Timers when both bits are set. This bit is set after the Reset cycle. **Note:** If an MFT is not included in the ST9 device, then this bit has no effect.

# Bit 6 = **TLIP**: Top Level Interrupt Pending.

This bit is set by hardware when a Top Level Interrupt Request is recognized. This bit can also be set by software to simulate a Top Level Interrupt Request.

0: No Top Level Interrupt pending

1: Top Level Interrupt pending

#### Bit 5 = **TLI**: *Top Level Interrupt bit*.

- Top Level Interrupt is acknowledged depending on the TLNM bit in the NICR Register.

- 1: Top Level Interrupt is acknowledged depending on the IEN and TLNM bits in the NICR Register (described in the Interrupt chapter).

#### Bit 4 = **IEN**: Interrupt Enable.

This bit is cleared by interrupt acknowledgement, and set by interrupt return (iret). IEN is modified implicitly by iret, ei and di instructions or by an interrupt acknowledge cycle. It can also be explicitly written by the user, but only when no interrupt is pending. Therefore, the user should execute a di instruction (or guarantee by other means that no interrupt request can arrive) before any write operation to the CICR register.

0: Disable all interrupts except Top Level Interrupt.

1: Enable Interrupts

# Bit 3 = IAM: Interrupt Arbitration Mode.

This bit is set and cleared by software to select the arbitration mode.

0: Concurrent Mode

1: Nested Mode.

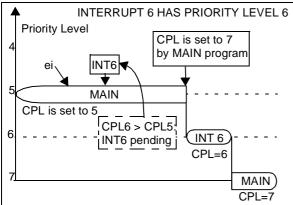

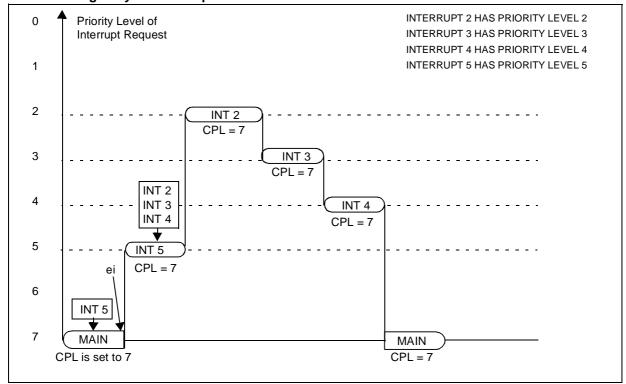

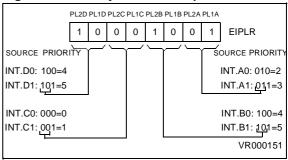

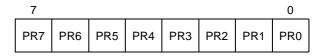

#### Bits 2:0 = CPL[2:0]: Current Priority Level.

These three bits record the priority level of the routine currently running (i.e. the Current Priority Level, CPL). The highest priority level is represented by 000, and the lowest by 111. The CPL bits can be set by hardware or software and provide the reference according to which subsequent interrupts are either left pending or are allowed to interrupt the current interrupt service routine. When the current interrupt is replaced by one of a higher priority, the current priority value is automatically stored until required in the NICR register.

# 2.3.2 Flag Register

The Flag Register contains 8 flags which indicate the CPU status. During an interrupt, the flag register is automatically stored in the system stack area and recalled at the end of the interrupt service routine, thus returning the CPU to its original status.

This occurs for all interrupts and, when operating in nested mode, up to seven versions of the flag register may be stored.

# FLAG REGISTER (FLAGR)

R231- Read/Write

Register Group: E (System) Reset value: 0000 0000 (00h)

| 7 |   |   |   |    |   |   | 0  |

|---|---|---|---|----|---|---|----|

| С | Z | S | ٧ | DA | н | - | DP |

#### Bit $7 = \mathbf{C}$ : Carry Flag.

The carry flag is affected by:

Addition (add, addw, adc, adcw),

Subtraction (sub, subw, sbc, sbcw),

Compare (cp, cpw),

Shift Right Arithmetic (sra, sraw),

Shift Left Arithmetic (sla, slaw),

Swap Nibbles (swap),

Rotate (rrc, rrcw, rlc, rlcw, ror, rol),

Decimal Adjust (da),

Multiply and Divide (mul, div, divws).

When set, it generally indicates a carry out of the most significant bit position of the register being used as an accumulator (bit 7 for byte operations and bit 15 for word operations).

The carry flag can be set by the Set Carry Flag (scf) instruction, cleared by the Reset Carry Flag (rcf) instruction, and complemented by the Complement Carry Flag (ccf) instruction.

# Bit 6 = **Z**: *Zero Flag*. The Zero flag is affected by:

Addition (add, addw, adc, adcw),

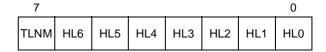

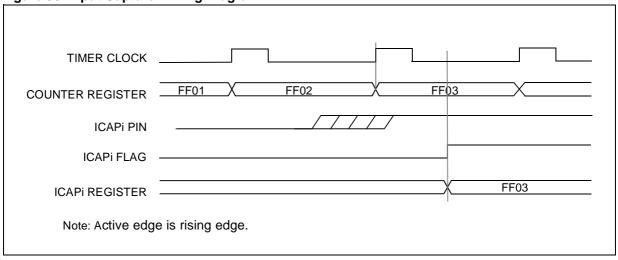

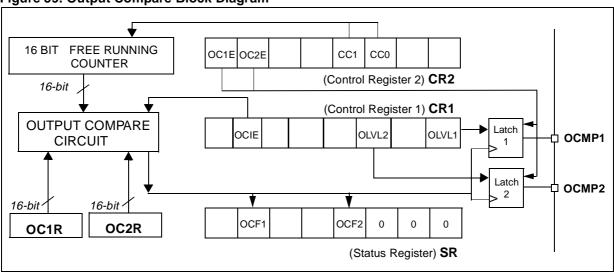

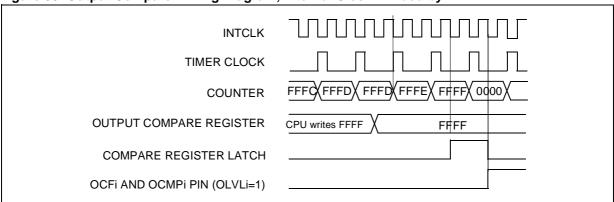

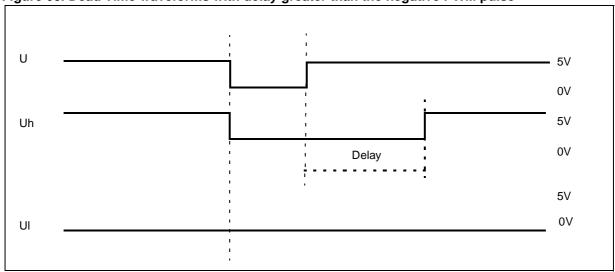

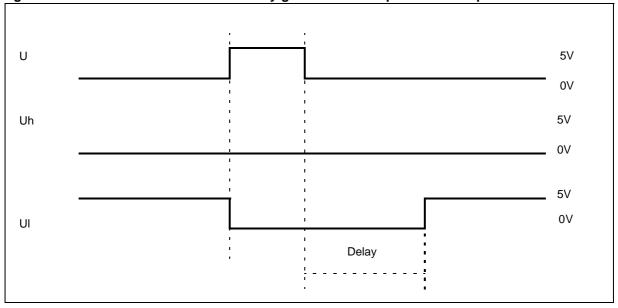

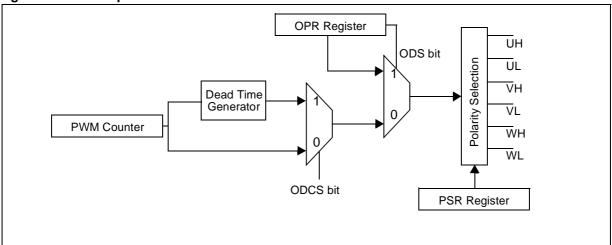

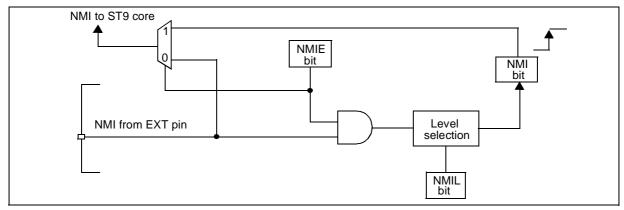

Subtraction (sub, subw, sbc, sbcw),