# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## General Description

The MAX1645 are high-efficiency battery chargers capable of charging batteries of any chemistry type. It uses the Intel System Management Bus (SMBus™) to control voltage and current charge outputs.

When charging lithium-ion (Li+) batteries, the MAX1645 automatically transition from regulating current to regulating voltage. The MAX1645 can also limit line input current so as not to exceed a predetermined current drawn from the DC source. A 175s charge safety timer prevents "runaway charging" should the MAX1645 stop receiving charging voltage/ current commands.

The MAX1645 employs a next-generation synchronous buck control circuitry that lowers the minimum input-to-output voltage drop by allowing the duty cycle to exceed 99%. The MAX1645 can easily charge one to four series Li+ cells.

## Applications

Notebook Computers

Point-of-Sale Terminals

Personal Digital Assistants

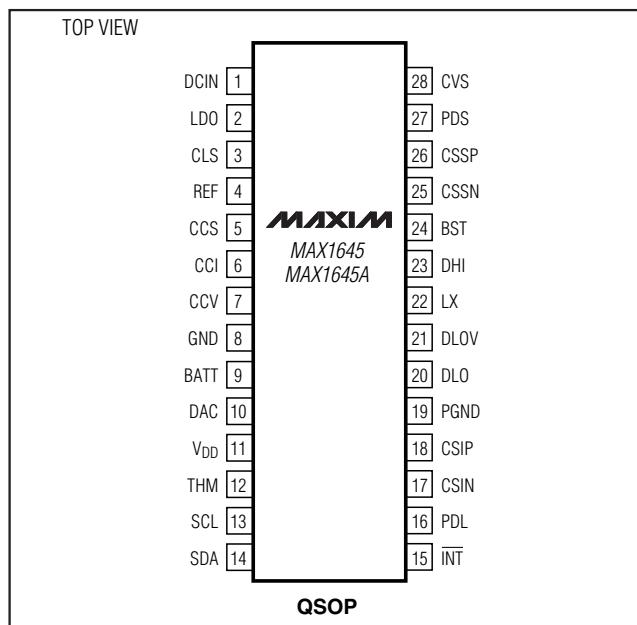

## Pin Configuration

## Features

- ◆ **Input Current Limiting**

- ◆ **175s Charge Safety Timeout**

- ◆ **128mA Wake-Up Charge**

- ◆ **Charges Any Chemistry Battery: Li+, NiCd, NiMH, Lead Acid, etc.**

- ◆ **Intel SMBus 2-Wire Serial Interface**

- ◆ **Compliant with Level 2 Smart Battery Charger Spec Rev. 1.0**

- ◆ **+8V to +28V Input Voltage Range**

- ◆ **Up to 18.4V Battery Voltage**

- ◆ **11-Bit Battery Voltage Setting**

- ◆ **±0.8% Output Voltage Accuracy with Internal Reference**

- ◆ **3A max Battery Charge Current**

- ◆ **6-Bit Charge Current Setting**

- ◆ **99.99% max Duty Cycle for Low-Dropout Operation**

- ◆ **Load/Source Switchover Drivers**

- ◆ **>97% Efficiency**

MAX1645/MAX1645A

## Ordering Information

| PART               | TEMP. RANGE    | PIN-PACKAGE |

|--------------------|----------------|-------------|

| <b>MAX1645EEI</b>  | -40°C to +85°C | 28 QSOP     |

| <b>MAX1645AEEI</b> | -40°C to +85°C | 28 QSOP     |

*Typical Operating Circuit appears at end of data sheet.*

SMBus is a trademark of Intel Corp.

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## ABSOLUTE MAXIMUM RATINGS

|                                     |                                              |

|-------------------------------------|----------------------------------------------|

| DCIN, CVS, CSSP, CSSN, LX to GND    | -0.3V to +30V                                |

| CSSP to CSSN, CSIP to CSIN          | -0.3V to +0.3V                               |

| PDS, PDL to GND                     | -0.3V to ( $V_{CSSP} + 0.3V$ )               |

| BST to LX                           | -0.3V to +6V                                 |

| DHI to LX                           | -0.3V to ( $V_{BST} + 0.3V$ )                |

| CSIP, CSIN, BATT to GND             | -0.3V to +22V                                |

| LDO to GND                          | -0.3V to (lower of 6V or $V_{DCIN} + 0.3V$ ) |

| DLO to GND                          | -0.3V to ( $V_{DLOV} + 0.3V$ )               |

| REF, DAC, CCV, CCI, CCS, CLS to GND | -0.3V to ( $V_{LDO} + 0.3V$ )                |

|                                                              |                                   |

|--------------------------------------------------------------|-----------------------------------|

| $V_{DD}$ , SCL, SDA, INT, DLOV to GND                        | -0.3V to +6V                      |

| THM to GND                                                   | -0.3V to ( $V_{DD} + 0.3V$ )      |

| PGND to GND                                                  | -0.3V to +0.3V                    |

| LDO Continuous Current                                       | 50mA                              |

| Continuous Power Dissipation ( $T_A = +70^\circ C$ )         |                                   |

| 28-Pin QSOP (derate 10.8mW/ $^\circ C$ above $+70^\circ C$ ) | 860mW                             |

| Operating Temperature Range                                  | -40 $^\circ C$ to +85 $^\circ C$  |

| Storage Temperature                                          | -60 $^\circ C$ to +150 $^\circ C$ |

| Lead Temperature (soldering, 10s)                            | +300 $^\circ C$                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(Circuit of Figure 1,  $V_{DD} = +3.3V$ ,  $V_{BATT} = +16.8V$ ,  $V_{DCIN} = +18V$ ,  $T_A = 0^\circ C$  to +85 $^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .)

| PARAMETER                                       | SYMBOL        | CONDITIONS                                                           | MIN                                 | TYP         | MAX         | UNITS   |

|-------------------------------------------------|---------------|----------------------------------------------------------------------|-------------------------------------|-------------|-------------|---------|

| <b>GENERAL SPECIFICATIONS</b>                   |               |                                                                      |                                     |             |             |         |

| DCIN Typical Operating Range                    | $V_{DCIN}$    |                                                                      | 8                                   | 28          |             | V       |

| DCIN Supply Current                             | $I_{DCIN}$    | 8V < $V_{DCIN}$ < 28V                                                |                                     | 1.7         | 6           | mA      |

| DCIN Supply Current Charging Inhibited          |               | 8V < $V_{DCIN}$ < 28V                                                |                                     | 0.7         | 2           | mA      |

| DCIN Undervoltage Threshold                     |               | When AC_PRESENT switches                                             | DCIN rising<br>DCIN falling         | 7.5<br>7    | 7.85<br>7.4 | V       |

| LDO Output Voltage                              | $V_{LDO}$     | 8V < $V_{DCIN}$ < 28V, 0 < $I_{LDO}$ < 15mA                          |                                     | 5.15        | 5.4         | 5.65    |

| $V_{DD}$ Input Voltage Range (Note 1)           |               | 8V < $V_{DCIN}$ < 28V                                                |                                     | 2.8         | 5.65        | V       |

| $V_{DD}$ Undervoltage Threshold                 |               | When the SMB responds to commands                                    | $V_{DD}$ rising<br>$V_{DD}$ falling | 2.55<br>2.1 | 2.8<br>2.5  | V       |

| $V_{DD}$ Quiescent Current                      | $I_{DD}$      | 0 < $V_{DCIN}$ < 6V, $V_{DD} = 5V$ , $V_{SCL} = 5V$ , $V_{SDA} = 5V$ |                                     | 80          | 150         | $\mu A$ |

| REF Output Voltage                              | $V_{REF}$     | 0 < $I_{REF}$ < 200 $\mu A$                                          |                                     | 4.066       | 4.096       | 4.126   |

| BATT Undervoltage Threshold (Note 2)            |               | When $I_{CHARGE}$ drops to 128mA                                     |                                     | 2.4         | 2.8         | V       |

| PDS Charging Source Switch Turn-Off Threshold   | $V_{PDS-OFF}$ | $V_{CVS}$ referred to $V_{BATT}$ , $V_{CVS}$ falling                 |                                     | 50          | 100         | 150     |

| PDS Charging Source Switch Threshold Hysteresis | $V_{PDS-HYS}$ | $V_{CVS}$ referred to $V_{BATT}$                                     |                                     | 100         | 200         | 300     |

| PDS Output Low Voltage, PDS Below CSSP          |               | $I_{PDS} = 0$                                                        |                                     | 8           | 10          | 12      |

| PDS Turn-On Current                             |               | $PDS = CSSP$                                                         |                                     | 100         | 150         | 300     |

| PDS Turn-Off Current                            |               | $V_{PDS} = V_{CSSP} - 2V$ , $V_{DCIN} = 16V$                         |                                     | 10          | 50          | mA      |

| PDL Load Switch Turn-Off Threshold              | $V_{PDL-OFF}$ | $V_{CVS}$ referred to $V_{BATT}$ , $V_{CVS}$ rising                  |                                     | -150        | -100        | -50     |

|                                                 |               |                                                                      |                                     |             |             | mV      |

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{DD} = +3.3V$ ,  $V_{BATT} = +16.8V$ ,  $V_{DCIN} = +18V$ ,  $T_A = 0^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                                  | SYMBOL        | CONDITIONS                                                                                  | MIN                                            | TYP    | MAX    | UNITS                   |    |

|--------------------------------------------|---------------|---------------------------------------------------------------------------------------------|------------------------------------------------|--------|--------|-------------------------|----|

| PDL Load Switch Threshold Hysteresis       | $V_{PDL-HYS}$ | $V_{CVS}$ referred to $V_{BATT}$                                                            | 100                                            | 200    | 300    | mV                      |    |

| PDL Turn-Off Current                       |               | $V_{CSSN} - V_{PDL} = 1V$                                                                   | 6                                              | 12     |        | mA                      |    |

| PDL Turn-On Resistance                     |               | PDL to GND                                                                                  | 50                                             | 100    | 150    | k $\Omega$              |    |

| CVS Input Bias Current                     |               | $V_{CVS} = 28V$                                                                             |                                                | 6      | 20     | $\mu\text{A}$           |    |

| BATT Full-Charge Voltage                   | $V_0$         | ChargingVoltage() = 0x41A0                                                                  | 16.666                                         | 16.8   | 16.934 | V                       |    |

|                                            |               | ChargingVoltage() = 0x3130                                                                  | 12.492                                         | 12.592 | 12.692 |                         |    |

|                                            |               | ChargingVoltage() = 0x20D0                                                                  | 8.333                                          | 8.4    | 8.467  |                         |    |

|                                            |               | ChargingVoltage() = 0x1060                                                                  | 4.150                                          | 4.192  | 4.234  |                         |    |

| BATT Charge Current (Note 3)               | $I_0$         | $R_{CS} = 50\text{m}\Omega$                                                                 | ChargingCurrent() = 0x0BC0                     | 2.798  | 3.008  | 3.218                   | A  |

|                                            |               |                                                                                             | ChargingCurrent() = 0x0080                     | 61.6   | 128    | 194.4                   | mA |

| DCIN Source Current Limit (Note 3)         |               | $R_{CSS} = 40\text{m}\Omega$                                                                | $V_{CLS} = 4.096V$                             | 4.714  | 5.12   | 5.526                   | A  |

|                                            |               |                                                                                             | $V_{CLS} = 2.048V$                             | 2.282  | 2.56   | 2.838                   |    |

| BATT Undervoltage Charge Current           |               | MAX1645                                                                                     | $V_{BATT} = 1V$ , $R_{CSI} = 50\text{m}\Omega$ | 20     | 128    | 200                     | mA |

|                                            |               | MAX1645A                                                                                    | $V_{BATT} = 1V$ , $R_{CSI} = 50\text{m}\Omega$ | 61.6   | 128    | 194.4                   |    |

| BATT/CSIP/CSIN Input Voltage Range         |               |                                                                                             |                                                | 0      | 20     | V                       |    |

| Total BATT Input Bias Current              |               | Total of $I_{BATT}$ , $I_{CSIP}$ , and $I_{CSIN}$ ; $V_{BATT} = 0$ to 20V                   | -700                                           | 700    |        | $\mu\text{A}$           |    |

| Total BATT Quiescent Current               |               | Total of $I_{BATT}$ , $I_{CSIP}$ , and $I_{CSIN}$ ; $V_{BATT} = 0$ to 20V, charge inhibited | -100                                           | 100    |        | $\mu\text{A}$           |    |

| Total BATT Standby Current                 |               | Total of $I_{BATT}$ , $I_{CSIP}$ , and $I_{CSIN}$ ; $V_{BATT} = 0$ to 20V, $V_{DCIN} = 0$   | -5                                             | 5      |        | $\mu\text{A}$           |    |

| CSSP Input Bias Current                    |               | $V_{CSSP} = V_{CSSN} = V_{DCIN} = 0$ to 28V                                                 | -100                                           | 540    | 1000   | $\mu\text{A}$           |    |

| CSSN Input Bias Current                    |               | $V_{CSSP} = V_{CSSN} = V_{DCIN} = 0$ to 28V                                                 | -100                                           | 35     | 100    | mA                      |    |

| CSSP/CSSN Quiescent Current                |               | $V_{CSSP} = V_{CSSN} = 28V$ , $V_{DCIN} = 0$                                                | -1                                             | 1      |        | $\mu\text{A}$           |    |

| Battery Voltage-Error Amp DC Gain          |               | From BATT to CCV                                                                            | 200                                            | 500    |        | V/V                     |    |

| CLS Input Bias Current                     |               | $V_{CLS} = V_{REF}/2$ to $V_{REF}$                                                          | -1                                             | 0.05   | 1      | $\mu\text{A}$           |    |

| Battery Voltage-Error Amp Transconductance |               | From BATT to CCV, ChargingVoltage() = 0x41A0, $V_{BATT} = 16.8V$                            | 0.111                                          | 0.222  | 0.444  | $\mu\text{A}/\text{mV}$ |    |

| Battery Current-Error Amp Transconductance |               | From CSIP/SCIN to CCI, ChargingCurrent() = 0x0BC0, $V_{CSIP} - V_{CSIN} = 150.4\text{mV}$   | 0.5                                            | 1      | 2      | $\mu\text{A}/\text{mV}$ |    |

| Input Current-Error Amp Transconductance   |               | From CSSP/CSSN to CCS, $V_{CLS} = 2.048V$ , $V_{CSSP} - V_{CSSN} = 102.4\text{mV}$          | 0.5                                            | 1      | 2      | $\mu\text{A}/\text{mV}$ |    |

| CCV/CCI/CCS Clamp Voltage (Note 4)         |               | $V_{CCV} = V_{CCI} = V_{CCS} = 0.25V$ to 2V                                                 | 150                                            | 300    | 600    | mV                      |    |

**MAX1645/MAX1645A**

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{DD} = +3.3V$ ,  $V_{BATT} = +16.8V$ ,  $V_{DCIN} = +18V$ ,  $T_A = 0^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                                                                               | SYMBOL       | CONDITIONS                                                                | MIN  | TYP   | MAX  | UNITS         |

|-----------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------|------|-------|------|---------------|

| <b>DC-TO-DC CONVERTER SPECIFICATIONS</b>                                                |              |                                                                           |      |       |      |               |

| Minimum Off-Time                                                                        | $t_{OFF}$    |                                                                           | 1    | 1.25  | 1.5  | $\mu\text{s}$ |

| Maximum On-Time                                                                         | $t_{ON}$     |                                                                           | 5    | 10    | 15   | ms            |

| Maximum Duty Cycle                                                                      |              |                                                                           | 99   | 99.99 |      | %             |

| LX Input Bias Current                                                                   |              | $V_{DCIN} = 28V$ , $V_{BATT} = V_{LX} = 20V$                              | 200  | 500   |      | $\mu\text{A}$ |

| LX Input Quiescent Current                                                              |              | $V_{DCIN} = 0$ , $V_{BATT} = V_{LX} = 20V$                                |      | 1     |      | $\mu\text{A}$ |

| BST Supply Current                                                                      |              | DHI high                                                                  | 6    | 15    |      | $\mu\text{A}$ |

| DLOV Supply Current                                                                     |              | $V_{DLOV} = V_{LDO}$ , DLO low                                            | 5    | 10    |      | $\mu\text{A}$ |

| Inductor Peak Current Limit                                                             |              | $R_{CSI} = 50\text{m}\Omega$                                              | 5.0  | 6.0   | 7.0  | A             |

| DHI Output Resistance                                                                   |              | DHI high or low, $V_{BST} - V_{LX} = 4.5V$                                | 6    | 14    |      | $\Omega$      |

| DLO Output Resistance                                                                   |              | DLO high or low, $V_{DLOV} = 4.5V$                                        | 6    | 14    |      | $\Omega$      |

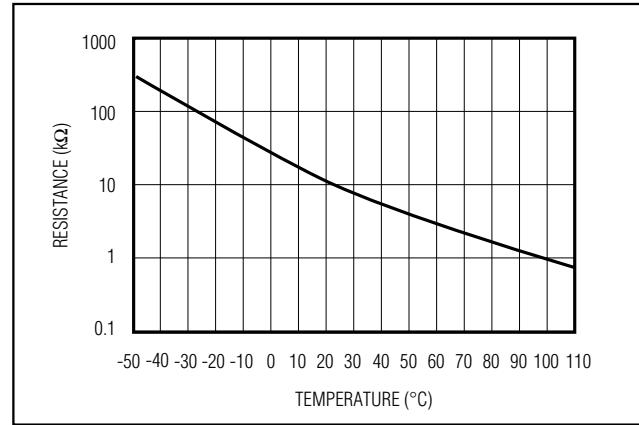

| <b>THERMISTOR COMPARATOR SPECIFICATIONS</b>                                             |              |                                                                           |      |       |      |               |

| THM Input Bias Current                                                                  |              | $V_{THM} = 4\%$ of $V_{DD}$ to 96% of $V_{DD}$ , $V_{DD} = 2.8V$ to 5.65V | -1   | 1     |      | $\mu\text{A}$ |

| Thermistor Overrange Threshold                                                          |              | $V_{DD} = 2.8V$ to 5.65V, $V_{THM}$ falling                               | 89.5 | 91    | 92.5 | % of $V_{DD}$ |

| Thermistor Cold Threshold                                                               |              | $V_{DD} = 2.8V$ to 5.65V, $V_{THM}$ falling                               | 74   | 75.5  | 77   | % of $V_{DD}$ |

| Thermistor Hot Threshold                                                                |              | $V_{DD} = 2.8V$ to 5.65V, $V_{THM}$ falling                               | 22   | 23.5  | 25   | % of $V_{DD}$ |

| Thermistor Underrange Threshold                                                         |              | $V_{DD} = 2.8V$ to 5.65V, $V_{THM}$ falling                               | 6    | 7.5   | 9    | % of $V_{DD}$ |

| Thermistor Comparator Threshold Hysteresis                                              |              | All 4 comparators, $V_{DD} = 2.8V$ to 5.65V                               |      | 1     |      | % of $V_{DD}$ |

| <b>SMB INTERFACE LEVEL SPECIFICATIONS</b> ( $V_{DD} = 2.8V$ to 5.65V)                   |              |                                                                           |      |       |      |               |

| SDA/SCL Input Low Voltage                                                               |              |                                                                           |      | 0.6   |      | V             |

| SDA/SCL Input High Voltage                                                              |              |                                                                           | 1.4  |       |      | V             |

| SDA/SCL Input Hysteresis                                                                |              |                                                                           | 220  |       |      | mV            |

| SDA/SCL Input Bias Current                                                              |              |                                                                           | -1   | 1     |      | $\mu\text{A}$ |

| SDA Output Low Sink Current                                                             |              | $V_{SDA} = 0.4V$                                                          | 6    |       |      | mA            |

| INT Output High Leakage                                                                 |              | $V_{INT} = 5.65V$                                                         |      | 1     |      | $\mu\text{A}$ |

| INT Output Low Voltage                                                                  |              | $I_{INT} = 1\text{mA}$                                                    | 25   | 200   |      | mV            |

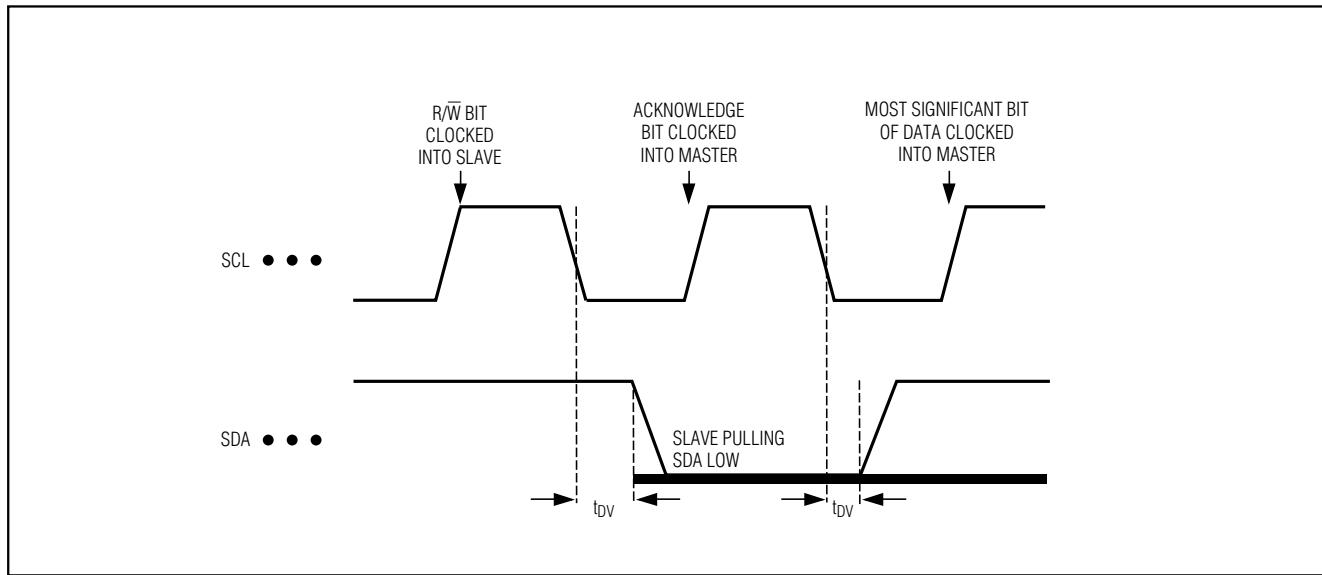

| <b>SMB INTERFACE TIMING SPECIFICATIONS</b> ( $V_{DD} = 2.8V$ to 5.65V, Figures 4 and 5) |              |                                                                           |      |       |      |               |

| SCL High Period                                                                         | $t_{HIGH}$   |                                                                           | 4    |       |      | $\mu\text{s}$ |

| SCL Low Period                                                                          | $t_{LOW}$    |                                                                           | 4.7  |       |      | $\mu\text{s}$ |

| Start Condition Setup Time from SCL                                                     | $t_{SU:STA}$ |                                                                           | 4.7  |       |      | $\mu\text{s}$ |

| Start Condition Hold Time from SCL                                                      | $t_{HD:STA}$ |                                                                           | 4    |       |      | $\mu\text{s}$ |

| SDA Setup Time from SCL                                                                 | $t_{SU:DAT}$ |                                                                           | 250  |       |      | ns            |

| SDA Hold Time from SCL                                                                  | $t_{HD:DAT}$ |                                                                           | 0    |       |      | ns            |

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{DD} = +3.3V$ ,  $V_{BATT} = +16.8V$ ,  $V_{DCIN} = +18V$ ,  $T_A = 0^{\circ}\text{C to } +85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                                                                            | SYMBOL    | CONDITIONS | MIN | TYP | MAX | UNITS         |

|--------------------------------------------------------------------------------------|-----------|------------|-----|-----|-----|---------------|

| SDA Output Data Valid from SCL                                                       | $t_{DV}$  |            |     | 1   |     | $\mu\text{s}$ |

| Maximum Charge Period<br>Without a ChargingVoltage() or<br>Charging Current() Loaded | $t_{WDT}$ |            | 140 | 175 | 210 | s             |

## ELECTRICAL CHARACTERISTICS

(Circuit of Figure 1,  $V_{DD} = +3.3V$ ,  $V_{BATT} = +16.8V$ ,  $V_{DCIN} = +18V$ ,  $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ , unless otherwise noted. Guaranteed by design.)

| PARAMETER                                       | SYMBOL        | CONDITIONS                                                            | MIN   | MAX   | UNITS         |

|-------------------------------------------------|---------------|-----------------------------------------------------------------------|-------|-------|---------------|

| <b>GENERAL SPECIFICATIONS</b>                   |               |                                                                       |       |       |               |

| DCIN Typical Operating Range                    | $V_{DCIN}$    |                                                                       | 8     | 28    | V             |

| DCIN Supply Current                             | $I_{DCIN}$    | $8V < V_{DCIN} < 28V$                                                 |       | 6     | mA            |

| DCIN Supply Current Charging Inhibited          |               | $8V < V_{DCIN} < 28V$                                                 |       | 2     | mA            |

| DCIN Undervoltage Threshold                     |               | When AC_PRESENT switches                                              | 7.85  |       | V             |

|                                                 |               | DCIN rising                                                           |       |       |               |

|                                                 |               | DCIN falling                                                          | 7     |       |               |

| LDO Output Voltage                              | $V_{LDO}$     | $8V < V_{DCIN} < 28V$ , $0 < I_{LDO} < 15\text{mA}$                   | 5.15  | 5.65  | V             |

| $V_{DD}$ Input Voltage Range<br>(Note 1)        |               | $8V < V_{DCIN} < 28V$                                                 | 2.8   | 5.65  | V             |

| $V_{DD}$ Undervoltage Threshold                 |               | When the SMB responds to commands                                     | 2.8   |       | V             |

|                                                 |               | $V_{DD}$ rising                                                       |       |       |               |

|                                                 |               | $V_{DD}$ falling                                                      | 2.1   |       |               |

| $V_{DD}$ Quiescent Current                      | $I_{DD}$      | $0 < V_{DCIN} < 6V$ , $V_{DD} = 5V$ , $V_{SCL} = 5V$ , $V_{SDA} = 5V$ |       | 150   | $\mu\text{A}$ |

| REF Output Voltage                              | $V_{REF}$     | $0 < I_{REF} < 200\mu\text{A}$                                        | 4.035 | 4.157 | V             |

| BATT Undervoltage Threshold<br>(Note 2)         |               | When $I_{CHARGE}$ drops to 128mA                                      | 2.4   | 2.8   | V             |

| PDS Charging Source Switch Turn-Off Threshold   | $V_{PDS-OFF}$ | $V_{CVS}$ referred to $V_{BATT}$ , $V_{CVS}$ falling                  | 50    | 150   | mV            |

| PDS Charging Source Switch Threshold Hysteresis | $V_{PDS-HYS}$ | $V_{CVS}$ referred to $V_{BATT}$                                      | 100   | 300   | mV            |

| PDS Output Low Voltage, PDS Below CSSP          |               | $I_{PDS} = 0$                                                         | 8     | 12    | V             |

| PDS Turn-On Current                             |               | $PDS = CSSP$                                                          | 100   | 300   | $\mu\text{A}$ |

| PDS Turn-Off Current                            |               | $V_{PDS} = V_{CSSP} - 2V$ , $V_{DCIN} = 16V$                          | 10    |       | mA            |

| PDL Load Switch Turn-Off Threshold              | $V_{PDL-OFF}$ | $V_{CVS}$ referred to $V_{BATT}$ , $V_{CVS}$ rising                   | -150  | -50   | mV            |

| PDL Load Switch Threshold Hysteresis            | $V_{PDL-HYS}$ | $V_{CVS}$ referred to $V_{BATT}$                                      | 100   | 300   | mV            |

| PDL Turn-Off Current                            |               | $V_{CSSN} - V_{PDL} = 1V$                                             | 6     |       | mA            |

**MAX1645/MAX1645A**

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{DD} = +3.3V$ ,  $V_{BATT} = +16.8V$ ,  $V_{DCIN} = +18V$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Guaranteed by design.)

| PARAMETER                                  | SYMBOL           | CONDITIONS                                                                                  | MIN                        | MAX    | UNITS                   |    |

|--------------------------------------------|------------------|---------------------------------------------------------------------------------------------|----------------------------|--------|-------------------------|----|

| PDL Turn-On Resistance                     |                  | PDL to GND                                                                                  | 50                         | 150    | $\text{k}\Omega$        |    |

| CVS Input Bias Current                     |                  | $V_{CVS} = 28V$                                                                             |                            | 20     | $\mu\text{A}$           |    |

| <b>ERROR AMPLIFIER SPECIFICATIONS</b>      |                  |                                                                                             |                            |        |                         |    |

| BATT Full-Charge Voltage                   | V <sub>O</sub>   | ChargingVoltage() = 0x41A0                                                                  | 16.532                     | 17.068 | V                       |    |

|                                            |                  | ChargingVoltage() = 0x3130                                                                  | 12.391                     | 12.793 |                         |    |

|                                            |                  | ChargingVoltage() = 0x20D0                                                                  | 8.266                      | 8.534  |                         |    |

|                                            |                  | ChargingVoltage() = 0x1060                                                                  | 4.124                      | 4.260  |                         |    |

| BATT Charge Current (Note 3)               | I <sub>O</sub>   | R <sub>CSI</sub> = 50m $\Omega$                                                             | ChargingCurrent() = 0x0BC0 | 2.608  | 3.408                   | A  |

|                                            |                  |                                                                                             | ChargingCurrent() = 0x0080 | 15.2   | 240.8                   | mA |

| DCIN Source Current Limit (Note 3)         |                  | R <sub>CSS</sub> = 40m $\Omega$                                                             | $V_{CLS} = 4.096V$         | 4.358  | 5.882                   | A  |

|                                            |                  |                                                                                             | $V_{CLS} = 2.048V$         | 2.054  | 3.006                   |    |

| BATT Undervoltage Charge Current           |                  | $V_{BATT} = 1V$ , $R_{CSI} = 50m\Omega$                                                     |                            | 20     | 200                     | mA |

| BATT/CSIP/CSIN Input Voltage Range         |                  |                                                                                             |                            | 0      | 20                      | V  |

| Total BATT Input Bias Current              |                  | Total of $I_{BATT}$ , $I_{CSIP}$ , and $I_{CSIN}$ ; $V_{BATT} = 0$ to 20V                   | -700                       | 700    | $\mu\text{A}$           |    |

| Total BATT Quiescent Current               |                  | Total of $I_{BATT}$ , $I_{CSIP}$ , and $I_{CSIN}$ ; $V_{BATT} = 0$ to 20V, charge inhibited | -100                       | 100    | $\mu\text{A}$           |    |

| Total BATT Standby Current                 |                  | Total of $I_{BATT}$ , $I_{CSIP}$ , and $I_{CSIN}$ ; $V_{BATT} = 0$ to 20V, $V_{DCIN} = 0$   | -5                         | 5      | $\mu\text{A}$           |    |

| CSSP/Input Bias Current                    |                  | $V_{CSSP} = V_{CSSN} = V_{DCIN} = 28V$                                                      | -100                       | 1000   | $\mu\text{A}$           |    |

| CSSN Input Bias Current                    |                  | $V_{CSSP} = V_{CSSN} = V_{DCIN} = 28V$                                                      | -100                       | 100    | $\mu\text{A}$           |    |

| CSSP/CSSN Quiescent Current                |                  | $V_{CSSP} = V_{CSSN} = 28V$ , $V_{DCIN} = 0$                                                | -1                         | 1      | $\mu\text{A}$           |    |

| Battery Voltage-Error Amp DC Gain          |                  | From BATT to CCV                                                                            | 200                        |        | V/V                     |    |

| CLS Input Bias Current                     |                  | $V_{CLS} = V_{REF}/2$ to $V_{REF}$                                                          | -1                         | 1      | $\mu\text{A}$           |    |

| Battery Voltage-Error Amp Transconductance |                  | From BATT to CCV, ChargingVoltage() = 0x41A0, $V_{BATT} = 16.8V$                            | 0.111                      | 0.444  | $\mu\text{A}/\text{mV}$ |    |

| Battery Current-Error Amp Transconductance |                  | From CSIP/CSIN to CCI, ChargingCurrent() = 0x0BC0, $V_{CSIP} - V_{CSIN} = 150.4\text{mV}$   | 0.5                        | 2      | $\mu\text{A}/\text{mV}$ |    |

| Input Current-Error Amp Transconductance   |                  | From CSSP/CSSN to CCS, $V_{CLS} = 2.048V$ , $V_{CSSP} - V_{CSSN} = 102.4\text{mV}$          | 0.5                        | 2      | $\mu\text{A}/\text{mV}$ |    |

| CCV/CCI/CCS Clamp Voltage (Note 4)         |                  | $V_{CCV} = V_{CCI} = V_{CCS} = 0.25V$ to 2V                                                 | 150                        | 600    | mV                      |    |

| <b>DC-TO-DC CONVERTER SPECIFICATIONS</b>   |                  |                                                                                             |                            |        |                         |    |

| Minimum Off-Time                           | t <sub>OFF</sub> |                                                                                             | 1                          | 1.5    | $\mu\text{s}$           |    |

| Maximum On-Time                            | t <sub>ON</sub>  |                                                                                             | 5                          | 15     | ms                      |    |

| Maximum Duty Cycle                         |                  |                                                                                             | 99                         |        | %                       |    |

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{DD} = +3.3V$ ,  $V_{BATT} = +16.8V$ ,  $V_{DCIN} = +18V$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Guaranteed by design.)

| PARAMETER                   | SYMBOL | CONDITIONS                                   | MIN | MAX | UNITS         |

|-----------------------------|--------|----------------------------------------------|-----|-----|---------------|

| LX Input Bias Current       |        | $V_{DCIN} = 28V$ , $V_{BATT} = V_{LX} = 20V$ |     | 500 | $\mu\text{A}$ |

| LX Input Quiescent Current  |        | $V_{DCIN} = 0$ , $V_{BATT} = V_{LX} = 20V$   |     | 1   | $\mu\text{A}$ |

| BST Supply Current          |        | DHI high                                     |     | 15  | $\mu\text{A}$ |

| DLOV Supply Current         |        | $V_{DLOV} = V_{LDO}$ , DLO low               |     | 10  | $\mu\text{A}$ |

| Inductor Peak Current Limit |        | $R_{CSI} = 50\text{m}\Omega$                 | 5.0 | 7.0 | A             |

| DHI Output Resistance       |        | DHI high or low, $V_{BST} - V_{LX} = 4.5V$   |     | 14  | $\Omega$      |

| DLO Output Resistance       |        | DLO high or low, $V_{DLOV} = 4.5V$           |     | 14  | $\Omega$      |

## THERMISTOR COMPARATOR SPECIFICATIONS

|                                 |  |                                                                           |      |      |               |

|---------------------------------|--|---------------------------------------------------------------------------|------|------|---------------|

| THM Input Bias Current          |  | $V_{THM} = 4\%$ of $V_{DD}$ to 96% of $V_{DD}$ , $V_{DD} = 2.8V$ to 5.65V | -1   | 1    | $\mu\text{A}$ |

| Thermistor Overrange Threshold  |  | $V_{DD} = 2.8V$ to 5.65V, $V_{THM}$ falling                               | 89.5 | 92.5 | % of $V_{DD}$ |

| Thermistor Cold Threshold       |  | $V_{DD} = 2.8V$ to 5.65V, $V_{THM}$ falling                               | 74   | 77   | % of $V_{DD}$ |

| Thermistor Hot Threshold        |  | $V_{DD} = 2.8V$ to 5.65V, $V_{THM}$ falling                               | 22   | 25   | % of $V_{DD}$ |

| Thermistor Underrange Threshold |  | $V_{DD} = 2.8V$ to 5.65V, $V_{THM}$ falling                               | 6    | 9    | % of $V_{DD}$ |

## SMB INTERFACE LEVEL SPECIFICATIONS ( $V_{DD} = 2.8V$ to 5.65V)

|                             |  |                                   |     |               |

|-----------------------------|--|-----------------------------------|-----|---------------|

| SDA/SCL Input Low Voltage   |  |                                   | 0.6 | V             |

| SDA/SCL Input High Voltage  |  |                                   | 1.4 | V             |

| SDA/SCL Input Bias Current  |  |                                   | -1  | $\mu\text{A}$ |

| SDA Output Low Sink Current |  | $V_{SDA} = 0.4V$                  | 6   | mA            |

| INT Output High Leakage     |  | $V_{INT} = 5.65V$                 |     | $\mu\text{A}$ |

| INT Output Low Voltage      |  | $I_{\overline{INT}} = 1\text{mA}$ | 200 | mV            |

## SMB INTERFACE TIMING SPECIFICATIONS ( $V_{DD} = 2.8V$ to 5.65V, Figures 4 and 5)

|                                     |              |  |     |               |

|-------------------------------------|--------------|--|-----|---------------|

| SCL High Period                     | $t_{HIGH}$   |  | 4   | $\mu\text{s}$ |

| SCL Low Period                      | $t_{LOW}$    |  | 4.7 | $\mu\text{s}$ |

| Start Condition Setup Time from SCL | $t_{SU:STA}$ |  | 4.7 | $\mu\text{s}$ |

| Start Condition Hold Time from SCL  | $t_{HD:STA}$ |  | 4   | $\mu\text{s}$ |

| SDA Setup Time from SCL             | $t_{SU:DAT}$ |  | 250 | ns            |

| SDA Hold Time from SCL              | $t_{HD:DAT}$ |  | 0   | ns            |

MAX1645/MAX1645A

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1,  $V_{DD} = +3.3V$ ,  $V_{BATT} = +16.8V$ ,  $V_{DCIN} = +18V$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Guaranteed by design.)

| PARAMETER                                                                      | SYMBOL    | CONDITIONS | MIN | MAX | UNITS         |

|--------------------------------------------------------------------------------|-----------|------------|-----|-----|---------------|

| SDA Output Data Valid from SCL                                                 | $t_{DV}$  |            |     | 1   | $\mu\text{s}$ |

| Maximum Charge Period Without a ChargingVoltage() or Charging Current() loaded | $t_{WDT}$ |            | 140 | 210 | s             |

**Note 1:** Guaranteed by meeting the SMB timing specs.

**Note 2:** The charger reverts to a trickle-charge mode of  $I_{CHARGE} = 128\text{mA}$  below this threshold.

**Note 3:** Does not include current-sense resistor tolerance.

**Note 4:** Voltage difference between CCV, and CCI or CCS when one of these three pins is held low and the others try to pull high.

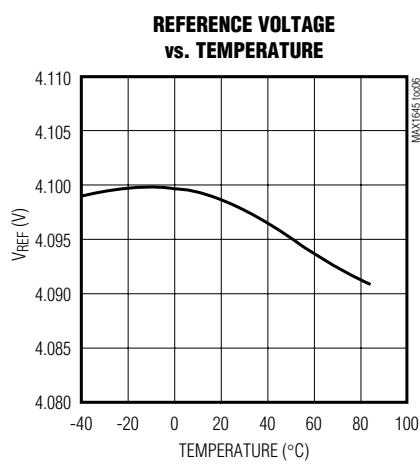

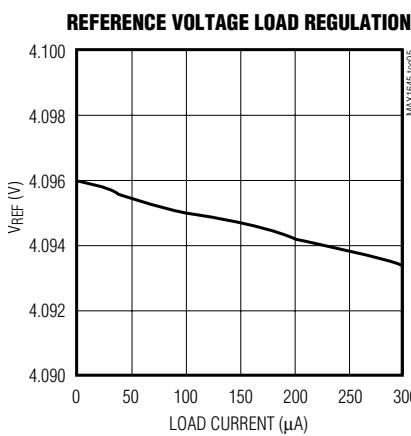

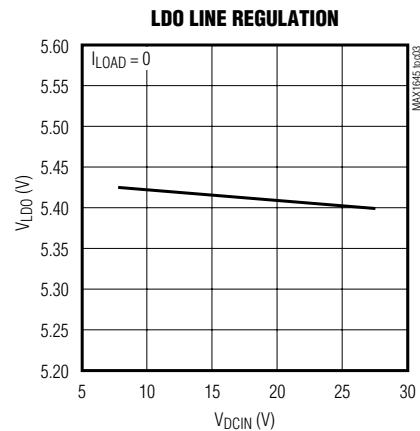

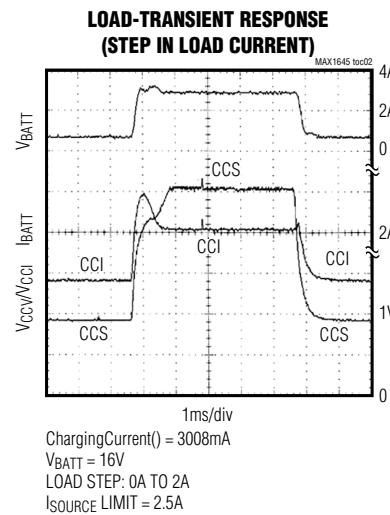

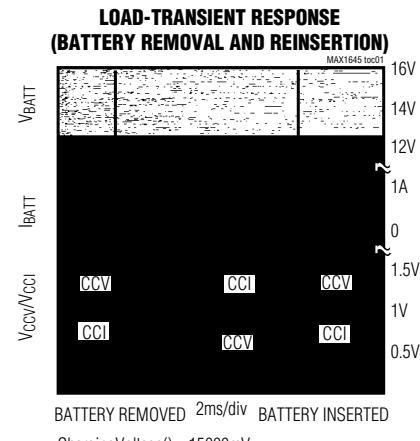

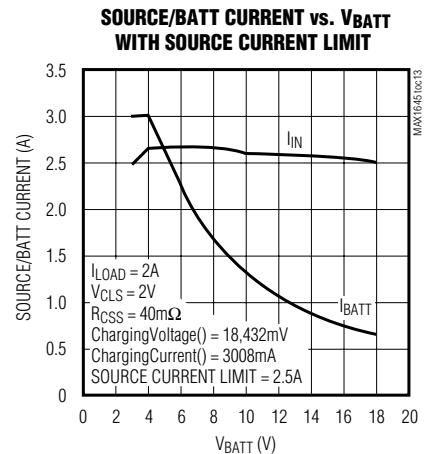

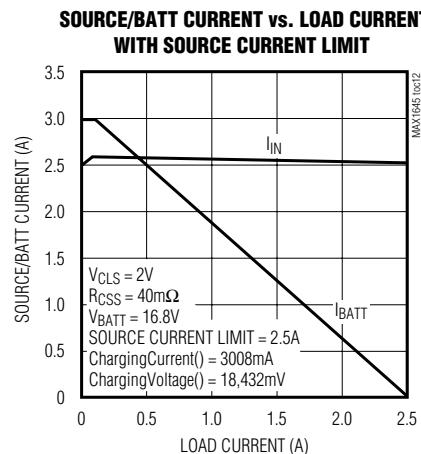

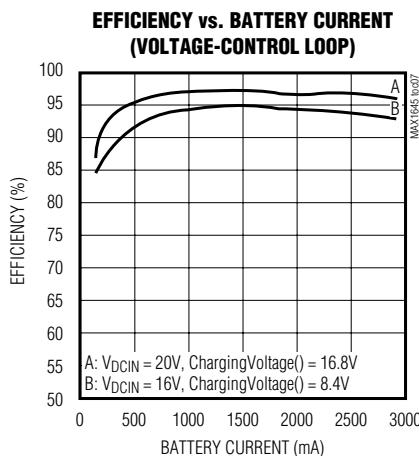

## Typical Operating Characteristics

(Circuit of Figure 1,  $V_{DCIN} = 20V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{DCIN} = 20V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

**MAX1645/MAX1645A**

## Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

### Pin Description

| PIN | NAME | FUNCTION                                                                                                                                |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DCIN | DC Supply Voltage Input                                                                                                                 |

| 2   | LDO  | 5.4V Linear-Regulator Voltage Output. Bypass with a 1 $\mu$ F capacitor to GND.                                                         |

| 3   | CLS  | Source Current Limit Input                                                                                                              |

| 4   | REF  | 4.096V Reference Voltage Output                                                                                                         |

| 5   | CCS  | Charging Source Compensation Capacitor Connection. Connect a 0.01 $\mu$ F capacitor from CCS to GND.                                    |

| 6   | CCI  | Battery Current-Loop Compensation Capacitor Connection. Connect a 0.01 $\mu$ F capacitor from CCI to GND.                               |

| 7   | CCV  | Battery Voltage-Loop Compensation Capacitor Connection. Connect a 10k $\Omega$ resistor in series with a 0.01 $\mu$ F capacitor to GND. |

| 8   | GND  | Ground                                                                                                                                  |

| 9   | BATT | Battery Voltage Output                                                                                                                  |

| 10  | DAC  | DAC Voltage Output                                                                                                                      |

| 11  | VDD  | Logic Circuitry Supply Voltage Input (2.8V to 5.65V)                                                                                    |

| 12  | THM  | Thermistor Voltage Input                                                                                                                |

| 13  | SCL  | SMB Clock Input                                                                                                                         |

| 14  | SDA  | SMB Data Input/Output. Open-drain output. Needs external pull-up.                                                                       |

| 15  | INT  | Interrupt Output. Open-drain output. Needs external pull-up.                                                                            |

| 16  | PDL  | PMOS Load Switch Driver Output                                                                                                          |

| 17  | CSIN | Battery Current-Sense Negative Input                                                                                                    |

| 18  | CSIP | Battery Current-Sense Positive Input                                                                                                    |

| 19  | PGND | Power Ground                                                                                                                            |

| 20  | DLO  | Low-Side NMOS Driver Output                                                                                                             |

| 21  | DLOV | Low-Side NMOS Driver Supply Voltage. Bypass with 0.1 $\mu$ F capacitor to GND.                                                          |

| 22  | LX   | Inductor Voltage Sense Input                                                                                                            |

| 23  | DHI  | High-Side NMOS Driver Output                                                                                                            |

| 24  | BST  | High-Side Driver Bootstrap Voltage Input. Bypass with 0.1 $\mu$ F capacitor to LX.                                                      |

| 25  | CSSN | Charging Source Current-Sense Negative Input                                                                                            |

| 26  | CSSP | Charging Source Current-Sense Positive Input                                                                                            |

| 27  | PDS  | Charging Source PMOS Switch Driver Output                                                                                               |

| 28  | CVS  | Charging Source Voltage Input                                                                                                           |

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## Detailed Description

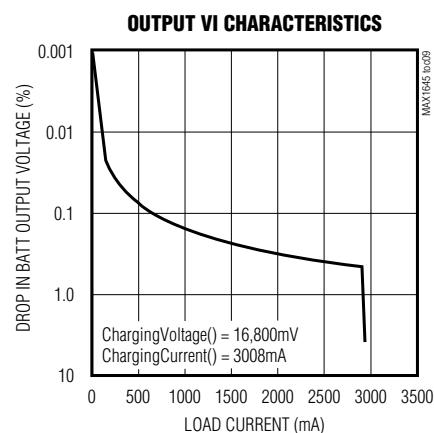

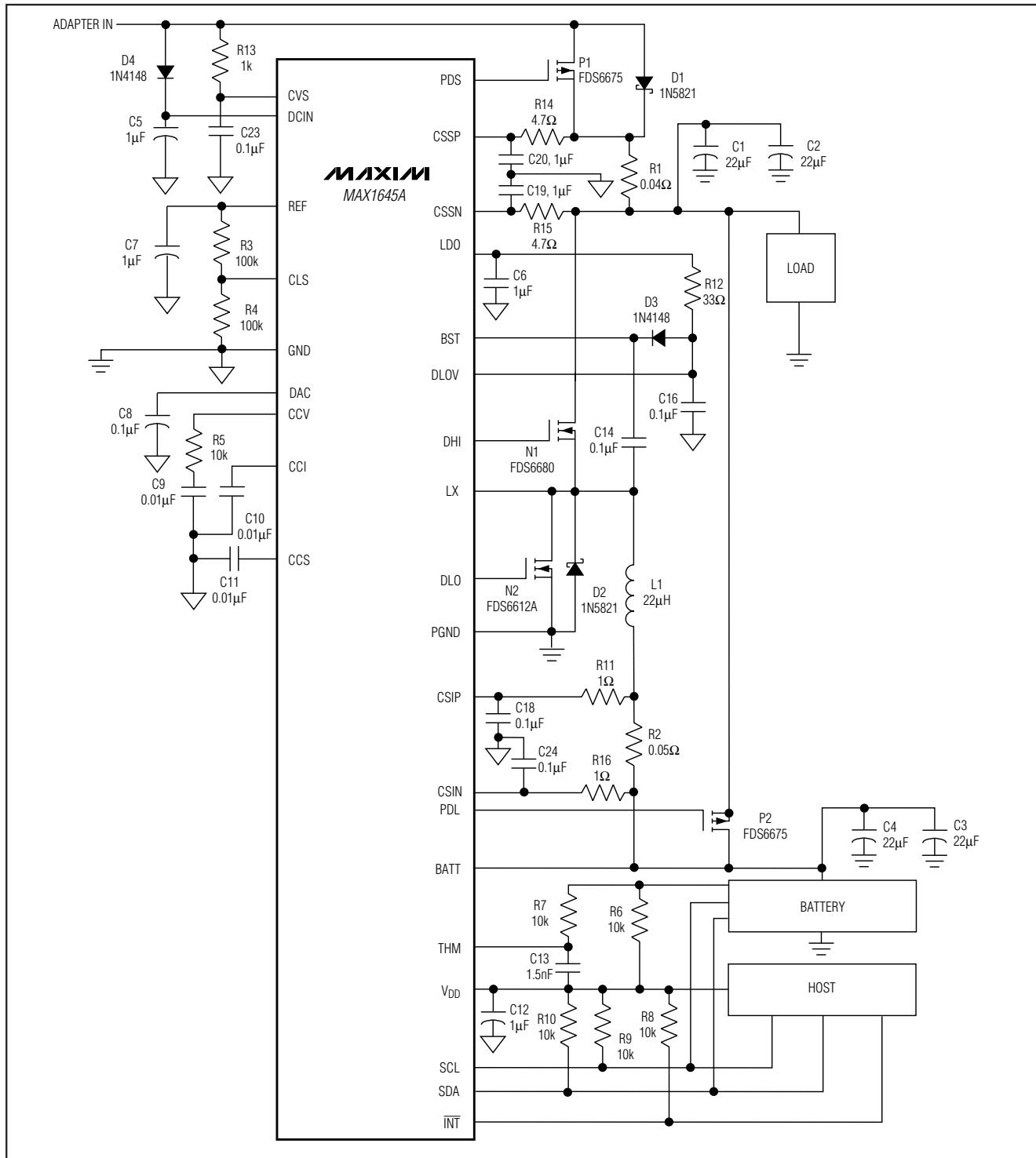

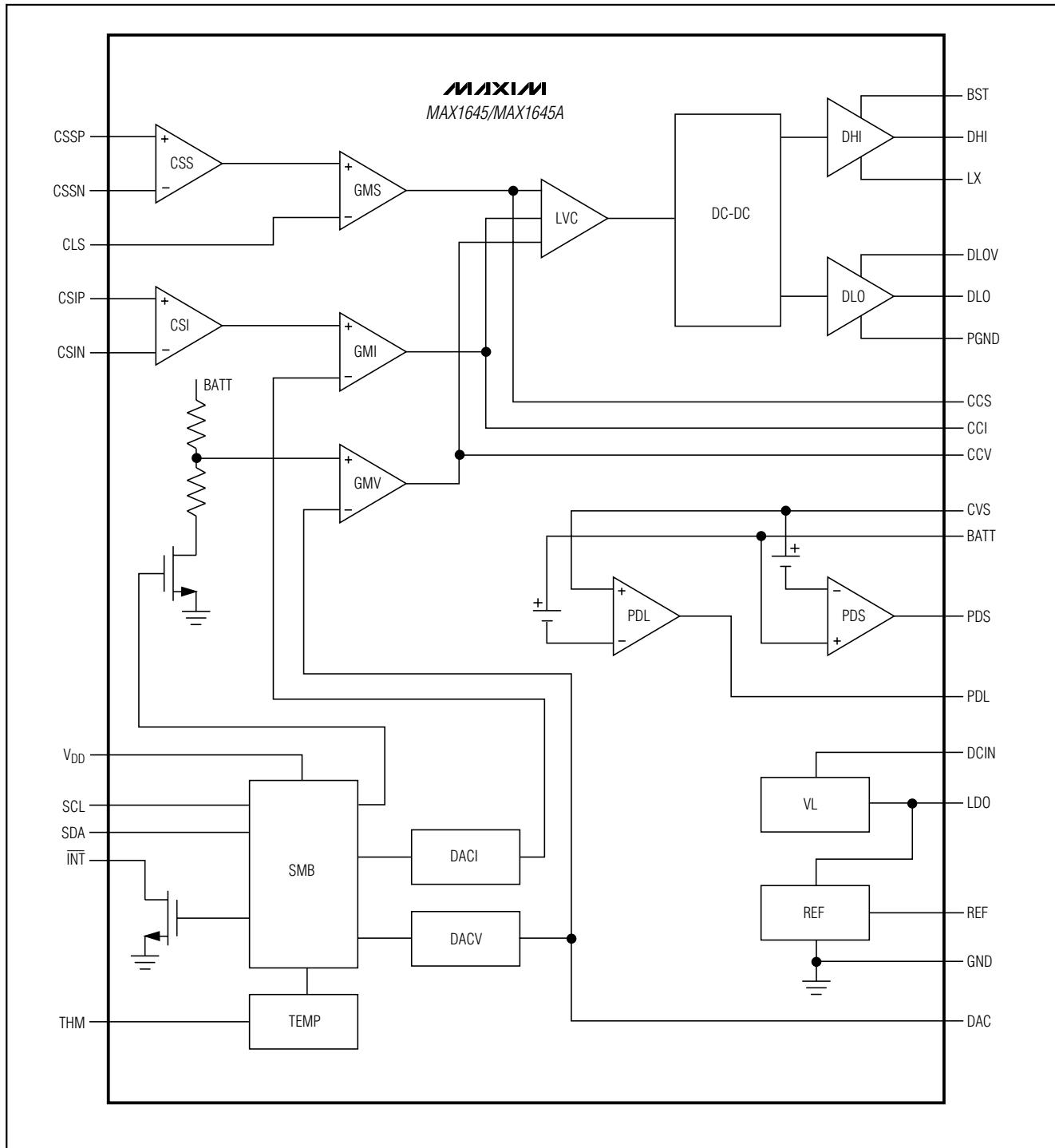

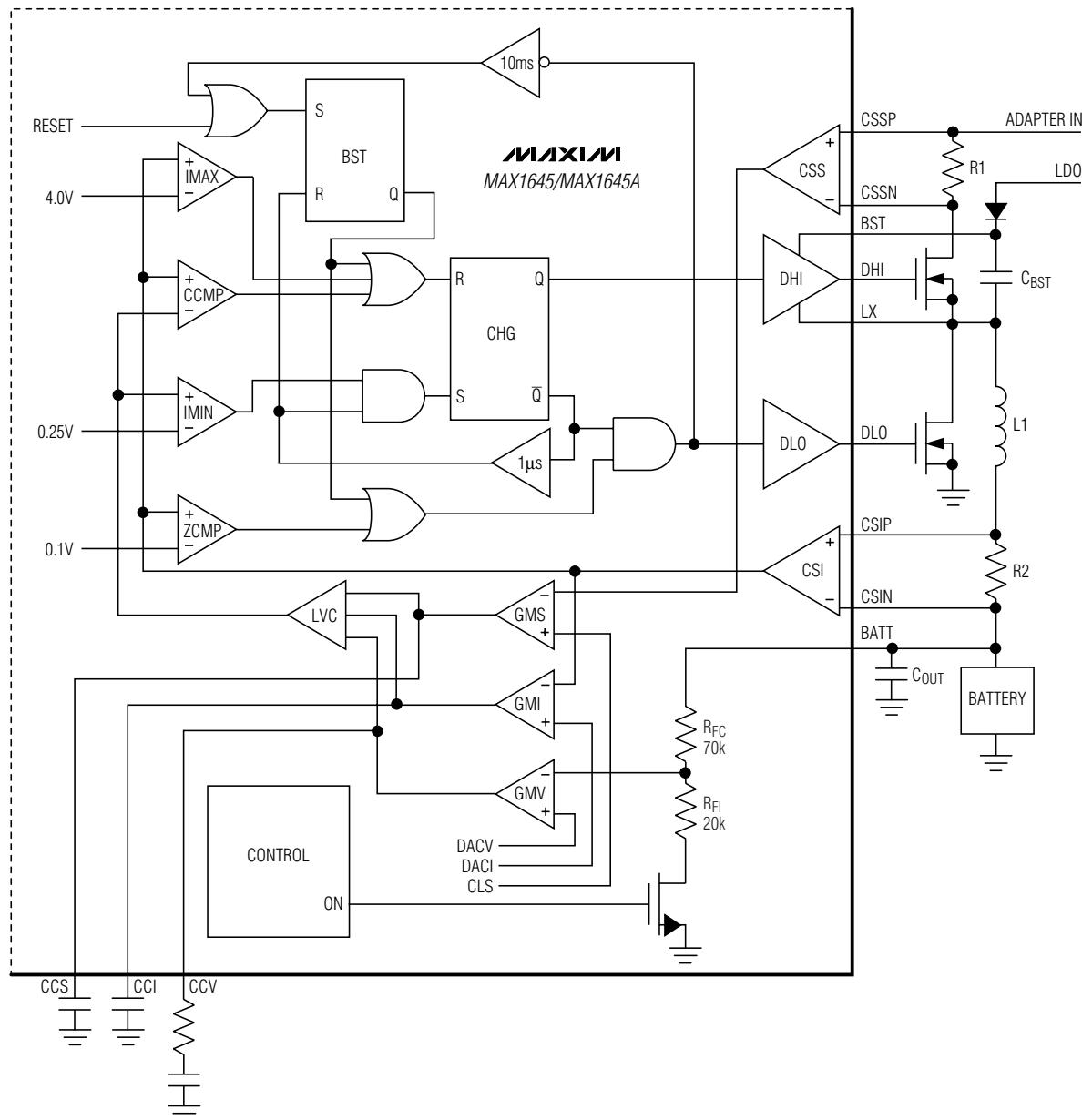

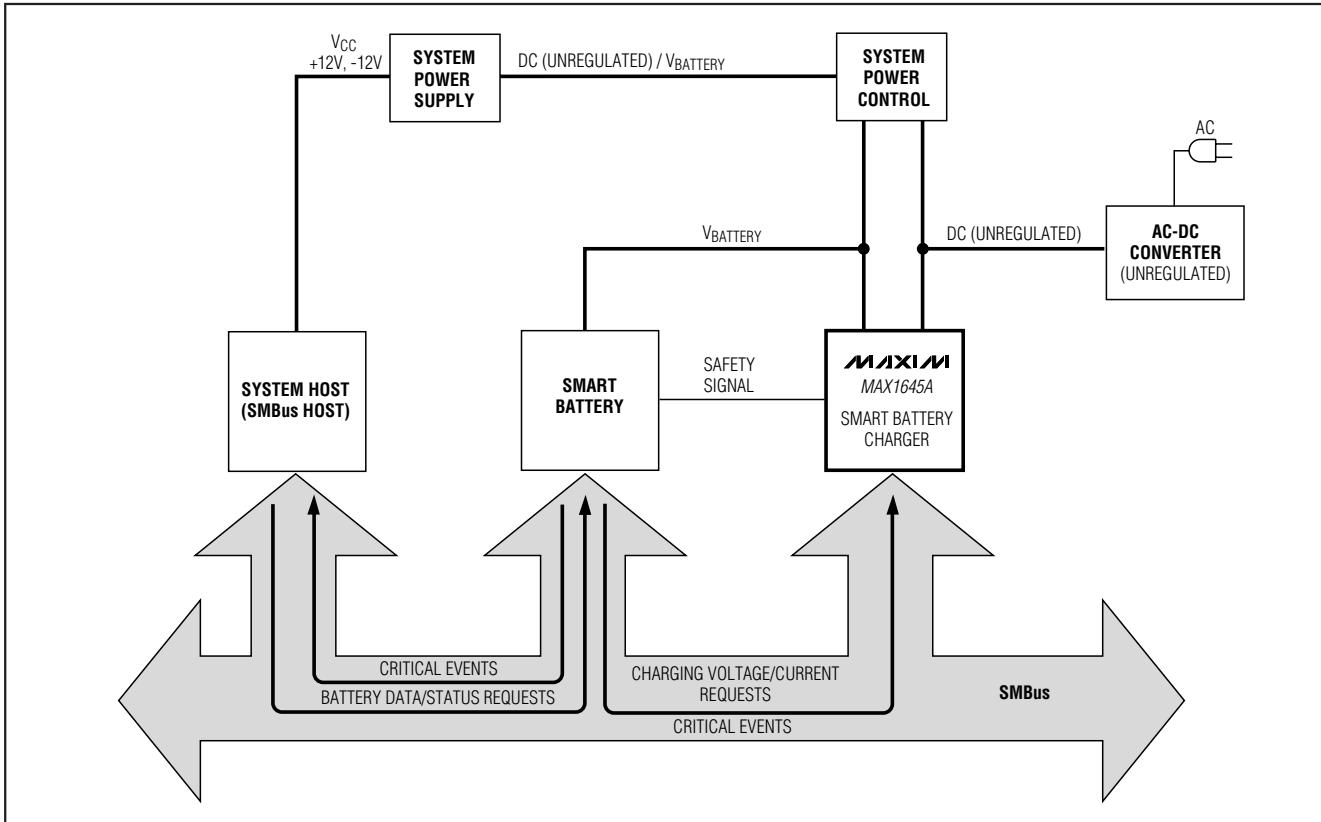

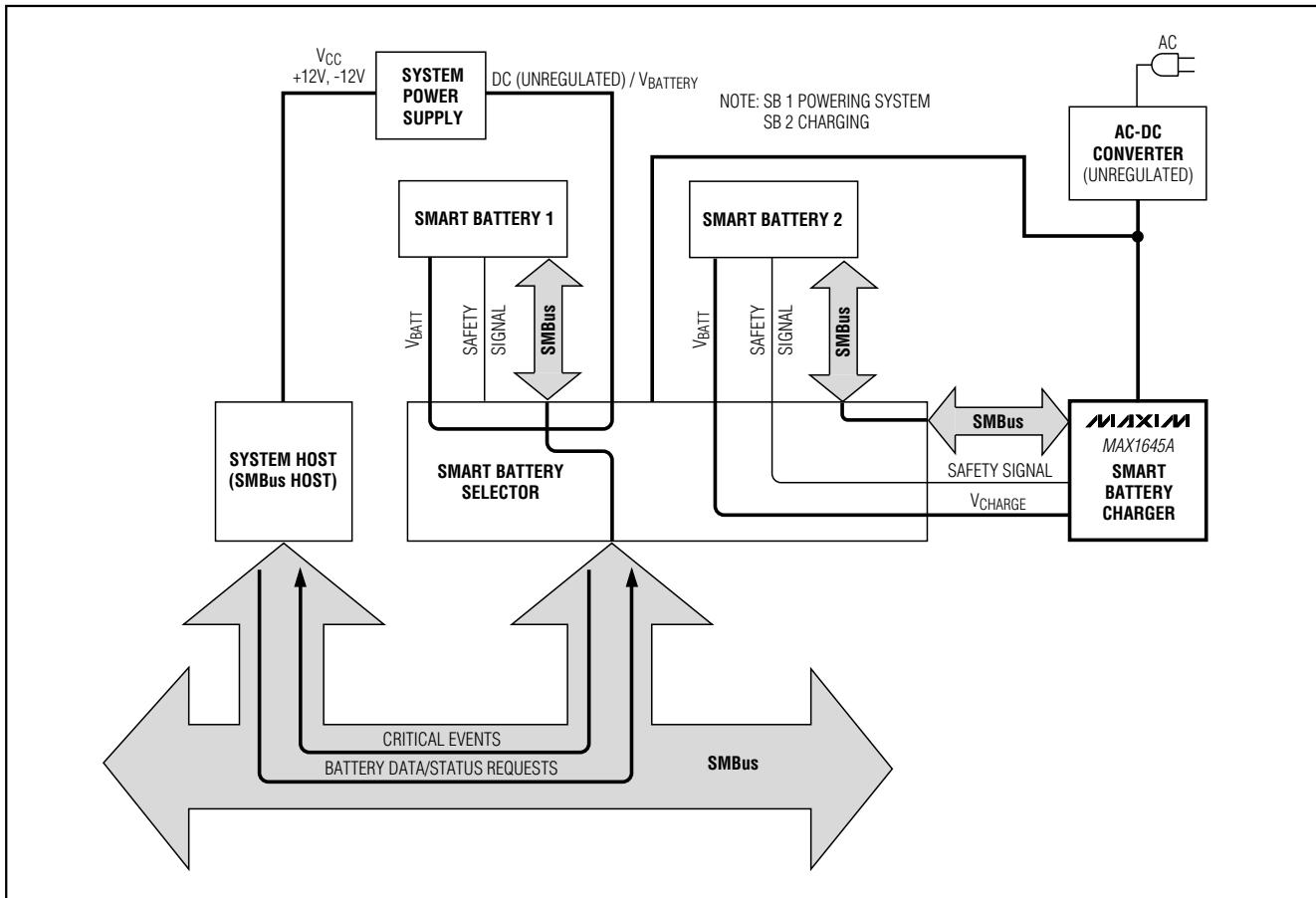

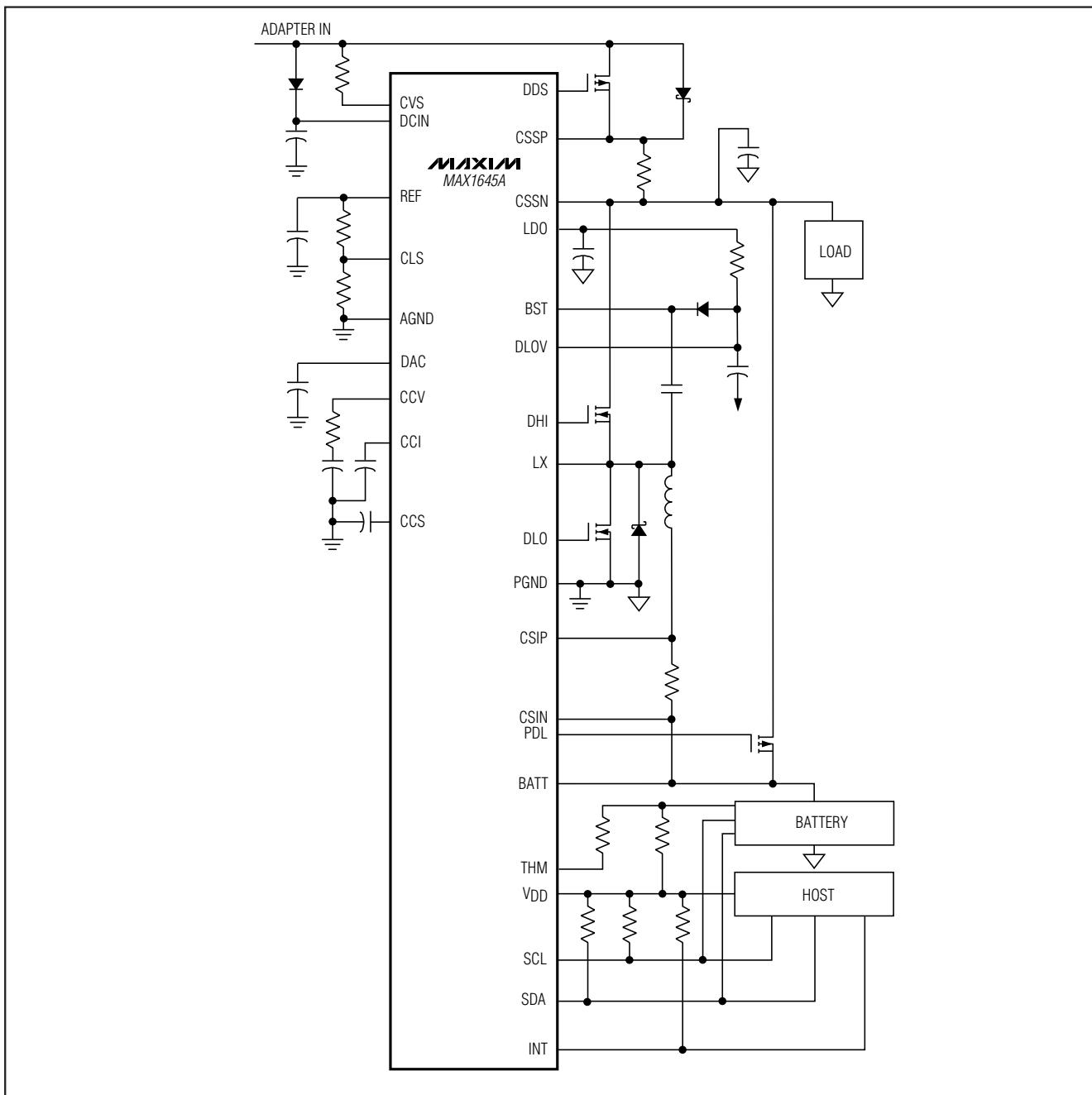

The MAX1645/MAX1645A consist of current-sense amplifiers, an SMBus interface, transconductance amplifiers, reference circuitry, and a DC-DC converter (Figure 2). The DC-DC converter generates the control signals for the external MOSFETs to maintain the voltage and the current set by the SMBus interface. The MAX1645/MAX1645A feature a voltage-regulation loop and two current-regulation loops. The loops operate independently of each other. The voltage-regulation loop monitors BATT to ensure that its voltage never exceeds the voltage set point ( $V_0$ ). The battery current-regulation loop monitors current delivered to BATT to ensure that it never exceeds the current-limit set point ( $I_0$ ). The battery current-regulation loop is in control as long as BATT voltage is below  $V_0$ . When BATT voltage reaches  $V_0$ , the current loop no longer regulates. A third loop reduces the battery-charging current when the sum of the system (the main load) and the battery charger input current exceeds the charging source current limit.

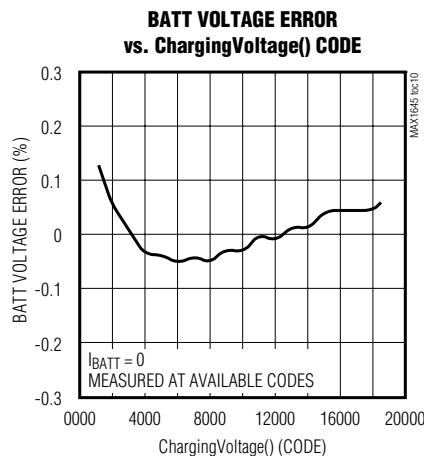

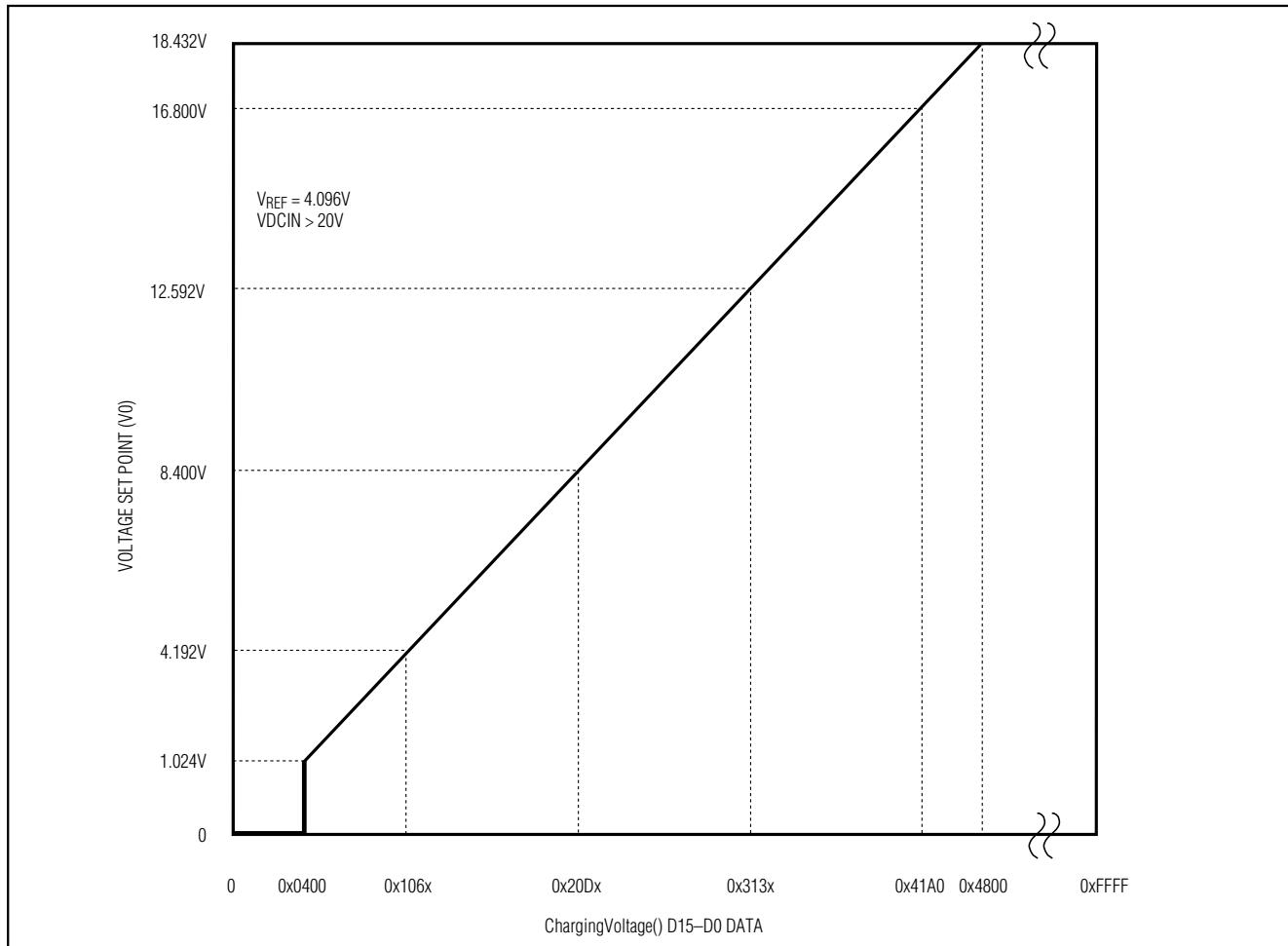

### Setting Output Voltage

The MAX1645/MAX1645A voltage DACs have a 16mV LSB and an 18.432V full scale. The SMBus specification allows for a 16-bit ChargingVoltage() command that translates to a 1mV LSB and a 65.535V full-scale voltage; therefore, the ChargingVoltage() value corresponds to the output voltage in millivolts. The MAX1645/MAX1645A ignore the first four LSBs and use the next 11 LSBs to control the voltage DAC. All codes greater than or equal to 0b0100 1000 0000 0000 (18432mV) result in a voltage overrange, limiting the charger voltage to 18.432V. All codes below 0b0000 0100 0000 0000 (1024mV) terminate charging.

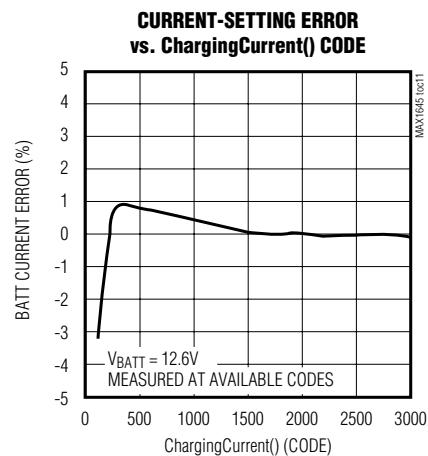

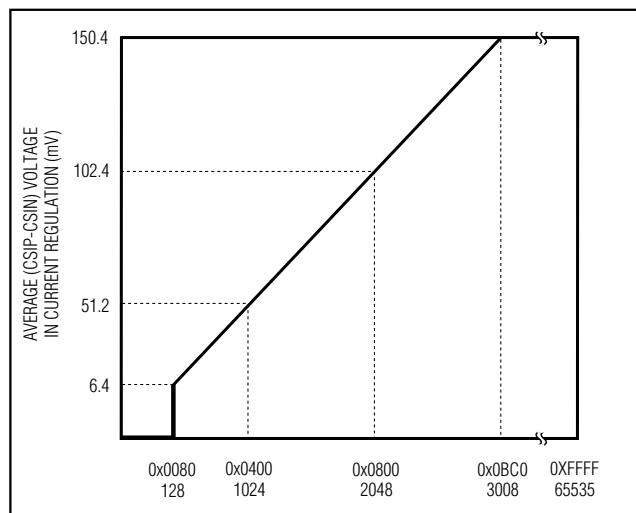

### Setting Output Current

The MAX1645/MAX1645A current DACs have a 64mA LSB and a 3.008A full scale. The SMBus specification allows for a 16-bit ChargingCurrent() command that translates to a 1mA LSB and a 65.535A full-scale current; the ChargingCurrent() value corresponds to the charging voltage in millamps. The MAX1645/MAX1645A drop the first six LSBs and use the next six LSBs to control the current DAC. All codes above 0b00 1011 1100 0000 (3008mA) result in a current overrange, limiting the charger current to 3.008A. All codes below 0b0000 0000 1000 0000 (128mA) turn the charging current off. A 50m $\Omega$  sense resistor (R2 in Figure 1) is required to achieve the correct CODE/current scaling.

### Input Current Limiting

The MAX1645/MAX1645A limit the current drawn by the charger when the load current becomes high. The devices limit the charging current so the AC adapter voltage is not loaded down. An internal amplifier, CSS, compares the voltage between CSSP and CSSN to the voltage at CLS/20. VCLS is set by a resistor-divider between REF and GND.

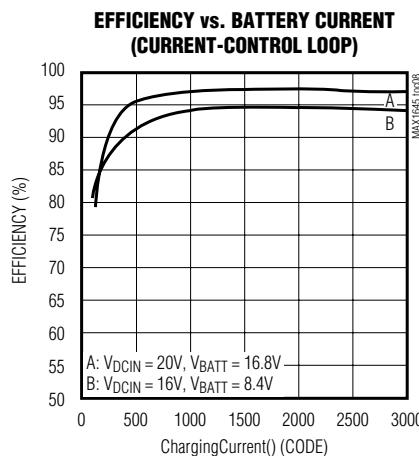

The input source current is the sum of the device current, the charge input current, and the load current. The device current is minimal (6mA max) in comparison to the charge and load currents. The charger input current is generated by the DC-DC converter; therefore, the actual source current required is determined as follows:

$$I_{\text{SOURCE}} = I_{\text{LOAD}} + [(I_{\text{CHARGE}} \cdot V_{\text{BATT}}) / (V_{\text{IN}} \cdot \eta)]$$

where  $\eta$  is the efficiency of the DC-DC converter (typically 85% to 95%).

VCLS determines the threshold voltage of the CSS comparator. R3 and R4 (Figure 1) set the voltage at CLS. Sense resistor R1 sets the maximum allowable source current. Calculate the maximum current as follows:

$$I_{\text{MAX}} = V_{\text{CLS}} / (20 \cdot R_1)$$

(Limit  $V_{\text{CSSP}} - V_{\text{CSSN}}$  to between 102.4mV and 204.8mV.)

The configuration in Figure 1 provides an input current limit of:

$$I_{\text{MAX}} = (2.048V / 20) / 0.04\Omega = 2.56A$$

### LDO Regulator

An integrated LDO regulator provides a +5.4V supply derived from DCIN, which can deliver up to 15mA of current. The LDO sets the gate-drive level of the NMOS switches in the DC-DC converter. The drivers are actually powered by DLOV and BST, which must be connected to LDO through a lowpass filter and a diode as shown in Figure 1. See also the *MOSFET Drivers* section. The LDO also supplies the 4.096V reference and most of the control circuitry. Bypass LDO with a 1 $\mu$ F capacitor.

### VDD Supply

This input provides power to the SMBus interface and the thermistor comparators. Typically connect VDD to LDO or, to keep the SMBus interface of the MAX1645/MAX1645A active while the supply to DCIN is removed, connect an external supply to VDD.

**MAX1645/MAX1645A**

# **Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting**

Figure 1. Typical Application Circuit

## Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

**MAX1645/MAX1645A**

Figure 2. Functional Diagram

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

## Operating Conditions

The MAX1645/MAX1645A change their operation depending on the voltages at DCIN, BATT, VDD, and THM. Several important operating states follow:

- **AC Present.** When DCIN is  $> 7.5V$ , the battery is considered to be in an AC Present state. In this condition, both the LDO and REF will function properly and battery charging is allowed. When AC is present, the AC\_PRESENT bit (bit 15) in the ChargerStatus() register is set to "1."

- **Power Fail.** When DCIN is  $< BATT + 0.3V$ , the part is in the Power Fail state, since the charger doesn't have enough input voltage to charge the battery. In Power Fail, the PDS input PMOS switch is turned off and the POWER\_FAIL bit (bit 13) in the ChargerStatus() register is set to "1."

- **Battery Present.** When THM is  $< 91\%$  of VDD, the battery is considered to be present. The MAX1645/MAX1645A use the THM pin to detect when a battery is connected to the charger. When the battery is present, the BATTERY\_PRESENT bit (bit 14) in the ChargerStatus() register is set to "1" and charging can proceed. When the battery is not present, all of the registers are reset. With no battery present, the charger will perform a "Float" charge to minimize contact arcing on battery connection. "Float" charge will still try to regulate the BATT pin voltage at 18.32V with 128mA of current compliance.

- **Battery Undervoltage.** When BATT  $< 2.5V$ , the battery is in an undervoltage state. This causes the charger to reduce its current compliance to 128mA. The content of the ChargingCurrent() register is unaffected and, when the BATT voltage exceeds 2.7V, normal charging resumes. ChargingVoltage() is unaffected and can be set as low as 1.024V.

- **VDD Undervoltage.** When VDD  $< 2.5V$ , the VDD supply is in an undervoltage state, and the SMBus interface will not respond to commands. Coming out of the undervoltage condition, the part will be in its Power-On Reset state. No charging will occur when VDD is under voltage.

## SMBus Interface

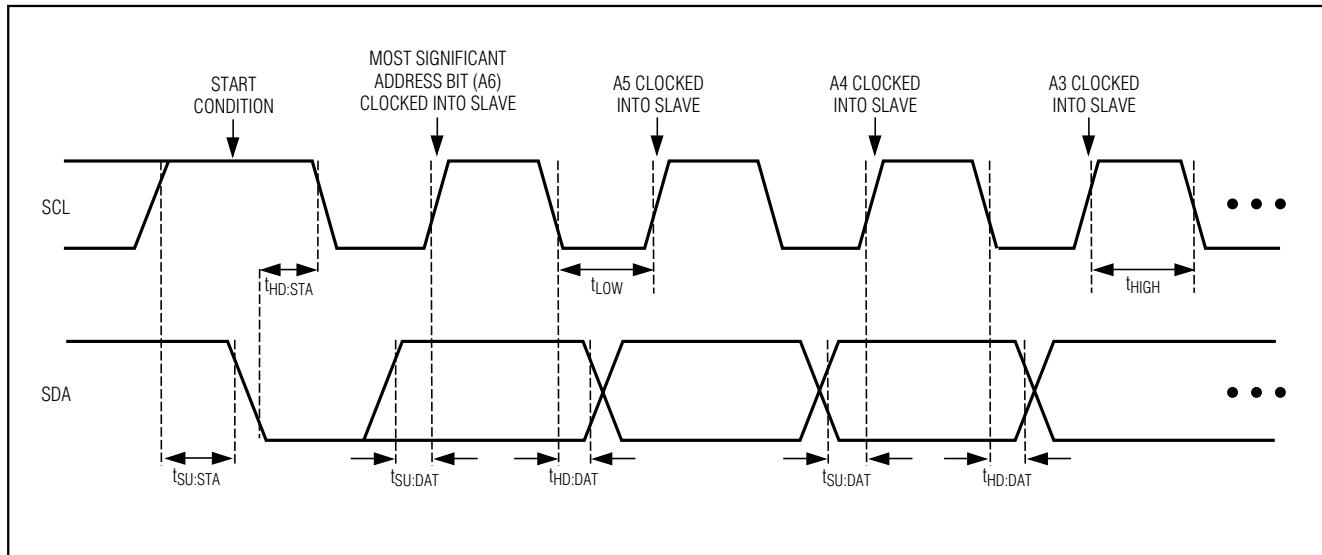

The MAX1645/MAX1645A receive control inputs from the SMBus interface. The serial interface complies with the SMBus specification (refer to the System Management Bus Specification from Intel Corporation). Charger functionality complies with the Intel/Duracell Smart Charger Specification for a Level 2 charger.

The MAX1645/MAX1645A use the SMBus Read-Word and Write-Word protocols to communicate with the battery being charged, as well as with any host system

that monitors the battery-to-charger communications as a Level 2 SMBus charger. The MAX1645/MAX1645A are SMBus slave devices and do not initiate communication on the bus. They receive commands and respond to queries for status information. Figure 3 shows examples of the SMBus Write-Word and Read-Word protocols, and Figures 4 and 5 show the SMBus serial-interface timing.

Each communication with these parts begins with the MASTER issuing a START condition that is defined as a falling edge on SDA with SCL high and ends with a STOP condition defined as a rising edge on SDA with SCL high. Between the START and STOP conditions, the device address, the command byte, and the data bytes are sent. The MAX1645/MAX1645As' device address is 0x12 and supports the charger commands as described in Tables 1–6.

## Battery Charger Commands

### ChargerSpecInfo()

The ChargerSpecInfo() command uses the Read-Word protocol (Figure 3b). The command code for ChargerSpecInfo() is 0x11 (0b00010001). Table 1 lists the functions of the data bits (D0–D15). Bit 0 refers to the D0 bit in the Read-Word protocol. The MAX1645/MAX1645A comply with level 2 Smart Battery Charger Specification Revision 1.0; therefore, the ChargerSpecInfo() command returns 0x01.

### ChargerMode()

The ChargerMode() command uses the Write-Word protocol (Figure 3a). The command code for ChargerMode() is 0x12 (0b00010010). Table 2 lists the functions of the data bits (D0–D15). Bit 0 refers to the D0 bit in the Write-Word protocol.

To charge a battery that has a thermistor impedance in the HOT range (i.e., THERMISTOR\_HOT = 1 and THERMISTOR\_UR = 0), the host must use the ChargerMode() command to clear HOT\_STOP after the battery is inserted. The HOT\_STOP bit returns to its default power-up condition ("1") whenever the battery is removed.

### ChargerStatus()

The ChargerStatus() command uses the Read-Word protocol (Figure 3b). The command code for ChargerStatus() is 0x13 (0b00010011). Table 3 describes the functions of the data bits (D0–D15). Bit 0 refers to the D0 bit in the Read-Word protocol.

The ChargerStatus() command returns information about thermistor impedance and the MAX1645/MAX1645A's internal state. The latched bits, THERMISTOR\_HOT and ALARM\_INHIBITED, are cleared when-

## **Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting**

ever BATTERY\_PRESENT = 0 or ChargerMode() is written with POR\_RESET = 1. The ALARM\_INHIBITED status bit can also be cleared by writing a new charging current OR charging voltage.

**MAX1645/MAX1645A**

| <b>a) Write-Word Format</b>                                                                                                                                                                                        |               |    |     |                                                                                                      |     |                        |               |     |                |               |     |                |      |   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----|-----|------------------------------------------------------------------------------------------------------|-----|------------------------|---------------|-----|----------------|---------------|-----|----------------|------|---|--|--|--|

| S                                                                                                                                                                                                                  | SLAVE ADDRESS | W  | ACK | COMMAND BYTE                                                                                         |     | ACK                    | LOW DATA BYTE | ACK | HIGH DATA BYTE | ACK           | P   |                |      |   |  |  |  |

|                                                                                                                                                                                                                    | 7 bits        | 1b | 1b  | 8 bits                                                                                               |     | 1b                     | 8 bits        | 1b  | 8 bits         | 1b            |     |                |      |   |  |  |  |

|                                                                                                                                                                                                                    | MSB LSB       | 0  | 0   | MSB LSB                                                                                              |     | 0                      | MSB LSB       | 0   | MSB LSB        | 0             |     |                |      |   |  |  |  |

| Preset to<br>0b0001001                                                                                                                                                                                             |               |    |     | ChargerMode() = 0x12<br>ChargingCurrent() = 0x14<br>ChargerVoltage() = 0x15<br>AlarmWarning() = 0x16 |     | D7                     | D0            | D15 | D8             |               |     |                |      |   |  |  |  |

| <b>b) Read-Word Format</b>                                                                                                                                                                                         |               |    |     |                                                                                                      |     |                        |               |     |                |               |     |                |      |   |  |  |  |

| S                                                                                                                                                                                                                  | SLAVE ADDRESS | W  | ACK | COMMAND BYTE                                                                                         | ACK | S                      | SLAVE ADDRESS | R   | ACK            | LOW DATA BYTE | ACK | HIGH DATA BYTE | NACK | P |  |  |  |

|                                                                                                                                                                                                                    | 7 bits        | 1b | 1b  | 8 bits                                                                                               | 1b  |                        | 7 bits        | 1b  | 1b             | 8 bits        | 1b  | 8 bits         | 1b   |   |  |  |  |

|                                                                                                                                                                                                                    | MSB LSB       | 0  | 0   | MSB LSB                                                                                              | 0   |                        | MSB LSB       | 1   | 0              | MSB LSB       | 0   | MSB LSB        | 1    |   |  |  |  |

| Preset to<br>0b0001001                                                                                                                                                                                             |               |    |     | ChargerSpecInfo() =<br>0x11<br>ChargerStatus() =<br>0x13                                             |     | Preset to<br>0b0001001 |               | D7  | D0             | D15           | D8  |                |      |   |  |  |  |

| Legend:<br>S = Start Condition or Repeated Start Condition<br>ACK = Acknowledge (logic low)<br>W = Write Bit (logic low)<br>P = Stop Condition<br>NACK = NOT Acknowledge (logic high)<br>R = Read Bit (logic high) |               |    |     |                                                                                                      |     |                        |               |     |                |               |     |                |      |   |  |  |  |

|  MASTER TO SLAVE<br>SLAVE TO MASTER                                                                                             |               |    |     |                                                                                                      |     |                        |               |     |                |               |     |                |      |   |  |  |  |

Figure 3. SMBus a) Write-Word and b) Read-Word Protocols

## Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

Figure 4. SMBus Serial Interface Timing—Address

Figure 5. SMBus Serial Interface Timing—Acknowledgment

## **Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting**

**Table 1. ChargerSpecInfo()**

| BIT | NAME             | DESCRIPTION                                                       |

|-----|------------------|-------------------------------------------------------------------|

| 0   | CHARGER_SPEC     | Returns a “1” for Version 1.0                                     |

| 1   | CHARGER_SPEC     | Returns a “0” for Version 1.0                                     |

| 2   | CHARGER_SPEC     | Returns a “0” for Version 1.0                                     |

| 3   | CHARGER_SPEC     | Returns a “0” for Version 1.0                                     |

| 4   | SELECTOR_SUPPORT | Returns a “0,” indicating no smart battery selector functionality |

| 5   | Reserved         | Returns a “0”                                                     |

| 6   | Reserved         | Returns a “0”                                                     |

| 7   | Reserved         | Returns a “0”                                                     |

| 8   | Reserved         | Returns a “0”                                                     |

| 9   | Reserved         | Returns a “0”                                                     |

| 10  | Reserved         | Returns a “0”                                                     |

| 11  | Reserved         | Returns a “0”                                                     |

| 12  | Reserved         | Returns a “0”                                                     |

| 13  | Reserved         | Returns a “0”                                                     |

| 14  | Reserved         | Returns a “0”                                                     |

| 15  | Reserved         | Returns a “0”                                                     |

Command: 0x11

## Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

**Table 2. ChargerMode()**

| BIT | NAME                 | DESCRIPTION                                                                                                                                                                                                            |

|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | INHIBIT_CHARGE       | 0* = Allow normal operation; clear the CHG_INHIBITED flip-flop.<br>1 = Turn off the charger; set the CHG_INHIBITED flip-flop.<br>The CHG_INHIBITED flip-flop is not affected by any other commands.                    |

| 1   | ENABLE_POLLING       | Not implemented                                                                                                                                                                                                        |

| 2   | POR_RESET            | 0 = No change.<br>1 = Change the ChargingVoltage() to 0xFFFF and the ChargingCurrent() to 0x00C0; clear the THERMISTOR_HOT and ALARM_INHIBITED flip-flops.                                                             |

| 3   | RESET_TO_ZERO        | Not implemented                                                                                                                                                                                                        |

| 4   | AC_PRESENT_MASK      | 0* = Interrupt on either edge of the AC_PRESENT status bit.<br>1 = Do not interrupt because of an AC_PRESENT bit change.                                                                                               |

| 5   | BATTERY_PRESENT_MASK | 0* = Interrupt on either edge of the BATTERY_PRESENT status bit.<br>1 = Do not interrupt because of a BATTERY_PRESENT bit change.                                                                                      |

| 6   | POWER_FAIL_MASK      | 0* = Interrupt on either edge of the POWER_FAIL status bit.<br>1 = Do not interrupt because of a POWER_FAIL bit change.                                                                                                |

| 7   |                      | Not implemented                                                                                                                                                                                                        |

| 8   |                      | Not implemented                                                                                                                                                                                                        |

| 9   |                      | Not implemented                                                                                                                                                                                                        |

| 10  | HOT_STOP             | 0 = The THERMISTOR_HOT status bit does not turn off the charger.<br>1* = The THERMISTOR_HOT status bit does turn off the charger.<br>THERMISTOR_HOT is reset by either POR_RESET or<br>BATTERY_PRESENT = 0 status bit. |

| 11  |                      | Not implemented                                                                                                                                                                                                        |

| 12  |                      | Not implemented                                                                                                                                                                                                        |

| 13  |                      | Not implemented                                                                                                                                                                                                        |

| 14  |                      | Not implemented                                                                                                                                                                                                        |

| 15  |                      | Not implemented                                                                                                                                                                                                        |

Command: 0x12

\*State at chip initial power-on (i.e.,  $V_{DD}$  from 0 to +3.3V)

# Advanced Chemistry-Independent, Level 2 Battery Chargers with Input Current Limiting

**Table 3. ChargerStatus()**

| BIT | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | CHARGE_INHIBITED | 0* = Ready to charge Smart Battery.<br>1 = Charger is inhibited, $I(chg) = 0mA$ .<br>This status bit returns the value of the CHG_INHIBITED flip-flop.                                                                                                                                                                                                                                        |

| 1   | MASTER_MODE      | Always returns "0"                                                                                                                                                                                                                                                                                                                                                                            |

| 2   | VOLTAGE_NOT_REG  | 0 = Battery voltage is limited at the set point.<br>1 = Battery voltage is less than the set point.                                                                                                                                                                                                                                                                                           |

| 3   | CURRENT_NOT_REG  | 0 = Battery current is limited at the set point.<br>1 = Battery current is less than the set point.                                                                                                                                                                                                                                                                                           |

| 4   | LEVEL_2          | Always returns a "1"                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | LEVEL_3          | Always returns a "0"                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | CURRENT_OR       | 0* = The ChargingCurrent() value is valid for the MAX1645.<br>1 = The ChargingCurrent() value exceeds the MAX1645 output range, i.e., programmed ChargingCurrent() exceeds 3008mA.                                                                                                                                                                                                            |

| 7   | VOLTAGE_OR       | 0 = The ChargingVoltage() value is valid for the MAX1645.<br>1* = The ChargingVoltage() value exceeds the MAX1645 output range, i.e., programmed ChargingVoltage() exceeds 1843mV.                                                                                                                                                                                                            |

| 8   | THERMISTOR_OR    | 0 = THM is < 91% of the reference voltage.<br>1 = THM is > 91% of the reference voltage.                                                                                                                                                                                                                                                                                                      |

| 9   | THERMISTOR_COLD  | 0 = THM is < 75.5% of the reference voltage.<br>1 = THM is > 75.5% of the reference voltage.                                                                                                                                                                                                                                                                                                  |

| 10  | THERMISTOR_HOT   | 0 = THM has not dropped to < 23.5% of the reference voltage.<br>1 = THM has dropped to < 23.5% of the reference voltage.<br>THERMISTOR_HOT flip-flop cleared by BATTERY_PRESENT = 0 or writing a "1" into the POR_RESET bit in the ChargerMode() command.                                                                                                                                     |

| 11  | THERMISTOR_UR    | 0 = THM is > 7.5% of the reference voltage.<br>1 = THM is < 7.5% of the reference voltage.                                                                                                                                                                                                                                                                                                    |

| 12  | ALARM_INHIBITED  | Returns the state of the ALARM_INHIBITED flip-flop. This flip-flop is set by either a watchdog timeout or by writing an AlarmWarning() command with bits 11, 12, 13, 14, or 15 set. This flip-flop is cleared by BATTERY_PRESENT = 0, writing a "1" into the POR_RESET bit in the ChargerMode() command, or by receiving successive ChargingVoltage() and ChargingCurrent() commands. POR: 0. |