# STPC CLIENT

# Multimedia PC on a Chip

- POWERFUL X86 PROCESSOR

- 64-BIT 66MHz BUS INTERFACE

- 64-BIT DRAM CONTROLLER

- SVGA GRAPHICS CONTROLLER

- UMA ARCHITECTURE

- VIDEO SCALER

- VIDEO OUTPUT PORT

- VIDEO INPUT PORT

- CRT CONTROLLER

- 135MHz RAMDAC

- 2 OR 3 LINE FLICKER FILTER

- SCAN CONVERTER

- PCI MASTER / SLAVE / ARBITER

- ISA MASTER/SLAVE

- IDE CONTROLLER

- DMA CONTROLLER

- INTERRUPT CONTROLLER

- TIMER / COUNTERS

- POWER MANAGEMENT

#### **DESCRIPTION**

The STPC Client integrates a fully static x86 processor, fully compatible with standard x86 processors, and combines it with powerful chipset, graphics and video pipelines to provide a single Consumer orientated PC compatible subsystem on a single device. The device is packaged in a 388 Ball Grid Array (PBGA).

### ■ X86 Processor core

- Fully static 32-bit 5-stage pipeline, x86 processor fully PC compatible.

- Can access up to 4GB of external memory.

- 8Kbyte unified instruction and data cache with write back and write through capability.

- Parallel processing integral floating point unit, with automatic power down.

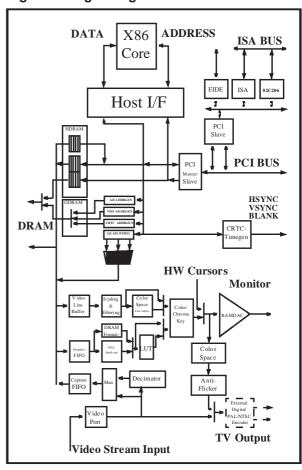

Figure 1. Logic Diagram

16/12/98 1/233

- Clock core speeds up to of 133 MHz.

- Fully static design for dynamic clock control.

- Low power and system management modes.

- Optimized design for 3.3V operation.

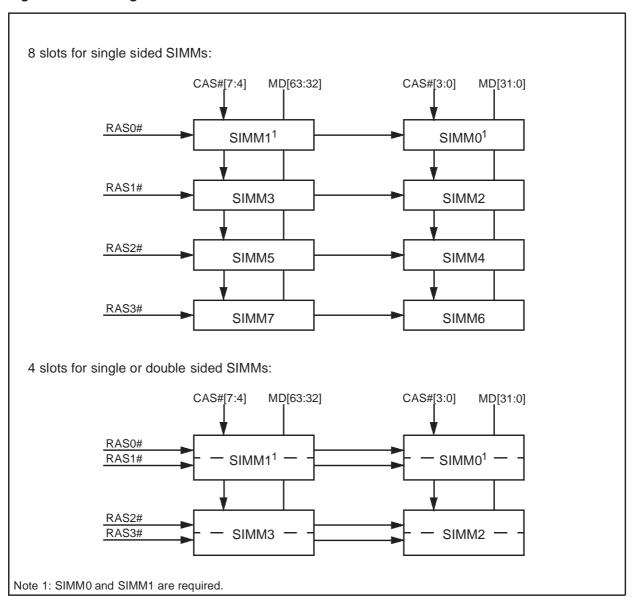

#### ■ DRAM Controller

- Integrated system memory and graphic frame memory.

- Supports up to 128 MBytes system memory in 4 banks and as little as 2Mbytes.

- Supports 4MB, 8MB, 16MB, 32MB singlesided and double-sided DRAM SIMMs.

- Four quad-word write buffers for CPU to DRAM and PCI to DRAM cycles.

- Four 4-word read buffers for PCI masters.

- Supports Fast Page Mode & EDO DRAMs.

- Programmable timing for DRAM parameters including CAS pulse width, CAS pre-charge time, and RAS to CAS delay.

- 60, 70, 80 & 100ns DRAM speeds.

- Memory hole between 1 MByte & 8 MByte supported for PCI/ISA busses.

- Hidden refresh.

# ■ Graphics Controller

- 64-bit windows accelerator.

- Backward compatibility to SVGA standards.

- Hardware acceleration for text, bitblts, transparent blts and fills.

- Up to 64 x 64 bit graphics hardware cursor.

- Up to 4MB long linear frame buffer.

- 8-, 16-, and 24-bit pixels.

- Drivers for Windows and other operating systems.

# CRT Controller

- Integrated 135MHz triple RAMDAC allowing for 1024 x 768 x 75Hz display.

- Requires external frequency synthesizer and reference sources.

- 8-, 16-, 24-bit pixels.

- Interlaced or non-interlaced output.

#### Video Pipeline

- Two-tap interpolative horizontal filter.

- Two-tap interpolative vertical filter.

- Color space conversion (RGB to YUV and YUV to RGB).

- Programmable window size.

- Chroma and color keying for integrated video overlay.

- Programmable two tap filter with gamma correction or three tap flicker filter.

- Progressive to interlaced scan converter.

#### Video Input port

- Accepts video inputs in CCIR 601/656 or ITU-R 601/656, and decodes the stream.

- Optional 2:1 decimator

- Stores captured video in off setting area of the onboard frame buffer.

- Video pass through to the onboard PAL/ NTSC encoder for full screen video images.

- HSYNC and B/T generation or lock onto external video timing source.

#### ■ PCI Controller

- Fully compliant with PCI 2.1 specification.

- Integrated PCI arbitration interface. Up to 3 masters can connect directly. External PAL allows for greater than 3 masters.

- Translation of PCI cycles to ISA bus.

- Translation of ISA master initiated cycle to

- Support for burst read/write from PCI master.

- 0.33X and 0.5X CPU clock PCI clock.

# ■ ISA master/slave

- Generates the ISA clock from either

14.318MHz oscillator clock or PCI clock

- Supports programmable extra wait state for ISA cycles

- Supports I/O recovery time for back to back I/ O cycles.

- Fast Gate A20 and Fast reset.

- Supports the single ROM that C, D, or E. blocks shares with F block BIOS ROM.

- Supports flash ROM.

- Supports ISA hidden refresh.

- Buffered DMA & ISA master cycles to reduce bandwidth utilization of the PCI and Host bus. NSP compliant.

- IDE Interface

- Supports PIO and Bus Master IDE

- Supports up to Mode 5 Timings

- Transfer Rates to 22 MBytes/sec

- Supports up to 4 IDE devices

- Concurrent channel operation (PIO & DMA modes) - 4 x 32-Bit Buffer FIFO per channel

- Support for PIO mode 3 & 4.

- Support for DMA mode 1 & 2.

- Support for 11.1/16.6 MB/s, I/O Channel Ready PIO data transfers.

- Supports 13.3/16.6 MB/s DMA data transfers

- Bus Master with scatter/gather capability

- Multi-word DMA support for fast IDE drives

- Individual drive timing for all four IDE devices

- Supports both legacy & native IDE modes

- Supports hard drives larger than 528MB

- Support for CD-ROM and tape peripherals

- Backward compatibility with IDE (ATA-1).

- Drivers for Windows and other OSes

- Integrated peripheral controller

- 2X8237/AT compatible 7-channel DMA controller.

- 2X8259/AT compatible interrupt Controller.

16 interrupt inputs ISA and PCI.

- Three 8254 compatible Timer/Counters.

- Co-processor error support logic.

# Power Management

- Four power saving modes: On, Doze, Standby, Suspend.

- Programmable system activity detector

- Supports SMM and APM.

- Supports STOPCLK.

- Supports IO trap & restart.

- Independent peripheral time-out timer to monitor hard disk, serial & parallel ports.

- Slow system clock down to 8MHz

- Slow Host clock down to 8Hz

- Slow graphic clock down to 8Hz

- Supports RTC, interrupts and DMAs wake-up

|      | Table of Contents                   |

|------|-------------------------------------|

| GENE | ERAL DESCRIPTION 9                  |

|      | TO USE THIS MANUAL                  |

| 2 1  | INTRODUCTION                        |

|      | SPECIFIC NOTES                      |

|      | DESCRIPTION                         |

|      | INTRODUCTION                        |

|      | SIGNAL DESCRIPTIONS                 |

| _    | ORY                                 |

|      |                                     |

|      | INTRODUCTION                        |

|      | MEMORY CONTROLLER                   |

|      | ADDRESS MAP                         |

|      | IO ADDRESS MAP:                     |

|      | DRAM INTERFACE                      |

| _    | CONTROLLER51                        |

|      |                                     |

|      | INTRODUCTION                        |

|      | THE EAST BRIDGE                     |

|      | THE WEST BRIDGE                     |

|      | NTERFACE                            |

|      | INTRODUCTION                        |

|      | PCI / ISA CYCLES                    |

|      | XBUS READ AND WRITE                 |

|      | FAST CPU RESET AND FAST GATE A20:74 |

| _    | ISA STANDARD REGISTERS              |

|      | ISA CONFIGURATION REGISTERS         |

|      | CONTROLLER 87                       |

|      | INTRODUCTION                        |

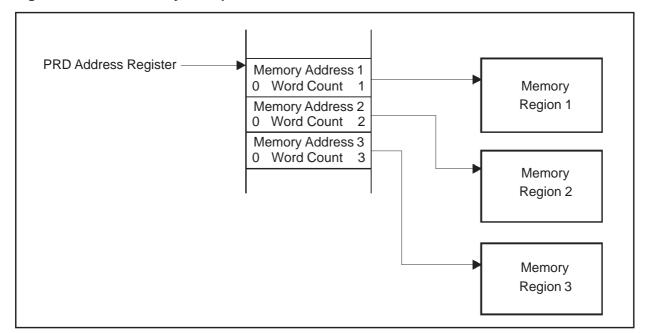

|      | PRD TABLE ENTRY                     |

|      | IDE BUS MASTER REGISTERS            |

|      | BUS MASTER IDE REGISTER DESCRIPTION |

|      | OPERATION                           |

|      | DATA SYNCHRONIZATION                |

|      | ERROR CONDITIONS                    |

|      | PCI SPECIFICS                       |

|      | CONTROLLER                          |

|      | INTRODUCTION                        |

|      | VGA CONTROLLER                      |

|      | VGA REGISTERS96                     |

|      | ADDITIONAL MODES                    |

| 8.5  | CRTC-VIDEO ARBITRATION147           |

| lable of Contents                     |     |

|---------------------------------------|-----|

| 8.6 INTERLACED MONITOR SUPPORT        | 147 |

| 8.7 RAMDAC REGISTERS                  | 148 |

| GRAPHICS ENGINE                       | 151 |

| 9.1 INTRODUCTION                      |     |

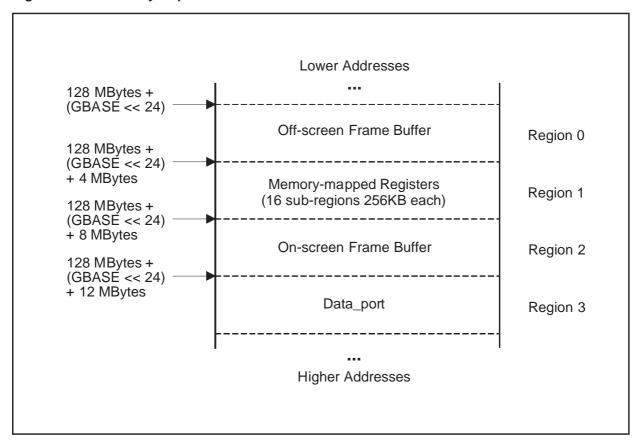

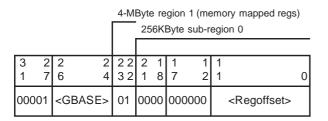

| 9.2 MEMORY ADDRESS SPACE:             | 151 |

| 9.3 DUMB FRAME BUFFER ACCESS          |     |

| 9.4 ADDRESSING                        |     |

| 9.5 VGA OPERATIONS                    |     |

| VIDEO CONTROLLER                      | 175 |

| 10.1 INTRODUCTION                     |     |

| 10.2 VIDEO INPUT PORT                 |     |

| 10.3 VIDEO INPUT MODULE ADDRESS SPACE | 178 |

| 10.4 VIP HOST PORT                    |     |

| 10.5 DMA CHANNEL OPERATION            |     |

| 10.6 VIP VIDEO INPUT PORT             |     |

| 10.7 RAW VBI DATA CAPTURE             |     |

| 10.8 VIDEO ACCELERATOR REGISTERS      |     |

| POWER MANAGEMENT                      | _   |

| 11.1 INTRODUCTION                     |     |

| 11.2 POWER MANAGEMENT REGISTERS       |     |

| ELECTRICAL SPECIFICATIONS             |     |

| 12.1 INTRODUCTION                     |     |

| 12.2 ELECTRICAL CONNECTIONS           |     |

| 12.3 ABSOLUTE MAXIMUM RATINGS         |     |

| 12.4 DC CHARACTERISTICS               |     |

| 12.5 AC CHARACTERISTICS               |     |

| MECHANICAL DATA                       | 227 |

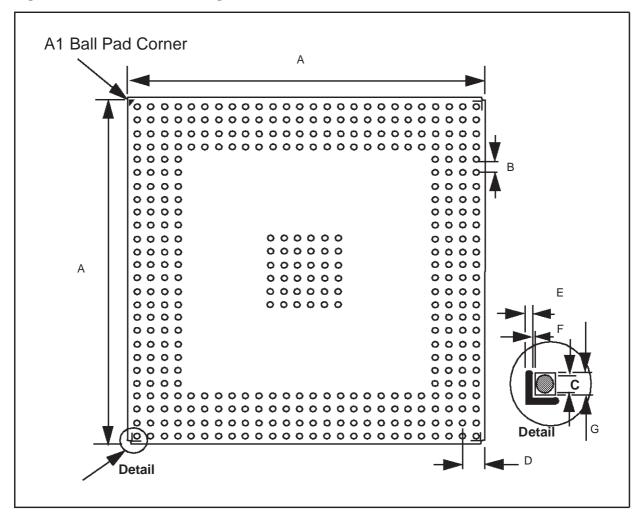

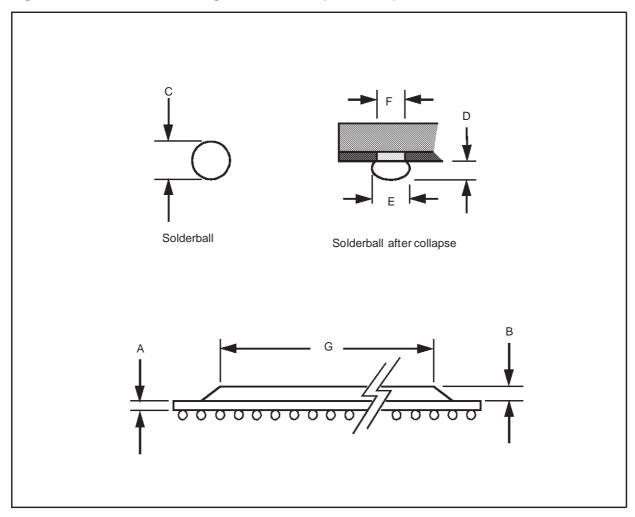

| 13.1388-PIN PACKAGE                   |     |

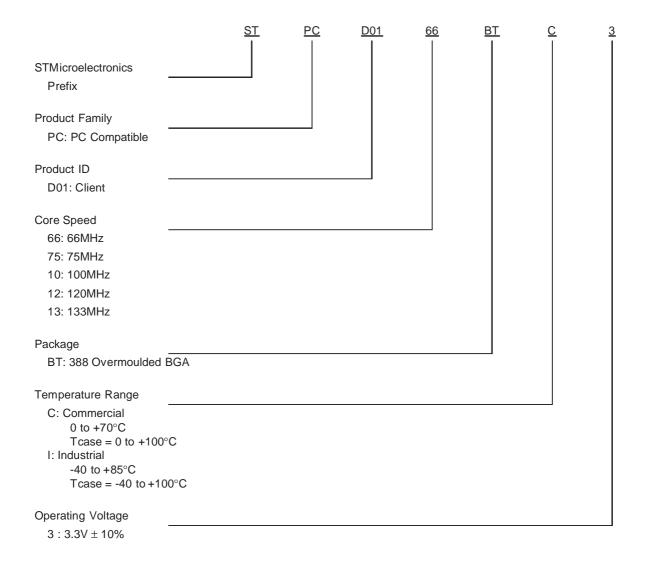

| ORDERING DATA                         | 231 |

| 14.1 ORDERING CODES                   |     |

| 14.2 AVAILABLE PART NUMBERS           |     |

| 14.3 CUSTOMER SERVICE                 |     |

# List of Figures ————

| g                                                                |

|------------------------------------------------------------------|

| Logic Diagram                                                    |

| Interfaces                                                       |

| Die Highlight                                                    |

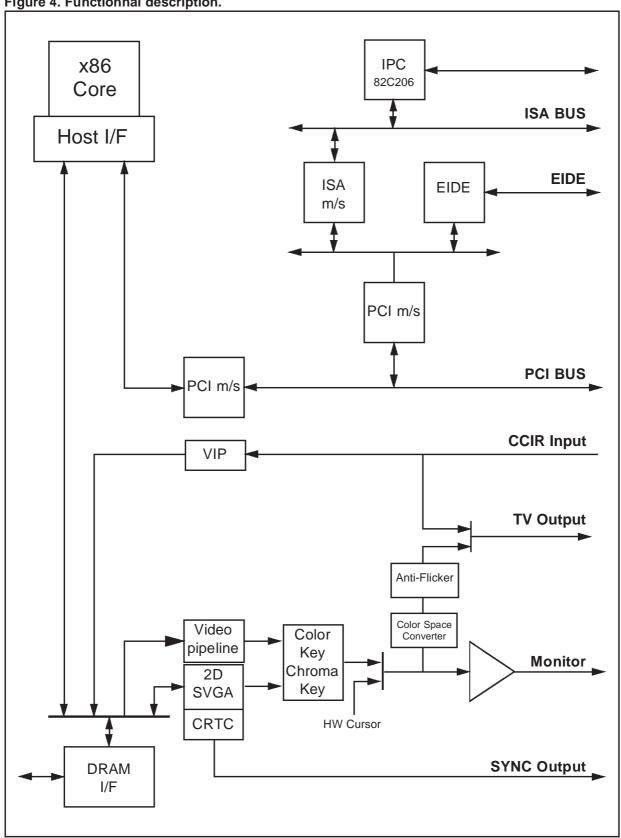

| Functionnal description                                          |

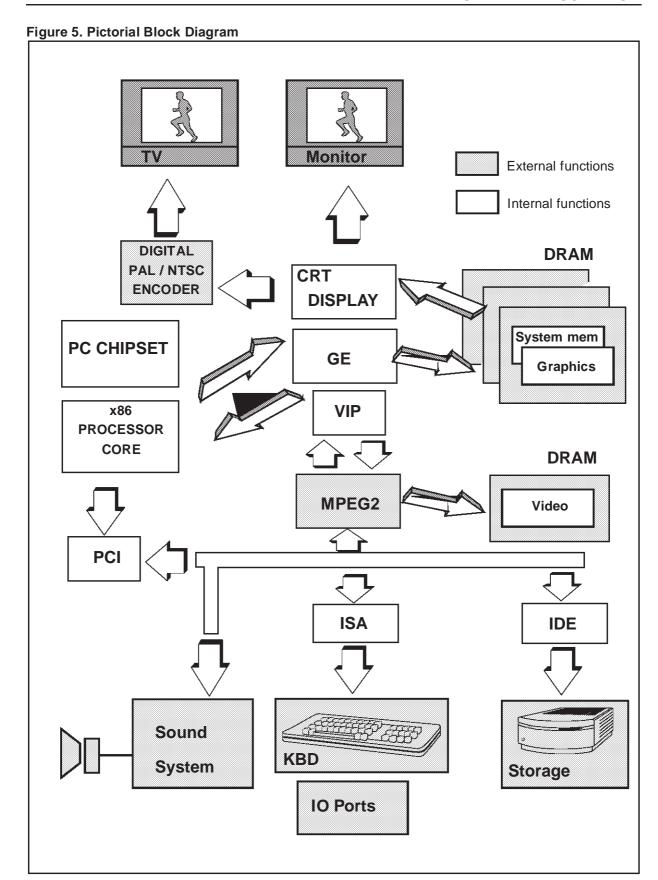

| Pictorial Block Diagram                                          |

| Typical Application                                              |

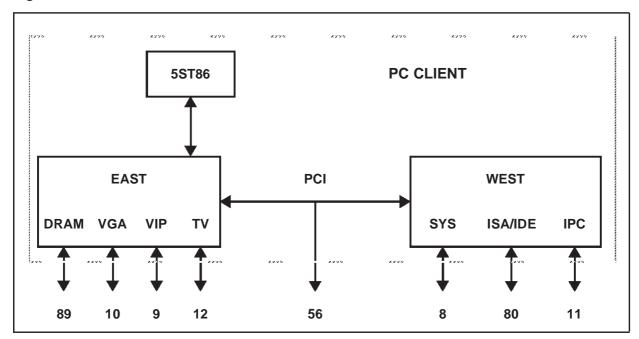

| PC Client External Interfaces                                    |

| DRAM Organisation                                                |

| PRD Table Entry Example                                          |

| GE memory Map                                                    |

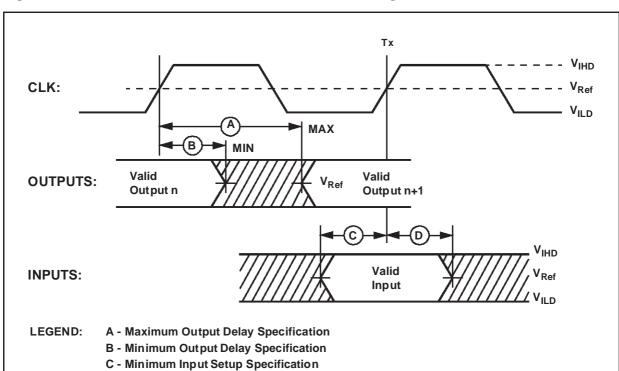

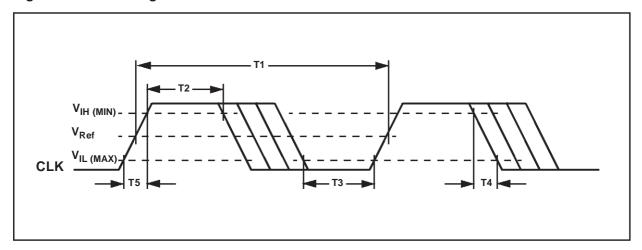

| Drive Level and Measurement Points for Switching Characteristics |

| CLK Timing Measurement Points                                    |

| 388-Pin PBGA Package - Top View                                  |

| 388-Pin PBGA Package - Dimensions                                |

| 388-Pin PRGA Package - Dimensions (Continued) 229                |

# List of Tables

| Signal Description                                               |

|------------------------------------------------------------------|

| Definition of Signal Pins                                        |

| Pinout                                                           |

| Host Address to MA Bus Mapping                                   |

| DRAM Page Mode Detect                                            |

| DRAM Speed Detect                                                |

| DMA 1 Registers                                                  |

| Interrupt Controller 1 registers                                 |

| Interval Timer registers                                         |

| Interrupt Controller 2 registers                                 |

| DMA Controller 2 registers                                       |

| DMA Page registers                                               |

| Video Input Module Address Space                                 |

| VIP Address Space                                                |

| VIP Host Control Registers                                       |

| Video Input Port Configuration Registers                         |

| Arbitration Type                                                 |

| Arbitration Priority Selection                                   |

| DMA End Byte Address (Ch1EBA, Ch2EBA)                            |

| Byte Enable Generation for the First Quad Word                   |

| Absolute Maximum Ratings                                         |

| DC Characteristics                                               |

| Drive Level and Measurement Points for Switching Characteristics |

| PCI Bus AC Timing                                                |

| IDE Bus AC Timing                                                |

| DRAM Bus AC Timing                                               |

| Video Input/TV Output AC Timing                                  |

| Graphics Adapter (VGA) AC Timing                                 |

| ISA Bus AC Timing                                                |

| PBGA388 - 388 Solder Ball Plastic 35mm x 35mm                    |

| PBGA388 - 388 Solder Ball Plastic 35mm x 35mm (Continued)        |

#### 1 GENERAL DESCRIPTION

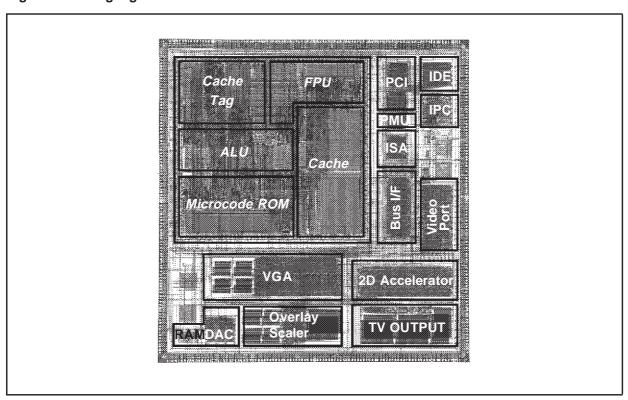

At the heart of the STPC Client is an advanced processor block, dubbed the 5ST86. The 5ST86 includes a powerful x86 processor core along with a 64-bit DRAM controller, advanced 64-bit accelerated graphics and video controller, a high speed PCI local-bus controller and Industry standard PC chip set functions (Interrupt controller, DMA Controller, Interval timer and ISA bus) and EIDE controller.

The STPC Client has in addition to the 5ST86 a Video subsystem and high quality digital Television output.

The STMicroelectronics x86 processor core is embedded with standard and application specific peripheral modules on the same silicon die. The core has all the functionality of the SGS-THOMSON standard x86 processor products, including the low power System Management Mode (SMM).

System Management Mode (SMM) provides an additional interrupt and address space that can be used for system power management or software transparent emulation of peripherals. While running in isolated SMM address space, the SMM interrupt routine can execute without interfering with the operating system or application programs.

Further power management facilities include a suspend mode that can be initiated from either hardware or software. Because of the static nature of the core, no internal data is lost.

The STPC Client makes use of a tightly coupled Unified Memory Architecture (UMA), where the same memory array is used for CPU main memory and graphics frame-buffer. This significantly reduces total system memory with system performances equal to that of a comparable solution with separate frame buffer and system memory. In addition, memory bandwidth is improved by attaching the graphics engine directly to the 64-bit processor host interface running at the speed of the processor bus rather than the traditional PCI bus.

The 64-bit wide memory array provides the system with 320MB/s peak bandwidth, double that of an equivalent system using 32 bits. This allows for higher screen resolutions and greater color depth. The processor bus runs at the speed of the processor (DX devices) or half the speed (DX2 devices).

The 'standard' PC chipset functions (DMA, interrupt controller, timers, power management logic) are integrated with the x86 processor core.

The PCI bus is the main data communication link to the STPC Client chip. The STPC Client translates appropriate host bus I/O and Memory cycles onto the PCI bus. It also supports generation of Configuration cycles on the PCI bus. The STPC Client, as a PCI bus agent (host bridge class), fully complies with PCI specification 2.1. The chip-set also implements the PCI mandatory header registers in Type 0 PCI configuration space for easy porting of PCI aware system BIOS. The device contains a PCI arbitration function for three external PCI devices.

The STPC Client integrates an ISA bus controller. Peripheral modules such as parallel and serial communications ports, keyboard controllers and additional ISA devices can be accessed by the STPC Client chip set through this bus.

An industry standard EIDE (ATA 2) controller is built in to the STPC Client and connected internally via the PCI bus.

Graphics functions are controlled by the on-chip SVGA controller and the monitor display is managed bythe 2D graphics display engine.

This Graphics Engine is tuned to work with the host CPU to provide a balanced graphics system with a low silicon area cost. It performs limited graphics drawing operations, which include hardware acceleration of text, bitblts, transparent blts and fills. These operations can operate on offscreen or on-screen areas. The frame buffer size is up to 4 Mbytes anywhere in the physical main memory.

The graphics resolution supported is a maximum of 1280x1024 in 65536 colours at 75Hz refresh rate and is VGA and SVGA compatible. Horizontal timing fields are VGA compatible while the vertical fields are extended by one bit to accommodate above display resolution.

STPC Client provides several additional functions to handle MPEG or similar video streams. The Video Input Port accepts an encoded digital video stream in one of a number of industry standard formats, decodes it, optionally decimates it by a factor of 2:1, and deposits it into an off screen area of the frame buffer. An interrupt request can be generated when an entire field or frame has been captured.

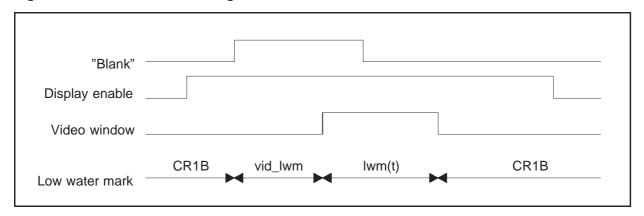

The video output pipeline incorporates a video-scaler and color space converter function and provisions in the CRT controller to display a video window. While repainting the screen the CRT controller fetches both the video as well as the normal non-video frame buffer in two separate internal FIFOs (256-bytes each). The video stream can be color-space converted (optionally) and smooth scaled. Smooth interpolative scaling in both horizontal and vertical direction are implemented. Color and Chroma key functions are also implemented to allow mixing video stream with non-video frame buffer.

The video output passes directly to the RAMDAC for monitor output or through another optional color space converter (RGB to 4:2:2 YCrCb) to the programmable anti-flicker filter. The flicker filter is configured as either a two line filter with gamma correction (primarily designed for DOS type text) or a 3 line flicker filter (primarily designed for Windows type displays). The flicker filter is optional and can be software disabled for use with large screen area's of video.

The Video output pipeline of the STPC Client interfaces directly to the external digital TV encoder (STV0119). It takes a 24 bit RGB non-interlaced pixel stream and converts to a multiplexed 4:2:2 YCrCb 8 bit output stream, the logic includes a progressive to interlaced scan converter and logic to insert appropriate CCIR656 timing reference codes into the output stream. It facilitates the high quality display of VGA or full screen video streams received via the Video input port to standard NTSC or PAL televisions.

The STPC Client core is compliant with the Advanced Power Management (APM) specification to provide a standard method by which the BIOS can control the power used by personal computers. The Power Management Unit module (PMU) controls the power consumption by providing a comprehensive set of features that control the power usage and supports compliance with the United States Environmental Protection Agency's Energy Star Computer Program. The PMU provides following hardware structures to assist the software in managing the power consumption by the system.

- System Activity Detection.

- 3 power-down timers detecting system inactivity:

- Doze timer (short durations).

- Stand-by timer (medium durations).

- Suspend timer (long durations).

- House-keeping activity detection.

- House-keeping timer to cope with short bursts of house-keeping activity while dozing or in stand-by state.

- Peripheral activity detection.

- Peripheral timer detecting peripheral inactivity

- SUSP# modulation to adjust the system performance in various power down states of the system including full power on state.

- Power control outputs to disable power from different planes of the board.

Lack of system activity for progressively longer period of times is detected by the three power down timers. These timers can generate SMI interrupts to CPU so that the SMM software can put the system in decreasing states of power consumption. Alternatively, system activity in a power down state can generate SMI interrupt to allow the software to bring the system back up to full power on state. The chip-set supports up to three power down states: Doze state, Stand-by state and Suspend mode. These correspond to decreasing levels of power savings.

Power down puts the STPC Client into suspend mode. The processor completes execution of the current instruction, any pending decoded instructions and associated bus cycles. During the suspend mode, internal clocks are stopped. removing power down, the processor resumes instruction fetching and begins execution in the instruction stream at the point it had stopped.

A reference design for the STPC Client is available including the schematics and layout files, the design is a PC ATX motherboard design. The design is available as a demonstration board for application and system development.

The STPC Client is supported by several BIOS vendors, including the super I/O device used in the reference design. Drivers for 2D accelerator, video features and EIDE are available on various operating systems.

The STPC Client has been designed using modern reusable modular design techniques, it is possible to add to or remove the standard features of the STPC Client or other variants of the 5ST86 family. Contact your local STMicroelectonics sales office for further information.

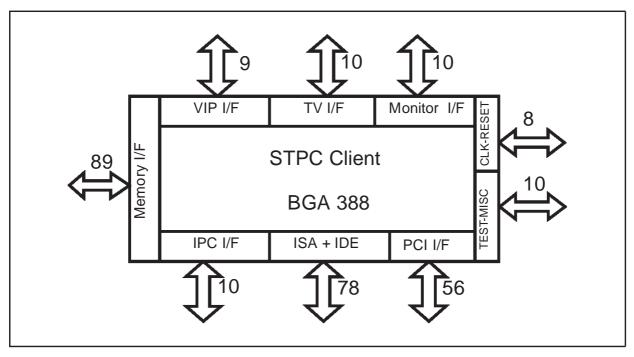

Figure 2. Interfaces

Figure 3. Die Highlight

Figure 4. Functionnal description.

Figure 6. Typical Application **Keyboard / Mouse Serial Ports** Super I/O **Parallel Port Floppy** RTC Flash 2x EIDE ISA DMUX MUX IRQ **Monitor** SVGA MUX DMA.REQ TV S-VHS **STPC Client** RGB PAL DMA.ACK NTSC STV0119 DMUX Video CCIR601 CCIR656 PCI 4x 16-bit EDO DRAMs

# 2. HOW TO USE THIS MANUAL

#### 2.1. INTRODUCTION

This manual provides full technical documentation for the STPC device. It is recommended that the reader is familiar with the x86 series processors and PC compatible architectures before reading this document. Many terms are used which related directly to the PC architecture.

#### chapters hold the information for a particular functional block of the device. For example, the chapter titled "Memory Access" gives the memory map of the STPC device, the memory architecture and interface to the external DRAM modules.

The manual itself is split into chapters. These

#### 2.2. SPECIFIC NOTES

#### 2.2.1. RESERVED BITS

Many bits in the register descriptions are noted as reserved. These bits are not internally connected, physically not present or are used for testing purposes. In all cases these bits should be set to a '0' when writing to a register with reserved bits. When reading from a register with reserved bits, these specific bits should be masked from the data value before action is taken on the data.

Any functionality found by setting the reserved bits to levels other than '0' cannot and will not be guaranteed on future revisions of the circuit design. Thus it is not recommended to use the bits marked as reserved in any way different from noted above.

#### 2.2.2. SIGNAL ACTIVE STATE

The pound symbol (#) following a signal name indicates that when the signal is in its active (asserted) state, the signal is at a logic low level. When the "#" is not present at the end of a signal name, the logic high level represents the active state.

### 2.2.3. HEX NOTATION

In this manual Hexadecimal (Hex) numbers (numbers to the base 16: [0-9,A-F]) are denoted by the postfix 'h'.

For example a memory address 7830A hexadecimal will be written 783Ah.

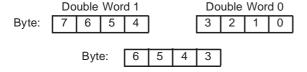

#### 2.2.4. **ENDIAN**

In common with the x86 architecture, values in memory are little-endian, that is the lower part of the memory contains the least significant byte.

For an 8-bit value

|  | N | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--|---|---|---|---|---|---|---|---|---|

|--|---|---|---|---|---|---|---|---|---|

For a 16-bit (word) value

| N   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|---|

| N+1 |   |   |   |   |   |   |   |   |

For a 24-bit value

| N   | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|----|----|----|----|

| N+1 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| N+2 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

For a 32-bit (long word) value

| N   | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|----|----|----|----|

| N+1 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| N+2 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| N+3 | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

For a 64-bit (QUAD word) value

| N   | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|----|----|----|----|

| N+1 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| N+2 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| N+3 | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

| N+4 | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

| N+5 | 47 | 46 | 45 | 44 | 43 | 42 | 41 | 40 |

| N+6 | 55 | 54 | 53 | 52 | 51 | 50 | 49 | 48 |

| N+6 | 63 | 62 | 61 | 60 | 59 | 58 | 57 | 56 |

# **3 PIN DESCRIPTION**

#### 3.1 INTRODUCTION

The STPC Client integrates most of the functionalities of the PC architecture. As a result, many of the traditional interconnections between the host PC microprocessor and the peripheral devices are totally internal to the STPC Client. This offers improved performance due to the tight coupling of the processor core and these peripherals. As a result many of the external pin connections are made directly to the on-chip peripheralfunctions.

Figure 7 shows the STPC Client's external interfaces. It defines the main busses and their function. Table 1 describes the physical implementation listing signals type and their functionality. Table 2 provides a full pin listing and description of pins. Table 3 provides a full listing of pin locations of the STPC Client package by physical connection. Please refer to the pin allocation drawing for reference.

**Table 1. Signal Description**

| Group name                                       | Qty |

|--------------------------------------------------|-----|

| Basic Clocks reset & Xtal                        | 7   |

| Memory Interface                                 | 89  |

| PCI interface                                    | 56  |

| ISA / IDE / IPC combined interface               | 88  |

| Video Input                                      | 9   |

| Video Output                                     | 10  |

| VGA Monitor interface                            | 10  |

| Grounds                                          | 69  |

| $V_{DD}$                                         | 24  |

| Analog specific V <sub>CC</sub> /V <sub>DD</sub> | 16  |

| Reserved                                         | 10  |

| Total Pin Count                                  | 388 |

**Note:** Several interface pins are multiplexed with other functions, refer to the Pin Description section for further details

Figure 7. PC Client External Interfaces

**Table 2. Definition of Signal Pins**

| Signal Name             | Dir      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Qty      |

|-------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| BASIC CLOCKS AND RES    | ETS      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •        |

| PWERGD                  |          | System Reset / Power good                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1        |

| XTALI                   | ı        | 14.3MHz Crystal Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1        |

| XTALO                   | I/O      | 14.3MHz Crystal Output - External Oscillator Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1        |

| HCLK                    | 0        | Host Clock (Test)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1        |

| DEV_CLK                 | 0        | 24MHz Peripheral Clock (floppy drive)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1        |

| GCLK2X                  | I/O      | 80MHz Graphics Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1        |

| DCLK                    | I/O      | 135MHz Dot Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1        |

| DCLK _DIR               | I        | Dot Clock Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1        |

|                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| MEMORY INTERFACE        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| MA[11:0]                | I/O      | Memory Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12       |

| RAS#[3:0]               | 0        | Row Address Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4        |

| CAS#[7:0]               | 0        | Column Address Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8        |

| MWE#                    | 0        | Write Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1        |

| MD[63:0]                | I/O      | Memory Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64       |

|                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| PCI INTERFACE           |          | Looming Dollars (Olevi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| PCI_CLKI                | <u> </u> | 33MHz PCI Input Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1        |

| PCI_CLKO                | 0        | 33MHz PCI Output Clock (from internal PLL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1        |

| AD[31:0]                | 1/0      | PCI Address / Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32       |

| CBE[3:0]                | 1/0      | Bus Commands / Byte Enables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4        |