# **Preliminary data sheet**

# LH79520 System-on-Chip

#### **FEATURES**

- · Highly Integrated System-on-Chip

- High Performance (77.4144 MHz CPU Speed)

- ARM720T™ RISC Core

- 32-bit ARM7TDMI™ RISC Core

- 8 kB Cache

- MMU (Windows CE™ Enabled)

- Write Buffer

- 32 kB On-Chip SRAM

- Flexible, Programmable Memory Interface

- SDRAM Interface

- 15-bit External Address Bus

- 32-bit External Data Bus

- Two Segments (128 MB each)

- SRAM/Flash/ROM Interface

- 26-bit External Address Bus

- 32-bit External Data Bus

- Seven Segments (64 MB Each)

- Multi-stream DMA Controller

- Four 32-bit Burst-based Data Streams

- · Clock and Power Management

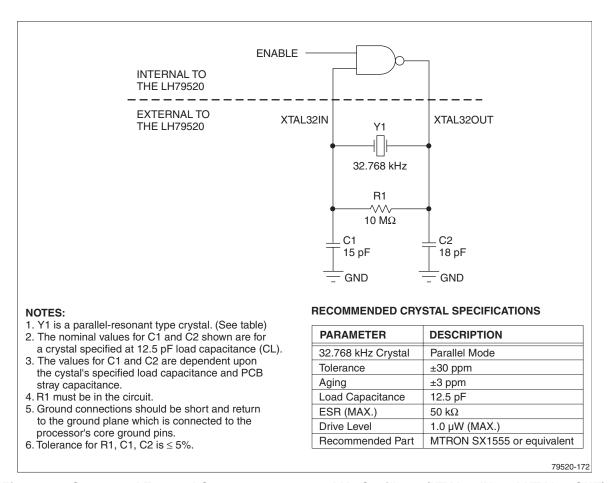

- 32.768 kHz Oscillator for Real Time Clock

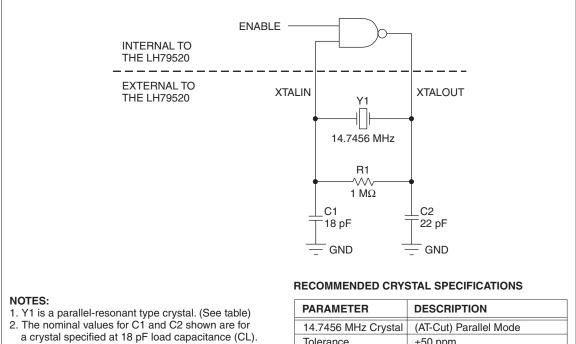

- 14.7456 MHz Oscillator and On-chip PLL for CPU and Bus Clocks

- Active, Standby, Sleep and Stop Power Modes

- Externally-supplied Clock Options

- Low Power Modes

- Active Mode: 55 mA (MAX.)

- Standby Mode: 35 mA (MAX.)

- Sleep Mode: 5.5 mA (MAX.)

- Stop Mode 2: 18 μA

- · Watchdog Timer

- Vectored Interrupt Controller

- 16 Standard and 16 Vectored IRQ Interrupts

- Hardware Interrupt Priority

- Software Interrupts

- FIQ Fast Interrupts

- Three UARTs

- 16-byte FIFOs for Rx and Tx

- IrDA SIR Support

- Supports Data Rates Up to 460.8 kb/s

- Two 16-bit Pulse Width Modulators

- · Two Dual Channel Timer Modules

- · Real Time Clock

- 32-bit Up-counter with Programmable Load

- Programmable 32-bit Match Compare Register

- 64 Programmable General Purpose I/O Signals

- Multiplexed with Peripheral I/O Signals

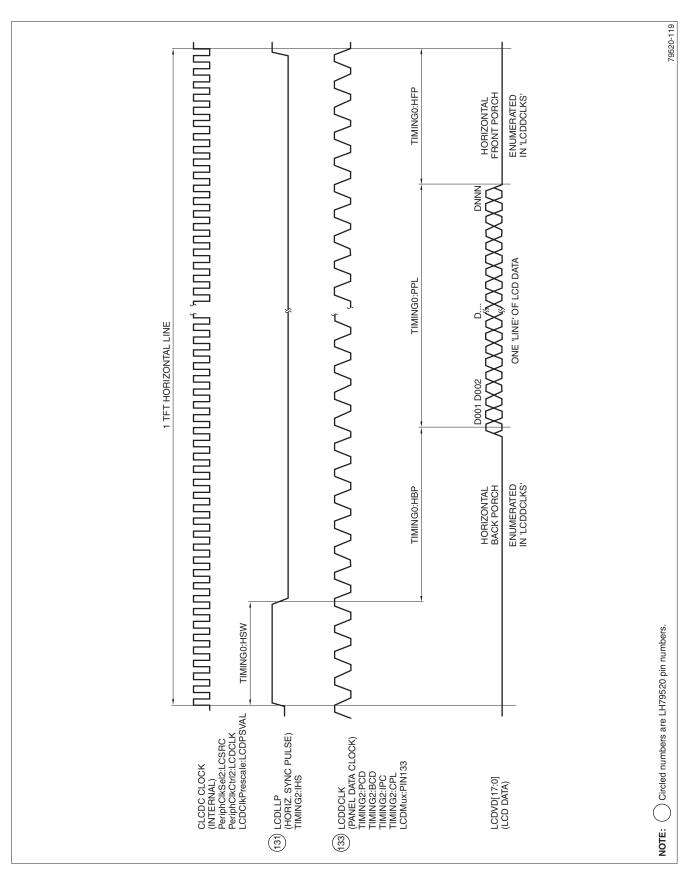

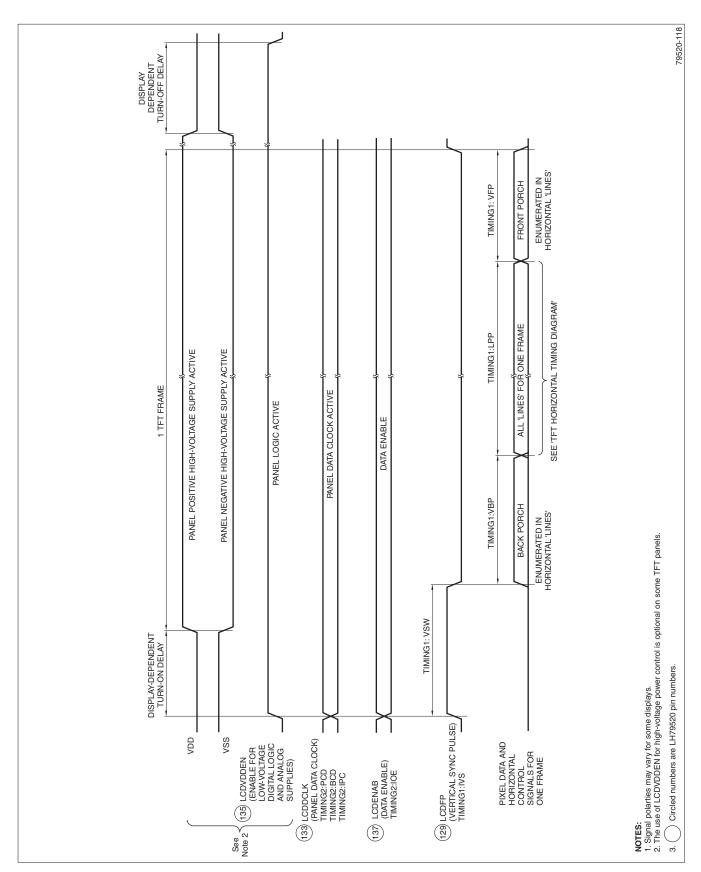

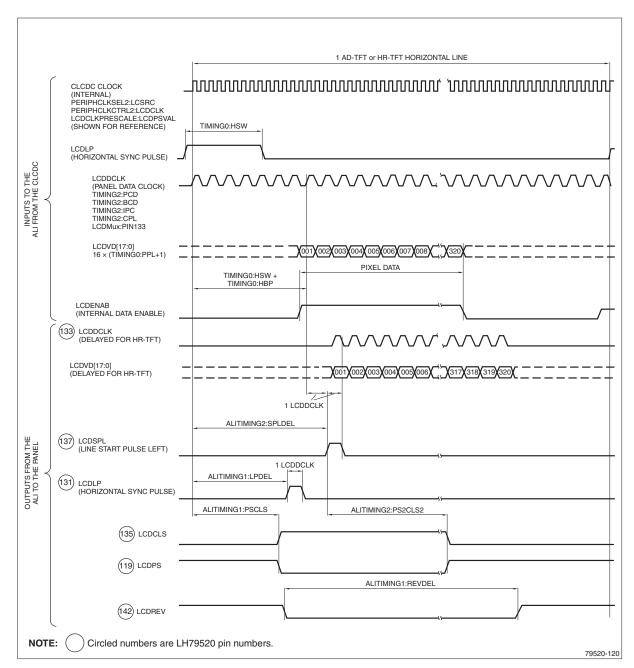

- Programmable Color LCD Controller

- Up to 800 × 600 Resolution

- Supports STN, Color STN, AD-TFT, TFT

- Supports 15 Shades of Gray

- TFT: Supports 64 k Direct Colors or 256 Colors selected from a Palette of 64,000 Colors

- Color STN: Supports 3,375 Direct Colors or 256 Colors Selected from a Palette of 3,375 Colors

- Synchronous Serial Port

- Supports Data Rates Up to 1.8452 Mb/s

- Compatible with Common Interface Schemes

- Motorola SPI™

- National Semiconductor MICROWIRE™

- Texas Instruments SSI

- JTAG Debug Interface and Boundary Scan

- 5 V Tolerant Digital I/O

- XTALIN and XTAL32IN inputs are 1.8 V  $\pm$  10 %

#### **DESCRIPTION**

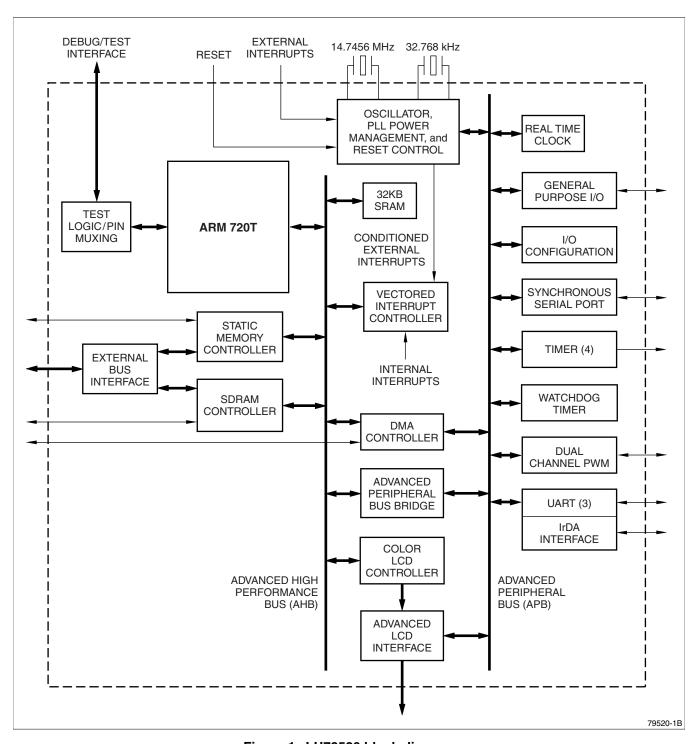

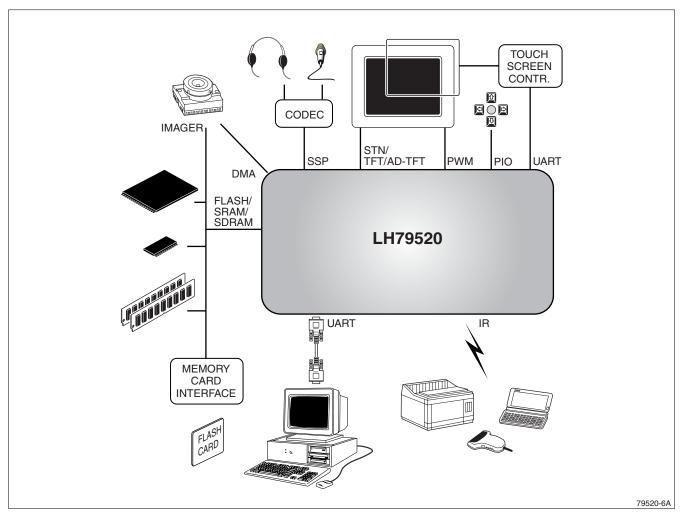

The LH79520, powered by an ARM720T, is a complete System-on-Chip with a high level of integration to satisfy a wide range of requirements and expectations. The LH79520 combines a 32-bit ARM720T RISC, Color LCD controller, Cache, Local SRAM, a number of essential peripherals such as Direct Memory Access, Serial and Parallel Interfaces, Infrared support, Timers, Real Time Clock, Watchdog Timer, Pulse Width Modulators, and an on-chip Phase Lock Loop. Debug is made simple by JTAG support.

This high level of integration lowers overall system costs, reduces development cycle time and accelerates product introduction. The LH79520's fully static design, power management unit, low voltage operation (1.8 V Core, 3.3 V I/O), on-chip PLL, fast interrupt response time, on-chip cache and SRAM, powerful instruction set, and low power RISC core provide high performance.

To build an advanced portable device, advanced processing capability is required. This capability must come with increased performance in the display system and peripherals, and yet demand less power from batteries. The LH79520 is an integrated solution to fit these needs.

# **ORDERING INFORMATION**

Table 1. Ordering information

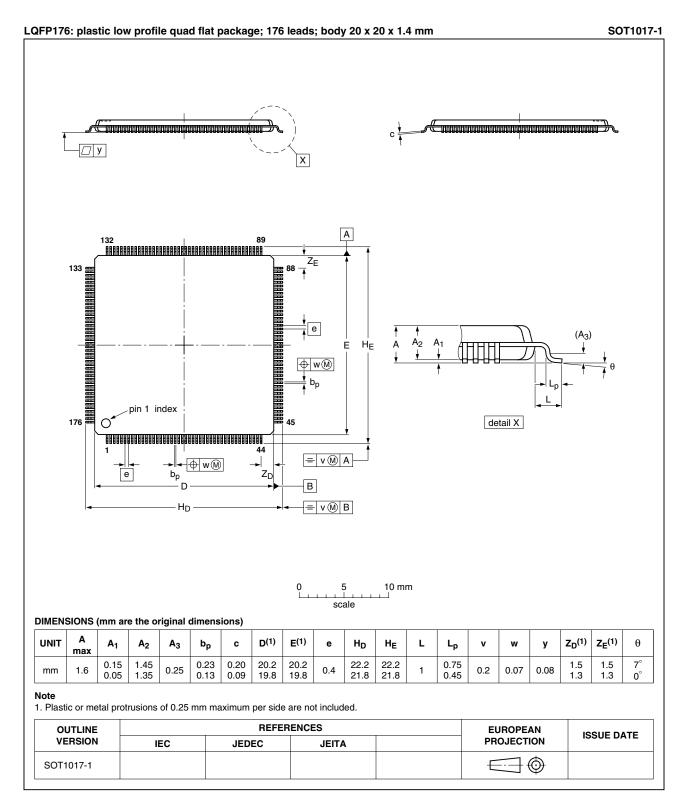

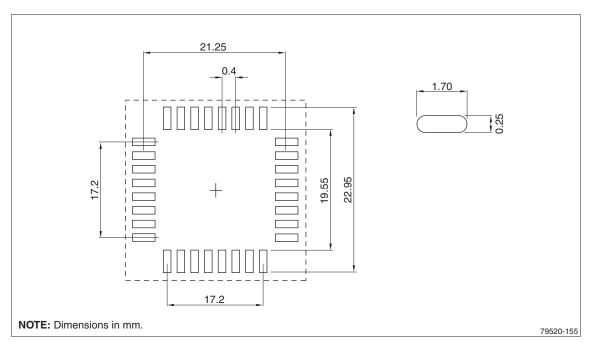

| Type number     |         | Package                                                                 | Version   |  |

|-----------------|---------|-------------------------------------------------------------------------|-----------|--|

| Type number     | Name    | Description                                                             | version   |  |

| LH79520N0Q000B1 | LQFP176 | plastic low profile quad flat package; 176 leads; body 20 x 20 x 1.4 mm | SOT1017-1 |  |

Figure 1. LH79520 block diagram

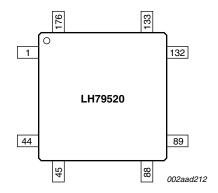

# **PIN CONFIGURATION**

Figure 2. LH79520 pin configuration

# **SIGNAL DESCRIPTIONS**

Table 2. LH79520 Signal Descriptions

| PIN NO.                                                              | SIGNAL NAME | TYPE         | DESCRIPTION                                                   | NOTES |  |  |

|----------------------------------------------------------------------|-------------|--------------|---------------------------------------------------------------|-------|--|--|

|                                                                      |             |              | MEMORY INTERFACE (MI)                                         |       |  |  |

| 2-7<br>9-12<br>14-17<br>19-22<br>24-27<br>29-32                      | A[25:0]     | Output       | Address Signals                                               |       |  |  |

| 50-54<br>56-63<br>65-66<br>67-69<br>71-74<br>76-79<br>81-84<br>86-87 | D[31:0]     | Input/Output | Data Input/Output Signals                                     | 1     |  |  |

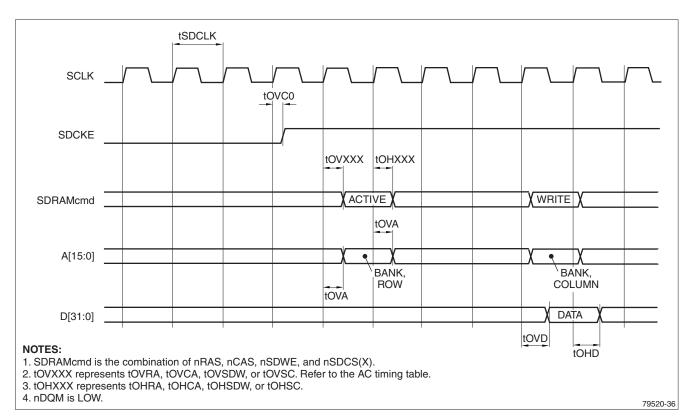

| 101                                                                  | SDCLK       | Output       | SDRAM Clock                                                   | 1     |  |  |

| 109                                                                  | DQM3        | Output       | Data Mask Output to SDRAMs                                    | 1     |  |  |

| 110                                                                  | DQM2        | Output       | Data Mask Output to SDRAMs                                    | 1     |  |  |

| 111                                                                  | DQM1        | Output       | Data Mask Output to SDRAMs                                    | 1     |  |  |

| 112                                                                  | DQM0        | Output       | Data Mask Output to SDRAMs                                    | 1     |  |  |

| 102                                                                  | SDCKE       | Output       | SDRAM Clock Enable                                            | 1     |  |  |

| 104                                                                  | nDCS1       | Output       | SDRAM Chip Select                                             | 1     |  |  |

| 105                                                                  | nDCS0       | Output       | SDRAM Chip Select                                             | 1     |  |  |

| 107                                                                  | nRAS        | Output       | Row Address Strobe                                            |       |  |  |

| 108                                                                  | nCAS        | Output       | Column Address Strobe                                         |       |  |  |

| 106                                                                  | nSDWE       | Output       | SDRAM Write Enable                                            | 1     |  |  |

| 41                                                                   | nCS6        | Output       | Static Memory Controller Chip Select                          | 1     |  |  |

| 42                                                                   | nCS5        | Output       | Static Memory Controller Chip Select                          | 1     |  |  |

| 43                                                                   | nCS4        | Output       | Static Memory Controller Chip Select                          | 1     |  |  |

| 44                                                                   | nCS3        | Output       | Static Memory Controller Chip Select                          | 1     |  |  |

| 46                                                                   | nCS2        | Output       | Static Memory Controller Chip Select                          |       |  |  |

| 47                                                                   | nCS1        | Output       | Static Memory Controller Chip Select                          |       |  |  |

| 48                                                                   | nCS0        | Output       | Static Memory Controller Chip Select                          |       |  |  |

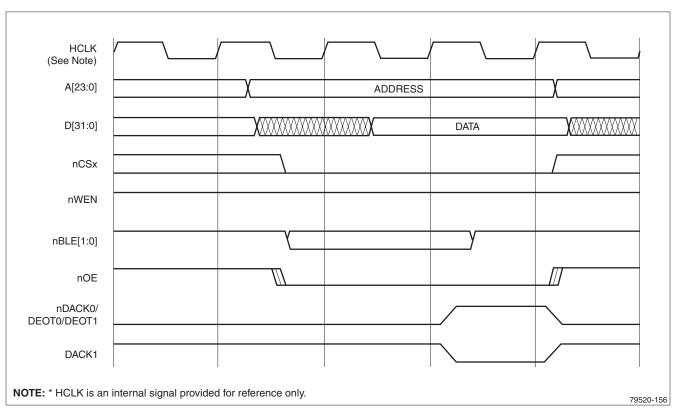

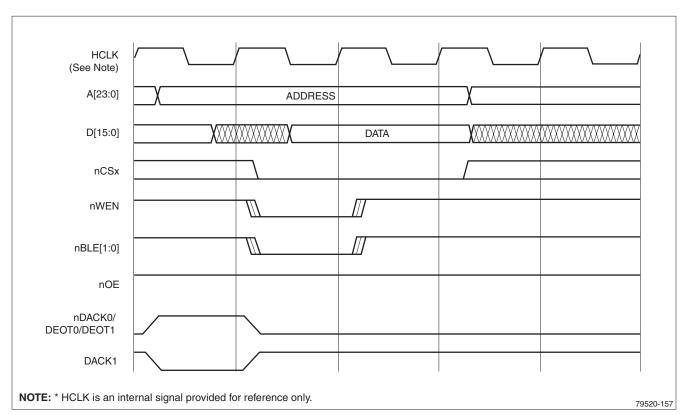

| 38                                                                   | nOE         | Output       | Static Memory Controller Output Enable                        |       |  |  |

| 34                                                                   | nBLE3       | Output       | Static Memory Controller Byte Lane Enable / Byte Write Enable | 1     |  |  |

| 35                                                                   | nBLE2       | Output       | Static Memory Controller Byte Lane Enable / Byte Write Enable | 1     |  |  |

| 36                                                                   | nBLE1       | Output       | Static Memory Controller Byte Lane Enable / Byte Write Enable |       |  |  |

| 37                                                                   | nBLE0       | Output       | Static Memory Controller Byte Lane Enable / Byte Write Enable |       |  |  |

| 39                                                                   | nWE         | Output       | Static Memory Controller Write Enable                         |       |  |  |

| 144                                                                  | nWAIT       | Input        | Static Memory Controller External Wait Control                | 1, 3  |  |  |

|                                                                      |             |              | DMA CONTROLLER (DMAC)                                         | ,     |  |  |

| 148                                                                  | DEOT0       | Output       | DMA 0 End of Transfer                                         | 1     |  |  |

| 147                                                                  | nDACK0      | Output       | DMA 0 Acknowledge                                             | 1     |  |  |

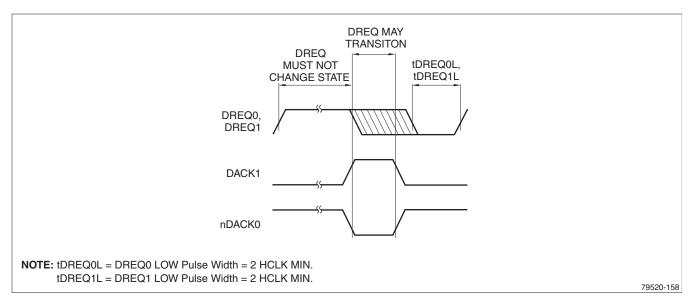

| 146                                                                  | DREQ0       | Input        | DMA 0 Request                                                 |       |  |  |

| 157                                                                  | DEOT1       | Output       | DMA 1 End of Transfer                                         | 1     |  |  |

| 145                                                                  | DACK1       | Output       | DMA 1 Acknowledge                                             | 1     |  |  |

| 144                                                                  | DREQ1       | Input        | DMA 1 Request                                                 | 1, 3  |  |  |

Table 2. LH79520 Signal Descriptions (Cont'd)

| PIN NO.                                                                                                                    | SIGNAL NAME                           | TYPE   | DESCRIPTION                                                                 | NOTES                                          |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|-----------------------------------------------------------------------------|------------------------------------------------|

|                                                                                                                            | <u>.</u>                              | C      | OLOR LCD CONTROLLER (CLCDC)                                                 | •                                              |

| 130<br>132<br>139<br>140<br>141<br>142<br>114<br>115<br>116<br>117<br>118<br>119<br>121<br>122<br>123<br>124<br>126<br>127 | LCDVD[17:0]                           | Output | LCD Panel Data bus                                                          | 1                                              |

| 137                                                                                                                        | LCDENAB                               | Output | LCD Data Enable                                                             | 1                                              |

| 129                                                                                                                        | LCDFP                                 | Output | Frame Pulse (STN), Vertical Synchronization Pulse (TFT)                     | 1                                              |

| 131                                                                                                                        | LCDLP                                 | Output | Line Synchronization Pulse (STN),<br>Horizontal Synchronization Pulse (TFT) | 1                                              |

| 133                                                                                                                        | LCDDCLK                               | Output | LCD Panel Data Clock                                                        | 1                                              |

| 134                                                                                                                        | LCDDCLKIN                             | Input  | LCD External Clock Input                                                    | 1                                              |

| 135                                                                                                                        | LCDVDDEN                              | Output | LCD Digital Supply Enable                                                   | 1                                              |

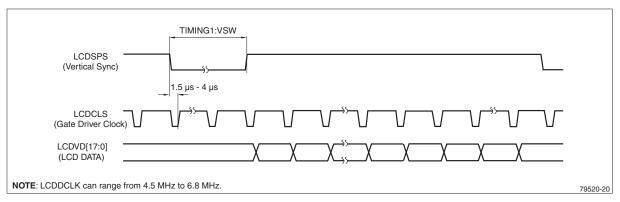

| 135                                                                                                                        | LCDCLS                                | Output | LCD Clock Signal for Gate Driver (AD-TFT, HR-TFT only)                      | 1                                              |

| 129                                                                                                                        | LCDSPS                                | Output | LCD Reset Signal for Row Display (AD-TFT, HR-TFT only)                      | 1                                              |

| 142                                                                                                                        | LCDREV                                | Output | LCD Reverse Signal (AD-TFT, HR-TFT only)                                    | 1                                              |

| 137                                                                                                                        | LCDSPL                                | Output | LCD Line Start Pulse (Left) (AD-TFT, HR-TFT only)                           | 1                                              |

| 119                                                                                                                        | LCDPS                                 | Output | LCD Power Save (AD-TFT, HR-TFT only)                                        | 1                                              |

|                                                                                                                            |                                       | S      | YNCHRONOUS SERIAL PORT (SSP)                                                | <u>,                                      </u> |

| 164                                                                                                                        | SSPFRM                                | Output | SSP Serial Frame Output                                                     | 1                                              |

| 165                                                                                                                        | SSPCLK                                | Output | SSP Clock                                                                   | 1                                              |

| 166                                                                                                                        | SSPEN                                 | Output | SSP Data Enable                                                             | 1                                              |

| 167                                                                                                                        | SSPTX                                 | Output | SSP Data Out                                                                | 1                                              |

| 169                                                                                                                        | SSPRX                                 | Input  | SSP Data In                                                                 | 1                                              |

|                                                                                                                            |                                       |        | PULSE WIDTH MODULATOR (PWM)                                                 |                                                |

| 150                                                                                                                        | PWM0                                  | Output | PWM0 Output                                                                 | 1                                              |

| 151                                                                                                                        | PWMSYNC0                              | Input  | PWM0 Synchronizing Input                                                    | 1                                              |

| 157                                                                                                                        | PWM1                                  | Output | PWM1 Output                                                                 | 1                                              |

|                                                                                                                            | · · · · · · · · · · · · · · · · · · · |        | UARTO (U0)                                                                  | <u> </u>                                       |

| 163                                                                                                                        | UARTRX0                               | Input  | UARTO Received Serial Data Input                                            | 1                                              |

| 162                                                                                                                        | UARTTX0                               | Output | UART0 Transmitted Serial Data Output                                        | 1                                              |

| 163                                                                                                                        | UARTIRRX0                             | Input  | UARTO InfraRed Receive                                                      | 1                                              |

| 162                                                                                                                        | UARTIRTX0                             | Output | UART0 InfraRed Transmit                                                     | 1                                              |

Table 2. LH79520 Signal Descriptions (Cont'd)

| PIN NO.    | SIGNAL NAME | TYPE                                 | DESCRIPTION                                                                           | NOTES |

|------------|-------------|--------------------------------------|---------------------------------------------------------------------------------------|-------|

|            | <u>'</u>    | <u> </u>                             | UART1 (U1)                                                                            | •     |

| 160        | UARTRX1     | Input                                | UART1 Received Serial Data Input                                                      | 1     |

| 159        | UARTTX1     | Output                               | UART1 Transmitted Serial Data Output                                                  | 1     |

|            |             | I                                    | UART2 (U2)                                                                            |       |

| 169        | UARTRX2     | Input                                | UART2 Received Serial Data Input                                                      | 1     |

| 167        | UARTTX2     | UART2 Transmitted Serial Data Output | 1                                                                                     |       |

|            | 1           | GENE                                 | RAL PURPOSE INPUT/OUTPUT (GPIO)                                                       | II.   |

| 153        | PA7         |                                      |                                                                                       |       |

| 155<br>156 | PA6<br>PA5  |                                      |                                                                                       |       |

| 159        | PA4         |                                      |                                                                                       |       |

| 160        | PA3         | Input/Output                         | General Purpose I/O Signals - Port A                                                  | 1     |

| 164        | PA2         |                                      |                                                                                       |       |

| 165<br>166 | PA1<br>PA0  |                                      |                                                                                       |       |

| 139        | PB7         |                                      |                                                                                       |       |

| 140        | PB6         |                                      |                                                                                       |       |

| 141        | PB5         |                                      |                                                                                       |       |

| 142        | PB4         | Input/Output                         | General Purpose I/O Signals - Port B                                                  | 1     |

| 146<br>147 | PB3<br>PB2  | 1                                    | 3                                                                                     |       |

| 148        | PB1         |                                      |                                                                                       |       |

| 152        | PB0         |                                      |                                                                                       |       |

| 129        | PC7         |                                      |                                                                                       |       |

| 130        | PC6         |                                      |                                                                                       |       |

| 131<br>132 | PC5<br>PC4  |                                      |                                                                                       |       |

| 133        | PC3         | Input/Output                         | General Purpose I/O Signals - Port C                                                  | 1     |

| 134        | PC2         |                                      |                                                                                       |       |

| 135        | PC1         |                                      |                                                                                       |       |

| 137        | PC0         |                                      |                                                                                       |       |

| 116<br>117 | PD7<br>PD6  |                                      |                                                                                       |       |

| 118        | PD5         |                                      |                                                                                       |       |

| 119        | PD4         | Input/Output                         | General Purpose I/O Signals - Port D                                                  | 1     |

| 121        | PD3         | input Gatpat                         | deficial i dipose i/o digitals i off b                                                | '     |

| 122<br>123 | PD2<br>PD1  |                                      |                                                                                       |       |

| 124        | PD0         |                                      |                                                                                       |       |

| 102        | PE7         |                                      |                                                                                       |       |

| 104        | PE6         |                                      |                                                                                       |       |

| 105<br>106 | PE5<br>PE4  |                                      |                                                                                       |       |

| 109        | PE3         | Input/Output                         | General Purpose I/O Signals - Port E                                                  | 1     |

| 110        | PE2         |                                      |                                                                                       |       |

| 111<br>112 | PE1<br>PE0  |                                      |                                                                                       |       |

|            | PF7         |                                      |                                                                                       |       |

| 61<br>62   | PF6         |                                      |                                                                                       |       |

| 63         | PF5         |                                      | Caparal Purposa I/O Signals - Port F                                                  |       |

| 65         | PF4         | Input/Output                         | General Purpose I/O Signals - Port F. GPIO PF1 is only available when CLKINSEL is '0' | 1     |

| 66<br>67   | PF3<br>PF2  | pas Garpar                           | (i.e. the external clock source is not being used).                                   |       |

| 99         | PF1         |                                      |                                                                                       |       |

| 101        | PF0         |                                      |                                                                                       |       |

|            | 1           |                                      |                                                                                       | 1     |

Table 2. LH79520 Signal Descriptions (Cont'd)

| PG7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN NO. | SIGNAL NAME | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NOTES  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| FG6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |             | <del>-</del> | 2200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.0.29 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | -           |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Fig.   Fig.  |         |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Fig.   Fig.  |         |             | Input/Output | General Purpose I/O Signals - Port G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1      |

| FG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59      |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Add   PH2   S0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |             | Input/Output | General Purpose I/O Signals - Port H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1      |

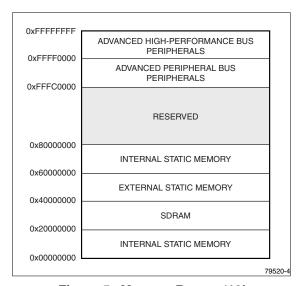

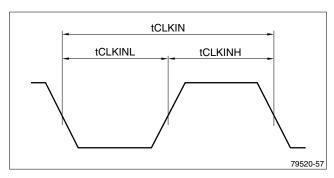

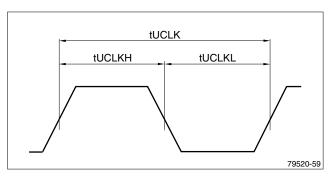

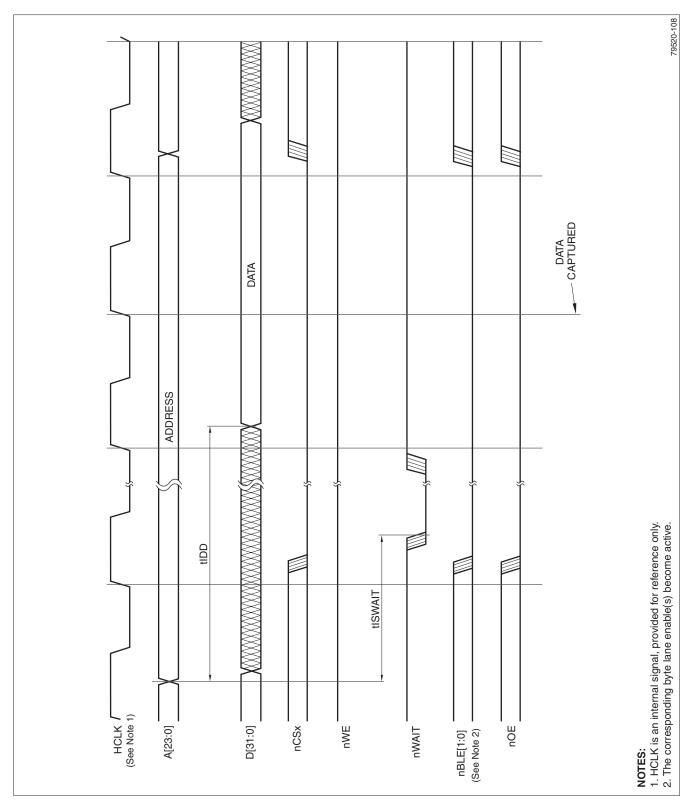

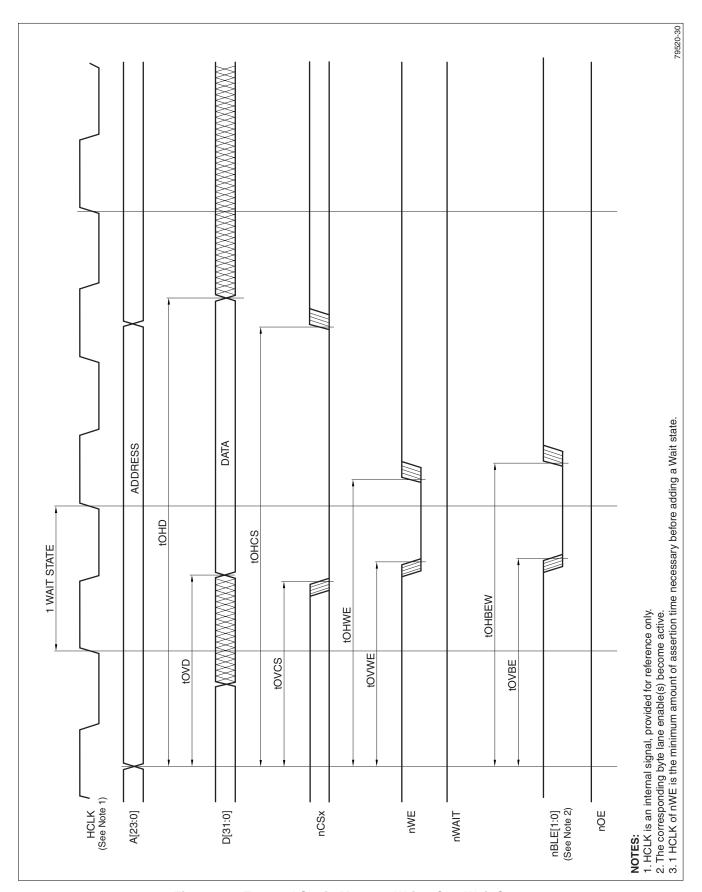

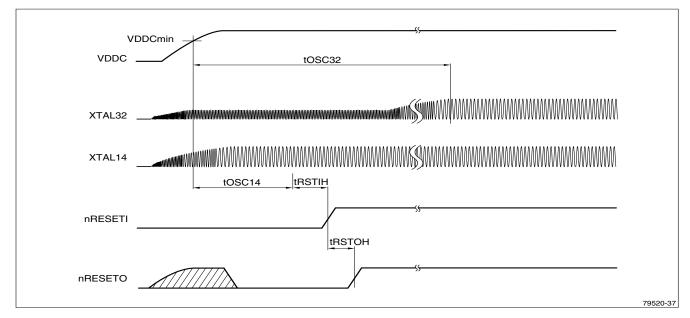

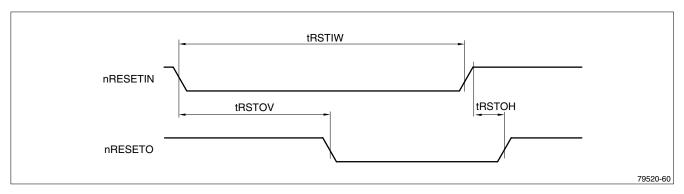

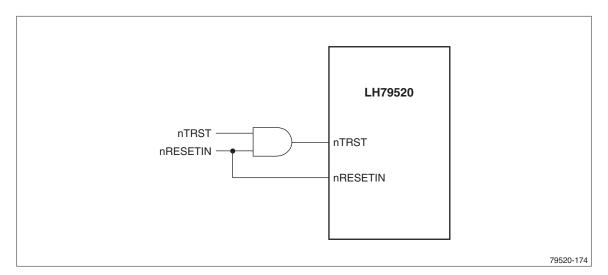

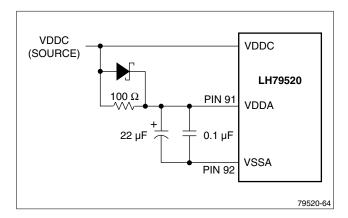

| Sol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |             |              | and the second of the second o |        |