# Intel<sup>®</sup> E7320 Memory Controller Hub (MCH) Datasheet

**Datasheet**

February 2005

Document Number: 303007-002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "Reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® E7320 MCH may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel, Intel Xeon, Intel NetBurst, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2004-2005, Intel Corporation

| 1 | Introd | uction     |                                                                   | 15 |

|---|--------|------------|-------------------------------------------------------------------|----|

|   | 1.1    | Termino    | ology                                                             | 15 |

|   | 1.2    |            | ice Documentation                                                 |    |

|   | 1.3    |            | 7320 MCH System Architecture                                      |    |

|   |        | 1.3.1      | 64-bit Intel <sup>®</sup> Xeon™ Processor with 800 MHz System Bus |    |

|   |        |            | (1 MB and 2 MB L2 Cache Versions)                                 | 18 |

|   |        | 1.3.2      | Memory Subsystem                                                  | 18 |

|   |        | 1.3.3      | PCI Express*                                                      | 19 |

|   |        | 1.3.4      | Hub Interface 1.5                                                 | 19 |

|   |        | 1.3.5      | Intel® 6700PXH 64-bit PCI Hub                                     | 19 |

|   |        | 1.3.6      | Platform Summary                                                  | 20 |

| 2 | Signa  | l Descript | ion                                                               | 21 |

|   | 2.1    | System     | Bus Interface Signals                                             | 21 |

|   | 2.2    |            | terface A Signals                                                 |    |

|   | 2.3    | DDR Int    | terface B Signals                                                 | 25 |

|   | 2.4    | DDR Int    | terface Shared Signals                                            | 25 |

|   | 2.5    | PCI Exp    | press Interface Port A Signals                                    | 26 |

|   | 2.6    | PCI Exp    | press Interface Signals                                           | 27 |

|   | 2.7    | Hub Inte   | erface Signals                                                    | 27 |

|   | 2.8    | Reset, F   | Power, and Miscellaneous Signals                                  | 27 |

| 3 | Regis  | ter Descri | iptions                                                           | 31 |

|   | 3.1    | Registe    | r Terminology                                                     | 31 |

|   |        | 3.1.1      | Platform Configuration                                            |    |

|   | 3.2    | Genera     | Routing Configuration Accesses                                    | 33 |

|   |        | 3.2.1      | Standard PCI Bus Configuration Mechanism                          |    |

|   |        | 3.2.2      | Logical PCI Bus 0 Configuration Mechanism                         |    |

|   |        | 3.2.3      | Primary PCI and Downstream Configuration Mechanism                | 35 |

|   |        | 3.2.4      | PCI Express Bus Configuration Mechanism                           | 35 |

|   | 3.3    | I/O Map    | ped Registers                                                     |    |

|   |        | 3.3.1      | CONFIG_ADDRESS - Configuration Address Register                   | 36 |

|   |        | 3.3.2      | CONFIG_DATA - Configuration Data Register                         |    |

|   | 3.4    | PCI Exp    | press Enhanced Configuration Mechanisms                           | 37 |

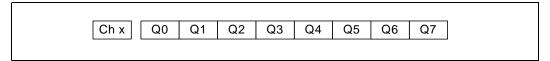

|   |        | 3.4.1      | PCI Express Configuration Transaction Header                      | 38 |

|   |        | 3.4.2      | Enhanced Configuration Memory Address Map                         | 38 |

|   | 3.5    | MCH Co     | ontrol Registers (D0:F0)                                          | 39 |

|   |        | 3.5.1      | VID – Vendor Identification (D0:F0)                               | 40 |

|   |        | 3.5.2      | DID – Device Identification (D0:F0)                               | 40 |

|   |        | 3.5.3      | PCICMD – PCI Command Register (D0:F0)                             | 41 |

|   |        | 3.5.4      | PCISTS – PCI Status Register (D0:F0)                              | 41 |

|   |        | 3.5.5      | RID – Revision Identification (D0:F0)                             |    |

|   |        | 3.5.6      | SUBC – Sub-Class Code (D0:F0)                                     | 43 |

|   |        | 3.5.7      | BCC – Base Class Code (D0:F0)                                     | 43 |

|   |        | 3.5.8      | MLT – Master Latency Timer (D0:F0)                                | 44 |

|   |        | 3.5.9      | HDR – Header Type (D0:F0)                                         |    |

|   |        | 3.5.10     | SVID – Subsystem Vendor Identification (D0:F0)                    |    |

|   |        | 3.5.11     | SID – Subsystem Identification (D0:F0)                            | 44 |

|   |        | 3.5.12     | CAPPTR – Capabilities Pointer (D0:F0)                             | 45 |

|   |        | 3.5.13     | MCHCFG0 – MCH Configuration 0 (D0:F0)                             | 45 |

|   |        | 3.5.14     | MCHSCRB – MCH Memory Scrub and Initialization                     |    |

|   |        |            | Configuration Register (D0:F0)                                    | 46 |

|     | 3.5.15 | FDHC - Fixed DRAM Hole Control (D0:F0)                          |     |

|-----|--------|-----------------------------------------------------------------|-----|

|     | 3.5.16 | PAM 0:6 – Programmable Attribute Map Registers 0 – 6 (D0:F0)    | 47  |

|     | 3.5.17 | DRB 0:7 – DRAM Row Boundary Register 0 - 7 (D0:F0)              | 49  |

|     | 3.5.18 | DRA 0:3 – DRAM Row Attribute Register 0 - 3 (D0:F0)             |     |

|     | 3.5.19 | DRT – DRAM Timing Register (D0:F0)                              | 52  |

|     | 3.5.20 | DRC – DRAM Controller Mode Register (D0:F0)                     |     |

|     | 3.5.21 | DRM – DRAM Mapping Register (D0:F0)                             |     |

|     | 3.5.22 | DRORC – Opportunistic Refresh Control Register (D0:F0)          |     |

|     | 3.5.23 | ECCDIAG – ECC Detection /Correction Diagnostic Register (D0:F0) |     |

|     | 3.5.24 | SDRC – DDR SDRAM Secondary Control Register (D0:F0)             |     |

|     | 3.5.25 | CKDIS – CK/CK# Disable Register (D0:F0)                         |     |

|     | 3.5.26 | CKEDIS – CKE/CKE# Disable Register (D0:F0)                      |     |

|     | 3.5.27 | DDRCSR – DDR Channel Configuration Control/Status               | 0 1 |

|     | 3.3.21 | Register (D0:F0)                                                | 61  |

|     | 2 5 20 | DEVPRES – Device Present (D0:F0)                                | 01  |

|     | 3.5.28 |                                                                 |     |

|     | 3.5.29 | ESMRC – Extended System Management RAM Control (D0:F0)          |     |

|     | 3.5.30 | SMRC – System Management RAM Control Register (D0:F0)           |     |

|     | 3.5.31 | EXSMRC – Expansion System Management RAM Control (D0:F0)        |     |

|     | 3.5.32 | DDR2ODTC – DDR2 ODT Control Register (D0:F0)                    |     |

|     | 3.5.33 | TOLM – Top of Low Memory Register (D0:F0)                       |     |

|     | 3.5.34 | REMAPBASE - Remap Base Address Register (D0:F0)                 |     |

|     | 3.5.35 | REMAPLIMIT – Remap Limit Address Register (D0:F0)               | 67  |

|     | 3.5.36 | REMAPOFFSET – Remap Offset (D0:F0)                              |     |

|     | 3.5.37 | TOM – Top of Memory Register (D0:F0)                            | 68  |

|     | 3.5.38 | EXPECBASE – PCI Express Enhanced Configuration Base             |     |

|     |        | Address Register (D0:F0)                                        |     |

|     | 3.5.39 | CACHECTL – Write Cache Control Register (D0:F0)                 |     |

|     | 3.5.40 | SKPD – Scratchpad Data (D0:F0)                                  |     |

|     | 3.5.41 | DEVPRES1 – Device Present 1 Register (D0:F0)                    | 69  |

|     | 3.5.42 | MCHTST - MCH Test Register (D0:F0)                              | 70  |

| 3.6 | MCH E  | rror Reporting Registers (D0:F1)                                | 70  |

|     | 3.6.1  | VID – Vendor Identification (D0:F1)                             | 72  |

|     | 3.6.2  | DID – Device Identification (D0:F1)                             | 72  |

|     | 3.6.3  | PCICMD – PCI Command Register (D0:F1)                           | 73  |

|     | 3.6.4  | PCISTS – PCI Status Register (D0:F1)                            |     |

|     | 3.6.5  | RID – Revision Identification (D0:F1)                           |     |

|     | 3.6.6  | SUBC – Sub-Class Code (D0:F1)                                   |     |

|     | 3.6.7  | BCC – Base Class Code (D0:F1)                                   |     |

|     | 3.6.8  | MLT – Master Latency Timer (D0:F1)                              |     |

|     | 3.6.9  | HDR – Header Type (D0:F1)                                       |     |

|     | 3.6.10 | SVID – Subsystem Vendor Identification (D0:F1)                  |     |

|     | 3.6.11 | SID – Subsystem Identification (D0:F1)                          |     |

|     | 3.6.12 | FERR_GLOBAL – Global First Error Register (D0:F1)               |     |

|     | 3.6.13 | NERR_GLOBAL – Global Next Error Register (D0:F1)                |     |

|     | 3.6.14 | HI_FERR – Hub Interface First Error Register (D0:F1)            |     |

|     | 3.6.15 | HI_NERR – Hub Interface Next Error Register (D0:F1)             |     |

|     | 3.6.16 | HI_ERRMASK – Hub Interface Error Mask Register (D0:F1)          |     |

|     | 3.6.17 | HI_SCICMD – Hub Interface SCI Command Register (D0:F1)          |     |

|     |        | HI_SMICMD – Hub Interface SMI Command Register (D0:F1)          |     |

|     | 3.6.18 |                                                                 |     |

|     | 3.6.19 | HI_SERRCMD – Hub Interface SERR Command Register (D0:F1)        |     |

|     | 3.6.20 | HI_MCERRCMD – Hub Interface MCERR# Register (D0:F1)             |     |

|     | 3.6.21 | SYSBUS_FERR – System Bus First Error Register (D0:F1)           |     |

|     | 3.6.22 | SYSBUS_NERR – System Bus Next Error Register (D0:F1)            |     |

|     | 3.6.23 | SYSBUS_ERRMASK – System Bus Error Mask Register (D0:F1)         |     |

|     | 3.6.24 | SYSBUS_SCICMD – System Bus SCI Command Register (D0:F1)         |     |

|     | 3.6.25 | SYSBUS_SMICMD – System Bus SMI Command Register (D0:F1)         | 86  |

| 3.6.26 | SYSBUS_SERRCMD – System Bus SERR Command                  |      |

|--------|-----------------------------------------------------------|------|

|        | Register (D0:F1)                                          | 88   |

| 3.6.27 | SYSBUS_MCERRCMD – System Bus MCERR# Command               |      |

|        | Register (D0:F1)                                          | 89   |

| 3.6.28 | BUF_FERR – Memory Buffer First Error Register (D0:F1)     |      |

| 3.6.29 | BUF_NERR – Memory Buffer Next Error Register (D0:F1)      |      |

| 3.6.30 | BUF_ERRMASK – Memory Buffer Error Mask Register (D0:F1)   |      |

| 3.6.31 | BUF_SCICMD – Memory Buffer SCI Command Register (D0:F1)   |      |

| 3.6.32 | BUF_SMICMD – Memory Buffer SMI Command Register (D0:F1)   |      |

| 3.6.33 | BUF_SERRCMD – Memory Buffer SERR Command                  |      |

| 0.0.00 | Register (D0:F1)                                          | 94   |

| 3.6.34 | BUF_MCERRCMD – Memory Buffer MCERR# Command               |      |

| 0.0.0  | Register (D0:F1)                                          | 94   |

| 3.6.35 | DRAM_FERR – DRAM First Error Register (D0:F1)             |      |

| 3.6.36 | DRAM_NERR – DRAM Next Error Register (D0:F1)              |      |

| 3.6.37 | DRAM_ERRMASK – DRAM Error Mask Register (D0:F1)           |      |

| 3.6.38 | DRAM_SCICMD – DRAM SCI Command Register (D0:F1)           |      |

| 3.6.39 | DRAM_SMICMD – DRAM SMI Command Register (D0:F1)           |      |

| 3.6.40 | DRAM_SERRCMD – DRAM SERR Command Register (D0:F1)         |      |

| 3.6.41 | DRAM_MCERRCMD – DRAM MCERR# Command                       | 100  |

| 3.0.41 | Register (D0:F1)                                          | 101  |

| 3.6.42 | THRESH_SEC0 – DIMM0 SEC Threshold Register (D0:F1)        |      |

| 3.6.43 | THRESH_SEC1 – DIMM1 SEC Threshold Register (D0:F1)        |      |

| 3.6.44 | THRESH_SEC1 - DIMM1 SEC Threshold Register (D0.F1)        |      |

|        |                                                           |      |

| 3.6.45 | THRESH_SEC3 – DIMM3 SEC Threshold Register (D0:F1)        | 103  |

| 3.6.46 | DRAM_SEC1_ADD – DRAM First Single-Bit Error Correct       | 400  |

| 2 0 47 | Address Register (D0:F1)                                  |      |

| 3.6.47 | DRAM_DED_ADD - DRAM DED Error Address (D0:F1)             |      |

| 3.6.48 | DRAM_SCRB_ADD - DRAM Scrub Error Address Register (D0:F1) |      |

| 3.6.49 | DRAM_RETR_ADD – DRAM DED Retry Address (D0:F1)            | 105  |

| 3.6.50 | DRAM_SEC_D0A – DRAM DIMM0 Channel A SEC Counter           | 405  |

| 0.0.54 | Register (D0:F1)                                          | 105  |

| 3.6.51 | DRAM_DED_D0A – DRAM DIMM0 Channel A DED Counter           | 400  |

| 0.0.50 | Register (D0:F1)                                          | 106  |

| 3.6.52 | DRAM_SEC_D1A – DRAM DIMM1 Channel A SEC Counter           | 400  |

| 0.0.50 | Register (D0:F1)                                          | 106  |

| 3.6.53 | DRAM_DED_D1A – DRAM DIMM1 Channel A DED Counter           | 4.0= |

|        | Register (D0:F1)                                          | 107  |

| 3.6.54 | DRAM_SEC_D2A – DRAM DIMM2 Channel A SEC Counter           | 4.0= |

|        | Register (D0:F1)                                          | 107  |

| 3.6.55 | DRAM_DED_D2A – DRAM DIMM2 Channel A DED Counter           |      |

|        | Register (D0:F1)                                          | 107  |

| 3.6.56 | DRAM_SEC_D3A – DRAM DIMM3 Channel A SEC Counter           |      |

|        | Register (D0:F1)                                          | 108  |

| 3.6.57 | DRAM_DED_D3A – DRAM DIMM3 Channel A DED Counter           |      |

|        | Register (D0:F1)                                          |      |

| 3.6.58 | THRESH_DED - DED Threshold Register (D0:F1)               | 108  |

| 3.6.59 | DRAM_SEC2_ADD – DRAM Next Single-Bit Error Correct        |      |

|        | Address Register (D0:F1)                                  | 109  |

| 3.6.60 | DRAM_SEC_D0B – DRAM DIMM0 Channel B SEC Counter           |      |

|        | Register (D0:F1)                                          | 109  |

| 3.6.61 | DRAM_DED_D0B – DRAM DIMM0 Channel B DED Counter           |      |

|        | Register (D0:F1)                                          | 110  |

| 3.6.62 | DRAM_SEC_D1B – DRAM DIMM1 Channel B SEC Counter           |      |

|        | Register (D0:F1)                                          | 110  |

|     | 3.6.63           | DRAM_DED_D1B - DRAM DIMM1 Channel B DED Counter              |     |

|-----|------------------|--------------------------------------------------------------|-----|

|     |                  | Register (D0:F1)                                             | 110 |

|     | 3.6.64           | DRAM_SEC_D2B - DRAM DIMM2 Channel B SEC Counter              |     |

|     |                  | Register (D0:F1)                                             | 111 |

|     | 3.6.65           | DRAM_DED_D2B - DRAM DIMM2 Channel B DED Counter              |     |

|     |                  | Register (D0:F1)                                             | 111 |

|     | 3.6.66           | DRAM_SEC_D3B - DRAM DIMM3 Channel B SEC Counter              |     |

|     |                  | Register (D0:F1)                                             | 111 |

|     | 3.6.67           | DRAM_DED_D3B - DRAM DIMM3 Channel B DED Counter              |     |

|     |                  | Register (D0:F1)                                             | 112 |

|     | 3.6.68           | DIMM_THR_EX - DIMM Threshold Exceeded Register (D0:F1)       | 112 |

|     | 3.6.69           | SYSBUS_ERR_CTL - System Bus Error Control Register (D0:F1)   | 113 |

|     | 3.6.70           | HI_ERR_CTL - Hub Interface Error Control Register (D0:F1)    | 114 |

|     | 3.6.71           | BUF_ERR_CTL - Buffer Error Control Register (D0:F1)          |     |

|     | 3.6.72           | DRAM_ERR_CTL - DRAM Error Control Register (D0:F1)           |     |

| 3.7 |                  | oress Port A Registers (D2:F0)                               |     |

|     | 3.7.1            | VID – Vendor Identification (D2:F0)                          |     |

|     | 3.7.2            | DID – Device Identification (D2:F0)                          |     |

|     | 3.7.3            | PCICMD – PCI Command Register (D2:F0)                        |     |

|     | 3.7.4            | PCISTS – PCI Status Register (D2:F0)                         | 121 |

|     | 3.7.5            | RID – Revision Identification (D2:F0)                        |     |

|     | 3.7.6            | SUBC – Sub-Class Code (D2:F0)                                |     |

|     | 3.7.7            | BCC – Base Class Code (D2:F0)                                |     |

|     | 3.7.8            | CLS – Cache Line Size (D2:F0)                                |     |

|     | 3.7.9            | HDR – Header Type (D2:F0)                                    |     |

|     | 3.7.10           | PBUSN – Primary Bus Number (D2:F0)                           | 124 |

|     | 3.7.10           | SBUSN – Secondary Bus Number (D2:F0)                         | 124 |

|     | 3.7.11           | SUBUSN – Subordinate Bus Number (D2:F0)                      |     |

|     | _                |                                                              |     |

|     | 3.7.13<br>3.7.14 | IOBASE – I/O Base Address Register (D2:F0)                   |     |

|     |                  | IOLIMIT – I/O Limit Address Register (D2:F0)                 |     |

|     | 3.7.15           | SEC_STS – Secondary Status Register (D2:F0)                  |     |

|     | 3.7.16           | MBASE – Memory Base Address Register (D2:F0)                 |     |

|     | 3.7.17           | MLIMIT – Memory Limit Address Register (D2:F0)               |     |

|     | 3.7.18           | PMBASE – Prefetchable Memory Base Address Register (D2:F0)   |     |

|     | 3.7.19           | PMLIMIT – Prefetchable Memory Limit Address Register (D2:F0) | 128 |

|     | 3.7.20           | PMBASU – Prefetchable Memory Base Upper Address              | 400 |

|     |                  | Register (D2:F0)                                             | 129 |

|     | 3.7.21           | PMLMTU – Prefetchable Memory Limit Upper Address             |     |

|     |                  | Register (D2:F0)                                             |     |

|     | 3.7.22           | CAPPTR – Capabilities Pointer (D2:F0)                        |     |

|     | 3.7.23           | INTRLINE – Interrupt Line Register (D2:F0)                   |     |

|     | 3.7.24           | INTRPIN – Interrupt Pin Register (D2:F0)                     |     |

|     | 3.7.25           | BCTRL – Bridge Control Register (D2:F0)                      |     |

|     | 3.7.26           | VS_CMD0 - Vendor Specific Command Register 0 (D2:F0)         |     |

|     | 3.7.27           | VS_CMD1 – Vendor Specific Command Register 1 (D2:F0)         |     |

|     | 3.7.28           | VS_STS0 - Vendor Specific Status Register 0 (D2:F0)          | 132 |

|     | 3.7.29           | VS_STS1 - Vendor Specific Status Register 1 (D2:F0)          | 133 |

|     | 3.7.30           | PMCAPID – Power Management Capabilities Structure (D2:F0)    | 133 |

|     | 3.7.31           | PMNPTR - Power Management Next Capabilities Pointer (D2:F0)  | 134 |

|     | 3.7.32           | PMCAPA – Power Management Capabilities (D2:F0)               |     |

|     | 3.7.33           | PMCSR – Power Management Status and Control (D2:F0)          |     |

|     | 3.7.34           | PMCSRBSE – Power Management Status and Control               |     |

|     |                  | Bridge Extensions (D2:F0)                                    | 135 |

|     | 3.7.35           | PMDATA – Power Management Data (D2:F0)                       |     |

|     | 3.7.36           | MSICAPID – MSI Capabilities Structure (D2:F0)                |     |

|     | 3.7.37           | MSINPTR – MSI Next Capabilities Pointer (D2:F0)              |     |

|     |                  |                                                              |     |

| 3.7.38 | MSICAPA – MSI Capabilities (D2:F0)                              |     |

|--------|-----------------------------------------------------------------|-----|

| 3.7.39 | MSIAR - MSI Address Register for PCI Express (D2:F0)            | 137 |

| 3.7.40 | MSIDR – MSI Data Register (D2:F0)                               |     |

| 3.7.41 | EXP_CAPID - PCI Express Features Capabilities Structure (D2:F0) | 138 |

| 3.7.42 | EXP_NPTR - PCI Express Next Capabilities Pointer (D2:F0)        |     |

| 3.7.43 | EXP_CAPA – PCI Express Features Capabilities (D2:F0)            |     |

| 3.7.44 | EXP_DEVCAP – PCI Express Device Capabilities (D2:F0)            |     |

| 3.7.45 | EXP_DEVCTL – PCI Express Device Control (D2:F0)                 |     |

| 3.7.46 | EXP_DEVSTS – PCI Express Device Status (D2:F0)                  |     |

| 3.7.47 | EXP_LNKCAP – PCI Express Link Capabilities (D2:F0)              |     |

| -      |                                                                 |     |

| 3.7.48 | EXP_LNKCTL – PCI Express Link Control (D2:F0)                   |     |

| 3.7.49 | EXP_LNKSTS – PCI Express Link Status (D2:F0)                    |     |

| 3.7.50 | EXP_SLTCAP – PCI Express Slot Capabilities (D2:F0)              | 140 |

| 3.7.51 | EXP_SLTCTL - PCI Express Slot Control (D2:F0)                   |     |

| 3.7.52 | EXP_SLTSTS - PCI Express Slot Status (D2:F0)                    |     |

| 3.7.53 | EXP_RPCTL – PCI Express Root Port Control (D2:F0)               |     |

| 3.7.54 | EXP_RPSTS – PCI Express Root Port Status (D2:F0)                | 148 |

| 3.7.55 | EXP_PFCCA – PCI Express Posted Flow Control Credits             |     |

|        | Allocated (D2:F0)                                               | 149 |

| 3.7.56 | EXP_NPFCCA – PCI Express Non Posted Flow Control                |     |

|        | Credits Allocated (D2:F0)                                       | 149 |

| 3.7.57 | EXP_ENHCAPST – PCI Express Enhanced Capability                  |     |

|        | Structure (D2:F0)                                               | 150 |

| 3.7.58 | EXP UNCERRSTS – PCI Express Uncorrectable Error                 |     |

|        | Status (D2:F0)                                                  | 150 |

| 3.7.59 | EXP_UNCERRMSK – PCI Express Uncorrectable Error                 |     |

|        | Mask (D2:F0)                                                    | 151 |

| 3.7.60 | EXP_UNCERRSEV – PCI Express Uncorrectable Error                 |     |

| 0.7.00 | Severity (D2:F0)                                                | 152 |

| 3.7.61 | EXP_CORERRSTS – PCI Express Correctable Error                   | 102 |

| 5.7.01 | Status (D2:F0)                                                  | 153 |

| 3.7.62 | EXP_CORERRMSK – PCI Express Correctable Error                   | 100 |

| 3.7.02 | Mask (D2:F0)                                                    | 151 |

| 2762   | EXP_AERCACR – PCI Express Advanced Error                        | 104 |

| 3.7.63 |                                                                 | 455 |

| 0.7.04 | Capabilities and Control (D2:F0)                                |     |

| 3.7.64 | EXP_HDRLOG0 – PCI Express Header Log DW0 (D2:F0)                |     |

| 3.7.65 | EXP_HDRLOG1 – PCI Express Header Log DW1 (D2:F0)                |     |

| 3.7.66 | EXP_HDRLOG2 – PCI Express Header Log DW2 (D2:F0)                |     |

| 3.7.67 | EXP_HDRLOG3 - PCI Express Header Log DW3 (D2:F0)                | 157 |

| 3.7.68 | EXP_RPERRCMD – PCI Express Root Port Error                      |     |

|        | Command (D2:F0)                                                 | 157 |

| 3.7.69 | EXP_RPERRMSTS – PCI Express Root Port Error Message             |     |

|        | Status (D2:F0)                                                  |     |

| 3.7.70 | EXP_ERRSID – PCI Express Error Source ID (D2:F0)                | 159 |

| 3.7.71 | EXP_UNITERR - PCI Express Unit Error Status (D2:F0)             | 160 |

| 3.7.72 | EXP_MASKERR - PCI Express Mask Error (D2:F0)                    | 162 |

| 3.7.73 | EXP_ERRDOCMD – PCI Express Error Do Command                     |     |

|        | Register (D2:F0)                                                | 163 |

| 3.7.74 | EXP_UNCERROMSK – PCI Express Uncorrectable Error                |     |

|        | Detect Mask (D2:F0)                                             | 165 |

| 3.7.75 | EXP_CORERRDMSK – PCI Express Correctable Error                  |     |

|        | Detect Mask (D2:F0)                                             | 166 |

| 3.7.76 | EXP_UNITERRDMSK – PCI Express Unit Error Detect                 |     |

| 0.1.10 | Mask (D2:F0)                                                    | 166 |

| 3.7.77 | EXP_FERR – PCI Express First Error Register (D2:F0)             |     |

| 3.7.78 | EXP_NERR PCI Express Next Error Register (D2:F0)                |     |

|        | LAL MENN LALEANGA NGALEHA NGUAIGHAZ HAZIRA                      |     |

|   |       | 3.7.79    | EXP_ERR_CTL - PCI Express Error Control Register (D2:F0)    | 169 |

|---|-------|-----------|-------------------------------------------------------------|-----|

|   | 3.8   | PCI Exp   | oress Port A1 Registers (D3:F0)                             | 169 |

|   |       | 3.8.1     | DID – Device Identification (D3:F0)                         |     |

|   |       | 3.8.2     | EXP_LNKCAP – PCI Express Link Capabilities (D3:F0)          |     |

|   | 3.9   | Extende   | ed Configuration Registers (D8:F0)                          | 173 |

|   |       | 3.9.1     | VID – Vendor Identification (D8:F0)                         |     |

|   |       | 3.9.2     | DID – Device Identification (D8:F0)                         | 174 |

|   |       | 3.9.3     | PCICMD – PCI Command Register (D8:F0)                       | 174 |

|   |       | 3.9.4     | PCISTS – PCI Status Register (D8:F0)                        |     |

|   |       | 3.9.5     | RID – Revision Identification (D8:F0)                       | 176 |

|   |       | 3.9.6     | SUBC – Sub-Class Code (D8:F0)                               | 176 |

|   |       | 3.9.7     | BCC – Base Class Code (D8:F0)                               | 176 |

|   |       | 3.9.8     | HDR – Header Type (D8:F0)                                   |     |

|   |       | 3.9.9     | SVID – Subsystem Vendor Identification (D8:F0)              |     |

|   |       | 3.9.10    | SID – Subsystem Identification (D8:F0)                      |     |

|   |       | 3.9.11    | SCRUBLIM – Scrub Limit and Control Register (D8:F0)         | 178 |

|   |       | 3.9.12    | SCRBADD – Scrub Address (D8:F0)                             | 178 |

|   |       | 3.9.13    | DTCL – DRAM Power Management Control Lower Register (D8:F0) | 179 |

|   |       | 3.9.14    | DTCU – DRAM Power Management Control Upper                  |     |

|   |       |           | Register (D8:F0)                                            | 181 |

|   | _     |           |                                                             |     |

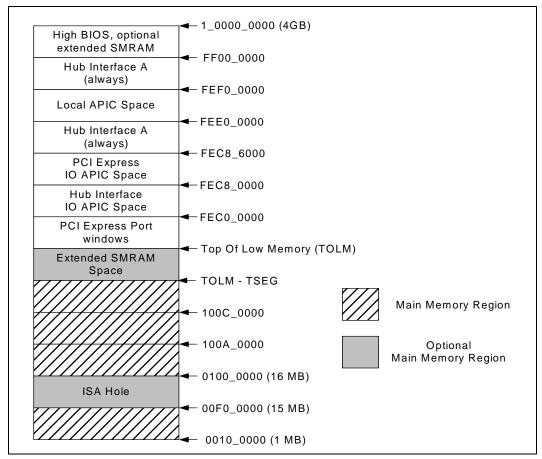

| 4 | Syste | m Addres  | ss Map                                                      | 183 |

|   | 4.1   | Overvie   | ew                                                          | 183 |

|   |       | 4.1.1     | System Memory Spaces                                        | 184 |

|   |       | 4.1.2     | VGA and MDA Memory Spaces                                   | 185 |

|   |       | 4.1.3     | PAM Memory Spaces                                           | 185 |

|   |       | 4.1.4     | ISA Hole Memory Space                                       | 186 |

|   |       | 4.1.5     | TSEG SMM Memory Space                                       | 186 |

|   |       | 4.1.6     | PCI Express Enhanced Configuration Aperture                 | 187 |

|   |       | 4.1.7     | I/O APIC Memory Space                                       | 187 |

|   |       | 4.1.8     | System Bus Interrupt Memory Space                           | 188 |

|   |       | 4.1.9     | High SMM Memory Space                                       | 188 |

|   |       | 4.1.10    | PCI Device Memory (MMIO)                                    | 188 |

|   | 4.2   | I/O Add   | Iress Space                                                 | 189 |

|   | 4.3   | System    | Management Mode (SMM) Space                                 | 190 |

|   |       | 4.3.1     | SMM Addressing Ranges                                       | 190 |

|   | 4.4   | Memory    | y Reclaim Background                                        | 191 |

|   |       | 4.4.1     | Memory Remapping                                            | 192 |

| E | Funct | ional Doa | cription                                                    | 102 |

| 5 |       |           |                                                             |     |

|   | 5.1   |           | Feature Set                                                 |     |

|   |       | 5.1.1     | Coherent Memory Write Buffer                                |     |

|   |       | 5.1.2     | Internal Data Protection                                    |     |

|   | 5.2   |           | Side Bus (FSB)                                              |     |

|   |       | 5.2.1     | In-Order Queue (IOQ)                                        |     |

|   |       | 5.2.2     | System Bus Interrupts                                       |     |

|   |       | 5.2.3     | System Bus Dynamic Inversion                                |     |

|   |       | 5.2.4     | Front Side Bus Parity                                       |     |

|   | 5.3   |           | y Interface                                                 |     |

|   |       | 5.3.1     | Memory Interface Performance Optimizations                  |     |

|   |       | 5.3.2     | Memory Interface RASUM                                      |     |

|   |       | 5.3.3     | Memory Address Translation Tables                           |     |

|   |       | 5.3.4     | Quad Word Ordering                                          |     |

|   |       | 5.3.5     | DDR Clock Voltage Crossing (VOX) Calibration                |     |

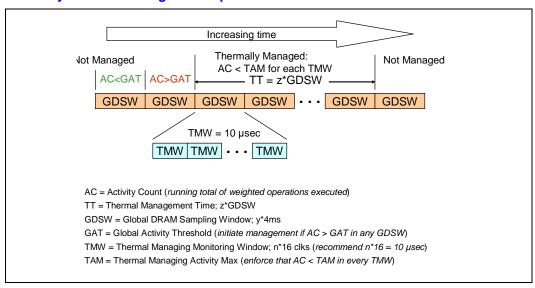

|   |       | 5.3.6     | Thermal Management                                          | 204 |

|   | 5.4    | PCI Exp    | press Interface                                      | 207  |

|---|--------|------------|------------------------------------------------------|------|

|   |        | 5.4.1      | PCI Express Training                                 | 207  |

|   |        | 5.4.2      | PCI Express Retry                                    | 207  |

|   |        | 5.4.3      | PCI Express Link Recovery                            | 208  |

|   |        | 5.4.4      | PCI Express Data Protection                          |      |

|   |        | 5.4.5      | PCI Express Retrain                                  | 208  |

|   | 5.5    | Hub Inte   | erface 1.5                                           |      |

|   | 5.6    |            | locking                                              |      |

|   |        | 5.6.1      | DDR Geared Clocking                                  | 209  |

|   |        | 5.6.2      | PCI Express Clocking                                 |      |

|   |        | 5.6.3      | Spread-Spectrum Clocking Limitations                 |      |

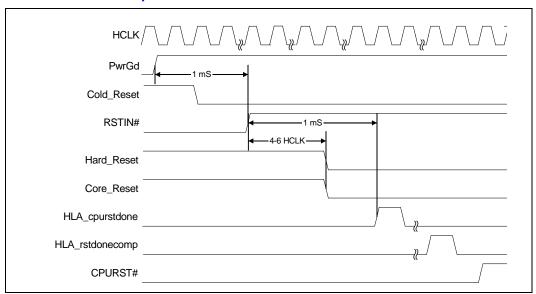

|   | 5.7    | System     | Reset                                                |      |

|   |        | 5.7.1      | MCH Reset Types                                      |      |

|   |        | 5.7.2      | Power Sequencing Requirement                         |      |

|   |        | 5.7.3      | Reset Sequencing                                     |      |

|   | 5.8    | Platform   | n Power Management Support                           |      |

|   |        | 5.8.1      | Supported System Power States                        |      |

|   |        | 5.8.2      | System Bus Interface Power Management                |      |

|   |        | 5.8.3      | DDR Interface Power Management                       | 215  |

|   |        | 5.8.4      | PCI Express Interface Power Management               | 215  |

|   |        | 5.8.5      | PCI Express Link Power State Definitions             | 215  |

|   |        | 5.8.6      | PME Support                                          | 218  |

|   |        | 5.8.7      | BIOS Support for PCI Express PM Messaging            | 220  |

|   | 5.9    | Debug I    | nterface (JTAG)                                      | 221  |

|   | 5.10   | Exception  | on Handling                                          | 221  |

|   |        | 5.10.1     | Error Classification                                 |      |

|   |        | 5.10.2     | Data Error Propagation between Interfaces/Units      |      |

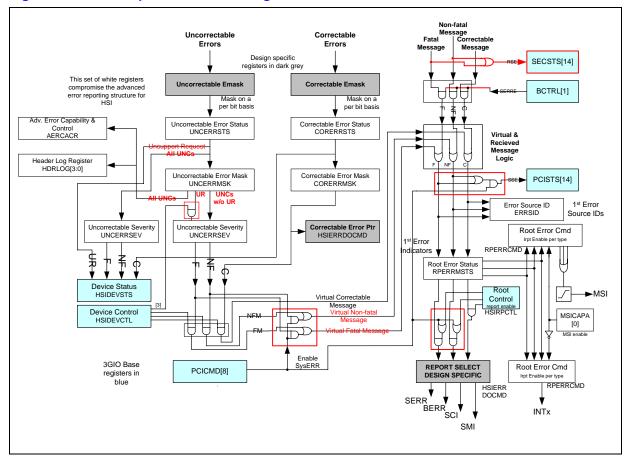

|   |        | 5.10.3     | FERR/NERR Global Register Scheme                     | 223  |

|   | 5.11   | SMBus      | Port Description                                     |      |

|   |        | 5.11.1     | Internal Access Mechanism                            | 228  |

|   |        | 5.11.2     | SMBus Transaction Field Definitions                  |      |

|   |        | 5.11.3     | Unsupported Access Addresses                         |      |

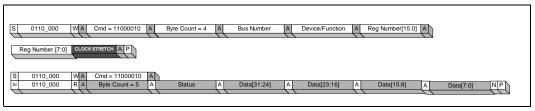

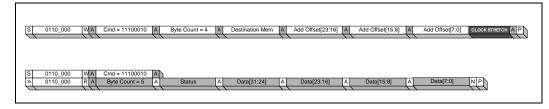

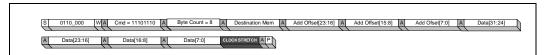

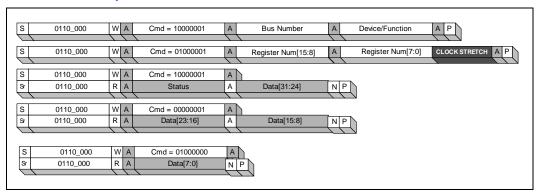

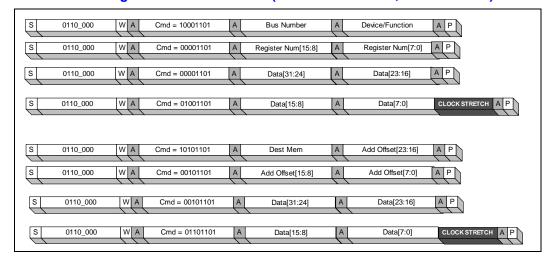

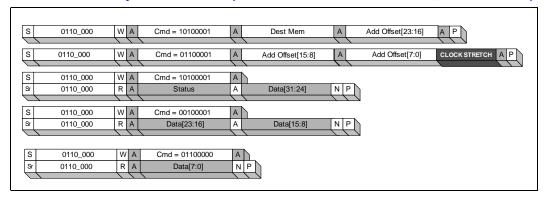

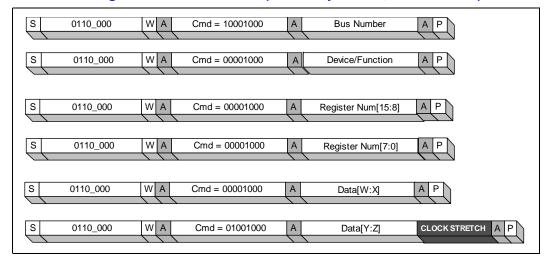

|   |        | 5.11.4     | SMB Transaction Pictograms                           | 232  |

| 6 | Electr | ical Chara | acteristics                                          | 235  |

|   | 6.1    |            | e Maximum Ratings                                    |      |

|   | 6.2    |            | Characteristics                                      |      |

|   | 6.3    |            | rface Signal Groupings                               |      |

|   | 6.4    |            | racteristics                                         |      |

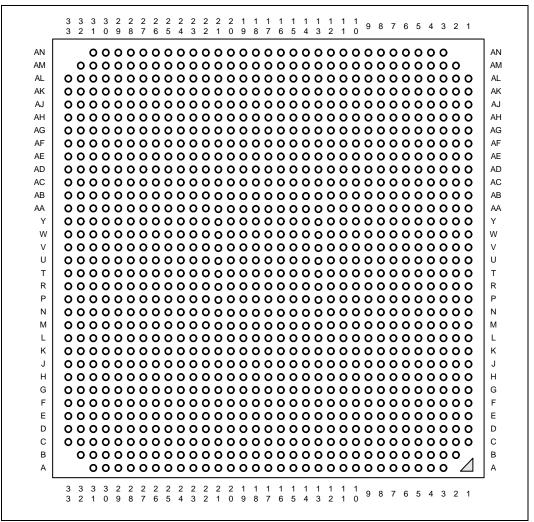

| 7 | Rallou | it and Pag | ckage Specifications                                 | 2/12 |

| , |        |            | 5 .                                                  |      |

|   | 7.1    |            | - Caralifornian                                      |      |

|   | 7.2    | •          | e Specifications                                     |      |

|   | 7.0    | 7.2.1      | Package Mechanical Requirements                      |      |

|   | 7.3    |            | terface Trace Length Compensation                    |      |

|   |        | 7.3.1      | System Bus Signal Package Trace Length Data          |      |

|   |        | 7.3.2      | Other MCH Interface Signal Package Trace Length Data | ∠5/  |

## **Figures**

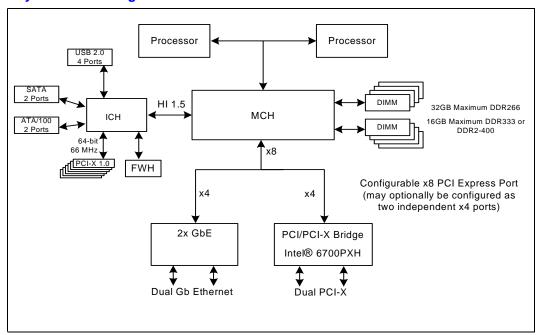

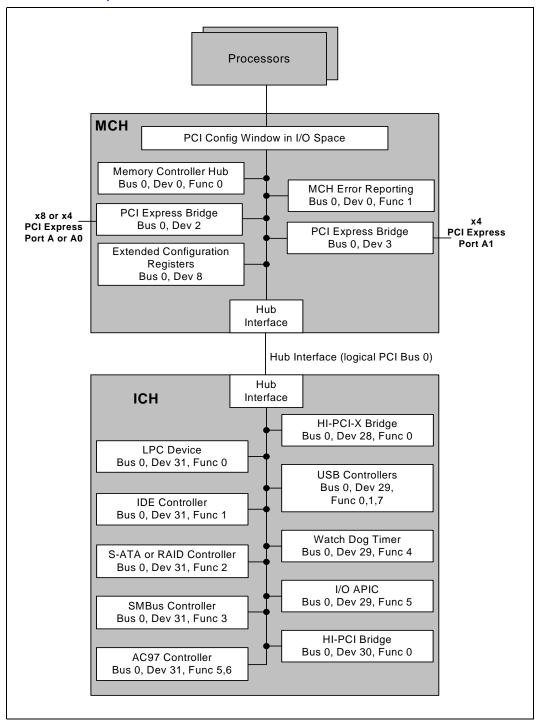

1-1 3-1

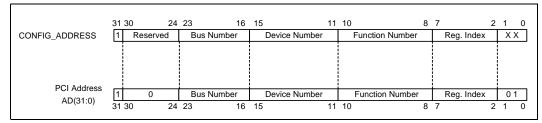

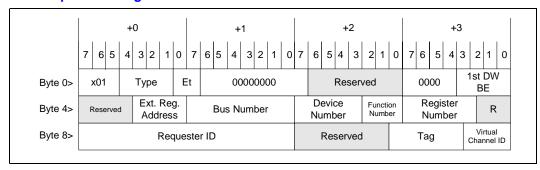

| 3-3         PCI Express Configuration Transaction Header         3           34         Enhanced Configuration Memory Address Map         3           3-5         PAM Associated Attribute Bits         4           4-1         Basic Memory Regions         18           4-2         DOS Legacy Region         18           4-3         1 MB through 4 GB Memory Regions         18           5-1         Error Ramp Rate         19           5-2         Error Count For Comparison         20           5-3         Dual Channel Memory Read         20           5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Write Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-12         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-13         DWORD Configuration Write Protocol (SMBus Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-2  | Type 1 Configuration Address to PCI Address Mapping       | 36             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------|----------------|

| 3-5         PAM Associated Attribute Bits         4           4-1         Basic Memory Regions         18           4-2         DOS Legacy Region         18           4-3         1 MB through 4 GB Memory Regions         18           5-1         Error Count For Comparison         20           5-2         Error Count For Comparison         20           5-3         Dual Channel Memory Read         20           5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Memory Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Write Protocol         23           5-12         DwORD Memory Write Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-13         DWORD Configuration Write Protocol (SMBus Word Write / PEC Disabled)         23           5-15         DWORD Memory Read Protocol (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-3  | PCI Express Configuration Transaction Header              | 38             |

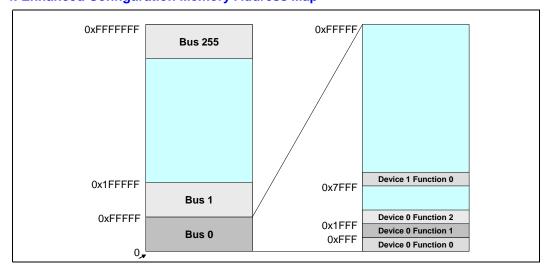

| 4-1         Basic Memory Regions         18           4-2         DOS Legacy Region         18           4-3         1 MB through 4 GB Memory Regions         18           5-1         Error Ramp Rate         19           5-2         Error Count For Comparison         20           5-3         Dual Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-12         DWORD Memory Write Protocol         23           5-13         DWORD Configuration Write Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-14         DWORD Configuration Write Protocol (SMBus Word Write, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Byte Write, PEC Disabled)         23 <td>3-4</td> <td>Enhanced Configuration Memory Address Map</td> <td> 38</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-4  | Enhanced Configuration Memory Address Map                 | 38             |

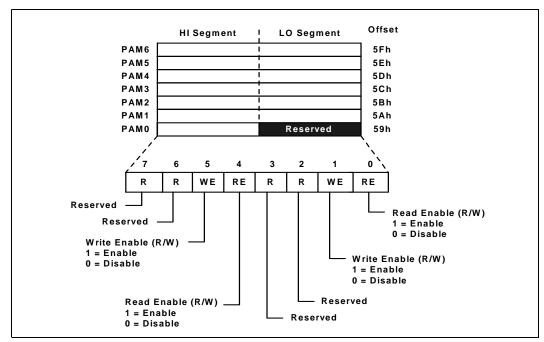

| 4-2         DOS Legacy Region         18           4-3         1 MB through 4 GB Memory Regions         18           5-1         Error Ramp Rate         19           5-2         Error Count For Comparison         20           5-3         Dual Channel Memory Read         20           5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Read Protocol (SMBus Word Write / Block Read, PEC Disabled)         23           5-12         DWORD Memory Write Protocol         (SMBus Word Write / Word Read, PEC Disabled)         23           5-14         DWORD Configuration Write Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Byte Write, PEC Disabled)         23           5-16         WORD Configuration Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-5  | PAM Associated Attribute Bits                             | 48             |

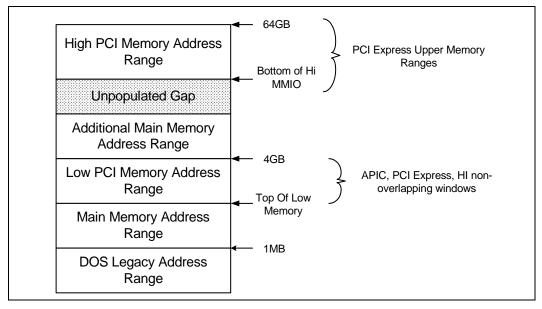

| 4-3         1 MB through 4 GB Memory Regions         18           5-1         Error Ramp Rate         19           5-2         Error Count For Comparison         20           5-3         Dual Channel Memory Read         20           5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-12         DWORD Memory Write Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-13         DWORD Configuration Write Protocol (SMBus Word Write, PEC Disabled)         23           5-14         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-1  | Basic Memory Regions                                      | 183            |

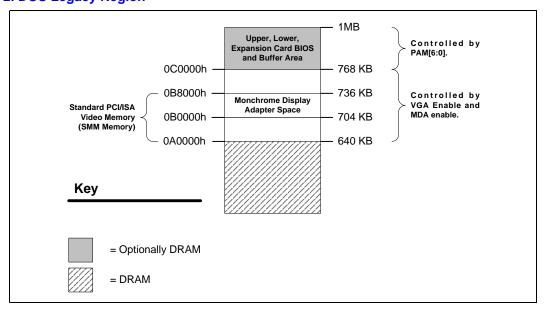

| 5-1         Error Ramp Rate         19           5-2         Error Count For Comparison         20           5-3         Dual Channel Memory Read         20           5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Read Protocol (SMBus Word Write / Block Read, PEC Disabled)         23           5-12         DWORD Memory Write Protocol         23           5-13         DWORD Configuration Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-14         DWORD Configuration Write Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-16         WORD Configuration Wrote Protocol (SMBus Byte Write, PEC Disabled)         23 <td< td=""><td>4-2</td><td>DOS Legacy Region</td><td> 184</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-2  | DOS Legacy Region                                         | 184            |

| 5-2         Error Count For Comparison         20           5-3         Dual Channel Memory Read         20           5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-12         DWORD Onfiguration Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-13         DWORD Configuration Write Protocol (SMBus Word Write, PEC Disabled)         23           5-14         DWORD Memory Read Protocol (SMBus Word Write, PEC Disabled)         23           5-15         DWORD Space Personal Wrote Protocol (SMBus Byte Write, PEC Disabled)         23           5-16         WORD Configuration Wrote Protocol (SMBus Byte Write, PEC Disabled)         23           5-17         WCRD Language Dimensions (Bottom View) <td< td=""><td>4-3</td><td>1 MB through 4 GB Memory Regions</td><td> 187</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-3  | 1 MB through 4 GB Memory Regions                          | 187            |

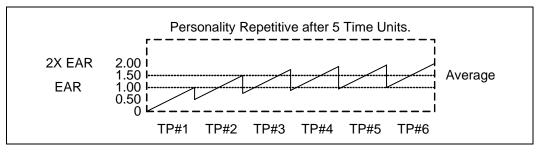

| 5-3         Dual Channel Memory Read         20           5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write, PEC Disabled)         23           5-11         DWORD Memory Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-12         DWORD Memory Write Protocol         23           5-13         DWORD Configuration Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-14         DWORD Configuration Write Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Byte Write, PEC Disabled)         23           5-16         WORD Configuration Wrote Protocol (SMBus Byte Write, PEC Disabled)         23           7-1         MCH Ballout Diagram (Top View)         24           7-2         MCH Package Dimensions (Bottom View)         25 <t< td=""><td>5-1</td><td>Error Ramp Rate</td><td> 199</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-1  | Error Ramp Rate                                           | 199            |

| 5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Memory Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Write Protocol         23           5-12         DWORD Memory Write Protocol (SMBus Word Write / Block Read, PEC Disabled)         23           5-13         DWORD Configuration Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-14         DWORD Configuration Write Protocol (SMBus Word Write, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-16         WORD Configuration Wrote Protocol (SMBus Byte Write, PEC Disabled)         23           7-1         MCH Ballout Diagram (Top View)         24           7-2         MCH Package Dimensions (Bottom View)         25           7-3         MCH Package Dimensions (Side View)         25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-2  | Error Count For Comparison                                | 200            |

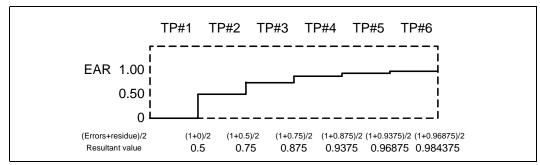

| 5-4         Single Channel Memory Read         20           5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Memory Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Write Protocol         23           5-12         DWORD Memory Write Protocol (SMBus Word Write / Block Read, PEC Disabled)         23           5-13         DWORD Configuration Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-14         DWORD Configuration Write Protocol (SMBus Word Write, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-16         WORD Configuration Wrote Protocol (SMBus Byte Write, PEC Disabled)         23           7-1         MCH Ballout Diagram (Top View)         24           7-2         MCH Package Dimensions (Bottom View)         25           7-3         MCH Package Dimensions (Side View)         25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-3  | Dual Channel Memory Read                                  | 204            |

| 5-5         Memory Thermal Management Operation         20           5-6         Power-On Reset Sequence         21           5-7         Global FERR/NERR Register Representation         22           5-8         PCI Express Error Handling         22           5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-11         DWORD Memory Read Protocol (SMBus Word Write / Block Read, PEC Disabled)         23           5-12         DWORD Memory Write Protocol         23           5-13         DWORD Configuration Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-14         DWORD Configuration Write Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-16         WORD Configuration Wrote Protocol (SMBus Byte Write, PEC Disabled)         23           7-1         MCH Ballout Diagram (Top View)         24           7-2         MCH Package Dimensions (Bottom View)         25           7-3         MCH Package Dimensions (Side View)         25           2-4         DDR Interface Shared Signals         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-4  |                                                           |                |

| 5-7 Global FERR/NERR Register Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-5  |                                                           |                |

| 5-7 Global FERR/NERR Register Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-6  |                                                           |                |

| 5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-7  |                                                           |                |

| 5-9         DWORD Configuration Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-10         DWORD Configuration Write Protocol (SMBus Block Write, PEC Disabled)         23           5-11         DWORD Memory Read Protocol (SMBus Block Write / Block Read, PEC Disabled)         23           5-12         DWORD Memory Write Protocol         23           5-13         DWORD Configuration Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-14         DWORD Configuration Write Protocol (SMBus Word Write, PEC Disabled)         23           5-15         DWORD Memory Read Protocol (SMBus Word Write / Word Read, PEC Disabled)         23           5-16         WORD Configuration Wrote Protocol (SMBus Byte Write, PEC Disabled)         23           7-1         MCH Ballout Diagram (Top View)         24           7-2         MCH Package Dimensions (Bottom View)         25           7-3         MCH Package Dimensions (Side View)         25           7-4         MCH Package Dimensions (Top View)         25           2-1         System Bus Signal Description         2           2-2-1         DDR Channel_A Interface Signals         2           2-3         DDR Channel_B Interface Signals         2           2-4         DDR Interface Shared Signals         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-8  | PCI Express Error Handling                                | 227            |

| PEC Disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-9  |                                                           |                |

| 5-10 DWORD Configuration Write Protocol (SMBus Block Write, PEC Disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                                           | 232            |

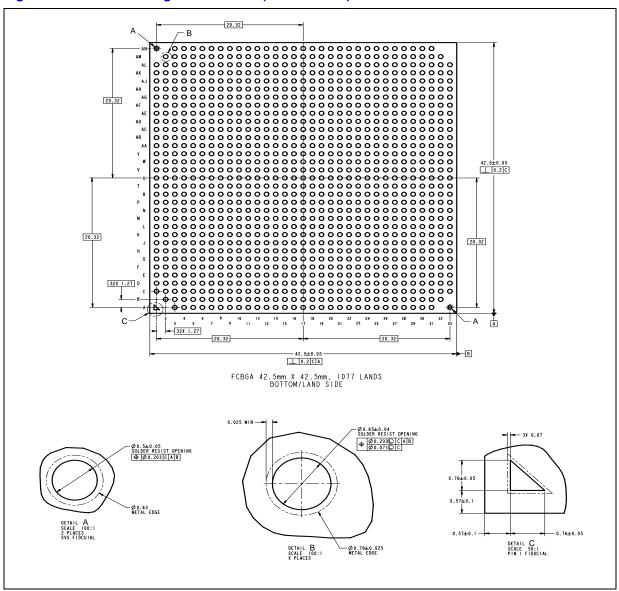

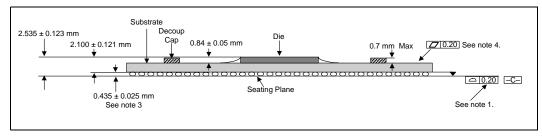

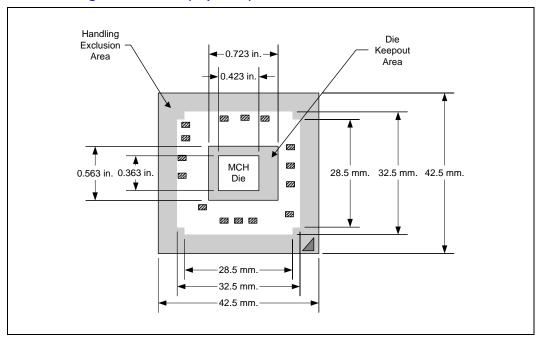

| PEC Disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-10 | DWORD Configuration Write Protocol (SMBus Block Write.    |                |