Low-Voltage, Full-Bridge Brushless DC Motor Driver with Integrated Hall Sensor IC, PWM Speed Control, Soft-Switching, and Reverse Battery and Short Circuit Protection

# **Discontinued Product**

This device is no longer in production. The device should not be purchased for new design applications. Samples are no longer available.

Date of status change: March 4, 2013

## **Recommended Substitutions:**

For existing customer transition, and for new customers or new applications, contact Allegro Sales.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

## Low-Voltage, Full-Bridge Brushless DC Motor Driver with Integrated Hall Sensor IC, PWM Speed Control, Soft-Switching, and Reverse Battery and Short Circuit Protection

#### **Features and Benefits**

- Low-voltage operation, 1.8 to 4.2 V

- Multifunction CONTROL pin input:

- Direct input PWM for speed control

- Active braking for fast stop cycle

- Sleep function to reduce average power consumption

- Reverse voltage protection on VDD and CONTROL pins

- Output thermal shutdown protection for robust performance

- Soft switching algorithm to reduce audible switching noise and EMI

- Hall chopper stabilization technique for precise signal response over operating range

- Antistall feature guarantees continuous rotation and prevents overheating

- Single-chip solution for high reliability

- Miniature MLP/DFN package with industry-leading 0.40 mm maximum overall thickness

### Package:

6-contact MLP/DFN

1.5 mm × 2 mm

0.40 mm maximum overall height

(EW package)

Approximate size

#### **Description**

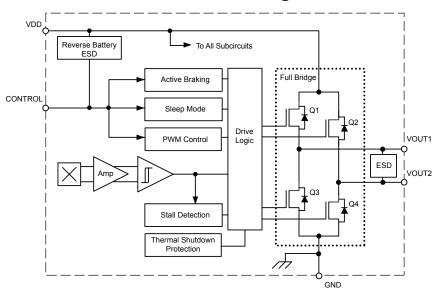

The A1448 is a full-bridge motor driver designed to drive low-voltage, brushless DC motors. The device is designed to allow the user to control several functions with a single input control pin. The pin allows for direct input PWM for speed control, is used to initiate the active braking function to reduce motor stop time, and acts as an enable pin to engage micro-power sleep mode to reduce average power consumption when not in use. The A1448 is designed for use in vibration motor applications in portable devices that require fast stop-start cycles, such as haptic applications and vibration ring tones.

Commutation of the motor is achieved by use of a single Hall element to detect the rotational position of an alternating-pole ring magnet. A high density CMOS semiconductor process allows the integration of all the necessary electronics. This includes the Hall element, the motor control circuitry, and the output full bridge. Low-voltage design techniques have been employed to achieve full device functionality down to 1.8 V  $V_{DD}$ . This fully integrated single chip solution provides enhanced reliability (including reverse battery protection and output short circuit protection) and eliminates the need for any external support components.

The A1448 employs a soft-switching algorithm to reduce audible switching noise and EMI interference. The micropower sleep mode can be initiated on the CONTROL pin, and reduces current consumption for battery management in

Continued on the next page...

## **Functional Block Diagram**

# Low-Voltage, Full-Bridge Brushless DC Motor Driver with Integrated Hall Sensor IC, PWM Speed Control, Soft-Switching, and Reverse Battery and Short Circuit Protection

#### **Description (continued)**

portable electronic devices. This feature allows the removal of a FET transistor for switching the device on and off.

The A1448 is optimized for vibration motor applications in cellular phones, pagers, electronic toothbrushes, hand-held video game controllers, and can also be used as a micro-fan driver for fans motors up to 1 W.

The Allegro DFN (EW) package is the thinnest DFN in the

industry with a 0.40 mm maximum thickness that allows for very thin BLDC coin motor designs. The small package outline and low profile make this device ideally suited for use in applications where printed circuit board area and component headroom are at a premium. It is available in a lead (Pb) free, 6-contact MLP/DFN micro-leadframe package, with an exposed pad for enhanced thermal dissipation. Leadframe is 100% matte tin plated.

#### Selection Guide

| Part Number               | Packing <sup>1</sup>       | Package                                                                                            |

|---------------------------|----------------------------|----------------------------------------------------------------------------------------------------|

| A1448EEWLT-P <sup>2</sup> | 3000 pieces per 7-in. reel | 1.5 mm × 2 mm , 0.40 mm maximum overall package height, 6-contact MLP/DFN with exposed thermal pad |

#### Absolute Maximum Ratings

| Characteristic                                     | Symbol            | Notes                                                             | Rating                     | Units |

|----------------------------------------------------|-------------------|-------------------------------------------------------------------|----------------------------|-------|

| Forward Supply Voltage                             | $V_{DD}$          |                                                                   | 5.5                        | V     |

| Reverse Supply Voltage                             | $V_{RDD}$         |                                                                   | -5.0                       | V     |

| Forward Output Voltage                             | V <sub>OUT</sub>  | V <sub>DD</sub> > 0 V                                             | 0 to V <sub>DD</sub> + 0.3 | V     |

| Reverse Output Voltage                             | V <sub>ROUT</sub> | V <sub>DD</sub> > 0 V                                             | -0.3                       | V     |

| Forward CONTROL Pin Input Voltage V <sub>IN</sub>  |                   |                                                                   | 0 to V <sub>DD</sub> + 0.3 | V     |

| Reverse CONTROL Pin Input Voltage V <sub>RIN</sub> |                   |                                                                   | V <sub>DD</sub> – 6.0 V    | V     |

| Continuous Output Current I <sub>OUT</sub>         |                   | Positive $I_{LOAD}$ flow is from VOUT1 to VOUT2, $T_J < T_J(max)$ | ±200                       | mA    |

| Peak Output Current I <sub>OUT(pk)</sub>           |                   | <1 ms                                                             | ±400                       | mA    |

| Operating Ambient Temperature T <sub>A</sub>       |                   | Range E                                                           | -40 to 85                  | °C    |

| Maximum Junction Temperature T <sub>J</sub> (max)  |                   |                                                                   | 165                        | °C    |

| Storage Temperature T <sub>stg</sub>               |                   |                                                                   | -65 to 170                 | °C    |

#### Thermal Characteristics may require derating at maximum conditions, see Power Derating section

| Characteristic Symbol      |                | Test Conditions*                                     | Value | Units |

|----------------------------|----------------|------------------------------------------------------|-------|-------|

| Package Thermal Resistance |                | On 2-layer PCB, with 0.23 in.2 copper area each side | 125   | °C/W  |

|                            | $R_{	heta JA}$ | On 4-layer PCB based on JEDEC standard               | 64    | °C/W  |

<sup>\*</sup>Additional thermal information available on the Allegro website

## **Terminal List**

## **Pin-out Diagram**

| N | lumber | Name    | Function                               |  |

|---|--------|---------|----------------------------------------|--|

|   | 1      | VDD     | Supply voltage                         |  |

|   | 2      | CONTROL | Input for PWM, braking, and sleep mode |  |

|   | 3      | NC      | No connection                          |  |

|   | 4      | GND     | Ground                                 |  |

|   | 5      | VOUT1   | First output                           |  |

|   | 6      | VOUT2   | Second output                          |  |

<sup>&</sup>lt;sup>1</sup>Contact Allegro for additional packing options.

<sup>2</sup>Allegro products sold in DFN package types are not intended for automotive applications.

#### OPERATING CHARACTERISTICS Valid over supply voltage and ambient temperature ranges, unless otherwise noted

| Characteristics                               | Symbol                 | Test Conditions                                                        | Min.                  | Тур. | Max.                  | Unit |

|-----------------------------------------------|------------------------|------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| Electrical Characteristics                    |                        |                                                                        |                       |      |                       |      |

| Supply Voltage V <sub>DD</sub>                |                        | $T_J < T_J(max)$                                                       | 2.0                   | _    | 4.2                   | V    |

| Extended Range of Supply Voltage <sup>1</sup> | V <sub>DDE</sub>       | $T_J < T_J(max)$                                                       | 1.8                   | _    | 4.2                   | V    |

| Supply Current                                | I <sub>DD</sub>        | V <sub>IN</sub> >V <sub>INHI</sub> , T <sub>A</sub> = 25°C, no load    | _                     | 4    | 6                     | mA   |

|                                               |                        | V <sub>IN</sub> < V <sub>INLO</sub> , T <sub>A</sub> = 25°C            | _                     | _    | 10                    | μΑ   |

|                                               |                        | I <sub>OUT</sub> = 70 mA, V <sub>DD</sub> = 2 V, T <sub>A</sub> = 25°C | _                     | 3.9  | _                     | Ω    |

| Total Output On-Resistance <sup>2</sup>       | R <sub>DS(on)</sub>    | I <sub>OUT</sub> = 70 mA, V <sub>DD</sub> = 3 V, T <sub>A</sub> = 25°C | _                     | 2.6  | _                     | Ω    |

|                                               |                        | I <sub>OUT</sub> = 70 mA, V <sub>DD</sub> = 4 V, T <sub>A</sub> = 25°C | _                     | 2.2  | _                     | Ω    |

| Reverse Battery Current                       | I <sub>RDD</sub>       | V <sub>RDD</sub> = -4.2 V                                              | _                     | _    | -10                   | mA   |

| CONTROL Pin Input Threshold                   | V <sub>INHI</sub>      |                                                                        | 0.7 × V <sub>DD</sub> | _    | -                     | V    |

|                                               | V <sub>INLO</sub>      |                                                                        | _                     | _    | 0.2 × V <sub>DD</sub> | V    |

| CONTROL Pin Input Current                     | I <sub>IN</sub>        | V <sub>IN</sub> = 3.0 V                                                | _                     | 1.0  | 5                     | μΑ   |

| ONTROL Pin Input Frequency f <sub>PWM</sub>   |                        |                                                                        | 100                   | 384  | 800                   | kHz  |

| CONTROL Prebraking Time <sup>3</sup>          | t <sub>PB</sub>        |                                                                        | _                     | -    | 2.5                   | ms   |

| Thermal Shutdown Limit                        | T <sub>JTSD</sub>      | Device is active                                                       | _                     | 165  | _                     | °C   |

| Thermal Shutdown Hysteresis                   | T <sub>JTSD(HYS)</sub> | Device is active                                                       | _                     | 20   | -                     | °C   |

| Magnetic Characteristics <sup>4</sup>         |                        |                                                                        |                       |      |                       |      |

|                                               | B <sub>OP</sub>        |                                                                        | _                     | 35   | 75                    | G    |

| Magnetic Switchpoints                         | B <sub>RP</sub>        |                                                                        | <b>–</b> 75           | -35  | _                     | G    |

|                                               | B <sub>HYS</sub>       |                                                                        | _                     | 70   | _                     | G    |

|                                               | VOUT1                  | B < B <sub>RP</sub>                                                    | _                     | LOW  | _                     | V    |

| Output Polority                               |                        | B > B <sub>OP</sub>                                                    | _                     | HIGH | _                     | V    |

| Output Polarity                               | VOLITO                 | B < B <sub>RP</sub>                                                    | _                     | HIGH | -                     | V    |

|                                               | VOUT2                  | B > B <sub>OP</sub>                                                    | _                     | LOW  | _                     | V    |

$<sup>^{1}\</sup>text{Extended V}_{\text{DD}} \text{ range affects R}_{\text{DS(on)}} \text{ and B}_{x}.$   $^{2}\text{Total Output On-Resistance} = R_{\text{DS(on)Q1}} + R_{\text{DS(on)Q4}}, \text{ or R}_{\text{DS(on)Q2}} + R_{\text{DS(on)Q3}}, \text{ where Qx refers to the internal full-bridge transistors.}$   $^{3}\text{Device initiates braking algorithm if the CONTROL pin is pulled to GND for longer than the maximum specified CONTROL Prebraking Time.}$

<sup>41</sup> G (gauss) = 0.1 mT (millitesla).

## **Functional Description**

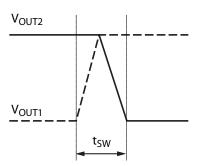

#### **Soft Switching**

The A1448 device includes a soft-switching algorithm that controls the output switching slew rate for both output pins. As a result, the A1448 device is ideal for use in applications requiring low audible switching noise and low EMI. The resistance of the output transistors is controlled to ensure the smooth switching of the outputs, as illustrated in figure 1.

# **CONTROL** Pin Functionality: PWM, Braking, and Sleep Mode Input

The CONTROL input pin accepts an external signal that can control the speed of the output bridge, initiate active braking, and put the device into sleep mode. Signals higher than the  $V_{\rm INHI}$

threshold will turn on the output bridge according to the applied magnetic field. Applying a PWM signal to the CONTROL pin will turn the bridge on and off according to the PWM duty cycle. When the CONTROL pin is pulled to GND, the device initiates its internal active braking algorithm to stop the motor. After braking, the device enters micro-power sleep mode. The device becomes active again when the CONTROL pin is pulled higher than  $V_{\rm INHI}$ .

#### **Antistall Algorithm**

If a stall condition occurs, the device will execute an antistall algorithm to re-start the motor.

Figure 1. A1448 output soft switching with a 30  $\Omega$  resistive load

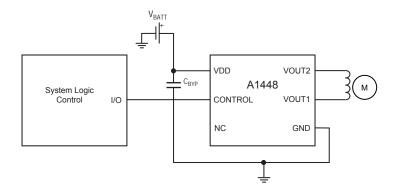

## **Application Information**

Figure 2 shows a typical vibration motor application in which speed control, active braking, and sleep mode are required on the CONTROL pin.

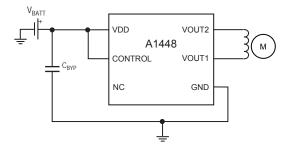

Figure 3 shows an application circuit in which 100% duty cycle is required. Tying the CONTROL pin to  $V_{DD}$  disables the braking function and the sleep mode. The user must control supply in order to control the speed of the motor. This represents a 2-wire motor design.

Note that:

- No external diode is required for reverse battery protection because the protection is fully integrated into the IC.

- Thermal shutdown also is integrated, to protect the device against inadvertent output shorts during manufacturing or testing.

- A bypass capacitor of 0.1  $\mu F$  is required. This capacitor is usually included on the end user PCB and therefore not necessary on the motor PCB.

Figure 2. Three-wire vibration motor application circuit

Figure 3. Two-wire vibration motor application circuit

## **Power Derating**

The device must be operated below the maximum junction temperature of the device,  $T_J$  (max). Under certain combinations of peak conditions, reliable operation may require derating supplied power or improving the heat dissipation properties of the application. This section presents a procedure for correlating factors affecting operating  $T_J$ . (Thermal data is also available on the Allegro MicroSystems website.)

The package thermal resistance,  $R_{\theta JA}$ , is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to the ambient air. Its primary component is the effective thermal conductivity, K, of the printed circuit board, including adjacent devices and traces. Radiation from the die through the device case,  $R_{\theta JC}$ , is relatively small component of  $R_{\theta JA}$ . Ambient air temperature,  $T_A$ , and air motion are significant external factors, damped by overmolding.

The effect of varying power levels (Power Dissipation,  $P_D$ ), can be estimated. The following formulas represent the fundamental relationships used to estimate  $T_J$ , at various  $P_D$  levels.

$$P_{D} = V_{IN} \times I_{IN} \tag{1}$$

$$\Delta T = P_D \times R_{\theta IA} \tag{2}$$

$$T_{I} = T_{\Delta} + \Delta T \tag{3}$$

For a load of 30  $\Omega$ , and given common conditions such as:  $T_A$ = 25°C,  $V_{DD}$  = 3 V,  $I_{DD}$  = 83 mA,  $V_{LOAD}$  = 2.43 V,  $I_{LOAD}$  = 81 mA, and  $R_{\theta JA}$  = 125 °C/W, (see figure 5)

then

$$P_D = V_{DD} \times I_{DD} - V_{LOAD} \times I_{LOAD}$$

= 3 V × 83 mA – 2.43 V × 81 mA

= 52.17 mW

$\Delta T = P_D \times R_{\theta JA}$

= 52.17 mW × 125 °C/W

= 7°C

$T_J = T_A + \Delta T$

= 25°C + 7°C

= 32°C

A worst-case estimate,  $P_D(max)$ , represents the maximum allowable power level, without exceeding  $T_J(max)$ , at a selected  $R_{\theta JA}$  and  $T_A.$

Figure 5. A1448 typical application

6

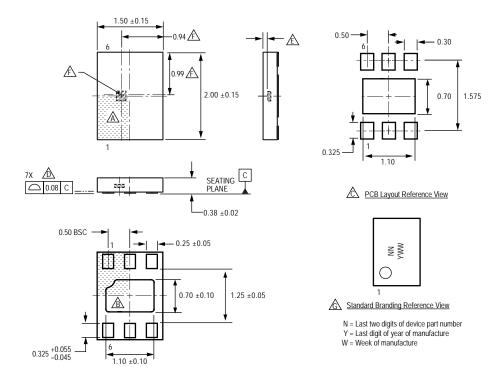

## Package EW, 6-Pin MLP/DFN

For Reference Only, not for tooling use (refernce DWG-2856; similar to JEDEC Type 1, MO-229X2BCD)  $\,$

Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

Reference land pattern layout (reference IPC7351 SON50P200X200X100-9M);

SON50P200X200X100-9M);

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Coplanarity includes exposed thermal pad and terminals

Active Area Depth 0.15 mm REF

Hall Element (not to scale)

Branding scale and appearance at supplier discretion

A1448

# Low-Voltage, Full-Bridge Brushless DC Motor Driver with Integrated Hall Sensor IC, PWM Speed Control, Soft-Switching, and Reverse Battery and Short Circuit Protection

#### **Revision History**

| Revision | Revision Date    | Date Description of Revision |  |  |

|----------|------------------|------------------------------|--|--|

| Rev. 4   | October 26, 2011 | Update Selection Guide       |  |  |

|          |                  |                              |  |  |

Copyright ©2008-2011, Allegro MicroSystems, Inc.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com