# **Dual CAN Flexible Data-Rate Transceiver**

#### **Features**

- Supports both "classic" CAN 2.0 and CAN FD physical layer requirements

- Optimized for CAN FD (Flexible Data-Rate) at 2, 5 and 8 Mbps Operation:

- Maximum Propagation Delay: 120 ns

- Loop Delay Symmetry: -10%/+10% (2 Mbps)

- Implements ISO-11898-2 and ISO-11898-5 Standard Physical Layer Requirements

- Very Low Standby Current (5 μA per transceiver, typical)

- Two Fully Independent V<sub>DDX</sub> and V<sub>SSX</sub> Pins per CAN FD Transceiver for Added Flexibility and Reliability:

- Optimal for redundant CAN networks

- · Compatible to 5V MCUs

- Functional Behavior Predictable Under All Supply Conditions:

- Device is in Unpowered mode if V<sub>DDX</sub> drops below undervoltage level

- An unpowered node or brown-out event will not load the CAN bus

- · Detection of Ground Fault:

- Permanent dominant detection on TXDX

- Permanent dominant detection on bus

- Power-on Reset and Undervoltage Lock-out on V<sub>DDX</sub> Pin

- Protection against Damage due to Short-Circuit Conditions (positive or negative battery voltage)

- Protection against High-Voltage Transients in Automotive Environments

- · Automatic Thermal Shutdown Protection

- Suitable for 12V and 24V Systems

- Meets or exceeds Stringent Automotive Design Requirements, including "Hardware Requirements for LIN, CAN and FlexRay™ Interfaces in Automotive Applications", Version 1.3, May 2012:

- Conducted emissions @ 2 Mbps with Common-Mode Choke (CMC)

- Direct Power Injection (DPI) @ 2 Mbps with CMC

- Meets SAE J2962/2 "Communication Transceivers Qualification Requirements – CAN".

- Passes radiated emissions at 2 Mbps without a CMC

- High Noise Immunity due to Differential Bus Implementation

- High ESD Protection on CANHx and CANLx, Meets IEC61000-4-2, up to ±6 kV

- Available in 14-Lead SOIC

- · Temperature Ranges:

- Extended (E): -40°C to +125°C

- High (H): -40°C to +150°C

### **Description**

The MCP25612FD is a second generation, dual CAN FD transceiver from Microchip Technology Inc. It offers all of the features from two fully independent MCP2561FD CAN transceivers, except for the SPLIT pin. It ensures Loop Delay Symmetry in order to support the higher data rates required for CAN FD. The maximum propagation delay is improved to support a longer bus length.

The device meets the automotive requirements for CAN FD bit rates, low quiescent current, robust Electromagnetic Compatibility (EMC) and Electrostatic Discharge (ESD).

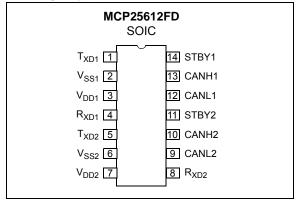

# **Package Types**

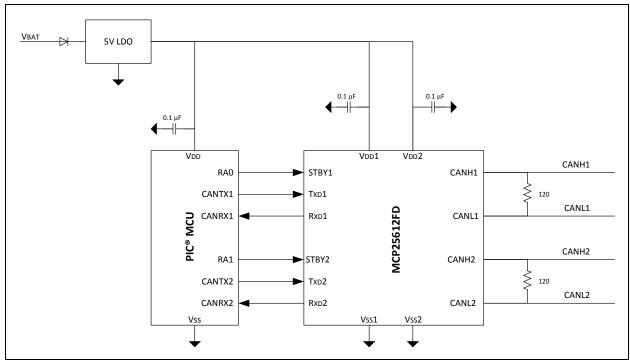

# **Typical Applications**

#### Automotive

- Powertrain

- Body Control

- · Gateway

- · Chassis and Safety

- · Infotainment

#### Industrial

- · Factory Automation

- Gateway

- Server Backplanes

- Elevators

- · Robotics

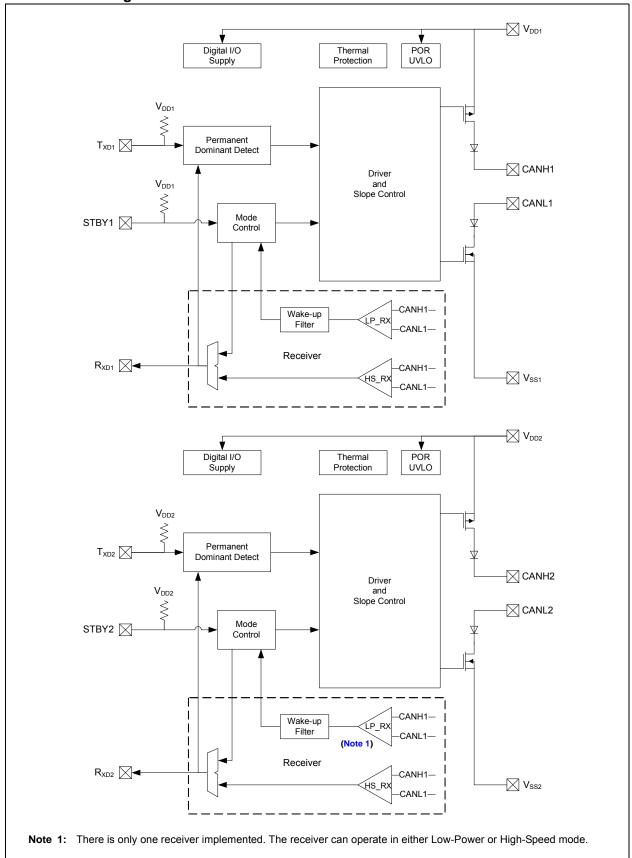

# **Device Block Diagram**

#### 1.0 DEVICE OVERVIEW

The MCP25612FD is a dual fully independent, CAN FD transceiver Fault tolerant device that serves as the interface between a CAN protocol controller and the physical bus. The MCP25612FD device provides differential transmit and receive capability for the CAN protocol controller, and is fully compatible with the ISO 11898-2 and ISO 11898-5 standards.

The Loop Delay Symmetry is ensured to support data rates up to 8 Mbps for CAN FD (Flexible Data-Rate). The maximum propagation delay was improved to support longer bus length.

Typically, each node in a CAN system must have a device to convert the digital signals generated by a CAN controller to signals suitable for transmission over the bus cabling (differential output). It also provides a buffer between the CAN controller and the high-voltage spikes that can be generated on the CAN bus by outside sources.

#### 1.1 Mode Control Block

The MCP25612FD supports two modes of operation between the two CAN transceivers independently:

- · Normal Mode

- · Standby Mode

These modes are summarized in Table 1-1.

#### 1.1.1 NORMAL MODE

Normal mode is selected by applying low-level voltage to the STBYx pin. The driver block is operational and can drive the bus pins. The slopes of the output signals on CANHx and CANLx are optimized to produce minimal Electromagnetic Emissions (EME).

The high-speed differential receiver is active.

#### 1.1.2 STANDBY MODE

The device may be placed in Standby mode by applying a high-level voltage to the STBYx pin. In Standby mode, the transmitter and the high-speed part of the receiver are switched off to minimize power consumption. The low-power receiver and the wake-up filter blocks are enabled to monitor the bus for activity. The Receive pin  $(R_{XDX})$  will show a delayed representation of the CAN bus due to the wake-up filter.

The CAN controller gets interrupted by a negative edge on the  $R_{XDX}$  pin (Dominant state on the CAN bus). The CAN controller must put the MCP25612FD back into Normal mode, using the STBYx pin, in order to enable high-speed data communication.

The CAN bus wake-up function requires V<sub>DDX</sub> to be in valid range.

TABLE 1-1: MODES OF OPERATION

| Mode    | STBYx Pin | R <sub>XDX</sub> Pin        |                             |  |  |  |

|---------|-----------|-----------------------------|-----------------------------|--|--|--|

| Wode    | SIDIXPIII | Low                         | High                        |  |  |  |

| Normal  | Low       | Bus is dominant             | Bus is recessive            |  |  |  |

| Standby | High      | Wake-up request is detected | No wake-up request detected |  |  |  |

#### 1.2 Transmitter Function

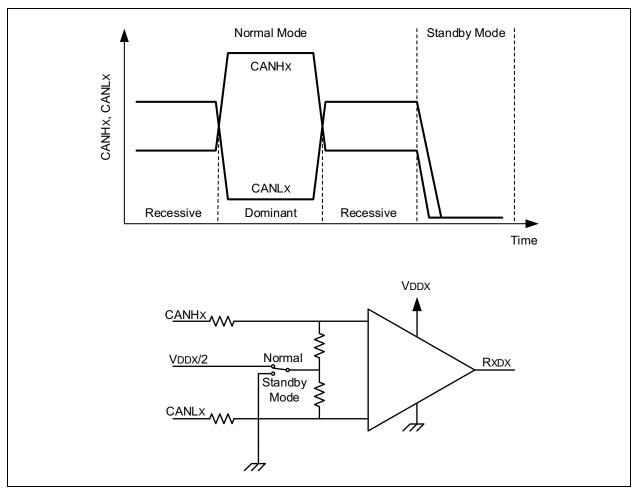

The CAN bus has two states:

- · Dominant state

- · Recessive state

A Dominant state occurs when the differential voltage between CANHx and CANLx is greater than  $V_{DIFFX(D)(I)}$ . A Recessive state occurs when the differential voltage is less than  $V_{DIFFX(R)(I)}$ . The Dominant and Recessive states correspond to the Low and High state of the  $T_{XDX}$  input pin, respectively. However, a Dominant state initiated by another CAN node will override a Recessive state on the CAN bus.

#### 1.3 Receiver Function

In Normal mode, the  $R_{XDX}$  output pin reflects the differential bus voltage between CANHx and CANLx. The Low and High states of the  $R_{XDX}$  output pin correspond to the Dominant and Recessive states of the CAN bus, respectively.

#### 1.4 Internal Protection

CANHx and CANLx are protected against battery short circuits and electrical transients that can occur on the CAN bus. This feature prevents destruction of the transmitter output stage during such a Fault condition.

The device is further protected from excessive current loading by thermal shutdown circuitry that disables the output drivers when the junction temperature exceeds a nominal limit of +175°C. All other parts of the chip remain operational and the chip temperature is lowered due to the decreased power dissipation in the transmitter outputs. This protection is essential to protect against bus line short-circuit induced damage. The activation of the internal protection in one of the transceivers will not affect the other one since these are fully independent.

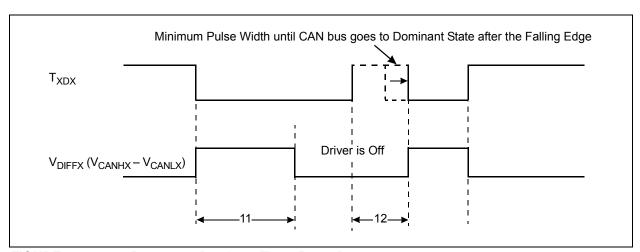

### 1.5 Permanent Dominant Detection

The MCP25612FD device prevents two conditions:

- Permanent dominant condition on T<sub>XDX</sub>

- · Permanent dominant condition on the bus

In Normal mode, if the MCP25612FD detects an extended Low state on the  $\mathsf{T}_{XDX}$  input, it will disable the CANHx and CANLx output drivers in order to prevent the corruption of data on the CAN bus. The drivers will remain disabled until  $\mathsf{T}_{XDX}$  goes to the High state.

In Standby mode, if the MCP25612FD detects an extended Dominant condition on the bus, it will set the  $R_{XDX}$  pin to the Recessive state. This allows the attached controller to go to Low-Power mode until the dominant issue is corrected.  $R_{XDX}$  is latched high until a Recessive state is detected on the bus and the wake-up function is enabled again.

Both conditions have a time-out of 1.25 ms (typical). This implies a maximum bit time of 69.44  $\mu$ s (14.4 kHz), allowing up to 18 consecutive dominant bits on the bus. The permanent dominant detection in one of the transceivers will not affect the other one since these are fully independent.

# 1.6 Power-on Reset (POR) and Undervoltage Detection

The MCP25612FD has undervoltage detection on the  $V_{DDX}$  supply pin. The typical undervoltage threshold is 4V.

When the device is powered on, CANHx and CANLx remain in a High-Impedance state until  $V_{DDX}$  exceeds its undervoltage level. Once powered on, CANHx and CANLx will enter a High-Impedance state if the voltage level at  $V_{DDX}$  drops below the undervoltage level, providing voltage brown-out protection during normal operation.

In Normal mode, the receiver output is forced to the Recessive state during an undervoltage condition on  $V_{DDX}$ . In Standby mode, the low-power receiver is only enabled when the  $V_{DDX}$  supply voltage rises above its undervoltage threshold. Once the threshold voltage is reached, the low-power receiver is no longer controlled by the POR comparator and remains operational down to about 2.5V on the  $V_{DDX}$  supply.

# 2.0 ELECTRICAL CHARACTERISTICS

# 2.1 Absolute Maximum Ratings†

| V <sub>DDX</sub>                                                                          | 7.0V                            |

|-------------------------------------------------------------------------------------------|---------------------------------|

| DC Voltage at T <sub>XDX</sub> , R <sub>XDX</sub> , STBYx and V <sub>SSX</sub>            | 0.3V to V <sub>DDX</sub> + 0.3V |

| DC Voltage at CANHx and CANLx                                                             | 58V to +58V                     |

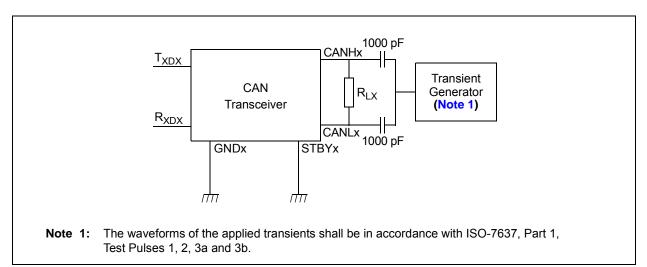

| Transient Voltage on CANHx, CANLx (ISO-7637) (see Figure 2-4)                             | 150V to +100V                   |

| Storage Temperature                                                                       | 55°C to +150°C                  |

| Operating Ambient Temperature                                                             | 40°C to +150°C                  |

| Virtual Junction Temperature, T <sub>VJ</sub> (IEC60747-1)                                | 40°C to +190°C                  |

| Soldering Temperature of Leads (10 seconds)                                               | +300°C                          |

| ESD Protection on CANHx and CANLx Pins (IEC 61000-4-2); 330Ω/150 pF; Unpowered; Con       | tact Discharge±6 kV             |

| ESD Protection on CANHx and CANLx Pins (IEC 801; Human Body Model); 1500 $\Omega$ /100 pF | ±8 kV                           |

| ESD Protection on All Other Pins (IEC 801; Human Body Model); 1500Ω/100 pF                | ±4 kV                           |

| ESD Protection on All Pins (IEC 801; Machine Model); 0Ω/200 pF                            | ±300V                           |

| ESD Protection on All Pins (IEC 801; Charge Device Model)                                 | ±750V                           |

† NOTICE: Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 2.2 Specifications

TABLE 2-1: DC ELECTRICAL SPECIFICATIONS

| <b>Electrical Characteristics:</b> Extended (E): $T_{AMB}$ = -40°C to +125°C; High (H): $T_{AMB}$ = -40°C to +150°C; $V_{DDX}$ = 4.5V to 5.5V, $R_{LX}$ = 60 $\Omega$ , $C_{LX}$ = 100 pF; unless otherwise specified. |                   |     |     |     |       |                                  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|-------|----------------------------------|--|

| Characteristic                                                                                                                                                                                                         | Sym               | Min | Тур | Max | Units | Conditions                       |  |

| Supply (V <sub>DDX</sub> Pin)                                                                                                                                                                                          |                   |     |     |     |       |                                  |  |

| Voltage Range                                                                                                                                                                                                          | $V_{DDX}$         | 4.5 | _   | 5.5 |       |                                  |  |

| Supply Current                                                                                                                                                                                                         | $I_{DD}$          |     | 5   | 10  | mA    | Recessive; $V_{TXDX} = V_{DDX}$  |  |

| (per transceiver)                                                                                                                                                                                                      |                   | _   | 45  | 70  |       | Dominant; V <sub>TXDX</sub> = 0V |  |

| Standby Current (per transceiver)                                                                                                                                                                                      | I <sub>DDS</sub>  | _   | 5   | 15  | μA    |                                  |  |

| High Level of the POR Comparator                                                                                                                                                                                       | V <sub>PORH</sub> | 3.8 | _   | 4.3 | V     |                                  |  |

| Low Level of the POR Comparator                                                                                                                                                                                        | V <sub>PORL</sub> | 3.4 | _   | 4.0 | V     |                                  |  |

| Hysteresis of the POR Comparator                                                                                                                                                                                       | V <sub>PORD</sub> | 0.3 | _   | 0.8 | V     |                                  |  |

Note 1: Characterized; not 100% tested.

2: -12V to 12V is ensured by characterization, tested from -2V to 7V.

TABLE 2-1: DC ELECTRICAL SPECIFICATIONS (CONTINUED)

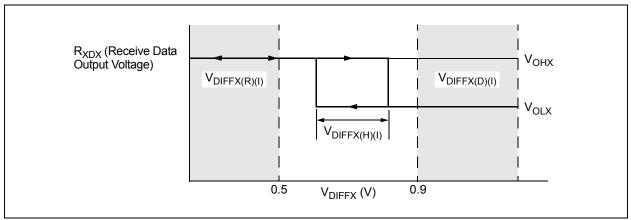

**Electrical Characteristics:** Extended (E):  $T_{AMB} = -40^{\circ}C$  to  $+125^{\circ}C$ ; High (H):  $T_{AMB} = -40^{\circ}C$  to  $+150^{\circ}C$ ;  $V_{DDX}$  = 4.5V to 5.5V,  $R_{LX}$  = 60 $\Omega$ ,  $C_{LX}$  = 100 pF; unless otherwise specified. Characteristic Units **Conditions** Sym Min Typ Max **Bus Line Transmitter (CANHx, CANLx)**  $0.5 \, V_{DDX}$ CANHx, CANLx: 2.0 3.0  $V_{TXDX} = V_{DDX}$ ; no load  $V_{O(R)}$ Recessive Bus Output Voltage  $\overline{STBYx} = V_{TXDX} = V_{DDX}$ ; no load CANHx. CANLx:  $V_{O(S)}$ -0.1 0.0 V +0.1 Bus Output Voltage in Standby -24V < V<sub>CAN</sub> < +24V Recessive Output Current  $I_{O(R)}$ -5 +5 mΑ CANHx: Dominant  $T_{TXDX} = 0$ ;  $R_{LX} = 50$  to  $65\Omega$  $V_{O(D)}$ 2.75 3.50 4.50 Output Voltage CANLx: Dominant 0.50 1.50 2.25  $R_{IX} = 50 \text{ to } 65\Omega$ Output Voltage Symmetry of Dominant  $V_{O(D)(M)}$ -400 0 +400 mV  $V_{TXDX} = V_{SSX}$  (Note 1) Output Voltage  $(V_{DDX} - V_{CANHX} - V_{CANLX})$ Dominant: Differential  $V_{TXDX} = V_{SSX}$ ;  $R_{LX} = 50$  to  $65\Omega$  (see Figure 2-1 and Figure 2-3) ٧ V<sub>O(DIFF)</sub> 1.5 2.0 3.0 Output Voltage Recessive: -120 0 12 mV  $V_{TXDX} = V_{DDX}$ (see Figure 2-1 and Figure 2-3) Differential Output Voltage  $V_{TXDX} = V_{DDX}$ ; no load -500 0 50 mV (see Figure 2-1 and Figure 2-3) CANHx: Short-Circuit -120 85  $V_{TXDX} = V_{SSX}; V_{CANHX} = 0V;$ mΑ I<sub>O(SC)</sub> CANLx: Floating **Output Current** Same as above, but  $V_{DDX} = 5V$ ; -100 mΑ  $T_{AMB} = +25^{\circ}C$  (Note 1) CANLx: Short-Circuit 75  $V_{TXDX} = V_{SSX}; V_{CANLX} = 18V;$ +120 mΑ **Output Current** CANHx: Floating +100 Same as above, but  $V_{DDX} = 5V$ ; mΑ  $T_{AMB} = +25^{\circ}C \text{ (Note 1)}$ **Bus Line Receiver (CANHx, CANLx)** Recessive Differential -1.0 +0.5 Normal mode:  $V_{DIFFX(R)(I)}$ -12V < V<sub>(CANHX</sub>, <sub>CANLX)</sub> < +12V (see Figure 2-5) **(Note 2)** Input Voltage -1.0 +0.4 Standby mode; -12V < V<sub>(CANHX</sub>, <sub>CANLX)</sub> < +12V (see Figure 2-5) (Note 2) Dominant Differential Normal mode:  $V_{DIFFX(D)(I)}$ 0.9  $V_{DDX}$ -12V < V<sub>(CANHX</sub>, <sub>CANLX)</sub> < +12V Input Voltage (see Figure 2-5) (Note 2) Standby mode; 1.0  $V_{DDX}$ -12V < V<sub>(CANHX</sub>, <sub>CANLX)</sub> < +12V (see Figure 2-5) (Note 2)

Note 1: Characterized; not 100% tested.

2: -12V to 12V is ensured by characterization, tested from -2V to 7V.

TABLE 2-1: DC ELECTRICAL SPECIFICATIONS (CONTINUED)

Electrical Characteristics: Extended (E): T<sub>AMB</sub> = -40°C to +125°C; High (H): T<sub>AMB</sub> = -40°C to +150°C;  $V_{DDX}$  = 4.5V to 5.5V,  $R_{LX}$  = 60 $\Omega$ ,  $C_{LX}$  = 100 pF; unless otherwise specified. Units **Conditions** Characteristic Sym Min Typ Max Bus Line Receiver (CANHx, CANLx) (Continued) Differential 0.5 0.7 0.9 Normal mode: V<sub>TH(DIFF)</sub> Receiver Threshold  $-12V < V_{(CANHX, CANLX)} < +12V$ (see Figure 2-5) (Note 2) 0.4 Standby mode; 1.0 -12V < V<sub>(CANHX, CANLX)</sub> < +12V (see Figure 2-5) (**Note 2**) Normal mode (see Figure 2-5) Differential 50 200 mV V<sub>HYS(DIFF)</sub> Input Hysteresis (Note 1) (Note 1) Common-Mode 10 30  $R_{IN}$ kΩ Input Resistance Common-Mode -1 0 +1  $V_{CANHX} = V_{CANLX}$  (Note 1)  $R_{IN(M)}$ Resistance Matching Differential Input Resistance (Note 1) R<sub>IN(DIFF)</sub> 10 100 kΩ Common-Mode 20 pF  $V_{TXDX} = V_{DDX}$  (Note 1)  $C_{IN(CM)}$ Input Capacitance  $V_{TXDX} = V_{DDX}$  (Note 1) Differential 10 C<sub>IN(DIFF)</sub> Input Capacitance CANHx, CANLx:  $V_{DDX} = V_{TXDX} = V_{STBYX} = 0V;$  $I_{LI}$ -5 +5  $V_{CANHX} = V_{CANLX} = 5V$ Input Leakage Digital Input Pins (TXDX, STBYx) High-Level Input Voltage  $0.7 V_{DDX}$  $V_{DDX} + 0.3$ ٧  $V_{IH}$ Low-Level Input Voltage  $V_{IL}$ -0.3  $0.3 V_{DDX}$ ٧ -1 High-Level Input Current +1 μΑ  $I_{IH}$ μΑ TXDX: Low-Level Input Current -270 -150 -30  $I_{IL(TXDX)}$ STBYx: Low-Level Input -30 -1 μΑ I<sub>IL(STBYX)</sub> Current Receive Data Output (R<sub>XDX</sub>)  $V_{DDX} - 0.4$ High-Level Output Voltage  $V_{OHX}$  $I_{OH} = -2 \text{ mA}$ ; typical -4 mA Low-Level Output Voltage  $V_{OLX}$ 0.4  $I_{OI}$  = 4 mA; typical 8 mA Thermal Shutdown °C Shutdown 185 -12V < V<sub>(CANHX, CANLX)</sub> < +12V  $T_{J(SD)}$ 165 175 Junction Temperature Shutdown 20 30  $-12V < V_{(CANHX, CANLX)} < +12V$  $T_{J(HYST)}$ Temperature Hysteresis (Note 1)

Note 1: Characterized; not 100% tested.

2: -12V to 12V is ensured by characterization, tested from -2V to 7V.

FIGURE 2-1: Physical Bit Representation and Simplified Bias Implementation.

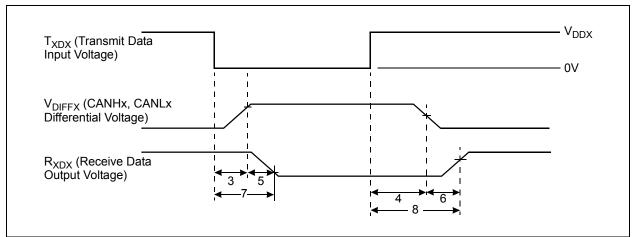

TABLE 2-2: AC ELECTRICAL SPECIFICATIONS

Electrical Characteristics: Extended (E):  $T_{AMB}$  = -40°C to +125°C; High (H):  $T_{AMB}$  = -40°C to +150°C;  $V_{DDX}$  = 4.5V to 5.5V,  $R_{LX}$  = 60Ω,  $C_{LX}$  = 100 pF; unless otherwise specified.

| Param. | Sym                       | Characteristic                                                          |      | Тур  | Max   | Units | Conditions                                                                                                |

|--------|---------------------------|-------------------------------------------------------------------------|------|------|-------|-------|-----------------------------------------------------------------------------------------------------------|

| 1      | t <sub>BIT</sub>          | Bit Time                                                                |      |      | 69.44 | μs    |                                                                                                           |

| 2      | f <sub>BIT</sub>          | Bit Frequency                                                           | 14.4 | _    | 8000  | kHz   |                                                                                                           |

| 3      | t <sub>TXDX-BUSON</sub>   | Delay T <sub>XDX</sub> Low to Bus Dominant                              | _    | 65   | _     | ns    | (Note 1)                                                                                                  |

| 4      | t <sub>TXDX-BUSOFF</sub>  | Delay T <sub>XDX</sub> High to Bus Recessive                            | _    | 90   | _     | ns    | (Note 1)                                                                                                  |

| 5      | t <sub>BUSON-RXDX</sub>   | Delay Bus Dominant to R <sub>XDX</sub>                                  | _    | 60   | _     | ns    | (Note 1)                                                                                                  |

| 6      | t <sub>BUSOFF-RXDX</sub>  | Delay Bus Recessive to R <sub>XDX</sub>                                 | _    | 65   | _     | ns    | (Note 1)                                                                                                  |

| 7      | t <sub>TXDX-RXDX</sub>    | Propagation Delay T <sub>XDX</sub> to R <sub>XDX</sub>                  | _    | 90   | 120   | ns    |                                                                                                           |

|        |                           |                                                                         | _    | 120  | 180   | ns    | $R_{LX} = 120\Omega,$<br>$C_{LX} = 200 \text{ pF (Note 1)}$                                               |

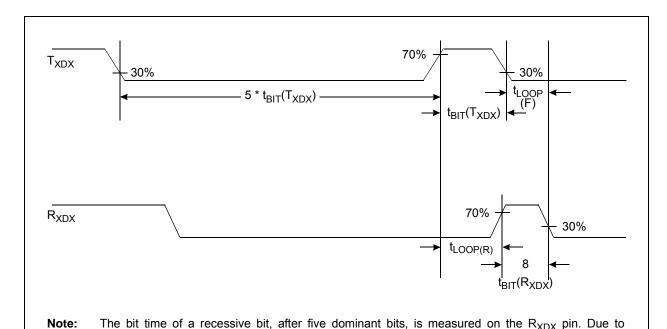

| 8a     | t <sub>BIT(RXDX),2M</sub> | Recessive Bit Time on R <sub>XDX</sub> – 2 Mbps,<br>Loop Delay Symmetry | 450  | 485  | 550   | ns    | $t_{BIT(TXDX)}$ = 500 ns<br>(see Figure 2-10)                                                             |

|        |                           |                                                                         | 400  | 460  | 550   | ns    | $t_{BIT(TXDX)}$ = 500 ns<br>(see Figure 2-10);<br>$R_{LX}$ = 120 $\Omega$ ,<br>$C_{LX}$ = 200 pF (Note 1) |

| 8b     | t <sub>BIT(RXDX),5M</sub> | Recessive Bit Time on R <sub>XDX</sub> – 5 Mbps,<br>Loop Delay Symmetry | 160  | 185  | 220   | ns    | $t_{BIT(TXDX)}$ = 200 ns<br>(see Figure 2-10)                                                             |

| 8c     | t <sub>BIT(RXDX),8M</sub> | Recessive Bit Time on R <sub>XDX</sub> – 8 Mbps,<br>Loop Delay Symmetry | 85   | 105  | 140   | ns    | t <sub>BIT(TXDX)</sub> = 120 ns<br>(see Figure 2-10)<br>( <b>Note 1</b> )                                 |

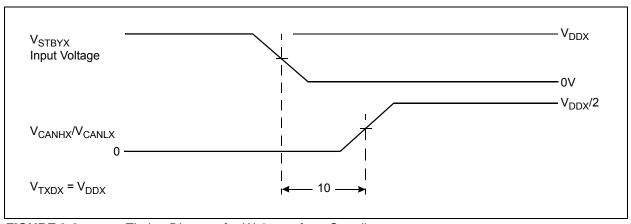

| 9      | t <sub>FLTR(WAKE)</sub>   | Delay Bus Dominant to R <sub>XDX</sub> (Standby mode)                   | 0.5  | 1    | 4     | μs    | Standby mode                                                                                              |

| 10     | t <sub>WAKE</sub>         | Delay Standby to Normal Mode                                            | 5    | 25   | 40    | μs    | Negative edge on STBYx                                                                                    |

| 11     | t <sub>PDT</sub>          | Permanent Dominant Detect Time                                          | _    | 1.25 | _     | ms    | T <sub>XDX</sub> = 0V                                                                                     |

| 12     | t <sub>PDTR</sub>         | Permanent Dominant Timer Reset                                          |      | 100  |       | ns    | The shortest Recessive pulse on T <sub>XDX</sub> or CAN bus to reset Permanent Dominant Timer             |

Note 1: Characterized, not 100% tested.

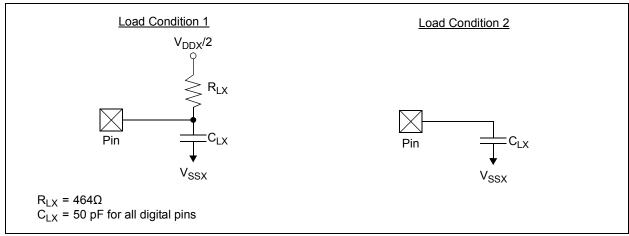

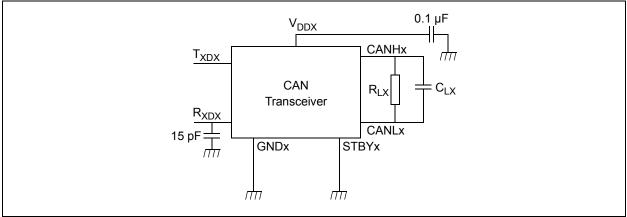

FIGURE 2-2: Test Load Conditions.

FIGURE 2-3: Test Circuit for Electrical Characteristics.

FIGURE 2-4: Test Circuit for Automotive Transients.

FIGURE 2-5: Hysteresis of the Receiver.

#### 2.3 Terms and Definitions

A number of terms are defined in ISO-11898 that are used to describe the electrical characteristics of a CAN transceiver device. These terms and definitions are summarized in this section.

#### 2.3.1 BUS VOLTAGE

$V_{CANLX}$  and  $V_{CANHX}$  denote the voltages of the bus line wires, CANLx and CANHx, relative to the ground of each individual CAN node.

# 2.3.2 COMMON-MODE BUS VOLTAGE RANGE

Boundary voltage levels of  $V_{CANLX}$  and  $V_{CANHX}$ , with respect to ground, for which proper operation will occur if up to the maximum number of CAN nodes are connected to the bus.

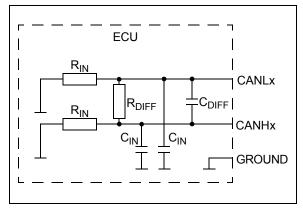

# 2.3.3 DIFFERENTIAL INTERNAL CAPACITANCE, C<sub>DIFF</sub> (OF A CAN NODE)

Capacitance seen between CANLx and CANHx during the Recessive state, when the CAN node is disconnected from the bus (see Figure 2-6).

# 2.3.4 DIFFERENTIAL INTERNAL RESISTANCE, R<sub>DIFF</sub> (OF A CAN NODE)

Resistance seen between CANLx and CANHx, during the Recessive state, when the CAN node is disconnected from the bus (see Figure 2-6).

# 2.3.5 DIFFERENTIAL VOLTAGE, V<sub>DIFFX</sub> (OF CAN BUS)

Differential voltage of the two-wire CAN bus value:  $V_{DIFFX} = V_{CANHX} - V_{CANLX}$ .

# 2.3.6 INTERNAL CAPACITANCE, C<sub>IN</sub> (OF A CAN NODE)

Capacitance seen between CANLx (or CANHx) and ground, during the Recessive state, when the CAN node is disconnected from the bus (see Figure 2-6).

# 2.3.7 INTERNAL RESISTANCE, R<sub>IN</sub> (OF A CAN NODE)

Resistance seen between CANLx (or CANHx) and ground, during the Recessive state, when the CAN node is disconnected from the bus (see Figure 2-6).

FIGURE 2-6:

Physical Layer Definitions.

# 2.4 Timing Diagrams and Specifications

FIGURE 2-7: Timing Diagram for AC Characteristics.

FIGURE 2-8: Timing Diagram for Wake-up from Standby.

FIGURE 2-9: Permanent Dominant Timer Reset Detect.

The bit time of a recessive bit, after five dominant bits, is measured on the  $R_{XDX}$  pin. Due to asymmetry of the loop delay, and the CAN transceiver not being a push-pull driver, the recessive bits tend to shorten.

**FIGURE 2-10:** Timing Diagram for Loop Delay Symmetry.

**TABLE 2-3:** THERMAL SPECIFICATIONS

| Parameter                    | Symbol            | Min. | Тур. | Max. | Units | Test Conditions |  |

|------------------------------|-------------------|------|------|------|-------|-----------------|--|

| Temperature Ranges           |                   |      |      |      |       |                 |  |

| Specified Temperature Range  | T <sub>A</sub>    | -40  | _    | +125 | °C    |                 |  |

|                              |                   | -40  | _    | +150 |       |                 |  |

| Operating Temperature Range  | T <sub>A</sub>    | -40  | _    | +150 | °C    |                 |  |

| Storage Temperature Range    | T <sub>A</sub>    | -55  | _    | +150 | °C    |                 |  |

| Thermal Package Resistance   |                   |      |      |      |       |                 |  |

| Thermal Resistance, 14L-SOIC | $\theta_{\sf JA}$ | _    | 90.8 | _    | °C/W  |                 |  |

### 3.0 PIN DESCRIPTIONS

Table 3-1 describes the MCP25612FD device pinout.

TABLE 3-1: MCP25612FD PIN FUNCTIONS

| SOIC | Pin Name           | Pin Type | Pin Function                     |  |

|------|--------------------|----------|----------------------------------|--|

| 1    | T <sub>XD1</sub>   | I        | Transmit Data Input              |  |

| 2    | V <sub>SS1</sub>   | Power    | Ground                           |  |

| 3    | V <sub>DD1</sub>   | Power    | Transceiver Supply Voltage       |  |

| 4    | R <sub>XD1</sub>   | 0        | Receive Data Output              |  |

| 5    | T <sub>XD2</sub>   | I        | Transmit Data Input              |  |

| 6    | V <sub>SS2</sub>   | Power    | Ground                           |  |

| 7    | $V_{\mathrm{DD2}}$ | Power    | Transceiver Supply Voltage       |  |

| 8    | R <sub>XD2</sub>   | 0        | Receive Data Output              |  |

| 9    | CANL2              | I/O      | CAN Low-Level Bus Line           |  |

| 10   | CANH2              | I/O      | CAN High-Level Bus Line          |  |

| 11   | STBY2              | I        | Standby Mode Input (active-high) |  |

| 12   | CANL1              | I/O      | CAN Low-Level Bus Line           |  |

| 13   | CANH1              | I/O      | CAN High-Level Bus Line          |  |

| 14   | STBY1              | I        | Standby Mode Input (active-high) |  |

# 3.1 Transmitter Data Input Pin (T<sub>XDX</sub>)

The CAN transceivers drive the differential output pins, CANHx and CANLx, according to  $T_{XDX}.\,T_{XDX}$  is usually connected to the transmitter data output of the CAN controller device. When  $T_{XDX}$  is low, CANHx and CANLx are in the Dominant state. When  $T_{XDX}$  is high, CANHx and CANLx are in the Recessive state, provided that another CAN node is not driving the CAN bus with a Dominant state.  $T_{XDX}$  is connected to an internal pull-up resistor (nominal 33 kΩ) to  $V_{DDX}.$

# 3.2 Ground Supply Pin (V<sub>SSX</sub>)

Ground supply pin.

### 3.3 Supply Voltage Pin (V<sub>DDX</sub>)

Positive supply voltage pin. Supplies the transmitter and receiver, including the wake-up receiver.

# 3.4 Receiver Data Output Pin (R<sub>XDX</sub>)

$R_{XDX}$  is a CMOS-compatible output that drives high or low, depending on the differential signals on the CANHx and CANLx pins, and is usually connected to the receiver data input of the CAN controller device.  $R_{XDX}$  is high when the CAN bus is in the Recessive state and low in the Dominant state.  $R_{XDX}$  is supplied by  $V_{DDX}.$

### 3.5 CAN Low Pin (CANLx)

The CANLx output drives the low side of the CAN differential bus. This pin is also tied internally to the receive input comparator. CANLx disconnects from the bus when MCP25612FD is not powered.

### 3.6 CAN High Pin (CANHx)

The CANHx output drives the high side of the CAN differential bus. This pin is also tied internally to the receive input comparator. CANHx disconnects from the bus when MCP25612FD is not powered.

### 3.7 Standby Mode Input Pin (STBYx)

This pin selects between Normal or Standby mode. In Standby mode, the transmitter and high-speed receiver are turned off; only the low-power receiver and wake-up filter are active. STBYx is connected to an internal MOS pull-up resistor to  $V_{DDX}$ . The typical value is 660 k $\Omega$ .

# 4.0 TYPICAL APPLICATIONS

In order to meet some EMC/EMI requirements, a Common-Mode Choke (CMC) may be needed for data rates greater than 1 Mbps.

FIGURE 4-1: MCP25612FD Application.

#### 5.0 PACKAGING INFORMATION

#### 5.1 **Package Marking Information**

### Example

Legend: XX...X Customer-specific information

Year code (last digit of calendar year) YY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn) (e3)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available

characters for customer-specific information.

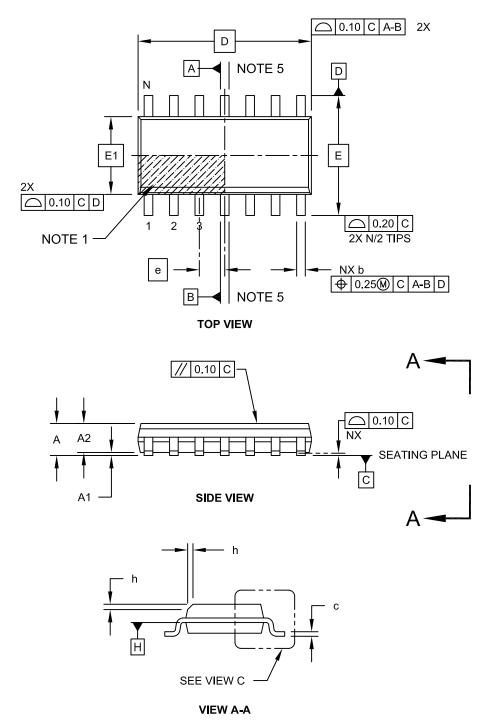

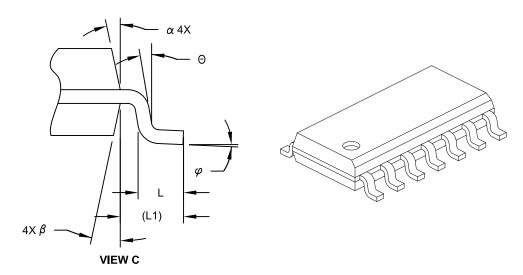

# 5.2 Package Details

# 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065C Sheet 1 of 2

# 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N    | <b>ILLIMETER</b> | S        |      |  |  |

|--------------------------|------|------------------|----------|------|--|--|

| Dimension Lir            | nits | MIN              | NOM      | MAX  |  |  |

| Number of Pins           | N    |                  | 14       |      |  |  |

| Pitch                    | е    |                  | 1.27 BSC |      |  |  |

| Overall Height           | Α    | -                | -        | 1.75 |  |  |

| Molded Package Thickness | A2   | 1.25             | -        | _    |  |  |

| Standoff §               | A1   | 0.10             | -        | 0.25 |  |  |

| Overall Width            | Е    | 6.00 BSC         |          |      |  |  |

| Molded Package Width     | E1   | 3.90 BSC         |          |      |  |  |

| Overall Length           | D    | 8.65 BSC         |          |      |  |  |

| Chamfer (Optional)       | h    | 0.25 - 0.50      |          |      |  |  |

| Foot Length              | L    | 0.40             | -        | 1.27 |  |  |

| Footprint                | L1   |                  | 1.04 REF |      |  |  |

| Lead Angle               | Θ    | 0°               | -        | -    |  |  |

| Foot Angle               | φ    | 0°               | -        | 8°   |  |  |

| Lead Thickness           |      | 0.10             | -        | 0.25 |  |  |

| Lead Width               | b    | 0.31             | =        | 0.51 |  |  |

| Mold Draft Angle Top     | α    | 5°               | -        | 15°  |  |  |

| Mold Draft Angle Bottom  | β    | 5°               | -        | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

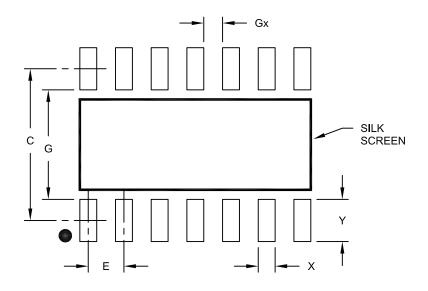

# 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                       | N.               | <b>IILLIMETER</b> | S    |      |  |

|-----------------------|------------------|-------------------|------|------|--|

| Dimension             | Dimension Limits |                   | NOM  | MAX  |  |

| Contact Pitch         | Е                | 1.27 BSC          |      |      |  |

| Contact Pad Spacing   | С                |                   | 5.40 |      |  |

| Contact Pad Width     | Х                |                   |      | 0.60 |  |

| Contact Pad Length    | Υ                |                   |      | 1.50 |  |

| Distance Between Pads | Gx               | 0.67              |      |      |  |

| Distance Between Pads | G                | 3.90              |      |      |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

NOTES:

# **APPENDIX A: REVISION HISTORY**

**Revision A (June 2015)**

Original release of this document.

**NOTES:**

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact the factory or one of the sales offices listed on the back page.

| PART NO.           | <u>-x</u>                                                                                | Ex | amples:                                                                    |

|--------------------|------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------|

| Device T           | emperature Package<br>Range                                                              | a) | MCP25612FD-E/SL: Extended Temperature, 14LD SOIC package                   |

| Device:            | MCP25612FD: Dual CAN FD Transceiver MCP25612FDT: Dual CAN FD Transceiver (Tape and Reel) | b) | MCP25612FDT-E/SL: Tape and Reel, Extended Temperature, 14LD SOIC package   |

|                    | (1000 2.12 1.001)                                                                        | c) | MCP25612FD-H/SL: High Temperature,<br>14LD SOIC package.                   |

| Temperature Range: | E = $-40$ °C to $+125$ °C (Extended)<br>H = $-40$ °C to $+150$ °C (High)                 | d) | MCP25612FDT-H/SL: Tape and Reel,<br>High Temperature,<br>14LD SOIC package |

| Package:           | SL= 14-Lead Plastic Small Outline - Narrow,<br>3.90 mm Body                              |    |                                                                            |

NOTES:

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- · Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELoQ, KEELoQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63277-484-2

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **Worldwide Sales and Service**

#### **AMERICAS**

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address:

www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi. MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Vieio, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongging Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan

Tel: 86-769-8702-9880

China - Hangzhou Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan Tel: 86-27-5980-5300

Fax: 86-27-5980-5118 China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870

Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Taiwan - Tainei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Pforzheim** Tel: 49-7231-424750

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw

Tel: 48-22-3325737 Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15