**IC card interface****TDA8004AT****FEATURES**

- 3 or 5 V supply for the IC (GND and  $V_{DD}$ )

- Step-up converter for  $V_{CC}$  generation (separately powered with a 5 V  $\pm 10\%$  supply,  $V_{DDP}$  and PGND)

- 3 specific protected half duplex bidirectional buffered I/O lines (C4, C7 and C8)

- $V_{CC}$  regulation (5 or 3 V  $\pm 5\%$  on  $2 \times 100$  nF or  $1 \times 100$  nF and  $1 \times 220$  nF multilayer ceramic capacitors with low ESR,  $I_{CC} < 65$  mA at  $4.5$  V  $< V_{DDP} < 6.5$  V, current spikes of 40 nAs up to 20 MHz, with controlled rise and fall times, filtered overload detection approximately 90 mA)

- Thermal and short-circuit protections on all card contacts

- Automatic activation and deactivation sequences (initiated by software or by hardware in the event of a short-circuit, card take-off, overheating or supply drop-out)

- Enhanced ESD protection on card side ( $> 6$  kV)

- 26 MHz integrated crystal oscillator

- Clock generation for the card up to 20 MHz (divided by 1, 2, 4 or 8 through CLKDIV1 and CLKDIV2 signals) with synchronous frequency changes

- Non-inverted control of RST via pin RSTIN

- ISO 7816, GSM11.11 and EMV (payment systems) compatibility

- Supply supervisor for spikes killing during power-on and power-off

- One multiplexed status signal  $\overline{OFF}$ .

**APPLICATIONS**

- IC card readers for banking

- Electronic payment

- Identification

- Pay TV.

**GENERAL DESCRIPTION**

The TDA8004AT is a complete low cost analog interface for asynchronous 3 or 5 V smart cards. It can be placed between the card and the microcontroller with very few external components to perform all supply protection and control functions.

**ORDERING INFORMATION**

| TYPE<br>NUMBER | PACKAGE |                                                            |          |

|----------------|---------|------------------------------------------------------------|----------|

|                | NAME    | DESCRIPTION                                                | VERSION  |

| TDA8004AT      | SO28    | plastic small outline package; 28 leads; body width 7.5 mm | SOT136-1 |

## IC card interface

## TDA8004AT

## QUICK REFERENCE DATA

| SYMBOL               | PARAMETER                                          | CONDITIONS                                                     | MIN. | TYP. | MAX. | UNIT    |

|----------------------|----------------------------------------------------|----------------------------------------------------------------|------|------|------|---------|

| <b>Supplies</b>      |                                                    |                                                                |      |      |      |         |

| $V_{DD}$             | supply voltage                                     |                                                                | 2.7  | —    | 6.5  | V       |

| $V_{DDP}$            | step-up supply voltage                             |                                                                | 4.5  | 5    | 6.5  | V       |

| $I_{DD}$             | supply current                                     | inactive mode; $V_{DD} = 3.3$ V;<br>$f_{XTAL} = 10$ MHz        | —    | —    | 1.2  | mA      |

|                      |                                                    | active mode; $V_{DD} = 3.3$ V;<br>$f_{XTAL} = 10$ MHz; no load | —    | —    | 1.5  | mA      |

| $I_{DDP}$            | step-up supply current                             | inactive mode; $V_{DDP} = 5$ V;<br>$f_{XTAL} = 10$ MHz         | —    | —    | 0.1  | mA      |

|                      |                                                    | active mode; $V_{DDP} = 5$ V;<br>$f_{XTAL} = 10$ MHz; no load  | —    | —    | 18   | mA      |

| <b>Card supply</b>   |                                                    |                                                                |      |      |      |         |

| $V_{CC}$             | card supply voltage including<br>ripple            | 5 V card                                                       | 4.75 | —    | 5.25 | V       |

|                      |                                                    | DC $ I_{CC}  < 65$ mA                                          | 4.65 | —    | 5.25 | V       |

|                      |                                                    | AC current spikes of 40 nAs                                    |      |      |      |         |

|                      |                                                    | 3 V card                                                       | 2.85 | —    | 3.15 | V       |

| $V_{i(ripple)(p-p)}$ | ripple voltage on $V_{CC}$<br>(peak-to-peak value) | DC $ I_{CC}  < 65$ mA                                          | 2.76 | —    | 3.20 | V       |

|                      |                                                    | AC current spikes of 40 nAs                                    |      |      |      |         |

| $ I_{CC} $           | card supply current                                | $V_{CC}$ from 0 to 5 or to 3 V                                 | —    | —    | 65   | mA      |

| <b>General</b>       |                                                    |                                                                |      |      |      |         |

| $f_{CLK}$            | card clock frequency                               |                                                                | 0    | —    | 20   | MHz     |

| $t_{de}$             | deactivation cycle duration                        |                                                                | 60   | 80   | 100  | $\mu$ s |

| $P_{tot}$            | continuous total power dissipation                 | $T_{amb} = -25$ to $+85$ °C                                    | —    | —    | 0.56 | W       |

| $T_{amb}$            | ambient temperature                                |                                                                | —25  | —    | +85  | °C      |

## IC card interface

## TDA8004AT

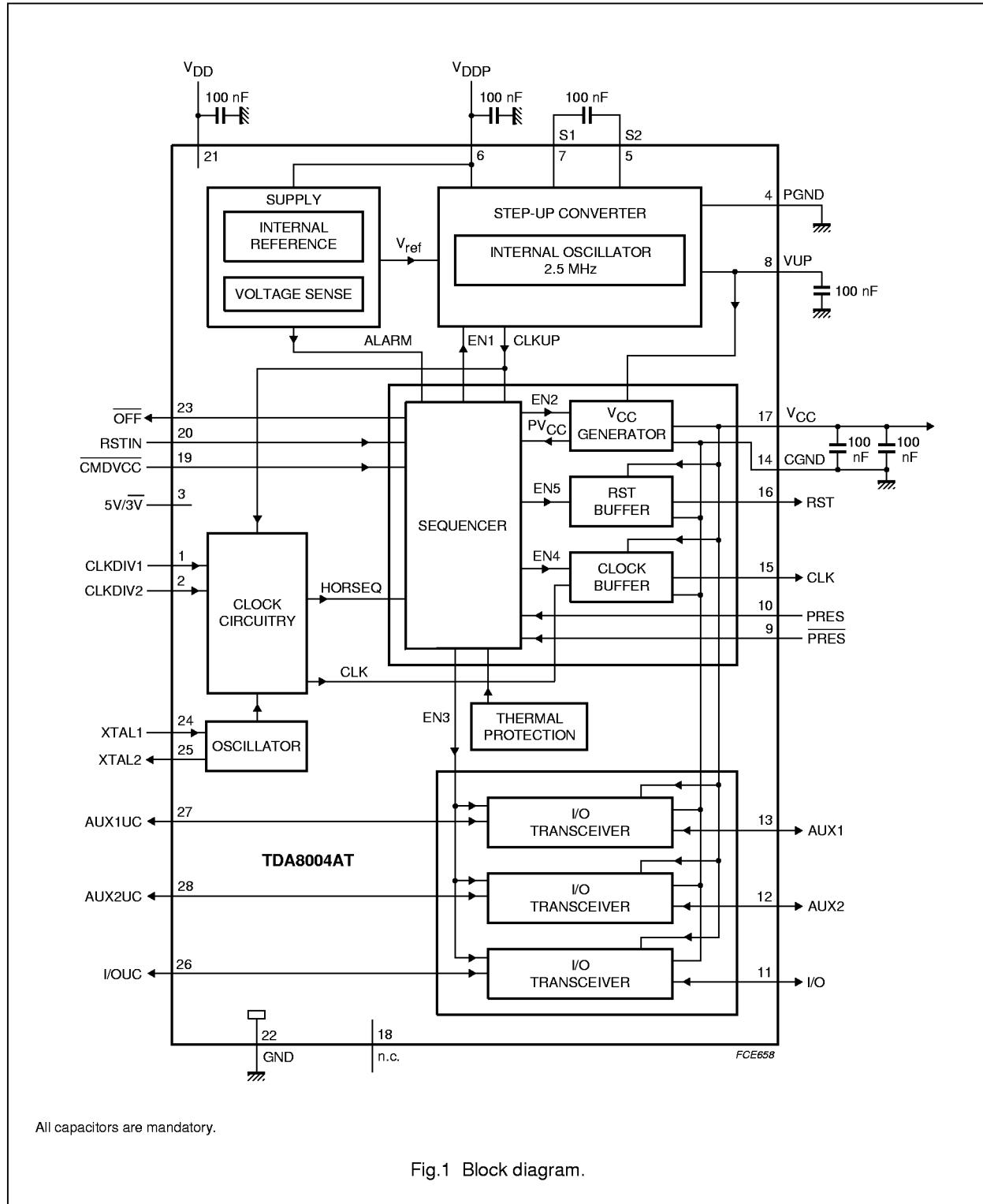

## BLOCK DIAGRAM

## IC card interface

## TDA8004AT

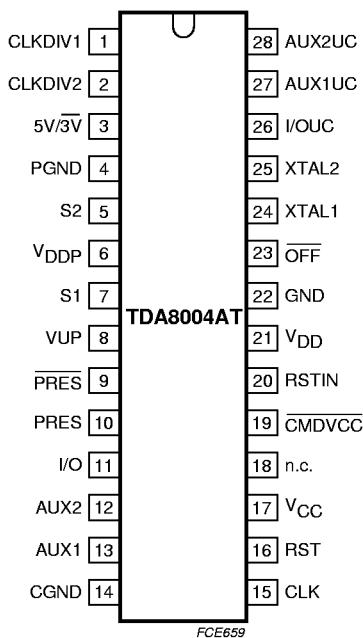

## PINNING

| SYMBOL    | PIN | I/O    | DESCRIPTION                                                                                                                                                                                                |

|-----------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKDIV1   | 1   | I      | control with CLKDIV2 for choosing CLK frequency                                                                                                                                                            |

| CLKDIV2   | 2   | I      | control with CLKDIV1 for choosing CLK frequency                                                                                                                                                            |

| 5V/3V     | 3   | I      | control signal for selecting $V_{CC} = 5$ V (HIGH) or $V_{CC} = 3$ V (LOW)                                                                                                                                 |

| PGND      | 4   | supply | power ground for step-up converter                                                                                                                                                                         |

| S2        | 5   | I/O    | capacitance connection for step-up converter (a 100 nF capacitor with $ESR < 100$ m $\Omega$ must be connected between pins S1 and S2)                                                                     |

| $V_{DDP}$ | 6   | supply | power supply voltage for step-up converter                                                                                                                                                                 |

| S1        | 7   | I/O    | capacitance connection for step-up converter (a 100 nF capacitor with $ESR < 100$ m $\Omega$ must be connected between pins S1 and S2)                                                                     |

| VUP       | 8   | O      | output of step-up converter (a 100 nF capacitor with $ESR < 100$ m $\Omega$ must be connected to PGND)                                                                                                     |

| PRES      | 9   | I      | card presence contact input (active LOW); if PRES or $\bar{PRES}$ is true, then the card is considered as present                                                                                          |

| PRES      | 10  | I      | card presence contact input (active HIGH); if PRES or $\bar{PRES}$ is true, then the card is considered as present                                                                                         |

| I/O       | 11  | I/O    | data line to and from card (C7) (internal 10 k $\Omega$ pull-up resistor connected to $V_{CC}$ )                                                                                                           |

| AUX2      | 12  | I/O    | auxiliary line to and from card (C8) (internal 10 k $\Omega$ pull-up resistor connected to $V_{CC}$ )                                                                                                      |

| AUX1      | 13  | I/O    | auxiliary line to and from card (C4) (internal 10 k $\Omega$ pull-up resistor connected to $V_{CC}$ )                                                                                                      |

| CGND      | 14  | supply | ground for card signals                                                                                                                                                                                    |

| CLK       | 15  | O      | clock to card (C3)                                                                                                                                                                                         |

| RST       | 16  | O      | card reset (C2)                                                                                                                                                                                            |

| $V_{CC}$  | 17  | O      | supply for card (C1); decouple to CGND with $2 \times 100$ nF or $1 \times 100$ nF and $1 \times 220$ nF capacitors with $ESR < 100$ m $\Omega$ (with 220 nF, the noise margin on $V_{CC}$ will be higher) |

| n.c.      | 18  | —      | not connected                                                                                                                                                                                              |

| CMDVCC    | 19  | I      | start activation sequence input from microcontroller (active LOW)                                                                                                                                          |

| RSTIN     | 20  | I      | card reset input from microcontroller (active HIGH)                                                                                                                                                        |

| $V_{DD}$  | 21  | supply | supply voltage                                                                                                                                                                                             |

| GND       | 22  | supply | ground                                                                                                                                                                                                     |

| OFF       | 23  | O      | NMOS interrupt to microcontroller (active LOW) with 20 k $\Omega$ internal pull-up resistor connected to $V_{DD}$ (refer section "Fault detection")                                                        |

| XTAL1     | 24  | I      | crystal connection or input for external clock                                                                                                                                                             |

| XTAL2     | 25  | O      | crystal connection (leave open circuit if an external clock source is used)                                                                                                                                |

| I/OUC     | 26  | I/O    | microcontroller data I/O line (internal 10 k $\Omega$ pull-up resistor connected to $V_{DD}$ )                                                                                                             |

| AUX1UC    | 27  | I/O    | auxiliary line to and from microcontroller (internal 10 k $\Omega$ pull-up resistor connected to $V_{DD}$ )                                                                                                |

| AUX2UC    | 28  | I/O    | auxiliary line to and from microcontroller (internal 10 k $\Omega$ pull-up resistor connected to $V_{DD}$ )                                                                                                |

## IC card interface

## TDA8004AT

Fig.2 Pin configuration.

## FUNCTIONAL DESCRIPTION

Throughout this document, it is assumed that the reader is familiar with ISO7816 norm terminology.

## Power supply

The supply pins for the IC are  $V_{DD}$  and GND.  $V_{DD}$  should be in the range from 2.7 to 6.5 V. All interface signals with the microcontroller are referenced to  $V_{DD}$ ; therefore be sure the supply voltage of the microcontroller is also at  $V_{DD}$ . All card contacts remain inactive during powering up or powering down. The sequencer is not activated until  $V_{DD}$  reaches  $V_{th2} + V_{hys(th2)}$  (see Fig.3). When  $V_{DD}$  falls below  $V_{th2}$ , an automatic deactivation of the contacts is performed.

For generating a  $5 V \pm 5\%$   $V_{CC}$  supply to the card, an integrated voltage doubler is incorporated. This step-up converter should be separately supplied by  $V_{DDP}$  and PGND (from 4.5 to 6.5 V). Due to large transient currents, the  $2 \times 100$  nF capacitors of the step-up converter should have an ESR of less than 100 m $\Omega$ , and be located as near as possible to the IC.

The supply voltages  $V_{DD}$  and  $V_{DDP}$  may be applied to the IC in any time sequence.

If a voltage between 7 and 9 V is available within the application, this voltage may be tied to pin VUP, thus blocking the step-up converter. In this case,  $V_{DDP}$  must be tied to  $V_{DD}$  and the capacitor between pins S1 and S2 may be omitted.

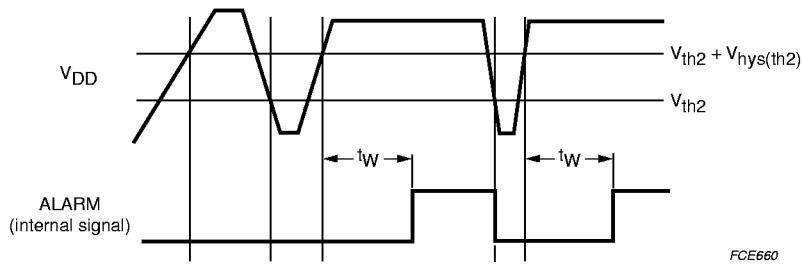

## Voltage supervisor

This block surveys the  $V_{DD}$  supply. A defined reset pulse of approximately 10 ms ( $t_W$ ) is used internally for maintaining the IC in the inactive mode during powering up or powering down of  $V_{DD}$  (see Fig.3)).

As long as  $V_{DD}$  is less than  $V_{th2} + V_{hys(th2)}$ , the IC will remain inactive whatever the levels on the command lines. This also lasts for the duration of  $t_W$  after  $V_{DD}$  has reached a level higher than  $V_{th2} + V_{hys(th2)}$ .

The system controller should not attempt to start an activation sequence during this time.

When  $V_{DD}$  falls below  $V_{th2}$ , a deactivation sequence of the contacts is performed.

## IC card interface

## TDA8004AT

Fig.3 Alarm as a function of  $V_{DD}$  ( $t_W = 10$  ms).**Clock circuitry**

The clock signal (CLK) to the card is either derived from a clock signal input on pin XTAL1 or from a crystal up to 26 MHz connected between pins XTAL1 and XTAL2.

The frequency may be chosen at  $f_{XTAL}$ ,  $\frac{1}{2}f_{XTAL}$ ,  $\frac{1}{4}f_{XTAL}$  or  $\frac{1}{8}f_{XTAL}$  via pins CLKDIV1 and CLKDIV2.

The frequency change is synchronous, which means that during transition, no pulse is shorter than 45% of the smallest period and that the first and last clock pulse around the change has the correct width.

In the case of  $f_{XTAL}$ , the duty factors are dependent on the signal at XTAL1.

In order to reach a 45% to 55% duty factor on pin CLK the input signal on XTAL1 should have a duty factor of 48% to 52% and transition times of less than 5% of the input signal period.

If a crystal is used with  $f_{XTAL}$ , the duty factor on pin CLK may be 45% to 55% depending on the layout and on the crystal characteristics and frequency.

In the other cases, it is guaranteed between 45% and 55% of the period.

The crystal oscillator runs as soon as the IC is powered-up. If the crystal oscillator is used, or if the clock pulse on XTAL1 is permanent, then the clock pulse will be applied to the card according to the timing diagram of the activation sequence (see Fig.5).

If the signal applied to XTAL1 is controlled by the microcontroller, then the clock pulse will be applied to the card by the microcontroller after completion of the activation sequence.

**Table 1** Clock circuitry definition

| CLKDIV1 | CLKDIV2 | CLK                   |

|---------|---------|-----------------------|

| 0       | 0       | $\frac{1}{8}f_{XTAL}$ |

| 0       | 1       | $\frac{1}{4}f_{XTAL}$ |

| 1       | 1       | $\frac{1}{2}f_{XTAL}$ |

| 1       | 0       | $f_{XTAL}$            |

## IC card interface

## TDA8004AT

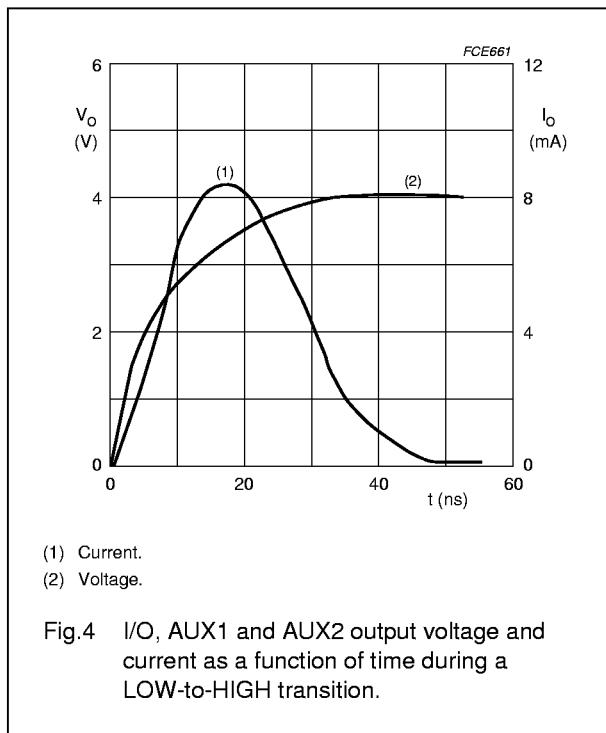

## I/O circuitry

The three data lines I/O, AUX1 and AUX2 are identical.

The Idle state is realized by data lines I/O and I/OUC being pulled HIGH via a 10 kΩ resistor (I/O to V<sub>CC</sub> and I/OUC to V<sub>DD</sub>).

I/O is referenced to V<sub>CC</sub>, and I/OUC to V<sub>DD</sub>, thus allowing operation with V<sub>CC</sub> ≠ V<sub>DD</sub>.

The first line on which a falling edge occurs becomes the master. An anti-latch circuit disables the detection of falling edges on the other line, which then becomes the slave.

After a time delay t<sub>d(edge)</sub> (approximately 200 ns), the N transistor on the slave line is turned on, thus transmitting the logic 0 present on the master line.

When the master line returns to logic 1, the P transistor on the slave line is turned on during the time delay t<sub>d(edge)</sub> and then both lines return to their Idle states.

This active pull-up feature ensures fast LOW-to-HIGH transitions; it is able to deliver more than 1 mA up to an output voltage of 0.9V<sub>CC</sub> on a 80 pF load. At the end of the active pull-up pulse, the output voltage only depends on the internal pull-up resistor, and on the load current (see Fig.4).

The maximum frequency on these lines is 1 MHz.

## Inactive state

After power-on reset, the circuit enters the inactive state. A minimum number of circuits are active while waiting for the microcontroller to start a session.

- All card contacts are inactive (approximately 200 Ω to GND)

- I/OUC, AUX1UC and AUX2UC are high impedance (10 kΩ pull-up resistor connected to V<sub>DD</sub>)

- Voltage generators are stopped

- XTAL oscillator is running

- Voltage supervisor is active.

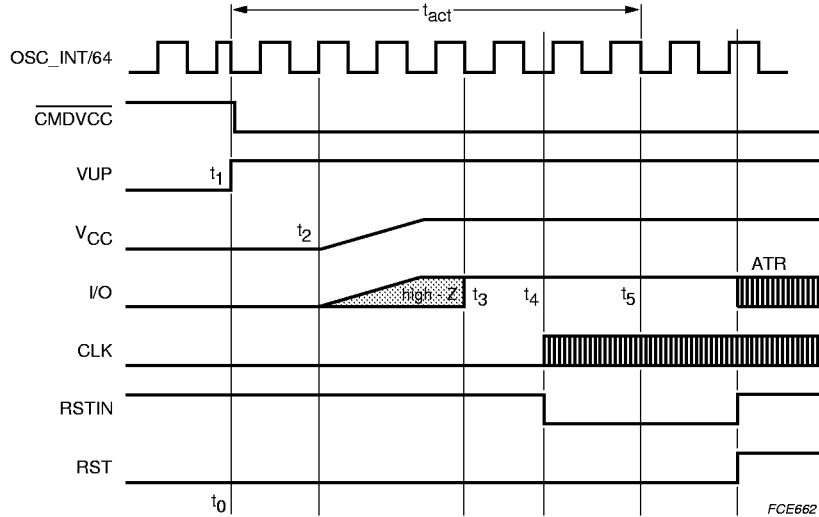

## Activation sequence

After power-on and, after the internal pulse width delay, the microcontroller may check the presence of the card with the signal OFF (OFF = HIGH while CMDVCC is HIGH means that the card is present; OFF = LOW while CMDVCC is HIGH means that no card is present).

If the card is in the reader (which is the case if PRES or PRE is true), the microcontroller may start a card session by pulling CMDVCC LOW.

The following sequence then occurs (see Fig.5):

- CMDVCC is pulled LOW (t<sub>0</sub>)

- The voltage doubler is started (t<sub>1</sub> ~ t<sub>0</sub>)

- V<sub>CC</sub> rises from 0 to 5 or 3V with a controlled slope (t<sub>2</sub> = t<sub>1</sub> + 1/23T) (I/O, AUX1 and AUX2 follow V<sub>CC</sub> with a slight delay); T is 64 times the period of the internal oscillator, approximately 25μs

- I/O, AUX1 and AUX2 are enabled (t<sub>3</sub> = t<sub>1</sub> + 4T)

- CLK is applied to the C3 contact (t<sub>4</sub>)

- RST is enabled (t<sub>5</sub> = t<sub>1</sub> + 7T).

The clock may be applied to the card in the following way:

Set RSTIN HIGH before setting CMDVCC LOW, and reset it LOW between t<sub>3</sub> and t<sub>5</sub>; CLK will start at this moment. RST will remain LOW until t<sub>5</sub>, where RST is enabled to be the copy of RSTIN. After t<sub>5</sub>, RSTIN has no further action on CLK. This is to allow a precise count of CLK pulses before toggling RST.

If this feature is not needed, then CMDVCC may be set LOW with RSTIN LOW. In this case, CLK will start at t<sub>3</sub>, and after t<sub>5</sub>, RSTIN may be set HIGH in order to get the Answer To Request (ATR) from the card.

## IC card interface

## TDA8004AT

Fig.5 Activation sequence.

**Active state**

When the activation sequence is completed, the TDA8004AT will be in the active state. Data is exchanged between the card and the microcontroller via the I/O lines. The TDA8004AT is designed for cards without  $V_{PP}$  (this is the voltage required to program or erase the internal non-volatile memory).

Depending on the layout and on the application test conditions (for example with an additional 1 pF cross capacitance between C2/C3 and C2/C7) it is possible that C2 is polluted with high frequency noise from C3. In this case, it will be necessary to connect a 220 pF capacitor between C2 and CGND.

It is recommended to:

1. Keep track C3 as far as possible from other tracks

2. Have straight connection between CGND and C5 (the 2 capacitors on C1 should be connected to this ground track)

3. Avoid ground loops between CGND, PGND and GND

4. Decouple  $V_{DDP}$  and  $V_{DD}$  separately; if the 2 supplies are the same in the application, then they should be connected in star on the main track.

With all these layout precautions, noise should be at an acceptable level, and jitter on C3 should be less than 100 ps. Refer to *Application Note AN97036* for specimen layouts.

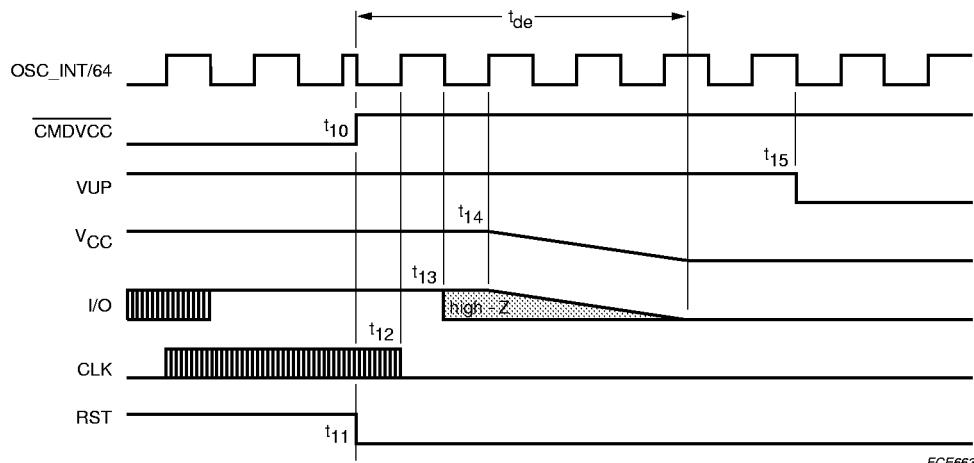

**Deactivation sequence**

When a session is completed, the microcontroller sets the CMDVCC line to the HIGH state. The circuit then executes an automatic deactivation sequence by counting the sequencer back and ends in the inactive state (see Fig.6):

- RST goes LOW  $\rightarrow (t_{11} = t_{10})$

- CLK is stopped LOW  $\rightarrow (t_{12} = t_{11} + \frac{1}{2}T)$ ; where T is approximately 25  $\mu$ s

- I/O, AUX1 and AUX2 are output into high-impedance state  $\rightarrow (t_{13} = t_{11} + T)$  (10 k $\Omega$  pull-up resistor connected to  $V_{CC}$ )

- $V_{CC}$  falls to zero  $\rightarrow (t_{14} = t_{11} + \frac{1}{2}3T)$ ; the deactivation sequence is completed when  $V_{CC}$  reaches its inactive state

- VUP falls to zero  $\rightarrow (t_{15} = t_{11} + 5T)$  and all card contacts become low-impedance to GND; I/OUC, AUX1UC and AUX2UC remain pulled up to  $V_{DD}$  via a 10 k $\Omega$  resistor.

## IC card interface

## TDA8004AT

Fig.6 Deactivation sequence.

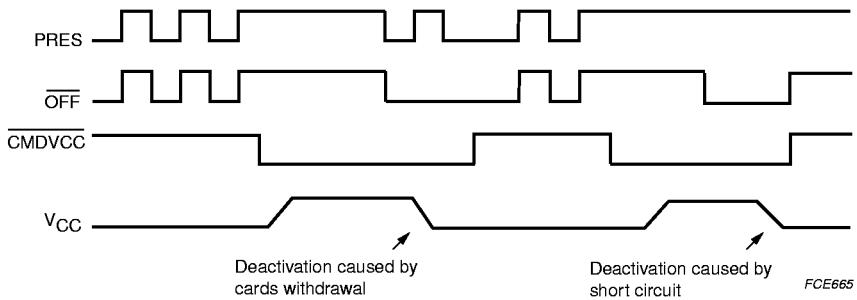

**Fault detection**

The following fault conditions are monitored by the circuit:

- Short-circuit or high current on  $V_{CC}$

- Removing card during transaction

- $V_{DD}$  dropping

- Overheating.

There are two different cases ((see Fig.7))

1.  $\overline{CMDVCC}$  HIGH: (outside a card session) then,  $\overline{OFF}$  is LOW if the card is not in the reader, and HIGH if the card is in the reader. A supply voltage drop on  $V_{DD}$  is detected by the supply supervisor which generates an internal power-on reset pulse, but does not act upon  $\overline{OFF}$ . The card is not powered-up, so no short-circuit or overheating is detected.

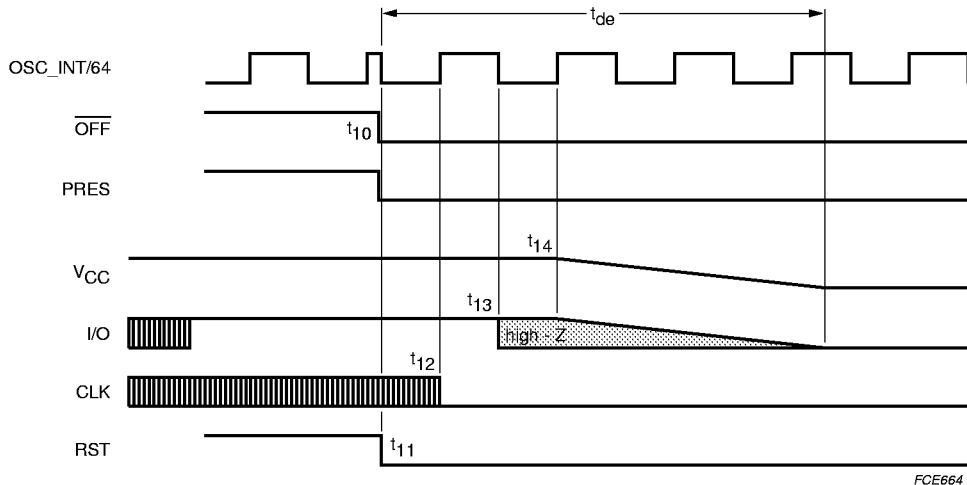

2.  $\overline{CMDVCC}$  LOW: (within a card session) then,  $\overline{OFF}$  falls LOW if the card is extracted, or if a short-circuit has occurred on  $V_{CC}$ , or if the temperature on the IC has become too high. As soon as the fault is detected, an emergency deactivation is automatically performed (see Fig.8).

When the system controller sets  $\overline{CMDVCC}$  back to HIGH, it may sense  $\overline{OFF}$  again in order to distinguish between a hardware problem or a card extraction. If a supply voltage drop on  $V_{DD}$  is detected whilst the card is activated, then an emergency deactivation will be performed, but  $\overline{OFF}$  remains HIGH.

Depending on the type of card presence switch within the connector (normally closed or normally open), and on the mechanical characteristics of the switch, a bouncing may occur on presence signals at card insertion or withdrawal.

There is no debounce feature in the device, so the software has to take it into account; however, the detection of card take off during active phase, which initiates an automatic deactivation sequence is done on the first True/False transition on  $PRES$  or  $\overline{PRES}$ , and is memorized until the system controller sets  $\overline{CMDVCC}$  HIGH.

So, the software may take some time waiting for presence switches to be stabilized without causing any delay on the necessary fast and normalized deactivation sequence.

## IC card interface

## TDA8004AT

Fig.7 Behaviour of  $\overline{\text{OFF}}$ ,  $\overline{\text{CMDVCC}}$ , PRES and  $V_{CC}$  (see also application note AN97036 for software decision algorithm on OFF signal).

Fig.8 Emergency deactivation sequence.

**$V_{CC}$  regulator**

The  $V_{CC}$  buffer is able to deliver up to 65 mA continuously (at 5V if  $5V/3V$  is HIGH or 3 V if  $5V/3V$  is LOW). It has an internal overload detection at approximately 90 mA.

This detection is internally filtered, allowing spurious current pulses up to 200 mA to be drawn by the card without causing a deactivation (the average current value must stay below 65 mA).

For  $V_{CC}$  accuracy reasons, a 100 nF capacitor with an ESR < 100 m $\Omega$  should be tied to CGND near pin 17, and a 100 nF (or better 220 nF) with same ESR should be tied to CGND near to the C1 contact.

## IC card interface

TDA8004AT

**LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 60134); notes 1 and 2.

| SYMBOL            | PARAMETER                                                                                                    | CONDITIONS                                 | MIN. | MAX. | UNIT |

|-------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|------|------|

| $V_{DD}, V_{DDP}$ | supply voltage                                                                                               |                                            | -0.3 | +7   | V    |

| $V_{n1}$          | voltage on pins XTAL1, XTAL2, 5V/3V, RSTIN, AUX2UC, AUX1UC, I/OUC, CLKDIV1, CLKDIV2, CMDVCC and OFF          |                                            | -0.3 | +7   | V    |

| $V_{n2}$          | voltage on card contact pins PRES, $\overline{\text{PRES}}$ , I/O, RST, AUX1, AUX2 and CLK                   |                                            | -0.3 | +7   | V    |

| $V_{n3}$          | voltage on pins VUP, S1 and S2                                                                               |                                            | -    | +9   | V    |

| $T_{stg}$         | IC storage temperature                                                                                       |                                            | -55  | +125 | °C   |

| $P_{tot}$         | continuous total power dissipation                                                                           | $T_{amb} = -25 \text{ to } +85 \text{ °C}$ | -    | 0.56 | W    |

| $T_j$             | junction temperature                                                                                         |                                            | -    | 150  | °C   |

| $V_{es1}$         | electrostatic voltage on pins I/O, RST, V <sub>CC</sub> , AUX1, CLK, AUX2, PRES and $\overline{\text{PRES}}$ |                                            | -6   | +6   | kV   |

| $V_{es2}$         | electrostatic voltage on all other pins                                                                      |                                            | -2   | +2   | kV   |

**Notes**

1. All card contacts are protected against any short with any other card contact.

2. Stress beyond these levels may cause permanent damage to the device. This is a stress rating only and functional operation of the device under this condition is not implied.

**HANDLING**

Every pin withstands the ESD test according to MIL-STD-883C class 3 for card contacts, class 2 for the remaining. Method 3015 (HBM; 1500  $\Omega$ ; 100 pF) 3 pulses positive and 3 pulses negative on each pin referenced to ground.

**THERMAL RESISTANCE**

| SYMBOL        | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|---------------|---------------------------------------------|-------------|-------|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air | 70    | K/W  |

## IC card interface

## TDA8004AT

## CHARACTERISTICS

$V_{DD} = 3.3$  V;  $V_{DDP} = 5$  V;  $T_{amb} = 25$  °C; all parameters remain within limits but are only statistically tested for the temperature range;  $f_{XTAL} = 10$  MHz; unless otherwise specified; all currents flowing into the IC are positive. When a parameter is specified as a function of  $V_{DD}$  or  $V_{CC}$  it means their actual value at the moment of measurement.

| SYMBOL                             | PARAMETER                                                                  | CONDITIONS                                                                      | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|------|

| <b>Temperature</b>                 |                                                                            |                                                                                 |      |      |      |      |

| $T_{amb}$                          | ambient temperature                                                        |                                                                                 | -25  | -    | +85  | °C   |

| <b>Supplies</b>                    |                                                                            |                                                                                 |      |      |      |      |

| $V_{DD}$                           | supply voltage                                                             |                                                                                 | 2.7  | -    | 6.5  | V    |

| $V_{DDP}$                          | supply voltage for the voltage doubler                                     |                                                                                 | 4.5  | 5    | 6.5  | V    |

| $V_o(V_{UP})$                      | output voltage on pin VUP from step-up converter                           |                                                                                 | -    | 5.5  | -    | V    |

| $V_i(V_{UP})$                      | input voltage to be applied on VUP in order to block the step-up converter |                                                                                 | 7    | -    | 9    | V    |

| $I_{DD}$                           | supply current                                                             | inactive mode                                                                   | -    | -    | 1.2  | mA   |

|                                    |                                                                            | active mode; $f_{CLK} = f_{XTAL}$ ; $C_L = 30$ pF                               | -    | -    | 1.5  | mA   |

| $I_P$                              | supply current for the step-up converter                                   | inactive mode                                                                   | -    | -    | 0.1  | mA   |

|                                    |                                                                            | active mode; $I_{CC} = 0$ ;<br>$f_{CLK} = f_{XTAL}$ ; $C_L = 30$ pF             |      |      |      |      |

|                                    |                                                                            | $I_{CC} = 0$<br>$I_{CC} = 65$ mA                                                | -    | -    | 18   | mA   |

|                                    |                                                                            |                                                                                 | -    | -    | 150  | mA   |

| $V_{th2}$                          | threshold voltage on $V_{DD}$ (falling)                                    |                                                                                 | 2.2  | -    | 2.4  | V    |

| $V_{hys(th2)}$                     | hysteresis on $V_{th2}$                                                    |                                                                                 | 50   | -    | 150  | mV   |

| $t_W$                              | width of the internal ALARM pulse                                          |                                                                                 | 6    | -    | 20   | ms   |

| <b>Card supply voltage; note 1</b> |                                                                            |                                                                                 |      |      |      |      |

| $V_{CC}$                           | output voltage including ripple                                            | inactive mode                                                                   | -0.1 | -    | +0.1 | V    |

|                                    |                                                                            | inactive mode; $I_{CC} = 1$ mA                                                  | -0.1 | -    | +0.4 | V    |

|                                    |                                                                            | active mode;<br>$ I_{CC}  < 65$ mA DC                                           |      |      |      |      |

|                                    |                                                                            | 5 V card                                                                        | 4.65 | -    | 5.25 | V    |

|                                    |                                                                            | 3 V card                                                                        | 2.85 | -    | 3.15 | V    |

|                                    |                                                                            | active mode; single current pulse of -100 mA; 2 $\mu$ s                         |      |      |      |      |

|                                    |                                                                            | 5 V card                                                                        | 4.65 | -    | 5.25 | V    |

|                                    |                                                                            | 3 V card                                                                        | 2.76 | -    | 3.15 | V    |

|                                    |                                                                            | active mode; current pulses of 40 nAs with<br>$ I_{CC}  < 200$ mA; $t < 400$ ns |      |      |      |      |

|                                    |                                                                            | 5 V card                                                                        | 4.65 | -    | 5.25 | V    |

|                                    |                                                                            | 3 V card                                                                        | 2.76 | -    | 3.20 | V    |

| $V_{i(ripple)(p-p)}$               | peak-to-peak ripple voltage on $V_{CC}$                                    | from 20 kHz to 200 MHz                                                          | -    | -    | 350  | mV   |

## IC card interface

## TDA8004AT

| SYMBOL           | PARAMETER      | CONDITIONS                              | MIN. | TYP. | MAX. | UNIT |

|------------------|----------------|-----------------------------------------|------|------|------|------|

| I <sub>cc1</sub> | output current | from 0 to 5 or 3 V                      | —    | —    | 65   | mA   |

|                  |                | V <sub>CC</sub> short-circuit to ground | —    | —    | 120  | mA   |

| SR               | slew rate      | up and down                             | 0.11 | 0.17 | 0.22 | V/μs |

## Crystal connections (pins XTAL1 and XTAL2)

|                       |                                             |                                                         |                    |   |                       |     |

|-----------------------|---------------------------------------------|---------------------------------------------------------|--------------------|---|-----------------------|-----|

| C <sub>ext</sub>      | external capacitors on pins XTAL1 and XTAL2 | depending on specification of crystal or resonator used | —                  | — | 15                    | pF  |

| f <sub>i(XTAL)</sub>  | crystal input frequency                     |                                                         | 2                  | — | 26                    | MHz |

| V <sub>IH(XTAL)</sub> | HIGH-level input voltage on XTAL1           |                                                         | 0.8V <sub>DD</sub> | — | V <sub>DD</sub> + 0.2 | V   |

| V <sub>IL(XTAL)</sub> | LOW-level input voltage on XTAL1            |                                                         | -0.3               | — | +0.2V <sub>DD</sub>   | V   |

## Data lines (pins I/O, I/OUC, AUX1, AUX2, AUX1UC and AUX2UC)

| GENERAL               |                                                                                                       |  |   |     |    |     |

|-----------------------|-------------------------------------------------------------------------------------------------------|--|---|-----|----|-----|

| t <sub>d(edge)</sub>  | delay between falling edge on pins I/OUC and I/O (or I/O and I/OUC) and width of active pull-up pulse |  | — | 200 | —  | ns  |

| f <sub>I/O(max)</sub> | maximum frequency on data lines                                                                       |  | — | —   | 1  | MHz |

| C <sub>i</sub>        | input capacitance on data lines                                                                       |  | — | —   | 10 | pF  |

DATA LINES; PINS I/O, AUX1 AND AUX2 (WITH 10 kΩ PULL-UP RESISTOR CONNECTED TO V<sub>CC</sub>)

|                       |                                                    |                                                                                      |                     |   |                       |    |

|-----------------------|----------------------------------------------------|--------------------------------------------------------------------------------------|---------------------|---|-----------------------|----|

| V <sub>OH</sub>       | HIGH-level output voltage on data lines            | no DC load                                                                           | 0.9V <sub>CC</sub>  | — | V <sub>CC</sub> + 0.1 | V  |

|                       |                                                    | I <sub>OH</sub> = -40 μA                                                             | 0.75V <sub>CC</sub> | — | V <sub>CC</sub> + 0.1 | V  |

| V <sub>OL</sub>       | LOW-level output voltage on data lines             | I = 1 mA                                                                             | —                   | — | 300                   | mV |

| V <sub>IH</sub>       | HIGH-level input voltage on data lines             |                                                                                      | 1.8                 | — | V <sub>CC</sub> + 0.3 | V  |

| V <sub>IL</sub>       | LOW-level input voltage on data lines              |                                                                                      | -0.3                | — | +0.8                  | V  |

| V <sub>inactive</sub> | voltage on data lines outside a session            | no load                                                                              | —                   | — | 0.1                   | V  |

|                       |                                                    | I <sub>I/O</sub> = 1 mA                                                              | —                   | — | 0.3                   | V  |

| I <sub>edge</sub>     | current from data lines when active pull-up active | V <sub>OH</sub> = 0.9V <sub>CC</sub> ; C <sub>o</sub> = 80 pF                        | -1                  | — | —                     | mA |

| I <sub>LIH</sub>      | input leakage current HIGH on data lines           | V <sub>IH</sub> = V <sub>CC</sub>                                                    | —                   | — | 10                    | μA |

| I <sub>IL</sub>       | LOW-level input current on data lines              | V <sub>IL</sub> = 0 V                                                                | —                   | — | 600                   | μA |

| t <sub>t(DI)</sub>    | input transition times on data lines               | from V <sub>IL</sub> max to V <sub>IH</sub> min                                      | —                   | — | 1                     | μs |

| t <sub>t(DO)</sub>    | output transition times on data lines              | C <sub>o</sub> = 80 pF, no DC load; 10% to 90% from 0 to V <sub>CC</sub> (see Fig.9) | —                   | — | 0.1                   | μs |

DATA LINES; PINS I/OUC, AUX1UC AND AUX2UC (WITH 10 kΩ PULL-UP RESISTOR CONNECTED TO V<sub>DD</sub>)

|                 |                                         |                          |                     |   |                       |    |

|-----------------|-----------------------------------------|--------------------------|---------------------|---|-----------------------|----|

| V <sub>OH</sub> | HIGH-level output voltage on data lines | no DC load               | 0.9V <sub>DD</sub>  | — | V <sub>DD</sub> + 0.2 | V  |

|                 |                                         | I <sub>OH</sub> = -40 μA | 0.75V <sub>DD</sub> | — | V <sub>DD</sub> + 0.2 | V  |

| V <sub>OL</sub> | LOW-level output voltage on data lines  | I = 1 mA                 | —                   | — | 300                   | mV |

## IC card interface

## TDA8004AT

| SYMBOL                                                                                                                        | PARAMETER                                                   | CONDITIONS                                                        | MIN.         | TYP. | MAX.           | UNIT        |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------|--------------|------|----------------|-------------|

| $V_{IH}$                                                                                                                      | HIGH-level input voltage on data lines                      |                                                                   | $0.7V_{DD}$  | —    | $V_{DD} + 0.3$ | V           |

| $V_{IL}$                                                                                                                      | LOW-level input voltage on data lines                       |                                                                   | 0            | —    | $0.3V_{DD}$    | V           |

| $ I_{LH} $                                                                                                                    | input leakage current HIGH on data lines                    | $V_{IH} = V_{DD}$                                                 | —            | —    | 10             | $\mu A$     |

| $I_{IL}$                                                                                                                      | LOW-level input on data lines                               | $V_{IL} = 0 V$                                                    | —            | —    | 600            | $\mu A$     |

| $R_{pu(int)}$                                                                                                                 | internal pull-up resistance between data lines and $V_{DD}$ |                                                                   | 9            | 11   | 13             | $k\Omega$   |

| $t_{t(DI)}$                                                                                                                   | input transition times on data lines                        | from $V_{IL}$ max to $V_{IH}$ min                                 | —            | —    | 1              | $\mu s$     |

| $t_{t(DO)}$                                                                                                                   | output transition times on data lines                       | $C_o = 30 \text{ pF}$ ; 10% to 90% from 0 to $V_{DD}$ (see Fig.9) | —            | —    | 0.1            | $\mu s$     |

| <b>Internal oscillator</b>                                                                                                    |                                                             |                                                                   |              |      |                |             |

| $f_{osc(int)}$                                                                                                                | frequency of internal oscillator                            |                                                                   | 2.2          | —    | 3.2            | MHz         |

| <b>Reset output to the card (pin RST)</b>                                                                                     |                                                             |                                                                   |              |      |                |             |

| $V_{o(\text{inactive})}$                                                                                                      | output voltage in inactive mode                             | no load                                                           | 0            | —    | 0.1            | V           |

|                                                                                                                               |                                                             | $I_o = 1 \text{ mA}$                                              | 0            | —    | 0.3            | V           |

| $t_d(RSTIN-RST)$                                                                                                              | delay between pins RSTIN and RST                            | RST enabled                                                       | —            | —    | 2              | $\mu s$     |

| $V_{OL}$                                                                                                                      | LOW-level output voltage                                    | $I_{OL} = 200 \mu A$                                              | 0            | —    | 0.3            | V           |

| $V_{OH}$                                                                                                                      | HIGH-level output voltage                                   | $I_{OH} = -200 \mu A$                                             | $0.9V_{CC}$  | —    | $V_{CC}$       | V           |

| $t_r, t_f$                                                                                                                    | rise and fall times                                         | $C_o = 250 \text{ pF}$                                            | —            | —    | 0.1            | $\mu s$     |

| <b>Clock output to the card (pin CLK)</b>                                                                                     |                                                             |                                                                   |              |      |                |             |

| $V_{o(\text{inactive})}$                                                                                                      | output voltage in inactive mode                             | no load                                                           | 0            | —    | 0.1            | V           |

|                                                                                                                               |                                                             | $I_o = 1 \text{ mA}$                                              | 0            | —    | 0.3            | V           |

| $V_{OL}$                                                                                                                      | LOW-level output voltage                                    | $I_{OL} = 200 \mu A$                                              | 0            | —    | 0.3            | V           |

| $V_{OH}$                                                                                                                      | HIGH-level output voltage                                   | $I_{OH} = -200 \mu A$                                             | $0.9V_{CC}$  | —    | $V_{CC}$       | V           |

| $t_r, t_f$                                                                                                                    | rise and fall times                                         | $C_L = 35 \text{ pF}$ ; note 2                                    | —            | —    | 8              | ns          |

| $\delta$                                                                                                                      | duty factor (except for $f_{XTAL}$ )                        | $C_L = 35 \text{ pF}$ ; note 2                                    | 45           | —    | 55             | %           |

| SR                                                                                                                            | slew rate (rise and fall)                                   | $C_L = 35 \text{ pF}$                                             | 0.2          | —    | —              | V/ns        |

| <b>Logic inputs (pins CLKDIV, CLKDIV2, PRES, <u>PRES</u>, CMDVCC, RSTIN and 5V/3V); note 3</b>                                |                                                             |                                                                   |              |      |                |             |

| $V_{IL}$                                                                                                                      | LOW-level input voltage                                     |                                                                   | —            | —    | $0.3V_{DD}$    | V           |

| $V_{IH}$                                                                                                                      | HIGH-level input voltage                                    |                                                                   | $0.7V_{DD}$  | —    | —              | V           |

| $ I_{LIL} $                                                                                                                   | input leakage current LOW                                   | $0 < V_{IL} < V_{DD}$                                             | —            | —    | 5              | $\mu A$     |

| $ I_{LH} $                                                                                                                    | input leakage current HIGH                                  | $0 < V_{IH} < V_{DD}$                                             | —            | —    | 5              | $\mu A$     |

| <b>OFF output (pin OFF is an open-drain with an internal 20 <math>k\Omega</math> pull-up resistor to <math>V_{DD}</math>)</b> |                                                             |                                                                   |              |      |                |             |

| $V_{OL}$                                                                                                                      | LOW-level output voltage                                    | $I_{OL} = 2 \text{ mA}$                                           | —            | —    | 0.4            | V           |

| $V_{OH}$                                                                                                                      | HIGH-level output voltage                                   | $I_{OH} = -15 \mu A$                                              | $0.75V_{DD}$ | —    | —              | V           |

| <b>Protections</b>                                                                                                            |                                                             |                                                                   |              |      |                |             |

| $T_{sd}$                                                                                                                      | shut-down temperature                                       |                                                                   | —            | 135  | —              | $^{\circ}C$ |

| $I_{CC(sd)}$                                                                                                                  | shut-down current at $V_{CC}$                               |                                                                   | —            | —    | 110            | mA          |

## IC card interface

## TDA8004AT

| SYMBOL        | PARAMETER                                       | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|---------------|-------------------------------------------------|------------|------|------|------|------|

| <b>Timing</b> |                                                 |            |      |      |      |      |

| $t_{act}$     | activation sequence duration                    | see Fig.5  | —    | 180  | 220  | μs   |

| $t_{de}$      | deactivation sequence duration                  | see Fig.6  | 60   | 80   | 100  | μs   |

| $t_3$         | start of the window for sending CLK to the card | see Fig.5  | —    | —    | 130  | μs   |

| $t_5$         | end of the window for sending CLK to the card   | see Fig.5  | 140  | —    | —    | μs   |

**Notes**

1. To meet these specifications  $V_{CC}$  should be decoupled to CGND using two ceramic multilayer capacitors of low ESR with values of either 100 nF or one 100 nF and one 220 nF.

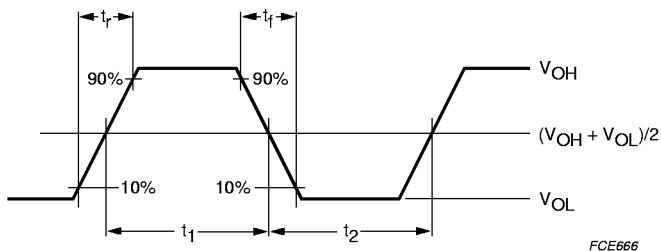

2. The transition times and duty factor definitions are shown in Fig.9;  $\delta = \frac{t_1}{t_1 + t_2}$

3.  $\overline{PRES}$  and  $\overline{CMDCC}$  are active LOW; RSTIN and PRES are active HIGH; for CLKDIV1 and CLKDIV2 see Table 1.

Fig.9 Definition of output transition times.

## IC card interface

## TDA8004AT

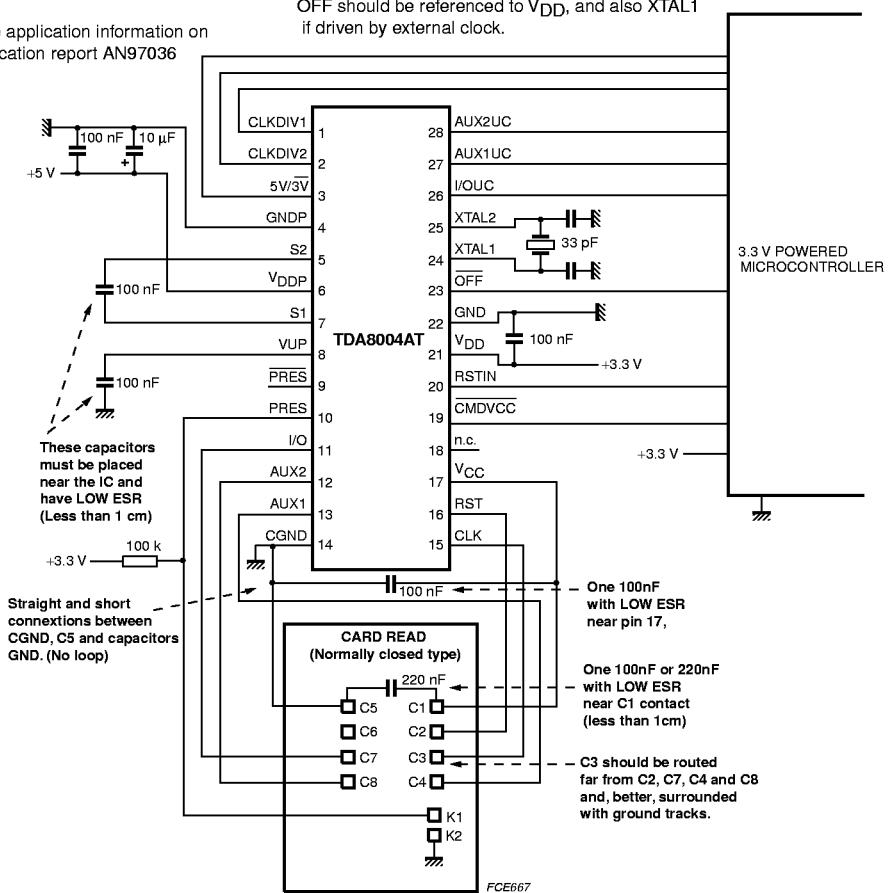

## APPLICATION DIAGRAM

V<sub>DD</sub> for the TDA8004 must be the same as controller supply voltage, CLKDIV1, CLKDIV2, RSTIN, PRES, PRES, AUXUC, I/OUC, AUX2UC, RFU1, CMDVCC, OFF should be referenced to V<sub>DD</sub>, and also XTAL1 if driven by external clock.

More application information on application report AN97036

Fig.10 Application diagram.

## IC card interface

## TDA8004AT

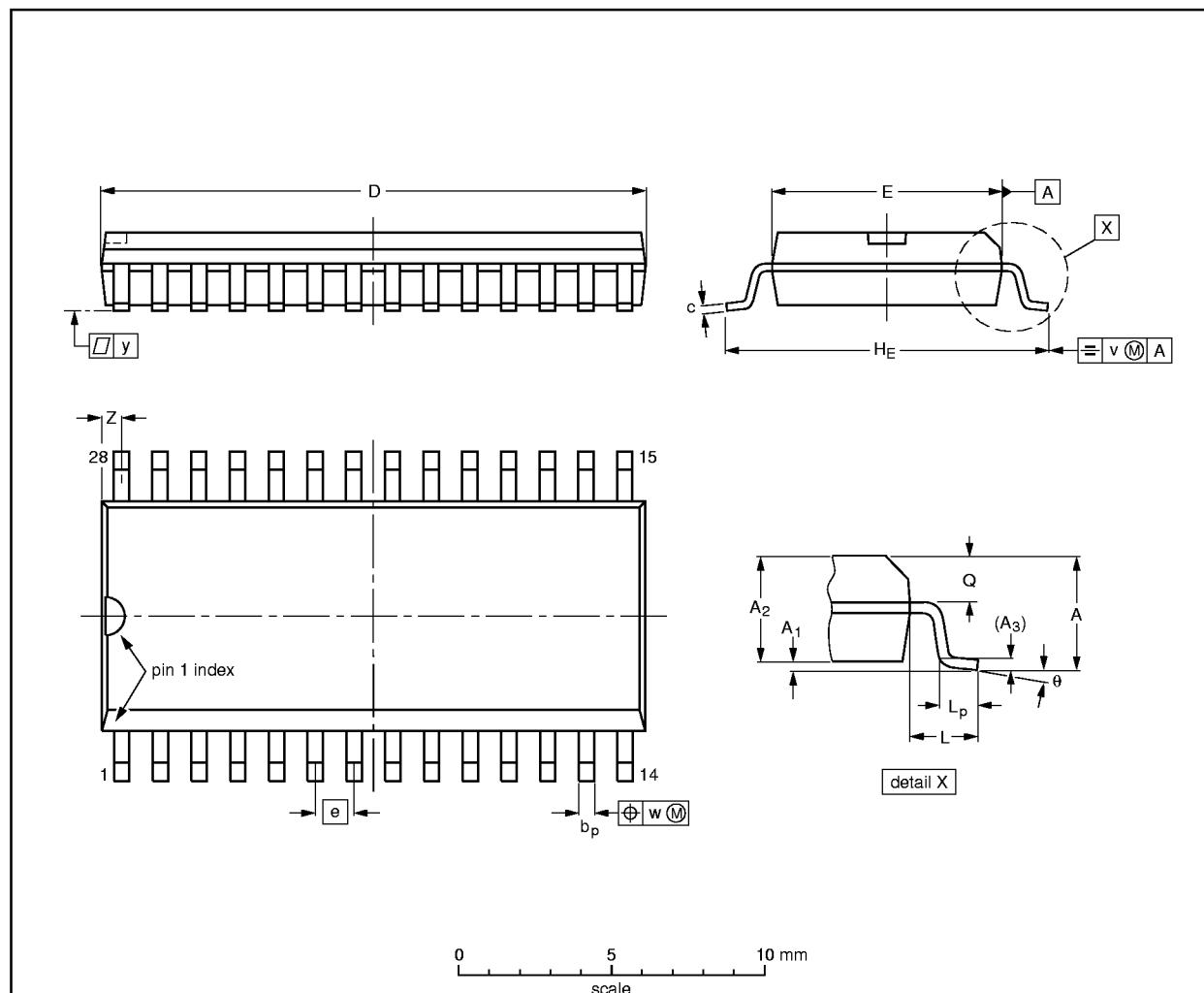

## PACKAGE OUTLINE

SO28: plastic small outline package; 28 leads; body width 7.5 mm

SOT136-1

## DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max.     | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | b <sub>p</sub> | c             | D <sup>(1)</sup> | E <sup>(1)</sup> | e     | H <sub>E</sub> | L     | L <sub>p</sub> | Q              | v    | w    | y              | z <sup>(1)</sup> | θ        |

|--------|---------------|----------------|----------------|----------------|----------------|---------------|------------------|------------------|-------|----------------|-------|----------------|----------------|------|------|----------------|------------------|----------|

| mm     | 2.65<br>0.10  | 0.30<br>2.25   | 2.45<br>0.36   | 0.25           | 0.49<br>0.36   | 0.32<br>0.23  | 18.1<br>17.7     | 7.6<br>7.4       | 1.27  | 10.65<br>10.00 | 1.4   | 1.1<br>0.4     | 1.1<br>1.0     | 0.25 | 0.25 | 0.1<br>0.4     | 0.9<br>0.4       | 8°<br>0° |

| inches | 0.10<br>0.004 | 0.012<br>0.089 | 0.096<br>0.014 | 0.01           | 0.019<br>0.009 | 0.013<br>0.69 | 0.71<br>0.29     | 0.30<br>0.29     | 0.050 | 0.419<br>0.394 | 0.055 | 0.043<br>0.016 | 0.043<br>0.039 | 0.01 | 0.01 | 0.004<br>0.016 | 0.035<br>0.016   |          |

## Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE<br>VERSION | REFERENCES |        |      |  | EUROPEAN<br>PROJECTION | ISSUE DATE           |

|--------------------|------------|--------|------|--|------------------------|----------------------|

|                    | IEC        | JEDEC  | EIAJ |  |                        |                      |

| SOT136-1           | 075E06     | MS-013 |      |  |                        | 97-05-22<br>99-12-27 |

## IC card interface

## TDA8004AT

### SOLDERING

#### Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"Data Handbook IC26; Integrated Circuit Packages"* (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering is not always suitable for surface mount ICs, or for printed-circuit boards with high population densities. In these situations reflow soldering is often used.

#### Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, infrared/convection heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferably be kept below 230 °C.

#### Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is **preferred** to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis **must** be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

- For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

## IC card interface

TDA8004AT

## Suitability of surface mount IC packages for wave and reflow soldering methods

| PACKAGE                                      | SOLDERING METHOD                  |                       |

|----------------------------------------------|-----------------------------------|-----------------------|

|                                              | WAVE                              | REFLOW <sup>(1)</sup> |

| BGA, LFBGA, SQFP, TFBGA                      | not suitable                      | suitable              |

| HBCC, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, SMS | not suitable <sup>(2)</sup>       | suitable              |

| PLCC <sup>(3)</sup> , SO, SOJ                | suitable                          | suitable              |

| LQFP, QFP, TQFP                              | not recommended <sup>(3)(4)</sup> | suitable              |

| SSOP, TSSOP, VSO                             | not recommended <sup>(5)</sup>    | suitable              |

## Notes

1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the "Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods".

2. These packages are not suitable for wave soldering as a solder joint between the printed-circuit board and heatsink (at bottom version) can not be achieved, and as solder may stick to the heatsink (on top version).

3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

## DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.                                                                                                |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later.                                                                                          |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                                                                                                         |

| Short-form specification                                                                                                                                                                                                                                                                                                                                                                                                                                  | The data in this specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook. |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                                                                                                                |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                |

| Where application information is given, it is advisory and does not form part of the specification.                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                |

## LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.