# Z86C90 SL1712

CMOS Z8® CCP™ CONSUMER CONTROLLER PROCESSOR

# **GENERAL DESCRIPTION**

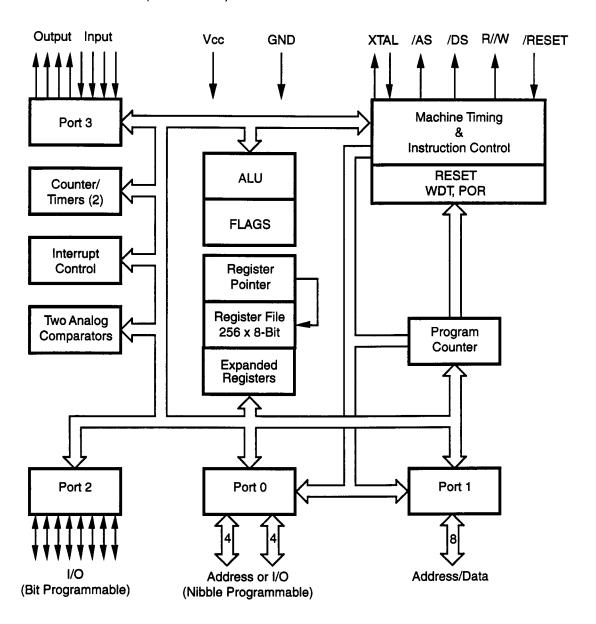

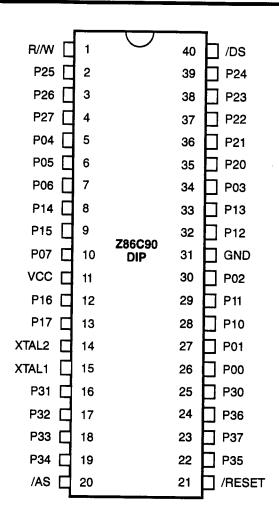

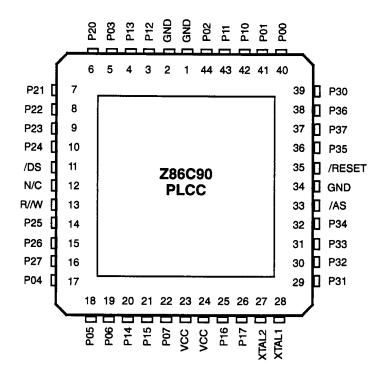

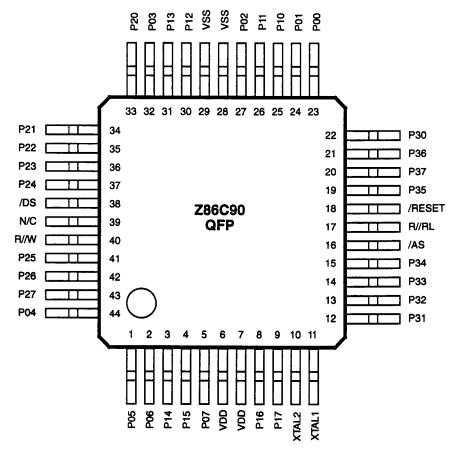

The Z86C90 CCP™ (Consumer Controller Processor) introduces a new level of sophistication to single-chip architecture. The Z86C90 is a ROMless member of the Z8 single-chip microcontroller family with 236 bytes of general purpose RAM. The Z86C90's on-chip oscillator accepts a crystal, ceramic resonator, LC, or external clock source drive. The CCP controllers are housed in a 40-pin DIP, 44-pin Leaded Chip Carrier, or a 44-pin Quad Flat Pack, and are CMOS compatible. The CCP offers the use of external memory which enables this Z8 microcomputer to be used where code flexibility is required. Zilog's CMOS microcomputer offers fast execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, and easy hardware/software system expansion along with low cost and low power consumption.

The Z86C90 architecture is based on Zilog's 8-bit microcontroller core with an Expanded Register File to allow access to register mapped peripheral and I/O circuits. The CCP offers a flexible I/O scheme, an efficient register and address space structure, and a number of ancillary features that are useful in many industrial, automotive, computer peripherals, and advanced scientific applications.

The CCP applications demand powerful I/O capabilities. The Z86C90 fulfills this with 32 pins dedicated to input and output. These lines are grouped into four ports. Each port consists of eight lines, and is configurable under software control to provide timing, status signals, parallel I/O with or without handshake, and an address/data bus for interfacing external memory.

There are four basic address spaces available to support this wide range of configurations: Program Memory, Register File, Data Memory, and Expanded Register File. The Register File is composed of 236 bytes of general purpose registers, four I/O port registers, and fifteen control and status registers. The Expanded Register File consists of two control registers.

To unburden the program from coping with the real-time problems, such as counting/timing and data communication, the Z86C90 offers two on-chip counter/timers. Included are a large number of user selectable modes, and two on-board comparators to process analog signals with a common reference voltage (see Functional Block Diagram).

## Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GŇĎ             | V <sub>ss</sub> |

DC-9069-00 (11-11-94)

# **GENERAL DESCRIPTION** (Continued)

**Functional Block Diagram**

**40-Pin DIP Pin Assignments**

# **PIN DESCRIPTION** (Continued)

## 44-Pin PLCC Pin Assignments

44-Pin QFP Pin Assignments

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                | Description                                                                  | Min        | Max          | Units   |

|-------------------------------------------------------|------------------------------------------------------------------------------|------------|--------------|---------|

| V <sub>DD</sub><br>T <sub>STG</sub><br>T <sub>A</sub> | Supply Voltage (*)<br>Storage Temp<br>Oper Ambient Temp<br>Power Dissipation | -0.3<br>65 | +7.0<br>+150 | V C C W |

Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

### Notes:

# STANDARD TEST CONDITIONS

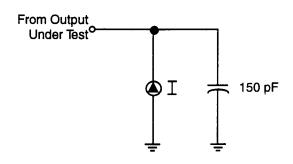

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (see Test Load Diagram).

**Test Load Diagram**

## CAPACITANCE

$T_A = 25$ °C,  $V_{DD} = GND = 0V$ , f = 1.0 MHz, Unmeasured pins to GND

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

<sup>\*</sup> Voltage on all pins with respect to GND. See Ordering Information.

## **PLEASE NOTE**

- (1) When ROM Protect is selected, instructions LDC, LDCI, LDE and LDEI are disabled from accessing memory locations 0000H to OFFFH.

- (2) The current samples will not have the enhanced ROM Protect feature. See note (1). It will be added after the first samples are evaluated and approved. The final production version will therefore have the enhanced ROM Protection such that LDC, LDCI, LDE, and LDEI instructions can access the memory locations OOOOH and OFFFH.

- (3) The Port 3 outputs are reset to High State after Reset, except after Stop-Mode Recovery, at which the outputs remain in the last state.

- (4) Extended timing is operable.

- (5) P0/P1/P2/P3 is Low EMI software programmable.

- (6) P0/P1/P2 is software programmable for open-drain.

- (7) Expanded register PCON is Write Only.

- (8) WDTMR is writeable only within the first 64 system clocks (128 XTAL clocks) after Reset. Afterward, the WDTMR is write protected.

- (9) Device functions down to the  $V_{BO}$  threshold. At temperatures below or colder than 25°C, the  $V_{BO}$  threshold will rise to a maximum  $V_{DD}$  of 3.6V.

- (10)Low EMI is 70% of standard pull-down output driver and 60% of standard pull-up output driver.

| Sym                                | Parameter                                                                                            | V <sub>DD</sub><br>Note [3]          | T <sub>A</sub> =<br>to 10<br>Min                        |                                             |                                             | 0° C<br>'0°C<br>Max                         | Typical<br>at<br>25°C        | Units                      | Conditions                                                                 | Notes          |      |

|------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|------------------------------|----------------------------|----------------------------------------------------------------------------|----------------|------|

|                                    | Max input Voltage                                                                                    | 5.0V                                 |                                                         | 7                                           |                                             | 7                                           |                              | ٧                          | 1 <sub>IN</sub> <250 uA                                                    |                |      |

| V <sub>CH</sub><br>V <sub>CL</sub> | Clock Input High Voltage<br>Clock Input Low Voltage                                                  |                                      | 0.7 V <sub>DD</sub><br>V <sub>SS</sub> -0.3             | V <sub>DD</sub> +0.3<br>0.2 V <sub>DD</sub> | 0.7 V <sub>DD</sub><br>V <sub>ss</sub> -0.3 | V <sub>DD</sub> +0.3<br>0.2 V <sub>DD</sub> | 2.5<br>1.5                   | V<br>V                     | Driven by External Clock G<br>Driven by External Clock G                   |                |      |

| VIH VIL VOH                        | Input High Voltage<br>Input Low Voltage<br>Output High Voltge<br>Low EMI Mode<br>Output High Voltage | 5.0V<br>5.0V<br>5.0V<br>5.0V         | $0.7  V_{DD}$ $V_{SS}$ -0.3 $V_{DD}$ -0.4 $V_{DD}$ -0.4 |                                             | $V_{DD} = 0.4$ $V_{DD} = 0.4$               | V <sub>DD</sub> +0.3<br>0.2 V <sub>DD</sub> | 2.5<br>1.5<br>4.8<br>4.8     | V<br>V<br>V                | l <sub>oH</sub> = -0.5 mA<br>l <sub>oH</sub> = -2.0 mA                     | [8]            |      |

| V <sub>OL</sub>                    | Output Low Voltage Low EMI Mode                                                                      | 5.0V                                 | DD O.T                                                  | 0.4                                         | V <sub>DD</sub> O.4                         | 0.4                                         | 0.2                          | V                          | I <sub>OL</sub> = 1.0 mA                                                   | [0]            |      |

| $V_{0L1} \\ V_{0L2}$               | Output Low Voltage Output Low Voltage                                                                | 5.0V<br>5.0V                         |                                                         | 0.4<br>1.2                                  |                                             | 0.4<br>1.2                                  | 0.1<br>0.5                   | V<br>V                     | $I_{0L} = +4.0 \text{ mA}$<br>$I_{0L} = +12 \text{ mA}, 3 \text{ Pin Max}$ | [8]<br>[8]     |      |

| $\overline{V_{RH}}$                | Reset Input High Voltage<br>Reset Input Low Voltage                                                  | 5.0V<br>5.0V                         | .8 V <sub>DD</sub><br>V <sub>SS</sub> -0.3              | V <sub>DD</sub> 0.2 V <sub>DD</sub>         | .8 V <sub>DD</sub><br>V <sub>SS</sub> –0.3  | V <sub>DD</sub><br>0.2 V <sub>DD</sub>      | 2.1<br>1.7                   | V                          |                                                                            |                |      |

| $\overline{V_{\text{OFFSET}}}$     | Comparator Input Offset<br>Voltage                                                                   | 5.0V                                 |                                                         | 25                                          |                                             | 25                                          | 10                           | mV                         |                                                                            |                |      |

| $V_{ICR}$                          | Input Common Mode<br>Voltage Range                                                                   | 5.0V                                 | 0                                                       | V <sub>DD</sub> -1.5V                       | 0                                           | V <sub>DD</sub> -1.0V                       | ,                            | ٧                          |                                                                            |                | [10] |

| IL<br>OL<br>IR<br>IDD              | Input Leakage<br>Output Leakage<br>Reset Input Current<br>Supply Current                             | 5.0V<br>5.0V<br>5.0V<br>5.0V<br>5.0V | -1<br>-1                                                | 2<br>2<br>-180<br>20<br>25                  | -1<br>-1                                    | 1<br>1<br>-180<br>20<br>25                  | <1<br><1<br>-112<br>15<br>20 | μΑ<br>μΑ<br>μΑ<br>mA<br>mA | $V_{IN} = 0V, V_{DD}$<br>$V_{IN} = 0V, V_{DD}$<br>@ 12 MHz<br>@ 16 MHz     | [4,5]<br>[4,5] |      |

# DC ELECTRICAL CHARACTERISTICS (Continued)

|                  |                                   | V <sub>DD</sub> | T <sub>A</sub> = - |      | T <sub>A</sub> = 0 |     | Typical at |       |                                        |          |

|------------------|-----------------------------------|-----------------|--------------------|------|--------------------|-----|------------|-------|----------------------------------------|----------|

| Sym              | Parameter                         | Note [3]        | Min                | Max  | Min                | Max | 25°C       | Units | Conditions                             | Notes    |

| I <sub>DD1</sub> | Standby Current                   | 5.0V            |                    | 6    |                    | 6   | 3.2        | mA    | @ 12 MHz                               | [4,5]    |

| ,                | (Halt Mode)                       | 5.0V            |                    | 5    |                    | 5   | 2.5        | mΑ    | Clock Div. by 16@12 MHz                | [4,5]    |

| İ <sub>DD2</sub> | Standby Current                   | 5.0V            |                    | 8    |                    | 8   | 3.7        | mΑ    | @ 16 MHz                               | [4,5]    |

| 552              | (Halt Mode)                       | 5.0V            |                    | 7    |                    | 7   | 2.9        | mA    | Clock Div. by 16@16 MHz                | [4,5]    |

| I <sub>DD2</sub> | Standby Current                   | 5.0V            |                    | 20   |                    | 10  | 2          | μA    | WDT is Running                         | [6,11,2] |

| 002              | (Stop Mode)                       | 5.0V            |                    | 1000 |                    | 800 | 600        | μA    | WDT is Running                         | [6,11,2] |

| ALL              | Auto Latch Low Current            | 5.0V            |                    | 40   |                    | 36  | 23         | μA    | OV < V <sub>IN</sub> < V <sub>DD</sub> | [9]      |

| 1                | Auto Latch High Current           | 5.0V            |                    | -36  |                    | -32 | -17        | μA    | $OV < V_{IN}^{III} < V_{DD}^{OD}$      | [9]      |

| V <sub>BO</sub>  | V <sub>cc</sub> Brown Out Voltage |                 | 2.0                | 3.6  | 2.2                | 3.3 | 3.0        | ·V    | 2 MHz max INT CLK Freq.                | [7]      |

## Note:

| [1] I <sub>DD1</sub> | Тур    | Max | Unit | Freq  |

|----------------------|--------|-----|------|-------|

| Clock Driven on XTAL | 0.3 mA | 5   | mA   | 8 MHz |

| Crystal or Resonator | 2.4 mA | 5   | mΑ   | 8 MHz |

[2] GND=0V.

[5] CL1= CL2 = 100pF.

- [8] STD Mode (not Low EMI Mode).

- [9] Auto Latch (mask option) selected.

- [10] For analog comparator inputs when analog comparators are enabled.

- [11] Clock must be forced Low, when XTAL1 is clock driven and XTAL2 is floating.

- [12] Typicals are at  $V_{cc} = 5.0V$ .

<sup>[3]</sup> The  $V_{op}$  voltage spec. of 5.0V guarantees 5.0V  $\pm$  0.5V.

<sup>[4]</sup> All outputs unloaded, I/O pins floating, inputs at  $V_{\rm DD}$ , GND rail.

<sup>[6]</sup> Same as note [4] except inputs at  $V_{\rm cc}$ .

[7] -40°C testing is done at  $V_{\rm cc}$  = 3.6 due to max.  $V_{\rm BO}$  level. The  $V_{\rm BO}$  threshold increases as the temperature decreases and overlaps device functionality.

# **AC CHARACTERISTICS**

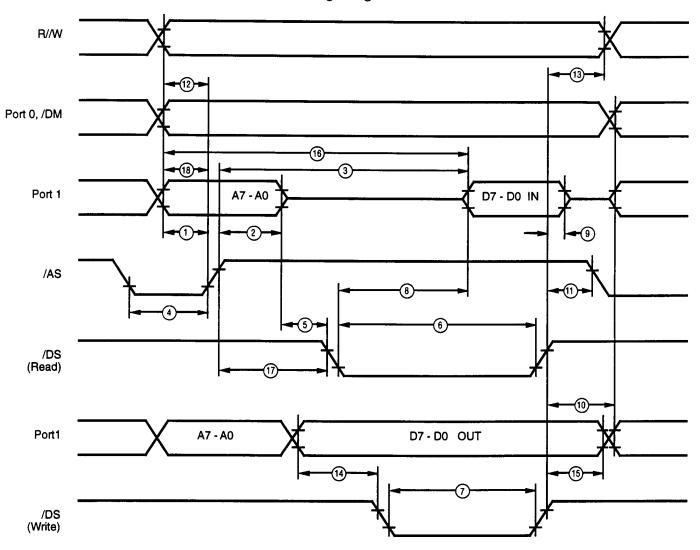

External I/O or Memory Read and Write Timing Diagram

External I/O or Memory Read/Write Timing

**AC CHARACTERISTICS**External I/O or Memory Read and Write Timing Table

|    |           |                                            | v                      | T <sub>A</sub> = -40°C to 105°C<br>T <sub>A</sub> = 0°C to 70°C<br>12 MHz | 16  | MHz     |       |         |  |

|----|-----------|--------------------------------------------|------------------------|---------------------------------------------------------------------------|-----|---------|-------|---------|--|

| No | Symbol    | Parameter                                  | V <sub>DD</sub><br>[3] | Min Max                                                                   | Min | Max     | Units | Notes   |  |

| 1  | TdA(AS)   | Address Valid to /AS Rise Delay            | 5.0                    | 35                                                                        | 25  |         | ····· | [2,4]   |  |

| 2  | TdAS(A)   | /AS Rise to Address Float Delay            | 5.0                    | 45                                                                        | 35  |         | ns    | [2,4]   |  |

| 3  | TdAS(DR)  | /AS Rise to Read Data Req'd Valid          | 5.0                    | 250                                                                       |     | 180     | ns    | [1,2,4] |  |

| 4  | TwAS      | /AS Low Width                              | 5.0                    | 55                                                                        | 40  |         | ns    | [2,4]   |  |

| 5  | TdAS(DS)  | Address Float to /DS Fall                  | 5.0                    | 0                                                                         | 0   |         | ns    |         |  |

| ŝ  | TwDSR     | /DS (Read) Low Width                       | 5.0                    | 180                                                                       | 135 |         | ns    | [1,2,4] |  |

| 7  | TwDSW     | /DS (Write) Low Width                      | 5.0                    | 110                                                                       | 80  |         | ns    | [1,2,4] |  |

| 3  | TdDSR(DR) | /DS Fall to Read Data Req'd Valid          | 5.0                    | 160                                                                       |     | 75      | ns    | [1,2,4] |  |

| 9  | ThDR(DS)  | Read Data to /DS Rise Hold Time            | 5.0                    | 0                                                                         | 0   |         | ns    | [2,4]   |  |

| 10 | TdDS(A)   | /DS Rise to Address Active Delay           | 5.0                    | 55                                                                        | 50  |         | ns    | [2,4]   |  |

| 11 | TdDS(AS)  | /DS Rise to /AS Fall Delay                 | 5.0                    | 45                                                                        | 35  |         | ns    | [2,4]   |  |

| 12 | TdR/W(AS) | R//W Valid to /AS Rise Delay               | 5.0                    | 45                                                                        | 25  |         | ns    | [2,4]   |  |

| 13 | TdDS(R/W) | /DS Rise to R//W Not Valid                 | 5.0                    | 45                                                                        | 35  | <b></b> | ns    | [2,4]   |  |

| 14 | TdDW(DSW) | Write Data Valid to /DS Fall (Write) Delay | 5.0                    | 55                                                                        | 25  |         | ns    | [2,4]   |  |

| 15 | TdDS(DW)  | /DS Rise to Write Data Not Valid Delay     | 5.0                    | 55                                                                        | 35  |         | ns    | [2,4]   |  |

| 16 | TdA(DR)   | Address Valid to Read Data Req'd Valid     | 5.0                    | 310                                                                       |     | 230     | ns    | [1,2,4] |  |

| 17 | TdAS(DS)  | /AS Rise to /DS Fall Delay                 | 5.0                    | 65                                                                        | 45  |         | ns    | [2,4]   |  |

| 18 | TdDM(AS)  | /DM Valid to /AS Fall Delay                | 5.0                    | 30                                                                        | 60  |         | ns    | [2,4]   |  |

## Standard Test Load

All timing references use 0.7  $\rm V_{DD}$  for a logic 1 and 0.2  $\rm V_{DD}$  for a logic 0.

<sup>[1]</sup> When using extended memory timing add 2 TpC.

<sup>[2]</sup> Timing numbers given are for minimum TpC and System Clock is XTAL frequency divide-by-two only.

<sup>[3]</sup> The  $V_{DD}$  voltage spec. of 5.0V guarantees 5.0V  $\pm$  0.5V.

<sup>[4]</sup> Standard Mode (not Low EMI Mode for outputs), SMR D1 = 0, D0 = 0.

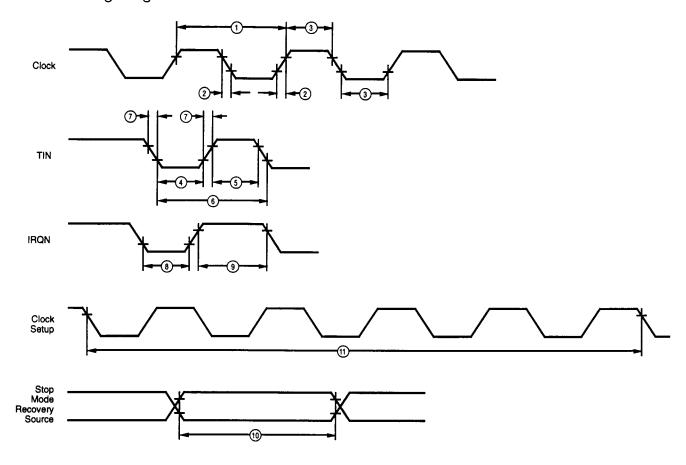

# **AC ELECTRICAL CHARACTERISTICS** Additional Timing Diagram

**Additional Timing**

Additional Timing Table (Divide-By-One Mode)

|          |                 |                                                          | V <sub>DD</sub> | $T_A = -40^{\circ}C$ $T_A = 0^{\circ}C \text{ to}$ $4 \text{ MH}$ | 70°C     |          |                        |           |

|----------|-----------------|----------------------------------------------------------|-----------------|-------------------------------------------------------------------|----------|----------|------------------------|-----------|

| No       | Symbol          | Parameter                                                | Note [6]        | Min                                                               | Max      | Units    | Notes                  |           |

| 1 2      | TpC<br>TrC,TfC  | Input Clock Period<br>Clock Input Rise & Fall Times      | 5.0V<br>5.0V    | 250                                                               | DC<br>25 | ns<br>ns | [1,5,7,8]<br>[1,5,7,8] |           |

| 3        | TwC<br>TwTinL   | Input Clock Width<br>Timer Input Low Width               | 5.0V<br>5.0V    | 100<br>70                                                         |          | ns<br>ns | [1,5,7,8]<br>[1,7,8]   | · · · · · |

| 5<br>6   | TwTinH<br>TpTin | Timer Input High Width<br>Timer Input Period             | 5.0V<br>5.0V    | 5TpC<br>8TpC                                                      |          |          | [1,7,8]<br>[1,7,8]     |           |

| 7        | TrTin,<br>TfTin | Timer Input Rise & Fall Timer                            | 5.0V            |                                                                   | 100      | ns       | [1,7,8]                |           |

| 8A       | TwlL            | Int. Request Low Time                                    | 5.0V            | 70                                                                |          | ns       | [1,2,7,8]              |           |

| 8B<br>9  | TwiL<br>TwiH    | Int. Request Low Time<br>Int. Request Input High Time    | 5.0V<br>5.0V    | 5TpC<br>5TpC                                                      |          |          | [1,3,7,8]<br>[1,2,7,8] |           |

| 10<br>11 | Twsm<br>Tost    | STOP Mode Recovery Width Spec<br>Oscillator Startup Time | 5.0V<br>5.0V    | 12                                                                | 5TpC     | ns       | [4,8]<br>[4,8,9]       |           |

## Notes:

- [1] Timing Reference uses 0.7  $V_{DD}$  for a logic 1 and 0.2  $V_{DD}$  for a logic 0. [2] Interrupt request via Port 3 (P31-P33).

- [3] Interrupt request via Port 3 (P30).

- [4] SMR-D5 = 1, POR STOP Mode Delay is on.

- [5] Divide-By-One mode is programmed independently of Low EMI oscillator mode.

- [6] The  $V_{DD}$  voltage spec. of 5.0V guarantees 5.0V  $\pm$  0.5V.

- [7] SMR  $D\tilde{1} = 0$ .

- [8] Maximum frequency for internal system clock is 4 MHz when using XTAL divide-by-one mode.

- [9] For RC and LC oscillator, and for oscillator driven by clock driver.

Additional Timing Table

| No              | Symbol          | Parameter                                                | V <sub>DD</sub><br>Note [6]  | T <sub>A</sub> = -40°C to<br>T <sub>A</sub> = °C to 70°<br>12 MHz<br>Min |          | 16 M<br>Min        | MHz<br>Max | Units          | Notes                                                            |

|-----------------|-----------------|----------------------------------------------------------|------------------------------|--------------------------------------------------------------------------|----------|--------------------|------------|----------------|------------------------------------------------------------------|

| 1 2             | TpC<br>TrC,TfC  | Input Clock Period<br>Clock Input Rise & Fall Times      | 5.0V<br>5.0V                 | 83                                                                       | DC<br>15 | 62.5               | DC<br>15   | ns<br>ns       | [1,7,8]<br>[1,7,8]                                               |

| 3<br>4          | TwC<br>TwTinL   | Input Clock Width<br>Timer Input Low Width               | 5.0V<br>5.0V                 | 26<br>70                                                                 |          | 31<br>70           |            | ns<br>ns       | [1,7,8]<br>[1,7,8]                                               |

| 5<br>6          | TwTinH<br>TpTin | Timer Input High Width<br>Timer Input Period             | 5.0V<br>5.0V                 | 5TpC<br>8TpC                                                             |          | 5TpC<br>8TpC       |            |                | [1,7,8]<br>[1,7,8]                                               |

| 7               | TrTin,<br>TfTin | Timer Input Rise & Fall Timer                            | 5.0V                         |                                                                          | 100      |                    | 100        | ns             | [1,7,8]                                                          |

| A8              | TwlL            | Int. Request Low Time                                    | 5. <b>0V</b>                 | 70                                                                       |          | 70                 |            | ns             | [1,2,7,8]                                                        |

| 8 <b>B</b><br>9 | TwlL<br>TwlH    | Int. Request Low Time<br>Int. Request Input High Time    | 5.0V<br>5.0V                 | 5TpC<br>5TpC                                                             | .,       | 5TpC<br>5TpC       |            |                | [1,3,7,8]<br>[1,2,7,8]                                           |

| 10<br>11        | Twsm<br>Tost    | STOP Mode Recovery Width Spec<br>Oscillator Startup Time | 5.0V<br>5.0V                 | 12                                                                       | 5ТрС     | 12                 | 5TpC       | ns             | [4,8]<br>[4,9]                                                   |

| 12              | Twdt            | Watchdog Timer Delay Time                                | 5.0V<br>5.0V<br>5.0V<br>5.0V | 3<br>8<br>16<br>66                                                       |          | 3<br>8<br>16<br>66 |            | ms<br>ms<br>ms | D1 = 0 [5,10]<br>D1 = 0 [5,10]<br>D1 = 1 [5,10]<br>D1 = 1 [5,10] |

| 13              | Tpor            | Power On Reset Delay                                     | 5.0V                         | 1.0                                                                      | 14       | 1.0                | 14         | ms             | D1 = 1 [0,10]                                                    |

## Notes:

<sup>[1]</sup> Timing Reference uses 0.7 V<sub>DD</sub> for a logic 1 and 0.2 V<sub>DD</sub> for a logic 0.

[2] Interrupt request via Port 3 (P31-P33).

<sup>[3]</sup> Interrupt request via Port 3 (P30).

<sup>[4]</sup> SMR-D5 = 1, POR STOP Mode Delay is on.

<sup>[5]</sup> Reg. WDTMR.

<sup>[6]</sup> The  $V_{DD}$  voltage spec. of 5.0V guarantees 5.0V  $\pm$  0.5V. [7] SMR D1 = 0.

<sup>[8]</sup> Maximum frequency for internal system clock is 4 MHz when using

XTAL divide-by-one mode.

<sup>[9]</sup> For RC and LC oscillator, and for oscillator driven by clock driver.

<sup>[10]</sup> Using internal RC.

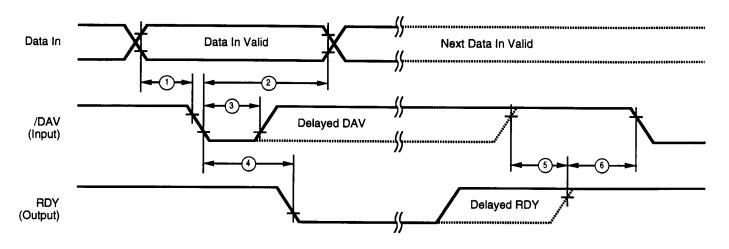

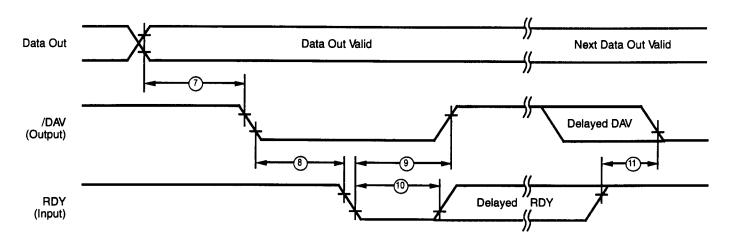

Handshake Timing Diagrams

**Input Handshake Timing**

**Output Handshake Timing**

Handshake Timing Table

| No     | Symbol                     | Parameter                                               | V <sub>DD</sub><br>Note [1] | T <sub>A</sub> = -40°C to 105°C<br>T <sub>A</sub> = 0°C to70°C<br>12 MHz<br>Min Max | 16 MHz<br>Min Max | Data Direction | Notes      |

|--------|----------------------------|---------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------|-------------------|----------------|------------|

| 1      | TsDI(DAV)                  | Data In Setup Time                                      | 5.0V                        | 0                                                                                   | 0                 | IN             | [2]        |

| 2      | ThDI(DAV)                  | Data In Hold Time                                       | 5.0V                        | 115                                                                                 | 115               | IN             | [2]        |

| 3      | TwDAV                      | Data Available Width                                    | 5.0V                        | 110                                                                                 | 110               | IN             | [2]        |

| 4      | TdDAVI(RDY)                | DAV Fall to RDY Fall Delay                              | 5.0V                        | 115                                                                                 | 115               | IN             | [2]        |

| 5<br>6 | TdDAVId(RDY)<br>RDY0d(DAV) | DAV Out to DAV Fall Delay<br>RDY Rise to DAV Fall Delay | 5.0V<br>5.0V                | 80                                                                                  | 0 80              | IN<br>IN       | [2]<br>[2] |

| 7      | TdD0(DAV)                  | Data Out to DAV Fall Delay                              | 5.0V                        | <b>42</b>                                                                           | 31                | OUT            | [2]        |

| 8      | TdDAV0(RDY)                | DAV Fall to RDY Fall Delay                              | 5.0V                        | 0                                                                                   | 0                 | OUT            | [2]        |

| 9      | TdRDY0(DAV)                | RDY Fall to DAV Rise Delay                              | 5.0V                        | 115                                                                                 | 115               | OUT            | [2]        |

| 10     | TwRDY                      | RDY Width                                               | 5.0V                        | 80                                                                                  | 80                | OUT            | [2]        |

| 11     | TdRDY0d(DAV)               | RDY Rise to DAV Fall Delay                              | 5.0V                        | 80                                                                                  | 80                | OUT            | [2]        |

Notes:

[1] Timing Reference uses 0.7 V<sub>DD</sub> for a logic 1 and 0.2 V<sub>DD</sub> for a logic 0.

[2] Standard Mode (not Low EMI Mode on output ports).

[3] The V<sub>DD</sub> voltage spec. of 5.0V guarantees 5.0V ± 0.5V.

## **Pre-Characterization Product:**

The product represented by this CPS is newly introduced and Zilog has not completed the full characterization of the product. The CPS states what Zilog knows about this product at this time, but additional features or non-conformance with some aspects of the CPS may be found, either by Zilog or its customers in the course of further application and characterization work. In addition, Zilog cautions that delivery may be uncertain at times, due to start-up yield issues.

## Low Margin:

Customer is advised that this product does not meet Zilog's internal guardbanded test policies for the specification requested and is supplied on an exception basis. Customer is cautioned that delivery may be uncertain and that, in addition to all other limitations on Zilog liability stated on the front and back of the acknowledgement, Zilog makes no claim as to quality and reliability under the CPS. The product remains subject to standard warranty for replacement due to defects in materials and workmanship.

© 1994 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 Telex 910-338-7621 FAX 408 370-8056