## TVP5010 NTSC/PAL Video Decoder

# Data Manual

December 1998

**Mixed-Signal Products**

SLAS183

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

## Contents

| <ul><li>1.1 Features .</li><li>1.2 Application</li><li>1.3 Functional</li><li>1.4 Terminal A</li></ul>                      | Block Diagram ssignments unctions                                                                                                                                           | 1–1<br>1–2<br>1–2<br>1–3                     |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2.1 Analog Vid<br>2.1.1 Vide<br>2.1.2 Ana                                                                                   | iption  deo Processors and A/D Converters  eo Input Selection  log Input Clamping and Automatic Gain Control Circuits  Converters                                           | 2–1<br>2–1<br>2–1                            |

| 2.2 Digital Pro<br>2.2.1 Y/C<br>2.2.2 Lun<br>2.2.3 Chr                                                                      | cessing                                                                                                                                                                     | 2–2<br>2–3<br>2–4<br>2–7                     |

| 2.3 I <sup>2</sup> C Interfa<br>2.3.1 I <sup>2</sup> C<br>2.3.2 I <sup>2</sup> C<br>2.3.3 I <sup>2</sup> C                  | Ce Write Operation Read Operation Microcode Write Operation Microcode Read Operation Microcode Read Operation                                                               | 2–8<br>2–10<br>2–11<br>2–12                  |

| <ul><li>2.4 Genlock C</li><li>2.5 Video Port</li><li>2.6 Video Port</li><li>2.7 Video Port</li><li>2.8 Video Port</li></ul> | ontrol Timing/Formatting 16-bit 4:2:2 Mode 12-Bit 4:1:1 Mode 8-Bit 4:2:2 Mode 8-Bit 656 Mode                                                                                | 2–14<br>2–14<br>2–16<br>2–18                 |

| 2.10 Reset<br>2.11 Internal Co<br>2.11.1 A<br>2.11.2 A<br>2.11.3 C<br>2.11.4 N                                              | ontrol Registers Analog Input Source Selection #1 Sub-Address = 00 Analog Channel Controls Operation Mode Controls Sub-Address = 02h Miscellaneous Controls                 | 2–23<br>2–23<br>2–24<br>2–26<br>2–27<br>2–28 |

| 2.11.6 L<br>2.11.7 L<br>2.11.8 E<br>2.11.9 C<br>2.11.10 H                                                                   | Color Killer Threshold Control  Luminance Processing Control 1  Luminance Processing Control 2  Brightness Control  Color Saturation Control  Hue Control  Contrast Control | 2–30<br>2–31<br>2–32<br>2–32                 |

|   |      | 2.11.12             |                                                   | 2-33  |

|---|------|---------------------|---------------------------------------------------|-------|

|   |      | 2.11.13             | Horizontal Sync (HSYN) Start for NTSC             | 2-33  |

|   |      | 2.11.14             | Horizontal Sync (HSYN) Start for PAL              |       |

|   |      | 2.11.15             | Vertical Blanking (VBLK) Start                    | 2-35  |

|   |      | 2.11.16             | Vertical Blanking VBLK Stop                       | 2-35  |

|   |      | 2.11.17             | Chrominance Control 1                             | 2-36  |

|   |      | 2.11.18             | Analog Input Source Selection Sub-Address=20h     | 2-37  |

|   |      | 2.11.19             | Device ID Register Sub-Address = 80h              |       |

|   |      | 2.11.20             | Status Register 1 Sub–Address = 81h               |       |

|   |      | 2.11.21             | Status Register 2 Sub–Address = 82h               |       |

|   |      | 2.11.22             | Status Register 3 Sub-Address = 83h               |       |

|   |      | 2.11.23             | Status Register 4 Sub-Address = 84h               | 2–40  |

| 3 | Elec | trical Spe          | ecifications                                      | . 3–1 |

|   | 3.1  | Absolute            | Maximum Ratings                                   | . 3–1 |

|   | 3.2  | Recomm              | nended Operating Conditions                       | . 3–1 |

|   | 3.3  | Electrica           | ll Characteristics                                | . 3–2 |

|   |      |                     | nalog Processing and Analog-to-Digital Converters |       |

|   |      | 3.3.2 D             | C Electrical Characteristics                      | . 3–2 |

|   | 3.4  |                     |                                                   |       |

|   |      |                     | locks, Video Data, Sync Timing                    |       |

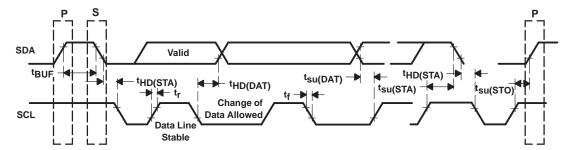

|   |      | $3.4.2 	ext{ } I^2$ | C Host Bus Timing                                 | . 3–4 |

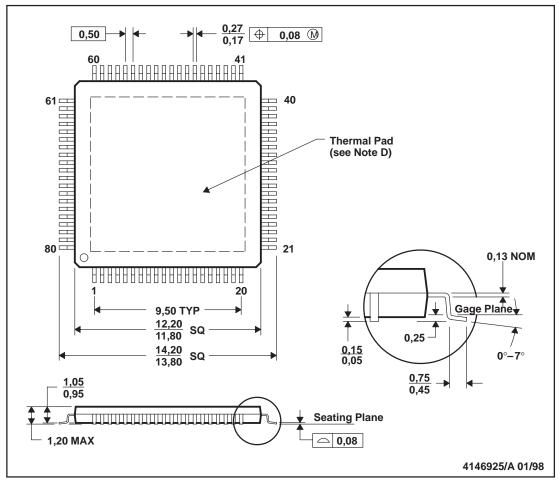

| 4 | Mec  | hanical D           | Oata                                              | . 4–1 |

## **List of Illustrations**

| Figure                                                                                                                                                                                                                                                                                                                                                                                                          | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                 | k Diagramssignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| 2–2 Digital Video Sig<br>2–3 Chroma Trap Fi<br>2–4 Chroma Trap Fi<br>2–5 Luminance Edg<br>2–6 Peaking Filter R<br>2–7 Peaking Filter R<br>2–8 Peaking Filter R<br>2–9 Transfer Curve<br>2–10 Clock Circuit D<br>2–11 Reference Clo<br>2–12 I <sup>2</sup> C Data Trans<br>2–13 GLCO Timing<br>2–14 Functional Tim<br>2–15 16-Bit 4:2:2 Fu<br>2–16 12-bit 4:1:1 Fu<br>2–17 8-Bit (uyvyuyv<br>2–18 8-Bit (uyvyuyv | rocessors and A/D Converters gnal Processing Block Diagram liter Frequency Response for 13.5 MHz Sampling liter Frequency Response for Square-Pixel Sampling e-Enhancer Response, 13.5 MHz Sampling Response, NTSC and PAL-M Square Pixel Response, PAL Square Pixel of Coring Circuit Diagram ck Configurations sfer Example  Inctional Timing Inctional Timing Inctional Timing OY) 4:2:2 Functional Timing Diagram OY) 656 Functional Timing | 2-3 2-4 2-4 2-5 2-5 2-6 2-6 2-7 2-7 2-8 2-9 2-14 2-15 2-17 2-19 2-21 |

|                                                                                                                                                                                                                                                                                                                                                                                                                 | rnc Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

## **List of Tables**

| Tabl | le Title                                                      | Page      |

|------|---------------------------------------------------------------|-----------|

| 2–1  | Summary of the Line Frequencies, Data Rates, and Pixel Counts | <br>. 2–8 |

|      | I <sup>2</sup> C Host Port Terminal Description               |           |

| 2–3  | Output Format: 16-Bit 4:2:2                                   | <br>2-16  |

| 2–4  | Output Format: 12-Bit 4:1:1                                   | <br>2-18  |

| 2–5  | Output Format: 8-bit 4:2:2 U0Y0V0Y1U2Y2V2Y3                   | <br>2-20  |

| 2–6  | Output Format: 8-bit 656 U0Y0V0Y1U2Y2V2Y3                     | <br>2-22  |

| 2–7  | Power-Up Reset Sequence                                       | <br>2-23  |

| 2–8  | Registers Summary                                             | <br>2-23  |

| 2–9  | Video Input Source Selection                                  | <br>2-25  |

| 2-10 | Digital Output Controls                                       | <br>2–29  |

| 2-11 | Vertical Blanking Interval Start and End                      | <br>2-35  |

#### 1 Introduction

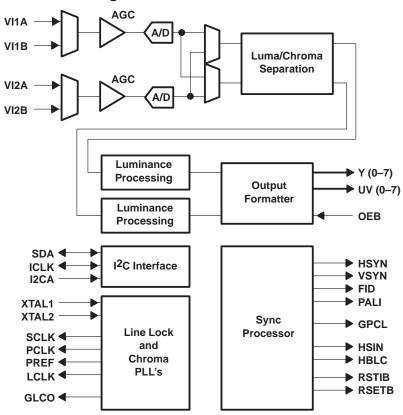

The TVP5010, is a high quality single chip digital video decoder that converts base-band analog NTSC and PAL video signals into digital components video. Both composite and S-video are supported and 8-, 12-, and 16-bit outputs are selectable. Sampling is square-pixel or ITU-R BT.601 (13.5 MHz) and is line locked for correct pixel alignment. The output formats can be 8-bit or 16-bit 4:2:2, 12-bit 4:1:1, or 8-bit ITU-R BT.656. The TVP5010 uses TI patented technology for locking to weak, noisy, or unstable signals, and a genlock control output is generated for synchronizing downstream video encoders.

Two-line (1-H delay) comb filtering is available for both the luma and chroma data paths to reduce both cross-luma and cross-chroma artifacts; a chroma trap filter is also available. Video characteristics including hue, contrast, and saturation are programmable using one of five supported host port interfaces. The TVP5010 generates synchronization, blanking, field, lock, and clock signals in addition to digital video outputs.

The main blocks of TVP5010 include:

- Analog processors and A/D converters

- Y/C separation

- Chrominance processor

- Luminance processor

- Clock/Timing processor and power-down control

- Output formatter

- Host port interface

## 1.1 Features

- Accepts NTSC (M) and PAL (B, D, G, H, I, M, N) composite video, S-video

- Four analog video inputs for up to 4 composite inputs or 2 S-video inputs

- Two built-in-analog signal processing channels with clamping and AGC

- Dual high speed 8-bit A/D converters for luminance and chrominance processing

- Patented architecture for locking to weak, noisy, or unstable signals

- · Comb filters for both cross-color and cross-luminance noise reductions

- Line locked clock and sampling

- I<sup>2</sup>C host port

- Programmable data rates:

- 12.2727 MHz square-pixel (NTSC)

- 14.7500 MHz square-pixel (PAL)

- 13.5 MHz ITU-R BT.601 (NTSC and PAL)

- Programmable output formats: 16-bit or 8-bit 4:2:2 YCbCr, 12-Bit 4:1:1 YCbCr and ITU-R BT.656 with embedded syncs

- ITU-R BT.601 or extended coding range

- Brightness, contrast, saturation, and hue control through host port

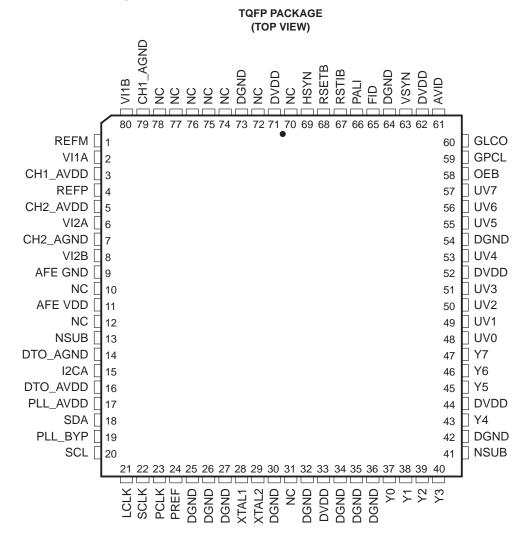

- 80-terminal TQFP package

## 1.2 Applications

- Digital image processing

- Video conferencing

- Multimedia

- Digital video

- Desktop video

- Video capture

- Video editing

## 1.3 Functional Block Diagram

Figure 1-1. Functional Block Diagram

## 1.4 Terminal Assignments

Figure 1-2. TVP5010 Pin Assignments

## 1.5 Terminal Functions

|                              | 5 TERMINAL TERMINAL                  |     |                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------------------|--------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                         | NO.                                  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Analog Video                 |                                      |     |                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| VI1A<br>VI1B<br>VI2A<br>VI2B | 2<br>80<br>6<br>8                    | I   | Analog Video inputs. Up to four composite inputs or two S-video inputs or a combination of the two. The inputs must be ac coupled. The recommended coupling capacitor is 0.1 $\mu\text{F}.$                                                                                                                                              |  |  |  |  |

| Digital Video                |                                      |     |                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Y[0:7]                       | 37, 38, 39,<br>40, 43, 45,<br>46, 47 | 0   | 8-bit digital luminance outputs, or 8-bit multiplexed luminance and chrominance outputs. These pins may also be configured to output data from the channel 1 A/D converter.                                                                                                                                                              |  |  |  |  |

| UV[0:7]                      | 48, 49, 50,<br>51, 53, 55,<br>56, 57 | I/O | 8-bit digital chrominance outputs. These pins may also be configured to output data from the channel 2 A/D converter.                                                                                                                                                                                                                    |  |  |  |  |

| Clock Signals                | 3                                    |     |                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| LCLK                         | 21                                   | 0   | Clock output with one-half the frequency of the pixel clock (PCLK)                                                                                                                                                                                                                                                                       |  |  |  |  |

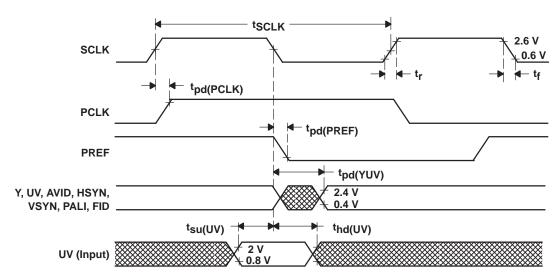

| SCLK                         | 22                                   | 0   | System clock output with twice the frequency of the pixel clock (PCLK).                                                                                                                                                                                                                                                                  |  |  |  |  |

| PCLK                         | 23                                   | 0   | Pixel clock output. The frequency is 12.2727 MHz for square-pixel NTSC, 14.75 MHz for square-pixel PAL, and 13.5 MHz for ITU-R BT.601 sampling modes.                                                                                                                                                                                    |  |  |  |  |

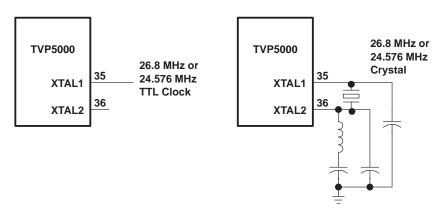

| XTAL1<br>XTAL2               | 28<br>29                             | I   | External clock reference. XTAL1 may be connected to a TTL-compatible oscillator or to one terminal of a crystal oscillator. XTAL2 may be connected to the second terminal of a crystal oscillator or left unconnected. The oscillator frequencies used are 26.800 MHz for square pixel sampling or 24.576 MHz for ITU-R BT.601 sampling. |  |  |  |  |

| PREF                         | 24                                   | 0   | Clock phase reference signal. This signal may be used to qualify clock edges when SCLK is used to clock data which is changing at the pixel clock rate.                                                                                                                                                                                  |  |  |  |  |

| Sync Signals                 |                                      |     |                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| HSYN                         | 69                                   | 0   | Horizontal sync signal. The rising edge time is programmable.                                                                                                                                                                                                                                                                            |  |  |  |  |

| VSYN                         | 63                                   | 0   | Vertical sync or vertical blanking signal. The function of this pin is selected via I <sup>2</sup> C control.                                                                                                                                                                                                                            |  |  |  |  |

| FID                          | 65                                   | 0   | Odd/even field indicator or vertical lock indicator. For odd/even indicator, a logic 1 indicates the odd field. For vertical lock indicator, a logic 1 indicates the internal vertical processor is in locked state. The function of this pin is selected via I <sup>2</sup> C control.                                                  |  |  |  |  |

| PALI                         | 66                                   | 0   | PAL line indicator or horizontal lock indicator. For PAL line indicator, a logic 1 indicates a noninverted line, and a logic 0 indicates an inverted line. For horizontal lock indicator, a logic 1 indicates the internal horizontal PLL is in a locked state. The function of this pin is selected via I <sup>2</sup> C control.       |  |  |  |  |

1.5 Terminal Functions (Continued)

|                      |                                                 | tions | s (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                 |                                                 | 1/0   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NAME                 | NO.                                             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Sync Signals         | ,                                               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AVID                 | 61                                              | 0     | Active video indicator. This signal is high during the horizontal active time of the video output on the Y and UV pins. AVID continues to toggle during vertical blanking intervals.                                                                                                                                                                                                                                                                                                                                                                       |

| I <sup>2</sup> C-Bus |                                                 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SDA                  | 18                                              | I/O   | I <sup>2</sup> C-bus serial data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SCL                  | 20                                              | I/O   | I <sup>2</sup> C-bus serial clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I2CA                 | 15                                              | I/O   | I <sup>2</sup> C slave address select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Miscellaneo          | us Signals                                      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RSTIB                | 67                                              | I     | Reset input, active low. A low input initiates the reset sequence described in Section 2.10.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RSETB                | 68                                              | 0     | Reset output, active low. This signal is low during the reset sequence described in Section 2.10.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OEB                  | 58                                              | I     | Output enable, active low; or data input for 9- or 10-bit external A/D. The function of this pin is selected via I <sup>2</sup> C control. When this pin is an output enable a logic 1 input forces Y and UV output pins to high impedance states.                                                                                                                                                                                                                                                                                                         |

| GLCO                 | 60                                              | 0     | Genlock control output. This pin serially outputs color subcarrier PLL information. The information can be decoded by a slave device to allow genlocking to the TVP5010. Data is transmitted at the SCLK rate.                                                                                                                                                                                                                                                                                                                                             |

| GPCL                 | 59                                              | I/O   | General purpose control logic. This pin has four functions:  1. General purpose output. In this mode the state of GPCL is directly programmed via I <sup>2</sup> C.  2. Vertical blank output. In this mode the GPCL pin is used to indicate the vertical blanking interval of the output video.  3. LSB of input data from 10-bit external A/D.  4. Sync lock control input. In this mode when GPCL is high the output clocks and horizontal line count are forced to nominal values.  The function of this pin is selected via I <sup>2</sup> C control. |

| No Connect           | 10, 12, 31,<br>70, 72, 74,<br>75, 76, 77,<br>78 | 0     | Factory test only, do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 1.5 Terminal Functions (Continued)

| TERMINAL             |                                                         |     |                                                                      |  |  |  |  |

|----------------------|---------------------------------------------------------|-----|----------------------------------------------------------------------|--|--|--|--|

|                      |                                                         | 1/0 | DESCRIPTION                                                          |  |  |  |  |

| NAME                 | NO.                                                     |     |                                                                      |  |  |  |  |

| Power Suppli         | es                                                      |     |                                                                      |  |  |  |  |

| REFP                 | 4                                                       |     | A/D reference supply. Connect to 5 V analog.                         |  |  |  |  |

| REFM                 | 1                                                       |     | A/D reference ground. Connect to analog ground.                      |  |  |  |  |

| CH1_AVDD<br>CH2_AVDD | 3<br>5                                                  |     | Analog front end supplies. Connect to 5 V analog.                    |  |  |  |  |

| CH1_AGND<br>CH2_AGND | 79<br>7                                                 |     | Analog front end grounds. Connect to analog ground.                  |  |  |  |  |

| DTO_AVDD             | 16                                                      |     | Supply for DTO portion of clock/sync circuit. Connect to 5 V analog. |  |  |  |  |

| DTO_AGND             | 14                                                      |     | Ground for DTO. Connect to analog ground.                            |  |  |  |  |

| PLL_AVDD             | 17                                                      |     | Supply for PLL portion of clock/sync circuit. Connect to 5 V analog. |  |  |  |  |

| PLL_BYP              | 19                                                      |     | Bypass to PLL_AVDD (pin 17) with a 0.1 μF capacitor.                 |  |  |  |  |

| AFE_DVDD             | 11                                                      |     | Digital supply for analog front end. Connect to 5 V digital.         |  |  |  |  |

| AFE_DGND             | 9                                                       |     | Digital ground for analog front end.                                 |  |  |  |  |

| NSUB                 | 13, 41                                                  |     | Substrate ground. Connect to analog ground.                          |  |  |  |  |

| DGND                 | 25, 26, 27,<br>30, 32, 34,<br>35, 36, 42,<br>54, 64, 73 |     | Digital grounds                                                      |  |  |  |  |

| DVDD                 | 33, 44, 52,<br>62, 71                                   |     | Digital supplies, 5 V                                                |  |  |  |  |

## 2 Detailed Description

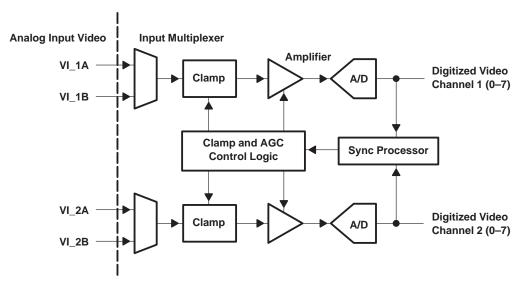

## 2.1 Analog Video Processors and A/D Converters

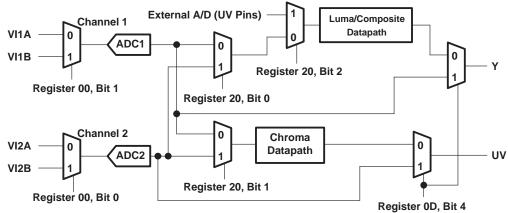

Figure 2–1 shows the detailed functional diagram of the analog video processors and A/D converters. This block provides the analog interface to all the video inputs. It accepts up to four inputs, performs analog signal conditioning (i.e., video clamping, video amplifying), and carries out analog-to-digital conversion.

#### 2.1.1 Video Input Selection

Four high impedance video inputs are sources for two internal analog channels in the TVP5010. The internal multiplexers via the host port bus can select the desired input. The user can connect the four analog video inputs in the following combinations:

- Four selectable individual composite video inputs

- 1 S-video input and two composite video inputs

- 2 S-video inputs

#### 2.1.2 Analog Input Clamping and Automatic Gain Control Circuits

The internal clamp circuit restores the ac coupled video signals to a fixed dc level before A/D conversion. The clamping circuits provides line-by-line restoration of the video sync level to a fixed dc reference voltage. The circuit has two modes of clamping, coarse and fine. In coarse, the most negative portion of the signal (typically the sync tip) is clamped to a fixed dc level. The circuit uses fine mode to prevent spurious level shifting caused by noise that is more negative than the sync tip on the input signal. When fine mode is enabled, after sync position is detected, clamping is only enabled during sync period. S-video requires fine clamping mode for proper operation.

Input video signals may vary significantly from the normal level of 1 Vpp. An automatic gain control (AGC) circuit adjusts the signal amplitude to use the maximum range of the A/D converters without clipping.

Figure 2-1. Analog Video Processors and A/D Converters

## 2.1.3 A/D Converters

The TVP5010 contains two 8-bit A/D converters which digitize the analog video signal inputs. To prevent high frequencies which are above half of the sampling rate from entering into the system, video input(s) may require an external antialiasing low pass filter.

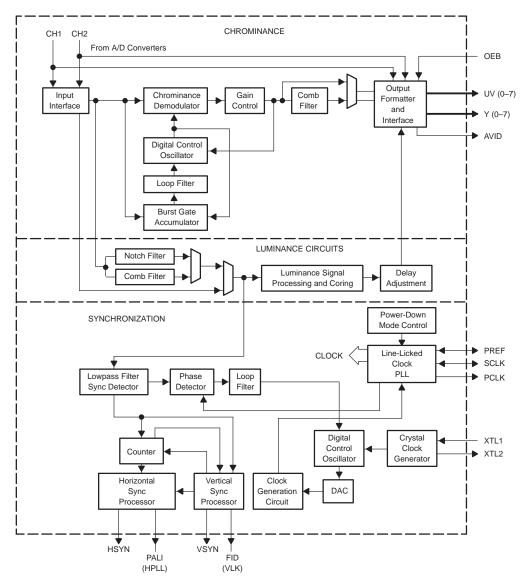

## 2.2 Digital Processing

Figure 2–2 shows the block diagram of the digital video decoder processing. This block receives digitized composite or S-video signals from the A/D converters, and performs Y/C separation, chroma demodulation, and Y-signal enhancements. It also generates the horizontal and vertical syncs. The YUV digital output may be programmed into various formats: 16-bit or 8-bit 4:2:2, 12-bit 4:1:1 and ITU-R BT.656 parallel interface standard. The circuit uses comb filters to reduce the cross-chroma and cross-luma noise.

Figure 2–2. Digital Video Signal Processing Block Diagram

## 2.2.1 Y/C Separation

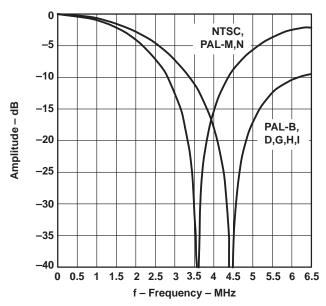

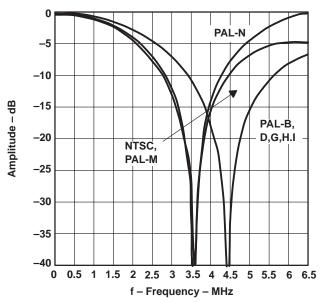

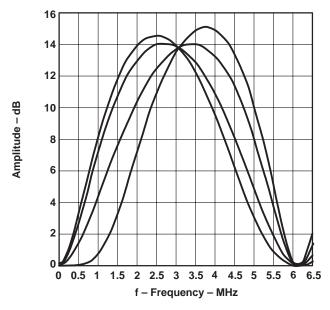

Luma/chroma separation may be done using either 2-line (1–H delay) comb filtering or a chroma trap filter. Comb filtering is available for both the luminance and the chrominance portion of the data path. The characteristics of the filter are shown in Figure 2–3 and 2–4.

Figure 2-3. Chroma Trap Filter Frequency Response for 13.5 MHz Sampling

Figure 2-4. Chroma Trap Filter Frequency Response for Square-Pixel Sampling

## 2.2.2 Luminance Processing

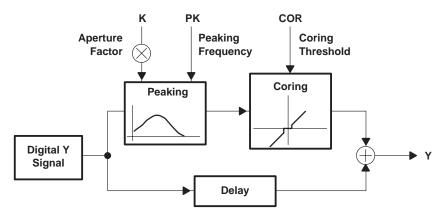

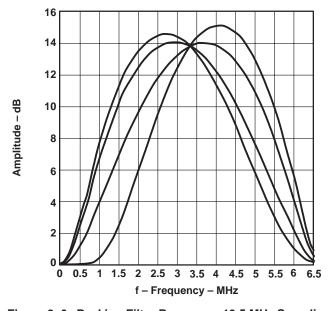

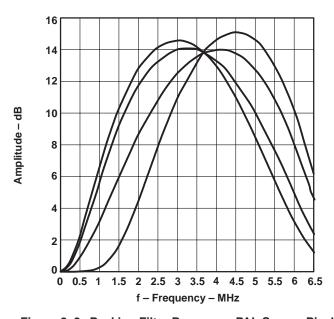

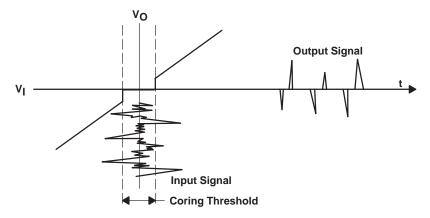

The digitized composite video signal from the output of A/D converters passes through a luminance comb filter or a chroma trap filter that removes the chrominance signal from the composite signal to generate luminance signal. The luminance signal is then fed to the input of luminance signal peaking and coring circuits. Figure 2–5 illustrates the basic functions of the luminance data path. In the case of S-video, the luminance signal will bypass the comb filter or notch filter and be fed to the peaking and coring circuits directly. High frequency components of the luminance signal are enhanced further by the peaking filter (edge

enhancer). Figures 2–6, 2–7, and 2–8 show the characteristic of the peaking filter at maximum gain. The coring circuit reduces the low-level, high-frequency noise. Figure 2–9 shows the transfer curve of the coring function. The peaking frequency, peaking gain, and coring threshold are programmable.

Figure 2-5. Luminance Edge-Enhancer

Figure 2-6. Peaking Filter Response, 13.5 MHz Sampling

Figure 2–7. Peaking Filter Response, NTSC and PAL-M Square Pixel

Figure 2–8. Peaking Filter Response, PAL Square Pixel

Figure 2-9. Transfer Curve of Coring Circuit

## 2.2.3 Chrominance Processing

A quadrature demodulator removes the U and V components from the composite signal in composite video mode, or the U and V components from the chroma signal in S-video mode. The U/V signals then pass through the gain control stage for chroma saturation adjustment. The U and V components pass through a comb filter to eliminate cross-chrominance noise. Phase shifting the digitally-controlled oscillator controls hue. The block includes an automatic color killer (ACK) circuit that suppresses the chroma processing when the color burst of the video signal is weak or not present.

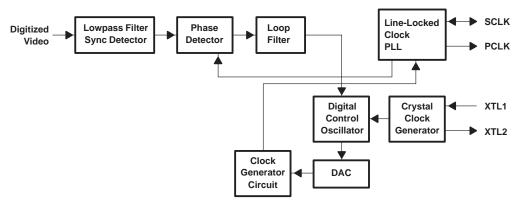

#### 2.2.4 Clock Circuits

An Internal line-locked PLL generates the system and pixel clocks. Figure 2–10 shows a simplified clock circuit diagram. The digital control oscillator generates the reference signal for the horizontal PLL.

The DCO outputs a signal that is fed to the D/A converter. The D/A converter outputs a line-locked clock signal (LCLK). The DCO requires a 26.8 or a 24.576 MHz clock as an input. The input for the DCO may enter terminal XTAL1 as TTL. Another input for the DCO may be a 26.8 or 24.576 MHz crystal connected across terminals XTAL1 and XTAL2. The crystal input requires passive tuning circuits to activate the internal crystal oscillator circuitry. Figure 2–11 shows the various reference clock configurations.

Figure 2-10. Clock Circuit Diagram

Figure 2-11. Reference Clock Configurations

The sampling frequencies that control the number of pixels per line differ depending on the video format and standards. Table 2–1 shows a summary of the sampling frequencies.

| Table 2 11 California y Critica Entre 1 requestiones, Para Traces, and 1 incompanies |                                  |                    |                           |                             |                                   |  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------|--------------------|---------------------------|-----------------------------|-----------------------------------|--|--|--|--|

| STANDARDS                                                                            | HORIZONTAL<br>LINE RATE<br>(kHz) | PIXELS<br>PER LINE | ACTIVE PIXELS<br>PER LINE | PIXEL<br>PCLK RATE<br>(MHz) | SYSTEM clk2<br>FREQUENCY<br>(MHz) |  |  |  |  |

| NTSC, square-pixel                                                                   | 15.73426                         | 780                | 640                       | 12.2727                     | 24.54                             |  |  |  |  |

| NTSC, ITU-R BT.601                                                                   | 15.73426                         | 858                | 720                       | 13.5                        | 27.0                              |  |  |  |  |

| PAL (B,D,G,H,I), square-pixel                                                        | 15.625                           | 944                | 768                       | 14.75                       | 29.5                              |  |  |  |  |

| PAL (B,D,G,H,I), ITU-R BT.601                                                        | 15.625                           | 864                | 720                       | 13.5                        | 27.0                              |  |  |  |  |

| PAL(M), square-pixel                                                                 | 15.73426                         | 780                | 640                       | 12.2727                     | 24.54                             |  |  |  |  |

| PAL(M), ITU-R BT.601                                                                 | 15.73426                         | 858                | 720                       | 13.5                        | 27.0                              |  |  |  |  |

| PAL(N), square-pixel                                                                 | 15.625                           | 944                | 768                       | 14.75                       | 29.5                              |  |  |  |  |

| PAL(N), ITU-R BT.601                                                                 | 15.625                           | 864                | 720                       | 13.5                        | 27.0                              |  |  |  |  |

Table 2-1. Summary of the Line Frequencies, Data Rates, and Pixel Counts

## 2.3 I<sup>2</sup>C Interface

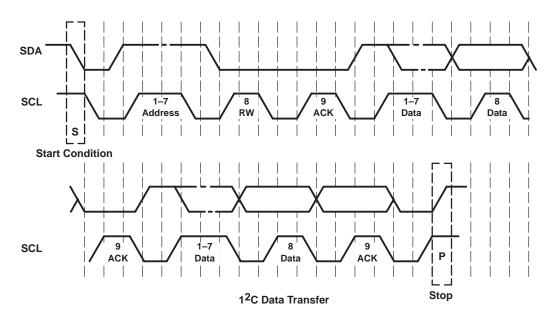

The I<sup>2</sup>C standard consists of two signals, serial input/output data (SDA) line and input/output clock line (SCL), that carry information between the devices connected to the bus. A third signal (I<sup>2</sup>CA) is used for slave address selection. Although the I<sup>2</sup>C system can be multimastered, the TVP5010 will function as a slave device only.

Both SDA and SCL are bidirectional lines that connect to a positive supply voltage via a pullup resistor. When the bus is free, both lines are high.

The slave address (I<sup>2</sup>CA) should be tied high or low to distinguish between two TVP5010 devices commonly on the I<sup>2</sup>C bus.

Table 2–3 summarizes the terminal functions of the I<sup>2</sup>C mode host interface.

|                   |                   | •                       |  |  |  |

|-------------------|-------------------|-------------------------|--|--|--|

| SIGNAL            | TYPE              | DESCRIPTION             |  |  |  |

| I <sup>2</sup> CA | I                 | Slave address selection |  |  |  |

| SCL               | I/O ( <b>OD</b> ) | Input/output clock line |  |  |  |

| SDA               | I/O ( <b>OD</b> ) | Input/output data line  |  |  |  |

Table 2-2. I<sup>2</sup>C Host Port Terminal Description

Figure 2-12. I<sup>2</sup>C Data Transfer Example

Data transfer rate on the bus is up to 400 kbits/s. The number of interfaces connected to the bus is dependent on the bus capacitance limit of 400 pF. The data on the SDA line must be stable during the high period of the clock. The high or low state of the data line can only change with the clock signal on the SCL line being low.

- Transferring multiple bytes during one read or write operation, the internal subaddress is not automatically incremented.

- A high to low transition on the SDA line while the SCL is high indicates a start condition.

- A low to high transition on the SDA line while the SCL is high indicates a stop condition

- Acknowledge (SDA low)

- Not–Acknowledge (SDA high)

Every byte placed on the SDA line must be 8 bits long. The number of bytes that can be transferred is unrestricted. An acknowledge bit follows each byte. If the slave can not receive another complete byte of data until it has performed another function, it holds the clock line (SCL) low. An SCL low forces the master into a wait state. Data transfer continues when the slave is ready for another byte of data and releases the clock line (SCL).

Data transfer with acknowledge is necessary. The master generates an acknowledge related clock pulse. The master releases the SDA line high during the acknowledge clock pulse. The slave pulls down the SDA line during the acknowledge clock pulse so that it remains stable low during the high period of this clock pulse.

When a slave does not acknowledge the slave address, the data line is left high. The master then generates a stop condition to abort the transfer.

If a slave acknowledges the slave address, but some time later in the transfer cannot receive any more data bytes, the master again aborts the transfer. The slave indicates a not ready condition by generating the not acknowledge. The slave leaves the data line high and the master generates the stop condition.

If a master-receiver is involved in a transfer, it indicates the end of data to the slave-transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave-transmitter must release the data line to allow the master to generate a stop or repeated start condition.

## 2.3.1 I<sup>2</sup>C Write Operation

Data transfers occur using the following illustrated formats.

The I<sup>2</sup>C master initiates a write operation to the TVP5010 by generating a start condition followed by the TVP5010's I<sup>2</sup>C address (101110X). The address is in MSB first bit order followed by a 0 to indicate a write cycle. After receiving a TVP5010 acknowledge, the I<sup>2</sup>C master sends a subaddress of the register or the block of registers where it will write. Following the subaddress is one or more bytes of data, with MSB first. The TVP5010 acknowledges the receipt of each byte upon completion of each transfer. The I<sup>2</sup>C master ends a write operation by generating a stop condition.

The X in the address of the TVP5010 is 0 when the  $I^2CA$  terminal is low and the X is 1 when the  $I^2CA$  is high. If the read or write cycle contains more than one byte, the internal subaddress increments automatically.

|                                               |      | -    |      |      |      |      |      |      |

|-----------------------------------------------|------|------|------|------|------|------|------|------|

|                                               | 0    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Start (Master)               | S    |      |      |      |      |      |      |      |

|                                               |      |      |      |      |      |      |      |      |

|                                               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General Address (Master)     | 1    | 0    | 1    | 1    | 1    | 0    | Χ    | 0    |

|                                               |      | 1    |      |      |      |      |      |      |

|                                               | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)          | А    |      |      |      |      |      |      |      |

|                                               |      |      |      |      |      |      |      |      |

|                                               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write Register Address (Mas) | Addr |

|                                               |      | 1    |      |      |      |      |      |      |

|                                               | 9    | 1    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)          | А    | ]    |      |      |      |      |      |      |

|                                               |      |      |      |      |      |      |      |      |

|                                               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write Data (Master)          | Data |

|                                               |      | 1    |      |      |      |      |      |      |

|                                               | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)          | А    | ]    |      |      |      |      |      |      |

|                                               |      | 1    |      |      |      |      |      |      |

|                                               | 0    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (Master)                | Р    |      |      |      |      |      |      |      |

| ,                                             |      | 4    |      |      |      |      |      |      |

## 2.3.2 I<sup>2</sup>C Read Operation

The read operation has two phases, the address phase and the data phase. In the address phase, the I $^2$ C master initiates a write operation to the TVP5010 by generating a start condition followed by the TVP5010's I $^2$ C address (101110X). The address is in MSB first bit order followed by a 0 to indicate a write cycle. After receiving a TVP5010 acknowledge, the I $^2$ C master sends a subaddress of the register or the block of registers where it will read. The TVP5010 acknowledges the receipt of the address upon completion of each transfer. The I $^2$ C master ends a read operation by generating a stop condition. During the data phase, the I $^2$ C master initiates a read operation to the TVP5010 by generating a start condition followed by the TVP5010's I $^2$ C address (101110X). The address is in MSB first bit order followed by a 1 to indicate a read cycle. The I $^2$ C master acknowledges the receipt of each byte upon completion of each transfer. After the TVP5010 transfers the last byte, the I $^2$ C master ends the read operation by generating a not acknowledge followed by a stop condition.

#### Read Phase 1

|                                               | 0    |      |      |      |      |      |      |      |

|-----------------------------------------------|------|------|------|------|------|------|------|------|

| I <sup>2</sup> C Start (Master)               | S    | ]    |      |      |      |      |      |      |

|                                               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General Address (Master)     | 1    | 0    | 1    | 1    | 1    | 0    | Х    | 0    |

|                                               | 9    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)          | А    | ]    |      |      |      |      |      |      |

|                                               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write Register Address (Mas) | Addr |

|                                               | 9    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)          | А    | ]    |      |      |      |      |      |      |

|                                               | i    | 1    |      |      |      |      |      |      |

|                                               | 0    |      |      |      |      |      |      |      |

#### Read Phase 2

|                                           | 0    |      |      |      |      |      |      |      |

|-------------------------------------------|------|------|------|------|------|------|------|------|

| I <sup>2</sup> C Start (Master)           | S    |      |      |      |      |      |      |      |

|                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General Address (Master) | 1    | 0    | 1    | 1    | 1    | 0    | Х    | 1    |

|                                           | 9    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)      | А    | ]    |      |      |      |      |      |      |

|                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Read Data (Slave)        | Data |

|                                           | 9    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)      | /A   | ]    |      |      |      |      |      |      |

|                                           |      | 1    |      |      |      |      |      |      |

|                                           | 0    |      |      |      |      |      |      |      |

## 2.3.3 I2C Microcode Write Operation

Data written during the microcode write operation will be written to the TVP5010 program RAM. Upon completion of the microcode download an internal reset will be generated to reset the TVP5010 internal microprocessor and the microprocessor will begin executing microcode from address zero. The internal microprocessor initializes all the I<sup>2</sup>C registers with their defaults and begins normal operation. All user accesses to I<sup>2</sup>C registers can proceed from this point.

| •                                             |          |      |      |      |      |      |      |      |

|-----------------------------------------------|----------|------|------|------|------|------|------|------|

|                                               | 0        | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Start (Master)               | S        | ]    |      |      |      |      |      |      |

|                                               | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General Address (Master)     | 1        | 0    | 1    | 1    | 1    | 0    | Х    | 0    |

|                                               | Ι .      | 1    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)          | <b>9</b> |      |      |      |      |      |      |      |

|                                               | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write Register Address (Mas) | 1        | 1    | 1    | 1    | 0    | 0    | 0    | 0    |

|                                               | 9        | 1    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)          | A        |      |      |      |      |      |      |      |

|                                               | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write Data (Master)          | Data     | Data | Data | Data | Data | Data | Data | Data |

|                                               | 9        | 1    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)          | A        |      |      |      |      |      |      |      |

|                                               | 0        | 1    |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (Master)                | P        | 1    |      |      |      |      |      |      |

## 2.3.4 I<sup>2</sup>C Microcode Read Operation

Data read during the microcode read operation will be read from the TVP5010 Program RAM. Upon completion of the microcode read operation an internal reset will be generated to reset the TVP5010 internal microprocessor and the microprocessor will begin executing microcode from address zero.

|                                                 | _        | 1      |      |      |      |      |      |      |

|-------------------------------------------------|----------|--------|------|------|------|------|------|------|

|                                                 | 0        |        |      |      |      |      |      |      |

| I <sup>2</sup> C Start (Master)                 | S        |        |      |      |      |      |      |      |

|                                                 | 7        |        |      |      |      |      |      |      |

| 1200                                            | 7        | 6      | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General Address (Master)       | 1        | 0      | 1    | 1    | 1    | 0    | Х    | 0    |

|                                                 | 9        | 1      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)            | А        | 1      |      |      |      |      |      |      |

|                                                 | i        |        |      |      |      |      |      |      |

| 22.7                                            | 7        | 6      | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Read Register Address (Master) | 1        | 1      | 1    | 1    | 0    | 0    | 0    | 1    |

|                                                 | 9        | ]      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)            | А        | 1      |      |      |      |      |      |      |

|                                                 | 0        | 1      |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (Master)                  | P        | 1      |      |      |      |      |      |      |

| 1 o dtop (Master)                               | <u>'</u> | 1      |      |      |      |      |      |      |

| Read Phase 2                                    |          |        |      |      |      |      |      |      |

|                                                 | 0        | ]      |      |      |      |      |      |      |

| I <sup>2</sup> C Start (Master)                 | S        | 1      |      |      |      |      |      |      |

|                                                 |          | -      |      |      |      |      |      |      |

|                                                 | 7        | 6      | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General Address (Master)       | 1        | 0      | 1    | 1    | 1    | 0    | Х    | 1    |

|                                                 |          | ,      |      |      |      |      |      |      |

|                                                 | 7        |        |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)            | Α        | ]      |      |      |      |      |      |      |

|                                                 |          | -<br>- |      |      |      |      |      |      |

|                                                 | 7        | 6      | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Read Data (Slave)              | Data     | Data   | Data | Data | Data | Data | Data | Data |

|                                                 | т_       | 1      |      |      |      |      |      |      |

| -2                                              | 7        | 1      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Master)           | Α        | ]      |      |      |      |      |      |      |

|                                                 | 7        | 6      | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Read Data (Slave)              | Data     | Data   | Data | Data | Data | Data | Data | Data |

| Until all data is read from program n           | nemorv   |        |      |      |      |      |      |      |

| l a la         | 9        | 1      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Master)           | /A       | 1      |      |      |      |      |      |      |

| Li C Ackilowieuge (Master)                      | _ /A     | 1      |      |      |      |      |      |      |

0

Р

I<sup>2</sup>C Stop (Master)

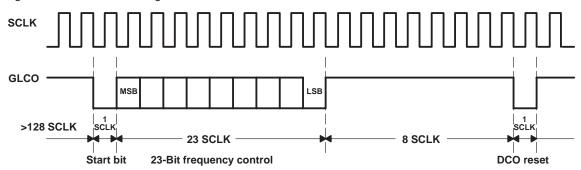

#### 2.4 Genlock Control

The frequency control word of the internal color subcarrier digital control oscillator (DCO) and the subcarrier phase reset bit are transmitted via the GLCO terminal. The frequency control word is a 23-bit binary number. The frequency of the DCO can be calculated from the following equation:

$$F_{dco} = \frac{F_{ctrl}}{2^{23}} \times F_{sclk}$$

Where  $F_{dCO}$  is the frequency of the DCO,  $F_{Ctrl}$  is the 23-bit DCO frequency control, and  $F_{SClk}$  is the frequency of the SCLK.

The last bit (bit 0) of the DCO frequency control is always 0.

A write of 1 to bit 4 of the chrominance control register at host port subaddress 1Ah causes the subcarrier DTO phase reset bit to be sent on the next scan line on GLCO. The active low reset bit occurs 8 SCLKs after the transmission of the last bit of DCO frequency control. Upon the transmission of the reset bit, the phase of the TVP5010 internal subcarrier DCO is reset to zero.

A genlocking slave device connected to the GLCO terminal can use the information on GLCO to synchronize its internal color phase DCO to achieve clean line and color lock.

Figure 2–13 shows the timing of GLCO.

Figure 2-13. GLCO Timing

## 2.5 Video Port Timing/Formatting

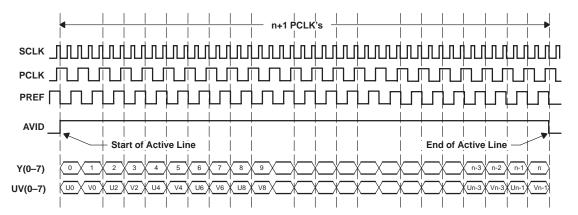

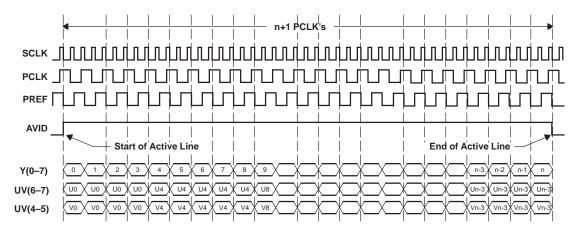

Applying the control signal to the OEB terminal and/or via host port control activates the YUV data outputs or sets them to high–impedance. When the host configures OEB to control the YUV outputs, then a logic 0 on OEB enables the output and a logic 1 puts the YUV output bus in a high impedance state. Alternately, OEB can be tied to ground and host port bus alone controls the YUV terminals. Figure 2–14 shows digital outputs, YUV, and the clock and control timing with OEB as the output control. PCLK and SCLK are the pixel clock and the system clock respectively. The active video indicator (AVID) signal defines which pixels in each horizontal video line contain picture information.

Figure 2–14. Functional Timing

The TVP5010 supports both square–pixel and ITU–R BT.601 sampling formats and multiple Y–UV output formats:

- 16-bit 4:2:2 See Table 2–3

- 12-bit 4:1:1 See Table 2-4

- 8-bit 4:2:2 See Table 2–5

- ITU-R BT.656 bit-parallel interface.

## 2.6 Video Port 16-bit 4:2:2 Mode

Table 2-3. Output Format: 16-Bit 4:2:2

Y BUS

| MSB |              |                |                |              |                |                |              | LSB            |

|-----|--------------|----------------|----------------|--------------|----------------|----------------|--------------|----------------|

| у   | Y7           | Y6             | Y5             | Y4           | Y3             | Y2             | Y1           | Y0             |

| 0   | Y <b>0</b> 7 | Y <b>0</b> 6   | Y <b>0</b> 5   | Y <b>0</b> 4 | Y <b>0</b> 3   | Y <b>0</b> 2   | Y <b>0</b> 1 | Y <b>0</b> 0   |

| 1   | Y17          | Y <b>1</b> 6   | Y <b>1</b> 5   | Y <b>1</b> 4 | Y <b>1</b> 3   | Y <b>1</b> 2   | Y <b>1</b> 1 | Y <b>1</b> 0   |

| 2   | Y <b>2</b> 7 | Y <b>2</b> 6   | Y <b>2</b> 5   | Y <b>2</b> 4 | Y <b>2</b> 3   | Y <b>2</b> 2   | Y <b>2</b> 1 | Y <b>2</b> 0   |

| 3   | Y37          | Y <b>3</b> 6   | Y <b>3</b> 5   | Y <b>3</b> 4 | Y <b>3</b> 3   | Y <b>3</b> 2   | Y <b>3</b> 1 | Y <b>3</b> 0   |

| 4   | Y <b>4</b> 7 | Y <b>4</b> 6   | Y <b>4</b> 5   | Y <b>4</b> 4 | Y <b>4</b> 3   | Y <b>4</b> 2   | Y <b>4</b> 1 | Y <b>4</b> 0   |

| 5   | Y <b>5</b> 7 | Y <b>5</b> 6   | Y <b>5</b> 5   | Y <b>5</b> 4 | Y <b>5</b> 3   | Y <b>5</b> 2   | Y <b>5</b> 1 | Y <b>5</b> 0   |

| 6   | Y <b>6</b> 7 | Y <b>6</b> 6   | Y <b>6</b> 5   | Y <b>6</b> 4 | Y <b>6</b> 3   | Y <b>6</b> 2   | Y <b>6</b> 1 | Y <b>6</b> 0   |

| 7   | Y <b>7</b> 7 | Y <b>7</b> 6   | Y <b>7</b> 5   | Y <b>7</b> 4 | Y <b>7</b> 3   | Y <b>7</b> 2   | Y <b>7</b> 1 | Y <b>7</b> 0   |

| :   | :            | :              | :              | :            | :              | :              | :            | :              |

| :   | :            | :              | :              | :            | :              | :              | :            | :              |

| :   | :            | :              | :              | :            | :              | :              | :            | :              |

| :   | Yn-3 7       | Y <b>n-3</b> 6 | Y <b>n-3</b> 5 | Yn-3 4       | Y <b>n-3</b> 3 | Y <b>n-3</b> 2 | Yn-3 1       | Y <b>n-3</b> 0 |

| :   | Yn-2 7       | Y <b>n-2</b> 6 | Y <b>n-2</b> 5 | Yn-2 4       | Y <b>n-2</b> 3 | Y <b>n–2</b> 2 | Yn-2 1       | Y <b>n-2</b> 0 |

| :   | Yn-17        | Y <b>n-1</b> 6 | Y <b>n-1</b> 5 | Yn-1 4       | Y <b>n-1</b> 3 | Y <b>n-1</b> 2 | Yn-1 1       | Y <b>n-1</b> 0 |

| n†  | Yn7          | Y <b>n</b> 6   | Y <b>n</b> 5   | Yn 4         | Y <b>n</b> 3   | Y <b>n</b> 2   | Yn 1         | Y <b>n</b> 0   |

U/V BUS

| MSB            |                |                |                |                |                |                |                | LSB |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----|

| UV7            | UV6            | UV5            | UV4            | UV3            | UV2            | UV1            | UV0            | uv  |

| U <b>0</b> 7   | U <b>0</b> 6   | U <b>0</b> 5   | U <b>0</b> 4   | U <b>0</b> 3   | U <b>0</b> 2   | U <b>0</b> 1   | U <b>0</b> 0   |     |

| <b>∨0</b> 7    | V <b>0</b> 6   | V <b>0</b> 5   | <b>∨0</b> 4    | V <b>0</b> 3   | V <b>0</b> 2   | <b>∨0</b> 1    | V <b>0</b> 0   | 0   |

| U <b>2</b> 7   | U <b>2</b> 6   | U <b>2</b> 5   | U <b>2</b> 4   | U <b>2</b> 3   | U <b>2</b> 2   | U <b>2</b> 1   | U <b>2</b> 0   |     |

| <b>∨2</b> 7    | V <b>2</b> 6   | V <b>2</b> 5   | V <b>2</b> 4   | V <b>2</b> 3   | V <b>2</b> 2   | V <b>2</b> 1   | V <b>2</b> 0   | 2   |

| U <b>4</b> 7   | U <b>4</b> 6   | U <b>4</b> 5   | U <b>4</b> 4   | U <b>4</b> 3   | U <b>4</b> 2   | U <b>4</b> 1   | U <b>4</b> 0   |     |

| V <b>4</b> 7   | V <b>4</b> 6   | V <b>4</b> 5   | V <b>4</b> 4   | V <b>4</b> 3   | V <b>4</b> 2   | V <b>4</b> 1   | V <b>4</b> 0   | 4   |

| U <b>6</b> 7   | U <b>6</b> 6   | U <b>6</b> 5   | U <b>6</b> 4   | U <b>6</b> 3   | U <b>6</b> 2   | U <b>6</b> 1   | U <b>6</b> 0   |     |

| V <b>6</b> 7   | V <b>6</b> 6   | V <b>6</b> 5   | V <b>6</b> 4   | V <b>6</b> 3   | V <b>6</b> 2   | V61            | V <b>6</b> 0   | 6   |

| :              | :              | :              | :              | :              | :              | :              | :              | :   |

| :              | :              | :              | :              | :              | :              | :              | :              | :   |

| :              | :              | :              | :              | :              | :              | :              | :              | :   |

| U <b>n-3</b> 7 | U <b>n-3</b> 6 | U <b>n-3</b> 5 | U <b>n−3</b> 4 | U <b>n−3 3</b> | U <b>n-3</b> 2 | U <b>n−3</b> 1 | U <b>n-3</b> 0 | n–3 |

| ∨n <b>–3</b> 7 | <b>∀n−3</b> 6  | <b>∀n–3</b> 5  | ∨n–3 4         | <b>∀n−3</b> 3  | V <b>n−3</b> 2 | ∨n–3 1         | <b>∀n−3</b> 0  |     |

| U <b>n-1</b> 7 | U <b>n-1</b> 6 | U <b>n-1</b> 5 | U <b>n-1</b> 4 | U <b>n-1</b> 3 | U <b>n-1</b> 2 | U <b>n-1</b> 1 | U <b>n-1</b> 0 |     |

| ∨n–1 7         | V <b>n−1</b> 6 | V <b>n−1</b> 5 | ∨n–1 4         | V <b>n−1</b> 3 | V <b>n−1</b> 2 | ∨ <b>n–1</b> 1 | V <b>n−1</b> 0 | n–1 |

<sup>†</sup> The last pixel number of each active line; n=639 for NTSC square-pixel, n=767 for PAL square-pixel, and n=719 for ITU-R BT.601 (NTSC and PAL).

Figure 2–15. 16-Bit 4:2:2 Functional Timing

## 2.7 Video Port 12-Bit 4:1:1 Mode

Table 2–4. Output Format: 12-Bit 4:1:1

Y BUS

|    | MSB          |                |                |              |                |                |              | LSB            |

|----|--------------|----------------|----------------|--------------|----------------|----------------|--------------|----------------|

| у  | Y7           | Y6             | Y5             | Y4           | Y3             | Y2             | Y1           | Y0             |

| 0  | Y <b>0</b> 7 | Y <b>0</b> 6   | Y <b>0</b> 5   | Y <b>0</b> 4 | Y <b>0</b> 3   | Y <b>0</b> 2   | Y <b>0</b> 1 | Y <b>0</b> 0   |

| 1  | Y17          | Y16            | Y <b>1</b> 5   | Y <b>1</b> 4 | Y <b>1</b> 3   | Y12            | Y <b>1</b> 1 | Y <b>1</b> 0   |

| 2  | Y <b>2</b> 7 | Y <b>2</b> 6   | Y <b>2</b> 5   | Y <b>2</b> 4 | Y <b>2</b> 3   | Y <b>2</b> 2   | Y <b>2</b> 1 | Y <b>2</b> 0   |

| 3  | Y <b>3</b> 7 | Y <b>3</b> 6   | Y <b>3</b> 5   | Y <b>3</b> 4 | Y <b>3</b> 3   | Y <b>3</b> 2   | Y <b>3</b> 1 | Y <b>3</b> 0   |

| 4  | Y <b>4</b> 7 | Y <b>4</b> 6   | Y <b>4</b> 5   | Y <b>4</b> 4 | Y <b>4</b> 3   | Y <b>4</b> 2   | Y <b>4</b> 1 | Y <b>4</b> 0   |

| 5  | Y <b>5</b> 7 | Y <b>5</b> 6   | Y <b>5</b> 5   | Y <b>5</b> 4 | Y <b>5</b> 3   | Y <b>5</b> 2   | Y <b>5</b> 1 | Y <b>5</b> 0   |

| 6  | Y <b>6</b> 7 | Y <b>6</b> 6   | Y <b>6</b> 5   | Y <b>6</b> 4 | Y <b>6</b> 3   | Y <b>6</b> 2   | Y <b>6</b> 1 | Y <b>6</b> 0   |

| 7  | Y <b>7</b> 7 | Y <b>7</b> 6   | Y <b>7</b> 5   | Y <b>7</b> 4 | Y <b>7</b> 3   | Y <b>7</b> 2   | Y <b>7</b> 1 | Y <b>7</b> 0   |

| :  | :            | :              | :              | :            | :              | :              | :            | :              |

| :  | :            | :              | :              | :            | :              | :              | :            | :              |

| :  | :            | :              | :              | :            | :              | :              | :            | :              |

| :  | Yn-3 7       | Y <b>n-3</b> 6 | Y <b>n-3</b> 5 | Yn-3 4       | Y <b>n-3</b> 3 | Y <b>n-3</b> 2 | Yn-3 1       | Yn-3 0         |

| :  | Yn-2 7       | Y <b>n-2</b> 6 | Y <b>n-2</b> 5 | Yn-2 4       | Y <b>n-2</b> 3 | Y <b>n-2</b> 2 | Yn-2 1       | Y <b>n-2</b> 0 |

| :  | Yn-17        | Y <b>n-1</b> 6 | Y <b>n-1</b> 5 | Yn-1 4       | Y <b>n-1</b> 3 | Y <b>n-1</b> 2 | Yn-1 1       | Y <b>n-1</b> 0 |

| n† | Yn7          | Y <b>n</b> 6   | Y <b>n</b> 5   | Yn 4         | Yn 3           | Y <b>n</b> 2   | Yn 1         | Y <b>n</b> 0   |

## U/V BUS

| MSB            |                |                |                |      |                                 |     |     | LSB |  |

|----------------|----------------|----------------|----------------|------|---------------------------------|-----|-----|-----|--|

| UV7            | UV6            | UV5            | UV4            | uv   | UV3                             | UV2 | UV1 | UV0 |  |

| U <b>0</b> 7   | U <b>0</b> 6   | <b>∨0</b> 7    | <b>∨0</b> 6    |      |                                 |     |     |     |  |

| U <b>0</b> 5   | U <b>0</b> 4   | V <b>0</b> 5   | <b>∨0</b> 4    | 0    |                                 |     |     |     |  |

| U <b>0</b> 3   | U <b>0</b> 2   | V <b>0</b> 3   | V <b>0</b> 2   |      |                                 |     |     |     |  |

| U <b>0</b> 1   | U <b>0</b> 0   | V <b>0</b> 1   | <b>∨0</b> 0    |      |                                 |     |     |     |  |

| U <b>4</b> 7   | U <b>4</b> 6   | V <b>4</b> 7   | V <b>4</b> 6   |      |                                 |     |     |     |  |

| U <b>4</b> 5   | U <b>4</b> 4   | V <b>4</b> 5   | V <b>4</b> 4   | 4    |                                 |     |     |     |  |

| U <b>4</b> 3   | U <b>4</b> 2   | V <b>4</b> 3   | V <b>4</b> 2   | 4    |                                 |     |     |     |  |

| U <b>4</b> 1   | U <b>4</b> 0   | V <b>4</b> 1   | V <b>4</b> 0   |      | These terminals are logic 0 out |     |     |     |  |

| :              | :              | :              | :              | :    |                                 |     |     |     |  |

| :              | :              | :              | :              | :    |                                 |     |     |     |  |

| :              | :              | :              | :              | :    |                                 |     |     |     |  |

| U <b>n-3</b> 7 | U <b>n-3</b> 6 | ∨n <b>–3</b> 7 | <b>∀n–3</b> 6  |      |                                 |     |     |     |  |

| U <b>n−3 5</b> | U <b>n−3</b> 4 | V <b>n−3</b> 5 | ∨n–3 4         | n–3  |                                 |     |     |     |  |

| U <b>n−3 3</b> | U <b>n-3</b> 2 | V <b>n−3</b> 3 | V <b>n−3</b> 2 | 11–3 |                                 |     |     |     |  |

| Un−3 1         | U <b>n-3</b> 0 | ∨n–3 1         | V <b>n−3</b> 0 |      |                                 |     |     |     |  |

$<sup>\</sup>dagger$  The last pixel number of each active line; n = 639 for NTSC square-pixel, n = 767 for PAL square-pixel, and n = 719 for ITU-R BT.601 (NTSC and PAL).

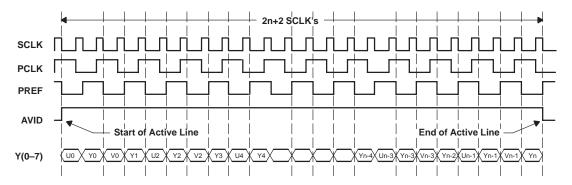

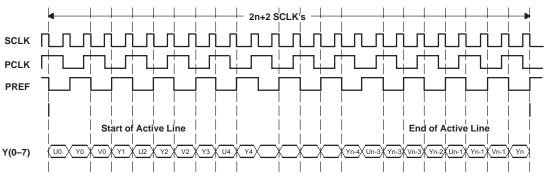

Figure 2-16. 12-bit 4:1:1 Functional Timing

## 2.8 Video Port 8-Bit 4:2:2 Mode