#### **General Description**

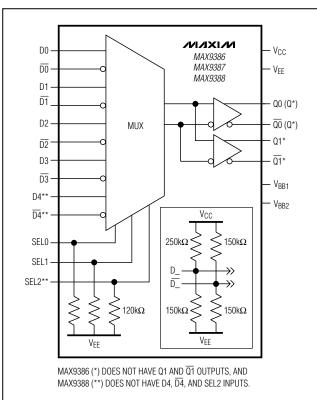

The MAX9386/MAX9387/MAX9388 are fully differential, high-speed, low-jitter ECL/PECL multiplexers (muxes) with output buffer(s). The devices are designed for clock-and-data distribution applications, and feature extremely low propagation delays (318ps, typ) and output-to-output skews (3.9ps, typ). The MAX9386 is a 5:1 mux with a single output buffer. The MAX9387 is a 5:1 mux with dual output buffers, and is intended for use in redundant systems. The MAX9388 is a 4:1 mux with a single output buffer, and is pin compatible with the MC100EP57.

Three single-ended select inputs, SEL0, SEL1, and SEL2, control the mux function on the MAX9386/ MAX9387. The MAX9388 has two select inputs, SEL0 and SEL1. The mux select inputs are compatible with ECL/PECL logic, and are internally referenced to the on-chip output VBB, nominally VCC - 1.425V. The select inputs accept signals between VCC and VEE. Internal pulldowns to VFF ensure a low-default condition if the select inputs are left open.

The differential inputs  $D_{-}$ ,  $\overline{D}_{-}$  can be configured to accept a single-ended signal when the unused complementary input is connected to the on-chip reference output VBB. All the differential inputs have internal bias and clamping circuits that ensure low-default output states when the inputs are left open.

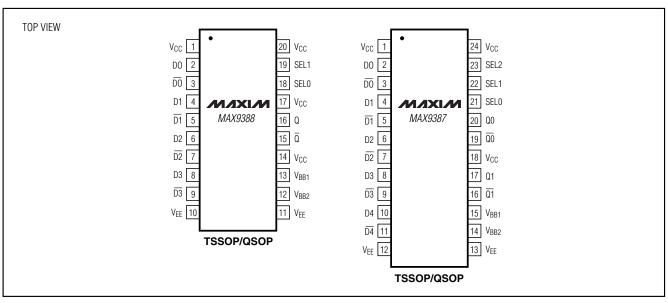

The MAX9386/MAX9387/MAX9388 operate with a wide supply range |VCC - VEE| of 2.375V to 5.5V. The MAX9386/MAX9388 are offered in 20-pin TSSOP and QSOP packages. The MAX9387 is offered in 24-pin TSSOP and QSOP packages.

### **Applications**

High-Speed Telecom and Datacom Applications Central Office Backplane Clock Distribution DSLAM/DLC

#### Features

- ♦ 318ps (typ) Propagation Delay

- ♦ >2.7GHz Toggle Frequency

- ♦ 0.3ps(RMS) Random Jitter

- ♦ <14ps (max) at +25°C Output-to-Output Skew

</p> (MAX9387)

- ♦ -2.375V to -5.5V Supplies for Differential LVECL/ECL

- ♦ +2.375V to +5.5V Supplies for Differential LVPECL/PECL

- **♦ Outputs Low for Open Inputs**

- ◆ Dual Output Buffers (MAX9387)

- ♦ Pin Compatible with MC100EP57 (MAX9388EUP)

- ♦ >2kV ESD Protection (Human Body Model)

#### **Ordering Information**

| PART        | TEMP<br>RANGE  | PIN-<br>PACKAGE | SELECTION                    |

|-------------|----------------|-----------------|------------------------------|

| MAX9386EUP  | -40°C to +85°C | 20 TSSOP        | 5:1 mux with 1 output buffer |

| MAX9386EEP* | -40°C to +85°C | 20 QSOP         | 5:1 mux with 1 output buffer |

Ordering Information continued at end of data sheet.

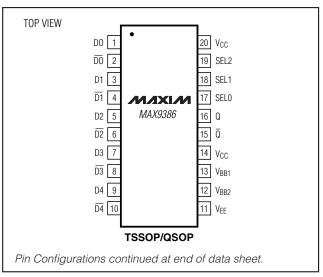

### Pin Configurations

N/IXI/N/

<sup>\*</sup>Future product—contact factory for availability.

#### **ABSOLUTE MAXIMUM RATINGS**

| VCC - VEE0.3V t<br>Inputs_(D_, D_, SEL_) to VEE0.3V to (VCC | + 0.3V) |

|-------------------------------------------------------------|---------|

| D_ to D                                                     |         |

| Continuous Output Current                                   |         |

| Surge Output Current                                        | 100mA   |

| VBB Sink/Source Current                                     | ±600µA  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)       | •       |

| 20-Lead TSSOP (derate 11.0mW/°C above +70°C)                | .880mW  |

| θ <sub>JA</sub> in Still Air+                               | -91°C/W |

| θJC+                                                        | -20°C/W |

| 24-Lead TSSOP (derate 12.2mW/°C above +70°C)                |         |

| θ <sub>JA</sub> in Still Air+                               | -82°C/W |

| θ <sub>JC</sub> +                                           | -15°C/W |

| 20-Lead QSOP (derate 9.1mW/°C above +70°C)727mW   |

|---------------------------------------------------|

| θ <sub>JA</sub> in Still Air+110°C/W              |

| θJC+34°C/W                                        |

| 24-Lead QSOP (derate 9.5mW/°C above +70°C)762mW   |

| θ <sub>JA</sub> in Still Air+105°C/W              |

| θ <sub>JC</sub> +34°C/W                           |

| Operating Temperature Range40°C to +85°C          |

| Junction Temperature+150°C                        |

| Storage Temperature Range65°C to +150°C           |

| ESD Protection                                    |

| Human Body Model (D_, D_, Q_, Q_, SEL_, VBB )≥2kV |

| Lead Temperature (soldering, 10s)+300°C           |

|                                                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} - V_{EE} = 2.375V \text{ to } 5.5V, \text{ outputs loaded with } 50\Omega \pm 1\% \text{ to } V_{CC} - 2V. \text{ Typical values are at } V_{CC} - V_{EE} = 3.3V, V_{IHD} = V_{CC} - 1V, V_{ILD} = V_{CC} - 1.5V, \text{ unless otherwise noted.})$  (Notes 1-4)

| PARAMETER                             | SYMBOL                                          | COND                                              | ITIONS                                      |                         | -40°C                                |                            |                            | +25°C             |                            |                             | +85°C             |                            | UNITS |

|---------------------------------------|-------------------------------------------------|---------------------------------------------------|---------------------------------------------|-------------------------|--------------------------------------|----------------------------|----------------------------|-------------------|----------------------------|-----------------------------|-------------------|----------------------------|-------|

| PARAMETER                             | STIVIBUL                                        | CONDITIONS                                        |                                             | MIN                     | TYP                                  | MAX                        | MIN                        | TYP               | MAX                        | MIN                         | TYP               | MAX                        | UNITS |

| INPUT (D_, D_, S                      | EL_)                                            |                                                   |                                             |                         |                                      |                            |                            |                   |                            |                             |                   |                            |       |

| Single-Ended<br>Input High<br>Voltage | V <sub>IH</sub>                                 | V <sub>BB</sub> conne<br>the unused<br>(Figure 1) |                                             | V <sub>CC</sub> - 1.225 |                                      | V <sub>CC</sub> - 0.880    | V <sub>CC</sub> - 1.225    |                   | V <sub>CC</sub> - 0.880    | V <sub>CC</sub> -<br>1.225  |                   | V <sub>CC</sub> - 0.880    | V     |

| Single-Ended<br>Input Low<br>Voltage  | VIL                                             | V <sub>BB</sub> conne<br>the unused<br>(Figure 1) |                                             | V <sub>CC</sub> - 1.945 |                                      | V <sub>CC</sub> -<br>1.625 | V <sub>CC</sub> -<br>1.945 |                   | V <sub>CC</sub> -<br>1.625 | V <sub>C</sub> C -<br>1.945 |                   | V <sub>CC</sub> -<br>1.625 | ٧     |

| Differential Input<br>High Voltage    | VIHD                                            | Figure 1                                          |                                             | V <sub>EE</sub> + 1.2   |                                      | Vcc                        | V <sub>EE</sub> + 1.2      |                   | Vcc                        | V <sub>EE</sub> + 1.2       |                   | Vcc                        | V     |

| Differential Input<br>Low Voltage     | V <sub>ILD</sub>                                | Figure 1                                          |                                             | VEE                     |                                      | V <sub>CC</sub> -<br>0.095 | VEE                        |                   | V <sub>CC</sub> - 0.095    | VEE                         |                   | V <sub>CC</sub> - 0.095    | >     |

| Differential Input<br>Voltage         | ut V <sub>IHD</sub> - V <sub>ILD</sub> Figure 1 | V <sub>CC</sub> - V <sub>EE</sub> < 3.0V          | 0.095                                       |                         | V <sub>CC</sub> -<br>V <sub>EE</sub> | 0.095                      |                            | V <sub>CC</sub> - | 0.095                      |                             | V <sub>CC</sub> - | V                          |       |

|                                       |                                                 | rigure i                                          | V <sub>CC</sub> - V <sub>EE</sub><br>≥ 3.0V | 0.095                   |                                      | 3.000                      | 0.095                      |                   | 3.000                      | 0.095                       |                   | 3.000                      | V     |

| Input Current                         | I <sub>IN</sub>                                 | VIH, VIL, VII                                     | HD, VILD                                    | -100                    |                                      | +100                       | -100                       |                   | +100                       | -100                        |                   | +100                       | μΑ    |

#### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} - V_{EE} = 2.375 V \text{ to } 5.5 V)$ , outputs loaded with  $50\Omega \pm 1\%$  to  $V_{CC} - 2V$ . Typical values are at  $V_{CC} - V_{EE} = 3.3 V$ ,  $V_{IHD} = V_{CC} - 1V$ ,  $V_{ILD} = V_{CC} - 1.5 V$ , unless otherwise noted.) (Notes 1–4)

| PARAMETER                              | SYMBOL                                 | CONDITIONS                                          |                          | -40°C                      |                            |                         | +25°C                      |                            |                         | +85°C                      |                            | UNITS |

|----------------------------------------|----------------------------------------|-----------------------------------------------------|--------------------------|----------------------------|----------------------------|-------------------------|----------------------------|----------------------------|-------------------------|----------------------------|----------------------------|-------|

| PANAMETER                              | STIMBOL                                | CONDITIONS                                          | MIN                      | TYP                        | MAX                        | MIN                     | TYP                        | MAX                        | MIN                     | TYP                        | MAX                        | UNITS |

| OUTPUT (Q_, $\overline{Q}$             | )                                      |                                                     |                          |                            |                            |                         |                            |                            |                         |                            |                            |       |

| Single-Ended<br>Output High<br>Voltage | Voн                                    | Figure 2                                            | V <sub>CC</sub> - 1.145  |                            | V <sub>CC</sub> - 0.895    | V <sub>CC</sub> - 1.145 |                            | V <sub>CC</sub> - 0.895    | V <sub>CC</sub> - 1.145 |                            | V <sub>CC</sub> - 0.895    | V     |

| Single-Ended<br>Output Low<br>Voltage  | V <sub>OL</sub>                        | Figure 2                                            | V <sub>C</sub> C - 1.945 |                            | V <sub>CC</sub> -<br>1.695 | V <sub>CC</sub> - 1.945 |                            | V <sub>CC</sub> -<br>1.695 | V <sub>CC</sub> - 1.945 |                            | V <sub>CC</sub> -<br>1.695 | V     |

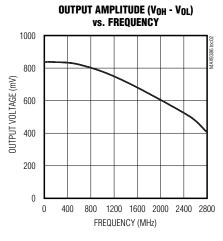

| Differential<br>Output Voltage         | V <sub>OH</sub> - V <sub>OL</sub>      | Figure 2                                            | 650                      | 830                        |                            | 650                     | 840                        |                            | 650                     | 840                        |                            | mV    |

| REFERENCE OU                           | TPUT (VBB_                             | _)                                                  |                          |                            |                            |                         |                            |                            |                         |                            |                            |       |

| Reference<br>Voltage Output            | V <sub>BB1</sub> ,<br>V <sub>BB2</sub> | $I_{BB1} + I_{BB2} = \pm 0.5 \text{mA}$<br>(Note 5) | V <sub>CC</sub> - 1.525  | V <sub>CC</sub> -<br>1.425 | V <sub>CC</sub> -<br>1.325 | V <sub>CC</sub> - 1.525 | V <sub>CC</sub> -<br>1.425 | V <sub>CC</sub> -<br>1.325 | V <sub>CC</sub> - 1.525 | V <sub>CC</sub> -<br>1.425 | V <sub>CC</sub> -<br>1.325 | ٧     |

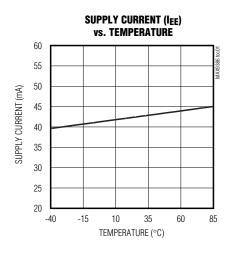

| POWER SUPPLY                           | POWER SUPPLY                           |                                                     |                          |                            |                            |                         |                            |                            |                         |                            |                            |       |

|                                        |                                        | MAX9386                                             |                          | 34                         | 50                         |                         | 36                         | 50                         |                         | 38                         | 50                         |       |

| Supply Current (Note 6)                | IEE                                    | MAX9387                                             |                          | 40                         | 60                         |                         | 42                         | 60                         |                         | 45                         | 60                         | mA    |

| (14016-0)                              |                                        | MAX9388                                             |                          | 31                         | 47                         |                         | 33                         | 47                         |                         | 35                         | 47                         |       |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} - V_{EE} = 2.375V \text{ to } 5.5V)$ , outputs loaded with  $50\Omega \pm 1\%$  to  $V_{CC} - 2V$ ,  $V_{IHD} - V_{ILD} = 0.15V$  to 1V,  $f_{IN} \le 2.5GHz$  input duty cycle = 50%, input transition time = 125ps (20% to 80%). Typical values are at  $V_{CC} - V_{EE} = 3.3V$ ,  $V_{IHD} = V_{CC} - 1V$ ,  $V_{ILD} = V_{CC} - 1.5V$ ,  $f_{IN} = 622MHz$ , input duty cycle = 50%, input transition time = 125ps (20% to 80%), unless otherwise noted.) (Note 7)

| PARAMETER                                | CVMDOL          | CONDITIONS                                                          |     | -40°C |      |     | +25°C |     |     | +85°C |     | UNITS |

|------------------------------------------|-----------------|---------------------------------------------------------------------|-----|-------|------|-----|-------|-----|-----|-------|-----|-------|

| PARAMETER                                | SYMBOL          | CONDITIONS                                                          | MIN | TYP   | MAX  | MIN | TYP   | MAX | MIN | TYP   | MAX | UNITS |

| Differential<br>Input-to-Output<br>Delay | tpLHD,<br>tpHLD | Figure 2                                                            | 222 | 309   | 377  | 238 | 318   | 395 | 254 | 333   | 431 | ps    |

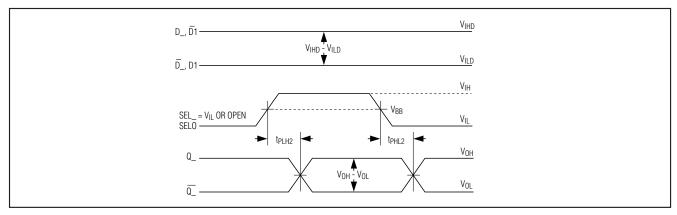

| SELto-Output<br>Delay                    | tpLH2,<br>tpHL2 | Figure 4, input<br>transition time = 500ps<br>(20% to 80%) (Note 8) |     |       | 1.64 |     |       | 1.4 |     |       | 1.6 | ns    |

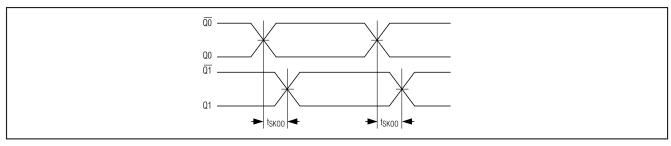

| Output-to-<br>Output Skew                | tskoo           | MAX9387 only, Figure 5 (Note 9)                                     |     | 3.9   | 26   |     | 3.9   | 14  |     | 8.0   | 26  | ps    |

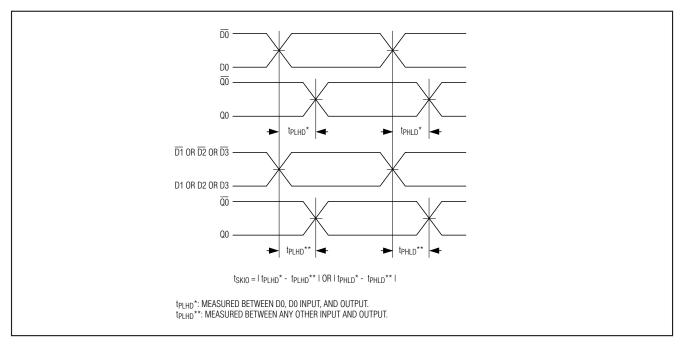

| Input-to-Output<br>Skew                  | tskio           | Figure 6 (Note 10)                                                  |     | 7.3   | 53   |     | 7.7   | 50  |     | 8.3   | 50  | ps    |

| Part-to-Part Skew                        | tskpp           | (Note 11)                                                           |     |       | 111  |     |       | 130 |     |       | 133 | ps    |

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

$V_{CC}$  -  $V_{EE}$  = 2.375V to 5.5V, outputs loaded with 50 $\Omega$  ±1% to  $V_{CC}$  - 2V,  $V_{IHD}$  -  $V_{ILD}$  = 0.15V to 1V,  $f_{IN}$   $\leq$  2.5GHz input duty cycle = 50%, input transition time = 125ps (20% to 80%). Typical values are at  $V_{CC}$  -  $V_{EE}$  = 3.3V,  $V_{IHD}$  =  $V_{CC}$  - 1V,  $V_{ILD}$  =  $V_{CC}$  - 1.5V,  $f_{IN}$  = 622MHz, input duty cycle = 50%, input transition time = 125ps (20% to 80%), unless otherwise noted.) (Note 7)

| DADAMETED                                    | CVMDOL                          | CONDITIONS                                   |                           |                           | -40°C |      |     | +25°C |      |     | +85°C |      | UNITS   |

|----------------------------------------------|---------------------------------|----------------------------------------------|---------------------------|---------------------------|-------|------|-----|-------|------|-----|-------|------|---------|

| PARAMETER                                    | SYMBOL                          |                                              |                           | MIN                       | TYP   | MAX  | MIN | TYP   | MAX  | MIN | TYP   | MAX  | UNITS   |

|                                              |                                 |                                              | $f_{IN} = 156MHz$         |                           | 0.3   | 1.15 |     | 0.3   | 1.15 |     | 0.3   | 1.15 |         |

| Added Random Jitter (Note 12)                | t <sub>RJ</sub>                 | Clock<br>pattern                             | $f_{IN} = 622MHz$         |                           | 0.3   | 1.15 |     | 0.3   | 1.15 |     | 0.3   | 1.15 | ps(RMS) |

| Office (140to 12)                            |                                 | pattern                                      | $f_{IN} = 2.5GHz$         |                           | 0.3   | 1.15 |     | 0.3   | 1.15 |     | 0.3   | 1.15 |         |

| Added                                        | eterministic T <sub>DJ</sub>    | PRBS                                         | f <sub>IN</sub> = 156Mbps |                           | 33    | 95   |     | 33    | 95   |     | 33    | 95   | 200     |

| Jitter (Note 12)                             |                                 | <sup>1DJ</sup> 2 <sup>23</sup>               | 2 <sup>23</sup> - 1       | f <sub>IN</sub> = 622Mbps |       | 21   | 61  |       | 21   | 61  |       | 21   | 61      |

| Switching<br>Frequency                       | f <sub>MAX</sub>                | V <sub>OH</sub> - V <sub>O</sub><br>Figure 2 | oL ≥ 300mV,               | 2.7                       |       |      | 2.7 |       |      | 2.7 |       |      | GHz     |

| Select Toggle<br>Frequency                   | fSEL                            |                                              |                           | 100                       |       |      | 100 |       |      | 100 |       |      | MHz     |

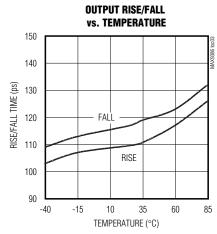

| Output Rise and<br>Fall Time (20%<br>to 80%) | t <sub>R</sub> , t <sub>F</sub> | Figure 2                                     |                           | 67                        | 105   | 138  | 74  | 117   | 155  | 81  | 128   | 165  | ps      |

- Note 1: Measurements are made with the device in thermal equilibrium.

- Note 2: Current into an I/O pin is defined as positive. Current out of an I/O pin is defined as negative.

- **Note 3:** DC parameters production tested at  $T_A = +25$ °C and guaranteed by design over the full operating temperature range.

- **Note 4:** Single-ended data input operation using  $V_{BB}$  is limited to  $(V_{CC} V_{EE}) \ge 3.0V$ .

- **Note 5:** Use V<sub>BB</sub> only for inputs that are on the same device as the V<sub>BB</sub> reference.

- Note 6: All pins open except VCC and VEE.

- Note 7: Guaranteed by design and characterization. Limits are set at ±6 sigma.

- Note 8: Measured from the 50% point of the input signal with the 50% point equal to VBB, to the 50% point of the output signal.

- Note 9: Measured between outputs of the same part at the signal crossing points for a same-edge transition.

- Note 10: Measured between input-to-output paths of the same part at the signal crossing points for a same-edge transition of the differential input signal.

- Note 11: Measured between outputs of different parts at the signal crossing points under identical conditions for a same-edge transition.

- Note 12: Device jitter added to the differential input signal.

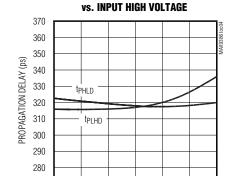

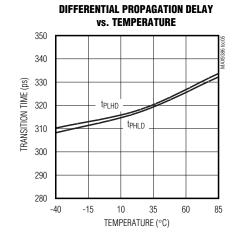

### Typical Operating Characteristics

$(V_{CC} - V_{EE} = 3.3V, V_{IHD} = V_{CC} - 1V, V_{ILD} = V_{CC} - 1.5V,$  outputs loaded with  $50\Omega \pm 1\%$  to  $V_{CC} - 2V$ ,  $f_{IN} = 1.5GHz$ , input duty cycle = 50%, input transition time = 125ps (20% to 80%), unless otherwise noted.)

1.2

1.5 1.8 2.1

2.4

INPUT HIGH VOLTAGE (V)

2.7

3.0

**DIFFERENTIAL PROPAGATION DELAY**

### MAX9386/MAX9388 Pin Description

| PIN     |                 |                  |                                                                                                                                                                                                                           |

|---------|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX9386 | MAX9388         | NAME             | FUNCTION                                                                                                                                                                                                                  |

| 1       | 2               | D0               | Noninverting Differential Input 0. Internal 250k $\Omega$ to V <sub>CC</sub> and 150k $\Omega$ to V <sub>EE</sub> .                                                                                                       |

| 2       | 3               | D0               | Inverting Differential Input 0. Internal 150k $\Omega$ to V <sub>CC</sub> and 150k $\Omega$ to V <sub>EE</sub> .                                                                                                          |

| 3       | 4               | D1               | Noninverting Differential Input 1. Internal 250k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                |

| 4       | 5               | D1               | Inverting Differential Input 1. Internal 150k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                   |

| 5       | 6               | D2               | Noninverting Differential Input 2. Internal 250k $\Omega$ to V <sub>CC</sub> and 150k $\Omega$ to V <sub>EE</sub> .                                                                                                       |

| 6       | 7               | D2               | Inverting Differential Input 2. Internal 150k $\Omega$ to V <sub>CC</sub> and 150k $\Omega$ to V <sub>EE</sub> .                                                                                                          |

| 7       | 8               | D3               | Noninverting Differential Input 3. Internal 250k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                |

| 8       | 9               | D3               | Inverting Differential Input 3. Internal 150k $\Omega$ to V <sub>CC</sub> and 150k $\Omega$ to V <sub>EE</sub> .                                                                                                          |

| 9       | _               | D4               | Noninverting Differential Input 4. Internal 250k $\Omega$ to V <sub>CC</sub> and 150k $\Omega$ to V <sub>EE</sub> .                                                                                                       |

| 10      | _               | D4               | Inverting Differential Input 4. Internal 150k $\Omega$ to V <sub>CC</sub> and 150k $\Omega$ to V <sub>EE</sub> .                                                                                                          |

| 11      | 10, 11          | VEE              | Negative Supply                                                                                                                                                                                                           |

| 12      | 12              | V <sub>BB2</sub> | Reference Output Voltage 2. Connect to the inverting or noninverting data input to provide a reference for single-ended operation. When used, bypass VBB2 to VCC with a 0.01µF ceramic capacitor. Otherwise leave open.   |

| 13      | 13              | V <sub>BB1</sub> | Reference Output Voltage 1. Connect to the inverting or noninverting data input to provide a reference for single-ended operation. When used, bypass VBB1 to VCC with a 0.01µF ceramic capacitor. Otherwise leave open.   |

| 14, 20  | 1, 14<br>17, 20 | Vcc              | Positive Supply. Bypass each V <sub>CC</sub> to V <sub>EE</sub> with 0.1µF and 0.01µF ceramic capacitors. Place the capacitors as close to the device as possible with the smaller value capacitor closest to the device. |

| 15      | 15              | Q                | Inverting Output. Typically terminate with $50\Omega$ resistor to $V_{CC}$ - $2V$ .                                                                                                                                       |

| 16      | 16              | Q                | Noninverting Output. Typically terminate with $50\Omega$ resistor to $V_{CC}$ - $2V$ .                                                                                                                                    |

| 17      | 18              | SEL0             | Select Logic Input 0. Internal 120kΩ pulldown to V <sub>EE</sub> .                                                                                                                                                        |

| 18      | 19              | SEL1             | Select Logic Input 1. Internal 120kΩ pulldown to V <sub>EE</sub> .                                                                                                                                                        |

| 19      | _               | SEL2             | Select Logic Input 2. Internal 120kΩ pulldown to V <sub>EE</sub> .                                                                                                                                                        |

6 \_\_\_\_\_\_ /I/XI//I

### MAX9387 Pin Description

| PIN       |                  |                                                                                                                                                                                                                                                 |

|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX9387   | NAME             | FUNCTION                                                                                                                                                                                                                                        |

| 1, 18, 24 | Vcc              | Positive Supply. Bypass each $V_{CC}$ to $V_{EE}$ with $0.1\mu F$ and $0.01\mu F$ ceramic capacitors. Place the capacitors as close to the device as possible with the smaller value capacitor closest to the device.                           |

| 2         | D0               | Noninverting Differential Input 0. Internal 250k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                      |

| 3         | D0               | Inverting Differential Input 0. Internal 150k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                         |

| 4         | D1               | Noninverting Differential Input 1. Internal 250k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                      |

| 5         | D1               | Inverting Differential Input 1. Internal 150k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                         |

| 6         | D2               | Noninverting Differential Input 2. Internal 250k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                      |

| 7         | D2               | Inverting Differential Input 2. Internal 150k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                         |

| 8         | D3               | Noninverting Differential Input 3. Internal 250k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                      |

| 9         | D3               | Inverting Differential Input 3. Internal 150k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                         |

| 10        | D4               | Noninverting Differential Input 4. Internal 250k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                      |

| 11        | D4               | Inverting Differential Input 4. Internal 150k $\Omega$ to VCC and 150k $\Omega$ to VEE.                                                                                                                                                         |

| 12, 13    | VEE              | Negative Supply                                                                                                                                                                                                                                 |

| 14        | V <sub>BB2</sub> | Reference Output Voltage 2. Connect to the inverting or noninverting data input to provide a reference for single-ended operation. When used, bypass V <sub>BB2</sub> to V <sub>CC</sub> with a 0.01µF ceramic capacitor. Otherwise leave open. |

| 15        | V <sub>BB1</sub> | Reference Output Voltage 1. Connect to the inverting or noninverting data input to provide a reference for single-ended operation. When used, bypass V <sub>BB1</sub> to V <sub>CC</sub> with a 0.01µF ceramic capacitor. Otherwise leave open. |

| 16        | Q1               | Inverting Output 1. Typically terminate with $50\Omega$ resistor to $V_{CC}$ - $2V$ .                                                                                                                                                           |

| 17        | Q1               | Noninverting Output 1. Typically terminate with $50\Omega$ resistor to $V_{CC}$ - $2V$ .                                                                                                                                                        |

| 19        | Q0               | Inverting Output 0. Typically terminate with $50\Omega$ resistor to $V_{CC}$ - $2V$ .                                                                                                                                                           |

| 20        | Q0               | Noninverting Output 0. Typically terminate with $50\Omega$ resistor to $V_{CC}$ - 2V.                                                                                                                                                           |

| 21        | SEL0             | Select Logic Input 0. Internal 120kΩ pulldown to V <sub>EE</sub> .                                                                                                                                                                              |

| 22        | SEL1             | Select Logic Input 1. Internal 120kΩ pulldown to V <sub>EE</sub> .                                                                                                                                                                              |

| 23        | SEL2             | Select Logic Input 2. Internal 120kΩ pulldown to VEE.                                                                                                                                                                                           |

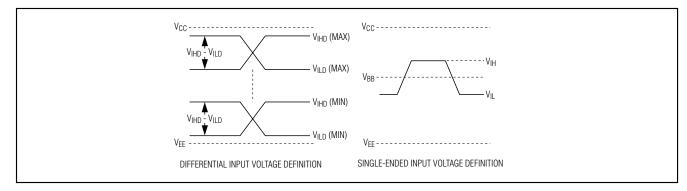

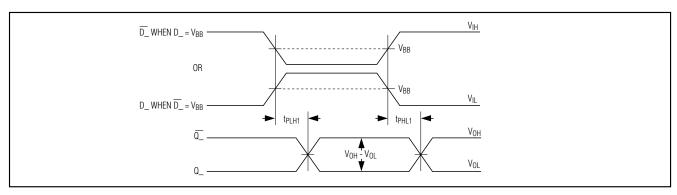

Figure 1. Input Definitions

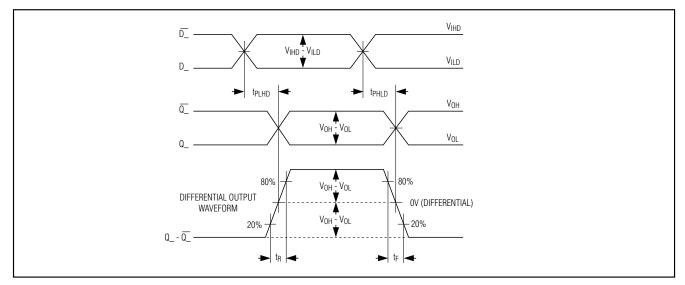

Figure 2. Differential Input-to-Output Propagation Delay Timing Diagram

Figure 3. Single-Ended Input-to-Output Propagation Delay Timing Diagram

Figure 4. Select Input (SEL0)-to-Output ( $Q_{-}, \overline{Q}_{-}$ ) Delay Timing Diagram

Figure 5. Output-to-Output Skew (t<sub>SKOO</sub>) Definition (MAX9387 Only)

Figure 6. Input-to-Output Skew (tSKIO) Definition

#### Detailed Description

The MAX9386/MAX9387/MAX9388 are fully differential, high-speed, and low-jitter ECL/PECL muxes with output buffer(s). The devices are designed for clock-and-data distribution applications, and feature extremely low propagation delays (318ps, typ) and output-to-output skews (3.9ps, typ). The MAX9386 is a 5:1 mux with a single output buffer. The MAX9387 is a 5:1 mux with dual output buffers, and is intended for use in redundant systems. The MAX9388 is a 4:1 mux with a single output buffer, and is pin compatible with the MC100EP57.

Three single-ended select inputs, SEL0, SEL1, and SEL2, control the mux function on the MAX9386/MAX9387. The MAX9388 has two select inputs, SEL0 and SEL1 (see Tables 1 and 2). The mux select inputs are compatible with ECL/PECL logic, and are internally referenced to the on-chip output VBB, nominally VCC - 1.425V. The select inputs accept signals between VCC and VEE. Internal 120k $\Omega$  pulldowns to VEE ensure a low default condition if the select inputs are left open, selecting the D0,  $\overline{\rm D0}$  input.

The differential inputs D,  $\overline{D}$  can be configured to accept a single-ended signal when the unused complementary input is connected to the on-chip reference voltage

Table 1. Mux Select Input Truth Table for MAX9386/MAX9387

| SEL2      | SEL1      | SEL0      | DATA OUTPUT |

|-----------|-----------|-----------|-------------|

| L or open | L or open | L or open | D0*         |

| L or open | L or open | Н         | D1          |

| L or open | Н         | L or open | D2          |

| L or open | Н         | Н         | D3          |

| Н         | X         | X         | D4          |

<sup>\*</sup>Default output when SEL0, SEL1, and SEL2 are left open.

Table 2. Mux Select Input Truth Table for MAX9388

| SEL1      | SEL0      | DATA OUTPUT |

|-----------|-----------|-------------|

| L or open | L or open | D0*         |

| L or open | Н         | D1          |

| Н         | L or open | D2          |

| Н         | Н         | D3          |

<sup>\*</sup>Default output when SEL0 and SEL1 are left open.

VBB. The reference output voltages, VBB1 and VBB2, provide the reference voltage for single-ended operation for each mux. A single-ended input of at least VBB\_  $\pm 100$ mV or a differential input of at least 100mV switches the outputs to the VOH and VOL levels specified in the DC Electrical Characteristics. The maximum magnitude of the differential input from D to  $\overline{\rm D}$  is  $\pm 3.0$ V. This limit also applies to the difference between a single-ended input and any reference voltage input.

Specifications for the high and low voltages of a differential input ( $V_{IHD}$  and  $V_{ILD}$ ) and the differential input voltage ( $V_{IHD}$  -  $V_{ILD}$ ) apply simultaneously.

#### **Single-Ended Operation**

The recommended supply voltage for single-ended operation is 3.0V to 5.5V. The differential inputs (D,  $\overline{D}$ ) can be configured to accept single-ended inputs when operating at supply voltages greater than 2.725V. In single-ended mode operation, the unused complementary input needs to be connected to the on-chip reference voltage,  $V_{BB}$ , as a reference. For example, the differential D,  $\overline{D}$  input is converted to a noninverting, single-ended input by connecting  $V_{BB}$  to  $\overline{D}$  and connecting the single-ended input to D. Similarly, an inverting input is obtained by connecting  $V_{BB}$  to D and connecting the single-ended input to  $\overline{D}$ . With a differential input configured as single ended (using  $V_{BB}$ ), the single-ended input can be driven to  $V_{CC}$  or  $V_{EE}$  or with a single-ended LVPECL/LVECL signal.

In single-ended mode operation, a user must ensure that the supply voltage (V<sub>CC</sub> - V<sub>EE</sub>) is greater than 2.725V. This is because the input high minimum level must be at (V<sub>EE</sub> + 1.2V) or higher for proper operation. The reference voltage, V<sub>BB</sub>, must be at least (V<sub>EE</sub> + 1.2V) for the same reason because it becomes the highlevel input when a single-ended input swings below it. The minimum V<sub>BB</sub> output for the MAX9386/MAX9387/ MAX9388 is (V<sub>CC</sub> - 1.38V). Substituting the minimum V<sub>BB</sub> output for (V<sub>BB</sub> = V<sub>EE</sub> + 1.2V) results in a minimum supply (V<sub>CC</sub> - V<sub>EE</sub>) of 2.725V. Rounding up to standard supplies gives the recommended single-ended operating supply ranges (V<sub>CC</sub> - V<sub>EE</sub>) of 3.0V to 5.5V.

When using the VBB reference output, bypass it with a  $0.01\mu F$  ceramic capacitor to VCC. If not used, leave it open. The VBB reference can source or sink a total of 0.5mA (shared between VBB1 and VBB2), which is sufficient to drive five inputs.

### Applications Information Output Termination

Terminate the outputs through  $50\Omega$  to V<sub>CC</sub> - 2V or use equivalent Thevenin terminations. Terminate each Q and  $\overline{Q}$  output with identical termination on each for minimal distortion. When a single-ended signal is taken from the differential output, terminate both Q and  $\overline{Q}$ .

Ensure that output currents do not exceed the current limits as specified in the *Absolute Maximum Ratings* table. Under all operating conditions, the device's total thermal limits should be observed.

#### Supply Bypassing

Bypass  $V_{CC}$  to  $V_{EE}$  with high-frequency surface-mount ceramic  $0.1\mu F$  and  $0.01\mu F$  capacitors. For PECL, bypass each  $V_{CC}$  to  $V_{EE}$ . For ECL, bypass each  $V_{EE}$  to  $V_{CC}$ . Place the capacitors as close to the device as possible with the  $0.01\mu F$  capacitor closest to the device pins.

Use multiple vias when connecting the bypass capacitors to ground. When using the V<sub>BB1</sub> or V<sub>BB2</sub> reference outputs, bypass each one with a 0.01µF ceramic capacitor to V<sub>CC</sub>. If the V<sub>BB1</sub> or V<sub>BB2</sub> reference outputs are not used, they can be left open.

#### Traces

Circuit board trace layout is very important to maintain the signal integrity of high-speed differential signals. Maintaining integrity is accomplished in part by reducing signal reflections and skew, and increasing common-mode noise immunity.

Signal reflections are caused by discontinuities in the  $50\Omega$  characteristic impedance of the traces. Avoid discontinuities by maintaining the distance between differential traces, not using sharp corners or using vias. Maintaining distance between the traces also increases common-mode noise immunity. Reducing signal skew is accomplished by matching the electrical length of the differential traces.

#### Chip Information

**TRANSISTOR COUNT: 583**

PROCESS: Bipolar

### Functional Block Diagram

### \_Ordering Information (continued)

| PART        | TEMP<br>RANGE  | PIN-<br>PACKAGE | SELECTION                     |

|-------------|----------------|-----------------|-------------------------------|

| MAX9387EUG  | -40°C to +85°C | 24 TSSOP        | 5:1 mux with 2 output buffers |

| MAX9387EEG* | -40°C to +85°C | 24 QSOP         | 5:1 mux with 2 output buffers |

| MAX9388EUP  | -40°C to +85°C | 20 TSSOP        | 4:1 mux with 1 output buffer  |

| MAX9388EEP* | -40°C to +85°C | 20 QSOP         | 4:1 mux with 1 output buffer  |

<sup>\*</sup>Future product—contact factory for availability.

### \_Pin Configurations (continued)

12 \_\_\_\_\_\_ **// // //**

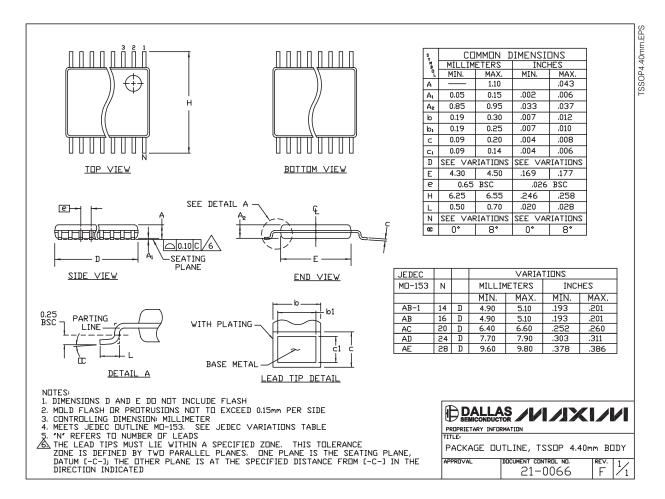

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

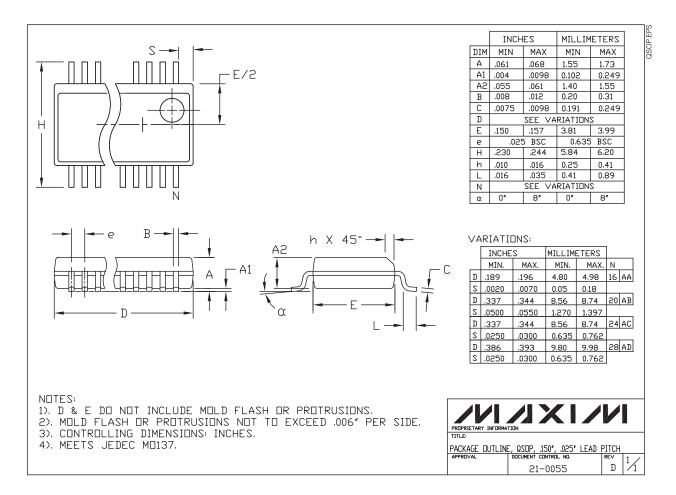

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.