# (LCD Driver with 40-Channel Outputs)

— Preliminary —

#### Description

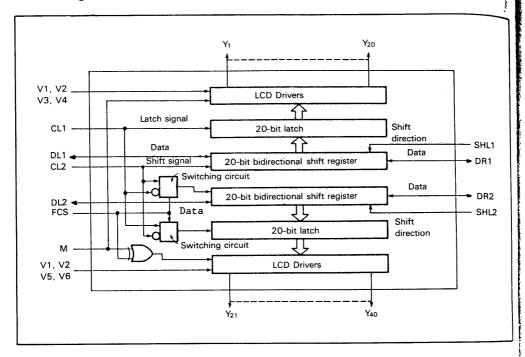

The HD44100R has two sets of 20-bit bidirectional shift registers, 20 data latch flipflops and 20 liquid crystal display driver circuits. It receives serial display data from a display control LSI, converts it into parallel data and supplies liquid crystal display waveforms to the liquid crystal.

The HD44100R is a highly general liquid crystal display driver which can drive a static drive liquid crystal and a dynamic drive liquid crystal, and can be applied as a common driver or segment driver.

#### **Features**

- Liquid crystal display driver with serial/ parallel conversion function

- Serial transfer facilitates board design

- Capable of interfacing to liquid crystal display controllers: HD43160AH, LCTC (HD61830/61830B), LCD-II (HD44780S, HD44780U), LCD-II A (HD66780), LCD-II/E (HD66702), LCD-III (HD44790), HD66710

- 40 internal liquid crystal display drivers

- Internal serial/parallel conversion circuits:

- –20-bit shift registerimes 2

- -20-bit data latch × 2 • Display bias: Static to 1/5

- Power supply:

- -Internal logic: V<sub>CC</sub>=2.7 to 5.5V

- -Liquid crystal display driver circuit:  $V_{CC}-V_{EE}=3$  to 13V

- Separation of internal logic from liquid crystal display driver circuit increases applicable controllers and liquid crystal types

- CMOS process

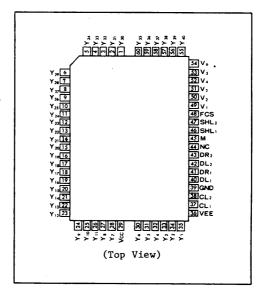

#### Pin Arrangement

## Ordering Information

| Type No.   | V <sub>CC</sub> (V) | V <sub>CC</sub> -V <sub>EE</sub> (V) | Package                     |  |

|------------|---------------------|--------------------------------------|-----------------------------|--|

| HD44100RFS | 2.7 to 5.5          | 3 to 13                              | 60-pin Plastic QFP (FP-60A) |  |

| HCD44100R  | 2.7 to 5.5          | 3 to 13                              | Chip                        |  |

## **Block Diagram**

£

## **Absolute Maximum Ratings**

| Item                  |             | Symbol                         | Value                                           | Unit |

|-----------------------|-------------|--------------------------------|-------------------------------------------------|------|

| Supply                | Logic       | Vcc*1                          | - 0.3 to + 7.0                                  | V    |

| voltage               | LCD drivers | V <sub>EE</sub> *2             | V <sub>CC</sub> - 15.0 to V <sub>CC</sub> + 0.3 | V    |

| Input voltage         |             | V <sub>T1</sub> * <sup>1</sup> | - 0.3 to V <sub>CC</sub> + 0.3                  | V    |

| Input voltage         |             | V <sub>T2</sub> *3             | $V_{CC}$ + 0.3 to $V_{EE}$ - 0.3                | V    |

| Operating temperature |             | T <sub>opr</sub>               | - 20 to + 75                                    | °C   |

| Storage temp          | erature     | T <sub>stg</sub>               | - 55 to + 125                                   | .c   |

Notes: \*1 All voltage values are referred to GND. \*2 Connect a protection resistor of 220  $\Omega$  ± 5 % to V<sub>EE</sub> power supply in series. \*3 Applies to V<sub>1</sub>to V<sub>6</sub>.

# **Electrical Characteristics**

$(\text{Vcc}=2.7 \text{ to } 5.5 \text{ V}, \text{ Vcc} - \text{V}_{\text{EE}}=3 \text{ to } 13 \text{ V}, \text{ GND}=0 \text{ V}, \text{ T}_a=-20 \text{ to } +75^{\circ}\text{C})$

| tem                   | Symbol          | Applicable Terminals                                       | Min                   | Тур | Max                 | Unit | Test Condition                                    |

|-----------------------|-----------------|------------------------------------------------------------|-----------------------|-----|---------------------|------|---------------------------------------------------|

| Input voltage         | ViH             | CL1, CL2, DL1, DL2,                                        | 0.7 V <sub>CC</sub>   | _   | Vcc                 | ٧    | V <sub>CC</sub> =4.5 to 5.5V                      |

|                       |                 | DR1, DR2, M, SHL1,                                         | 0.8 V <sub>CC</sub>   | _   | Vcc                 | ٧    | V <sub>CC</sub> =2.7 to 4.5V                      |

|                       | VIL             | SHL2, FCS                                                  | 0                     | _   | 0.3 V <sub>CC</sub> | ٧    | V <sub>CC</sub> =4.5 to 5.5V                      |

|                       |                 |                                                            | 0                     | _   | 0.2 V <sub>CC</sub> | ٧    | V <sub>CC</sub> =2.7 to 4.5V                      |

| Output voltage        | V <sub>OH</sub> | DL1, DL2, DR1, DR2                                         | V <sub>CC</sub> - 0.4 | 1 — | _                   | ٧    | $I_{OH} = -0.4 \text{ mA}$                        |

|                       | VoL             |                                                            | _                     | _   | 0.4                 | V    | $I_{OL} = + 0.4 \text{ mA}$                       |

| On resistance         | Ron             | *1                                                         | _                     | _   | 20                  | kΩ   | $\pm I_d = 0.05 \text{ mA}, V_{CC} - V_{EE} = 4V$ |

| Input leakage current | I <sub>IL</sub> | CL1, CL2, DL1, DL2,<br>DR1, DR2, M, SHL1,<br>SHL2, FCS, NC | - 5.0                 | _   | 5.0                 | μΑ   | $V_{in} = 0$ to $V_{CC}$                          |

| Vi leakage<br>current | I <sub>VL</sub> | *2                                                         | - 10.0                | _   | 10.0                | μА   | $V_{in} = V_{CC}$ to $V_{EE}$                     |

| Power supply          | Icc             | *3                                                         | <del>-</del>          | _   | 1.0                 | mA   | f <sub>CL2</sub> = 400 kHz                        |

| current               | lee             | •                                                          | _                     | _   | 10                  | μА   | f <sub>CL1</sub> = 1 kHz                          |

Notes: \*1 Applies to the resistance between  $V_i$  and  $Y_j$  when a current  $\pm I_d = 0.05$  mA flows through

<sup>\*1</sup> Applies to the resistance between v<sub>i</sub> and v<sub>j</sub> when a current ± I<sub>d</sub> = 0.05 mA nows through all of the Y pins.

\*2 Output Y1 to Y40 open.

\*3 Input/output current is excluded; when input is at the intermediate level with CMOS, excessive current flows through the input circuit to the power supply. To avoid this, input level must be fixed at high as low. level must be fixed at high or low.

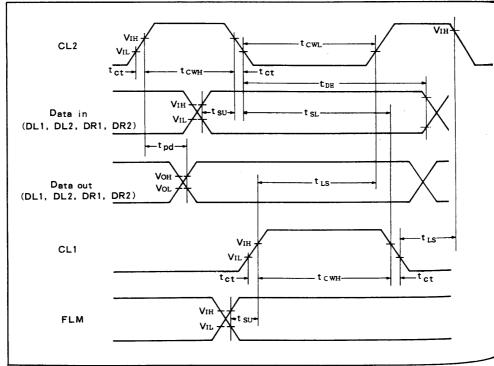

## **Timing Characteristics**

$(V_{CC} = 2.7 \text{ to } 5.5 \text{ V}, V_{CC} - V_{EE} = 3 \text{ to } 13 \text{ V}, \text{ GND} = 0 \text{ V}, T_a = -20 \text{ to } +75^{\circ}\text{C})$

| Item                              |            | Symbol          | Applicable Terminals       | Min | Тур | Max | Unit | Test Condition         |

|-----------------------------------|------------|-----------------|----------------------------|-----|-----|-----|------|------------------------|

| Data shift frequency              |            | f <sub>CL</sub> | CL2                        | -   | _   | 400 | kHz  |                        |

| Clock                             | high level | tcwn            | CL1, CL2                   | 800 |     | _   | ns   |                        |

| width                             | Low level  | tcwL            | CL2                        | 800 |     | _   | ns   |                        |

| Data set-up time                  |            | tsu             | DL1, DL2, DR1, DR2,<br>FLM | 300 | _   | _   | ns   |                        |

| Clock set-up time                 |            | t <sub>SL</sub> | CL1, CL2                   | 500 |     | -   | ns   | (CL2→CL1)              |

| Clock set-up time t <sub>LS</sub> |            | t <sub>LS</sub> | CL1, CL2                   | 500 |     | _   | ns   | (CL1→CL2)              |

| Data delay time t <sub>pd</sub>   |            | t <sub>pd</sub> | DL1, DL2, DR1, DR2         | _   | _   | 500 | ns   | C <sub>L</sub> = 15 pF |

| Clock rise/fall time tct          |            | t <sub>ct</sub> | CL1, CL2                   | _   | _   | 200 | ns   |                        |

| Data hold time t <sub>DH</sub>    |            | t <sub>DH</sub> | DL1, DL2, DR1, DR2,<br>FLM | 300 | _   | _   | ns   |                        |

できることになっていることになっている。

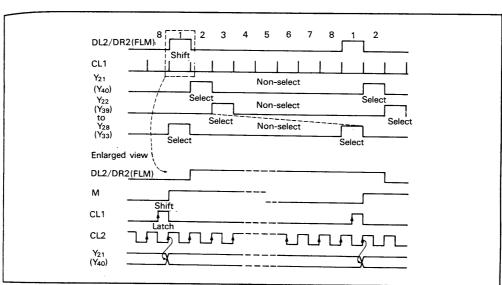

Figure 1 Timing Waveform

# Terminal Function

# Table 1 Functional Description of Terminals

| Signal<br>Name | Number of Lines | input/<br>Output | Connected to              | Function                                                                                                                                                                                     |  |  |  |  |

|----------------|-----------------|------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Vcc            | 1               |                  | power supply              | Power supply for logical circuit                                                                                                                                                             |  |  |  |  |

| GND            | 1               |                  | Power supply              | 0 V                                                                                                                                                                                          |  |  |  |  |

| VEE            | 1               |                  | Power supply              | Power supply for liquid crystal display drive                                                                                                                                                |  |  |  |  |

| Y1-Y20         | 20              | Output           | Liquid crystal            | Liquid crystal driver output (Channel 1)                                                                                                                                                     |  |  |  |  |

| Y21-Y40        | 20              | Output           | Liquid crystal            | Liquid crystal driver output (Channel 2)                                                                                                                                                     |  |  |  |  |

| V1, V2         | 2               | Input            | Power supply              | Power supply for liquid crystal display drive (Select level)                                                                                                                                 |  |  |  |  |

| V3. V4         | 2               | Input            | Power supply              | Power supply for liquid crystal display drive (Non-select level for channel 1)                                                                                                               |  |  |  |  |

| V5. V6         | 2               | Input            | Power supply              | Power supply for liquid crystal display drive (Non-select level for channel 2)                                                                                                               |  |  |  |  |

| SHL1           | 1               | Input            | V <sub>CC</sub> or GND    | Selection of the shift direction of channel 1 shift register                                                                                                                                 |  |  |  |  |

|                |                 |                  |                           | SHL1 DL1 DR1                                                                                                                                                                                 |  |  |  |  |

|                |                 |                  |                           | Vcc Out In                                                                                                                                                                                   |  |  |  |  |

|                |                 |                  |                           | GND In Out                                                                                                                                                                                   |  |  |  |  |

| SHL2           | 1               | Input            | V <sub>CC</sub> or GND    | Selection of the shift direction of channel 2 shift register                                                                                                                                 |  |  |  |  |

| •              |                 | ·                | 100 01 0110               | SHL2 DL2 DR2                                                                                                                                                                                 |  |  |  |  |

|                |                 |                  |                           | V <sub>CC</sub> Out In                                                                                                                                                                       |  |  |  |  |

|                |                 |                  |                           | GND In Out                                                                                                                                                                                   |  |  |  |  |

|                |                 |                  |                           |                                                                                                                                                                                              |  |  |  |  |

| DL1, DR1       | 2               | Input/<br>output | Controller<br>or HD44100R | Data input/output of channel 1 shift register                                                                                                                                                |  |  |  |  |

| DL2, DR2       | 2               | Input/<br>output | Controller<br>or HD44100R | Data input/output of channel 2 shift register                                                                                                                                                |  |  |  |  |

| M              | 1               | Input            | Controller                | Alternated signal for liquid crystal driver output                                                                                                                                           |  |  |  |  |

| CL1            | 1               | Input            | Controller                | ntroller Latch signal for channel 1 ( ) *1 Used for channel 2 when FCS is GND                                                                                                                |  |  |  |  |

| CL2            | 1               | Input            | Controller                | Controller Shift signal for channel 1 ( ) *1 Used for channel 2 when FCS is GND                                                                                                              |  |  |  |  |

| FCS            | 1               | Input            | V <sub>CC</sub> or GND    | Mode select signal of channel 2. FCS signal exchanges the latch signal and the shift signal of channel 2 and inverts M for channel 2. Thus, this signal exchanges the function of channel 2. |  |  |  |  |

|                |                 |                  |                           | Channel 2                                                                                                                                                                                    |  |  |  |  |

|                |                 |                  | FCS Level                 | Latch signal Shift signal M Polarity Function                                                                                                                                                |  |  |  |  |

|                |                 |                  | Vcc                       | CL2 CL1 M For common drive                                                                                                                                                                   |  |  |  |  |

|                |                 |                  | GND                       | CL1 CL2 M For segment drive                                                                                                                                                                  |  |  |  |  |

|                |                 |                  |                           | *1 *1 *2                                                                                                                                                                                     |  |  |  |  |

| NC             | 1               |                  | 7.7.                      | Don't connect any wires to this terminal.                                                                                                                                                    |  |  |  |  |

Notes: \*1 \_\_\_ and \_\_ indicate the latches at rise and fall times, respectively.

\*2 The output level relationship between channel 1 and channel 2 based on the FCS signal level is as follows:

|              |                                                     | Output Level                                 |                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|--------------|-----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Data         | M                                                   | Channel 1 (Y <sub>1</sub> -Y <sub>20</sub> ) | Channel 2 (Y <sub>21</sub> -Y <sub>40)</sub>                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1            | 1                                                   | V <sub>1</sub>                               | V <sub>2</sub>                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| (Select)     | 0                                                   | V <sub>2</sub>                               | V <sub>1</sub>                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 0            | 1                                                   | V <sub>3</sub>                               | V <sub>6</sub>                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| (Non-select) | 0                                                   | V <sub>4</sub>                               | V <sub>5</sub>                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 1            | 1                                                   | V <sub>1</sub>                               | V <sub>1</sub>                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| (Select)     | 0                                                   | V <sub>2</sub>                               | V <sub>2</sub>                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 0            | 1                                                   | V <sub>3</sub>                               | V <sub>5</sub>                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| (Non-select) | 0                                                   | V <sub>4</sub>                               | V <sub>6</sub>                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|              | 1<br>(Select)<br>O<br>(Non-select)<br>1<br>(Select) | 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0      | Data         M         Channel 1 (Y <sub>1</sub> -Y <sub>20</sub> )           1         1         V <sub>1</sub> (Select)         0         V <sub>2</sub> 0         1         V <sub>3</sub> (Non-select)         0         V <sub>4</sub> 1         1         V <sub>1</sub> (Select)         0         V <sub>2</sub> 0         1         V <sub>3</sub> |  |  |  |

<sup>1</sup> and 0 indicate high and low levels, respectively.

## **Applications**

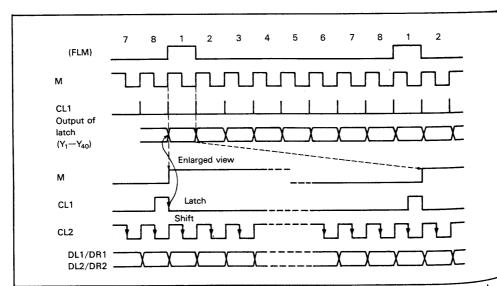

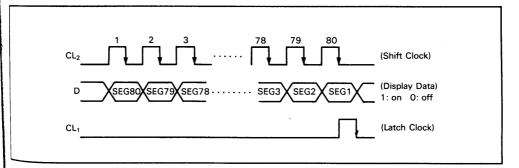

## Segment Driver

When the HD44100R is used as a segment driver, FCS is set to GND to transfer display data with the timing shown in figure 2. In this

case, both channel 1 and channel 2 shift data at the fall of CL2 and latch it at the fall of CL1  $V_3$  and  $V_5$ ,  $V_4$  and  $V_6$  of the liquid crystal display driver power supply are short-clicuited, respectively.

Figure 2 Segment Data Waveforms (A Type Waveforms, 1/8 Duty Cycle)

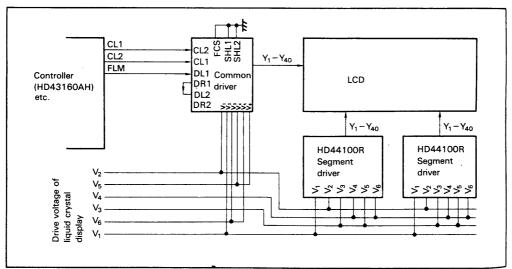

# Common Driver

In this case, channel 1 is used as a segment driver and channel 2 as common driver. When channel 2 of HD44100R is used as common driver, FCS is set to  $V_{\rm CC}$  to transfer

display data with the timing shown in figure 3.

In this case, channel 2 shifts data at the rise of CL1 and latches it at the rise of CL2. Channel 1 shifts and latches as shown in figure 2.

Figure 3 Common Data Waveforms (A Type Waveforms of Channel 2, 1/8 Duty Cycle)

# Both Channel 1 and Channel 2 Used as Common Drivers (FCS = GND)

When both of channel 1 and channel 2 of HD44100R are used common drivers, FCS is set to GND and the signals (CL1, CL2, FLM) from the controller are connected as shown in figure 4.

In this case, connection of the liquid crystal display driver power supply is different from that of segment driver, so refer to figure 4.

- V<sub>1</sub>, V<sub>2</sub>: Select level of segment and common

- V<sub>3</sub>, V<sub>4</sub>: Non-select level of segment

- V<sub>5</sub>, V<sub>6</sub>: Non-select level of common

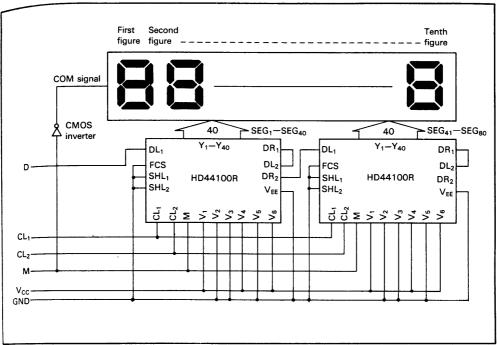

#### Static Drive

When the HD44100R is used in the static drive method (figure 5), data is transferred at

the fall of CL2 and latched at the fall of CL1. The frequency of CL1 becomes the frame frequency of the liquid crystal display driver. The signal applied terminal M must have twice the frequency of CL1 and be synchronized at the fall of CL1. The power supply for liquid crystal display driver is used by short-circuiting  $V_1,\ V_4$  and  $V_6,\$ and  $V_2,\ V_3,\$ and  $V_5$  respectively.

One of the liquid crystal display driver output terminals can be used for a common output. In this case, FCS is set to GND and data is transferred so that 0 can be always latched in the latch corresponding to the liquid crystal display driver output terminal used as the common output. If the latch signal corresponding to the segment output is 1, the segments of LCD light. They also light for common side = 1, and segment side 0.

Figure 4 Connection When Both Channels Are Common Drivers

Figure 5 Static Drive Connection

#### Timing Chart of Input Waveforms

#### Votes

- Input square waves of 50% duty cycle (about 30—500 Hz) to M. The frequency depends on the specifications of LCD panels.

- The drive waveforms corresponding to the new displayed data are output at the fall of CL1. Therefore, when the alternating signal M and CL1 do not fall synchronously, DC elements are produced on the LCD drive waveforms. These DC elements may shorten the life span of the LCD, if the displayed data frequently changes (e.g. display of hours, minutes, and seconds of a clock). To avoid

- this, have CL1 fall synchronously with the one edge of  $\mathbf{M}$ .

- In this example, the CMOS inverter is used as a COM signal driver in consideration of the large display area. (The load capacitance on COM is large because it is common to all the displayed segments.)

- Usually, one of the HD44100R outputs can be used as a COM signal. The displayed data corresponding to the terminal should be 0 in that case.

# COM LCD CL2 39 40 Y1 Y2-Y40 Data transformed to Y2 to Y40 CL1 CL1 CL2 Data transformed to Y2 to Y40 CL1

T. w. L. It la in It

F