**MAXIM****2.7Gbps Dual Mux/Buffer with Loopback****MAX3783****General Description**

The MAX3783 is a dual serial multiplexer (mux) and buffer with selectable line-side loopback for system interconnect and serial backplane applications up to 2.7Gbps. Each independent channel consists of a transmitter with fanout of two and a receiver with a 2:1 input mux. Selectable loopback paths support system testing.

Operating from a single 3.3V supply, this device has current-mode logic (CML) inputs and outputs, which can be AC-coupled for PECL compatibility, if desired. The IC is packaged in a compact 48-pin TQFP-EP package with exposed pad. Typical power consumption is 1.12W.

**Applications**

2.7Gbps Serial Communications

System Interconnect

Serial Backplane

Fail-Over and Protection Switching

**Features**

- ◆ Provides Redundant Serial I/O

- ◆ 11ps Deterministic Jitter

- ◆ Selectable Loopback

- ◆ On-Chip 50Ω Termination Resistors

- ◆ 3.3V Power Supply

- ◆ Two-Port Integration

**Ordering Information**

| PART       | TEMP. RANGE  | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX3783UCM | 0°C to +85°C | 48 TQFP-EP* |

\* Exposed pad

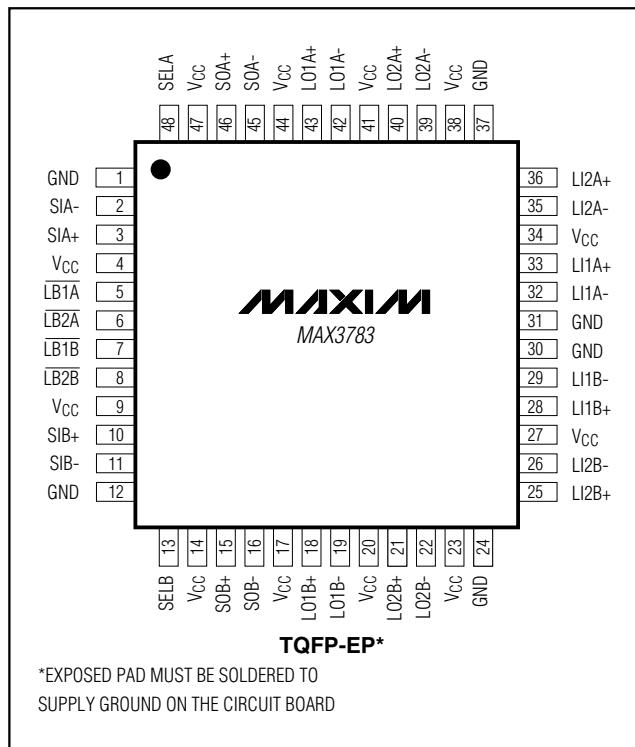

**Pin Configuration****MAXIM**

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at [www.maxim-ic.com](http://www.maxim-ic.com).

## 2.7Gbps Dual Mux/Buffer with Loopback

### ABSOLUTE MAXIMUM RATINGS

Supply Voltage,  $V_{CC}$  .....-0.5V to 4.0V

Continuous Current at Serial Outputs..... $\pm 36\text{mA}$

Voltage at  $SEL_{-}$ ,  $\overline{LB}_{-}$  Pins .....-0.5V to ( $V_{CC}$  + 0.5V)

Common-Mode Input Voltage ( $SI_{-}$ ,  $LI_{-}$ ) .....-0.5V to ( $V_{CC}$  + 0.5V)

Differential Input Voltage ( $SI_{-}$ ,  $LI_{-}$ ) (Note 1) ..... $\pm 2.8\text{V}$

Continuous Power Dissipation ( $T_A = +85^\circ\text{C}$ )

48-Pin TQFP-EP (derate 27mW/ $^\circ\text{C}$  above  $+85^\circ\text{C}$ ) .....1.76W

Storage Ambient Temperature .....-55 $^\circ\text{C}$  to +150 $^\circ\text{C}$

Lead Temperature (soldering, 10s) .....+300 $^\circ\text{C}$

**Note 1:** The sum of the common-mode voltage and differential voltage on any input pin must be within -0.5V to ( $V_{CC}$  + 0.5V).

*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.*

### ELECTRICAL CHARACTERISTICS

( $V_{CC} = 3.0\text{V}$  to  $3.6\text{V}$ , serial data rate = 2.75Gbps,  $T_A = 0^\circ\text{C}$  to  $+85^\circ\text{C}$ . Typical values at  $V_{CC} = 3.3\text{V}$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

| PARAMETER                          | SYMBOL        | CONDITIONS                                                                  | MIN  | TYP   | MAX  | UNITS         |

|------------------------------------|---------------|-----------------------------------------------------------------------------|------|-------|------|---------------|

| Maximum Serial Data Rate           |               |                                                                             | 2.75 | 3.125 |      | Gbps          |

| Power Dissipation                  |               | AC-coupled inputs, outputs                                                  |      | 1.12  | 1.68 | W             |

| Supply Current                     | $I_{CC}$      |                                                                             | 340  | 466   |      | mA            |

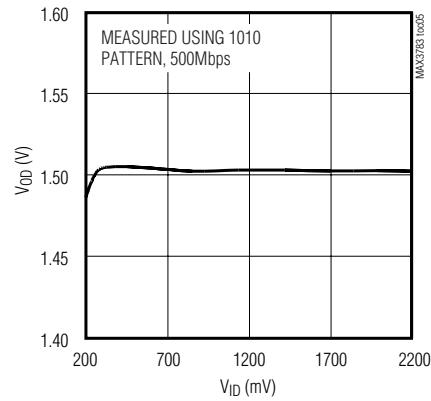

| CML Differential Output Voltage    | $V_{OD}$      | $R_L = 50\Omega$ to $V_{CC}$ , or $100\Omega$ differential (Note 2)         | 1200 | 1500  | 2200 | mVp-p         |

| CML Differential Input Voltage     | $V_{ID}$      |                                                                             | 200  | 1600  | 2200 | mVp-p         |

| CML Output Impedance               | $R_{OUT}$     | Single ended                                                                | 42.5 | 50    | 57.5 | $\Omega$      |

| CML Input Impedance                | $R_{IN}$      | Differential                                                                | 85   | 100   | 116  | $\Omega$      |

| Random Jitter                      |               | (Note 3)                                                                    |      | 1     | 2    | psRMS         |

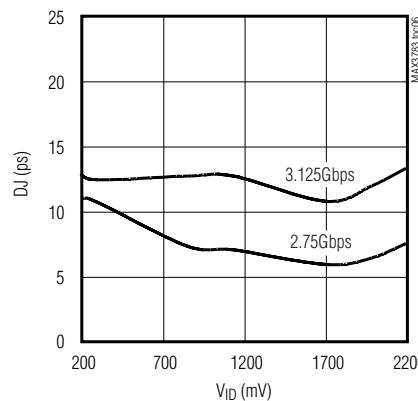

| Deterministic Jitter               |               | (Notes 3, 4, 5)                                                             |      | 11    | 25   | psp-p         |

| CML Output Edge Speed (20% to 80%) | $t_R$ , $t_F$ | 2.5Gbps input (Note 3)                                                      | 70   | 135   |      | ps            |

|                                    |               | 1.25Gbps input (Note 3)                                                     | 80   | 200   |      |               |

| Propagation Delay                  |               | $LI_{-}$ to $SO_{-}$ , $SI_{-}$ to $LO_{-}$ , $LI_{-}$ to $LO_{-}$ (Note 3) | 340  | 500   |      | ps            |

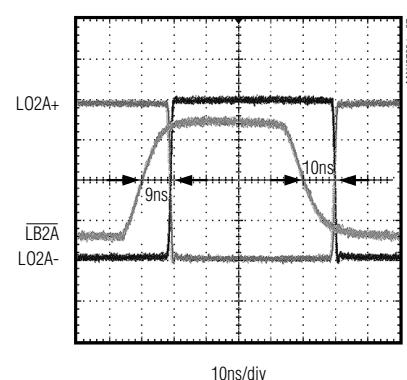

| Multiplexer Switch Time            |               | $SEL_{-}$ or $\overline{LB}_{-}$ to valid output                            |      | 9     |      | ns            |

| TTL Input Current High             |               | $V_{IH} = +2.0\text{V}$ to ( $V_{CC}$ + 0.3V)                               |      |       | 180  | $\mu\text{A}$ |

| TTL Input Current Low              |               | $V_{IL} = -0.3\text{V}$ to +0.8V                                            |      |       | 440  | $\mu\text{A}$ |

**Note 2:** Typical value measured using a repeating 1010 pattern at 500Mbps.

**Note 3:** AC specifications are guaranteed by design and characterization.

**Note 4:** Deterministic jitter is measured with a repeating K28.5 pattern.

**Note 5:** With the peak-to-peak input swing on the selected (transmitted) CML input equal to or greater than that on the nonselected inputs.

# 2.7Gbps Dual Mux/Buffer with Loopback

MAX3783

## Typical Operating Characteristics

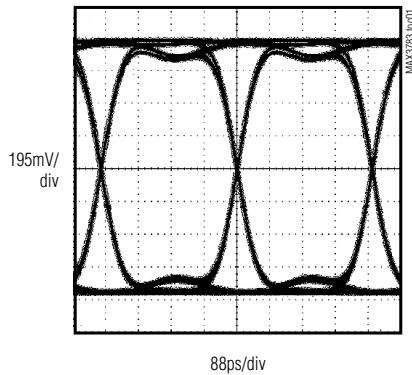

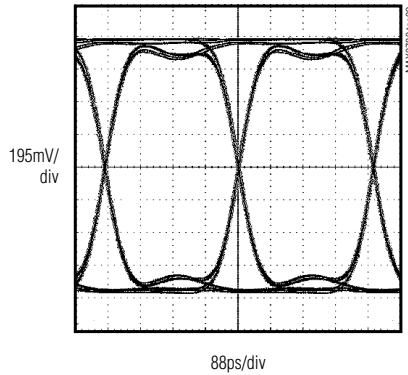

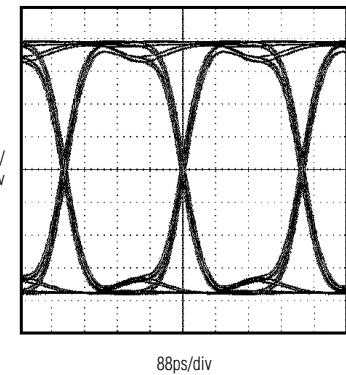

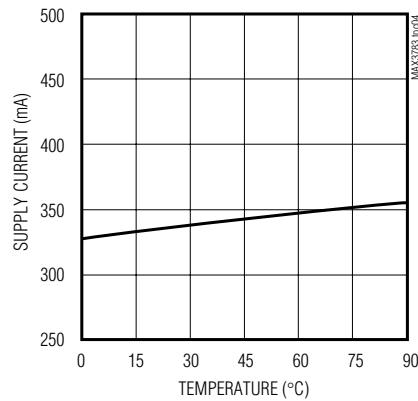

( $V_{CC} = 3.3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

**ELECTRICAL EYE DIAGRAM**

2.75 Gbps, 2<sup>23</sup> - 1 PRBS PATTERN

**ELECTRICAL EYE DIAGRAM**

2.75 Gbps, K28.5 PATTERN

**ELECTRICAL EYE DIAGRAM**

3.125 Gbps, K28.5 PATTERN

**SUPPLY CURRENT vs. TEMPERATURE**

**CML DIFFERENTIAL OUTPUT VOLTAGE**

vs. CML DIFFERENTIAL INPUT VOLTAGE

**DETERMINISTIC JITTER vs. CML**

DIFFERENTIAL INPUT VOLTAGE

**MUXPLEXER SWITCH TIME**

## 2.7Gbps Dual Mux/Buffer with Loopback

### Pin Description

| PIN                                          | NAME        | FUNCTION                                                                                                              |

|----------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|

| 1, 12, 24, 30, 31, 37                        | GND         | Supply Ground                                                                                                         |

| 2                                            | SIA-        | Serial Input A Negative, CML                                                                                          |

| 3                                            | SIA+        | Serial Input A Positive, CML                                                                                          |

| 4, 9, 14, 17, 20, 23, 27, 34, 38, 41, 44, 47 | VCC         | +3.3V Supply                                                                                                          |

| 5                                            | LB1A        | Line Out 1A Loopback Mode Select. TTL low selects loopback.                                                           |

| 6                                            | LB2A        | Line Out 2A Loopback Mode Select. TTL low selects loopback.                                                           |

| 7                                            | LB1B        | Line Out 1B Loopback Mode Select. TTL low selects loopback.                                                           |

| 8                                            | LB2B        | Line Out 2B Loopback Mode Select. TTL low selects loopback.                                                           |

| 10                                           | SIB+        | Serial Input B Positive, CML                                                                                          |

| 11                                           | SIB-        | Serial Input B Negative, CML                                                                                          |

| 13                                           | SELB        | Serial Output B Input Select, TTL                                                                                     |

| 15                                           | SOB+        | Serial Output B Positive, CML                                                                                         |

| 16                                           | SOB-        | Serial Output B Negative, CML                                                                                         |

| 18                                           | LO1B+       | Line Out 1B Positive, CML                                                                                             |

| 19                                           | LO1B-       | Line Out 1B Negative, CML                                                                                             |

| 21                                           | LO2B+       | Line Out 2B Positive, CML                                                                                             |

| 22                                           | LO2B-       | Line Out 2B Negative, CML                                                                                             |

| 25                                           | LI2B+       | Line In 2B Positive, CML                                                                                              |

| 26                                           | LI2B-       | Line In 2B Negative, CML                                                                                              |

| 28                                           | LI1B+       | Line In 1B Positive, CML                                                                                              |

| 29                                           | LI1B-       | Line In 1B Negative, CML                                                                                              |

| 32                                           | LI1A-       | Line In 1A Negative, CML                                                                                              |

| 33                                           | LI1A+       | Line In 1A Positive, CML                                                                                              |

| 35                                           | LI2A-       | Line In 2A Negative, CML                                                                                              |

| 36                                           | LI2A+       | Line In 2A Positive, CML                                                                                              |

| 39                                           | LO2A-       | Line Out 2A Negative, CML                                                                                             |

| 40                                           | LO2A+       | Line Out 2A Positive, CML                                                                                             |

| 42                                           | LO1A-       | Line Out 1A Negative, CML                                                                                             |

| 43                                           | LO1A+       | Line Out 1A Positive, CML                                                                                             |

| 45                                           | SOA-        | Serial Output A Negative, CML                                                                                         |

| 46                                           | SOA+        | Serial Output A Positive, CML                                                                                         |

| 48                                           | SELA        | Serial Out A Input Select, TTL                                                                                        |

| EP                                           | Exposed Pad | Ground. Must be soldered to the circuit board for proper thermal and electrical performance (see <i>EP Package</i> ). |

# 2.7Gbps Dual Mux/Buffer with Loopback

MAX3783

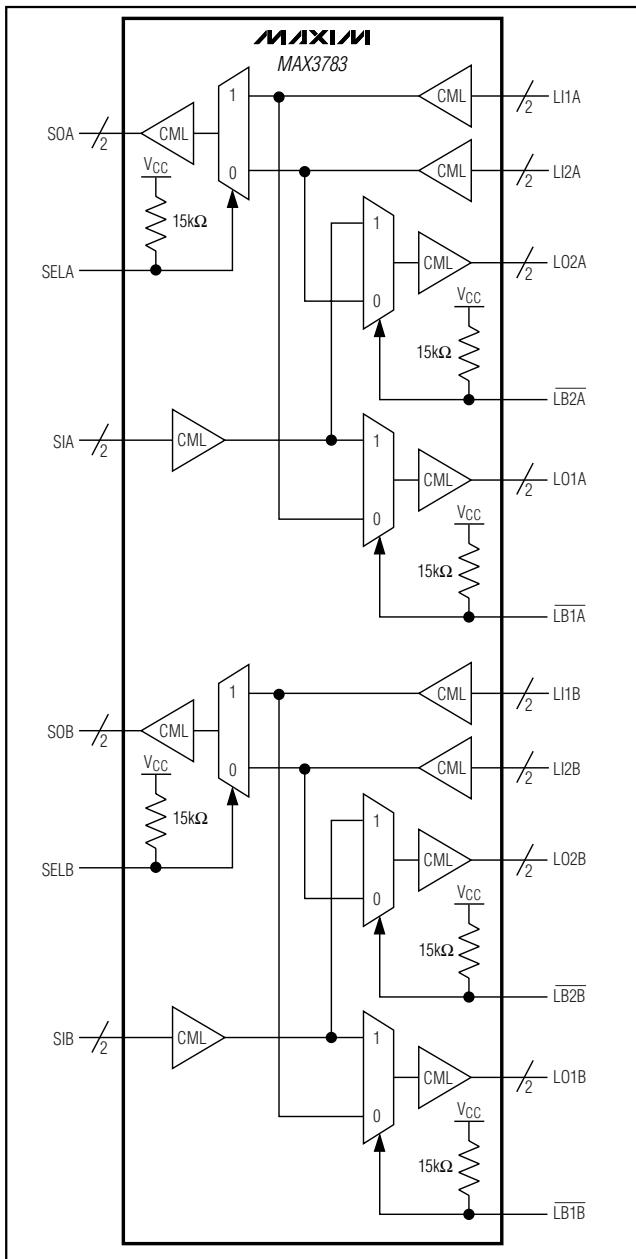

## Functional Diagram

## Detailed Description

The MAX3783 is a 2.7Gbps dual serial mux/buffer with selectable line-side loopback for system test. Each half of the MAX3783 provides a transmitter with a fanout of two and a receiver with a 2:1 mux, as shown in the functional diagram.

**Input Stages**

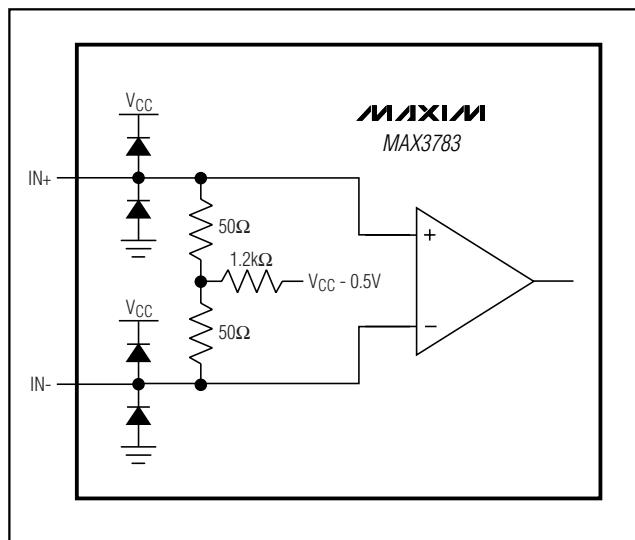

The input amplifiers accept CML or AC-coupled PECL signals and each input has an on-chip  $100\Omega$  differential impedance for optimal termination, as shown in Figure 1.

Figure 1. Input Structure

## Control Lines

TTL-compatible control lines are provided to select the MAX3783's operating mode (Table 1). SELA and SELB set the mux for channels A and B, respectively, to select LI1\_ or LI2\_ to connect to the SO\_ output. LB1A, LB1B, LB2A, and LB2B enable loopback mode for each of the four LO\_ outputs. All control lines are internally pulled high through  $15k\Omega$  resistors.

## Table 1. Operating Modes

| SEL_ | SO_  |

|------|------|

| 0    | LI2_ |

| 1    | LI1_ |

| LB_ | LO_ |

|-----|-----|

| 0   | LI_ |

| 1   | SI_ |

## Output Buffers

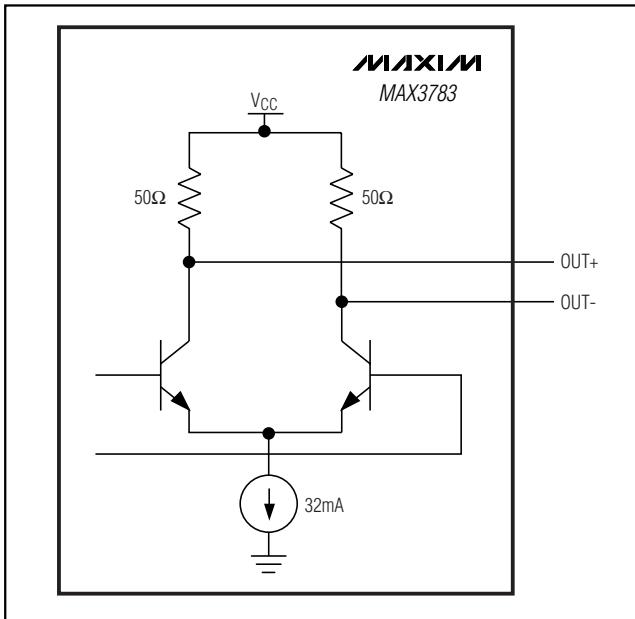

The outputs are high-speed CML interfaces with  $50\Omega$  back termination, as shown in Figure 2.

## Exposed-Pad (EP) Package

The exposed pad on the 48-pin TQFP-EP provides a very low thermal-resistance path for heat removal from the IC. The pad is also electrical ground on the MAX3783 and must be soldered to the circuit board for proper thermal and electrical performance.

## 2.7Gbps Dual Mux/Buffer with Loopback

Figure 2. CML Output Structure

### Chip Information

TRANSISTOR COUNT: 2816

PROCESS: Bipolar

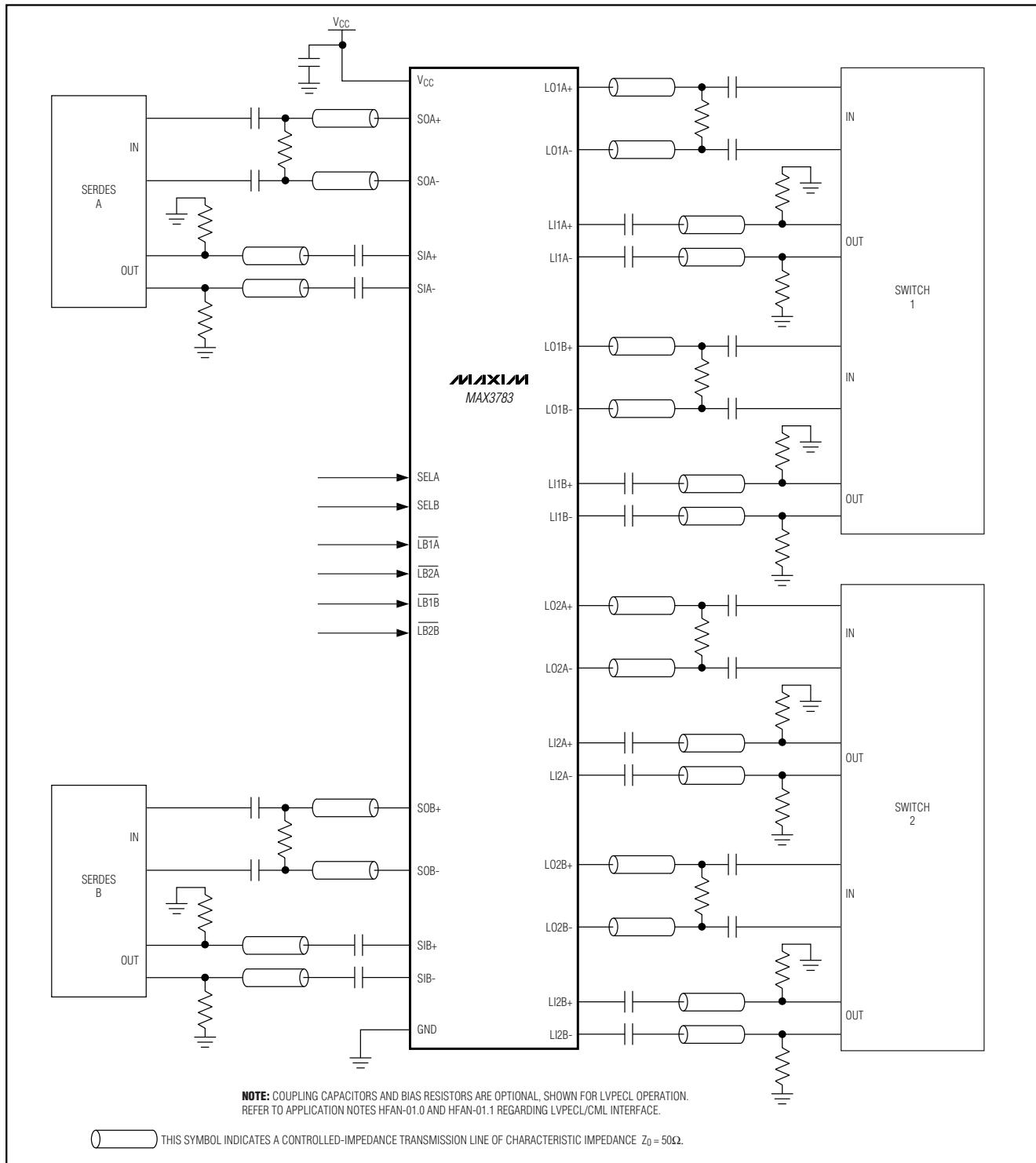

## 2.7Gbps Dual Mux/Buffer with Loopback

MAX3783

### Typical Application Circuit

## 2.7Gbps Dual Mux/Buffer with Loopback

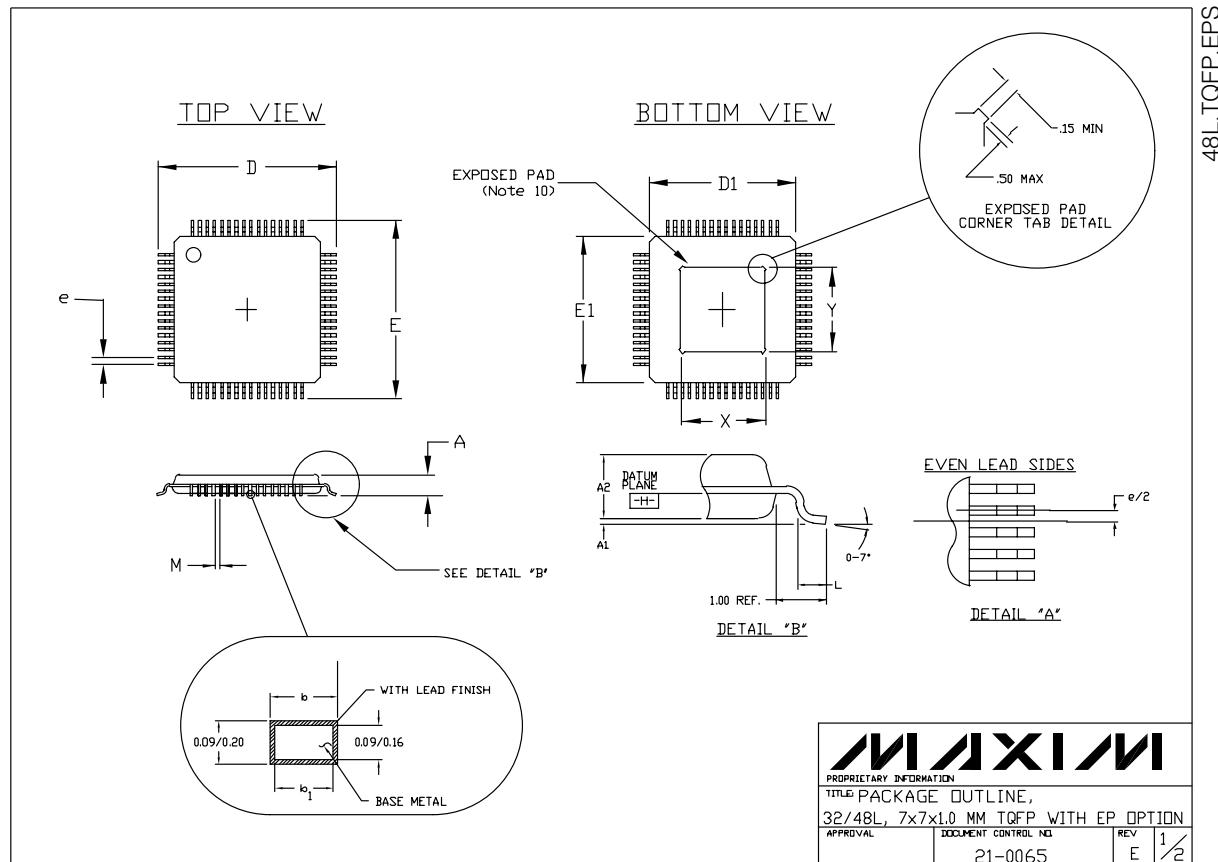

### Package Information

| MAXIM                   |                     |     |     |

|-------------------------|---------------------|-----|-----|

| PROPRIETARY INFORMATION |                     |     |     |

| APPROVAL                | DOCUMENT CONTROL NO | REV | 1/2 |

| 21-0065                 | E                   |     |     |

# 2.7Gbps Dual Mux/Buffer with Loopback

## Package Information (continued)

MAX3783

### NOTES:

1. ALL DIMENSIONS AND TOLERANCING CONFORM TO ANSI Y14.5-1982.

2. DATUM PLANE [—H—] IS LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

3. DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.254 MM ON D1 AND E1 DIMENSIONS.

4. THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE BY 0.15 MILLIMETERS.

5. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE b DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. CONTROLLING DIMENSION: MILLIMETER.

7. THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-136, VARIATIONS AC AND AE.

8. LEADS SHALL BE COPLANAR WITHIN .004 INCH.

9. EXPOSED DIE PAD SHALL BE COPLANAR WITH BOTTOM OF PACKAGE WITHIN 2 MILS (.05 MM).

10. DIMENSIONS X & Y APPLY TO EXPOSED PAD (EP) VERSIONS ONLY. SEE INDIVIDUAL PRODUCT DATASHEET TO DETERMINE IF A PRODUCT USES EXPOSED PAD PACKAGE.

| SYMBOL         | JEDEC VARIATION<br>ALL DIMENSIONS IN MILLIMETERS |      |      |      |      |      |

|----------------|--------------------------------------------------|------|------|------|------|------|

|                | AC                                               |      |      | AE   |      |      |

|                | MIN.                                             | NOM. | MAX. | MIN. | NOM. | MAX. |

| A              | —x—                                              | —x—  | 1.20 | —x—  | —x—  | 1.20 |

| A <sub>1</sub> | 0.05                                             | 0.10 | 0.15 | 0.05 | 0.10 | 0.15 |

| A <sub>2</sub> | 0.95                                             | 1.00 | 1.05 | 0.95 | 1.00 | 1.05 |

| D              | 9.00                                             | BSC. |      | 9.00 | BSC. |      |

| D <sub>1</sub> | 7.00                                             | BSC. |      | 7.00 | BSC. |      |

| E              | 9.00                                             | BSC. |      | 9.00 | BSC. |      |

| E <sub>1</sub> | 7.00                                             | BSC. |      | 7.00 | BSC. |      |

| L              | 0.45                                             | 0.60 | 0.75 | 0.45 | 0.60 | 0.75 |

| M              | 0.15                                             | —x—  | —x—  | 0.14 | —x—  | —x—  |

| N              | 32                                               |      |      | 48   |      |      |

| e              | 0.80                                             | BSC. |      | 0.50 | BSC. |      |

| b              | 0.30                                             | 0.37 | 0.45 | 0.17 | 0.22 | 0.27 |

| b <sub>1</sub> | 0.30                                             | 0.35 | 0.40 | 0.17 | 0.20 | 0.23 |

| *X             | 3.20                                             | 3.50 | 3.80 | 3.70 | 4.00 | 4.30 |

| *Y             | 3.20                                             | 3.50 | 3.80 | 3.70 | 4.00 | 4.30 |

\* EXPOSED PAD

(Note 10)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

9