#

# Am79C874

# **NetPHY™-1LP Low Power 10/100-TX/FX Ethernet Transceiver**

#### DISTINCTIVE CHARACTERISTICS

- 10/100BASE-TX Ethernet PHY device with 100BASE-FX fiber optic support

- Typical power consumption of 0.3 W

- Sends/receives data reliably over cable lengths greater than 130 meters

- MII mode supports 100BASE-X and 10BASE-T

- 7-Wire (General Purpose Serial Interface (GPSI)) mode supports 10BASE-T

- Three PowerWise™ management modes (from 300 mW typical)

- Power down: only management respondsTypical power = 3 mW

- Unplugged: no cable, no receive clock

Typical power = 100 mW

- Idle wire: no wire signal, no receiver power

Typical power = 285 mW; MAC saves over

100 mW

- Supports 1:1 or 1.25:1 transmit transformer

- Using a 1.25:1 ratio saves 20% transmit power consumption

- No external filters or chokes required

- Waveshaping no external filter required

- Full and half-duplex operation with full-featured Auto-Negotiation function

- LED indicators: Link, TX activity, RX activity, Collision, 10 Mbps, 100 Mbps, Full or Half Duplex

- MDIO/MDC operates up to 25 MHz

- Automatic Polarity Detection

- Built-in loopback and test modes

- Single 3.3-V power supply with 5-V I/O tolerance

- 12 mm x 12 mm 80-pin TQFP package

- Support for industrial temperature (-40°C to +85°C)

#### GENERAL DESCRIPTION

The Am79C874 NetPHY-1LP device provides the physical (PHY) layer and transceiver functions for one 10/100 Mbps Ethernet port. It delivers the dual benefits of CMOS low power consumption and small package size. Operating at 3.3 V, it consumes only 0.3 W. Three power management modes provide options for even lower power consumption levels. The small 12x12 mm 80-pin PQL package conserves valuable board space on adapter cards, switch uplinks, and embedded Ethernet applications.

The NetPHY-1LP 10/100 Mbps Ethernet PHY device is IEEE 802.3 compliant. It can receive and transmit data reliably at over 130 meters. It includes on-chip input filtering and output waveshaping for unshielded twisted pair operation without requiring external filters or chokes. The NetPHY-1LP device can use 1:1 isolation transformers or 1.25:1 isolation transformers. 1.25:1 isolation transformers provide 20% lower transmit power consumption. A PECL interface is available for 100BASE-FX applications.

Interface to the Media Access Controller (MAC) layer is established via the standard Media Independent Interface (MII), a 5-bit symbol interface, or a 7-wire (GPSI)

interface. Auto-Negotiation determines the network speed and full or half-duplex operation. Automatic polarity correction is performed during Auto-Negotiation and during 10BASE-T signal reception.

Multiple LED pins are provided for front panel status feedback. One option is to use two bi-color LEDs to show when the device is in 100BASE-TX or 10BASE-T mode (by illuminating), Half or Full Duplex (by the color), and when data is being received (by blinking). Individual LEDs can indicate link detection, collision detection, and data being transmitted.

The NetPHY-1LP device needs only one external 25-MHz oscillator or crystal because it uses a dual-speed clock synthesizer to generate all other required clock domains. The receiver has an adaptive equalizer/DC restoration circuit for accurate clock/data recovery from the 100BASE-TX signal.

The NetPHY-1LP device is available in the commercial (0°C to +70°C) or industrial (-40°C to +85°C) temperature ranges. The industrial temperature range is well suited to environments, such as enclosures with restricted air flow or outdoor equipment.

Publication# 22235 Rev: K Issue Date: May 2005

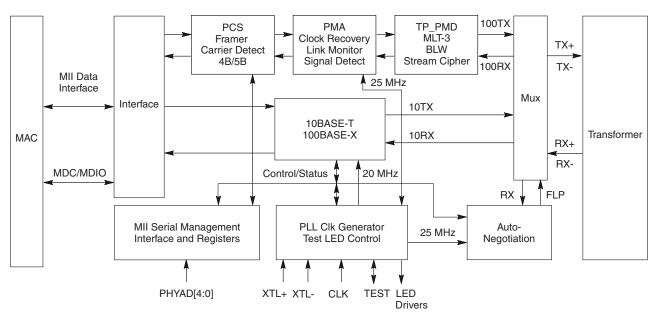

# **BLOCK DIAGRAM**

22236G-1

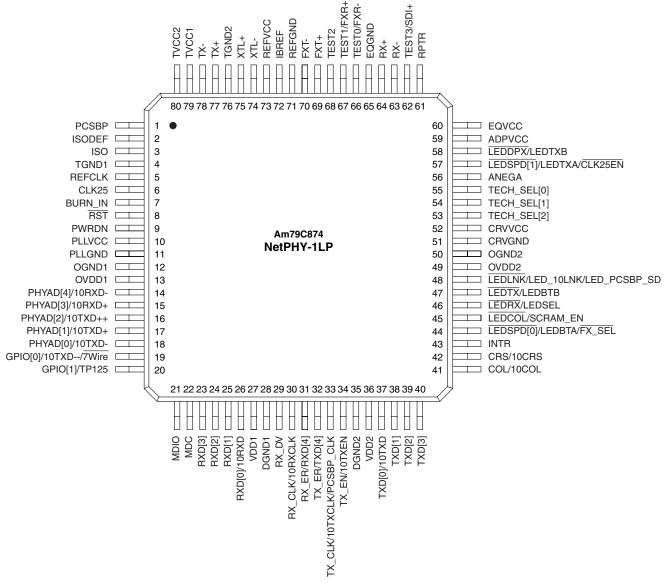

# **CONNECTION DIAGRAM**

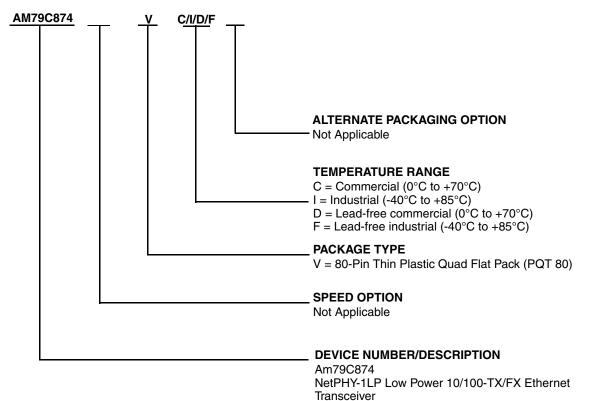

# **ORDERING INFORMATION**

# **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |    |  |  |  |

|--------------------|----|--|--|--|

| AM79C874           | VC |  |  |  |

| AM79C874           | VI |  |  |  |

| AM79C874           | VD |  |  |  |

| AM79C874           | VF |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# **RELATED AMD PRODUCTS**

# **Table 1. Related AMD Products**

| Part No.                                                                                                            | Description                                                      |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|--|

| Integrated Contro                                                                                                   | Integrated Controllers                                           |  |  |  |  |  |

| Am79C973B/<br>Am79C975B PCnet- <i>FAST™ III</i> Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |                                                                  |  |  |  |  |  |

| Am79C976                                                                                                            | PCnet-PRO™ 10/100 Mbps PCI Ethernet PCI Controller               |  |  |  |  |  |

| Am79C978A                                                                                                           | PCnet-Home™ Single-Chip 1/10 Mbps PCI Home Networking Controller |  |  |  |  |  |

| Physical Layer D                                                                                                    | evices (Single-Port)                                             |  |  |  |  |  |

| Am79C901A HomePHY™ Single-Chip 1/10 Mbps Home Networking PHY                                                        |                                                                  |  |  |  |  |  |

| Physical Layer Devices (Multi-Port)                                                                                 |                                                                  |  |  |  |  |  |

| Am79C875 NetPHY™-4LP Low Power Quad10/100-TX/FX Ethernet Transceiver                                                |                                                                  |  |  |  |  |  |

# **TABLE OF CONTENTS**

| DISTINCTIVE CHARACTERISTICS                  |    |

|----------------------------------------------|----|

| GENERAL DESCRIPTION                          |    |

| BLOCK DIAGRAM                                |    |

| CONNECTION DIAGRAM                           | 3  |

| ORDERING INFORMATION                         |    |

| Standard Products                            | 4  |

| RELATED AMD PRODUCTS                         |    |

| TABLE OF CONTENTS                            |    |

| LIST OF FIGURES                              |    |

| LIST OF TABLES                               |    |

| PIN DESIGNATIONS.                            |    |

| PIN DESCRIPTIONS                             |    |

| Media Connections                            |    |

| MII/7-Wire (GPSI) Signals                    |    |

| Miscellaneous Functions                      |    |

| LED Port Pins                                |    |

| Bias                                         |    |

| Power and Ground.                            |    |

| FUNCTIONAL DESCRIPTION                       |    |

| Modes of Operation                           |    |

| MII Mode                                     |    |

| 7-Wire (GPSI) Mode                           |    |

| 5B Symbol Mode                               |    |

| 100BASE-X Block                              |    |

| Transmit Process                             |    |

| Receive Process                              |    |

| 4B/5B Encoder/Decoder                        |    |

| Scrambler/Descrambler                        |    |

| Link Monitor                                 |    |

| MLT-3                                        |    |

| Adaptive Equalizer                           |    |

| Baseline Wander Compensation                 |    |

| Clock/Data Recovery                          |    |

| PLL Clock Synthesizer                        |    |

|                                              |    |

| Clock and Crystal Inputs                     |    |

| 10BASE-T Block                               |    |

| Twisted Pair Transmit Process                |    |

| Twisted Pair Receive Process                 |    |

| Twisted Pair Interface Status                |    |

| Collision Detect Function                    |    |

| Jabber Function                              |    |

| Reverse Polarity Detection and Correction    |    |

| Auto-Negotiation and Miscellaneous Functions |    |

| Auto-Negotiation                             |    |

| Parallel Detection                           |    |

| Far-End Fault                                |    |

| SQE (Heartbeat)                              |    |

| Loopback Operation                           |    |

| Reset                                        |    |

| LED Port Configuration                       |    |

| Power Savings Mechanisms                     |    |

| Selectable Transformer                       |    |

| Power Down                                   |    |

| Unplugged                                    |    |

| Idle Wire                                    |    |

| PHY CONTROL AND MANAGEMENT BLOCK (PCM BLOCK) | 30 |

| Register Administration for 100BASE-X PHY Device   |    |

|----------------------------------------------------|----|

| Description of the Methodology                     |    |

| Bad Management Frame Handling                      |    |

| REGISTER DESCRIPTIONS                              |    |

| Serial Management Registers                        |    |

| Reserved Registers (Registers 8-15, 20, 22, 25-31) |    |

| ABSOLUTE MAXIMUM RATINGS                           | 42 |

| Commercial (C)                                     | 42 |

| Industrial (I)                                     |    |

| DC CHARACTERISTICS                                 | 42 |

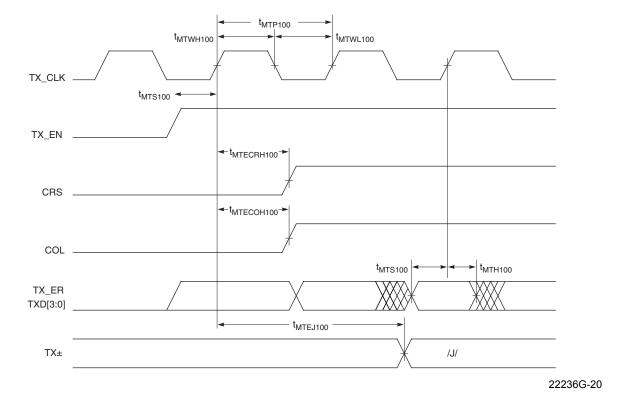

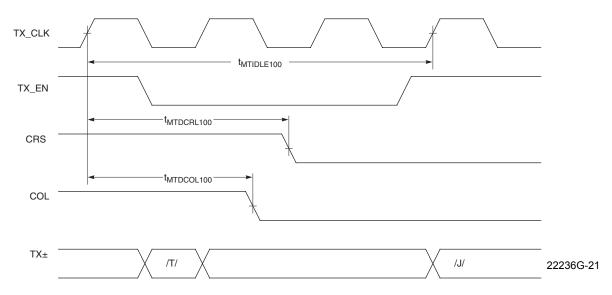

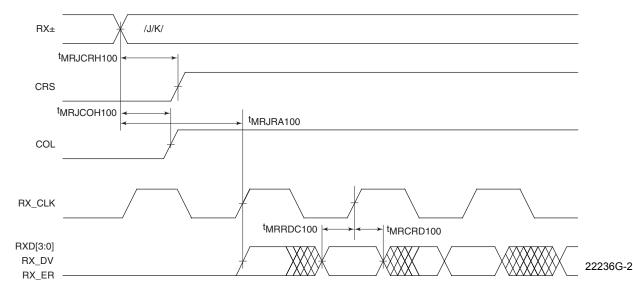

| SWITCHING WAVEFORMS                                | 44 |

| Key to Switching Waveforms                         | 44 |

| SWITCHING CHARACTERISTICS                          | 47 |

| System Clock Signal                                | 47 |

| MLT-3 Signals                                      | 47 |

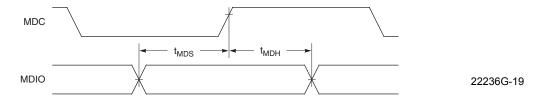

| MII Management Signals                             | 48 |

| MII Signals                                        | 49 |

| GPSI Signals                                       | 55 |

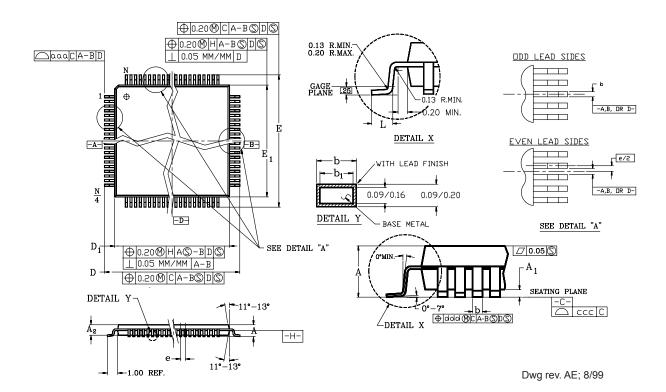

| PHYSICAL DIMENSIONS                                | 58 |

| PQT80 (measured in millimeters)                    |    |

| ERRATA FOR REVISION [B.7] SILICON                  | 59 |

| Revision [B.7] Errata Summary                      | 59 |

| Errata for NetPHY-1LP [B.7]                        |    |

| B7 Errata 1- Advanced LED Mode Activity            | 59 |

| B7 Errata 2 - Auto-Negotiation ACK Bit             |    |

| B7 Errata 3 - Missing or Distorted /T/R/           | 59 |

| DEVISION STIMMADY                                  | 60 |

# **LIST OF FIGURES**

| Figure 1.  | FXT± and FXR± Termination for 100BASE-FX                | .18 |

|------------|---------------------------------------------------------|-----|

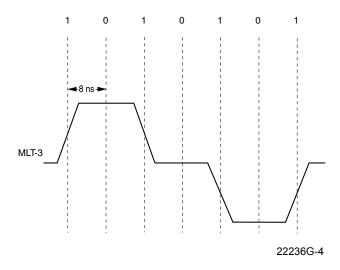

| Figure 2.  | MLT-3 Waveform                                          |     |

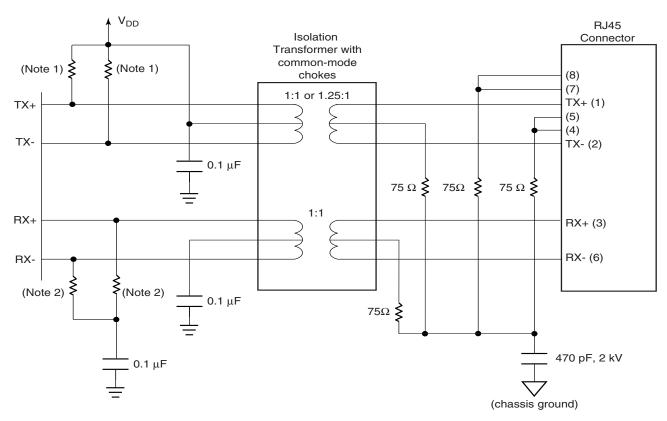

| Figure 3.  | TX± and RX± Termination for 100BASE-TX and 10BASE-T     | .22 |

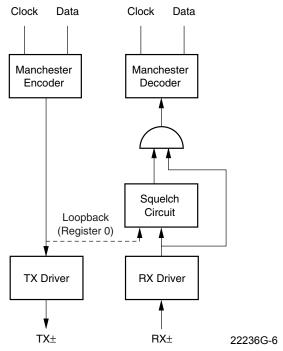

| Figure 4.  | 10BASE-T Transmit /Receive Data Paths                   | .23 |

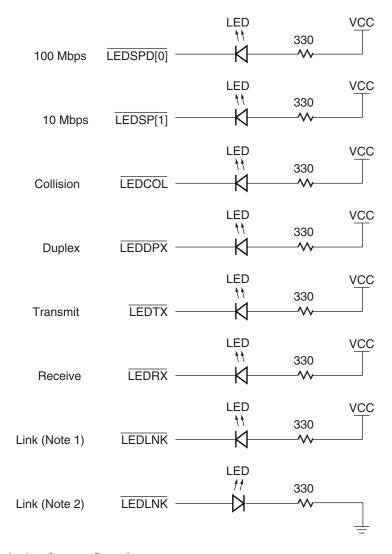

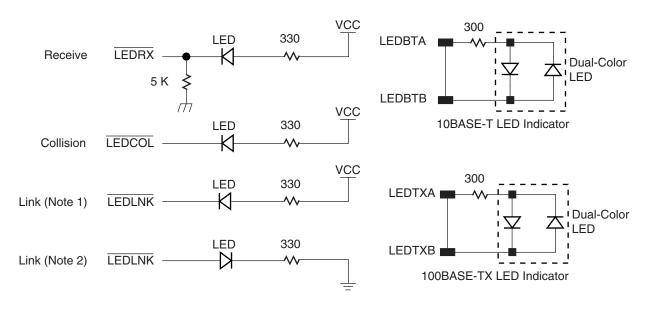

| Figure 5.  | Standard LED Configuration                              |     |

| Figure 6.  | Advanced LED Configuration                              | .28 |

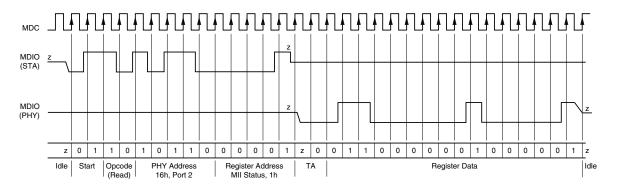

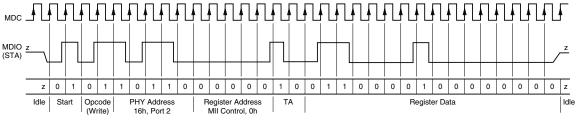

| Figure 7.  | PHY Management Read and Write Operations                | .30 |

| Figure 8.  | MLT-3 Receive Input                                     |     |

| Figure 9.  | MLT-3 and 10BASE-T Test Load with 1:1 Transformer Ratio | .45 |

| Figure 10. |                                                         |     |

| Figure 11. | Near-End 100BASE-TX Waveform                            | .45 |

| Figure 12. | 10BASE-T Waveform With 1:1 Transformer Ratio            | .46 |

| Figure 13. |                                                         |     |

| Figure 14. |                                                         |     |

| Figure 15. |                                                         |     |

| Figure 16. |                                                         |     |

| Figure 17. | · · · · · · · · · · · · · · · · · · ·                   |     |

| Figure 18. | •                                                       |     |

| Figure 19. | ·                                                       |     |

| Figure 20. | ·                                                       |     |

| Figure 21. |                                                         |     |

| Figure 22. |                                                         |     |

| Figure 23. | · · · · · · · · · · · · · · · · · · ·                   |     |

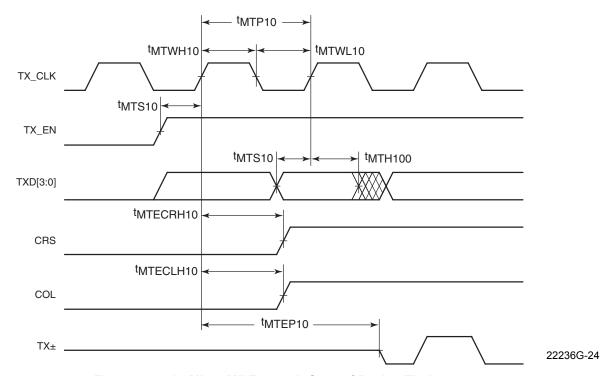

| Figure 24. | ·                                                       |     |

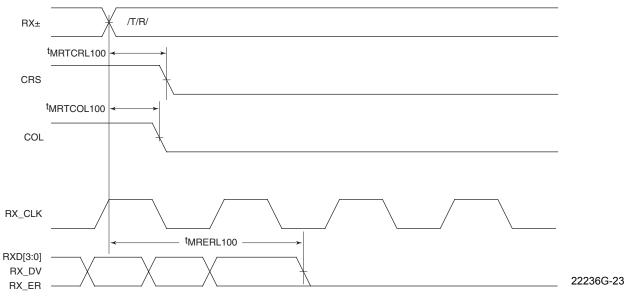

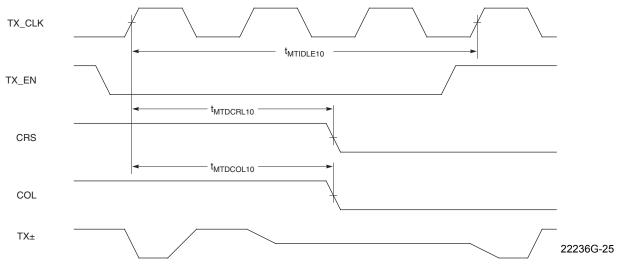

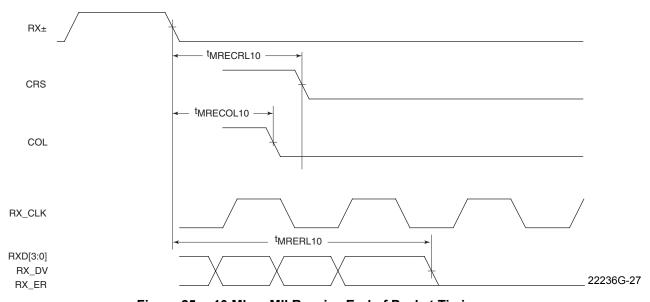

| Figure 25. | 10 Mbps MII Receive End of Packet Timing                | .54 |

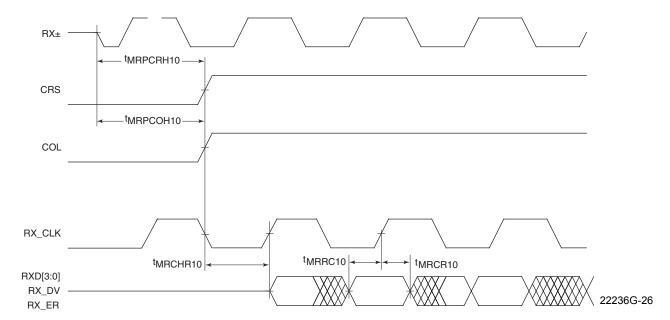

| Figure 26. | · · · · · · · · · · · · · · · · · · ·                   |     |

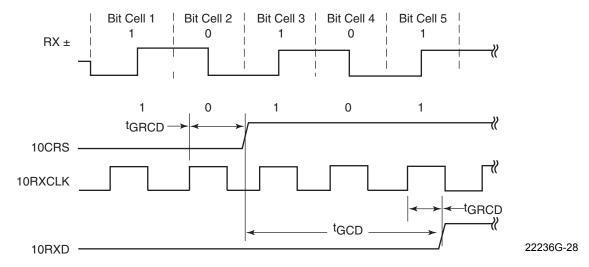

| Figure 27. | GPSI Receive Timing - End of Reception (Last Bit = 0)   | .55 |

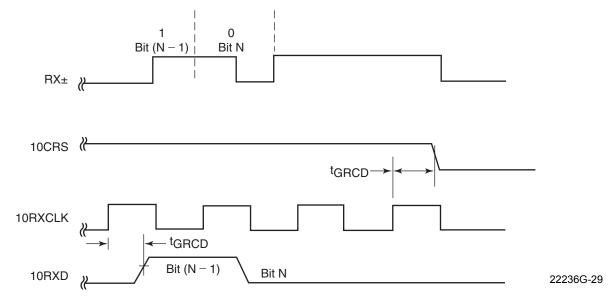

| Figure 28. |                                                         |     |

| Figure 29. |                                                         | .56 |

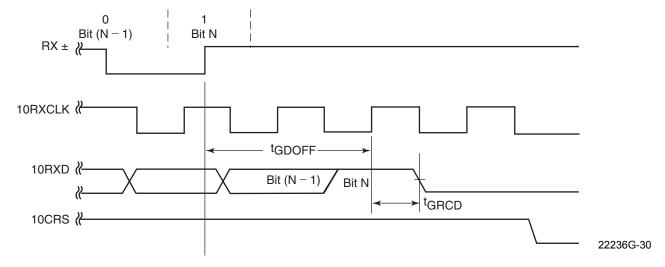

| Figure 30. | <u> </u>                                                |     |

| Figure 31. |                                                         |     |

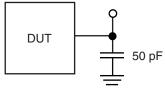

| Figure 32. | Test Load for 10RXD, 10CRS, 10RXCLK, 10TXCLK and 10COL  | .57 |

# **LIST OF TABLES**

| Table 1.  | Related AMD Products                                                            | 5  |

|-----------|---------------------------------------------------------------------------------|----|

| Table 2.  | Pin Designations Listed by Pin Number                                           | 10 |

| Table 3.  | Pin Description Terminology                                                     | 11 |

| Table 4.  | MII Pins that Relate to 10 Mbps 7-Wire (GPSI) mode                              | 17 |

| Table 5.  | Code-Group Mapping                                                              |    |

| Table 6.  | Speed and Duplex Capabilities                                                   | 25 |

| Table 7.  | Standard LED Mode and Advanced LED Mode Pins                                    | 26 |

| Table 8.  | Duplex LED Status Configuration in Advanced LED Mode1                           | 27 |

| Table 9.  | Activity LED Configuration in Advanced LED Mode                                 | 28 |

| Table 10. | Clause 22 Management Frame Format                                               | 30 |

| Table 11. | PHY Address Setting Frame Structure                                             | 30 |

| Table 12. | Supported Registers                                                             | 31 |

| Table 13. | Serial Management Registers                                                     | 31 |

| Table 14. | MII Management Control Register (Register 0)                                    | 32 |

| Table 15. | MII Management Status Register (Register 1)                                     |    |

| Table 16. | PHY Identifier 1 Register (Register 2)                                          | 33 |

| Table 17. | PHY Identifier 2 Register (Register 3)                                          | 34 |

| Table 18. | Auto-Negotiation Advertisement Register (Register 4)                            | 34 |

| Table 19. |                                                                                 |    |

| Table 20. | Auto-Negotiation LInk Partner Ability Register in Next Page Format (Register 5) | 35 |

| Table 21. | Auto-Negotiation Expansion Register (Register 6)                                | 36 |

| Table 22. | Auto-Negotiation Next Page Advertisement Register (Register 7)                  | 36 |

| Table 23. | Miscellaneous Features Register (Register 16)                                   | 37 |

| Table 24. | Interrupt Control/Status Register (Register 17)                                 | 38 |

| Table 25. | Diagnostic Register (Register 18)                                               | 38 |

| Table 26. | Power/Loopback Register (Register 19)                                           | 39 |

| Table 27. | Mode Control Register (Register 21)                                             | 40 |

| Table 28. | Disconnect Counter (Register 23)                                                | 41 |

| Table 29. | Receive Error Counter Register (Register 24)                                    | 41 |

| Table 30. | DC Characteristics                                                              | 42 |

| Table 31. | System Clock Signal                                                             | 47 |

| Table 32. | MLT-3 Signals                                                                   | 47 |

| Table 33. | MII Management Signals                                                          | 48 |

| Table 34. | 100 Mbps MII Transmit Timing                                                    | 49 |

| Table 35. | 100 Mbps MII Receive Timing                                                     | 51 |

| Table 36. | 10 Mbps MII Transmit Timing                                                     |    |

| Table 37. | 10 Mbps MII Receive Timing                                                      | 54 |

| Table 38. | 10 Mbps GPSI Receive Timing                                                     | 55 |

| Table 39. | 1                                                                               |    |

| Table 40. | 1                                                                               |    |

| Table 41. | 1                                                                               |    |

| Table 42. | i G                                                                             |    |

| Table 43. |                                                                                 |    |

| Table 44. | Revision Summary                                                                | 60 |

# **PIN DESIGNATIONS**

Table 2. Pin Designations Listed by Pin Number

| Pin<br>No. Pin Name |                         | Pin<br>No. Pin Name |                              | Pin<br>No. Pin Name                 |                              | Pin No. | Pin Name   |

|---------------------|-------------------------|---------------------|------------------------------|-------------------------------------|------------------------------|---------|------------|

| 1                   | PCSBP                   | 21                  | MDIO                         | 41 COL/10COL                        |                              | 61      | RPTR       |

| 2                   | ISODEF                  | 22                  | MDC                          | 42                                  | CRS/10CRS                    | 62      | TEST3/SDI+ |

|                     |                         |                     |                              |                                     |                              |         |            |

| 3                   | ISO                     | 23                  | RXD[3]                       | 43                                  | INTR                         | 63      | RX-        |

| 4                   | TGND1                   | 24                  | RXD[2]                       | 44                                  | LEDSPD[0]/<br>LEDBTA/FX_SEL  | 64      | RX+        |

| 5                   | REFCLK                  | 25                  | RXD[1]                       | 45                                  | LEDCOL/<br>SCRAM_EN          | 65      | EQGND      |

| 6                   | CLK25                   | 26                  | RXD[0]/10RXD                 | 46                                  | LEDRX/LEDSEL                 | 66      | TEST0/FXR- |

| 7                   | BURN_IN                 | 27                  | VDD1                         | 47                                  | LEDTX/LEDBTB                 | 67      | TEST1/FXR+ |

| 8                   | RST                     | 28                  | DGND1                        | DGND1 48 LED_10LNK/<br>LED_PCSBP_SD |                              | 68      | TEST2      |

| 9                   | PWRDN                   | 29                  | RX_DV                        | 49                                  | OVDD2                        | 69      | FXT+       |

| 10                  | PLLVCC                  | 30                  | RX_CLK/10RXCLK               | 50                                  | OGND2                        | 70      | FXT-       |

| 11                  | PLLGND                  | 31                  | RX_ER/RXD[4]                 | 51                                  | CRVGND                       | 71      | REFGND     |

| 12                  | OGND1                   | 32                  | TX_ER/TXD[4]                 | 52                                  | CRVVCC                       | 72      | IBREF      |

| 13                  | OVDD1                   | 33                  | TX_CLK/10TXCLK/<br>PCSBP_CLK | 53                                  | TECH_SEL[2]                  | 73      | REFVCC     |

| 14                  | PHYAD[4]/10RXD-         | 34                  | TX_EN/10TXEN                 | 54                                  | TECH_SEL[1]                  | 74      | XTL-       |

| 15                  | PHYAD[3]/10RXD+         | 35                  | DGND2                        | 55                                  | TECH_SEL[0]                  | 75      | XTL+       |

| 16                  | PHYAD[2]/10TXD++        | 36                  | VDD2                         | 2 56 ANEGA                          |                              | 76      | TGND2      |

| 17                  | PHYAD[1]/10TXD+         | 37                  | TXD[0]/10TXD                 | 57                                  | LEDSPD[1]/<br>LEDTXA/CLK25EN | 77      | TX+        |

| 18                  | PHYAD[0]/10TXD-         | 38                  | TXD[1]                       | 58                                  | LEDDPX/LEDTXB                | 78      | TX-        |

| 19                  | GPIO[0]/10TXD/<br>7Wire | 39                  | TXD[2]                       | 59                                  | ADPVCC                       | 79      | TVCC1      |

| 20                  | GPIO[1]/TP125           | 40                  | TXD[3]                       | 60                                  | EQVCC                        | 80      | TVCC2      |

#### PIN DESCRIPTIONS

The following table describes terms used in the pin descriptions.

Table 3. Pin Description Terminology

| Term           | Description                                    |  |  |

|----------------|------------------------------------------------|--|--|

| Input          | Digital input to the PHY                       |  |  |

| Analog Input   | Analog input to the PHY                        |  |  |

| Output         | Digital output from the PHY                    |  |  |

| Analog Output  | Analog output from the PHY                     |  |  |

| High Impedance | Tri-state capable output from the PHY          |  |  |

| Pull-Up        | PHY has internal pull-up resistor.<br>NC=HIGH  |  |  |

| Pull-Down      | PHY has internal pull-down resistor.<br>NC=LOW |  |  |

## **Media Connections**

#### TX±

# **Transmitter Outputs**

# **Analog Output**

The TX $\pm$  pins are the differential transmit output pair. The TX $\pm$  pins transmit 10BASE-T or MLT-3 signals depending on the state of the link of the port. If the TX $\pm$  pins are not used, they can be left unconnected.

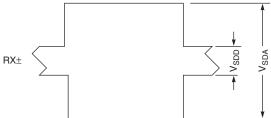

#### **RX±**

# **Receiver Input**

**Analog Input**

The RX $\pm$  pins are the differential receive input pair. The RX $\pm$  pins can receive 10BASE-T or MLT-3 signals depending on the state of the link of the port. If the RX $\pm$  pins are not used, they can be connected to each other with standard resistor termination.

#### **FXT**±

#### **FX Transmit**

**Analog Output**

These pins are not connected in 10/100BASE-TX mode.

When FX\_SEL (Pin 44) is pulled low, these pins become the PECL level transmit output for 100BASE-FX.

#### TESTO/FXR-

#### Test Output/FX Receive -Analog Output/Input

When BURN\_IN (Pin 7) is pulled high, this pin serves as a test mode output monitor pin.

When FX\_SEL (Pin 44) is pulled low, this pin becomes a PECL level negative receive input for 100BASE-FX.

This pin can be left unconnected when the device is operating in 100BASE-TX or 10BASE-T mode.

#### TEST1/FXR+

## Test Output/FX Receive +Analog Output/Input

When BURN\_IN (Pin 7) is pulled high, this pin serves as a test mode output monitor pin.

When FX\_SEL (Pin 44) is pulled low, this pin becomes a PECL level positive receive input for 100BASE-FX.

This pin can be left unconnected when the device is operating in 100BASE-TX or 10BASE-T mode.

#### TEST3/SDI+

#### FX Transceiver Signal Detect Analog Output/Input

When BURN\_IN (Pin 7) is pulled high, this pin serves as a test mode output monitor pin.

This pin is not connected in 10/100BASE-TX mode.

When FX\_SEL (Pin 44) is pulled low, this pin becomes the Signal Detect input from the Fiber-Optic transceiver. When the signal quality is good, the SDI+ pin should be driven high.

# MII/7-Wire (GPSI) Signals

#### RXD[3:0]

# MII Receive Data Output, High Impedance

The data is synchronous with RX\_CLK when RX\_DV is active. When the 7-wire 10BASE-T interface operation is enabled (GPIO[0]= HIGH), RXD[0] will serve as the 10 MHz serial data output.

#### RX DV

# Receive Data Valid Output, High Impedance

RX\_DV is asserted when the NetPHY-1LP device is presenting recovered nibbles on RXD[3:0]. This includes the preamble through the last nibble of the data stream on RXD[3:0]. In 100BASE-X mode, the /J/K/ is considered part of the preamble; thus RX\_DV is asserted when /J/K/ is detected. In 10BASE-T mode, RX\_DV is asserted (and data is presented on RXD[3:0]) when the device detects valid preamble bits. RX\_DV is synchronized to RX\_CLK.

#### RX\_CLK/10RXCLK

#### Receive Clock Output, High Impedance

A continuous clock (which is active while LINK is established) provides the timing reference for RX\_DV, RX\_ER, and RXD[3:0] signals. It is 25 MHz in 100BASE-TX/FX and 2.5 MHz in 10BASE-T. To further reduce power consumption of the overall system, the device provides an optional mode enabled through MII Register 16, bit 0 in which RX\_CLK is held inactive (low) when no data is received. If RX\_CLK is needed when LINK is not established, the NetPHY-1LP must be placed into digital loopback or force the link via register 21, bits 13 or 14.

When 7-wire 10BASE-T mode is enabled, this pin will provide a 10 MHz clock. RX\_CLK is high impedance when the ISO pin is enabled

#### RX ER/RXD[4]

## Receive Error Output, High Impedance

When RX\_ER is active high, it indicates an error has been detected during frame reception.

This pin becomes the highest-order bit of the receive 5-bit code group in PCS bypass (PCSBP=HIGH) mode. This output is ignored in 10BASE-T operation.

# TX\_ER/TXD[4] Transmit Error

#### Input

When TX\_ER is asserted, it will cause the 4B/5B encoding process to substitute the transmit error codegroup /H/ for the encoded data word.

This pin becomes the higher-order bit of the transmit 5-bit code group in PCS bypass (PCSBP=HIGH) mode. This input is ignored in the 10BASE-T operation.

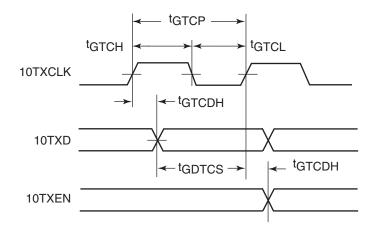

#### TX CLK/10TXCLK/PCSBPCLK

## Transmit Clock Output, High Impedance

A free-running clock which provides timing reference for TX\_EN, TX\_ER, and TXD[3:0] signals. It is 25 MHz in 100BASE-TX/FX and 2.5 MHz in 10BASE-T.

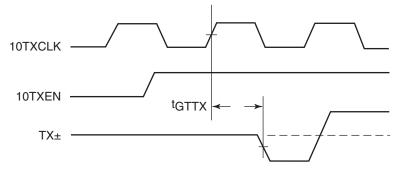

When 7-wire GPSI mode is enabled, this pin will provide a 10 MHz transmit clock for 10BASE-T operation. When the cable is unplugged, the 10TXCLK ceases operation.

When working in PCSBP mode, this pin will provide a 25 MHz clock for 100BASE-TX operation, and 20 MHZ clock for 10BASE-T operation. TX\_CLK is high impedance when the ISO pin is enabled.

#### TX\_EN/10TXEN

#### Transmit Enable

Input

The TX\_EN pin is asserted by the MAC to indicate that data is present on TXD[3:0].

When 7-wire 10BASE-T mode is enabled, this pin is the transmit enable signal.

#### TXD[3:1]

#### Transmit Data

Input

The MAC will source TXD[3:1] to the PHY. The data will be synchronous with TX\_CLK when TX\_EN is asserted. The PHY will clock in the data based on the rising edge of TX\_CLK.

#### TXD[0]/10TXD

#### Transmit Data[0]/10 Mbps Transmit Data Input

The MAC will source TXD[0] to the PHY. The data will be synchronous with TX\_CLK when TX\_EN is asserted. The PHY will clock in the data based on the rising edge TX\_CLK.

When 7-wire 10BASE-T mode is enabled, this pin will transmit serial data.

#### COL/10COL

# Collision

#### **Output, High Impedance**

COL is asserted high when a collision is detected on the media. COL is also used for the SQE test function in 10BASE-T mode.

10COL is asserted high when a collision is detected during 7-wire interface mode.

#### CRS/10CRS

## Carrier Sense Output, High Impedance

CRS is asserted high when twisted pair media is nonidle. This signal is used for both 10BASE-T and 100BASE-X. In full duplex mode, CRS responds only to RX activity. In half duplex mode, CRS responds to both RX and TX activity.

10CRS is used as the carrier sense output for the 7-wire interface mode.

# **Miscellaneous Functions**

#### **PCSBP**

## **PCS Bypass**

#### Input, Pull-Down

The 100BASE-TX PCS as well as scrambler/descrambler will be bypassed when PCSBP is pulled high via a 1-4.7 k $\Omega$  resistor. TX\_ER will become TXD[4] and RX ER will become RXD[4].

In 10 Mbps PCS bypass mode, the MII signals are not valid. The signals that interface to the MAC (i.e., DECPC 21143) are located on pins 14 to 19. The signals are defined as follows:

- 10RXD± are the differential receive outputs to the MAC.

- 10TXD± are the differential transmit inputs from the MAC.

- 10TXD++/10TXD-- are the differential preemphasis transmit outputs from the MAC.

When left unconnected, the device operates in MII or GPSI mode.

#### ISODEF

#### **Isolate Default**

Input, Pull-Down

This pin is used when multiple PHYs are connected to a single MAC. When it is pulled high via a 1-4.7 k $\Omega$  resistor, the MII interface will be high impedance. The status of this pin will be latched into MII Register 0, bit 10 after reset.

When this pin is left unconnected, the default condition of the MII output pins are not in the high impedance state.

#### ISO

# Isolate

# Input, Pull-Down

The MII output pins will become high impedance when ISO is pulled high via a 1-4.7 k $\Omega$  resistor. However, the MII input pins will still respond to data. This allows multiple PHYs to be attached to the same MII interface. The same isolate condition can also be achieved by asserting MII Register 0, bit 10. In repeater mode, ISO will not tri-state the CRS pin.

When this pin is left unconnected, the MII output pins are not in the high impedance state.

# REFCLK

# **Clock Input**

#### Input, Pull-Down

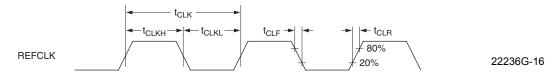

This pin connects to a 25-MHz  $\pm$ 50 ppm clock source with a 40% to 60% duty cycle. When a crystal input is used, this pin should be pulled low via a 1 k $\Omega$  resistor.

#### **XTL±**

# **Crystal Inputs**

#### **Analog Input**

These pins should be connected to a 25-MHz crystal. The crystal should be parallel resonant and have a frequency stability of  $\pm 100$  ppm and a frequency tolerance of  $\pm 50$  ppm. REFCLK (Pin 5) should be pulled low when the crystal is used as a clock source.

These pins may be left unconnected when REFCLK is used as a clock source.

#### CLK25

#### 25 MHz Clock

Output

When the CLK25EN pin is pulled low, the CLK25 pin provides a continuous 25 MHz clock to the MAC.

# **BURN\_IN**

#### **Test Enable**

Input, Pull-Down

When pulled high via a 1-4.7  $k\Omega$  resistor, this pin forces the NetPHY-1LP device into Burn-in mode for reliability assurance control. When left unconnected the device operates normally.

#### TEST2

#### **Test Output**

**Analog Output**

When BURN\_IN (pin 7) is pulled high, this pin serves as a test mode output monitor pin. TEST2 can be left unconnected when the device is operating.

# RST

# Reset

Input, Pull-Up

A LOW input forces the NetPHY-1LP device to a known reset state. The chip can also be reset through internal power-on-reset or MII Register 0, bit 15.

#### **PWRDN**

#### **Power Down**

Input, Pull-Down

If this pin is pulled high via a 1-4.7 k $\Omega$  resistor on the rising edge of reset, the device will power down the analog modules and reset the digital circuits. However, the device will still respond to MDC/MDIO data. The same power-down state can also be achieved through the MII Register 0, bit 11. However, the device will respond activity on the PWRDN pin even when bit 11 is not set.

When left unconnected, the device operates normally.

This pin can be pulled down anytime during normal operation to enter Power Down mode.

#### PHYAD[4:0]

#### **PHY Address**

Input/Output, Pull-Up

These pins allow 32 configurable PHY addresses. The PHYAD will also determine the scramble seed, which

helps to reduce EMI when there are multiple ports switching at the same time (repeater/switch applications). Each pin should either be pulled low via a 1 k $\Omega$  – 4.7 k $\Omega$  resistor (set bit to zero) or left unconnected (set bit to 1) in order to achieve the desired PHY address. New address changes take effect after a reset has been issued, or at power up.

In PCS bypass mode, PHYAD[4:0] and GPIO[1:0] serves as 10BASE-T serial input and output.

**Note:** In GPSI mode, the PHYAD pins must be set to addresses other than 00h.

# GPIO[0]/10TXD--/7Wire

# General Purpose I/O 0

Input/Output, Pull-Up

If this pin is pulled low via a 1-4.7 k $\Omega$  resistor, on the rising edge of reset, the device will operate in 10BASE-T 7-wire (GPSI) mode. If this pin is left unconnected during the rising edge of reset, the device will operate in standard MII mode.

After the reset operation has completed, this pin can function as an input or an output (dependent on the value of GPIO[0] DIR (MII Register 16, bit 6). If MII Register 16, bit 6 is set HIGH, GPIO[0] is an input. The input value on the GPIO[0] pin will be reflected in MII Register 16, bit 7 – GPIO[0] Data. If MII Register 16, bit 6 is set LOW, GPIO[0] is an output. The value of MII Register 16, bit 7 will be reflected on the GPIO[0] output pin.

#### GPIO[1]/TP125

## General Purpose I/O 1 Input/Output, Pull-Down

If this pin is pulled high via a 1-4.7 k $\Omega$  resistor, on the rising edge of reset, the device will be enabled for use with a 1.25:1 transmit ratio transformer. If this pin is left unconnected during the rising edge of reset, the device will be enabled for use with a 1:1 transmit ratio transformer.

After the reset operation has completed, this pin can function as an input or an output (dependent on the value of GPIO[1] DIR – MII Register 16, bit 8). If MII Register 16, bit 8 is set HIGH, GPIO[1] is an input. The input value on the GPIO[1] pin will be reflected in MII Register 16, bit 9 – GPIO[1] Data. If MII Register 16, bit 8 is set LOW, GPIO[1] is an output. The value of MII Register 16, bit 9 will be reflected on the GPIO[1] output pin.

#### **MDIO**

# Management Data Input/Output

Pull-Down

This pin is a bidirectional data interface used by the MAC to access management registers within the Net-PHY-1LP device. This pin has an internal pull-down, therefore, it requires a 1.5 k $\Omega$  pull-up resistor as specified in IEEE 802.3 when interfaced with a MAC. This pin can be left unconnected when management is not used.

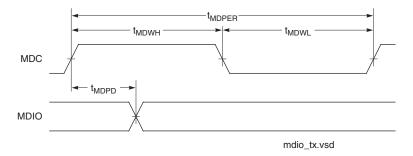

#### **MDC**

#### Management Data Clock

This clock is sourced by the MAC and is used to synchronize MDIO data. When management is not used, this pin should be tied to ground.

#### **INTR**

## Interrupt Output, High Impedance

This pin is used to signal an interrupt to the MAC. The pin will be forced high or low (normally high impedance) to signal an interrupt depending upon the value of the INTR\_LEVL bit, MII Register 16, bit 14. The events which trigger an interrupt can be programmed via the Interrupt Control Register (Register 17).

# TECH\_SEL[2:0] Technology Select

Input, Pull-Up

The Technology Select pins, in conjunction with the ANEGA pin, set the speed and duplex configurations for the device on the rising edge of reset. These capabilities are reflected in MII Register 1 and MII Register 4. Table 6 lists the possible configurations for the device. If the input is listed as LOW, the pin should be pulled to ground via a 1-4.7 k $\Omega$  resistor on the rising edge of reset. If the input is listed as HIGH, the pin can be left unconnected.

**Note:** By using resistors to hard wire the TECH\_SEL[2:0] pins and the ANEGA pin, using the MDC/MDIO management interface pins becomes optional. The device's speed, duplex, and auto-negotiation capabilities are set via hardware. If the management interface is used, the registers cannot be set to a higher capability than the hard-wired setting. The highest capabilities are Full Duplex, 100 Mbps, and Auto-Negotiation enabled.

#### **ANEGA**

#### Auto-Negotiation Ability Input, Pull-Up

When this pin is pulled to ground via a 1-4.7 k $\Omega$  resistor, on the rising edge of reset, Auto-Negotiation is disabled. When this pin is left unconnected, on the rising edge of reset, Auto-Negotiation is enabled. Note that this pin acts in conjunction with Tech\_Sel[2:0] on the rising edge of reset. Refer to Table 3 to determine the desired configuration for the device.

In 100BASE-FX mode, ANEGA should be pulled to ground.

**Note:** By using resistors to hard wire the TECH\_SEL[2:0] pins and the ANEGA pin, using the MDC/MDIO management interface pins becomes optional. The device's speed, duplex, and auto-negotiation capabilities are set via hardware. If the management interface is used, the registers cannot be set to a higher capability than the hard-wired setting. The highest capabilities are Full Duplex, 100 Mbps, and Auto-Negotiation enabled.

#### **RPTR**

Input

# **Repeater Mode**

Input

This pin should be tied to ground via a 1-4.7 k $\Omega$  resistor if repeater mode is to be disabled. When this pin is pulled high via a 1-4.7 k $\Omega$  resistor, repeater mode will be enabled. Repeater mode can also enabled via MII Register 16, bit 15. In this mode, the port is set to Half Duplex and SQE is not performed.

# **LED Port Pins**

# LEDRX/LED\_SEL

## Receive LED/LED Configuration Select

## Input/Output, Pull-Up

When this pin is pulled low via a 1 k $\Omega$  resistor, on the rising edge of reset, the advanced LED configuration is enabled. If there is no pull-down resistor present, on the rising edge of reset, the standard LED configuration is enabled.

After the rising edge of reset this pin controls the Receive LED. This pin toggles between high and low when data is received. When the device is operating in the standard LED mode, refer to Figure 5 in the *LED Port Configuration* section. When the device is operating in the advanced LED mode, refer to Table 9 and Figure 6 in the *LED Port Configuration* section.

# LEDCOL/SCRAM\_EN Collision LED/Scrambler Enable

#### Input/Output, Pull-Up

When this pin is pulled low via a 1-k $\Omega$  resistor, on the rising edge of reset, the scrambler/descrambler is disabled. If no pull-down resistor is present, on the rising edge of reset, the scrambler/descrambler is enabled.

After the rising edge of reset this pin controls the Collision LED. This pin toggles between high and low when there is a collision in half-duplex operation. In full-duplex operation this pin is inactive. When the device is operating in the standard LED mode, refer to Figure 5 in the *LED Port Configuration* section. When the device is operating in the advanced LED mode, see Figure 6.

# LEDLNK/LED\_10LNK/LED\_PCSBP\_SD Link LED/7-Wire Link LED/PCSBP Signal Detect Output

When a link is established in 100BASE-X or 10BASE-T mode, this pin will assume a logic low level.

When a link is established in 7-Wire mode, this pin will assume a logic high level.

When in PCS Bypass mode, this pin assumes a logic high level indicating Signal Detect.

Refer to Figure 4 in the *LED Port Configuration* section if the device is operating in the standard LED mode. See Figure 5 if the device is operating in the advanced LED mode.

AMD

**Note:** If 7-Wire mode is chosen the polarity of the LED should be reversed and the cathode of the LED should be tied to ground.

# LEDSPD[0]/LEDBTA/FX\_SEL

# 100 Mbps Speed LED/Advanced LED/Fiber Select Input/Output, Pull-Up

When this pin is pulled low via a 1 k $\Omega$  resistor, on the rising edge of reset, the device will be enabled for 100BASE-FX operation. When no pull-down resistor is present, on the rising edge of reset, the device will be enabled for 100BASE-TX or 10BASE-T operation.

When the standard LED configuration is enabled (see LEDRX/LEDSEL pin description), this pin serves as the 100 Mbps speed LED. A logic low level indicates 100 Mbps operation. A logic high level indicates 10 Mbps operation. Refer to Figure 5 in the *LED Port Configuration* section to determine the correct polarity of the LED.

When the advanced LED configuration is enabled, this pin works in conjunction with LEDTX/LEDBTB (pin 47). Refer to Table 7 and Figure 6 in the *LED Port Configuration* section to determine the correct polarity of the bidirectional LED.

#### LEDTX/LEDBTB

#### Transmit LED/Advanced LED Output

When the standard LED configuration is enabled (see LEDRX/LEDSEL pin description), this pin serves as the transmit LED. This pin toggles between high and low when data is transmitted. Refer to Figure 5 in the *LED Port Configuration* section to determine the correct polarity of the LED.

When the advanced LED configuration is enabled, this pin works in conjunction with LEDSPD[0]/LEDBTA/FX\_SEL (pin 44). Refer to Table 7 and Figure 6 in the LED Port Configuration section to determine the correct polarity of the bi-directional LED.

# LEDSPD[1]/LEDTXA/CLK25EN

# 10 Mbps Speed LED/Advanced LED/25 MHz Clock Enable Input/Output, Pull-Up

When this pin is pulled low via a 1 k $\Omega$  resistor, on the rising edge of reset, the device will output a 25 MHz clock on CLK25 (pin 6). When no pull-down resistor is present, on the rising edge of reset, CLK25 is inactive.

When the standard LED configuration is enabled (see LEDRX/LEDSEL pin description), this pin serves as the 10 Mbps speed LED. A logic low level indicates 10 Mbps operation. A logic high level indicates 100 Mbps operation. Refer to Figure 5 in the LED Port Configuration section to determine the correct polarity of the LED.

When the advanced LED configuration is enabled, this pin works in conjunction with LEDDPX/LEDTXB (pin 58). Refer to Table 8 and Figure 6 in the *LED Port Con-*

figuration section to determine the correct polarity of the bi-directional LED.

#### LEDDPX/LEDTXB

#### **Duplex LED/Advanced LED**

**Output**

When the standard LED configuration is enabled (see LEDRX/LEDSEL description), this pin serves as the duplex LED. A logic low level indicates full duplex operation. A logic high level indicates half duplex operation. See Figure 5 in the LED Port Configuration section to determine the correct polarity of the LED.

When the advanced LED configuration is enabled, this pin works in conjunction with LEDSPD[1] LEDTXA/ CLK25EN (pin 57). Refer to Table 8 and Figure 6 in the LED Port Configuration section to determine the correct polarity of the bi-directional LED.

#### **Bias**

#### **IBREF**

#### Reference Bias Resistor

**Analog**

This pin must be tied to an external 10.0 k $\Omega$  (1%) resistor which should be connected to ground. The 1% resistor provides the bandgap reference voltage.

**Note:** This signal trace should be short and not close to other signals.

## **Power and Ground**

# PLLVCC, OVDD1, OVDD2, VDD1, VDD2, CRVVCC, ADPVCC, EQVCC, REFVCC, TVCC1, TVCC2 Power Pins Power

These pins are 3.3 V power for sections of the NetPHY-1LP device as follows:

PLLVCC is power for the PLL; OVDD1 and OVDD2 are power for the I/O; VDD1 and VDD2 are power for the digital logic; CRVVCC is power for clock recovery; AD-PVCC and EQVCC are power for the equalizer; REFVCC is power for the bandgap reference; and TVCC1 and TVCC2 are power for the transmit driver.

# PLLGND, OGND1, OGND2, DGND1, DGND2, CRVGND, EQGND, REFGND, TGND1, TGND2 Ground Pins Power

These pins are ground for the power pins as follows:

PLLGND is ground for PLLVCC; OGND is ground for OVDD; DGND is ground for VDD; CRVGND is ground for CRVVCC and ADPVCC; EQGND is ground for EQVCC; REFGND is ground for REFVCC; and TGND is ground for TVCC.

**Note:** Bypass capacitors of 0.1  $\mu$ F between the power and ground pins are recommended. The four areas where the capacitors must be very close to the pins (within 3 mm) are the PLL (pins 10 and 11), Clock Recovery (pins 51 and 52), Equalizer (pins 60 and 65), and Bandgap Reference (pins 71 and 73) areas. The other bypass capacitors should be placed as close to the pins as possible.

#### **FUNCTIONAL DESCRIPTION**

The NetPHY-1LP device integrates the 100BASE-X PCS, PMA, and PMD functions and the 10BASE-T Manchester ENDEC and transceiver functions in a single chip for Ethernet 10 Mbps and 100 Mbps operations. It performs 4B/5B, MLT3, NRZI, and Manchester encoding and decoding, clock and data recovery, stream cipher scrambling/descrambling, adaptive equalization, line transmission, carrier sense and link integrity monitor, Auto-Negotiation, and MII management functions. It provides an IEEE 802.3u compatible Media Independent Interface (MII) to communicate with an Ethernet Media Access Controller (MAC). Selection of 10 Mbps or 100 Mbps operation is based on settings of internal Serial Management Interface registers or determined by the on-chip Auto-Negotiation logic. The device can be set to operate either in full-duplex mode or half-duplex mode for either 10 Mbps or 100 Mbps.

The NetPHY-1LP device communicates with a repeater, switch, or MAC device through either the Media Independent Interface (MII) or the 10 Mbps 7-wire (GPSI) interface.

The NetPHY-1LP device consists of the following functional blocks:

- MII Mode

- 7-Wire (GPSI) Mode

- PCS Bypass (5B Symbol) Mode

- 100BASE-X Block including:

- Transmit Process

- Receive Process

- 4B/5B Encoder and Decoder

- Scrambler and Descrambler

- Link Monitor

- MLT-3

- Adaptive Equalizer

- Baseline Wander Compensation

- Clock/Data Recovery

- PLL Clock Synthesizer

- 10BASE-T Block including:

- Transmit Process

- Receive Process

- Interface Status

- Collision Detect

- Jabber

- Reverse Polarity Detection and Correction

- Auto-Negotiation and miscellaneous functions including:

- Auto-Negotiation

- Parallel Detection

- Far-End Fault

- SQE (Heartbeat)

- Loopback Operation

- Reset

- LED Port Configuration

- Power Savings Mechanisms including:

- Selectable Transformer

- Power Down

- Unplugged

- Idle Wire

- PHY Control and Management

# **Modes of Operation**

The MII/GPSI/5B Symbol interface provides the data path connection between the NetPHY-1LP transceiver and the Media Access Controller (MAC), repeater, or switch. The MDC and MDIO pins are responsible for communication between the NetPHY-1LP transceiver and the station management entity (STA). The MDC and MDIO pins can be used in any mode of operation.

#### **MII Mode**

The purpose of the MII mode is to provide a simple, easy to implement connection between the MAC Reconciliation layer and the PHY. The MII is designed to make the differences between various media transparent to the MAC sublayer.

The MII consists of a nibble wide receive data bus, a nibble wide transmit data bus, and control signals to facilitate data transfers between the PHY and the Reconciliation layer.

- TXD (transmit data) is a nibble (4 bits) of data that are driven by the reconciliation sublayer synchronously with respect to TX\_CLK. For each TX\_CLK period which TX\_EN is asserted, TXD[3:0] are accepted for transmission by the PHY.

- TX\_CLK (transmit clock) output to the MAC reconciliation sublayer is a continuous clock that provides the timing reference for the transfer of the TX\_EN, TXD, and TX\_ER signals.

- TX\_EN (transmit enable) input from the MAC reconciliation sublayer to indicate nibbles are being presented on the MII for transmission on the physical medium. TX\_ER (transmit coding error) transitions synchronously with respect to TX\_CLK. If TX\_ER is asserted for one or more clock periods, and TX\_EN is asserted, the PHY will emit one or more symbols that are not part of the valid data delimiter set somewhere in the frame being transmitted.

- RXD (receive data) is a nibble (4 bits) of data that is sampled by the reconciliation sublayer synchronously with respect to RX\_CLK. For each RX\_CLK period which RX\_DV is asserted, RXD[3:0] are transferred from the PHY to the MAC reconciliation sublayer.

- RX\_CLK (receive clock) output to the MAC reconciliation sublayer is a continuous clock (during LINK only) that provides the timing reference for the transfer of the RX\_DV, RXD, and RX\_ER signals.

- RX\_DV (receive data valid) input from the PHY to indicate the PHY is presenting recovered and decoded nibbles to the MAC reconciliation sublayer. To interpret a receive frame correctly by the reconciliation sublayer, RX\_DV must encompass the frame starting no later than the Start-of-Frame delimiter and excluding any End-Stream delimiter.

- RX\_ER (receive error) transitions synchronously with respect to RX\_CLK. RX\_ER will be asserted for 1 or more clock periods to indicate to the reconciliation sublayer that an error was detected somewhere in the frame being received by the PHY.

- CRS (carrier sense) is asserted by the PHY when either the transmit or receive medium is non-idle and deasserted by the PHY when the transmit and receive medium are idle.

# 7-Wire (GPSI) Mode

7-Wire (GPSI) mode uses the existing MII pins, but data is transferred only on TXD[0] and RXD[0]. This mode is used in a General Purpose Serial Interface (GPSI) configuration for 10BASE-T. If the GPIO[0] pin is LOW at the rising edge of reset, then GPSI mode is selected. For this configuration, TX\_CLK runs at 10 MHz. When the cable is unplugged, 10TXCLK ceases operation. Note that 7-wire mode does not define the use of Auto-Negotiation or MDC/MDIO.

The MII pins that relate to 7-wire (GPSI) mode are shown in the following table. The unused *input* pins in this mode should be tied to ground through a 1 k $\Omega$  resistor. The RPTR pin must be connected to GND.

Table 4. MII Pins that Relate to 10 Mbps 7-Wire (GPSI) mode

| MII Pin Name   | 7-Wire (GPSI)               |

|----------------|-----------------------------|

| TX_CLK/10TXCLK | Transmit Clock              |

| TXD[0]/10TXD   | Transmit Serial Data Stream |

| TXD[3:1]       | Not used                    |

| TX_EN/10TXEN   | Transmit Enable             |

| TX_ER          | Not used                    |

| RX_CLK/10RXCLK | Receive Clock               |

| RXD[0] /10RXD  | Receive Serial Data Stream  |

| RXD[3:1]       | Not used                    |

| COL/10COL      | Collision Detect            |

Table 4. MII Pins that Relate to 10 Mbps 7-Wire (GPSI) mode (continued)

| MII Pin Name | 7-Wire (GPSI)        |

|--------------|----------------------|

| RX_ER        | Not used             |

| CRS/10CRS    | Carrier Sense Detect |

**Note:** CRS ends one and one-half bit times after the last data bit. The effect is one or two dribbling bits on every packet. All MACs truncate packets to eliminate the dribbling bits. The only noticeable effect is that all CRC errors are recorded as framing errors.

Use the TECH\_SEL[2:0] to select the desired 10BASE-T operation.

#### **5B Symbol Mode**

The purpose of the 5B Symbol mode is to provide a way for the MAC to do the 4B/5B encoding/decoding and scrambling/descrambling in 100 Mbps operation.

In 10 Mbps operation, the MII signals are not used. Instead, the NetPHY-1LP device operates as a 10BASE-T transceiver, providing received data to the MAC over a serial differential pair (see PCSBP pin). The MAC uses two serial differential pairs to provide transmit data to the NetPHY-1LP device, where the two differential pairs are combined in the NetPHY-1LP device to compensate for inter-symbol interference on the twisted pair medium.

#### 100BASE-X Block

The functions performed by the device include encoding of MII 4-bit data (4B/5B), decoding of received code groups (5B/4B), generating carrier sense and collision detect indications, serialization of code groups for transmission, de-serialization of serial data upon reception, mapping of transmit, receive, carrier sense, and collision at the MII interface, and recovery of clock from the incoming data stream. It offers stream cipher scrambling and descrambling capability for 100BASE-TX applications.

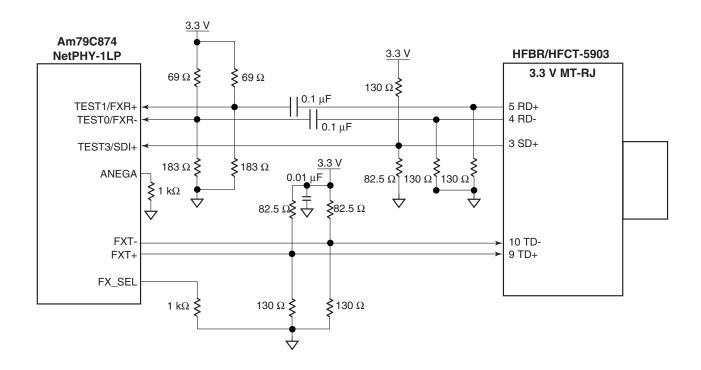

In the transmit data path for 100 Mbps, the NetPHY-1LP transceiver receives 4-bit (nibble) wide data across the MII at 25 million nibbles per second. For 100BASE-TX applications, it encodes and scrambles the data, serializes it, and transmits an MLT-3 data stream to the media via an isolation transformer. For 100BASE-FX applications, it encodes and serializes the data and transmits a Pseudo-ECL (PECL) data stream to the fiber optic transmitter. See Figure 1.

In the receive data path for 100 Mbps, the NetPHY-1LP transceiver receives an MLT-3 data stream from the network. For 100BASE-TX, it then recovers the clock from the data stream, de-serializes the data stream, and descrambles/decodes the data stream (5B/4B) before presenting it at the MII interface.

22236G-3

Figure 1. FXT± and FXR± Termination for 100BASE-FX

For 100BASE-FX operation, the NetPHY-1LP device receives a PECL data stream from the fiber optic transceiver and decodes that data stream.

The 100BASE-X block consists of the following subblocks:

- Transmit Process

- Receive Process

- 4B/5B Encoder and Decoder

- Scrambler/Descrambler

- Link Monitor

- Far End Fault Generation and Detection & Code-Group Generator

- MLT-3 encoder/decoder with Adaptive Equalization

- Baseline Restoration

- Clock Recovery

#### **Transmit Process**

The transmit process generates code-groups based on the transmit control and data signals on the MII. This process is also responsible for frame encapsulation into a Physical Layer Stream, generating the collision signal based on whether a carrier is received simultaneously during transmission and generating the Carrier Sense CRS and Collision COL signals at the MII. The transmit process is implemented in compliance with the

transmit state diagram as defined in Clause 24 of the IEEE 802.3u specification.

The NetPHY-1LP device transmit function converts synchronous 4-bit data nibbles from the MII to a 125-Mbps differential serial data stream. The entire operation is synchronous to a 25-MHz clock and a 125-MHz clock. Both clocks are generated by an on-chip PLL clock synthesizer that is locked to an external 25-MHz clock source.

In 100BASE-FX mode, the NetPHY-1LP device will bypass the scrambler. The output data is an NRZI PECL signal. This PECL level signal will then drive the Fiber transmitter.

#### **Receive Process**

The receive path includes a receiver with adaptive equalization and DC restoration, MLT-3-to-NRZI conversion, data and clock recovery at 125-MHz, NRZI-to-NRZ conversion, Serial-to-Parallel conversion, descrambling, and 5B to 4B decoding. The receiver circuit starts with a DC bias for the differential RX± inputs, follows with a low-pass filter to filter out high-frequency noise from the transmission channel media. An energy detect circuit is also added to determine whether there is any signal energy on the media. This is useful in the power-saving mode. (See the description in *Power*

Savings Mechanisms section). All of the amplification ratio and slicer thresholds are set by the on-chip bandgap reference.

In 100BASE-FX mode, signal will be received through a PECL receiver, and directly passed to the clock recovery for data/clock extraction. In FX mode, the scrambler/descrambler cipher will be bypassed.

#### 4B/5B Encoder/Decoder

The 100 Mbps process in the NetPHY-1LP device uses the 4B/5B encoding scheme as defined in IEEE 802.3, Section 24. This scheme converts between raw data on the MII and encoded data on the media pins. The encoder converts raw data to the 4B/5B code. It also inserts the stream boundary delimiters (/J/K/ and /T/R/) at the beginning and end of the data stream as appropriate. The decoder converts between encoded data on the media pins and raw data on the MII. It also detects the stream boundary delimiters to help determine the start and end of packets. The code-group mapping is defined in Table .

The 4B/5B encoding is bypassed when MII Register 21, bit 1 is set to "1", or the PCSBP pin (pin 1) is strapped high.

#### Scrambler/Descrambler

The 4B/5B encoded data has repetitive patterns which result in peaks in the RF spectrum large enough to keep the system from meeting the standards set by regulatory agencies such as the FCC. The peaks in the radiated signal are reduced significantly by scrambling the transmitted signal. Scramblers add the output of a random generator to the data signal. The resulting signal has fewer repetitive data patterns.

After reset, the scrambler seed in each port will be set to the PHY address value to help improve the EMI performance of the device.

The scrambled data stream is descrambled at the receiver by adding it to the output of another random generator. The receiver's random generator uses the same function as the transmitter's random generator.

In 100BASE-TX mode, all 5-bit transmit data streams are scrambled as defined by the TP-PMD Stream

Cipher function in order to reduce radiated emissions on the twisted pair cable. The scrambler encodes a plain text NRZ bit stream using a key stream periodic sequence of 2047 bits generated by the recursive linear function:

$$X[n] = X[n-11] + X[n-9]$$

(modulo 2)

The scrambler reduces peak emissions by randomly spreading the signal energy over the transmit frequency range, thus eliminating peaks at a single frequency.

When MII Register 21, bit 2 is set to "1," the data scrambling function is disabled and the 5-bit data stream is clocked directly to the device's PMA sublayer.

#### **Link Monitor**

Signal levels are detected through a squelch detection circuit. A signal detect (SD) circuit following the equalizer is asserted high whenever the peak detector senses a post-equalized signal with a peak-to-ground voltage level larger than 400 mV. This is approximately 40 percent of the normal signal voltage level. In addition, the energy level must be sustained longer than 2 ms in order for the signal detect to be asserted. It gets de-asserted approximately 1 ms after the energy level is consistently less than 300 mV from peak-to-ground.

The link signal is forced to low during a local loopback operation (i.e., when MII Register 0, bit 14, Loopback is asserted) and forced to high when a remote loopback is taking place (i.e., when MII Register 21, bit 3, EN RPBK, is set).

In 100BASE-TX mode, when no signal or an invalid signal is detected on the receive pair, the link monitor will enter in the "link fail" state where only the scrambled idle code will be transmitted. When a valid signal is detected for a minimum period of time, the link monitor will then enter the link pass state when transmit and receive functions are entered.

In 100BASE-FX mode, the external fiber-optic receiver performs the signal energy detection function and communicates this information directly to the NetPHY-1LP device through the SDI+ pin.

Table 5. Code-Group Mapping

| MII (TXD[3:0]) | Name | PCS Code-Group | Interpretation                                                      |  |

|----------------|------|----------------|---------------------------------------------------------------------|--|

| 0 0 0 0        | 0    | 11110          | Data 0                                                              |  |

| 0 0 0 1        | 1    | 01001          | Data 1                                                              |  |

| 0010           | 2    | 10100          | Data 2                                                              |  |

| 0 0 1 1        | 3    | 10101          | Data 3                                                              |  |

| 0 1 0 0        | 4    | 01010          | Data 4                                                              |  |

| 0 1 0 1        | 5    | 01011          | Data 5                                                              |  |

| 0 1 10         | 6    | 01110          | Data 6                                                              |  |

| 0111           | 7    | 01111          | Data 7                                                              |  |

| 1000           | 8    | 10010          | Data 8                                                              |  |

| 1001           | 9    | 10011          | Data 9                                                              |  |

| 1010           | Α    | 10110          | Data A                                                              |  |

| 1011           | В    | 10111          | Data B                                                              |  |

| 1100           | С    | 11010          | Data C                                                              |  |

| 1101           | D    | 11011          | Data D                                                              |  |

| 1110           | E    | 11100          | Data E                                                              |  |

| 1111           | F    | 11101          | Data F                                                              |  |

| Undefined      | I    | 11111          | IDLE; used as inter-Stream fill code                                |  |

| 0101           | J    | 11000          | Start-of-Stream Delimiter, Part 1 of 2; always used in pairs with K |  |

| 0101           | К    | 10001          | Start-of-Stream Delimiter, Part 2 of 2; always used in pairs with J |  |

| Undefined      | Т    | 01101          | End-of-Stream Delimiter, Part 1 of 2; always used in pairs with R   |  |

| Undefined      | R    | 00111          | End-of-Stream Delimiter, Part 2 of 2; always used in pairs with T   |  |

| Undefined      | Н    | 00100          | Transmit Error; used to force signaling errors                      |  |

| Undefined      | V    | 00000          | Invalid Code                                                        |  |

| Undefined      | V    | 0 0 0 0 1      | Invalid Code                                                        |  |

| Undefined      | V    | 00010          | Invalid Code                                                        |  |

| Undefined      | V    | 00011          | Invalid Code                                                        |  |

| Undefined      | V    | 00101          | Invalid Code                                                        |  |

| Undefined      | V    | 00110          | Invalid Code                                                        |  |

| Undefined      | V    | 01000          | Invalid Code                                                        |  |

| Undefined      | V    | 01100          | Invalid Code                                                        |  |

| Undefined      | V    | 10000          | Invalid Code                                                        |  |

| Undefined      | V    | 11001          | Invalid Code                                                        |  |

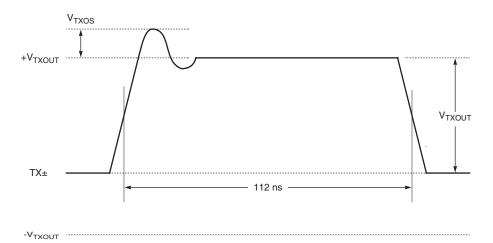

# MLT-3

This block is responsible for converting the NRZI data stream from the PDX block to the MLT-3 encoded data stream. The effect of MLT-3 is the reduction of energy on the copper media (TX or FX cable) in the critical frequency range of 1 MHz to 100 MHz. The receive section of this block is responsible for equalizing and amplifying the received data stream and link detection.

The adaptive equalizer compensates for the amplitude and phase distortion due to the cable.

MLT-3 is a tri-level signal. All transitions are between 0 V and +1 V or 0 V and -1 V. A transition has a logical value of 1 and a lack of a transition has a logical value of 0. The benefit of MLT-3 is that it reduces the maximum frequency over the data line. The bit rate of TX data is 125 Mbps. The maximum frequency (using

NRZI) is half of 62.5 MHz. MLT-3 reduces the maximum frequency to 31.25 MHz.

A data signal stream following MLT-3 rules is illustrated in Figure 2. The data stream is 1010101.

Figure 2. MLT-3 Waveform

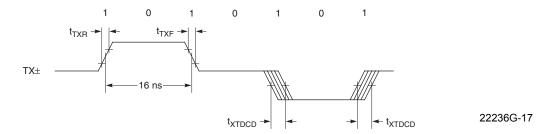

The TX± drivers convert the NRZI serial output to MLT-3 format. The RX± receivers convert the received MLT-3 signals to NRZI. The transmit and receive signals will be compliant with IEEE 802.3u, Section 25. The required signals (MLT-3) are described in detail in ANSI X3.263:1995 TP-PMD Revision 2.2 (1995).

The NetPHY-1LP device provides on-chip filtering. External filters are not required for either the transmit or receive signals. The traces from the transformer to the NetPHY-1LP device should have a controlled impedance as a differential pair of 100 ohms. The same is true between the transformer and the RJ-45 connector.

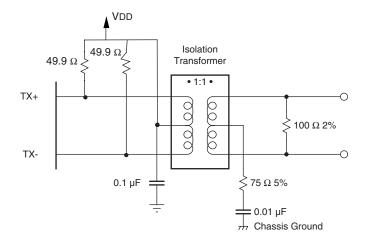

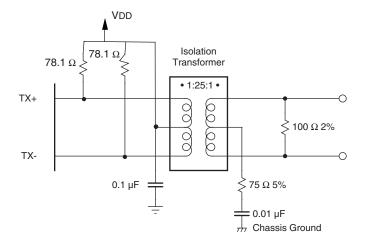

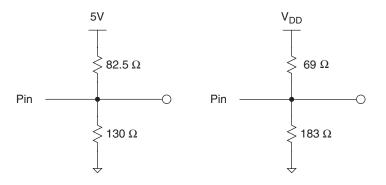

The TX± pins can be connected to the media via either a 1:1 transformer or a 1.25:1 transformer. The 1.25:1 ratio provides a 20% transmit power savings over the 1:1 ratio. Refer to Figure 3.

#### **Adaptive Equalizer**

The NetPHY-1LP device is designed to accommodate a maximum cable length of 140 meters UTP CAT-5 cable. 140 meters of UTP CAT-5 cable has an attenuation of 31 dB at 100 MHz. The typical attenuation of a 100 meter cable is 21 dB. The worst case attenuation is around 24-26 dB defined by TP-PMD.

The amplitude and phase distortion from the cable will cause intersymbol interference (ISI) which makes clock and data recovery impossible. The adaptive equalizer is made by closely matching the inverse transfer function of the twist-pair cable. This is a variable equalizer that changes its equalizer frequency response in accordance to cable length. The cable length is estimated based on comparisons of incoming signal strength against some of the known cable characteristics. The equalizer has a monotonical frequency response, and tunes itself automatically for any cable length to compensate for the amplitude and phase distortion incurred from the cable.

#### **Baseline Wander Compensation**

The 100BASE-TX data stream is not always DC balanced. The transformer blocks the DC component of the incoming signal, thus the DC offset of the differential receive inputs can wander. The shift in the signal levels, coupled with non-zero rise and fall times of the serial stream can cause pulse-width distortion. This creates jitter and a possible increase in error rates. Therefore, a DC restoration circuit is needed to compensate for the attenuation of the DC component.

The NetPHY-1LP device implements a patent-pending DC restoration circuit. Unlike the traditional implementation, it does not need the feedback information from the slicer and clock recovery circuit. This not only simplifies the system/circuit design, but also eliminates any random/systematic offset on the receive path. In 10BASE-T and 100Base-FX modes, the baseline wander correction circuit is not required and therefore will be bypassed.

22236G-5

Notes:

1. 49.9  $\Omega$  if a 1:1 isolation transformer is used or 78.1  $\Omega$  if a 1.25:1 isolation transformer is used.

2. 49.9  $\Omega$  is normal, but 54.9  $\Omega$  can be used for extended cable length operation.

Figure 3. TX± and RX± Termination for 100BASE-TX and 10BASE-T

#### Clock/Data Recovery

The equalized MLT-3 signal passes through a slicer circuit which then converts it to NRZI format. The Net-PHY-1LP device uses an analog phase-locked loop (APLL) to extract clock information from the incoming NRZI data. The extracted clock is used to re-time the data stream and set the data boundaries. The transmit clock is locked to the 25-MHz clock input, while the receive clock is locked to the incoming data streams.

When initial lock is achieved, the APLL switches to lock to the data stream, extracts a 125 MHz clock from it and use that for bit framing to recover data. The recovered 125 MHz clock is also used to generate the 25 MHz RX\_CLK. The APLL requires no external components for its operation and has high noise immunity and low jitter. It provides fast phase align (lock) to data in one transition and its data/clock acquisition time after power-on is less than 60 transitions.

The APLL can maintain lock on run-lengths of up to 60 data bits in the absence of signal transitions. When no valid data is present, i.e., when the SD is de-asserted, the APLL switches back to lock with TX\_CLK, thus providing a continuously running RX\_CLK.

The recovered data is converted from NRZI-to-NRZ and then to a 5-bit parallel format. The 5-bit parallel data is not necessarily aligned to 4B/5B code-group's symbol boundary. The data is presented to PCS at receive data register output, gated by the 25-MHz RX\_CLK.

#### **PLL Clock Synthesizer**

The NetPHY-1LP device includes an on-chip PLL clock synthesizer that generates a 125 MHz and a 25 MHz clock for the 100BASE-TX or a 100 MHz and 20 MHz clock for the 10BASE-T and Auto-Negotiation operations. Only one external 25 MHz crystal or a signal source is required as a reference clock.

After power-on or reset, the PLL clock synthesizer is defaulted to generating the 20 MHz clock output and will stay active until the 100BASE-X operation mode is selected.

#### **Clock and Crystal Inputs**

A 25 MHz crystal can be used for XTL± inputs to the NetPHY-1LP. The crystal should be parallel resonant and have a frequency stability of ±100 ppm and a frequency tolerance ±50 ppm. Recommended parts are

Ecliptek (EC-AT-25.000M, ECSM-AT-25.000M) and Epson (MA-505-25.000M).

Alternatively, a crystal oscillator can be used to source a clock on the REFCLK input. The oscillator must be 25 MHz ±50 ppm with a 40% to 60% duty cycle. Recommended parts are Ecliptek (EC1300 HSTS-25.000M) and Epson (MA506-25.000 MHz).

Note that PLL oscillators cannot be used for XTL± or REFCLK.

Using crystals or oscillators beyond these specifications will not guarantee successful operation of the NetPHY-1LP.

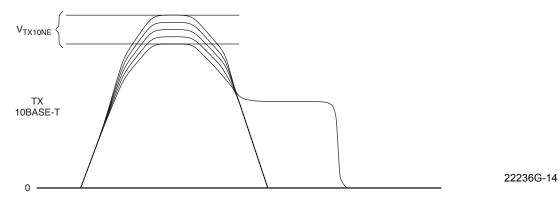

## 10BASE-T Block

The NetPHY-1LP transceiver incorporates the 10BASE-T physical layer functions, including clock recovery (ENDEC), MAUs, and transceiver functions. The NetPHY-1LP transceiver receives 10-Mbps data from the MAC, switch, or repeater across the MII at 2.5 million nibbles per second (parallel), or 10 million bits per second (serial). It then Manchester encodes the data before transmission to the network.

Refer to Figure 4 for the 10BASE-T transmit and receive data paths.

Figure 4. 10BASE-T Transmit /Receive Data Paths

#### **Twisted Pair Transmit Process**

In 10BASE-T mode, Manchester code will be generated by the 10BASE-T core logic, which will then be synthesized through the output waveshaping driver. This will help reduce any EMI emission, eliminating the need for an external filter. Data transmission over the

10BASE-T medium requires use of the integrated 10BASE-T MAU and uses the differential driver circuitry on the TX± pins.

TX± is a differential twisted-pair driver. When properly terminated, TX± meets the transmitter electrical requirements for 10BASE-T transmitters as specified in IEEE 802.3, Section 14.3.1.2. The load is a twisted pair cable that meets IEEE 802.3, Section 14.4.

The TX± signal is filtered on the chip to reduce harmonic content per Section 14.3.2.1 (10BASE-T). Since filtering is performed in silicon, TX± can be connected directly to a standard transformer. External filtering modules are not needed

#### **Twisted Pair Receive Process**

In 10BASE-T mode, the signal first passes through a third order Elliptical filter, which filters all the noise from the cable, board, and transformer. This eliminates the need for a 10BASE-T external filter. A Manchester decoder and a Serial-to-Parallel converter then follow to generate the 4-bit nibble in MII mode.

RX± ports are differential twisted-pair receivers. When properly terminated, each RX± port meets the electrical requirements for 10BASE-T receivers as specified in IEEE 802.3, Section 14.3.1.3. Each receiver has internal filtering and does not require external filter modules or common mode chokes.

Signals appearing at the RX± differential input pair are routed to the internal decoder. The receiver function meets the propagation delays and jitter requirements specified by the 10BASE-T standard. The receiver squelch level drops to half its threshold value after unsquelch to allow reception of minimum amplitude signals and to mitigate carrier fade in the event of worst case signal attenuation and crosstalk noise conditions.

#### **Twisted Pair Interface Status**

The NetPHY-1LP transceiver will power up in the Link Fail state. The Auto-Negotiation algorithm will apply to allow it to enter the Link Pass state. A link-pulse detection circuit constantly monitors the RX± pins for the presence of valid link pulses. In the Link Pass state, receive activity which passes the pulse width/amplitude requirements of the RX± inputs cause the PCS Control block to assert Carrier Sense (CRS) signal at the MII interface.

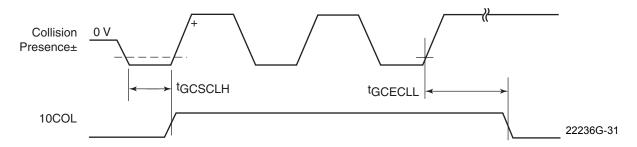

#### **Collision Detect Function**

Simultaneous activity (presence of valid data signals) from both the internal encoder transmit function and the twisted pair RX± pins constitutes a collision, thereby causing the PCS Control block to assert the COL pin at the MII.

Collisions cause the PCS Control block to assert the Carrier Sense (CRS) and Collision (COL) signals at the MII. In the Link Fail state, this block would cause the

PCS Control block to de-assert Carrier Sense (CRS) and Collision (COL).

#### **Jabber Function**

The Jabber function inhibits the 10BASE-T twisted pair transmit function of the NetPHY-1LP transceiver device if the TX± circuits are active for an excessive period (20-150 ms). This prevents one port from disrupting the network due to a *stuck-on* or faulty transmitter condition. If the maximum transmit time is exceeded, the data path through the 10BASE-T transmitter circuitry is disabled (although Link Test pulses will continue to be sent). The PCS Control block also asserts the COL pin at the MII and sets the Jabber Detect bit in MII Register 1. Once the internal transmit data stream from the MENDEC stops, an *unjab* time of 250-750 ms will elapse before this block causes the PCS Control block to de-assert the COL indication and re-enable the transmit circuitry.

When jabber is detected, this block causes the PCS control block to assert the COL pin and allows the PCS Control block to assert or de-assert the CRS pin to indicate the current state of the RX± pair. If there is no receive activity on RX±, this block causes the PCS Control block to assert only the COL pin at the MII. If there is RX± activity, this block causes the PCS Control block to assert both COL and CRS at the MII. The Jabber function can be disabled by setting MII Register 21, bit 12.

#### **Reverse Polarity Detection and Correction**