# CMOS 4-BIT MICROCONTROLLER

# TMP47C237AN

The 47C237A is based on the TLCS-47 CMOS series. The 47C237A has display on-screen circuit (OSD) to display bar which indicate channel or volume on TV screen, A/D converter input, D/A converter output which is suitable for application to the digital tuning system such as TV.

| PART No.    | ROM          | RAM         | PACKAGE |

|-------------|--------------|-------------|---------|

| TMP47C237AN | 2048 x 8-bit | 128 × 4-bit | SDIP30  |

#### **FEATURES**

- ◆4-bit single chip microcomputer

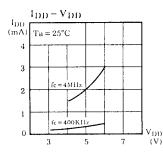

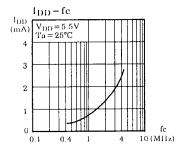

- ♦Instruction execution time: 1.9µs (at 4.2MHz)

- ♦89 basic instructions.

- ◆Table look-up instructions

- ◆Subroutine nesting: 15 levels max.

- ◆6 interrupt sources (External: 2, Internal: 4)

All sources have independent latches, and multiple interrupt control is available.

- ♦I/O port

- Input 2 ports 5 pins

I/O 5 ports 19 pins

- ♦Interval Timer

- ◆Two 12-bit Timer/Counter

Timer, event counter, and pulse width measurement mode

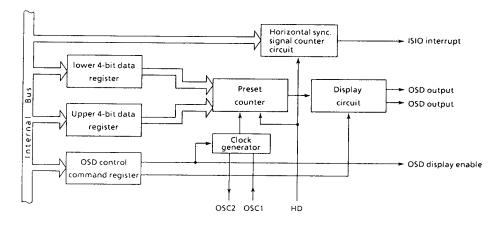

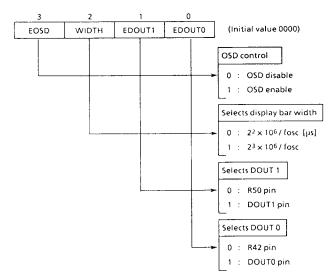

- ◆On-screen display circuit (bar display)

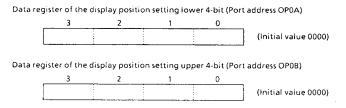

- Variable display position: horizontal 256 steps

- 2 colors

- 2 display bar width

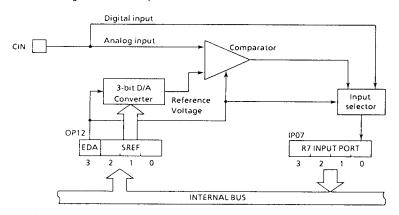

- ◆3-bit A/D converter input.

Auto frequency control signal (S-shaped curve) detection

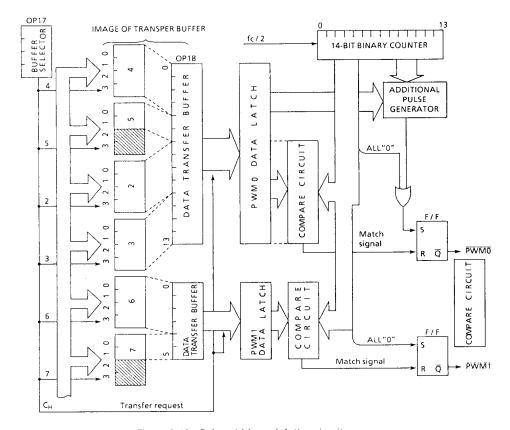

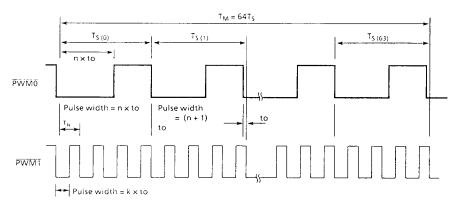

- ◆Pulse width modulation outputs

- 14-bit resolution 1 channel

- 6-bit resolution 1 channel

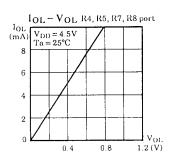

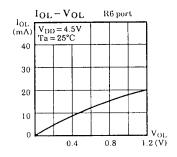

- ◆High current outputs

LED direct drive capability (typ. 10mA x 4bit)

◆Hold function

Battery / Capacitor back-up

◆Real Time Emulator : BM47C337A

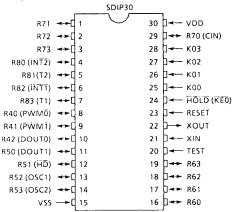

# PIN ASSIGNMENT (TOP VIEW)

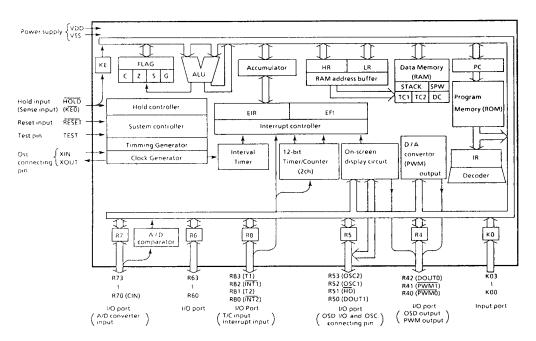

# **BLOCK DIAGRAM**

# PIN FUNCTION

| PIN NAME    | Input/Output  | FUNCTIONS                                                                        |                                  |  |  |

|-------------|---------------|----------------------------------------------------------------------------------|----------------------------------|--|--|

| K03-K00     | Input         | 4-bit input port                                                                 |                                  |  |  |

| R42 (DOUT0) |               | 3-bit I/O port with latch.                                                       | OSD output                       |  |  |

| R41 (PWM1)  | I/O (Input)   | When used as input port, D/A converter                                           | 6-bit D/A converter output       |  |  |

| R40 (PWM0)  |               | output pin and OSD output pin, the latch must be set to"1".                      | 14-bit D/A converter output      |  |  |

| R53 (O5C2)  | I/O (Output ) | A bit (/O more with load)                                                        |                                  |  |  |

| R52 (OSC1)  | I/O (Input)   | 4-bit I/O port with latch. When used as input port, resonator                    | Resonator connecting pin for OSD |  |  |

| R51 (ĤĎ)∙   | I/O (Input)   | connectting pin for and OSD output pin, the latch must be set to "1".            | Horizontal sync signal input     |  |  |

| R50 (DOUT1) | I/O (Output)  | _                                                                                | OSD output                       |  |  |

| R63-R60     | 1/0           | 4-bit I/O port with latch. When used as input port, the latch must be            | set to "1".                      |  |  |

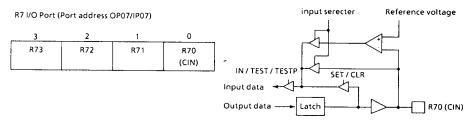

| R73-R71     | 1/0           | 4-bit I/O port with latch.                                                       |                                  |  |  |

| R70 (CIN)   | I/O (Input)   | When used as input port, AFC comparater input pin, the latch mast be set to "1". | AFC comparater input.            |  |  |

| R83 (T1)    |               | 4-bit i/O port with latch.                                                       | Timer/Counter 1 input            |  |  |

| R82 (INT1)  | . I/O (Input) | when used as input port, external                                                | External interrupt 1 input       |  |  |

| R81 (T2)    | (input)       | interrupt and timer / counter input pin, the latch mast be set to "1".           | Timer/Counter 2 external input   |  |  |

| R80 (ÎNT2)  |               |                                                                                  | External interrupt 2 input       |  |  |

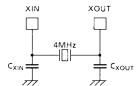

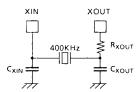

| XIN, XOUT   | input, Output | Resonator connecting pin. For inputting external clock, XIN is used and          | d XOUT is opened.                |  |  |

| RËSËT       | Input         | Reset signal input.                                                              |                                  |  |  |

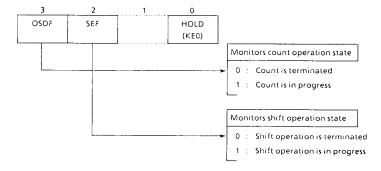

| HOLD (KEO)  | Input (input) | Hold request/release signal input                                                | Sense input                      |  |  |

| TEST        | Input         | Test pin for out-going test. Be opened or fix                                    | red to low level.                |  |  |

| VDD         |               | + 5V                                                                             |                                  |  |  |

| VSS         | Power supply  | 0V (GND)                                                                         |                                  |  |  |

#### OPERATIONAL DESCRIPTION

Concerning the 47C237A, the configuration and functions of hardwares are described.

As the description is porvided with priority on those parts differing from the 47C200A, the technical data sheets for the 47C200A shall also be referred to.

Note. The 47C237A have no serial port, differing from the 47C200A.

#### SYSTEM CONFIGURATION

(1) I/O Port

(4) R6 port

- (2) On-screen display (OSD) circuit

- (3) AFC comparator input.

- (4) D/A converter output.

# 2. PERIPHERAL HARDWARE FUNCTION

#### I/O Port 2.1

The 47C237A have 7 I/O Port(24 Pins)each as follow.

- ① K0 port ; 4-bit input

- ; 3-bit input/output (R42 pin is shared with OSD output. R41, R42 pins is shared by 2 R4 port

- D/A converter output)

- ; 4-bit input/output (R53, R52 pins is shared with Resonator connecting pin for OSD 3 R5 port

- R51, R50 pins is shared with I/O port.) ; 4-bit input/output

- ; 4-bit input/output (R70 pins is shared with AFC comparater input.) 5 R7 port

- ; 4-bit input/output (shared with external interrupt input and timer/counter input) 6: R8 port

- ; 1-bit sense input (shared with hold request/release signal input.) KE port

This section describes ports of ②, ③, ⑤ which are changed from the 47C200A.

The 47C237A has no P1, P2 and R9, therefore 5-bit 8-bit data conversion instruction [OUTB @HL] can not use.

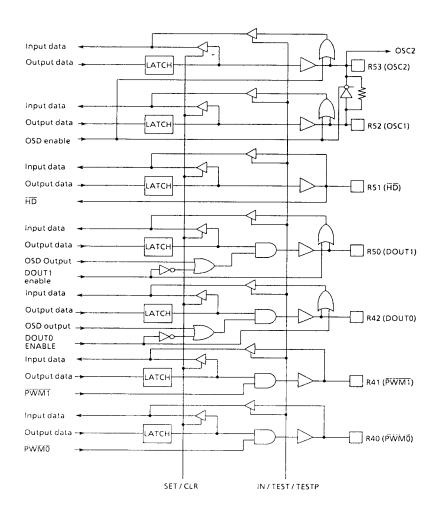

#### (1) Port R4 (R42-R40)

3-bit I/O port with latch. When used as input port, the latch must be set to "1". The latch is initialized to "1".

This pin is used both as R42 for OSD output, and as R40 and R41 for D/A converter output. When used for OSD output, select DOUT0 to enable OSD. To use for D/A converter, set the latch to "1".

Also, when this pin is used as R42 for OSD output, "1" is read in during the input instruction is executed. There is no R43 pin, but "1" is read in during the input instruction is executed.

# (2) Port R5 (R53-R50)

4-bit I/O port with latch. When used as input port, the latch must be set to "1" and OSD must be disable for R53, R52 and R50 pins. The latch is initialized to "1".

R53, R52 pins is shared by resonator connecting pin for OSD. When used as resonator connecting pin, the latch must be set to "1" and OSD must be enable.

This pin is also used as R51 for horizontal sync. signal input. To use this pin for horizontal sync. signal input, set the latch to "1". Like the R42 pin, the R50 pin is also used for OSD output. Also, when the input instruction is executed with the OSD display enabled, "1" is read into the R50, R52 and R53 pin, and horizontal sync. signal input is read into the R51 pin.

| Port R4 (Po | rt address Of   | P04 / IP04)   |               | Port R5 (Port | address OP05  | /iP05)    |

|-------------|-----------------|---------------|---------------|---------------|---------------|-----------|

| 3           | 2               | 1             | 0             | 3             | 2             | 1         |

|             | R42<br>(DOU F0) | R41<br>(PWM1) | R40<br>(PWM0) | R53<br>(OSC2) | R52<br>(OSC1) | R5<br>(HI |

| . 3    | 2      | 1    | 0       |   |

|--------|--------|------|---------|---|

| R53    | R52    | R51  | R50     | ] |

| (OSC2) | (OSC1) | (HD) | (DOUT1) | Į |

Figure 2-1. Ports R4 and R5

| address  (**) Inp  004 K0 input port. 02 03 03 04 R4 input port 05 R5 input port 06 R6 input port 07 R7 input port 09 R8 input port 00 R8 input port 00 R8 input port 00 R8 input port 00 R9 inpu | ut (IP++)                       | Output (OP**)  4 output port 5 output port 7 output port 8 output port 8 output port 10 postion lower 4-bits 50 position lower 4-bits 50 control            | N N N N N N N N N N N N N N N N N N N   | OUT A,%p                               | 00 % % % % % % % % % % % % % % % % % % | OUT8 @HL      | SET %p,b | TEST %p,b<br>TESTP %p,b | SET @L<br>CLR @L<br>TEST@L |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------|----------------------------------------|---------------|----------|-------------------------|----------------------------|

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | R4 output port R5 output port R6 output port R7 output port R7 output port R8 output port C0SD position lower 4-bits OSD position uper 4-bits OSD control   | 0 + + + + + + + + + + + + + + + + + + + |                                        | 11110000                               |               |          | 0                       |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | R4 output port R5 output port R6 output port R7 output port R7 output port R8 output port OSD position lower 4-bits OSD position uper 4-bits                | 11100000111                             | :::::::::::::::::::::::::::::::::::::: | 1110000                                |               | 114000   | ,                       | ,                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | R4 output port R5 output port R6 output port R7 output port R7 output port R8 output port C0SD position lower 4-bits OSD position uper 4-bits OSD control   | + + 000000 + + +                        | OOOOO_C                                | 110000                                 | 1 4 1 3 1 1 1 | 1.000    | ı                       | 1                          |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | R4 output port R5 output port R6 output port R7 output port R8 output port R8 output port C0SD position lower 4-bits OSD position uper 4-bits OSD control   | 100000111                               | 1000010                                | 10000                                  | 1 1 1 1 1     | 1000     | ı                       | ı                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | R4 output port R5 output port R6 output port R7 output port R8 output port R8 output port R9 output port OSD position lower 4-bits OSD position uper 4-bits | 00000                                   | 0000010                                | 0000                                   | 1 1 1 1       | 000      | ı                       | ı                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | R5 output port R6 output port R7 output port R8 output port R8 output port OSD position lower 4-bits OSD control                                            | 0000                                    | 0000+0                                 | 000                                    | }             | 00       | 0                       | 0                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | R6 output port R7 output port R8 output port C0SD position lower 4-bits OSD costion uper 4-bits                                                             | 000+++                                  | 000+0                                  | 00                                     | 1 1 1         | 0        | 0                       | 0                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | R8 output port R8 output port OSD position lower 4-bits OSD position uper 4-bits OSD control                                                                | 00111                                   | 00+0                                   | (                                      | 1 1           |          | 0                       | 0                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | R8 output port  OSD position lower 4-bits OSD position uper 4-bits OSD control                                                                              | 0                                       | 0 + 0                                  | )                                      | •             | ()·      | 0                       | 0                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | OSD position lower 4-bits OSD position uper 4-bits OSD control                                                                                              | 1 1 1                                   | + C                                    | 0                                      |               | 0        | 0                       | 1                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | OSD position lower 4-bits OSD position uper 4-bits OSD control                                                                                              | 1 1                                     | C                                      | 1 1                                    | 1             | 1        | ı                       | ı                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | OSD position uper 4-bits<br>OSD control                                                                                                                     | 1                                       | )                                      | 0                                      | í             | 1        | i                       | ı                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | OSD control                                                                                                                                                 |                                         | 0                                      | 0                                      | :             | ı        | 1                       | ı                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |                                                                                                                                                             | ı                                       | 0                                      | 0                                      | •             | ı        | 1                       | 1                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | -                                                                                                                                                           | 1                                       | 1                                      |                                        | ı             |          | ,                       | 1                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                               |                                                                                                                                                             | 0                                       | i                                      | ı                                      | ı             | ı        | 0                       | ı                          |

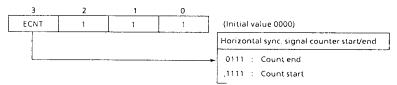

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Horizontal sync. signal counter |                                                                                                                                                             | 0                                       | ı                                      | ı                                      | ı             | 1        | ı                       | ı                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | HOLD control                                                                                                                                                |                                         | 0                                      | ı                                      |               | -        | -                       | -                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |                                                                                                                                                             | ı                                       | 1                                      | ı                                      | ı             | 1        | ,                       | ı                          |

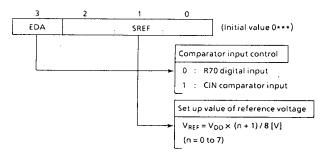

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | AFC comparator input control                                                                                                                                | 1                                       | 0                                      | 1                                      | ı             | 1        | 1                       | 1                          |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |                                                                                                                                                             | 1                                       | 1                                      | ı                                      | ı             | ı        | ı                       | •                          |

| 14 Undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | 1                                                                                                                                                           | ı                                       | ı                                      | 1                                      | ı             | 1        | ı                       | ı                          |

| 15 Undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | 1                                                                                                                                                           | 1                                       | 1                                      | ı                                      | 1             | ı        | ı                       | ı                          |

| 16 Undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | 1                                                                                                                                                           | r                                       | 1                                      | ı                                      | 1             | 1        | ı                       | ı                          |

| 17 Undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | PWM buffer                                                                                                                                                  | ı                                       | 0                                      | 1                                      | 1             | 1        | 1                       | 1                          |

| 18 Undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | PWM data transfer buffer                                                                                                                                    | ı                                       | 0                                      | 1                                      | 1             | 1        | 1                       | ı                          |

| 19 Undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | Interval Timer interrupt control                                                                                                                            | 1                                       | 0                                      | 1                                      | ,             | ,        | 1                       | ı                          |