## Miniature KNX transceiver with voltage regulators and microcontroller support

VFQFPN24 (4 x 4 x 1.0 mm, 0.5 mm pitch)

### **Features**

- Very thin fine pitch 4 x 4 mm VQFNPN24 package

- KNX certified, KNX TP1-256 supported

- · Easy interface to microcontroller

- · Very small system solution

- Two integrated voltage regulators for external use in application

- Selectable 3.3 V / 5 V 20 mA linear regulator

- Adjustable 1 V to 12 V 150 mA high- efficiency DC/DC step down switching converter

- KNX bus power extractor supporting bus current up to 30 mA

- · Adjustable KNX bus current slew rate dl/dt

- No crystal required

- Operating temperature range -40 °C to +85 °C

### **Applications**

KNX twisted pair network (KNX TP1-256)

### **Description**

The STKNX is a transceiver device for KNX TP communication. The small package and few external components enable very compact KNX node design.

The simple interface to the microcontroller allows easy replacement of physical layer discrete component implementations.

The STKNX device features two integrated voltage regulators for external use in the application: the selectable  $3.3\ V\ /\ 5\ V\ -\ 20\ mA$  linear regulator and the adjustable 1 V to 12 V - 150 mA high-efficiency DC/DC step down switching converter.

The integrated KNX bus power extractor supports bus current up to 30 mA to power external devices and the STKNX transceiver's own power needs, while limiting the bus current slew rate according to KNX specifications.

The STKNX ensures safe coupling to the bus and provides the bus monitoring warning for the loss of bus power.

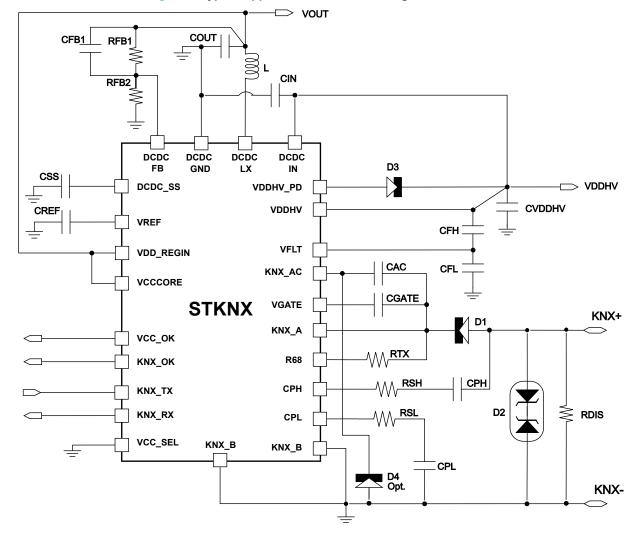

## 1 Typical application circuit and block diagram

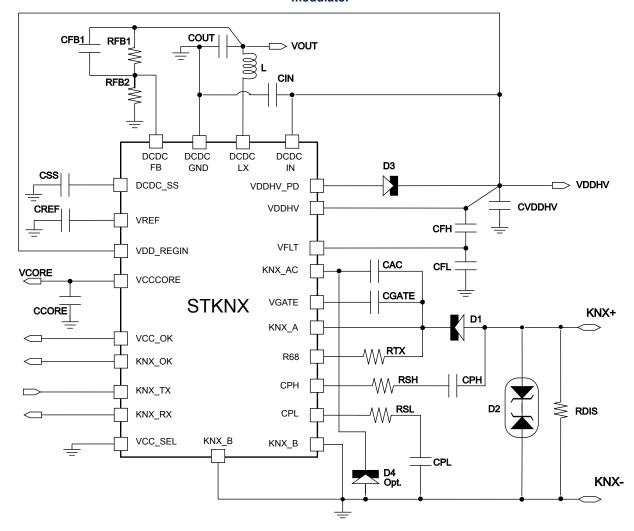

### 1.1 Typical application circuit

Figure 1. Typical application circuit, buck converter enabled, linear regulator supplied by impedance modulator

Note: VOUT range 1 V - 12 V.

VCORE selectable to 3.3 V / 5 V through VCC\_SEL (3.3 V in the example).

DS12399 - Rev 3 page 2/27

→ VOUT CFB1 COUT RFB1 CIN RFB2 DCDC DCDC DCDC DCDC D3 FΒ GND LX DCDC\_SS VDDHV\_PD > VDDHV CVDDHV **VDDHV CREF VREF** CFH VFLT VDD\_REGIN CAC **CFL** KNX\_AC **VCORE** VCCCORE **CGATE VGATE STKNX** CCORE KNX+ KNX\_A VCC\_OK R68 KNX\_OK CPH СРН KNX\_TX D2 RDIS KNX\_RX CPL VCC\_SEL KNX\_B KNX\_B CPL KNX-

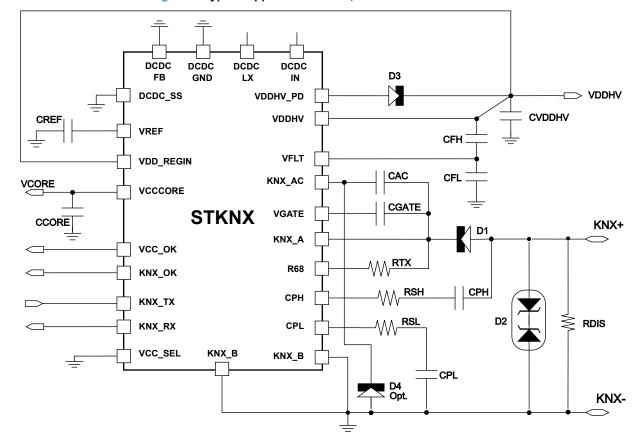

Figure 2. Typical application circuit, buck converter enabled, linear regulator supplied by buck converter

Note: The VOUT level needs to be compliant with VDD\_REGIN recommended operating conditions. VCORE selectable to 3.3 V / 5 V through VCC\_SEL (3.3 V in the example).

DS12399 - Rev 3 page 3/27

Figure 3. Typical application circuit, buck converter disabled

Note: VCORE selectable to 3.3 V / 5 V through VCC\_SEL (3.3 V in the example).

DS12399 - Rev 3 page 4/27

Figure 4. Typical application circuit, linear regulator disabled

Note: The VOUT level needs to be compliant with VCCCORE recommended operating conditions. VCC\_SEL needs to be set according to the VCCCORE level (3.3 V in the example).

Table 1. External components typical value

| Reference | Туре                 | Typ. value Rating |                           | Description                                             |

|-----------|----------------------|-------------------|---------------------------|---------------------------------------------------------|

|           |                      | Capaci            | itors                     |                                                         |

| СРН       | MLCC                 | 100 nF            | V <sub>RATED</sub> ≥ 50 V | Equalizer storage capacitor                             |

| CPL       | MLCC                 | 100 nF            | V <sub>RATED</sub> ≥ 50 V | Equalizer storage capacitor                             |

| CGATE     | MLCC or electrolytic | 10 μF - 47 μF     | V <sub>RATED</sub> ≥ 10 V | Impedance modulator storage capacitor - see Table 7     |

| CAC       | MLCC                 | 10 nF             | V <sub>RATED</sub> ≥ 50 V | Bus AC coupling capacitor                               |

| CVDDHV    | Electrolytic         | ≥ 100 µF          | V <sub>RATED</sub> ≥ 35 V | Impedance modulator output bulk capacitor - see Table 7 |

| CFH       | MLCC                 | 47 nF             | V <sub>RATED</sub> ≥ 35 V | Impedance modulator compensation capacitor              |

DS12399 - Rev 3 page 5/27

| Reference | Туре           | Typ. value                                                            | Rating                                                           | Description                                                                                            |

|-----------|----------------|-----------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| CFL       | MLCC           | 47 nF                                                                 | V <sub>RATED</sub> ≥ 35 V                                        | Impedance modulator compensation capacitor                                                             |

| CIN       | MLCC           | 10 μF                                                                 | V <sub>RATED</sub> ≥ 35 V                                        | Buck converter input decoupling capacitor                                                              |

| COUT      | MLCC           | 22 μF                                                                 | V <sub>RATED</sub> > V <sub>OUT</sub>                            | Buck converter output capacitor                                                                        |

| CSS       | MLCC           | 10 nF - 470 nF                                                        | V <sub>RATED</sub> ≥ 6.3 V                                       | Buck converter soft-start time programming capacitor - see Eq. (3)                                     |

| CREF      | MLCC           | 470 nF                                                                | V <sub>RATED</sub> ≥ 35 V                                        | VREF decoupling capacitor                                                                              |

| CCORE     | MLCC           | 4.7 μF                                                                | V <sub>RATED</sub> ≥ 6.3 V                                       | Linear regulator output capacitor                                                                      |

| CFB1      | MLCC           | 1/(2π * RFB1 * 28 kHz)<br>NM if RFB1 = 0 Ω                            | V <sub>RATED</sub> ≥ 16 V                                        | Buck converter compensation capacitor                                                                  |

|           |                | Resist                                                                | tors                                                             |                                                                                                        |

| RDIS      | Resistor       | 4.7 ΜΩ                                                                | -                                                                | Reverse polarity discharging resistor                                                                  |

| RSH       | Resistor       | 1 kΩ                                                                  | -                                                                | Series resistor to CPH                                                                                 |

| RSL       | Resistor       | 1 kΩ                                                                  | -                                                                | Series resistor to CPL                                                                                 |

| RTX       | Resistor       | 68 Ω                                                                  | P <sub>DISS</sub> ≥ 1 W                                          | Tx current limiting resistor                                                                           |

| RFB1      | Resistor       | (V <sub>OUT</sub> / 1 V - 1) * RFB2<br>0 Ω for V <sub>OUT</sub> = 1 V | -                                                                | Buck converter output voltage adjusting resistor                                                       |

| RFB2      | Resistor       | 10 kΩ typ. (< 100 kΩ)<br>NM for $V_{OUT} = 1 V$                       | -                                                                | Buck converter output voltage adjusting resistor                                                       |

|           |                | Induct                                                                | tors                                                             |                                                                                                        |

| L         | Power inductor | 33 μΗ                                                                 | I <sub>R</sub> > 150 mA<br>I <sub>SAT</sub> > 550 mA             | Buck converter output inductor                                                                         |

|           |                | Diod                                                                  | es                                                               |                                                                                                        |

| D1        | Diode          | LL4148 or equivalent                                                  | $V_{BR} > 50 \text{ V}$<br>$V_{F} (50 \text{ mA}) < 1 \text{ V}$ | Input diode (protection from reverse polarity connection)                                              |

| D2        | TVS            | SMAJ40CA or lower clamping voltage                                    | -                                                                | Transient voltage suppressor diode                                                                     |

| D3        | Diode          | LL4148 or equivalent                                                  | V <sub>BR</sub> > 50 V<br>V <sub>F</sub> (50 mA) < 1 V           | Output diode                                                                                           |

| D4        | Diode          | LL4148 or equivalent                                                  | V <sub>BR</sub> > 50 V<br>V <sub>F</sub> (50 mA) < 1 V           | Optional KNX_AC clamping diode.<br>Recommended for noise immunity<br>improvement in noisy environment. |

DS12399 - Rev 3 page 6/27

## 1.2 Block diagram

Figure 5. STKNX Block diagram DCDC DCDC KNX\_A FΒ VGATE Step-down switching DCDC IN VREF Internal Impedance VDDHV\_PD ( supply Modulator & ref. converter VDDHV VFLT ( DCDC LX CP\_H ( Pulse **Equalizer** DCDC GND CP\_L VDD\_REGIN **STKNX** Lin. Reg. Transmitter VCCCORE R68 Logic Level VCC\_OK Receiver Interface KNX\_OK KNX\_AC ( KNX\_RX KNX\_TX VCCSEL

KNX\_B

DS12399 - Rev 3 page 7/27

# 2 Pin connection and pin description

### 2.1 Pin connection

Figure 6. Pin connection (top view)

## 2.2 Pin description

Table 2. STKNX Pin description

| Pin | Pin name  | Function                                                                                                       |

|-----|-----------|----------------------------------------------------------------------------------------------------------------|

| 1   | VDD_REGIN | Linear regulator supply input. Short to VCCCORE to disable the linear regulator and supply VCCCORE externally. |

| 2   | KNX_AC    | BUS AC-coupled sense for the Rx input and Tx feedback. DC biased to 9.7 V typ.                                 |

| 3   | R68       | KNX transmitter output                                                                                         |

| 4   | KNX_B     | Analog ground                                                                                                  |

| 5   | CP_H      | Equalization cap connection to KNX supply (KNX+)                                                               |

| 6   | CP_L      | Equalization cap connection to KNX ground (KNX-)                                                               |

| 7   | VFLT      | Impedance modulator compensation                                                                               |

| 8   | VREF      | Impedance modulator reference                                                                                  |

| 9   | VDDHV     | VDDHV supply input and impedance modulator feedback                                                            |

| 10  | VDDHV_PD  | Impedance modulator power output                                                                               |

| 11  | KNX_A     | KNX power supply input (KNX+)                                                                                  |

| 12  | KNX_B     | Analog ground                                                                                                  |

| 13  | VGATE     | Impedance modulator storage capacitor connection                                                               |

DS12399 - Rev 3 page 8/27

| Pin | Pin name    | Function                                                                                                                                                                            |  |  |  |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 14  | DCDC_IN     | Step down converter supply input. Short to ground or leave floating to disable the switching converter.                                                                             |  |  |  |

| 15  | DCDC_LX     | Step down converter switching output                                                                                                                                                |  |  |  |

| 16  | DCDC_GND    | Step down converter power ground                                                                                                                                                    |  |  |  |

| 17  | DCDC_SS     | Step down converter soft-start programming pin                                                                                                                                      |  |  |  |

| 18  | DCDC_FB     | Step down converter feedback input. Sets output voltage (1 V - 12 V range) through the resistor divider.                                                                            |  |  |  |

| 19  | VCC_OK      | VCCCORE power good CMOS digital output                                                                                                                                              |  |  |  |

| 20  | VCCCORE     | Linear regulator output (3.3 V / 5 V selectable). Supply voltage for digital I/O.                                                                                                   |  |  |  |

| 21  | KNX_OK      | KNX bus power good CMOS digital output                                                                                                                                              |  |  |  |

| 22  | VCC_SEL     | Selects linear regulator output voltage. Internally pulled down (6 µA typ.).                                                                                                        |  |  |  |

|     | VCC_SLL     | Tie to VCCCORE to select 5 V. Short to ground or leave floating to select 3.3 V.                                                                                                    |  |  |  |

| 23  | KNX_RX      | Receiver CMOS digital output                                                                                                                                                        |  |  |  |

| 24  | KNX_TX      | Transmitter digital input. Internally pulled down (6 μA typ.).                                                                                                                      |  |  |  |

|     |             | Connect to analog ground.                                                                                                                                                           |  |  |  |

| -   | Exposed pad | For thermal optimization, maximize the area of the ground layer on which the exposed pad is soldered and provide good thermal connection with the bottom ground layer through vias. |  |  |  |

DS12399 - Rev 3 page 9/27

# 3 Thermal characteristics

**Table 3. Thermal characteristics**

| Symbol            | Parameter                                            | Test condition                                                                                          | Value      | Unit |

|-------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------|------|

| T <sub>J</sub>    | Maximum operating junction temperature               | -                                                                                                       | 110        | °C   |

| T <sub>AMB</sub>  | Operating ambient temperature                        | -                                                                                                       | -40 to 85  | °C   |

| T <sub>STG</sub>  | Storage temperature                                  | -                                                                                                       | -50 to 150 | °C   |

| R <sub>thJA</sub> | Thermal resistance junction to ambient, steady state | Mounted on a 2s2p PCB, with a dissipating surface connected through vias on the bottom side of the PCB. | 35         | °C/W |

DS12399 - Rev 3 page 10/27

# 4 Electrical specifications

## 4.1 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Symbol          | Parameter                                           | Min.                        | Max.                      | Unit |

|-----------------|-----------------------------------------------------|-----------------------------|---------------------------|------|

| KNX_A           | KNX supply input                                    | -0.3                        | 45                        | V    |

| VDD_REGIN       | Linear regulator supply input                       | -0.3                        | 40                        | V    |

| VDDHV           | VDDHV supply input and impedance modulator feedback | -0.3                        | 40                        | V    |

| VREF            | Impedance modulator reference                       | -0.3                        | 40                        | V    |

| KNX_B, DCDC_GND | Variation between different ground pins             | -0.3                        | 0.3                       | V    |

| CP_H            | Equalizing cap. high                                | -0.3                        | KNX_A + 0.3               | V    |

| CP_L            | Equalizing cap. low                                 | -0.3                        | KNX_A + 0.3               | V    |

| R68             | KNX transmitter output                              | -0.3                        | KNX_A + 0.3               | V    |

| KNX_AC          | BUS AC-coupled sense                                | -0.3                        | KNX_A + 0.3               | V    |

| VDDHV_PD        | Impedance modulator power output                    | -0.3                        | KNX_A + 0.3               | V    |

| VGATE           | Impedance modulator coupling cap.                   | Max. (-0.3,<br>KNX_A - 7.2) | KNX_A + 0.3               | V    |

| VCCCORE         | Linear reg. output. I/O supply.                     | -0.3                        | 5.5                       | V    |

| KNX_TX          | Transmitter digital input                           | -0.3                        | Min. (5.5, VCCCORE + 0.3) | V    |

| KNX_RX          | Transmitter digital output                          | -0.3                        | Min. (5.5, VCCCORE + 0.3) | V    |

| KNX_OK          | KNX bus power good                                  | -0.3                        | Min. (5.5, VCCCORE + 0.3) | V    |

| VCC_SEL         | 3.3 V / 5 V selection for linear reg.               | -0.3                        | Min. (5.5, VCCCORE + 0.3) | V    |

| VCC_OK          | VCCCORE power good                                  | -0.3                        | Min. (5.5, VCCCORE + 0.3) | V    |

| VFLT            | Impedance modulator compensation                    | -0.3                        | 5.5                       | V    |

| DCDC_IN         | Step down converter input                           | -0.3                        | 40                        | V    |

| DCDC_LX         | Step down converter switching node                  | -0.3                        | Min. (40, DCDC_IN + 0.3)  | V    |

| DCDC_FB         | Step down converter feedback                        | -0.3                        | 3.6                       | V    |

| DCDC_SS         | Step down converter soft-start programming pin      | -0.3                        | 3.6                       | V    |

## 4.2 Recommended operating conditions

Table 5. Recommended operating conditions

| Symbol    | Parameter                                    | Test condition         | Min. | Max. | Unit |

|-----------|----------------------------------------------|------------------------|------|------|------|

| KNX_A     | KNX supply input <sup>(1)</sup>              | -                      | 20   | 32   | V    |

| VCCCORE   | I/O supply and linear reg. output            | -                      | 3    | 5.5  | V    |

| DCDC_IN   | Step down converter input                    | -                      | 13   | 32   | V    |

| VDD_REGIN | Linear regulator supply input <sup>(2)</sup> | VCC_SEL shorted to GND | 6.8  | 32   | V    |

DS12399 - Rev 3 page 11/27

| Symbol                | Parameter                                                   | Test condition             | Min. | Max. | Unit |

|-----------------------|-------------------------------------------------------------|----------------------------|------|------|------|

| VDD_REGIN             | Linear regulator supply input <sup>(2)</sup>                | VCC_SEL shorted to VCCCORE | 8.5  | 32   | V    |

| I <sub>VDDHV_PD</sub> | Continuous output current from VDDHV pin <sup>(3)</sup>     | -                          | -    | 30   | mA   |

| I <sub>REG</sub>      | Continuous output current from VCCCORE pin <sup>(3)</sup>   | -                          | -    | 20   | mA   |

| I <sub>DCDC</sub>     | Continuous output current from DCDC switching converter (3) | -                          | -    | 150  | mA   |

- 1. Indicates DC value. With the active and equalization pulse bus voltage must be between 11 V and 45 V.

- 2. Short VDD\_REGIN to VCCCORE to disable the internal linear regulator and provide VCCCORE voltage externally.

- 3. The maximum current capability refers to the voltage regulator only. The usable current capability can be limited by the KNX bus current consumption specification.

### 4.3 Electrical characteristics

**Table 6. Electrical characteristics**

Parameters given for a device operating within the recommended operating conditions, unless otherwise specified. Typical values are referred to  $T_J = 27 \, ^{\circ}\text{C}$ .

| Symbol                           | Parameter                                            | Conditions                                                                                                                                   | Min. | Тур. | Max. | Unit |

|----------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                                  |                                                      | Power supply                                                                                                                                 |      |      |      |      |

| V(KNX_A)                         | DC supply voltage on KNX_A pin                       | Excluding active and equalization pulse                                                                                                      | 20   | -    | 32   | V    |

|                                  | Bus current consumption, no load                     | V(KNX_A) = 32 V, no activity on bus, no transmission, no external load                                                                       | -    | 1    | -    | mA   |

| I(KNX_A)                         | Bus current consumption, 30 mA load                  | V(KNX_A) = 32 V, no activity on<br>bus, no transmission, 30 mA load<br>on VDDHV rail (including linear<br>regulator and switching converter) | -    | 31   | -    | mA   |

| KNX_OK <sub>RIS</sub><br>(VREF)  | KNX_OK rising threshold referred to VREF voltage     | VREF rising                                                                                                                                  | -    | -    | 13.5 | V    |

| KNX_OK <sub>FALL</sub><br>(VREF) | KNX_OK falling threshold referred to VREF voltage    | VREF falling                                                                                                                                 | 9.7  | -    | -    | V    |

| KNX_OK <sub>HYST</sub><br>(VREF) | KNX_OK hysteresis referred to VREF voltage           | -                                                                                                                                            | -    | 1.4  | -    | V    |

| KNX_OK <sub>RIS</sub><br>(KNX_A) | KNX_OK rising threshold referred to KNX_A DC voltage | KNX_A rising slowly, VREF settled                                                                                                            | -    | -    | 18.5 | V    |

|                                  | Imp                                                  | pedance modulator                                                                                                                            |      |      |      |      |

| VDDHV drop                       | V(KNX_A) - V(VDDHV) voltage drop                     | V(KNX_A) = 20 V DC<br>I <sub>LOAD</sub> = 5 mA<br>D3 = LL4148 or equivalent                                                                  | -    | -    | 6.5  | V    |

| VDDHV drop                       | V(KNX_A) - V(VDDHV) voltage drop                     | V(KNX_A) = 20 V DC,<br>I <sub>LOAD</sub> = 30 mA,<br>D3 = LL4148 or equivalent                                                               | -    | -    | 7.2  | V    |

| VREF drop                        | V(KNX_A) - V(REF)<br>voltage drop                    | V(KNX_A) = 20 V DC, VREF settled                                                                                                             | 3    | 4.3  | 5    | V    |

|                                  | VCCCORE                                              | oltage and linear regulator                                                                                                                  |      |      |      |      |

| VCCCORE                          | Regulated voltage                                    | VCC_SEL shorted to GND                                                                                                                       | 3    | 3.3  | 3.6  | V    |

| VOCCORE                          | regulated voltage                                    | VCC_SEL shorted to VCCCORE                                                                                                                   | 4.5  | 5    | 5.5  | V    |

| VCC_OK <sub>RIS</sub>            | VCC_OK rising threshold                              | VCC_SEL shorted to GND                                                                                                                       | 2.3  | -    | 2.8  | V    |

DS12399 - Rev 3 page 12/27

| Symbol                 | Parameter                                             | Conditions                                                                                                                    | Min. | Тур. | Max. | Unit     |

|------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| VCC_OK <sub>RIS</sub>  | VCC_OK rising threshold                               | VCC_SEL shorted to VCCCORE                                                                                                    | 3.3  | -    | 4    | V        |

| \(\(\alpha\)           | 1400 0146 111 11 11 11                                | VCC_SEL shorted to GND                                                                                                        | 2.0  | -    | 2.5  | V        |

| VCC_OK <sub>FALL</sub> | VCC_OK falling threshold                              | VCC_SEL shorted to VCCCORE                                                                                                    | 2.9  | -    | 3.6  | V        |

| VCC OK                 | 1/00 0/41 1                                           | VCC_SEL shorted to GND                                                                                                        | -    | 0.3  | -    | V        |

| VCC_OK <sub>HYST</sub> | VCC_OK hysteresis                                     | VCC_SEL shorted to VCCCORE                                                                                                    | -    | 0.4  | -    | V        |

| I <sub>VCCSEL</sub>    | VCCSEL internal pull- down current                    | -                                                                                                                             | -    | 6    | -    | μA       |

|                        | Programmable                                          | e DC-DC switching converter                                                                                                   |      |      |      |          |

| V <sub>IN</sub>        | Input voltage at DCDC_IN pin                          | -                                                                                                                             | 13   | -    | 32   | V        |

| V <sub>OUT</sub>       | Output voltage adjusting range                        | -                                                                                                                             | 1    | -    | 12   | V        |

| V <sub>FB</sub>        | Feedback voltage reference                            | -                                                                                                                             | 0.9  | 1    | 1.1  | V        |

| UVLO <sub>RIS</sub>    | Undervoltage lockout rising threshold on VIN voltage  | V <sub>IN</sub> rising                                                                                                        | 9    | 10   | 11   | V        |

| UVLO <sub>FALL</sub>   | Undervoltage lockout falling threshold on VIN voltage | V <sub>IN</sub> falling                                                                                                       | 5.4  | 6    | 6.6  | V        |

| UVLO <sub>HYST</sub>   | Undervoltage lockout hysteresis on VIN voltage        | -                                                                                                                             | -    | 4    | -    | V        |

| I <sub>LIM</sub>       | High side MOSFET current limit                        | -                                                                                                                             | 325  | 650  | 975  | mA       |

| V <sub>OUT_RIP</sub>   | Output voltage ripple                                 | 13 V < $V_{IN}$ < 32 V<br>3.3 V < $V_{OUT}$ < 12 V<br>$I_{OUT}$ = 5 mA ~ 150 mA<br>$C_{OUT}$ = 22 $\mu$ F MLCC <sup>(1)</sup> | -    | 50   | -    | mV       |

| R <sub>DS(ON)</sub>    | High side MOSFET on resistance                        | -                                                                                                                             | -    | 1.9  | -    | Ω        |

| ,                      | Low side MOSFET on resistance                         | -                                                                                                                             | -    | 1.2  | -    |          |

| ОТР                    | Overtemperature protection                            | Junction temperature <sup>(2)</sup>                                                                                           | 110  | 140  | -    | °C       |

| OVP <sub>RIS</sub>     | Overvoltage protection rising threshold on FB         | FB voltage rising                                                                                                             | 1.1  | 1.25 | 1.4  | V        |

| OVP <sub>FALL</sub>    | Overvoltage protection falling threshold on FB        | FB voltage falling                                                                                                            | 0.95 | 1.1  | 1.25 | V        |

| I <sub>SS</sub>        | Current sourced from SS pin                           | During soft-start                                                                                                             | -    | 2.5  | -    | μA       |

|                        |                                                       | Transmitter                                                                                                                   |      |      |      |          |

| R <sub>DS(ON)</sub>    | Tx MOSFET on resistance                               | -                                                                                                                             | -    | 5    | -    | Ω        |

| I <sub>KNX_TX</sub>    | KNX_TX internal pull- down current                    | -                                                                                                                             | -    | 6    | -    | μΑ       |

|                        |                                                       | Digital I/Os                                                                                                                  |      |      |      |          |

|                        | Maximum voltage level that will                       | VCCCORE = 3.3 V                                                                                                               | 0.7  | -    | -    |          |

| $V_{IL}$               | be interpreted as a logic 0                           | VCCCORE = 5 V                                                                                                                 | 1.2  | -    | -    | V        |

|                        | Minimum voltagelevel that will be                     | VCCCORE = 3.3 V                                                                                                               | -    | -    | 2.2  | <b>+</b> |

| $V_{IH}$               | interpreted as a logic 1                              | VCCCORE = 5 V                                                                                                                 | -    | -    | 3    | V        |

|                        |                                                       | VCCCORE = 3.3 V<br>I <sub>SUNK</sub> = 300 μA                                                                                 | 0    | -    | 0.4  | V        |

| V <sub>OL</sub>        | Logic low output level                                | VCCCORE = 5 V<br>I <sub>SUNK</sub> = 400 μA                                                                                   | 0    | -    | 0.4  | V        |

DS12399 - Rev 3 page 13/27

| Symbol          | Parameter               | Conditions                                        | Min.                         | Тур. | Max.                | Unit |

|-----------------|-------------------------|---------------------------------------------------|------------------------------|------|---------------------|------|

| V               |                         | VCCCORE = 3.3 V,<br>I <sub>SOURCED</sub> = 300 μA | VCC <sub>CORE</sub><br>- 0.5 | -    | VCC <sub>CORE</sub> | V    |

| V <sub>OH</sub> | Logic high output level | VCCCORE = 5 V,<br>I <sub>SOURCED</sub> = 400 μA   | VCC <sub>CORE</sub><br>- 0.5 | -    | VCC <sub>CORE</sub> | V    |

- 1. Not tested in production. Guaranteed by design.

- 2. Not tested in production. Based on characterization.

DS12399 - Rev 3 page 14/27

### 5 Device description

The STKNX is a transceiver device for twisted pair communication, following the KNX twisted pair standard (KNX TP1-256). Detailed information on the KNX bus can be found in the KNX standards and on the KNX website (www.knx.org).

The STKNX is composed of two main functional blocks: the bus interface and the voltage regulators.

- The bus interface consists of the transmitter, receiver and impedance modulator

- The voltage regulators block consists of an adjustable output voltage step down switching converter with integrated power MOSFETs and a 3.3 V / 5 V programmable linear regulator

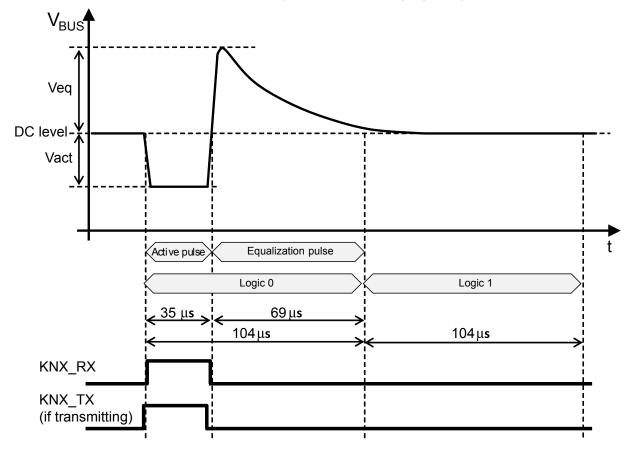

Figure 7. KNX bus voltage and corresponding digital signals

#### 5.1 Bus interface

The bus interface connects the STKNX to the KNX bus for transmitting, receiving and extracting power. Through the bus interface, the STKNX supports

- Interfacing a microcontroller with the KNX bus, translating signals between the logic level domain and KNX bus domain

- Extracting power from the bus to supply the STKNX itself, the microcontroller and application devices

The KNX standard specifies a bit period of 104 µs. It defines the logic 1 as the idle state of the bus (DC voltage level between 21 V and 32 V), the logic 0 (also called active pulse) as a voltage drop of the bus.

The active pulse is generated by the transmitter. Ideally, the drop has a rectangular shape, a depth between 6 V and 9 V and a duration of 35  $\mu$ s. Each active pulse is followed by an equalization phase of 69  $\mu$ s typical duration, which consists in an overshoot of the bus voltage above the DC level, followed by an exponential decay. See the KNX Twisted Pair Standard (KNX TP1-256) for more detailed information.

DS12399 - Rev 3 page 15/27

#### 5.1.1 Transmitter

The transmitter converts logic level signals received at the KNX\_TX pin to analog signals on the KNX bus. To transmit a logic 1 (equivalent to transmitter in idle state), the KNX\_TX pin has to be kept low for 104  $\mu$ s. To transmit a logic 0, the KNX\_TX has to be forced high for 35  $\mu$ s (active pulse) and then low for 69  $\mu$ s.

During the active pulse, the transmitter forces a voltage drop of 7.5 V typ. on the KNX bus, by sinking current through the R68 pin.

#### 5.1.2 Receiver

The receiver detects the beginning and the end of the active pulse and provides a logic level output on the KNX\_RX pin. The KNX\_RX pin is high during the active pulse, low during the equalization phase and idle state.

The detection threshold for the start of the active pulse is 0.6 V typ. below the bus DC voltage.

### 5.1.3 Impedance modulator

The KNX standard allows a bus voltage ranging from 21 V to 32 V (DC component). The bus provides supply for the STKNX and is the communication medium. During transmission, a -10.5 V / +13 V AC component can be superimposed to the DC component mentioned above.

Moreover, the KNX standard specifies that each module connected to the bus has to show a controlled impedance and to limit the bus load current slope dl/dt, while not transmitting.

The impedance modulator purpose is to extract power from the KNX bus in order to supply STKNX integrated voltage converters and the application on the KNX module, while ensuring compliance to KNX impedance specifications.

In particular, impedance modulator:

- Extracts a stable power rail (VDDHV) from the KNX bus DC level

- · Smooths any load change applied at its output, limiting dl/dt on the bus current

- Controls the impedance of the bus device during the active pulse and the equalization pulse according to KNX standard requirements

Since the current drawn from the bus must change very slowly, abrupt load current steps from the load applied to the STKNX have to be absorbed by the large filter capacitor on VDDHV rail (CVDDHV on Figure 1), which should be sized accordingly.

The bus current slope limit is controlled through CGATE (Figure 1).

CGATE =  $47 \mu F$  sets a slope lower than 0.5 mA/ms, compliant to the KNX requirement for fan in model up to the 10 mA bus load.

For a higher fan in, it can be useful to set a higher current slope limit, in order to manage wider load changes minimizing the CVDDHV value. That can be done by reducing the CGATE value proportionally to the desired slope limit increase.

Table 7 shows recommended CGATE and CVDDHV values for the minimum and maximum fan in.

Table 7. Recommended CGATE and CVDDHV vs. fan-in

| Fan in | Recommended CGATE | Recommended minimum CVDDHV |

|--------|-------------------|----------------------------|

| 10 mA  | 47 μF             | 100 μF                     |

| 30 mA  | 10 μF - 47 μF     | 220 μF                     |

### 5.2 Voltage regulators

The STKNX features two integrated voltage regulators for external use in the application:

- a linear regulator with 3.3 V or 5 V selectable output voltage, 20 mA current capability

- a step down switching converter with 1 V 12 V adjustable output voltage, 150 mA current capability.

#### **5.2.1 3.3 V / 5 V linear regulator**

The linear regulator converts the input voltage on the VDD\_REGIN pin to 3.3 V or 5 V output on the VCCCORE pin. The output voltage level is selectable by the VCCSEL pin.

DS12399 - Rev 3 page 16/27

- VCCSEL tied to GND → VCCCORE = 3.3 V

- VCCSEL tied to VCCCORE → VCCCORE = 5 V

VCCSEL should not be changed when STKNX is operational.

The output current capability is 20 mA. A  $4.7 \mu F$  capacitor or higher is required between VCCCORE and KNX\_B for stability.

VCCCORE is also the supply input for STKNX digital I/Os. The linear regulator can be disabled by shorting VCCCORE to VDD\_REGIN; in that case VCCCORE voltage to supply I/Os has to be provided externally and VCCSEL has to be configured according to the voltage level (3.3 V or 5 V).

#### 5.2.2 Buck converter

The STKNX integrates a high-efficiency low-consumption buck switching converter.

The switching converter is supplied from the DCDC\_IN pin, connected to VDDHV rail in the typical application. When voltage at the DCDC\_IN pin is lower than UVLO, the switching converter is disabled.

Buck converter output voltage is adjustable between 1 V and 12 V by means of an external resistor divider on the DCDC\_FB pin, according to the following expression:

$$Vout = 1V \cdot (1 + RFB1/RFB2) \tag{1}$$

Where RFB1 and RFB2 are the upper and lower resistor of the divider respectively (see Figure 1). The RFB2 typical value is  $10 \text{ k}\Omega$  (RFB2 values higher than  $100 \text{ k}\Omega$  should be avoided).

To set  $V_{OUT}$  = 1 V, RFB1 should be 0  $\Omega$  and RFB2 not mounted.

In the usual case of the low ESR ceramic capacitor as the output capacitor for the converter, it is recommended to add an external feedforward compensation capacitor CFB1 in parallel to RFB1, for  $V_{OUT} > 1$  V.

The CFB1 default value can be calculated according to the following expression:

$$CFB1 = \frac{1}{2\pi \cdot RFB1 \cdot 28kHz} \tag{2}$$

The buck converter can deliver a continuous output current up to 150 mA, however the maximum current capability will not always be usable. In fact, at the application level, the KNX bus current consumption must stay within the KNX specification.

The buck converter implements soft-start to prevent a high inrush current at start-up. Soft-start time  $T_{SS}$  is programmable through the external capacitor  $C_{SS}$  between the DCDC\_SS pin and GND, according to the following expression:

$$T_{SS} = 1V \cdot \frac{C_{SS}}{I_{SS}} \tag{3}$$

where  $I_{SS}$  is 2.5  $\mu A$  typ.

The buck converter features a full set of protections, which includes overtemperature protection (OTP), overcurrent protection (OCP) and overvoltage protection (OVP).

DS12399 - Rev 3 page 17/27

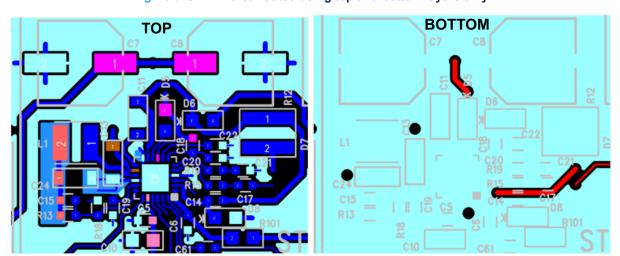

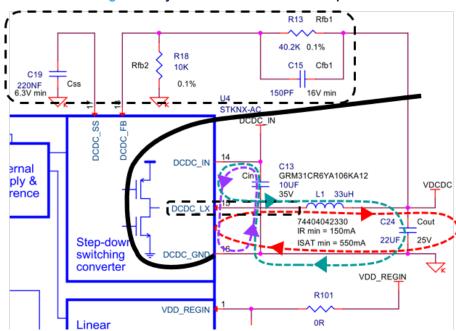

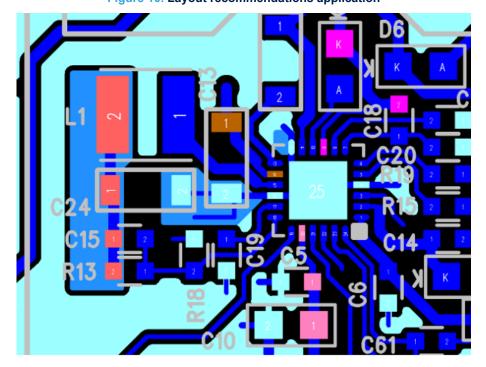

### 6 Layout recommendations

PCB layout is an important part of DC-DC switching converter design. A poor board layout can compromise important parameters of the DC-DC converter such as efficiency, output voltage ripple, line and load regulation and stability.

Good layout for the STKNX can be implemented by following the few simple design rules listed in this section. These rules have been applied to the STKNX routed area on the STKNX evaluation board (EVALKITSTKNX), where only the TOP and BOTTOM layers have been used from the four available, so it can be transposed on a low cost 2-layer PCB. It is then easy to implement the rules on a final KNX product. The source files of EVALKITSTKNX PCB layout are available for download from www.st.com.

Figure 8. STKNX area routed using top and bottom layers only

Refer to Figure 9 and Figure 10 below for the recommendations described below:

- Place CIN (C13) close to the STKNX and connect it between pins VIN and DCDC\_GND directly on top layer (DCDC\_LX trace crosses between CIN pads)

- Connect COUT (C24) to DCDC\_GND directly on top layer

- Keep the following power loops short:

- CIN → DCDC\_IN → DCDC\_LX → L1 → COUT → CIN (green)

- COUT → DCDC GND → DCDC LX → L1 → COUT (red)

- $\qquad \text{CIN} \rightarrow \text{DCDC\_IN} \rightarrow \text{DCDC\_GND} \rightarrow \text{CIN (purple)}$

- Use properly sized traces or shapes for power paths (DCDC\_IN, DCDC\_GND, VDCDC, LX)

- Keep FB/Feedback and SS/Soft-Start components (Rfbx, Cfb1, Css) away from switching / noisy node (DCDC\_LX), shielding with quiet nets (DCDC\_GND in the image) is recommended (black)

- Connect DCDC\_GND pin (16) and KNX\_B pins (4 and 12) to the exposed pad shape below the IC, as shown in Figure 10, to ensure ground consistency

- Place several GND vias on STKNX package exposed pad (x9 in EVALKITSTKNX).

DS12399 - Rev 3 page 18/27

Figure 9. Layout recommendations description

Figure 10. Layout recommendations application

DS12399 - Rev 3 page 19/27

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

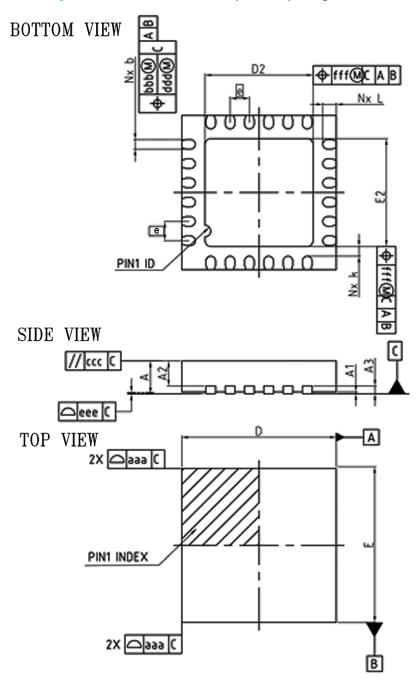

### 7.1 VFQFPN 4 x 4 x 1.0 24 pitch 0.5 package information

Figure 11. VFQFPN 4 x 4 x 1.0 24 pitch 0.5 package outline

DS12399 - Rev 3 page 20/27

Table 8. VFQFPN 4 x 4 x 1.0 24 pitch 0.5 package mechanical data

| O. male al | Dimensions [mm]                                 |      |      |  |

|------------|-------------------------------------------------|------|------|--|

| Symbol     | Min.                                            | Nom. | Max. |  |

| А          | 0.80                                            | -    | 1.00 |  |

| A1         | 0.00                                            | -    | 0.05 |  |

| A2         | -                                               | 0.65 | -    |  |

| A3         | -                                               | 0.20 | -    |  |

| b          | 0.20                                            | 0.25 | 0.30 |  |

| D          | 3.9                                             | 4.0  | 4.1  |  |

| D2         | 2.7                                             | 2.8  | 2.9  |  |

| е          | -                                               | 0.5  | -    |  |

| E          | 3.9                                             | 4.0  | 4.1  |  |

| E2         | 2.7                                             | 2.8  | 2.9  |  |

| L          | 0.30                                            | 0.35 | 0.40 |  |

| k          | 0.20                                            | -    | -    |  |

| N          | -                                               | 24   | -    |  |

| Symbol     | Tolerance of form and position [mm]  0.15  0.10 |      |      |  |

| aaa        |                                                 |      |      |  |

| bbb        |                                                 |      |      |  |

| ccc        | 0.10                                            |      |      |  |

| ddd        | 0.05                                            |      |      |  |

| eee        |                                                 | 0.08 |      |  |

| fff        | 0.10                                            |      |      |  |

DS12399 - Rev 3 page 21/27

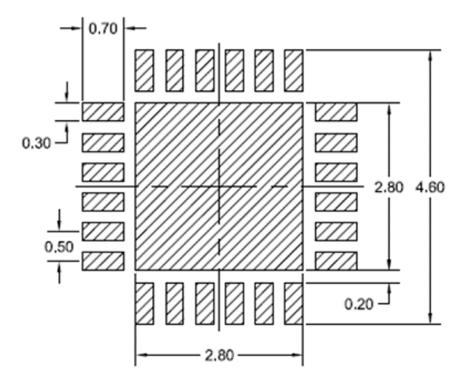

Figure 12. Suggested footprint

DS12399 - Rev 3 page 22/27

# **Revision history**

Table 9. Document revision history

| Date        | Version | Changes                                                                                                      |

|-------------|---------|--------------------------------------------------------------------------------------------------------------|

| 08-Feb-2018 | 1       | Initial release.                                                                                             |

| 06-Dec-2020 | 2       | Throughout document: - layout and template changes - minor text edits Added Section 6 Layout recommendations |

| 20-May-2021 | 3       | Change to Equation 1 in Section 5.2.2                                                                        |

DS12399 - Rev 3 page 23/27

## **Contents**

| 1  | Тур    | ical app  | plication circuit and block diagram              |    |

|----|--------|-----------|--------------------------------------------------|----|

|    | 1.1    | Typica    | al application circuit                           |    |

|    | 1.2    | Block     | diagram                                          |    |

| 2  | Pin    | connec    | ction and pin description                        | 8  |

|    | 2.1    | Pin co    | onnection                                        | 8  |

|    | 2.2    | Pin de    | escription                                       | 8  |

| 3  | The    | rmal ch   | haracteristics                                   | 10 |

| 4  | Elec   | ctrical s | specifications                                   | 11 |

|    | 4.1    | Absol     | lute maximum ratings                             |    |

|    | 4.2    | Reco      | mmended operating conditions                     | 11 |

|    | 4.3    | Electr    | rical characteristics                            |    |

| 5  | Dev    | ice des   | scription                                        |    |

|    | 5.1    | Bus ir    | nterface                                         |    |

|    |        | 5.1.1     | Transmitter                                      | 16 |

|    |        | 5.1.2     | Receiver                                         | 16 |

|    |        | 5.1.3     | Impedance modulator                              | 16 |

|    | 5.2    | Volta     | ge regulators                                    | 16 |

|    |        | 5.2.1     | 3.3 V / 5 V linear regulator                     | 16 |

|    |        | 5.2.2     | Buck converter                                   | 17 |

| 6  | Lay    | out rec   | commendations                                    | 18 |

| 7  | Pac    | kage in   | nformation                                       | 20 |

|    | 7.1    | VFQF      | FPN 4 x 4 x 1.0 24 pitch 0.5 package information | 20 |

| Re | vision | history   | v                                                | 23 |

# **List of figures**

| Figure 1.  | Typical application circuit, buck converter enabled, linear regulator supplied by impedance modulator | . 2 |

|------------|-------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Typical application circuit, buck converter enabled, linear regulator supplied by buck converter      | . 3 |

| Figure 3.  | Typical application circuit, buck converter disabled                                                  | . 4 |

| Figure 4.  | Typical application circuit, linear regulator disabled                                                | . 5 |

| Figure 5.  | STKNX Block diagram                                                                                   | . 7 |

| Figure 6.  | Pin connection (top view)                                                                             | . 8 |

| Figure 7.  | KNX bus voltage and corresponding digital signals                                                     | 15  |

| Figure 8.  | STKNX area routed using top and bottom layers only                                                    | 18  |

| Figure 9.  | Layout recommendations description                                                                    | 19  |

| Figure 10. | Layout recommendations application                                                                    | 19  |

| Figure 11. | VFQFPN 4 x 4 x 1.0 24 pitch 0.5 package outline                                                       | 20  |

| Figure 12. | Suggested footprint                                                                                   | 22  |

DS12399 - Rev 3 page 25/27

## **List of tables**

| Table 1. | External components typical value                       | 5  |

|----------|---------------------------------------------------------|----|

|          | STKNX Pin description                                   |    |

|          | Thermal characteristics                                 |    |

| Table 4. | Absolute maximum ratings                                | 11 |

|          | Recommended operating conditions                        |    |

| Table 6. | Electrical characteristics                              | 12 |

| Table 7. | Recommended CGATE and CVDDHV vs. fan-in                 | 16 |

| Table 8. | VFQFPN 4 x 4 x 1.0 24 pitch 0.5 package mechanical data | 21 |

|          | Document revision history                               |    |

DS12399 - Rev 3

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS12399 - Rev 3 page 27/27