# **ST-NXP Wireless**

# **IMPORTANT NOTICE**

Dear customer,

As from August 2<sup>nd</sup> 2008, the wireless operations of NXP have moved to a new company, ST-NXP Wireless.

As a result, the following changes are applicable to the attached document.

- Company name NXP B.V. is replaced with ST-NXP Wireless.

- Copyright the copyright notice at the bottom of each page "© NXP B.V. 200x. All rights reserved", shall now read: "© ST-NXP Wireless 200x All rights reserved".

- Web site <a href="http://www.nxp.com">http://www.stnwireless.com</a>

- Contact information the list of sales offices previously obtained by sending an email to <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>, is now found at <a href="http://www.stnwireless.com">http://www.stnwireless.com</a> under Contacts.

If you have any questions related to the document, please contact our nearest sales office. Thank you for your cooperation and understanding.

ST-NXP Wireless

# 1. General description

The ISP1362 is a single-chip Universal Serial Bus (USB) On-The-Go (OTG) controller integrated with the advanced NXP Slave Host Controller and the NXP ISP1181B Peripheral Controller. The USB OTG Controller is compliant with Ref. 1 "On-The-Go Supplement to the USB 2.0 Specification Rev. 1.0a". The Host and Peripheral Controllers are compliant with Ref. 2 "Universal Serial Bus Specification Rev. 2.0" (full-speed and low-speed support only), supporting data transfer at full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s).

The ISP1362 has two USB ports: port 1 and port 2. Port 1 can be hardware configured to function as a downstream port, an upstream port or an OTG port whereas port 2 can only be used as a downstream port. The OTG port can switch roles from host to peripheral, or from peripheral to host. The OTG port can become a host through Host Negotiation Protocol (HNP) as specified in the OTG supplement.

A USB product with OTG capability can function either as a host or as a peripheral. For instance, with this dual-role capability, a PC peripheral such as a printer may switch roles from a peripheral to a host for connecting to a digital camera so that the printer can print pictures taken by the camera without using a PC. When a USB product with OTG capability is inactive, the USB interface is turned off. This feature has made OTG a technology well-suited for use in portable devices, such as, Personal Digital Assistant (PDA), Digital Still Camera (DSC) and mobile phone, in which power consumption is a concern. The ISP1362 is an OTG Controller designed to perform such functions.

#### 2. Features

- Complies fully with:

- ♠ Ref. 2 "Universal Serial Bus Specification Rev. 2.0"

- ◆ Ref. 1 "On-The-Go Supplement to the USB 2.0 Specification Rev. 1.0a"

- Supports data transfer at full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s)

- Adapted from Ref. 4 "Open Host Controller Interface Specification for USB Release 1.0a"

- USB OTG:

- Supports Host Negotiation Protocol (HNP) and Session Request Protocol (SRP) for OTG dual-role devices

- Provides status and control signals for software implementation of HNP and SRP

- Provides programmable timers required for HNP and SRP

- Supports built-in and external source of V<sub>BUS</sub>

- Output current of the built-in charge pump is adjustable by using an external capacitor

- USB host:

#### **Single-chip USB OTG Controller**

- Supports integrated physical 4096 bytes of multiconfiguration memory

- Supports all four types of USB transfers: control, bulk, interrupt and isochronous

- Supports multiframe buffering for isochronous transfer

- Supports automatic interrupt polling rate mechanism

- Supports paired buffering for bulk transfer

- ◆ Directly addressable memory architecture; memory can be updated on-the-fly

- USB device:

- Supports high performance USB interface device with integrated Serial Interface Engine (SIE), buffer memory and transceiver

- Supports fully autonomous and multiconfiguration Direct Memory Access (DMA) operation

- Supports up to 14 programmable USB endpoints with two fixed control IN/OUT endpoints

- ◆ Supports integrated physical 2462 bytes of multiconfiguration memory

- Supports endpoints with double buffering to increase throughput and ease real-time data transfer

- ◆ Supports controllable LazyClock (110 kHz ± 50 %) output during 'suspend'

- Supports two USB ports: port 1 and port 2

- Port 1 can be configured to function as a downstream port, an upstream port or an OTG port

- Port 2 can be used only as a downstream port

- Supports software-controlled connection to the USB bus (SoftConnect)

- Supports good USB connection indicator that blinks with traffic (GoodLink)

- Complies with USB power management requirements

- Supports internal power-on and low-voltage reset circuit, with possibility of a software reset

- High-speed parallel interface to most CPUs available in the market, such as Hitachi SH-3, Intel StrongARM, NXP XA, Fujitsu SPARClite, NEC and Toshiba MIPS, ARM7/9, Freescale DragonBall and PowerPC Reduced Instruction Set Computer (RISC):

- 16-bit data bus

- ◆ 10 MB/s data transfer rate between the microprocessor and the ISP1362

- Supports Programmed I/O (PIO) or DMA

- Supports 'suspend' and remote wake-up

- Uses 12 MHz crystal or direct clock source with on-chip Phase-Locked Loop (PLL) for low ElectroMagnetic Interference (EMI)

- Operates at 3.3 V power supply

- Operating temperature range from –40 °C to +85 °C

- Available in 64-pin LQFP and TFBGA packages

# 3. Applications

The ISP1362 can be used to implement a dual-role USB device in any application, USB host or USB peripheral, depending on the cable connection. If the dual-role device is connected to a typical USB peripheral, it behaves like a typical USB host. The dual-role device, however, can also be connected to a PC or any other USB host and behave like a typical USB peripheral.

SP1362\_5 © NXP B.V. 2007. All rights reserved.

## Single-chip USB OTG Controller

#### 3.1 Host/peripheral roles

- Mobile phone to/from:

- Mobile phone: exchange contact information

- ◆ Digital still camera: e-mail pictures or upload pictures to the web

- MP3 player: upload, download and broadcast music

- Mass storage: upload and download files

- Scanner: scan business cards

- Digital still camera to/from:

- ◆ Digital still camera: exchange pictures

- ◆ Mobile phone: e-mail pictures, upload pictures to the web

- Printer: print pictures

- Mass storage: store pictures

- Printer to/from:

- Digital still camera: print pictures

- Scanner: print scanned image

- Mass storage: print files stored in a device

- MP3 player to/from:

- MP3 player: exchange songs

- Mass storage: upload and download songs

- Oscilloscope to/from:

- Printer: print screen image

- Personal digital assistant to/from:

- Personal digital assistant: exchange files

- Printer: print files

- Mobile phone: upload and download files

- MP3 player: upload and download songs

- Scanner: scan pictures

- Mass storage: upload and download files

- ◆ Global Positioning System (GPS): obtain directions, mapping information

- Digital still camera: upload pictures

- Oscilloscope: configure oscilloscope

# Single-chip USB OTG Controller

# 4. Ordering information

#### Table 1. Ordering information

| Type number | Package |                                                                                               |          |  |  |  |

|-------------|---------|-----------------------------------------------------------------------------------------------|----------|--|--|--|

|             | Name    | Description                                                                                   |          |  |  |  |

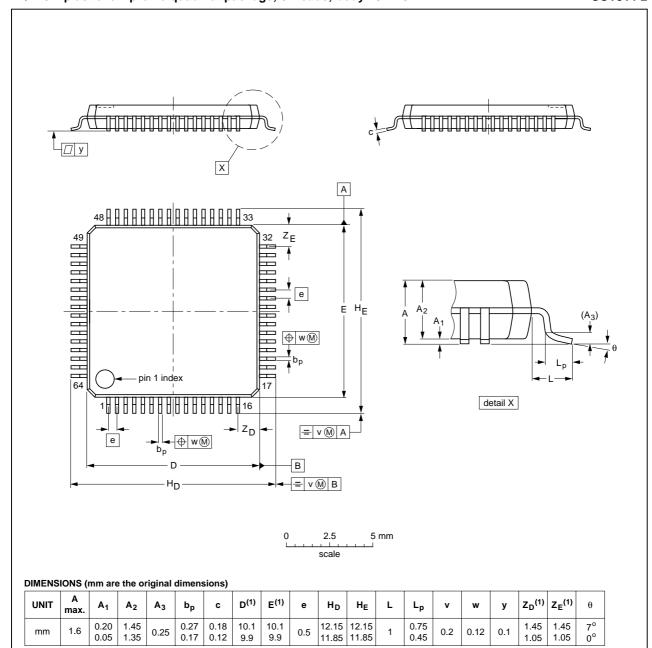

| ISP1362BD   | LQFP64  | plastic low profile quad flat package; 64 leads; body $10 \times 10 \times 1.4$ mm            | SOT314-2 |  |  |  |

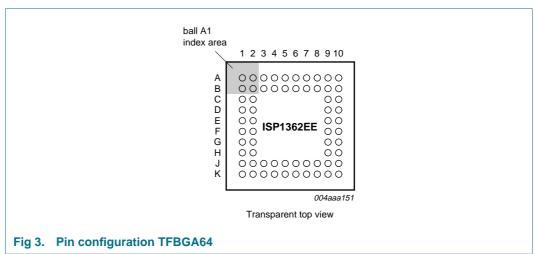

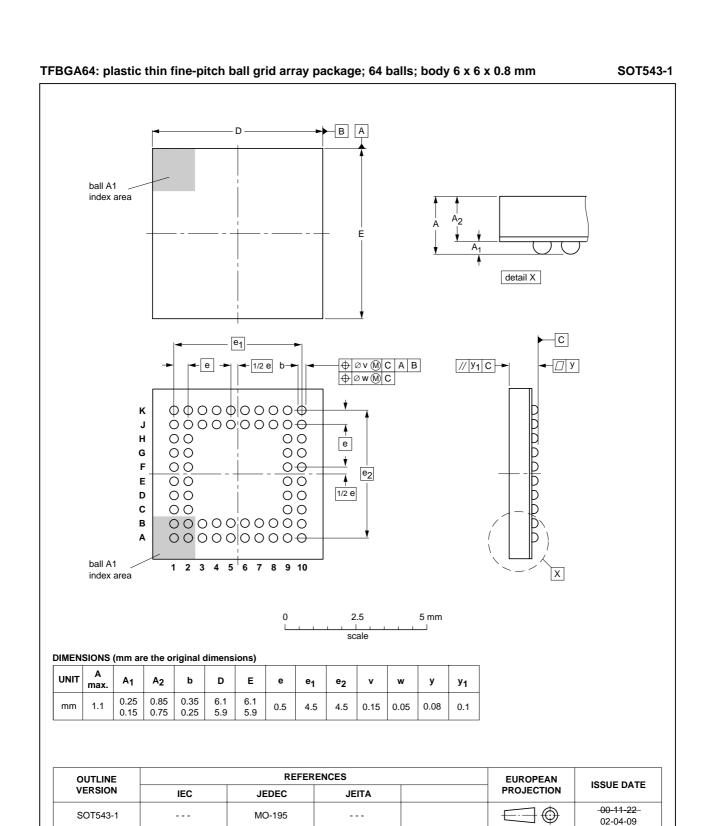

| ISP1362EE   | TFBGA64 | plastic thin fine-pitch ball grid array package; 64 balls; body $6\times6\times0.8~\text{mm}$ | SOT543-1 |  |  |  |

**SP1362**

9

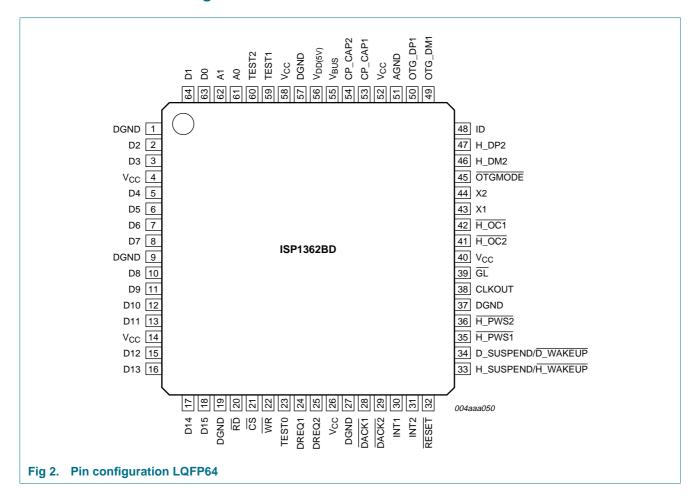

The figure shows the LQFP pinout. For the TFBGA ballout, see Table 2.

Fig 1. Block diagram

ISP1362\_5

Product data sheet

**Rev. 05**

8 May 2007

#### **Single-chip USB OTG Controller**

# 6. Pinning information

#### 6.1 Pinning

SP1362\_5 © NXP B.V. 2007. All rights reserved.

# Single-chip USB OTG Controller

# 6.2 Pin description

Table 2. Pin description

| Symbol[1]       | Pin    |         | Туре | Description                                                                                                                                                           |  |  |

|-----------------|--------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 | LQFP64 | TFBGA64 | _    |                                                                                                                                                                       |  |  |

| DGND            | 1      | B1      | -    | digital ground                                                                                                                                                        |  |  |

| D2              | 2      | C2      | I/O  | bit 2 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle  |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| D3              | 3      | C1      | I/O  | bit 3 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle  |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| V <sub>CC</sub> | 4      | D2      | -    | supply voltage (3.3 V); it is recommended that you connect a decoupling capacitor of 0.01 $\mu\text{F}$                                                               |  |  |

| D4              | 5      | D1      | I/O  | bit 4 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle  |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| D5              | 6      | E2      | I/O  | bit 5 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle  |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| D6              | 7      | E1      | I/O  | bit 6 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle  |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| D7              | 8      | F2      | I/O  | bit 7 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle  |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| DGND            | 9      | F1      | -    | digital ground                                                                                                                                                        |  |  |

| D8              | 10     | G2      | I/O  | bit 8 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle  |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| D9              | 11     | G1      | I/O  | bit 9 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle  |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| D10             | 12     | H2      | I/O  | bit 10 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

| D11             | 13     | H1      | I/O  | bit 11 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle |  |  |

|                 |        |         |      | bidirectional, push-pull input, 3-state output                                                                                                                        |  |  |

Table 2.

Pin description ...continued

| LQFP64 |                            |                                                | Description                                                                                                                                                                                                                                  |  |  |

|--------|----------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | TFBGA64                    |                                                |                                                                                                                                                                                                                                              |  |  |

| 14     | J2                         | -                                              | supply voltage (3.3 V); it is recommended that you connect a decoupling capacitor of 0.01 $\mu\text{F}$                                                                                                                                      |  |  |

| 15     | J1                         | I/O                                            | bit 12 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle                                                                        |  |  |

| 40     | 174                        | 1/0                                            | bidirectional, push-pull input, 3-state output                                                                                                                                                                                               |  |  |

| 10     | K I                        | 1/0                                            | bit 13 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle                                                                        |  |  |

|        |                            |                                                | bidirectional, push-pull input, 3-state output                                                                                                                                                                                               |  |  |

| 17     | K2                         | I/O                                            | bit 14 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle                                                                        |  |  |

|        |                            |                                                | bidirectional, push-pull input, 3-state output                                                                                                                                                                                               |  |  |

| 18     | J3                         | I/O                                            | bit 15 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle                                                                        |  |  |

|        |                            |                                                | bidirectional, push-pull input, 3-state output                                                                                                                                                                                               |  |  |

| 19     | K3                         | -                                              | digital ground                                                                                                                                                                                                                               |  |  |

| 20     | J4                         | I                                              | read strobe input; when asserted LOW, it indicates that the Host Controller/Peripheral Controller driver is requesting a read to the buffer memory or the internal registers of the Host Controller/Peripheral Controller                    |  |  |

|        |                            |                                                | input with hysteresis                                                                                                                                                                                                                        |  |  |

| 21     | K4                         | I                                              | chip select input (active LOW); enables the Host Controller/Peripheral Controller driver to access the buffer memory and registers of the Host Controller/Peripheral Controller input                                                        |  |  |

| 22     | J5                         | I                                              | write strobe input; when asserted LOW, it indicates that the Host Controller/Peripheral Controller driver is requesting a write to the buffer memory or the internal registers of the Host Controller/Peripheral Controller                  |  |  |

| 22     | VE                         | 1/0                                            | input with hysteresis                                                                                                                                                                                                                        |  |  |

| ۷۵     | r/O                        | 1/0                                            | for test input and output; pulled HIGH by a 100 kΩ resistor bidirectional, push-pull input, 3-state output                                                                                                                                   |  |  |

| 24     | IC                         | 0                                              |                                                                                                                                                                                                                                              |  |  |

| 24     | Jo                         | U                                              | DMA request output; when active, it signals the DMA controller that a data transfer is requested by the Host Controller; the active level (HIGH or LOW) of the request is programmed by using the HcHardwareConfiguration register (20h/A0h) |  |  |

|        |                            |                                                | If the OneDMA bit of the HcHardwareConfiguration register is set to logic 1, both the Host Controller and the Peripheral Controller DMA channel will be routed to DREQ1 and DACK1.  push-pull output                                         |  |  |

|        | 16<br>17<br>18<br>19<br>20 | 16 K1  17 K2  18 J3  19 K3 20 J4  21 K4  22 J5 | 16 K1 I/O  17 K2 I/O  18 J3 I/O  19 K3 - 20 J4 I  21 K4 I  22 J5 I                                                                                                                                                                           |  |  |

Table 2.

Pin description ...continued

| Symbol[1]              | Pin    |         | Туре | Description                                                                                                                                                                                                                                                                                                                                                |  |

|------------------------|--------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                        | LQFP64 | TFBGA64 |      |                                                                                                                                                                                                                                                                                                                                                            |  |

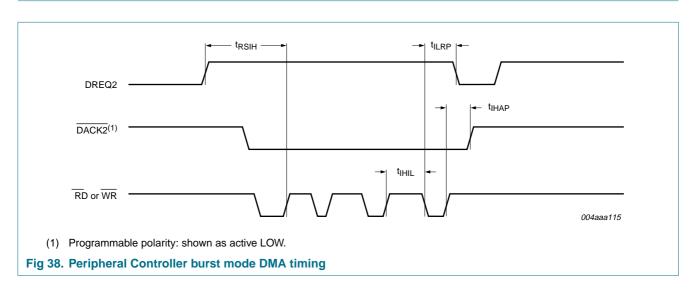

| DREQ2                  | 25     | K6      | 0    | DMA request output; when active, it signals the DMA controller that a data transfer is requested by the Peripheral Controller; the active level (HIGH or LOW) of the request is programmed by using the DcHardwareConfiguration register (BAh/BBh)                                                                                                         |  |

|                        |        |         |      | push-pull output                                                                                                                                                                                                                                                                                                                                           |  |

| V <sub>CC</sub>        | 26     | J7      | -    | supply voltage (3.3 V); it is recommended that you connect a decoupling capacitor of 0.01 $\mu\text{F}$                                                                                                                                                                                                                                                    |  |

| DGND                   | 27     | K7      | -    | digital ground                                                                                                                                                                                                                                                                                                                                             |  |

| DACK1                  | 28     | J8      | I    | DMA acknowledge input; indicates that a request for DMA transfer from the Host Controller has been granted by the DMA controller; the active level (HIGH or LOW) of the acknowledge signal is programmed by using the HcHardwareConfiguration register (20h/A0h); when not in use, this pin must be connected to $V_{CC}$ through a 10 k $\Omega$ resistor |  |

|                        |        |         |      | input with hysteresis                                                                                                                                                                                                                                                                                                                                      |  |

| DACK2                  | 29     | K8      | I    | DMA acknowledge input; indicates that a request for DMA transfer fro the Peripheral Controller has been granted by the DMA controller; the active level (HIGH or LOW) of the acknowledge signal is programmed using the DcHardwareConfiguration register (BAh/BBh); when not in u this pin must be connected to $V_{CC}$ through a 10 k $\Omega$ resistor  |  |

|                        |        |         |      | input with hysteresis                                                                                                                                                                                                                                                                                                                                      |  |

| INT1                   | 30     | J9      | 0    | interrupt request from the Host Controller; provides a mechanism for the Host Controller to interrupt the microprocessor; for details, see HcHardwareConfiguration register (20h/A0h) Section 14.4.1                                                                                                                                                       |  |

|                        |        |         |      | If the OneINT bit of the HcHardwareConfiguration register is set to logic 1, both the Host Controller and the Peripheral Controller interrupt request will be routed to INT1.                                                                                                                                                                              |  |

|                        |        |         |      | push-pull output                                                                                                                                                                                                                                                                                                                                           |  |

| INT2                   | 31     | K9      | 0    | interrupt request from the Peripheral Controller; provides a mechanism for the Peripheral Controller to interrupt the microprocessor; for details, see DcHardwareConfiguration register (BAh/BBh) Section 15.1.4                                                                                                                                           |  |

|                        |        |         |      | push-pull output                                                                                                                                                                                                                                                                                                                                           |  |

| RESET                  | 32     | K10     | I    | reset input                                                                                                                                                                                                                                                                                                                                                |  |

|                        |        |         |      | input with hysteresis and internal pull-up resistor                                                                                                                                                                                                                                                                                                        |  |

| H_SUSPEND/<br>H_WAKEUP | 33     | J10     | I/O  | I/O pin (open-drain); goes HIGH when the Host Controller is in suspend mode; a LOW pulse must be applied to this pin to wake up the Host Controller; connect a 100 k $\Omega$ resistor to $V_{CC}$                                                                                                                                                         |  |

|                        |        |         |      | bidirectional, push-pull input, 3-state open-drain output                                                                                                                                                                                                                                                                                                  |  |

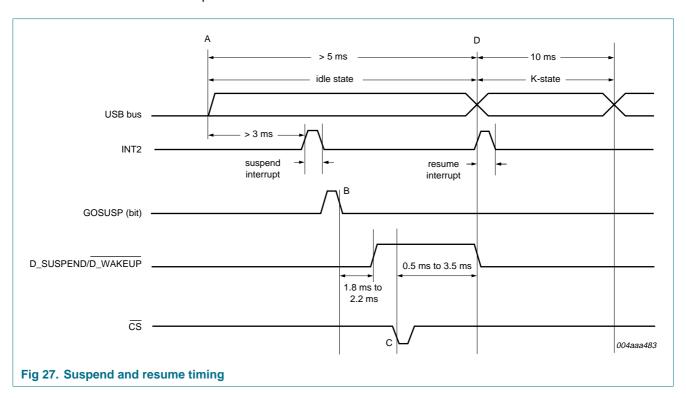

| D_SUSPEND/<br>D_WAKEUP | 34     | H9      | I/O  | I/O pin (open-drain); goes HIGH when the Peripheral Controller is in suspend mode; a LOW pulse must be applied to this pin to wake up the Peripheral Controller; connect a 100 k $\Omega$ resistor to $V_{CC}$                                                                                                                                             |  |

|                        |        |         |      | bidirectional, push-pull input, 3-state open-drain output                                                                                                                                                                                                                                                                                                  |  |

Table 2.

Pin description ...continued

| Symbol[1]       | Pin    |         | Туре | Description                                                                                                                                                                                                                                                                                                                                             |  |  |

|-----------------|--------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 | LQFP64 | TFBGA64 |      |                                                                                                                                                                                                                                                                                                                                                         |  |  |

| H_PSW1          | 35     | H10     | 0    | connects to the external PMOS switch; required when the external charge pump or external V <sub>BUS</sub> is used for providing V <sub>BUS</sub> to the downstream port <b>LOW</b> — switches on the PMOS providing V <sub>BUS</sub> to the downstream port <b>HIGH</b> — switches off the PMOS  when not in use, leave this pin open open-drain output |  |  |

| H_PSW2          | 36     | G9      | 0    | connects to the external PMOS switch <b>LOW</b> — switches on the PMOS providing V <sub>BUS</sub> to the downstream port <b>HIGH</b> — switches off the PMOS  when not in use, leave this pin open  open-drain output                                                                                                                                   |  |  |

| DGND            | 37     | G10     | -    | digital ground                                                                                                                                                                                                                                                                                                                                          |  |  |

| CLKOUT          | 38     | F9      | 0    | programmable clock output; the default clock frequency is 12 MHz and can be varied from 3 MHz to 48 MHz push-pull output                                                                                                                                                                                                                                |  |  |

| GL              | 39     | F10     | 0    | GoodLink LED indicator output; the LED is off by default, blinks on at USB traffic                                                                                                                                                                                                                                                                      |  |  |

| V <sub>CC</sub> | 40     | E9      | -    | open-drain output; 4 mA supply voltage (3.3 V); it is recommended that you connect a decoupl capacitor of 0.01 μF                                                                                                                                                                                                                                       |  |  |

| H_OC2           | 41     | E10     | 1    | overcurrent sense input for downstream port 2; both the digital and analog overcurrent inputs can be used for port 2, depending on the hardware mode register setting; when not in use, it is recommended the you connect this pin to the V <sub>DD(5V)</sub> pin                                                                                       |  |  |

| H_OC1           | 42     | D9      | I    | overcurrent sensing input for downstream port 1; both the digital and analog overcurrent inputs can be used for port 1, depending on the hardware mode register setting; when not in use, it is recommended that you connect this pin to the $V_{\text{DD}(5V)}$ pin                                                                                    |  |  |

| X1              | 43     | D10     | Al   | crystal input; directly connected to a 12 MHz crystal; when this pin is connected to an external clock oscillator, leave pin X2 open                                                                                                                                                                                                                    |  |  |

| X2              | 44     | C9      | AO   | crystal output; directly connected to a 12 MHz crystal; when pin X1 is connected to an external clock oscillator, leave this pin open                                                                                                                                                                                                                   |  |  |

| OTGMODE         | 45     | C10     | I    | to select whether port 1 is operating in OTG or non-OTG mode; see Table 8 input with hysteresis                                                                                                                                                                                                                                                         |  |  |

| H_DM2           | 46     | В9      | AI/O | downstream D– signal; host only, port 2; when not in use, leave this pin open and set bit ConnectPullDown_DS2 of the HcHardwareConfiguration register                                                                                                                                                                                                   |  |  |

| H_DP2           | 47     | B10     | AI/O | downstream D+ signal; host only, port 2; when not in use, leave this pin open and set bit ConnectPullDown_DS2 of the HcHardwareConfiguration register                                                                                                                                                                                                   |  |  |

| ID              | 48     | A10     | I    | input pin for sensing OTG ID; the status of this input pin is reflected in the OTGStatus register (bit 0); see <u>Table 8</u> input with hysteresis                                                                                                                                                                                                     |  |  |

## **Single-chip USB OTG Controller**

Table 2.

Pin description ...continued

| Symbol <sup>[1]</sup> | Pin            |    | Туре | Description                                                                                                                                                                                                                                                |  |  |

|-----------------------|----------------|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                       | LQFP64 TFBGA64 |    |      |                                                                                                                                                                                                                                                            |  |  |

| OTG_DM1               | 49             | A9 | AI/O | D– signal of the OTG port, the downstream host port 1 or the upstream device port; when not in use, leave this pin open and set bit ConnectPullDown_DS1 of the HcHardwareConfiguration register [2]                                                        |  |  |

| OTG_DP1               | 50             | B8 | AI/O | D+ signal of the OTG port, the downstream host port 1 or the upstream device port; when not in use, leave this pin open and set bit ConnectPullDown_DS1 of the HcHardwareConfiguration register[2]                                                         |  |  |

| AGND                  | 51             | A8 | -    | analog ground; used for OTG ATX                                                                                                                                                                                                                            |  |  |

| V <sub>CC</sub>       | 52             | B7 | -    | supply voltage (3.3 V); it is recommended that you connect a decoupling capacitor of 0.01 $\mu\text{F}$                                                                                                                                                    |  |  |

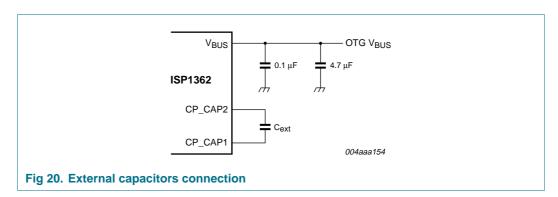

| CP_CAP1               | 53             | A7 | AI/O | charge pump capacitor pin 1; low ESR; see Section 10.6                                                                                                                                                                                                     |  |  |

| CP_CAP2               | 54             | B6 | AI/O | charge pump capacitor pin 2; low ESR; see Section 10.6                                                                                                                                                                                                     |  |  |

| $V_{BUS}$             | 55             | A6 | I/O  | analog input and output                                                                                                                                                                                                                                    |  |  |

|                       |                |    |      | <b>OTG mode</b> — built-in charge pump output or $V_{BUS}$ voltage comparators input; connect to pin $V_{BUS}$ of the OTG connector                                                                                                                        |  |  |

|                       |                |    |      | <b>Peripheral Controller mode</b> — input as $V_{BUS}$ sensing; connect to pin $V_{BUS}$ of the upstream connector                                                                                                                                         |  |  |

|                       |                |    |      | Host Controller mode — not used; leave open                                                                                                                                                                                                                |  |  |

| $V_{DD(5V)}$          | 56             | B5 | I    | supply reference voltage (5 V); to be used together with built-in overcurrent circuit; when built-in overcurrent circuit is not in use, this parameter can be tied to $V_{CC}$ ; it is recommended that you connect a decoupling capacitor of 0.01 $\mu F$ |  |  |

| DGND                  | 57             | A5 | -    | digital ground                                                                                                                                                                                                                                             |  |  |

| V <sub>CC</sub>       | 58             | B4 | -    | supply voltage (3.3 V); it is recommended that you connect a decouplir capacitor of 0.01 $\mu\text{F}$                                                                                                                                                     |  |  |

| TEST1                 | 59             | A4 | I/O  | for test input and output, pulled to GND by a 10 $k\Omega$ resistor bidirectional, push-pull input, 3-state output                                                                                                                                         |  |  |

| TEST2                 | 60             | В3 | I/O  | for test input and output, pulled to GND by a 10 $k\Omega$ resistor                                                                                                                                                                                        |  |  |

|                       |                |    |      | bidirectional, push-pull input, 3-state output                                                                                                                                                                                                             |  |  |

| A0                    | 61             | A3 | I    | command or data phase input                                                                                                                                                                                                                                |  |  |

| A1                    | 62             | B2 | I    | LOW — PIO bus of the Host Controller is selected HIGH — PIO bus of the Peripheral Controller is selected input                                                                                                                                             |  |  |

| D0                    | 63             | A2 | I/O  | bit 0 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle                                                                                       |  |  |

|                       |                |    |      | bidirectional, push-pull input, 3-state output                                                                                                                                                                                                             |  |  |

| D1                    | 64             | A1 | I/O  | bit 1 of the bidirectional data bus that connects to the internal registers and buffer memory of the ISP1362; the bus is in the high-impedance state when it is idle                                                                                       |  |  |

|                       |                |    |      | bidirectional, push-pull input, 3-state output                                                                                                                                                                                                             |  |  |

<sup>[1]</sup> Symbol names with an overscore (for example,  $\overline{NAME}$ ) represent active LOW signals.

ISP1362\_5 © NXP B.V. 2007. All rights reserved.

<sup>[2]</sup> In OTG mode, this pin is pulled down by an internal resistor.

**Single-chip USB OTG Controller**

# 7. Functional description

#### 7.1 On-The-Go (OTG) controller

The OTG Controller provides all the control, monitoring and switching functions required in OTG operations.

## 7.2 Advanced NXP Slave Host Controller

The advanced NXP Slave Host Controller is designed for highly optimized USB host functionality. Many advanced features are integrated to fully utilize the USB bandwidth. A number of tasks are performed at the hardware level. This reduces the requirement on the microprocessor and thus speeds up the system.

#### 7.3 NXP Peripheral Controller

The NXP Peripheral Controller is a high performance USB device with up to 14 programmable endpoints. These endpoints can be configured as double-buffered endpoints to further enhance the throughput.

#### 7.4 Phase-Locked Loop (PLL) clock multiplier

A 12 MHz-to-48 MHz clock multiplier PLL is integrated on-chip. This allows the use of a low-cost 12 MHz crystal that also minimizes ElectroMagnetic Interference (EMI) because of low frequency. No external components are required for the operation of PLL.

#### 7.5 USB and OTG transceivers

The integrated transceivers (for typical downstream port) directly interface to the USB connectors (type A) and cables through some termination resistors. The transceiver is compliant with Ref. 2 "Universal Serial Bus Specification Rev. 2.0".

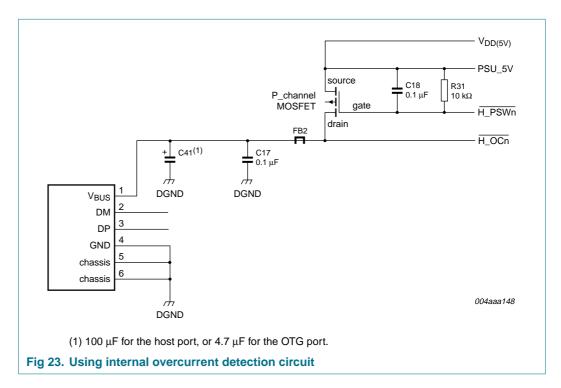

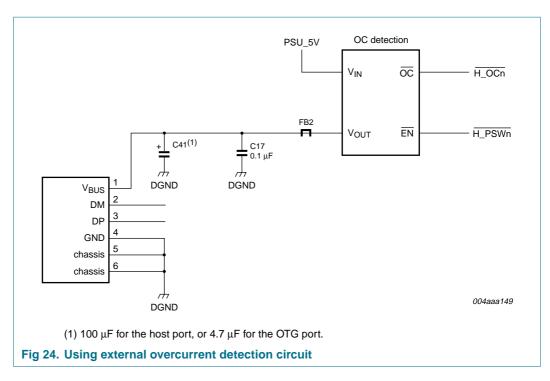

#### 7.6 Overcurrent protection

The ISP1362 has a built-in overcurrent protection circuitry. This feature monitors the current drawn on the downstream  $V_{BUS}$  and switches off  $V_{BUS}$  when the current exceeds the current threshold. The built-in overcurrent protection feature can be used when the port acts as a host port.

#### 7.7 Bus interface

The bus interface connects the microprocessor to the USB host and the USB device, allowing fast and easy access to both.

#### 7.8 Peripheral Controller and Host Controller buffer memory

4096 bytes (host) and 2462 bytes (device) of built-in memory provide sufficient space for the buffering of USB traffic. Memory in the Host Controller is addressable by using the fast and versatile direct addressing method.

#### **Single-chip USB OTG Controller**

#### 7.9 GoodLink

Indication of a good USB connection is provided through the GoodLink technology (open-drain, maximum current: 4 mA). During enumeration, LED indicators momentarily blink on corresponding to the enumeration traffic of the ISP1362 ports. The LED also blinks on whenever there is valid traffic to the USB ports. In 'suspend' mode, the LED is off.

This feature of GoodLink provides a user-friendly indication on the status of the USB traffic between the host and the hub, as well as the connected devices. It is a useful diagnostics tool to isolate faulty equipment, and helps to reduce field support and hotline costs.

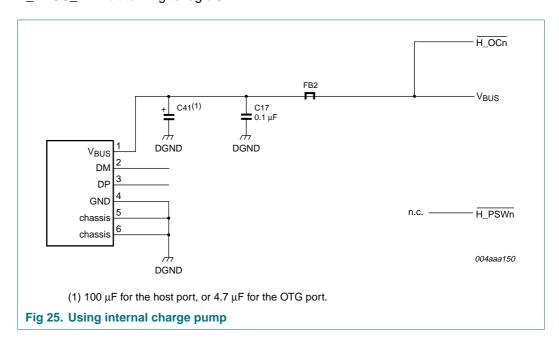

## 7.10 Charge pump

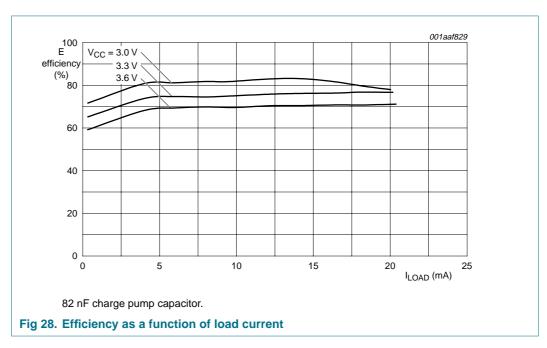

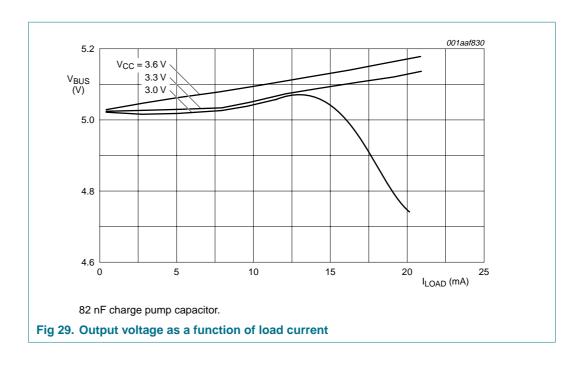

The charge pump generates a 5 V supply from 3.3 V to drive  $V_{BUS}$  when the ISP1362 is an A-device in OTG mode. For details, see Section 10.6.

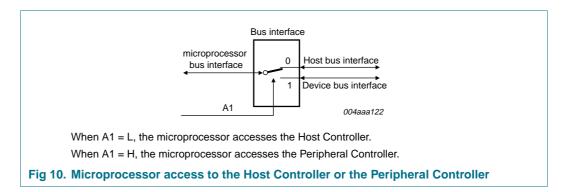

#### 8. Host and device bus interface

The interface between the external microprocessor and the ISP1362 Host Controller (HC) and Peripheral Controller is separately handled by the individual bus interface circuitry. The host or device automultiplex selects the path for the host access or the device access. This selection is determined by the A1 address line. For any access to the Host Controller or Peripheral Controller registers, the command phase and the data phase are needed, which is determined by the A0 address line.

All the functionality of the ISP1362 can be accessed using a group of registers and two buffer memory areas (one for the Host Controller and the other for the Peripheral Controller). Registers can be accessed using Programmed I/O (PIO) mode. The buffer memory can be accessed using both PIO and Direct Memory Access (DMA) modes.

When  $\overline{CS}$  is LOW (active), address pin A1 has priority over DREQ and  $\overline{DACK}$ . Therefore, as long as the  $\overline{CS}$  pin is held LOW, the ISP1362 bus interface does not respond to any  $\overline{DACK}$  signals. When  $\overline{CS}$  is HIGH (inactive), the bus interface will respond to DREQn and  $\overline{DACKn}$ . Address pin A1 will be ignored when  $\overline{CS}$  is inactive.

An active  $\overline{DACKn}$  signal when DREQn is inactive will be ignored. If DREQ1,  $\overline{DACK1}$ , DREQ2 and  $\overline{DACK2}$  are active, the bus interface will be switched off to avoid potential data corruption.

Table 3 provides the bus access priority for the ISP1362.

Table 3. Bus access priority table for the ISP1362

| Priority | CS | <b>A</b> 1 | DACK1 | DACK2 | DREQ1 | DREQ2 | Host Controller and Peripheral Controller active |

|----------|----|------------|-------|-------|-------|-------|--------------------------------------------------|

| 1        | L  | L          | Χ     | Χ     | Χ     | Χ     | Host Controller                                  |

| 2        | L  | Н          | Χ     | Χ     | Χ     | Χ     | Peripheral Controller                            |

| 3        | Н  | X          | L     | X     | Н     | L     | Host Controller <sup>[1]</sup>                   |

| 4        | Н  | X          | Χ     | L     | L     | Н     | Peripheral Controller[1]                         |

| 5        | Н  | X          | Χ     | Χ     | Н     | Н     | no driving                                       |

<sup>[1]</sup> Only to enable and disable the bus. Depends only on the DACK signal.

SP1362\_5 © NXP B.V. 2007. All rights reserved.

#### **Single-chip USB OTG Controller**

# 8.1 Memory organization

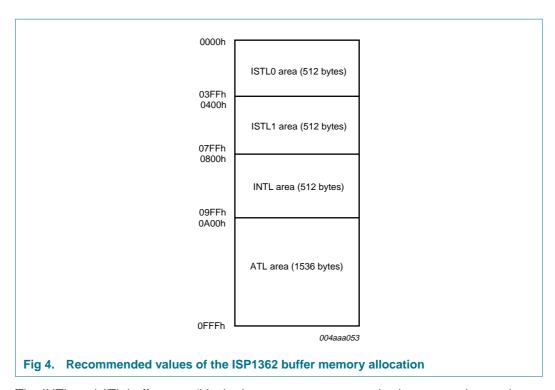

The buffer memory in the Host Controller uses a multiconfigurable direct addressing architecture. The 4096 bytes Host Controller buffer memory is shared by the ISTL0, ISTL1, INTL and ATL buffers. ISTL0 and ISTL1 are used for isochronous traffic (double buffer), INTL is used for interrupt traffic, and ATL is used for control and bulk traffic.

The allocation of the buffer memory follows the sequence ISTL0, ISTL1, INTL, ATL and unused memory. For example, consider that the buffer sizes of the ISTL, INTL and ATL buffers are 1024 bytes, 1024 bytes and 1024 bytes, respectively. Then, ISTL0 will start from memory location 0, ISTL1 will start from memory location 1024 (size of ISTL0), INTL will start from memory location 2048 (size of ISTL0 + size of ISTL1) and ATL will start from memory location 3072 (size of ISTL0 + size of ISTL1 + size of INTL).

The Host Controller Driver (HCD) has the responsibility to ensure that the sum of the four memory buffers does not exceed the total memory size. If this condition is violated, it will lead to data corruption. The buffer size must be a multiple of 2 bytes (one word).

The buffer memory of the Peripheral Controller follows a similar architecture. Details on the Peripheral Controller memory area allocation can be found in <u>Section 12.3</u>. Note that the Peripheral Controller buffer memory does not support direct addressing mode.

#### 8.1.1 Memory organization for the Host Controller

The Host Controller in the ISP1362 has a total of 4096 bytes of buffer memory. This buffer area is divided into four parts (see <u>Table 4</u> and <u>Figure 4</u>).

Table 4. Buffer memory areas and their applications

| Buffer memory area | Application                             |

|--------------------|-----------------------------------------|

| ISTL0 and ISTL1    | isochronous transfer (double buffering) |

| INTL               | interrupt transfer                      |

| ATL                | control and bulk transfer               |

The ISTL0 and ISTL1 buffers must have the same size. Memory is allocated by the Host Controller according to the value set by the HCD in HcISTLBufferSize, HcINTLBufferSize and HcATLBufferSize. All buffer sizes must be multiples of 2 bytes (one word).

#### Single-chip USB OTG Controller

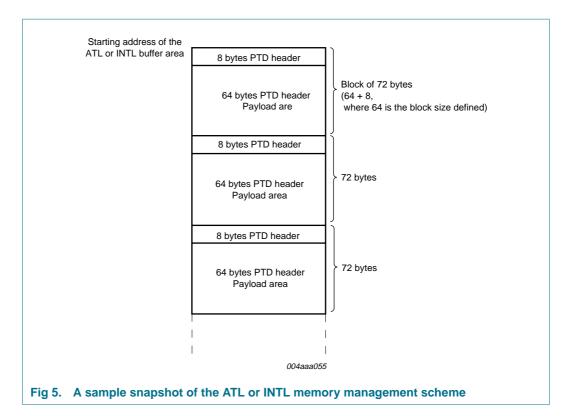

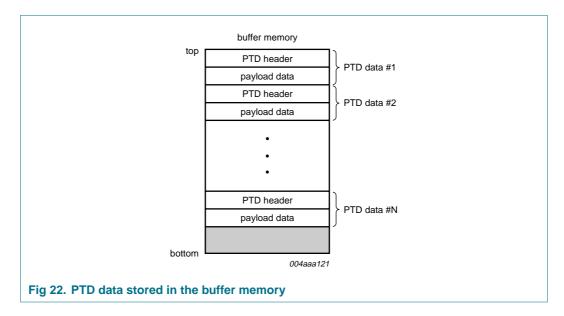

The INTL and ATL buffers use 'blocked memory management' scheme to enhance the status and control capability of each and every individual Philips Transfer Descriptor (PTD) structure. The INTL and ATL buffers are further divided into blocks of equal sizes, depending on the value written to the HcATLBlkSize register (ATL) and the HcINTLBlkSize register (INTL). The ISP1362 Host Controller supports up to 32 blocks in the ATL and INTL buffers. Each of these blocks can be used for one complete PTD data.

Note that the block size does not include the 8 bytes PTD header and is strictly the size of the payload. Both the ATL and INTL block sizes must be a multiple of double word (4 bytes).

#### **Single-chip USB OTG Controller**

<u>Figure 5</u> provides a snapshot of a sample ATL or INTL buffer area of 256 bytes with a block size of 64 bytes. The HCD may put a PTD with payload size of up to 64 bytes but not more. Depending on the ATL or INTL buffer size, up to 32 ATL blocks and 32 INTL blocks can be allocated. Note that a portion of the ATL or INTL buffer remains unused. This is allowed but can be avoided by choosing the appropriate ATL or INTL buffer size and block size.

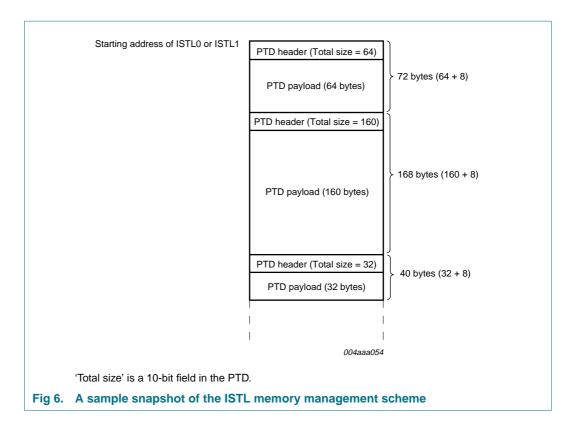

The ISTL0 or ISTL1 buffer memory (for isochronous transfer) uses a different memory management scheme (see <a href="Figure 6">Figure 6</a>). There is no fixed block size for the ISTL buffer memory. While the PTD header remains 8 bytes for all PTDs, the PTD payload can be of any size. The PTD payload, however, is padded to the next double word boundary when the Host Controller calculates the location of the next PTD header. The ISP1362 Host Controller checks the payload size from the 'Total size' field of the PTD itself and calculates the location of the next PTD header based on this information.

#### **Single-chip USB OTG Controller**

#### 8.1.2 Memory organization for the Peripheral Controller

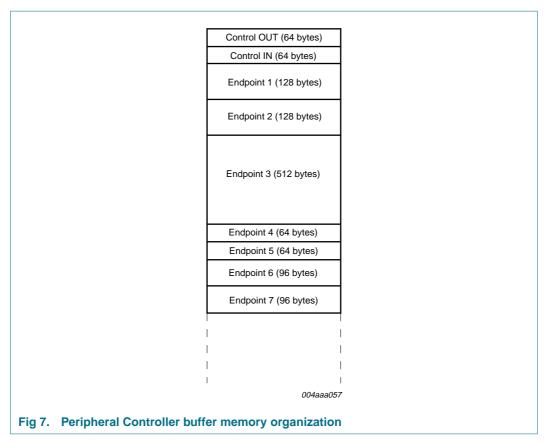

The ISP1362 Peripheral Controller has a total of 2462 bytes of built-in buffer memory. This buffer memory is multiconfigurable to support the requirements of different applications. The Peripheral Controller buffer memory is divided into 16 areas to be used by control OUT, control IN and 14 programmable endpoints.

Figure 7 provides a snapshot of the Peripheral Controller buffer memory.

Single-chip USB OTG Controller

The buffer memory is configured by DcEndpointConfiguration Registers (ECRs). Although the control endpoint has a fixed configuration, all 16 endpoints (control OUT, control IN and 14 programmable endpoints) must be configured before the Peripheral Controller internally allocates the buffer. The 14 programmable endpoints can be programmed into sizes ranging from 16 bytes to 1023 bytes, single or double buffering.

The Peripheral Controller buffer memory for each endpoint can be accessed through the DcEndpointStatusImage registers.

#### 8.2 PIO access mode

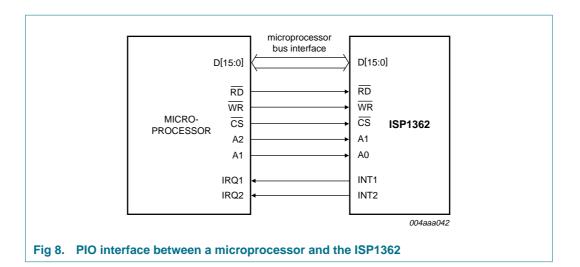

The ISP1362 provides PIO mode for external microprocessors to access its internal control registers and buffer memory. It occupies only four I/O ports or four memory locations of a microprocessor. An external microprocessor can read or write to the internal control registers and buffer memory of the ISP1362 through PIO operating mode. Figure 8 shows the PIO interface between a microprocessor and the ISP1362.

#### Single-chip USB OTG Controller

#### 8.3 DMA mode

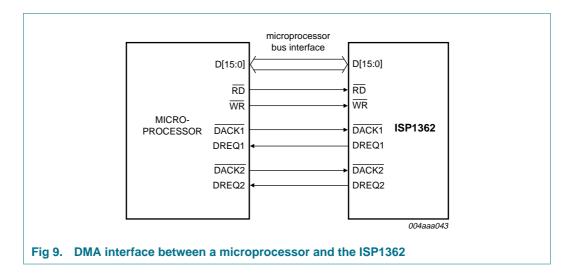

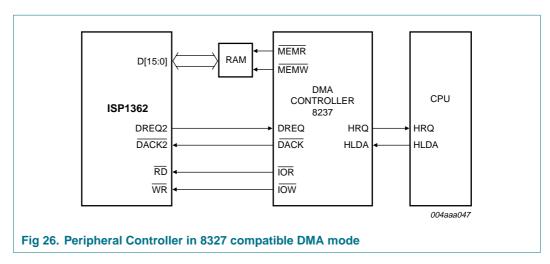

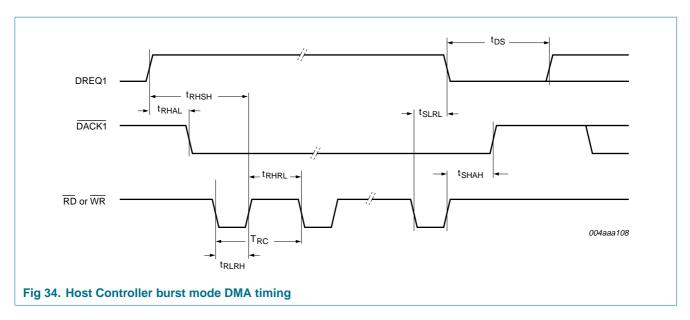

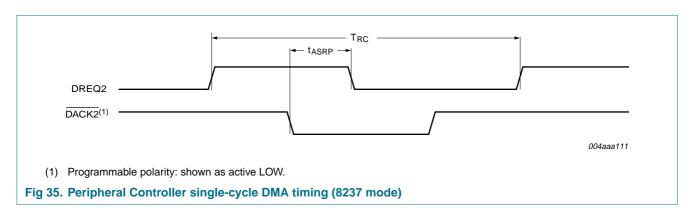

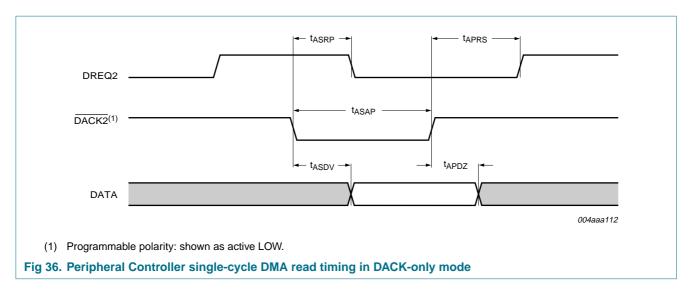

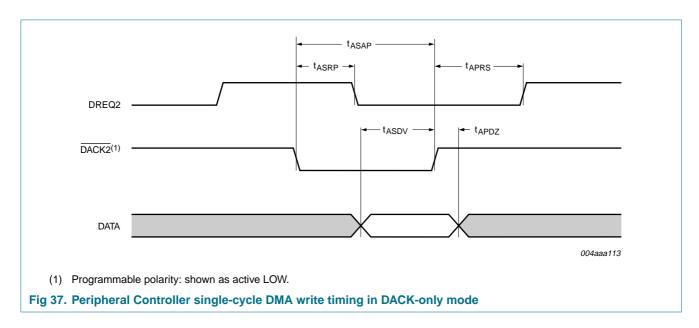

The ISP1362 also provides DMA mode for external microprocessors to access the internal buffer memory of the ISP1362. The DMA operation enables data to be transferred between the system memory of a microprocessor and the internal buffer memory of the ISP1362.

**Remark:** The DMA operation must be controlled by the DMA controller of the external microprocessor system (master). Figure 9 shows the DMA interface between a microprocessor system and the ISP1362.

The ISP1362 provides two DMA channels. DMA channel 1 (controlled by the DREQ1 and DACK1 signals) is for the DMA transfer between the system memory of a microprocessor and the internal buffer memory of the ISP1362 Host Controller. DMA channel 2 (controlled by the DREQ2 and DACK2 signals) is for the DMA transfer between the system memory of a microprocessor and the internal buffer memory of the ISP1362 Peripheral Controller. The ISP1362 provides an internal End-Of-Transfer (EOT) signal to terminate the DMA transfer.

#### **Single-chip USB OTG Controller**

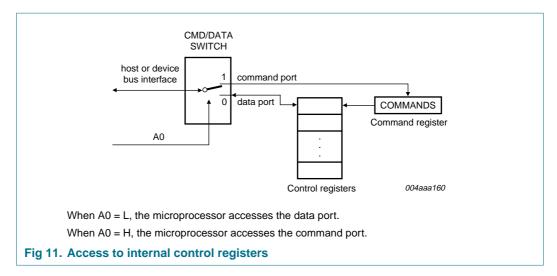

#### 8.4 PIO access to internal control registers

<u>Table 5</u> shows the I/O port addressing in the ISP1362. The complete I/O port address decoding must combine with the chip select signal ( $\overline{CS}$ ) and address lines (A1 and A0). The direction of access of I/O ports, however, is controlled by the  $\overline{RD}$  and  $\overline{WR}$  signals.

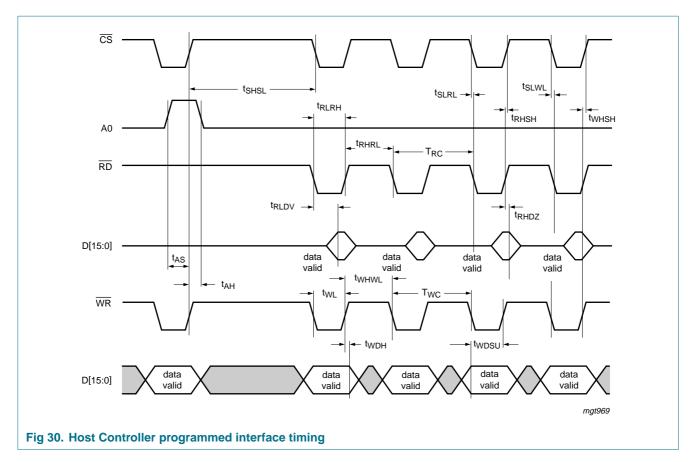

When  $\overline{RD}$  is LOW, the microprocessor reads data from the data port of the ISP1362 (see Figure 10). When  $\overline{WR}$  is LOW, the microprocessor writes command to the command port or writes data to the data port (see Figure 11).

Table 5. I/O port addressing

| CS | <b>A</b> 1 | A0 | Access | Data bus width | Description                        |

|----|------------|----|--------|----------------|------------------------------------|

| L  | L          | L  | R/W    | 16 bits        | Host Controller data port          |

| L  | L          | Н  | W      | 16 bits        | Host Controller command port       |

| L  | Н          | L  | R/W    | 16 bits        | Peripheral Controller data port    |

| L  | Н          | Н  | W      | 16 bits        | Peripheral Controller command port |

The register structure in the ISP1362 is a command-data register pair structure. A complete register access needs a command phase followed by a data phase. The command (also named as the index of a register) is used to inform the ISP1362 about the register that will be accessed at the data phase.

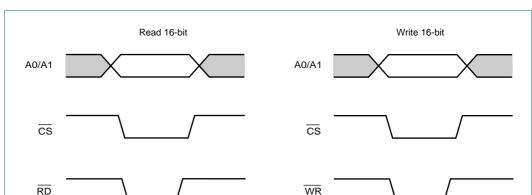

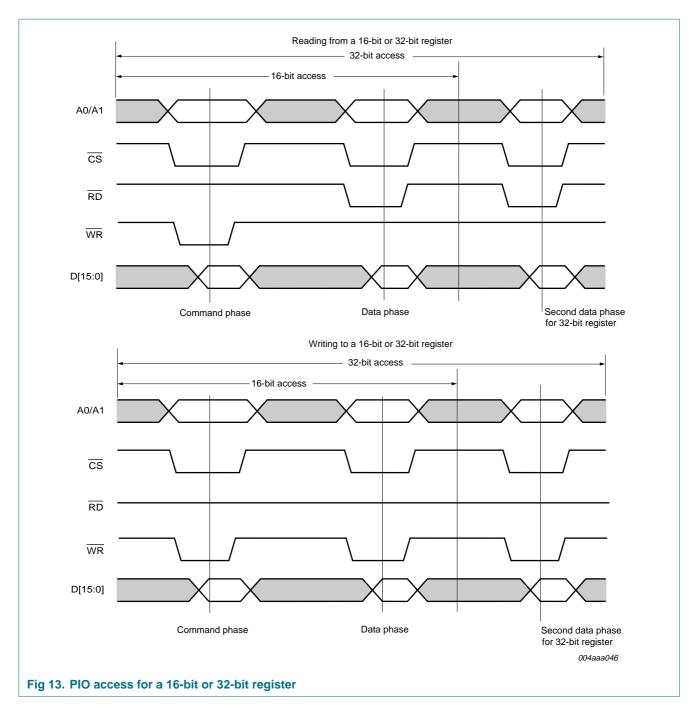

On the 16-bit data bus of a microprocessor, a command occupies the lower byte and the upper byte is filled with zeros (see Figure 12).

For 32-bit registers, the access cycle is shown in <u>Figure 13</u>. It consists of a command phase followed by two data phases.

#### **Single-chip USB OTG Controller**

004aaa045

D[15:0]

Fig 12. PIO register access

D[15:0]

#### **Single-chip USB OTG Controller**

The following is a sample code for PIO access to internal control registers:

```

unsigned long read_reg32(unsigned char reg_no)

{

unsigned int result_l,result_h;

unsigned long result;

outport(hc_com, reg_no); // Command phase

result_l = inport(hc_data); // Data phase

result_h = inport(hc_data); // Data phase

```

```

result = result h;

result = result << 16;

result = result+result 1;

return(result);

void write_reg32(unsigned char reg_no, unsigned long data2write)

unsigned int low word;

unsigned int hi_word;

low word=data2write&0x0000FFFF;

hi_word=(data2write&0xFFFF0000)>>16;

outport(hc_com,reg_no|0x80); // Command phase

outport(hc_data,low_word); // Data phase

outport(hc_data,hi_word); // Data phase

unsigned int read_reg16(unsigned char reg_no)

unsigned int result;

outport(hc_com, reg_no); // Command phase

result = inport(hc_data); // Data phase

return(result);

void write reg16(unsigned char reg no, unsigned int data2write)

outport(hc_com,reg_no|0x80); // Command phase

outport(hc_data,data2write); // Data phase

```

#### 8.5 PIO access to the buffer memory

The buffer memory in the ISP1362 can be addressed using either the direct addressing method or the indirect addressing method.

#### 8.5.1 PIO access to the buffer memory by using direct addressing

This method uses the HcDirectAddressLength register to specify two parameters required to randomly access the ISP1362 buffer memory (total of 4096 bytes). These two parameters are:

**Starting address** — location to start writing or reading **Data length** — number of bytes to write or read.

The following is a sample code to set the HcDirectAddressLength register:

#### **Single-chip USB OTG Controller**

```

void Set_DirAddrLen(unsigned int data_length,unsigned int addr)

{

unsigned long RegData = 0;

RegData =(long)(addr&0x7FFF);

RegData|=(((long)data_length)<<16);

write_reg32(HcDirAddrLen,RegData);

}</pre>

```

After the proper value is written to the HcDirectAddressLength register, data is accessible from the HcDirectAddressData register (called as HcDirAddr\_Port in the following sample code). A sample code to write word\_size bytes of data from \*w\_ptr to the memory locations of the ISP1362 buffer starting from the address start\_addr is as follows:

Direct addressing allows fast and random access to any location within the ISP1362 memory. Your program, however, needs the address location of each buffer area to access them.

#### 8.5.2 PIO access to the buffer memory by using indirect addressing

Indirect addressing is the addressing method that is compatible with NXP ISP1161 addressing mode. This method uses a unique data port for each buffer memory area (ATL, INTL, ISTL0 and ISTL1). These four data areas share the HcTransferCounter register that is used to indicate the number of bytes to be transferred.

A sample code to write an array at \*a\_ptr into the ATL memory area with word\_size as the word size is given as follows:

#### **Single-chip USB OTG Controller**

**Remark:** The HcTransferCounter register counts the number of bytes even though the transfer is in number of words. Therefore, the transfer counter must be set to word\_size  $\times$  2. Incorrect setting of the HcTransferCounter register may cause the ISP1362 to go into an indeterminate state.

The buffer memory access using indirect addressing always starts from location 0 of each buffer area. Only the front portion of the memory (example: first 64 bytes of a 1024 bytes buffer) can be accessed. Therefore, to access a portion of the memory that does not start from memory location 0, all memory locations before that location must be accessed in a sequential order. The method is similar to the sequential file access method.

## 8.6 Setting up a DMA transfer

The ISP1362 uses two DMA channels to individually serve the Host Controller and the Peripheral Controller. The DMA transfer allows the system CPU to work on other tasks while the DMA controller transfers data to or from the ISP1362. The DMA slave controller, in the ISP1362, is compatible with the 8327 type DMA controller.

The DMA transfer can be used with direct addressing mode or indirect addressing mode. The registers used in these two modes are shown in <u>Table 6</u>.

Table 6. Registers used in addressing modes

| Addressing mode[1]  | HcDMAConfiguration bit[3:1] | Total bytes to transfer |

|---------------------|-----------------------------|-------------------------|

| Direct addressing   | 1XXB                        | HcDirectAddressLength   |

| Indirect addressing | 0XXB                        | HcTransferCounter       |

<sup>[1]</sup> In direct addressing mode, HcTransferCounter must be set to 0001h.

#### 8.6.1 Configuring registers for a DMA transfer

To set up a DMA transfer, the following Host Controller registers must be configured, depending on the type of transfer required:

- HcHardwareConfiguration

- DREQ1 output polarity (bit 5)

- DACK1 input polarity (bit 6)

- DACK mode (bit 8)

- HcµPInterruptEnable

- If you want an interrupt to be generated after the DMA transfer is complete, set EOTInterruptEnable (bit 3).

- HcuPInterrupt

- Before initiating the DMA transfer, clear AllEOTInterrupt (bit 3). This bit is set when the DMA transfer is complete.

ISP1362\_5 © NXP B.V. 2007. All rights reserved.

#### **Single-chip USB OTG Controller**

- HcTransferCounter

- If DMACounterEnable of the HcDMAConfiguration register is set (that is, the DMA counter is enabled), HcTransferCounter must be set to the number of bytes to be transferred.

- HcDMAConfiguration

- Read or write DMA (bit 0)

- Targeted buffer: ISTL0, ISTL1, ATL and INTL (bits 1 to 3)

- DMA enable or disable (bit 4)

- Burst length (bits 5 to 6)

- DMA counter enable (bit 7)

**Remark:** Configure the HcDMAConfiguration register only after you have configured all the other registers. The ISP1362 will assert DREQ1 once the DMA enable bit in this register is set.

#### 8.6.2 Combining the two DMA channels

The ISP1362 allows systems with limited DMA channels to use a single DMA channel (DMA1) for both the Host Controller and the Peripheral Controller. This option can be enabled by writing logic 1 to the OneDMA bit of the HcHardwareConfiguration register. If this option is enabled, the polarity of the Peripheral Controller DMA and the Host Controller DMA must be set to DACK active LOW and DREQ active HIGH.

## 8.7 Interrupts

Various events in the Host Controller, the Peripheral Controller and the OTG Controller can be programmed to generate a hardware interrupt. By default, the interrupt generated by the Host Controller and the OTG Controller is routed out at the INT1 pin and the interrupt generated by the Peripheral Controller is routed out at the INT2 pin.

#### 8.7.1 Interrupt in the Host Controller and the OTG Controller

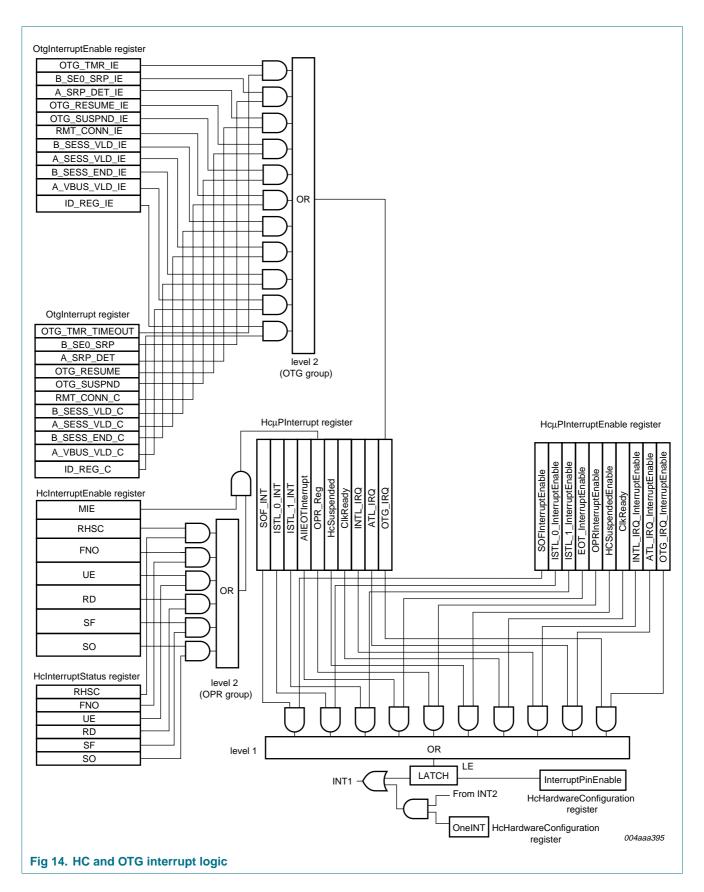

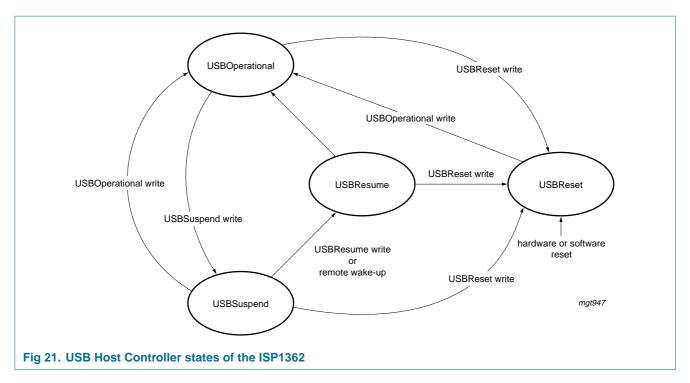

There are two levels of interrupts represented by level 1 and level 2 (see Figure 14).

#### **Single-chip USB OTG Controller**

Interrupt level 2 (OPR group) contains six possible interrupt events (recorded in the HcInterruptStatus register). When any of these events occurs, the corresponding bit will be set to logic 1, and if the corresponding bit in the HcInterruptEnable register is also logic 1, the 6-input OR gate will output logic 1. This output is combined with the value of MIE (bit 31 of HcInterruptEnable) using the AND operation and logic 1 output at this AND gate will cause the OPR bit in the HcµPInterrupt register to be set to logic 1.

Interrupt level 2 (OTG group) contains 11 possible interrupt events (recorded in the OtgInterrupt register). When any of these events occurs, the corresponding bit will be set to logic 1, and if the corresponding bit in the OtgInterruptEnable register is also logic 1, the 11-input OR gate will output logic 1 and cause the OTG\_IRQ bit in the Hc $\mu$ PInterrupt register to be set to logic 1.

Level 1 interrupts contains 10 possible interrupt events. The HcµPInterrupt and HcµPInterruptEnable registers work in the same way as the HcInterruptStatus and HcInterruptEnable registers. The output from the 10-input OR gate is connected to a latch, which is controlled by InterruptPinEnable (the bit 0 of HcHardwareConfiguration register).

When the software wishes to temporarily disable the interrupt output of the ISP1362 Host Controller and OTG Controller, follow this procedure:

- 1. Set the InterruptPinEnable bit in the HcHardwareConfiguration register to logic 1.

- 2. Clear all bits in the HcµPInterrupt register.

- 3. Set the InterruptPinEnable bit to logic 0.

To re-enable the interrupt generation, set the InterruptPinEnable bit to logic 1.

**Remark:** The InterruptPinEnable bit in the HcHardwareConfiguration register controls the latch of the interrupt output. When this bit is set to logic 0, the interrupt output will remain unchanged, regardless of any operation on interrupt control registers.

If INT1 is asserted, and the HCD wishes to temporarily mask off the INT signal without clearing the HcµPInterrupt register, follow this procedure:

- 1. Make sure that the InterruptPinEnable bit is set to logic 1.

- 2. Clear all bits in the HcuPInterruptEnable register.

- 3. Set the InterruptPinEnable bit to logic 0.

To re-enable the interrupt generation:

- 1. Set all bits in the HcµPInterruptEnable register, according to the HCD requirements.

- 2. Set the InterruptPinEnable bit to logic 1.

#### 8.7.2 Interrupt in the Peripheral Controller

The registers that control the interrupt generation in the ISP1362 Peripheral Controller are:

- DcMode (bit 3)

- DcHardwareConfiguration (bits 0 and 1)

- DcInterruptEnable

- DcInterrupt

#### **Single-chip USB OTG Controller**

The DcMode register (bit 3) is the overall Peripheral Controller interrupt enable.

DcHardwareConfiguration determines the following features:

- Level-triggered or edge-triggered (bit 1)

- Output polarity (bit 0)

For details on the interrupt logic in the Peripheral Controller, refer to Ref. 5 "Interrupt Control application note".

#### 8.7.3 Combining INT1 and INT2

In some embedded systems, interrupt inputs to the CPU are a very scarce resource. The system designer might want to use just one interrupt line to serve the Host Controller, the Peripheral Controller and the OTG Controller. In such a case, make sure the OneINT feature is activated.

When OneINT (bit 9 of the HcHardwareConfiguration register) is set to logic 1, both the INT1 (HC or OTG Controller) interrupt and the INT2 (Peripheral Controller) interrupt are routed to pin INT1, thereby reducing hardware resource requirements.

**Remark:** Both the Host Controller (or OTG Controller) and the Peripheral Controller interrupts must be set to the same polarity (active HIGH or active LOW) and the same trigger type (edge or level). Failure to conform to this will lead to unpredictable behavior of the ISP1362.

#### 8.7.4 Behavior difference between level-triggered and edge-triggered interrupts

In many microprocessor systems, the operating system disables an interrupt when it is in an Interrupt Service Routine (ISR). If there is an interrupt event during this period, it will lead to level-triggered interrupt and edge-triggered interrupt.

#### 8.7.4.1 Level-triggered interrupt

When the ISP1362 interrupt asserts, the operating system takes no action because it disables the interrupt when it is in the ISR. The interrupt line of the ISP1362 remains asserted. When the operating system exits the ISR and re-enables the interrupt processing, it sees the asserted interrupt line and immediately enters the ISR.

#### 8.7.4.2 Edge-triggered interrupt

When the ISP1362 outputs a pulse, the operating system takes no action because it disables the interrupt when it is in the ISR. The interrupt line of the ISP1362 goes back to the inactive state. When the operating system exits the ISR and re-enables the interrupt processing, it sees no pending interrupt. As a result, the interrupt is missed.

If the system needs to know whether an interrupt (approximately 160 ns pulse width) occurs during this period, it may read the HcµPInterrupt register (see Table 69).

#### **Single-chip USB OTG Controller**

# 9. Power-On Reset (POR)

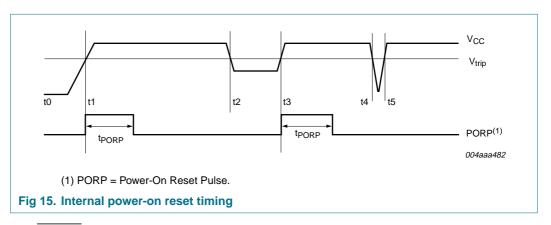

When  $V_{CC}$  is directly connected to the  $\overline{RESET}$  pin, the internal POR pulse width ( $t_{PORP}$ ) will typically be 800 ns. The pulse is started when  $V_{CC}$  rises above  $V_{trip}$  (2.03 V).

To give a better view of the functionality, <u>Figure 15</u> shows a possible curve of  $V_{CC}$  with dips at t2 to t3 and t4 to t5. If the dip at t4 to t5 is too short (that is, < 11  $\mu$ s), the internal POR pulse will not react and will remain LOW. The internal POR starts with a HIGH at t0. At t1, the detector will see the passing of the trip level and a delay element will add another  $t_{PORP}$  before it drops to LOW.

The internal POR pulse will be generated whenever  $V_{CC}$  drops below  $V_{trip}$  for more than 11  $\mu$ s.

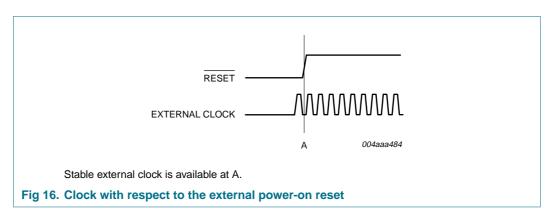

The  $\overline{\text{RESET}}$  pin can be either connected to  $V_{CC}$  (using the internal POR circuit) or externally controlled (by the micro, ASIC, and so on). Figure 16 shows the availability of the clock with respect to the external reset pulse.

**Single-chip USB OTG Controller**

# 10. On-The-Go (OTG) Controller

#### 10.1 Introduction

OTG is a supplement to the Hi-Speed USB (USB 2.0) specification that augments existing USB peripherals by adding to these peripherals limited host capability to support other targeted USB peripherals. It is primarily targeted at portable devices because it addresses concerns related to such devices, such as a small connector and low power. Non-portable devices (even standard hosts), nevertheless, can also benefit from OTG features.

The ISP1362 OTG Controller is designed to perform all the tasks specified in the OTG supplement. It supports Host Negotiation Protocol (HNP) and Session Request Protocol (SRP) for dual-role devices. The ISP1362 uses software implementation of HNP and SRP for maximum flexibility. A set of OTG registers provides the control and status monitoring capabilities to support software HNP or SRP.

Besides the normal USB transceiver, timers and analog components required by OTG are also integrated on-chip. The analog components include:

- Built-in 3.3 V-to-5 V charge pump

- Voltage comparators

- Pull-up or pull-down resistors on data lines

- Charge or discharge resistors for V<sub>BUS</sub>

#### 10.2 Dual-role device

When port 1 of the ISP1362 is configured in OTG mode, it can be used as an OTG dual-role device. A dual-role device is a USB device that can function either as a host or as a peripheral. As a host, the ISP1362 can support all four types of transfers (control, bulk, isochronous and interrupt) at full-speed or low-speed. As a peripheral, the ISP1362 can support two control endpoints and up to 14 configurable endpoints, which can be programmed to any of the four transfer types.

The default role of the ISP1362 is controlled by the ID pin, which in turn is controlled by the type of plug connected to the mini-AB receptacle. If ID = LOW (mini-A plug connected), it becomes an A-device, which is a host by default. If ID = HIGH (mini-B plug connected), it becomes a B-device, which is a peripheral by default.

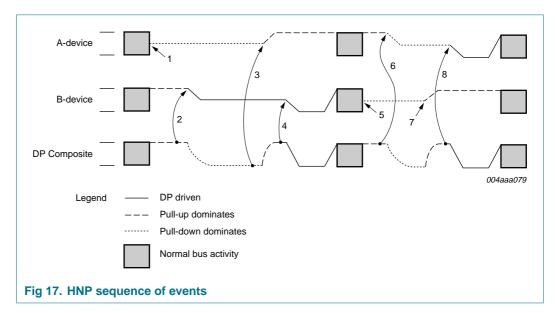

Both the A-device and the B-device work on a session base. A session is defined as the period of time in which devices exchange data. A session starts when  $V_{BUS}$  is driven and ends when  $V_{BUS}$  is turned off. Both the A-device and the B-device may start a session. During a session, the role of the host can be transferred back and forth between the A-device and the B-device any number of times by using HNP.

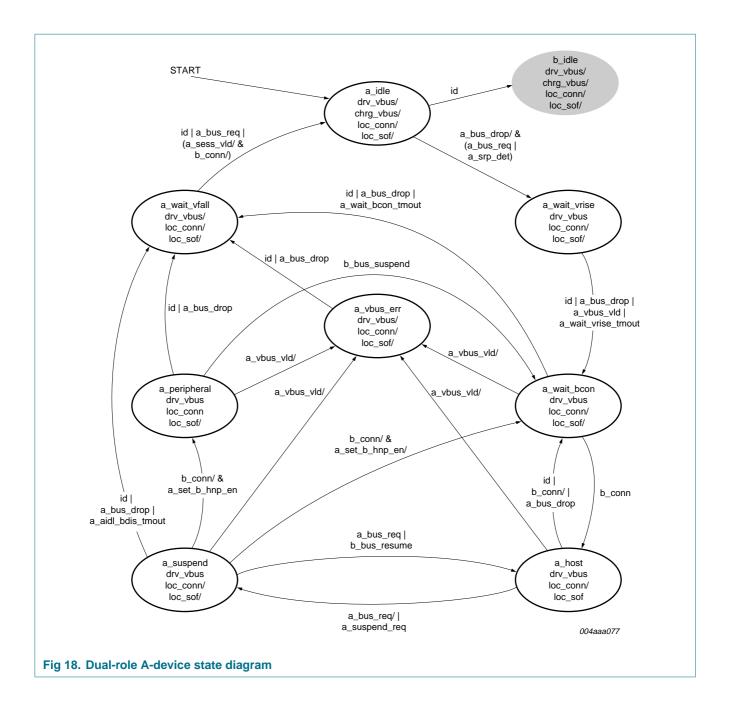

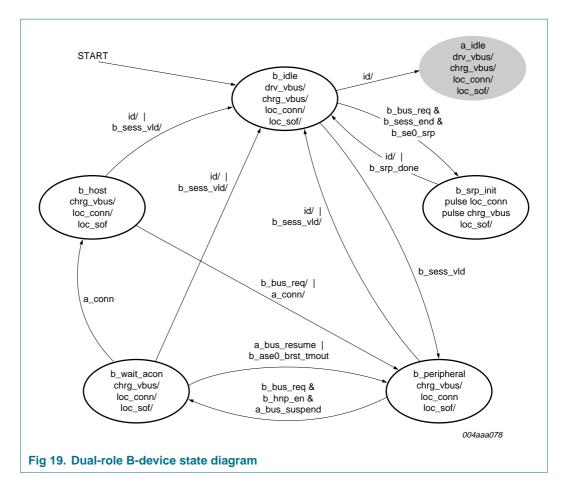

If the A-device wants to start a session, it turns on  $V_{BUS}$  by enabling the charge pump. The B-device detects that  $V_{BUS}$  has risen above the B\_SESS\_VLD level and assumes the role of a peripheral, asserting its pull-up resistor on the DP line. The A-device detects the remote pull-up resistor and assumes the role of a host. Then, the A-device can communicate with the B-device as long as it wishes. When the A-device finishes communicating with the B-device, the A-device turns-off  $V_{BUS}$  and both the devices finally go into the idle state. See Figure 18 and Figure 19.

#### Single-chip USB OTG Controller

If the B-device wants to start a session, it must initiate SRP by 'data line pulsing' and ' $V_{BUS}$  pulsing'. When the A-device detects any of these SRP events, it turns on its  $V_{BUS}$  (note that only the A-device is allowed to drive  $V_{BUS}$ ). The B-device assumes the role of a peripheral, and the A-device assumes the role of a host. The A-device detects that the B-device can support HNP by getting the OTG descriptor from the B-device. The A-device will then enable the HNP hand-off by using SetFeature (b\_hnp\_enable) and then go into the 'suspend' state. The B-device signals claiming the host role by de-asserting its pull-up resistor. The A-device acknowledges by going into the peripheral state. The B-device then assumes the role of a host and communicates with the A-device as long as it wishes. When the B-device finishes communicating with the A-device, both the devices finally go into the idle state. See Figure 18 and Figure 19.

#### 10.3 Session Request Protocol (SRP)

As a dual-role device, the ISP1362 can initiate and respond to SRP. The B-device initiates SRP by data line pulsing, followed by  $V_{BUS}$  pulsing. The A-device can detect either data line pulsing or  $V_{BUS}$  pulsing.