# ADS7869

# Analog Motor Control Front-End with Simultaneous Sampling on Seven S/H Capacitors and Three 1MSPS, 12-Bit, 12-Channel ADCs

# Data Manual

Literature Number: SBAS253E May 2003 – Revised July 2006

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SBAS253E - MAY 2003 - REVISED JULY 2006

# **Contents**

| Fe | atures .  | ures 1         |                                    |     |  |  |  |

|----|-----------|----------------|------------------------------------|-----|--|--|--|

| Αp | plication | ns             |                                    | . 1 |  |  |  |

| De | scriptio  | n              |                                    | . 1 |  |  |  |

|    | 1.1       | Ordering       | Information                        | . 2 |  |  |  |

|    | 1.2       | Absolute       | Maximum Ratings                    | . 2 |  |  |  |

|    | 1.3       | Recomm         | nended Operating Conditions        | . 2 |  |  |  |

|    | 1.4       | Package        | Dissipation Ratings                | . 2 |  |  |  |

|    | 1.5       | Electrica      | ll Characteristics                 | . 3 |  |  |  |

|    | 1.6       | Pinout D       | rawing                             | . 6 |  |  |  |

|    | 1.7       |                | ctions                             |     |  |  |  |

|    | 1.8       | Basic Cir      | rcuit Configuration                | . 9 |  |  |  |

|    | 1.9       | Typical A      | Application Circuit                | 10  |  |  |  |

|    | 1.10      |                | Characteristics                    |     |  |  |  |

|    | 1.11      | Function       | al Block Diagram                   | 15  |  |  |  |

| 2  | Analog    | <b>Section</b> |                                    | 16  |  |  |  |

|    | 2.1       | Fully Diff     | ferential Analog Inputs            | 16  |  |  |  |

|    |           | 2.1.1          | Analog-to-Digital Converter Inputs | 16  |  |  |  |

|    |           | 2.1.2          | Window Comparator Inputs           | 17  |  |  |  |

|    |           | 2.1.3          | Sign Comparator Inputs             | 17  |  |  |  |

|    | 2.2       | Analog-1       | To-Digital Converter               | 17  |  |  |  |

|    |           | 2.2.1          | HOLD1, HOLD2                       | 17  |  |  |  |

|    |           | 2.2.2          | Clock                              | 18  |  |  |  |

|    |           | 2.2.3          | Reset                              | 18  |  |  |  |

|    |           | 2.2.4          | Gain Adjustment                    | 18  |  |  |  |

|    |           | 2.2.5          | Offset Adjustment                  | 18  |  |  |  |

|    |           | 2.2.6          | Transition Noise                   | 19  |  |  |  |

|    | 2.3       | Sign Cor       | mparators                          | 19  |  |  |  |

|    | 2.4       | Window         | Comparators                        | 21  |  |  |  |

|    | 2.5       | 8-Bit Dig      | jital-to-Analog Converter          | 22  |  |  |  |

|    | 2.6       | Internal I     | Reference                          | 22  |  |  |  |

|    | 2.7       | Groundir       | ng                                 | 22  |  |  |  |

|    | 28        | Supply         |                                    | 22  |  |  |  |

SBAS253E - MAY 2003 - REVISED JULY 2006

| Digital | Section .   |                                                                                                | 23 |

|---------|-------------|------------------------------------------------------------------------------------------------|----|

| 3.1     |             | ncn                                                                                            |    |

| 3.2     | VECANA      | Interface                                                                                      | 24 |

|         | 3.2.1       | Input Channel Selection                                                                        | 25 |

|         | 3.2.2       | VECANA Timing Characteristics                                                                  |    |

|         | 3.2.3       | WINCLK Selection                                                                               |    |

| 3.3     | Serial Per  | ipheral Interface (SPI)                                                                        |    |

|         | 3.3.1       | SPI Timing Characteristics                                                                     |    |

| 3.4     | Parallel In | terface                                                                                        |    |

|         | 3.4.1       | Parallel Read and Write Control                                                                |    |

|         | 3.4.2       | Mode 10 Bus Access                                                                             |    |

|         | 3.4.3       | Mode 11 Bus Access (Standard Mode)                                                             |    |

|         | 3.4.4       | Mode 11 Bus Access (TMS320c54xx DSP Family-Compatible Mode)                                    |    |

| 3.5     | -           | Мар                                                                                            |    |

| 3.6     | -           | Descriptions                                                                                   |    |

|         | 3.6.1       | FIFO Data Register (00 <sub>H</sub> )                                                          |    |

|         | 3.6.2       | Offset Registers (01 <sub>H</sub> to 0C <sub>H</sub> )                                         |    |

|         | 3.6.3       | Gain Registers (0D <sub>H</sub> to 18 <sub>H</sub> )                                           |    |

|         | 3.6.4       | WINDAC Register (19 <sub>H</sub> )                                                             |    |

|         | 3.6.5       | Control Register (1A <sub>H</sub> )                                                            |    |

|         | 3.6.6       | Counter Control/Status Register (1BH)                                                          |    |

|         | 3.6.7       | Edge Count Register (1C <sub>H</sub> , 1D <sub>H</sub> , 20 <sub>H</sub> and 21 <sub>H</sub> ) |    |

|         | 3.6.8       | Edge Period Register (1E <sub>H</sub> and 22 <sub>H</sub> )                                    |    |

|         | 3.6.9       | Edge Time Period Register (1F <sub>H</sub> and 23 <sub>H</sub> )                               |    |

|         | 3.6.10      | FIFO Test Register (24 <sub>H</sub> )                                                          |    |

|         | 3.6.11      | Comparator Test Register (25 <sub>H</sub> )                                                    |    |

|         | 3.6.12      | Interrupt Register (26 <sub>H</sub> )                                                          |    |

|         | 3.6.13      | Parallel Register (27 <sub>H</sub> )                                                           |    |

|         | 3.6.14      | Reset Register (28 <sub>H</sub> )                                                              |    |

| 3.7     | FIFO        |                                                                                                |    |

|         | 3.7.1       | DAV Timing Characteristics                                                                     |    |

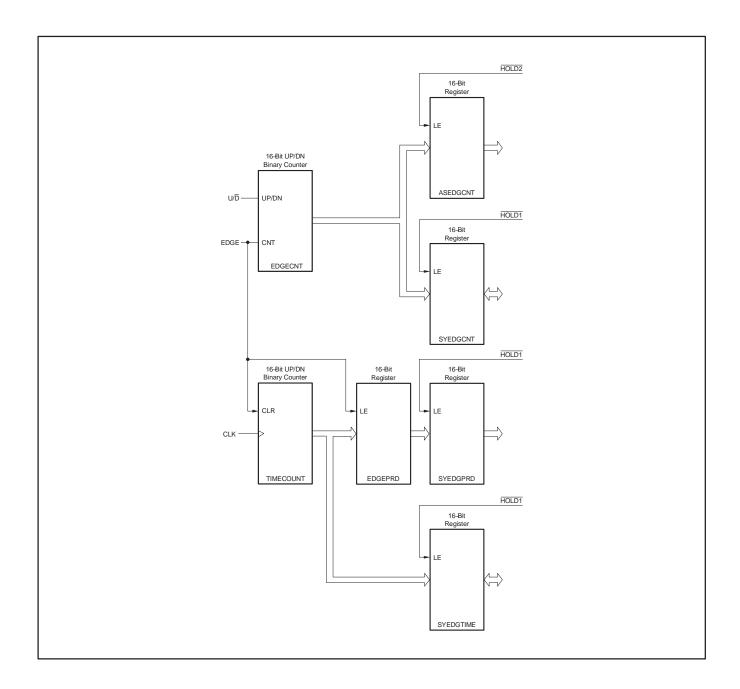

| 3.8     | 0           | unter Modules                                                                                  |    |

|         | 3.8.1       | Operation                                                                                      |    |

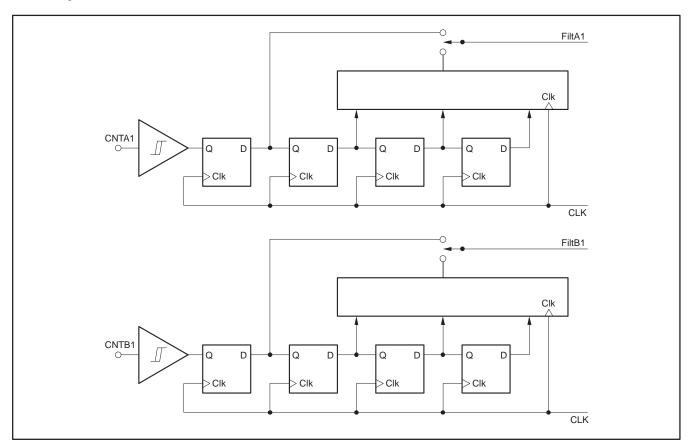

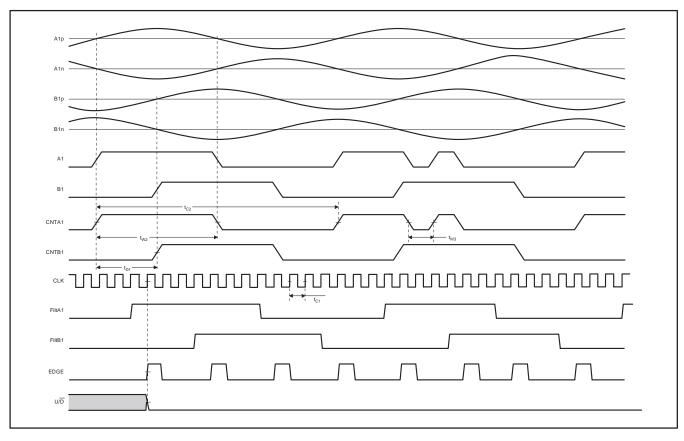

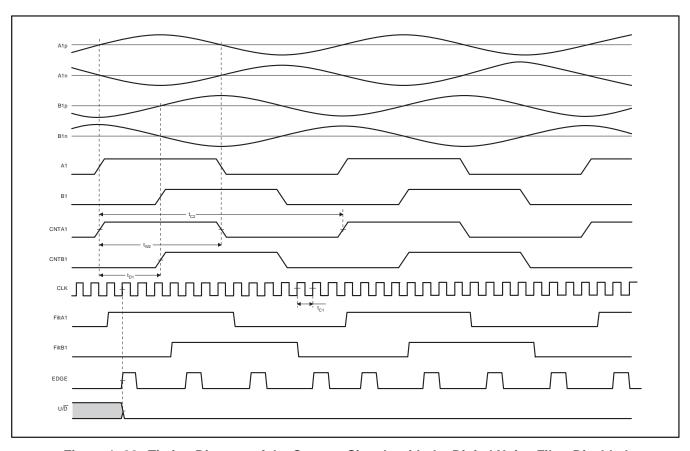

|         | 3.8.2       | Digital Noise Filter                                                                           |    |

|         | 3.8.3       | Binary Counters and Registers                                                                  |    |

| 3.9     |             |                                                                                                |    |

| 3.10    |             |                                                                                                |    |

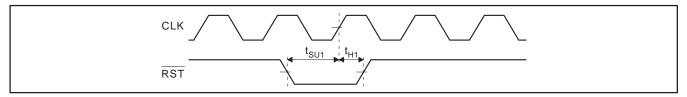

|         | 3 10 1      | Reset Timing Characteristics                                                                   | 58 |

SBAS253E - MAY 2003 - REVISED JULY 2006

# **List of Illustrations**

| 1–1.   | Typical Motor Control Application                                            | 10 |

|--------|------------------------------------------------------------------------------|----|

| 1–2. F | Functional Diagram                                                           | 15 |

| 1–3. E | Equivalent Input Circuit to the ADCs                                         | 16 |

| 1–4. E | Equivalent Input Circuit of the Window Comparators                           | 17 |

| 1–5. l | Histogram of 8000 Conversions                                                | 19 |

| 1–6. ¯ | Typical Transfer Function of a Sign Comparator                               | 19 |

| 1–7.   | Position Sensor Comparator Overdrive                                         | 20 |

| 1–8. ( | Current Sign Comparator Overdrive                                            | 20 |

| 1–9. ¯ | Typical Transfer Function of a Window Comparator                             | 21 |

| 1–10.  | VECANA Access                                                                | 26 |

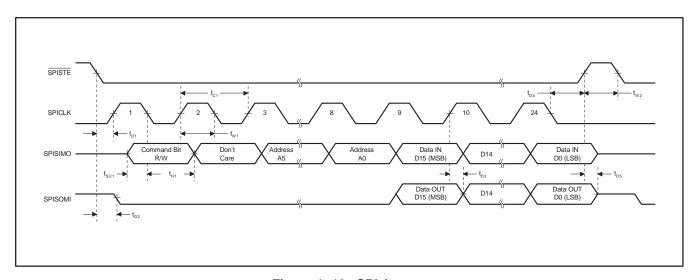

| 1–11.  | One SPI Transfer Cycle                                                       | 27 |

| 1–12.  | Continuous SPI Transfer Cycle                                                | 28 |

| 1–13.  | SPI Access                                                                   | 29 |

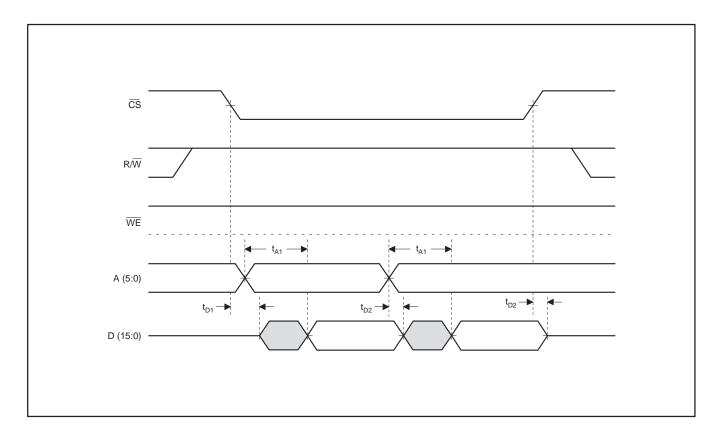

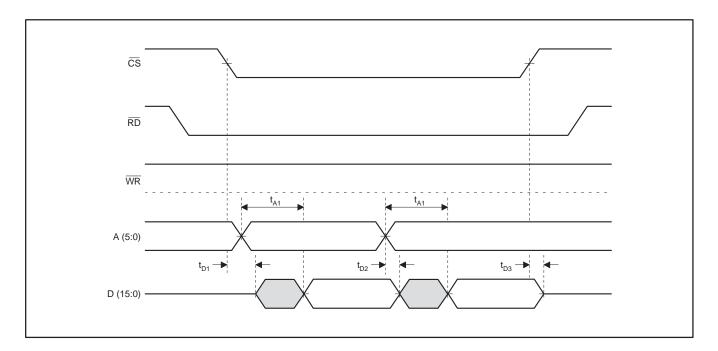

| 1–14.  | Mode 10 Read Access                                                          | 31 |

| 1–15.  | Mode 10 Write Access                                                         | 32 |

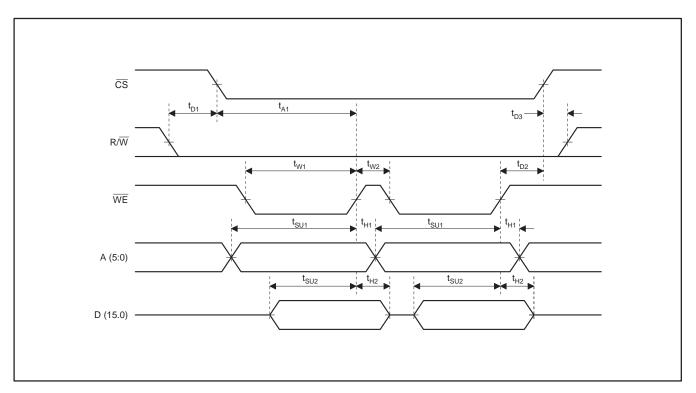

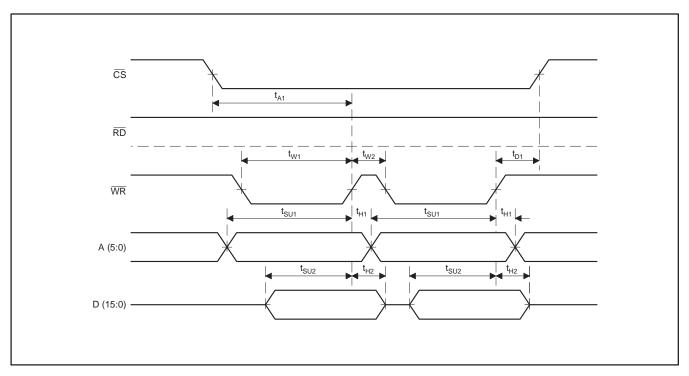

| 1–16.  | Mode 11 Read Access (Standard Mode)                                          | 33 |

| 1–17.  | Mode 11 Write Access (Standard Mode)                                         | 34 |

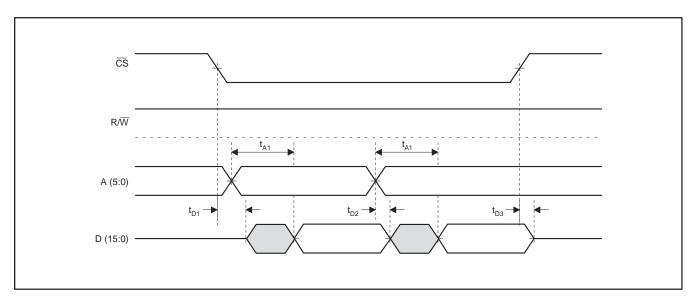

| 1–18.  | Mode 11 Read Access (TMS320c54xx mode)                                       | 35 |

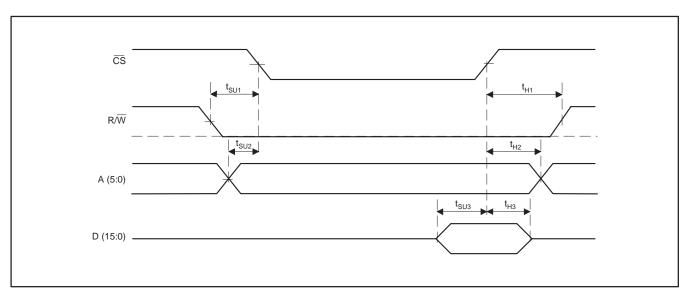

| 1–19.  | Mode 11 Write Access (TMS320c54xx mode)                                      | 36 |

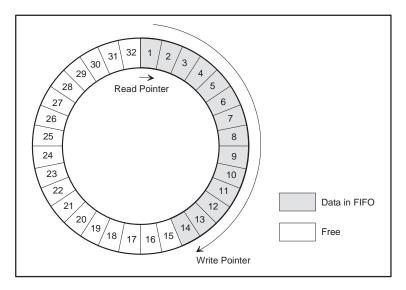

| 1–20.  | FIFO Structure                                                               | 49 |

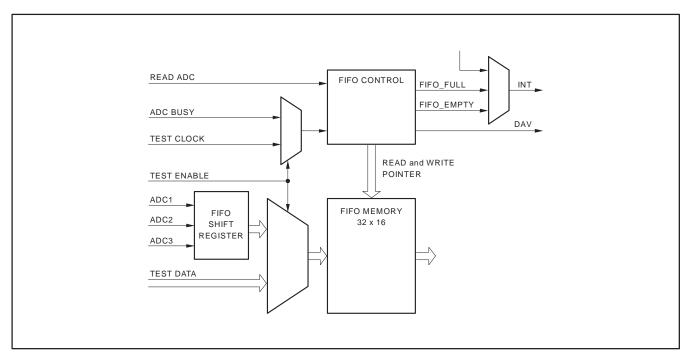

| 1–21.  | FIFO Block Diagram                                                           | 50 |

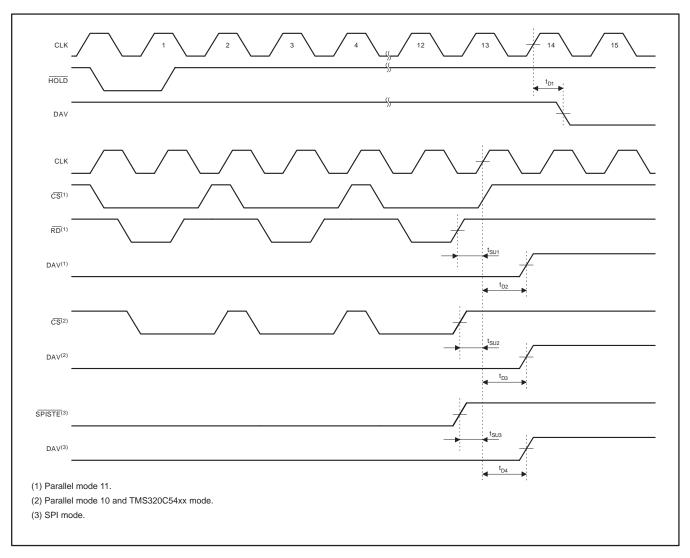

| 1–22.  | Timing of the DAV Signal                                                     | 51 |

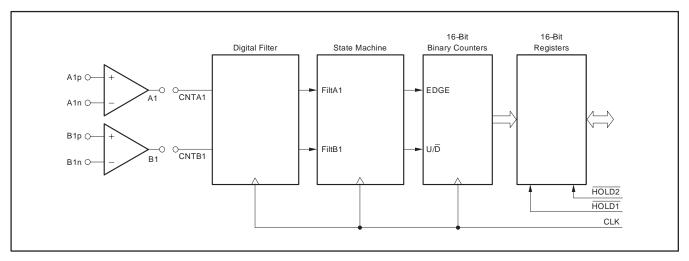

| 1–23.  | Block Diagram of a Counter Module                                            | 52 |

| 1–24.  | Digital Noise Filter Block Diagram                                           | 53 |

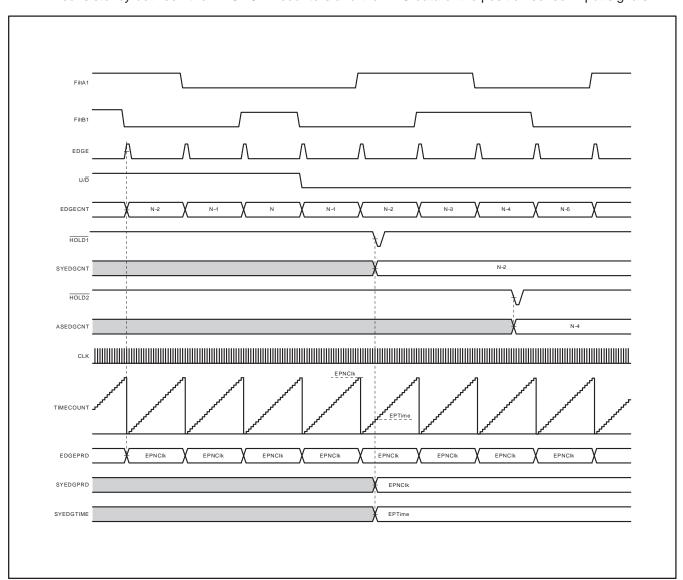

| 1–25.  | Timing Diagram of the Counter Signals with the Digital Noise Filter Enabled  | 54 |

| 1–26.  | Timing Diagram of the Counter Signals with the Digital Noise Filter Disabled | 55 |

| 1–27.  | Detail Counter Block Diagram                                                 | 56 |

| 1–28.  | Detail Counter Timing Diagram                                                | 57 |

| 1–29.  | Timing Diagram of the Reset Signal RST                                       | 58 |

# **List of Tables**

| 1–1. Select | tion of Interface Mode                      | 23         |

|-------------|---------------------------------------------|------------|

| 1-2. Mode   | vs Pin Functions                            | 23         |

| 1-3. DAC I  | Input/Output Relationships                  | 24         |

| 1-4. VECA   | ANA Gain Select Information                 | 24         |

| 1-5. 13-bit | : VECANA ADIN Word Format                   | 25         |

| 1-6. Contro | ols for Input Multiplexers and Sample Holds | 25         |

| 1-7. Windo  | ow Comparator Clock                         | 27         |

| 1-8. SPI W  | Vrite 24-bit Word Format                    | 27         |

| 1-9. Host F | Parallel Port Operation                     | 30         |

| 1-10. Regi  | ister Map Write 16-bit Data                 | 37         |

| 1-11. Regi: | ister Map Read 16-bit Data                  | 38         |

| 1–12. FIFC  | Output Word Format 3                        | 39         |

| 1–13. Offse | et Registers                                | 10         |

| 1-14. Gain  | n Registers                                 | <b>4</b> C |

| 1–15. WINI  | DAC Register                                | <b>4</b> C |

| 1-16. Cont  | trol Registers                              | 11         |

| 1-17. Cour  | nter/Control Status Register                | 12         |

| 1-18. Sync  | chronous Latched Edge Count Register 4      | 13         |

| 1-19. Asyn  | nchronous Latched Edge Count Register       | 13         |

| 1–20. Edge  | e Period Register                           | 13         |

| 1–21. Edge  | e Time Period Register                      | 14         |

| 1-22. FIFC  | D Test Register                             | 14         |

| 1-23. Com   | nparator Test Register                      | 15         |

| 1-24. Inter | rupt Register                               | 16         |

| 1-25. Para  | allel Register                              | 17         |

| 1–26. Rese  | et Register                                 | 48         |

| 1_27 FIFC   | 2.16-bit Data Read Format                   | 10         |

SBAS253E - MAY 2003 - REVISED JULY 2006

# **FEATURES**

- Seven Simultaneously-Sampling Sample-and-Hold (S/H) Capacitors

- Fully Differential Inputs

- Flexible Digital Interface with Four Modes

- One Mode 100% Software-Compatible to VECANA01

- SPI and Two Parallel Modes

- Two Up-Down Counter Modules On-Chip

- 12-Bit System Gain Adjustment for Every Channel

- 12-Bit Accurate System Offset Adjustment for Every Channel

# **APPLICATIONS**

Motor Control

### DESCRIPTION

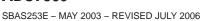

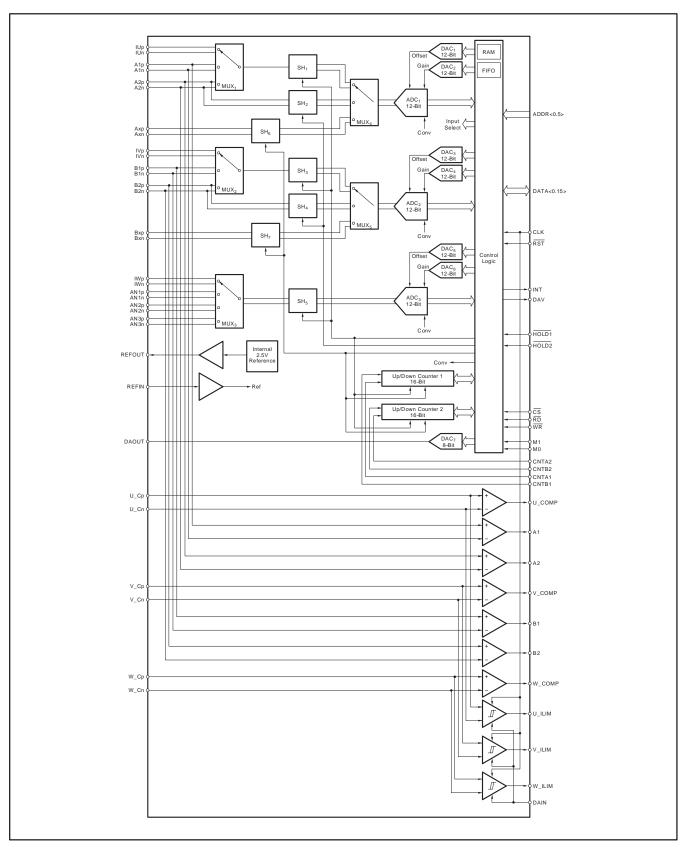

The ADS7869 is a motor control front-end that includes three analog-to-digital converters (ADCs) with a total of seven sample-and-hold capacitors and 12 fully differential input channels. There are four sign comparators connected to four input channels. There are also three additional fully differential inputs; each input is connected to a window comparator and a sign comparator.

In addition, the ADS7869 also offers a very flexible digital interface with a parallel port that can be configured to different standards. Furthermore, a serial peripheral interface (SPI) and a specialized serial interface with three data lines (VECANA01 mode) are provided. This allows the ADS7869 to interface with most digital signal processors (DSPs) or microcontrollers. The chip is specialized for motor-control applications. For the position sensor analysis, two up–down counters are added on the silicon. This feature ensures that the analog input of the encoder is held at the same point of time as the counter value.

SBAS253E - MAY 2003 - REVISED JULY 2006

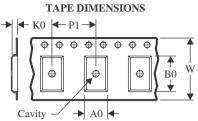

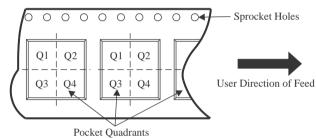

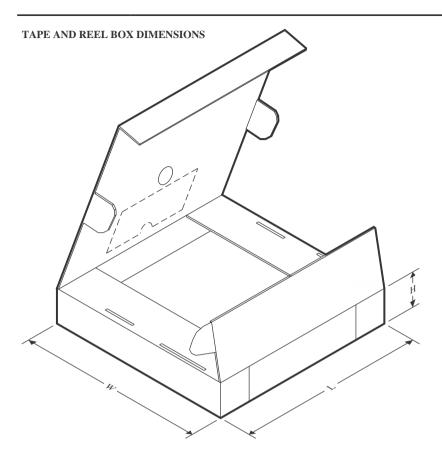

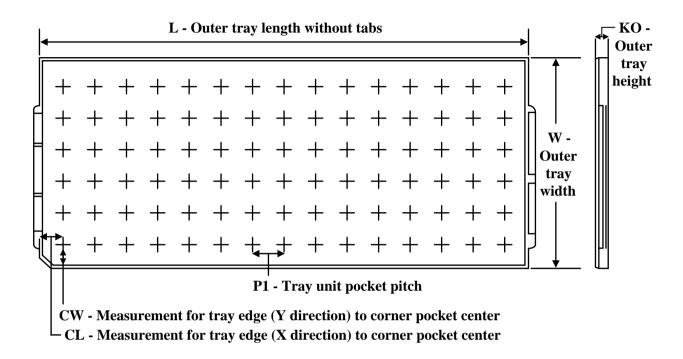

### 1.1 ORDERING INFORMATION(1)

| PRODUCT  | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>ERROR (LSB) | NO MISSING<br>CODES<br>ERROR (LSB) | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA,<br>QUANTITY |

|----------|-------------------------------------------------|------------------------------------|------------------|-----------------------|-----------------------------------|--------------------|---------------------------------|

|          |                                                 |                                    |                  |                       |                                   | ADS7869IPZT        | Tray, 90                        |

| ADS7869I | ±2                                              | 11                                 | TQFP-100         | PZT                   | -40°C to +85°C                    | ADS7869IPZTR       | Tape and Reel,<br>1000          |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum located at the end of this data manual.

#### 1.2 ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted(1)

|                                                             | ADS7869I                             | UNIT |

|-------------------------------------------------------------|--------------------------------------|------|

| Supply voltage, AV <sub>DD</sub> to AGND                    | -0.3 to 6                            | V    |

| Supply voltage, BV <sub>DD</sub> to BGND                    | -0.3 to 6                            | V    |

| Analog input voltage with respect to AGND                   | AGND – 0.3 to AV <sub>DD</sub> + 0.3 | V    |

| Reference input voltage with respect to AGND                | AGND – 0.3 to AV <sub>DD</sub> + 0.3 | V    |

| Digital input voltage with respect to BGND                  | BGND – 0.3 to BV <sub>DD</sub> + 0.3 | V    |

| Ground voltage difference AGND to BGND                      | ± 0.3                                | V    |

| Input current to any pin except supply                      | -10 to +10                           | mA   |

| Operating virtual junction temperature range, TJ            | -40 to +150                          | °C   |

| Operating free-air temperature range, T <sub>A</sub>        | -40 to +85                           | °C   |

| Storage temperature range, T <sub>STG</sub>                 | -65 to +150                          | °C   |

| Lead temperature 1,6mm (1/16-inch) from case for 10 seconds | +260                                 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 1.3 RECOMMENDED OPERATING CONDITIONS

|                                                                   |                    | MIN      | NOM | MAX      | UNIT |

|-------------------------------------------------------------------|--------------------|----------|-----|----------|------|

| Supply Voltage, AGND to AV <sub>DD</sub>                          |                    | 4.5      | 5   | 5.5      | V    |

| Supply Voltage, BGND to BV <sub>DD</sub>                          | Low-Voltage Levels | 2.7      |     | 3.6      | V    |

|                                                                   | 5V Logic Levels    | 4.5      | 5   | 5.5      | V    |

| Reference Input Voltage                                           |                    | 2.475    | 2.5 | 2.525    | V    |

| Analog Inputs (also see Fully Differential Analog Inputs section) | +IN - (-IN)        | -REF_ADC |     | +REF_ADC | V    |

| Operating junction temperature range, T <sub>J</sub>              |                    | -40      | •   | +85      | °C   |

### 1.4 PACKAGE DISSIPATION RATINGS

| BOARD     | PACKAGE | $R_\ThetaJC$ | $R_{\Theta}JA$ | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|-----------|---------|--------------|----------------|------------------------------------------------|----------------------------------------------------|---------------------------------------|---------------------------------------|

| Low-K(1)  | PZT     | 3.5°C/W      | 45°C/W         | 22.222mW/°C                                    | 2778mW                                             | 1778mW                                | 1444mW                                |

| High-K(2) | PZT     | 3.5°C/W      | 2.82°C/W       | 35.461mW/°C                                    | 4433mW                                             | 2837mW                                | 2305mW                                |

<sup>(1)</sup> The JEDEC Low-K (1s) board design used to derive this data was a 3-inch x 3-inch, two-layer board with 2-ounce copper traces on top of the board.

<sup>(2)</sup> The JEDEC High-K (2s2p) board design used to derive this data was a 3-inch x 3-inch, multilayer board with 1-ounce internal power and ground planes and 2-ounce copper traces on the top and bottom of the board.

SBAS253E - MAY 2003 - REVISED JULY 2006

# 1.5 ELECTRICAL CHARACTERISTICS

Over recommended operating free-air temperature range at  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $\text{AV}_{DD} = 5\text{V}$ ,  $\text{BV}_{DD} = 3.3\text{V}$ ,  $\text{V}_{REF} = \text{internal} +2.5\text{V}$ ,  $\text{f}_{CLK} = 16\text{MHz}$ ,  $\text{f}_{SAMPLE} = 1$  MSPS, unless otherwise noted.

| PARAMETER                                    | CONDITION                            | MIN                 | TYP(1) | MAX                    | UNIT   |

|----------------------------------------------|--------------------------------------|---------------------|--------|------------------------|--------|

| Resolution                                   |                                      | 12                  |        |                        | Bit    |

| Analog Input                                 |                                      |                     |        |                        |        |

| Full-scale Voltage, Differential             | See Gain Adjustment                  | -REF_ADC            |        | +REF_ADC               | V      |

| Input Capacitance                            |                                      |                     | 10     |                        | pF     |

| Input Leakage Current                        |                                      |                     | ±1     |                        | nA     |

| CMRR                                         | At DC                                |                     | 64     |                        | dB     |

| DC Accuracy                                  |                                      |                     |        |                        |        |

| No Missing Codes                             |                                      | 11                  |        |                        | Bit    |

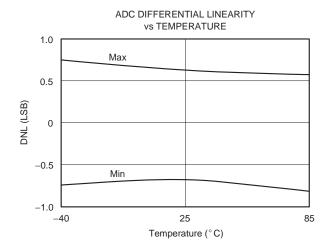

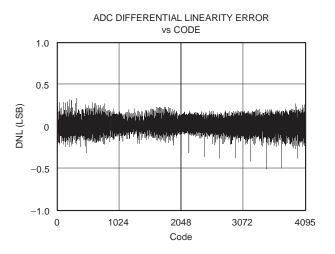

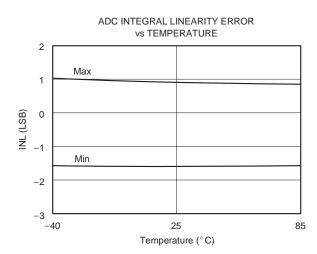

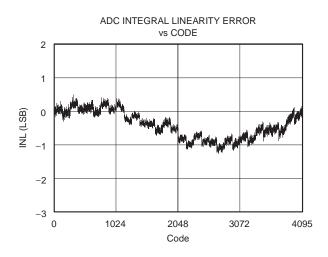

| INL Integral Linearity Error                 |                                      |                     | ±1     | ±2.5                   | LSB    |

| DNL Differential Linearity Error             |                                      |                     | ±0.65  | ±2                     | LSB    |

| V <sub>OS</sub> Bipolar Offset Error         | Synchronous Channels                 |                     | 2      | ±6                     | LSB    |

| V <sub>OS</sub> Bipolar Offset Error         | AX and BX Channels                   |                     | 5      | ±8                     | LSB    |

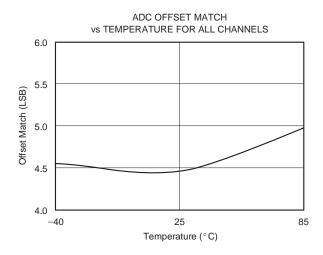

| Vos Bipolar Offset Match                     | IU, IV, and IW Channels              |                     | 2.5    | 6                      | LSB    |

| V <sub>OS</sub> Bipolar Offset Match         | A1, B1, A2, and B2 Channels          |                     | 0.5    | 3                      | LSB    |

| V <sub>OS</sub> Bipolar Offset Match         | AX and BX Channels                   |                     | 0.5    | 3                      | LSB    |

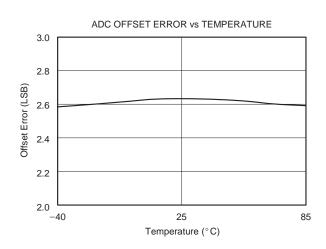

| TCV <sub>OS</sub> Bipolar Offset Error Drift |                                      |                     | 1      | † †                    | μV/°C  |

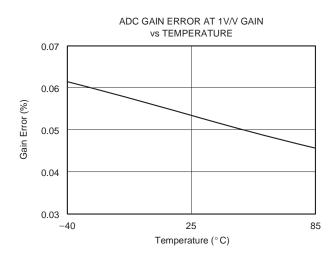

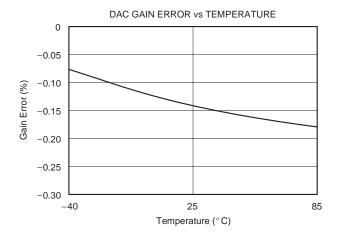

| Gain Error                                   | Max Input Range, Related to REFIN    |                     | 0.05   | 1                      | %      |

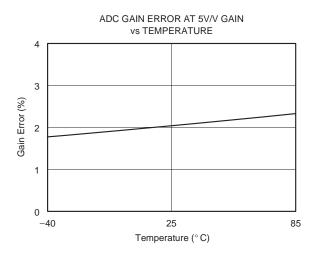

| Gain Error                                   | Every Other Input Range              |                     | 1.5    | 4                      | %      |

| Gain Error Drift                             | Max Input Range, Related to REFIN    |                     | 3      |                        | ppm/°C |

| PSRR Power-Supply Rejection Ratio            | 4.5V < AV <sub>DD</sub> < 5.5V       |                     | 70     |                        | dB     |

| Sampling Dynamics                            |                                      |                     |        |                        |        |

| t <sub>CONV</sub> Conversion Time per ADC    | 16MHz ≤ f <sub>CLK</sub> ≤ 1MHz      | 0.75                |        | 12                     | μS     |

| t <sub>AQ</sub> Acquisition Time             | 02.1                                 | 250                 |        |                        | ns     |

| Throughput Rate                              |                                      |                     |        | 1000                   | kSPS   |

| Aperture Delay                               |                                      |                     |        | 20                     | ns     |

| Aperture Delay Matching                      |                                      |                     | 1      |                        | ns     |

| Aperture Jitter                              |                                      |                     | 50     |                        | ps     |

| Clock Frequency                              |                                      | 1                   |        | 16                     | MHz    |

| AC Accuracy                                  |                                      |                     |        | 1                      |        |

| Total Harmonic Distortion THD                | $V_{IN} = \pm 2.5 V_{PP}$ at 10kHz   |                     | -78    |                        | dB     |

| Signal-to-Noise Distortion SNR               | $V_{IN} = \pm 2.5 V_{PP}$ at 10kHz   |                     | 71     |                        | dB     |

| Signal-to-Noise + Distortion SINAD           | $V_{IN} = \pm 2.5 V_{PP}$ at 10kHz   |                     | 70     |                        | dB     |

| Digital Inputs(2)                            |                                      |                     |        |                        |        |

| Logic Family                                 |                                      |                     | CMOS   | T 1                    |        |

| V <sub>IH</sub> High-Level Input Voltage     |                                      | 0.7•V <sub>DD</sub> |        | BV <sub>DD</sub> + 0.3 | V      |

| V <sub>II</sub> Low-Level Input Voltage      |                                      | -0.3                |        | 0.3•V <sub>DD</sub>    | V      |

| IN Input Current                             | BV <sub>DD</sub> to BGND             |                     |        | ±50                    | nA     |

| C <sub>I</sub> Input Capacitance             |                                      |                     | 5      | † †                    | pF     |

| Digital Outputs <sup>(2)</sup>               |                                      |                     |        |                        | •      |

| Logic Family                                 |                                      |                     | CMOS   |                        |        |

| VOH High-Level Output Voltage                | $BV_{DD} = 4.5V, I_{OH} = -100\mu A$ | 4.44                |        | † †                    | V      |

| V <sub>OL</sub> Low-Level Output Voltage     | $BV_{DD} = 4.5V, I_{OL} = +100\mu A$ |                     |        | 0.5                    | V      |

| IOZ High-Impedance-State Output Current      | $V_I = BV_{DD}$ to BGND              |                     |        | ±50                    | nA     |

| CO Output Capacitance                        | . 22                                 |                     | 5      | †                      | pF     |

| C <sub>L</sub> Load Capacitance              |                                      |                     |        | 30                     | pF     |

<sup>(1)</sup> All values are at  $T_A = +25^{\circ}C$ .

<sup>(2)</sup> Applies for 5.0V nominal supply: 4.5V < BV<sub>DD</sub> < 5.5V.

<sup>(3)</sup> Applies for 3.0V nominal supply: 2.7V < BV<sub>DD</sub> < 3.6V.

SBAS253E - MAY 2003 - REVISED JULY 2006

## 1.5 ELECTRICAL CHARACTERISTICS (continued)

Over recommended operating free-air temperature range at -40 °C to +85 °C,  $AV_{DD} = 5V$ ,  $BV_{DD} = 3.3V$ ,  $V_{REF} = internal +2.5V$ ,  $f_{CLK} = 16MHz$ ,  $f_{SAMPLE} = 1$  MSPS, unless otherwise noted.

|                                               |                                                   |                        | ADS7869I |                        |        |

|-----------------------------------------------|---------------------------------------------------|------------------------|----------|------------------------|--------|

| PARAMETER                                     | CONDITION                                         | MIN                    | TYP(1)   | MAX                    | UNIT   |

| Digital Inputs(3)                             |                                                   |                        |          | 1                      |        |

| Logic Family                                  |                                                   |                        | LVCMOS   |                        |        |

| VIH High-Level Input Voltage                  | BV <sub>DD</sub> = 3.6V                           | 2                      |          | BV <sub>DD</sub> + 0.3 | V      |

| V <sub>II</sub> Low-Level Input Voltage       | BV <sub>DD</sub> = 2.7V                           | -0.3                   |          | 0.8                    | V      |

| I <sub>IN</sub> Input Current                 | $V_I = BV_{DD}$ to BGND                           |                        |          | ±50                    | nA     |

| C <sub>I</sub> Input Capacitance              | . 55                                              |                        | 5        |                        | pF     |

| Digital Outputs(3)                            |                                                   |                        |          |                        | ·      |

| Logic Family                                  |                                                   |                        | LVCMOS   |                        |        |

| VOH High-Level Output Voltage                 | $BV_{DD} = 2.7V, I_{OH} = -100\mu A$              | BV <sub>DD</sub> – 0.2 |          |                        | V      |

| V <sub>OL</sub> Low-Level Output Voltage      | BV <sub>DD</sub> = 2.7V, I <sub>OL</sub> = +100μA |                        |          | 0.2                    | V      |

| IOZ High-Impedance-State Output Current       | $V_I = BV_{DD}$ to BGND                           |                        |          | ±50                    | nA     |

| CO Output Capacitance                         |                                                   |                        | 5        |                        | pF     |

| C <sub>L</sub> Load Capacitance               |                                                   |                        |          | 30                     | pF     |

| Power Supply                                  |                                                   |                        |          |                        | •      |

| AV <sub>DD</sub> Analog Supply Voltage        |                                                   | 4.5                    |          | 5.5                    | V      |

| BV <sub>DD</sub> Buffer I/O Supply Voltage    |                                                   | 2.7                    |          | 5.5                    | V      |

| AIDD Analog Supply Current                    |                                                   |                        | 45       | 50                     | mA     |

| BI <sub>DD</sub> Buffer I/O Supply Voltage    |                                                   |                        | 2        |                        | mA     |

| Power Dissipation                             |                                                   |                        |          | 250                    | mW     |

| Reference Output                              |                                                   |                        |          |                        |        |

| V <sub>REF</sub> Reference Output Voltage     | -40°C > t > +85°C                                 | 2.475                  | 2.500    | 2.525                  | V      |

| V <sub>REF</sub> Reference Output Voltage     | at 25°C                                           | 2.480                  | 2.500    | 2.520                  | V      |

| dV <sub>REF</sub> /dT Reference Voltage Drift |                                                   |                        | ±20      |                        | ppm/°C |

| PSRR Power-Supply Rejection Ratio             |                                                   |                        | 60       |                        | dB     |

| IOUT Output Current                           | DC Current                                        |                        |          | 1                      | μΑ     |

| I <sub>SC</sub> Short-Circuit Current         |                                                   |                        | 1        |                        | mA     |

| t <sub>ON</sub> Turn-On Setting Time          |                                                   |                        | 100      |                        | μs     |

| Reference Input                               |                                                   | •                      |          | •                      |        |

| V <sub>IN</sub> Reference Input Voltage       |                                                   | 2.475                  | 2.5      | 2.525                  | V      |

| Input Resistance                              |                                                   |                        | 100      |                        | ΜΩ     |

| Input Capacitance                             |                                                   |                        | 5        |                        | pF     |

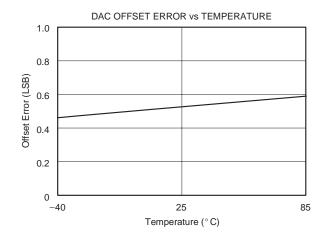

| Digital-to-Analog Converter                   |                                                   |                        |          |                        | •      |

| Resolution                                    |                                                   | 8                      |          |                        | Bits   |

| Output Range                                  | I <sub>OUT</sub> = 0                              | 0                      |          | 2.49                   | V      |

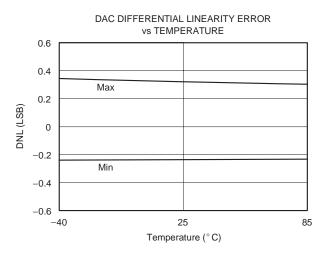

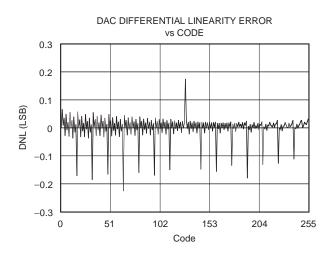

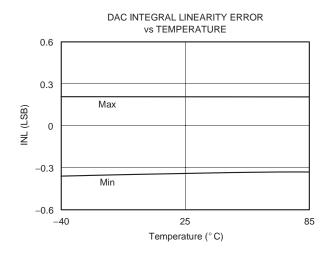

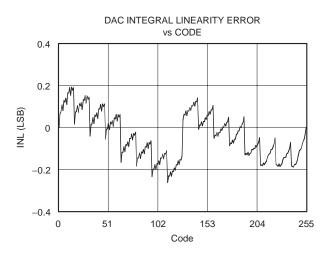

| INL Integral Linearity Error                  | 551                                               |                        |          | ±1                     | LSB    |

| DNL Differential Linearity Error              |                                                   |                        |          | ±2                     | LSB    |

| Offset Error                                  |                                                   |                        | 0.5      | 1                      | LSB    |

| Full-Scale Error                              | FS = Internal Reference Voltage - 1LSB            |                        |          | ±1                     | %      |

| IOUT Output Current                           |                                                   |                        |          | 0.5                    | μΑ     |

| Output Settling Time                          | to 0.5LSB, no load capacitance                    |                        | 0.2      | 1                      | μs     |

| Position Sensor Sign Comparator               |                                                   | •                      |          |                        |        |

| Input Range                                   | Lower Voltage of Differential Inputs              | 0                      |          | AV <sub>DD</sub> – 1.8 | V      |

| Offset Range                                  |                                                   | 1                      | ±5       | ±30                    | mV     |

| Hysteresis                                    |                                                   | 1                      | 75       | 100                    | mV     |

| Delay Time                                    |                                                   | 1                      | 25       | 150                    | ns     |

<sup>(1)</sup> All values are at  $T_A = +25^{\circ}C$ .

<sup>(2)</sup> Applies for 5.0V nominal supply: 4.5V < BV<sub>DD</sub> < 5.5V.

<sup>(3)</sup> Applies for 3.0V nominal supply: 2.7V < BV<sub>DD</sub> < 3.6V.

SBAS253E - MAY 2003 - REVISED JULY 2006

## 1.5 ELECTRICAL CHARACTERISTICS (continued)

Over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $AV_{DD} = 5$ V,  $BV_{DD} = 3.3$ V,  $V_{REF} = internal +2.5$ V,  $f_{CLK} = 16$ MHz,  $f_{SAMPLE} = 1$  MSPS, unless otherwise noted.

|                               |                                      |      | ADS7869I |                        |      |

|-------------------------------|--------------------------------------|------|----------|------------------------|------|

| PARAMETER                     | CONDITION                            | MIN  | TYP(1)   | MAX                    | UNIT |

| Current Sign Comparator       | •                                    | •    | •        |                        |      |

| Input Range                   | Lower Voltage of Differential Inputs | 0    |          | AV <sub>DD</sub> – 1.8 | V    |

| Offset Range                  |                                      |      | ±2       | ±20                    | mV   |

| Hysteresis                    |                                      |      | 10       | 30                     | mV   |

| Delay Time                    |                                      |      | 25       | 150                    | ns   |

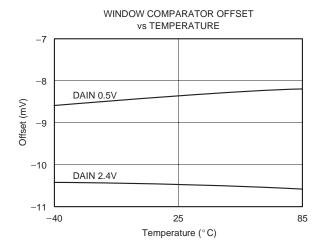

| Window Comparator             |                                      |      |          |                        |      |

| Input Range                   |                                      | -0.3 |          | $AV_{DD} + 0.3$        | V    |

| Offset Range                  |                                      |      | ±10      | ±30                    | mV   |

| Hysteresis                    |                                      | 60   | 70       | 80                     | mV   |

| Delay Time                    | f <sub>CLK</sub> = 16MHz             |      | 250      | 375                    | ns   |

| Threshold Voltage Input Range | (DAIN pin)                           | 0.5  | 1        | 2.5                    | V    |

<sup>(1)</sup> All values are at  $T_A = +25$ °C.

<sup>(2)</sup> Applies for 5.0V nominal supply:  $4.5V < BV_{DD} < 5.5V$ .

<sup>(3)</sup> Applies for 3.0V nominal supply: 2.7V < BV<sub>DD</sub> < 3.6V.

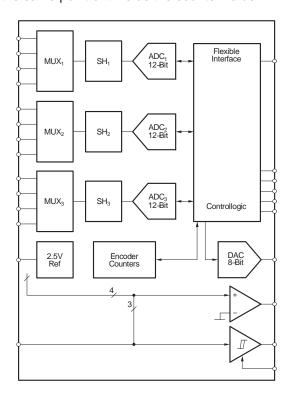

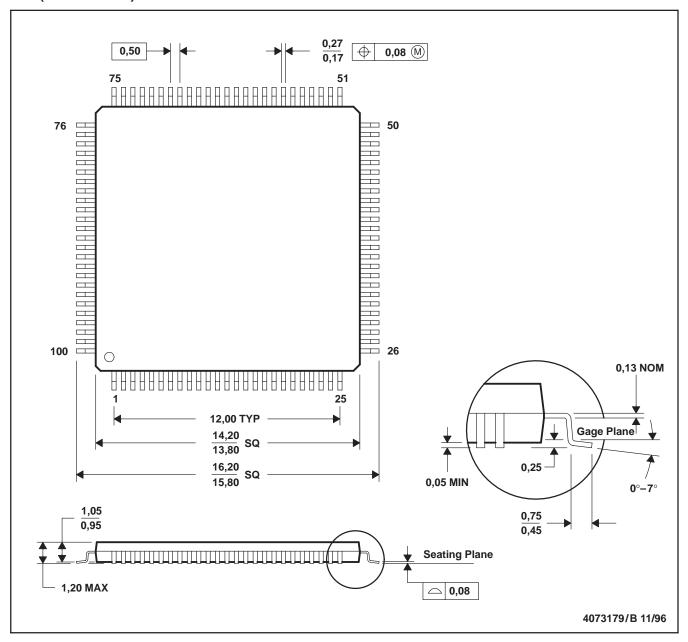

#### 1.6 PINOUT DRAWING

### TQFP Package

SBAS253E - MAY 2003 - REVISED JULY 2006

# 1.7 PIN FUNCTIONS

# **TQFP Package**

| SIGNAL     | PIN NUMBER | TYPE        | DESCRIPTION                                                         |

|------------|------------|-------------|---------------------------------------------------------------------|

| ANALOG SIG | NALS       |             |                                                                     |

|            |            | Analog      | Input Signals of Position Sensors                                   |

| A1p        | 2          | Analog In   | Position Sensor 1, Analog Input of SIN, Positive Input              |

| A1n        | 1          | Analog In   | Position Sensor 1, Analog Input of SIN, Negative Input              |

| В1р        | 24         | Analog In   | Position Sensor 1, Analog Input of COS, Positive Input              |

| B1n        | 25         | Analog In   | Position Sensor 1, Analog Input of COS, Negative Input              |

| AXp        | 7          | Analog In   | Position Sensor X, Asynchronous Analog Input of SIN, Positive Input |

| AXn        | 6          | Analog In   | Position Sensor X, Asynchronous Analog Input of SIN, Negative Input |

| A2p        | 100        | Analog In   | Position Sensor 2, Analog Input of SIN, Positive Input              |

| A2n        | 99         | Analog In   | Position Sensor 2, Analog Input of SIN, Negative Input              |

| В2р        | 26         | Analog In   | Position Sensor 2, Analog Input of COS, Positive Input              |

| B2n        | 27         | Analog In   | Position Sensor 2, Analog Input of COS, Negative Input              |

| ВХр        | 19         | Analog In   | Position Sensor X, Asynchronous Analog Input of COS, Positive Input |

| BXn        | 20         | Analog In   | Position Sensor X, Asynchronous Analog Input of COS, Negative Input |

|            |            | Coun        | ter Signals of Position Sensors                                     |

| A1         | 91         | Digital Out | Sign of SIN Signal, Position Sensor 1                               |

| B1         | 38         | Digital Out | Sign of COS Signal, Position Sensor 1                               |

| A2         | 89         | Digital Out | Sign of SIN Signal, Position Sensor 2                               |

| B2         | 40         | Digital Out | Sign of COS Signal, Position Sensor 2                               |

| CNTA1      | 90         | Digital In  | Input Signal SIN to 16-bit Up/Down Counter 1                        |

| CNTB1      | 88         | Digital In  | Input Signal COS to 16-bit Up/Down Counter 1                        |

| CNTA2      | 39         | Digital In  | Input Signal SIN to 16-bit Up/Down Counter 2                        |

| CNTB2      | 41         | Digital In  | Input Signal COS to 16-bit Up/Down Counter 2                        |

|            |            | Analog      | Input Signals of Phase Currents                                     |

| IUp        | 4          | Analog In   | Phase U Current, Positive Input                                     |

| IUn        | 3          | Analog In   | Phase U Current, Negative Input                                     |

| IVp        | 22         | Analog In   | Phase V Current, Positive Input                                     |

| IVn        | 23         | Analog In   | Phase V Current, Negative Input                                     |

| IWp        | 17         | Analog In   | Phase W Current, Positive Input                                     |

| IWn        | 16         | Analog In   | Phase W Current, Negative Input                                     |

SBAS253E - MAY 2003 - REVISED JULY 2006

# **TQFP Package**

| PIN NUMBER        | TYPE                                                                                                                                                                                                              | DESCRIPTION                                                                 |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| •                 | Compa                                                                                                                                                                                                             | rator Signals of Phase Currents                                             |  |  |  |  |  |

| 29                | Analog Out                                                                                                                                                                                                        | 8-Bit DAC Output for Over-Current Limit Value                               |  |  |  |  |  |

| 30                | Analog In                                                                                                                                                                                                         | Over-Current Limit Value as Input for Window Comparators                    |  |  |  |  |  |

| 31                | Analog In                                                                                                                                                                                                         | Phase U Current Signal Input for Sign and Window Comparator, Positive Input |  |  |  |  |  |

| 32                | Analog In                                                                                                                                                                                                         | Phase U Current Signal Input for Sign and Window Comparator, Negative Inpu  |  |  |  |  |  |

| 33                | Analog In                                                                                                                                                                                                         | Phase V Current Signal Input for Sign and Window Comparator, Positive Input |  |  |  |  |  |

| 34                | Analog In                                                                                                                                                                                                         | Phase V Current Signal Input for Sign and Window Comparator, Negative Input |  |  |  |  |  |

| 35                | Analog In                                                                                                                                                                                                         | Phase W Current Signal Input for Sign and Window Comparator, Positive Input |  |  |  |  |  |

| 36                | Analog In                                                                                                                                                                                                         | Phase W Current Signal Input for Sign and Window Comparator, Negative Input |  |  |  |  |  |

| 42                | Digital Out                                                                                                                                                                                                       | Sign of Phase U Current                                                     |  |  |  |  |  |

| 43                | Digital Out                                                                                                                                                                                                       | Sign of Phase V Current                                                     |  |  |  |  |  |

| 44                | Digital Out                                                                                                                                                                                                       | Sign of Phase W Current                                                     |  |  |  |  |  |

| 45                | Digital Out                                                                                                                                                                                                       | Over-current Output of Phase U, Active Low Output                           |  |  |  |  |  |

| 46                | Digital Out                                                                                                                                                                                                       | Over-current Output of Phase V, Active Low Output                           |  |  |  |  |  |

| 47                | Digital Out                                                                                                                                                                                                       | Over-current Output of Phase W, Active Low Output                           |  |  |  |  |  |

|                   |                                                                                                                                                                                                                   | Other Analog Signals                                                        |  |  |  |  |  |

| 15, 12, 10        | Analog In                                                                                                                                                                                                         | Auxiliary Analog Input Channel (x), Positive Input                          |  |  |  |  |  |

| 14, 11, 9         | Analog In                                                                                                                                                                                                         | Auxiliary Analog Input Channel (x), Negative Input                          |  |  |  |  |  |

| 97                | Analog In                                                                                                                                                                                                         | Reference Voltage Input Pin                                                 |  |  |  |  |  |

| 96                | Analog Out                                                                                                                                                                                                        | Reference Voltage Output Pin                                                |  |  |  |  |  |

| 84, 92, 93, 94    | _                                                                                                                                                                                                                 | No connection (should be left open)                                         |  |  |  |  |  |

| RFACE SIGNALS     |                                                                                                                                                                                                                   | •                                                                           |  |  |  |  |  |

| 56 – 51           | Digital In                                                                                                                                                                                                        | Address Decode Input <sup>(1)</sup>                                         |  |  |  |  |  |

| 75 – 60           | Digital In/Out                                                                                                                                                                                                    | Bidirectional 3-state Data Bus <sup>(1)</sup>                               |  |  |  |  |  |

| 57                | Digital In                                                                                                                                                                                                        | Active Low Chip-Select Signal <sup>(1)</sup>                                |  |  |  |  |  |

| 59                | Digital In                                                                                                                                                                                                        | Active Low Read Signal <sup>(1)</sup>                                       |  |  |  |  |  |

| 58                | Digital In                                                                                                                                                                                                        | Active Low Write Signal <sup>(1)</sup>                                      |  |  |  |  |  |

| 77                | Digital In                                                                                                                                                                                                        | System Clock                                                                |  |  |  |  |  |

| 49                | Digital Out                                                                                                                                                                                                       | Active High Interrupt Output                                                |  |  |  |  |  |

| 79                | Digital In                                                                                                                                                                                                        | Active Low Reset Input                                                      |  |  |  |  |  |

| 81, 80            | Digital In                                                                                                                                                                                                        | Mode Select Pins(1)                                                         |  |  |  |  |  |

| 83                | Digital Out                                                                                                                                                                                                       | Data Available Signal                                                       |  |  |  |  |  |

| 87                | Digital In                                                                                                                                                                                                        | Active Low Convert Start and Synchronous Hold Signal for Sample-and-Hold    |  |  |  |  |  |

|                   |                                                                                                                                                                                                                   | Amplifiers                                                                  |  |  |  |  |  |

| 86                | Digital In                                                                                                                                                                                                        | Active Low Asynchronous Hold Signal for Sample-and-Hold Amplifiers          |  |  |  |  |  |

| LY                |                                                                                                                                                                                                                   |                                                                             |  |  |  |  |  |

| 8, 18, 28, 85, 98 | Power                                                                                                                                                                                                             | Analog Power Supply                                                         |  |  |  |  |  |

| 48, 78            | Power                                                                                                                                                                                                             | Interface Power Supply                                                      |  |  |  |  |  |

| 5, 21, 37, 82, 95 |                                                                                                                                                                                                                   | Analog Ground                                                               |  |  |  |  |  |

| 50, 76            |                                                                                                                                                                                                                   | Interface Ground                                                            |  |  |  |  |  |

| 13                |                                                                                                                                                                                                                   | Signal Ground                                                               |  |  |  |  |  |

|                   | 29 30 31 31 32 33 34 35 36 42 43 44 45 46 47  15, 12, 10 14, 11, 9 97 96 84, 92, 93, 94  RFACE SIGNALS  56 – 51 75 – 60 57 59 58 77 49 79 81, 80 83 87  86  LY  8, 18, 28, 85, 98 48, 78 5, 21, 37, 82, 95 50, 76 | 29                                                                          |  |  |  |  |  |

<sup>(1)</sup> See Digital section for detailed information about the different modes.

SBAS253E - MAY 2003 - REVISED JULY 2006

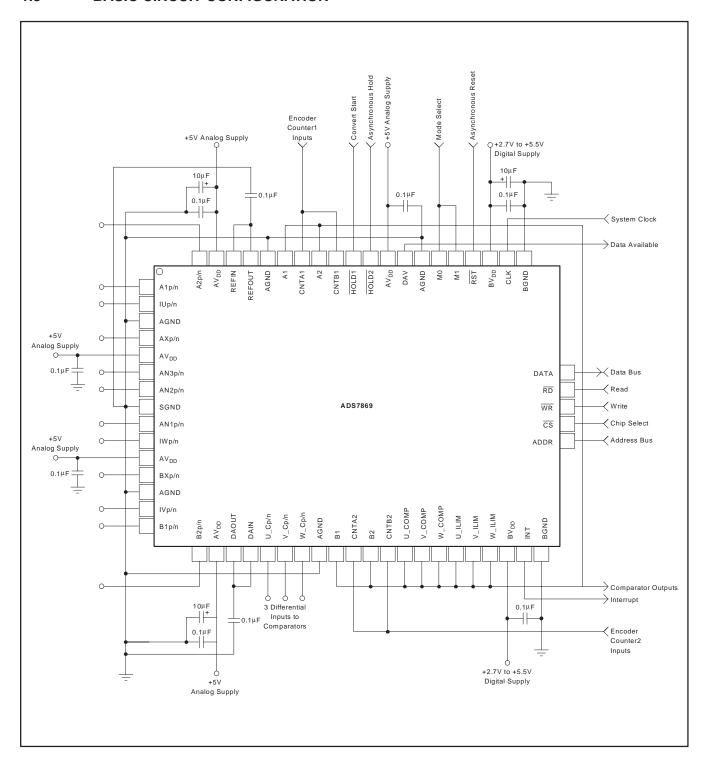

### 1.8 BASIC CIRCUIT CONFIGURATION

#### 1.9 TYPICAL APPLICATION CIRCUIT

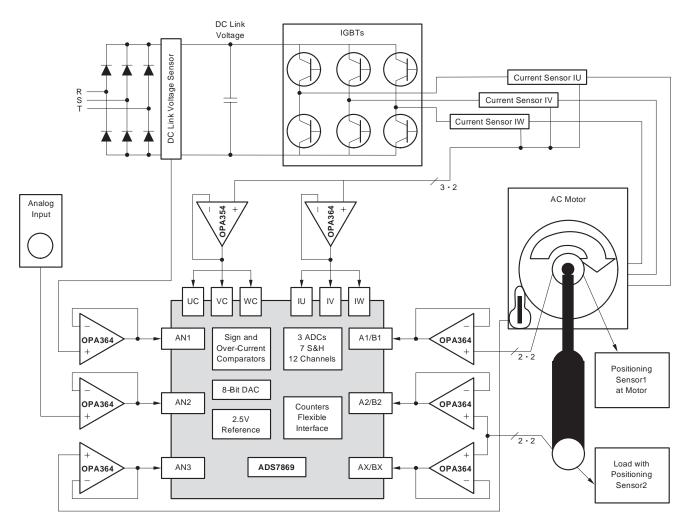

Figure 1-1. Typical Motor Control Application

Figure 1–1 shows an example of a typical motor control circuit. The IU, IV and IW channels measure the currents of the motor. The position (speed) of the motor and load are measured simultaneously by A1, B1 and A2, B2, respectively, using resolver or analog encoder sensors. The asynchronous inputs AX and BX can be used to capture the reference signal of encoders to derive the absolute position. Channel AN1 measures the differential DC link voltage. AN3 measures the temperature of the motor. An auxiliary voltage can be measured with channel AN2. The counter inputs connect to the appropriate comparator outputs (A1 to CNTA1, B1 to CNTB1 and so on). The level input of the window comparators, DAIN, should be connected to the 8-bit DAC output DAOUT.

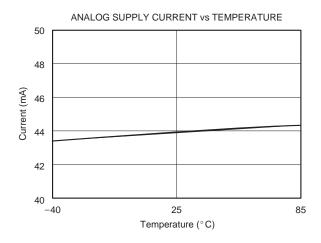

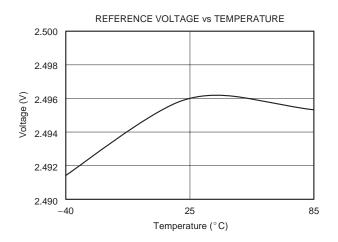

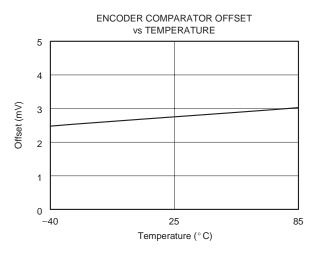

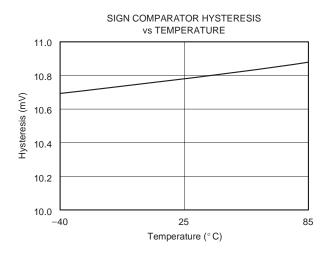

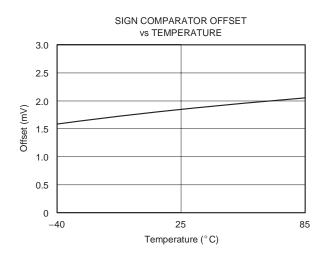

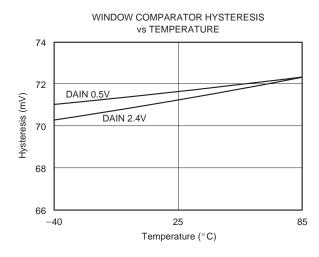

### 1.10 TYPICAL CHARACTERISTICS

At  $T_A = +25$ °C,  $AV_{DD} = 5V$ ,  $BV_{DD} = 3.3V$ ,  $V_{REF} = internal +2.5V$ ,  $f_{CLK} = 16MHz$ ,  $f_{SAMPLE} = 1$  MSPS, unless otherwise noted.

SBAS253E - MAY 2003 - REVISED JULY 2006

### TYPICAL CHARACTERISTICS (Continued)

At TA = +25°C, AVDD = 5V, BVDD = 3.3V, VREF = internal +2.5V, fCLK = 16MHz, fSAMPLE = 1 MSPS, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (Continued)**

At T<sub>A</sub> = +25°C, AV<sub>DD</sub> = 5V, BV<sub>DD</sub> = 3.3V, V<sub>REF</sub> = internal +2.5V, f<sub>CLK</sub> = 16MHz, f<sub>SAMPLE</sub> = 1 MSPS, unless otherwise noted.

SBAS253E - MAY 2003 - REVISED JULY 2006

### **TYPICAL CHARACTERISTICS (Continued)**

At TA = +25°C, AVDD = 5V, BVDD = 3.3V, VREF = internal +2.5V, fCLK = 16MHz, fSAMPLE = 1 MSPS, unless otherwise noted.

# 1.11 FUNCTIONAL BLOCK DIAGRAM

Figure 1-2. Functional Diagram

# 2 Analog Section

The analog section addresses the Analog-to-Digital Converters, including the gain and offset adjustment. There is also a discussion of the analog inputs, the seven sign comparators, three window comparators, the 8-bit Digital-to-Analog Converter (DAC), the reference voltage, grounding, and the supply voltage.

### 2.1 Fully Differential Analog Inputs

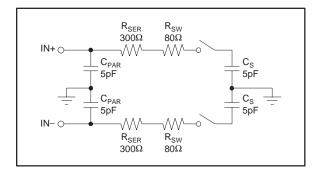

### 2.1.1 Analog-to-Digital Converter Inputs

The 12 inputs to the ADCs, as well as the three inputs (U\_C, V\_C and W\_C) to the comparators, are fully differential and provide a good common-mode rejection of 60dB at 50kHz. This is very important to suppress noise in difficult environments.

The seven sample-and-hold circuits from the ADC contain a 5pF capacitor ( $C_S$  in Figure 1–3) that is connected via a switch to the analog inputs. Opening the switch holds the data. The switch closes when the conversion is finished. The capacitor is then loaded to an initial voltage that is equal to the reference at the ADC, which is selected with the gain adjustment.

The voltage of the input pin is usually different from the voltage of the sample capacitor when the input switch closes. The sample capacitor needs to be recharged to the 12-bit accuracy, one-half of a least significant bit (LSB), within an acquisition time  $(t_{AQ})$  of at least 200ns.

The minimum –3dB bandwidth of the driving operational amplifier can be calculated to:

$$f_{3db} = \frac{\ln(2) \cdot (n+1)}{2\pi \cdot t_{AQ}} \tag{1}$$

where n is equal to 12, the resolution of the ADC (in the case of the ADS7869). When  $t_{AQ}$  = 200ns, the minimum bandwidth of the driving amplifier is 7MHz. The bandwidth can be relaxed if the acquisition time is increased by the application.

The OPA364 from Texas Instruments is recommended; besides the necessary bandwidth, it provides a low offset in a small package at a low price.

The phase margin of the driving operational amplifier is usually reduced by the sampling capacitor of the ADC. A resistor between the capacitor and the amplifier reduces this effect; therefore, an internal  $300\Omega$  resistor (R<sub>SER</sub>) is in series with the switch. The resistance of the closed switch (R<sub>SW</sub>) is approximately  $80\Omega$ . See Figure 1–3.

Figure 1-3. Equivalent Input Circuit to the ADCs

The differential input range (positive minus negative input) of the ADC is ±REF\_ADC, the reference of the converter, which is selected with the gain adjustment.

It is important that the voltage to all inputs does not exceed more than 0.3V above the analog supply or 0.3V below the ground. There is no DC current flow through the inputs. Current is only necessary when recharging the sample-and-hold capacitors,  $C_S$ .

SBAS253E - MAY 2003 - REVISED JULY 2006

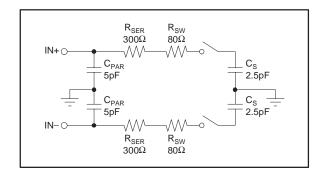

### 2.1.2 Window Comparator Inputs

A sampling architecture was selected for the window comparators. The sampling time is two clock cycles with a minimum  $t_{AQ}$  (see Equation 1) of 125ns. The necessary accuracy is 10mV (see 8-bit DAC section) with a 5V input range. The required bandwidth of the driving amplifier is 8.8MHz (see Equation 1). The OPAx354 from Texas Instruments is recommended.

The input circuit of the window comparator is similar to the ADC inputs. The only difference is that the sampling capacitors are reduced to 2.5pF. (See Figure 1–4.)

Figure 1-4. Equivalent Input Circuit of the Window Comparators

### 2.1.3 Sign Comparator Inputs

Four sign comparators are connected to the ADC inputs (A1, B1, A2 and B2); three of the sign comparators are wired to the window comparator inputs (U\_C, V\_C, and W\_C).

The sample capacitors of the ADCs and the window comparators could produce voltage glitches; therefore, it is important to drive the inputs with low impedance.

The lower voltage of the differential input should remain within the range of 0 to  $AV_{DD}$ -1.8V.

#### 2.2 Analog-To-Digital Converter

The ADS7869 includes three, SAR-type, 1MSPS, 12-bit ADCs, and three pairs of S/H capacitors, which are each connected to ADC<sub>1</sub> and ADC<sub>2</sub>. A single S/H capacitor is connected to ADC<sub>3</sub>. Gain and offset adjustments are added to each ADC. (See Figure 1–2 on page 15.)

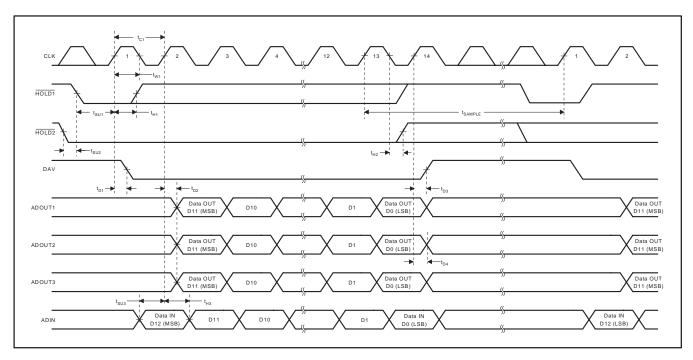

### 2.2.1 **HOLD1**, **HOLD2**

The analog inputs are held when the  $\overline{HOLDx}$  signals go low. The charges of the synchronous sample-and-holds (S/H<sub>1-5</sub>) are frozen on the falling edge of  $\overline{HOLD1}$ . The setup time of  $\overline{HOLD1}$ , against the rising edge of the system clock, is typically 25ns. The conversion will automatically start on the next rising edge of the clock. The S/Hs are switched back into the sample mode when the conversion is finished, 12 clock cycles later. This point of time is indicated by DAV. (See Figure 1–10 on page 26.)  $\overline{HOLD1}$  must go high at the latest at the 13th falling clock after conversion start.

The asynchronous sample and holds  $(S/H_{6-7})$  are triggered by the active low  $\overline{HOLD2}$  signal. The setup time of  $\overline{HOLD2}$ , against the falling edge of  $\overline{HOLD1}$ , is 0ns; see Figure 1–10. The conversion of these S/H circuits is initiated when they are selected through the digital interface and the  $\overline{HOLD1}$  signal goes low. The inputs are connected back to the S/H capacitor when the  $\overline{HOLD2}$  signal goes high.  $\overline{HOLD2}$  needs to be low during the whole conversion. It is possible to connect  $\overline{HOLD1}$  and  $\overline{HOLD2}$  together.

TEXAS INSTRUMENTS

SBAS253E - MAY 2003 - REVISED JULY 2006

#### 2.2.2 Clock

The ADC uses the external clock CLK, which needs to be in the range of 1MHz to 16MHz. 12 clock cycles are necessary for a conversion, with a minimum of four clock cycles for the acquisition. Therefore, the maximum throughput rate of 1MSPS is achieved with a 16MHz clock and 16 clock cycles per complete conversion cycle. The duty cycle should be 50%; however, the ADS7869 will still function properly with a duty cycle between 30% and 70%.

#### 2.2.3 Reset

A reset condition stops any ongoing conversion and reconnects the synchronous S/Hs to the inputs; see the *Reset* Section.

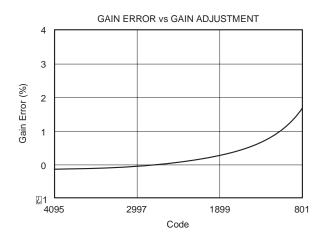

### 2.2.4 Gain Adjustment

The output of a 12-bit DAC (REF\_ADC) is used as the reference voltage for the ADC. There is one DAC for each ADC. The voltage range is between 0V (code  $000_H$ ) and the 2.5V of REFIN (code FFF<sub>H</sub>). The ADC operates correctly if the selected voltage is in the range of 0.5V to 2.5V. The output voltage of the DAC sets the differential input range of the ADC, which is  $\pm$ REF\_ADC. The desired input range can be adjusted in 1.22mV steps.

In the VECANA mode, the gain information contained in the digital input word ADIN automatically sets the DAC value. See the *Vecana Interface* section for further information.

In all other modes, there is a register for every input channel inside the digital interface, which stores the gain information for any given channel. When a particular channel is selected by the application, the value of this register is automatically written to the DAC and the DAC output is adjusted to the desired value. The DAC settles to this value within 250ns (equivalent to the minimum acquisition time).

The gain information inside the registers is set to zero when a reset condition occurs. These registers need to be set to the selected value before the ADCs are used.

In VECANA mode, the DAC is initially set to Full-Scale and the differential input range is equal to  $\pm$ (voltage at the REFIN pin).

**CAUTION:** An essential offset error occurs when data is held on the sampling capacitors A2 and B2 (or AX and BX) and the gain of the ADC is modified in intermediate conversions before converting the particular channels A2 and B2 (or AX and BX). This offset error is possible under two conditions:

- Data can be held on the asynchronous sample-and-hold capacitors AX and BX with the HOLD2 signal.

Other channels can be converted before the asynchronous signals AX and BX. The offset error occurs if the gain is changed during these conversions.

- 2. With the input commands 4–6, channels A1 and B1 are held together with A2 and B2. Channels A1 and B1 will be converted first. During this conversion or further intermediate conversions, the offset error occurs if the gain is modified before the conversion of channels A2 and B2.

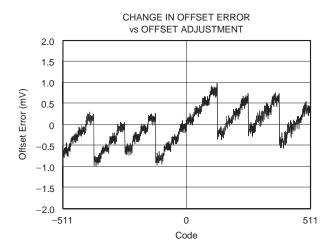

#### 2.2.5 Offset Adjustment

The offset can be adjusted, similar to the gain, to a 12-bit level with respect to the actual input voltage range of the ADC. For example, if the input range is  $\pm 1$ V, the offset can be adjusted in increments of  $488\mu$ V. The maximum adjustment is  $\pm 12.5\%$  of the input range.

There is a register inside the digital interface for each input channel. This registers store the offset adjustment value for each channel. When a channel is selected for conversion, the offset is automatically adjusted. The selected channel and the related register information must not be changed during the conversion.

Setting the register to  $201_H$  results in a -12.5% adjustment,  $000_H$  results in no adjustment, and  $1FF_H$  results in a +12.5% adjustment. The offset adjustment value  $200_H$  is not allowed.

The offset adjustment cannot be used in VECANA mode. A reset condition will set the offset adjustment to zero.

### 2.2.6 Transition Noise

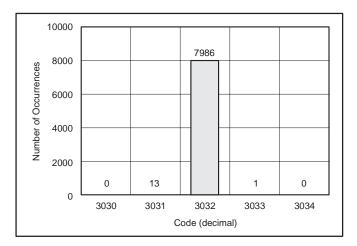

The transition noise of the ADS7869 itself is low, as shown in Figure 1–5. Applying a low-noise DC input and initiating 8000 conversions generated this histogram.

Figure 1-5. Histogram of 8000 Conversions

## 2.3 Sign Comparators

The ADS7869 includes two sets of sign comparators that differ in their hysteresis. The first set, which is used for the position sensor inputs in motor control applications, is connected to the inputs A1, B1, A2, and B2. The hysteresis of these comparators is typically 75mV. In motor control applications, these comparators are used to measure the signs of the position sensor input signals.

The second set is in parallel to the window comparators at the U\_C, V\_C, and W\_C pins. The hysteresis of these components is typically 10mV. In motor control applications, these comparators are used to measure the sign of the main currents.

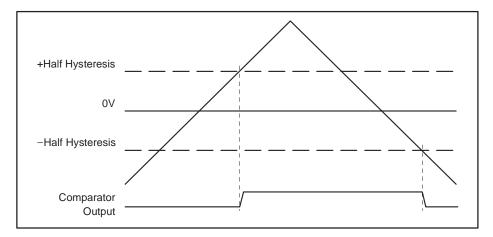

The sign comparator switches from 0 to 1 if the differential input voltage is above +1/2 of the hysteresis. If the output is 1, the sign comparator switches back to 0 if the differential input voltage is below -1/2 of the hysteresis. See Figure 1–6.

Figure 1-6. Typical Transfer Function of a Sign Comparator

SBAS253E - MAY 2003 - REVISED JULY 2006

The input range of the comparators is limited. The lower voltage of the differential inputs should always be within the range of 0 to  $AV_{DD}-1.8V$ .

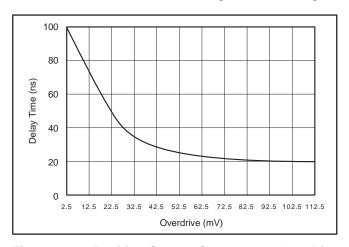

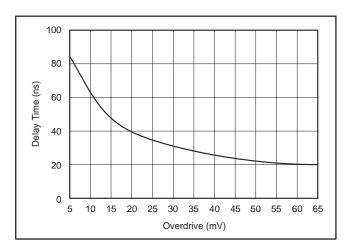

On every comparator, the output is delayed to the input voltage. This delay is dependent on the overdrive of the comparator inputs. The overdrive is the input voltage  $(V_{IN})$  minus one-half of the hysteresis.

If the differential input voltage of the position sensor sign comparator is switching from –40mV to +40mV (step function, 2.5mV overdrive), then the delay time of the output is typically 100ns. The delay is reduced to typically 25ns if the comparator is switching between –100mV and +100mV (72.5mV overdrive). For the delay times as a function of step size with different overdrives, see Figure 1–7 and Figure 1–8.

Figure 1–7. Position Sensor Comparator Overdrive

Figure 1-8. Current Sign Comparator Overdrive

SBAS253E - MAY 2003 - REVISED JULY 2006

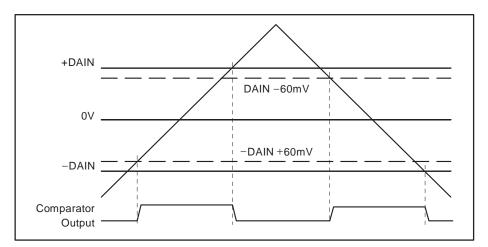

### 2.4 Window Comparators

The window comparators test if the input voltage is within a certain range; this range is  $\pm$ (voltage applied to DAIN, pin 30). If the differential input voltage remains within this range, then the output of the window comparator is 1. If the voltage is outside this range, then the output is set to 0. The window comparator has a hysteresis that is turned on when the output is 0. The comparator outputs switch back to 1 when the input voltage is within in the range of  $\pm$ (DAIN -60mV). (See Figure 1-9.) The voltage at DAIN needs to be in a range of 0.5V to 2.5V.

The window comparator has a switched capacitor circuitry, similar to the ADC architecture, but different from other window comparators. This design dramatically increases the accuracy; due to the additional accuracy, a proper front-end of the input signal is required. (See the *Window Comparator Inputs* section.)

Figure 1-9. Typical Transfer Function of a Window Comparator

Two clock cycles are used to sample the inputs. The next two clock cycles are used to test the lower and the upper voltage limit. Every four clock cycles (or every 250ns with a 16MHz clock) the output of the window comparator is updated. In a worst-case scenario, it takes six clock cycles for the window comparator to detect a current limit. The window comparators need a continuous clock to operate properly.

In motor control applications, the window comparators are used to monitor the main currents for failures.

TEXAS INSTRUMENTS www.ti.com

SBAS253E - MAY 2003 - REVISED JULY 2006

# 2.5 8-Bit Digital-to-Analog Converter

A voltage between 0.5V to 2.5V is required at DAIN (pin 30) to set the range of the window comparators; this can be accomplished with the 8-bit DAC. The DAC value is programmed via the digital interface. Input code  $00_H$  corresponds to a DAC output voltage of 0V. The full-scale value (FF<sub>H</sub>) is at 2.49V (internal reference minus 1LSB).

The impedance of the output is typically  $10k\Omega$ ; the output impedance is independent of the output voltage. The DAC output is connected to DAOUT (pin 29). The settling time ( $t_S$ ) is dependent on the external capacitance ( $C_P$ ) on this pin, and can be calculated to:

$$t_s = 10k\Omega \cdot C_e \cdot (n+1) \cdot ln(2)$$

(2)

In this equation, n is equal to 8, the resolution of the DAC. The output impedance also limits the output current. This current should not exceed  $0.5\mu A$  ( $0.5\mu A \cdot 10k\Omega = 5mV$ ).

DAOUT and DAIN can be shorted. A capacitor (typically  $0.1\mu F$ ) can be used to low-pass the DAC output; however, this low-pass configuration is not required.

#### 2.6 Internal Reference

The internal reference, REFOUT (pin 96), provides the 2.5V required for the reference input of the ADCs at REFIN (pin 97). An internal buffer with a high impedance output drives the reference output pin. This internal buffer is optimized to reject glitches at the reference pin. Any capacitor can be connected to the REFOUT pin in able to reduce noise. It is recommended that a 0.1µF capacitor be connected between the REFOUT (pin 96) and the SGND (pin 13). The Signal ground, SGND, is used internally as a negative reference. The reference voltage is considered a differential voltage between this ground and REFOUT.

Normally, the REFOUT and REFIN pins are both shorted. The internal reference provides an excellent temperature drift, typically 20ppm, and an initial accuracy of 2.5V±20mV at 25°C. If this does not provide the required accuracy for an application, then an external reference can be connected to the REFIN pin.

### 2.7 Grounding

Optimal test results were achieved with a solid ground plane: linearity, offset, and noise performance each showed improvement. During PCB layout, care should be taken that the return currents do not cross any sensitive areas or signals.

Digital signals that interface with the ADS7869 are referenced to the solid ground plane. ESD protection diodes, inside the ADS7869, start conducting if the grounds are separated and the digital inputs go below –0.3V; this includes short glitches. Current will flow through the substrate of the ADS7869 and will disturb the analog performance.

#### 2.8 Supply

The ADS7869 has two separate supplies, BV<sub>DD</sub> (pins 48 and 78) and AV<sub>DD</sub> (pins 8, 18, 28, 85 and 98).

$BV_{DD}$  is used as a digital pad supply only, and is in the range of 2.7V to 5.5V. This allows the ADS7869 to interface with all state-of-the-art processors and controllers.  $BV_{DD}$  should be filtered in order to limit the noise energy from the external digital circuitry to the ADS7869. The current through  $BV_{DD}$  is far below 5mA; depending on the external load, a  $10\Omega$  to  $100\Omega$  resistor can be placed between the external digital circuitry and the ADS7869. Bypass capacitors (two  $0.1\mu F$  and one  $10\mu F$ ) should be placed between the two  $BV_{DD}$  pins and the ground plane.

$AV_{DD}$  supplies the internal circuitry, and can vary from 4.5 to 5.5V. It is not possible to use a passive filter between the digital board supply of the application and the  $AV_{DD}$  pins, because the supply current of the ADS7869 is typically 45mA. In order to generate the analog supply voltage for the ADS7869 and the necessary analog front-end, a linear regulator (7805 family) is recommended. Bypass capacitors of  $0.1\mu$ F should be placed between all  $AV_{DD}$  pins and the ground plane. Bypass capacitors of  $10\mu$ F should be placed between two  $AV_{DD}$  pins and the ground plane.

SBAS253E - MAY 2003 - REVISED JULY 2006

# 3 Digital Section

#### 3.1 Introduction

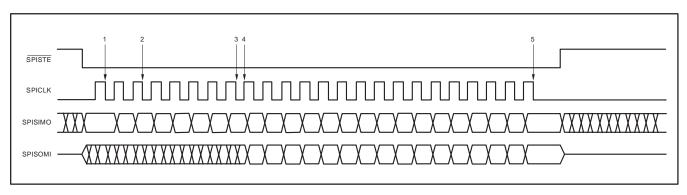

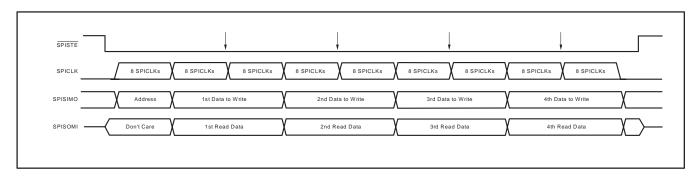

The ADS7869 can interface with a DSP or  $\mu$ C in four different ways. The M1 and M0 pins determine in which mode the ADS7869 will communicate; see Table 1–1. It can be connected as a standard VECANA01 interface, as an SPI, or as two different parallel interfaces.

Table 1-1. Selection of Interface Mode

| M1 | MO | MODE        |

|----|----|-------------|

| 0  | 0  | VECANA mode |

| 0  | 1  | SPI mode    |

| 1  | 0  | Parallel 1  |

| 1  | 1  | Parallel 2  |

As a function of the selected mode, some pins will have different assignment as shown in Table 1–2.