AT91SAM7S-EK Evaluation Board

User Guide

### Table of Contents

| Section   | 1                             |             |

|-----------|-------------------------------|-------------|

| Overviev  | N                             | 1-1         |

| 1.1       | Scope                         | <b>1</b> -1 |

| 1.2       | Deliverables                  | 1-1         |

| 1.3       | AT91SAM7S-EK Evaluation Board | 1-1         |

| Section   | 2                             |             |

| Setting l | Jp the AT91SAM7S-EK Board     | 2-1         |

| 2.1       | Electrostatic Warning         |             |

| 2.2       | Requirements                  |             |

| 2.3       | Powering Up the Board         |             |

| 2.4       | Getting Started               |             |

| 2.5       | AT91SAM7S-EK Block Diagram    |             |

| Section   | 3                             |             |

| Board D   | escription                    | 3-1         |

| 3.1       | AT91SAM7S256 Microcontroller  |             |

| 3.2       | AT91SAM7S256 Block Diagram    |             |

| 3.3       | Memory                        |             |

| 3.4       | Clock Circuitry               |             |

| 3.5       | Reset Circuitry               | 3-4         |

| 3.6       | Power Supply Circuitry        | 3-4         |

| 3.7       | Remote Communication          | 3-4         |

| 3.8       | Analog Interface              | 3-4         |

| 3.9       | User Interface                | 3-4         |

| 3.10      | Debug Interface               | 3-4         |

| 3.11      | Expansion Connector           | 3-4         |

| 3.12      | 2 Wrapping User Area          | 3-4         |

| Section   | 4                             |             |

| Configur  | ration Straps                 | 4-1         |

| 4.1       | Configuration Strap           |             |

| Section   | -<br>- 5                      |             |

|           | tics                          | 5-1         |

| 5.1       | Schematics                    |             |

|           |                               |             |

| Section   |                               |             |

|           | History                       |             |

| 6.1       | Revision History              | 6-1         |

Table of Contents

### **Overview**

### 1.1 Scope

The AT91SAM7S-EK evaluation board enables the evaluation of and code development for applications running on an AT91SAM7Sxx device.

This document describes the evaluation board fitted with an AT91SAM7S256.

This guide focuses on the AT91SAM7S-EK board as an evaluation platform for the AT91SAM7S family.

#### 1.2 Deliverables

### 1.2.1 Standard Version AT91SAM7S-EK VAR

The AT91SAM7S-EK package contains the following items:

- An AT91SAM7S-EK board

- One A/B-type USB cable

- One DVD-ROM containing summary and full datasheets, datasheets with electrical and mechanical characteristics, application notes and getting started documents for all development boards and AT91 microcontrollers. An AT91 software package with C and assembly listings is also provided. This allows the user to begin evaluating the AT91 ARM® Thumb® 32-bit microcontroller quickly.

## 1.3 AT91SAM7S-EK Evaluation Board

The board is generally equipped with an AT91SAM7S256 (64-pin PQFP package) together with the following:

- USB device port interface

- Two serial communication ports

- JTAG/ICE debug interface

- Four buffered analog inputs

- Four general-purpose LEDs and pushbuttons

- Expansion connector

- Prototyping area

**Note:** The user can also evaluate the AT91SAM7S32 with this board. A 48-pin TQFP footprint has been provided for this purpose. To do so, the user must unsolder the AT91SAM7S256 microcontroller (IC4) and fit the AT91SAM7S32 on the 48-pin TQFP footprint (IC5).

# Setting Up the AT91SAM7S-EK Board

## 2.1 Electrostatic Warning

The AT91SAM7S-EK evaluation board is shipped in protective anti-static packaging. The board must not be subjected to high electrostatic potentials. A grounding strap or similar protective device should be worn when handling the board. Avoid touching the component pins or any other metallic element.

### 2.2 Requirements

In order to set up the AT91SAM7S-EK evaluation board, the following items are needed:

- The AT91SAM7S-EK evaluation board itself.

- Optional DC power supply capable of supplying 7V to 12V at 0.5 A.

**Note:** The AT91SAM7S-EK is not delivered with the JTAG/ICE interface required to start evaluating the device.

## 2.3 Powering Up the Board

AT91SAM7S-EK is self-powered by the USB port. If the USB port is not used, the card can be supplied by an external DC power supply via the 2.1 mm socket (J1). The polarity of the power supply is not critical.

The regulator allows the input voltage range to be from 7V to 12V.

### 2.4 Getting Started

The AT91SAM7S-EK evaluation board is delivered with a DVD-ROM containing all necessary information and step-by-step procedures for working with the most common development toolchains. Please refer to this DVD-ROM, or to the AT91 web site, http://www.atmel.com/products/AT91/, for the most up-to-date information on getting started with the AT91SAM7S-EK.

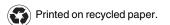

## 2.5 AT91SAM7S-EK Block Diagram

Figure 2-1. Block Diagram for AT91SAM7S-EK Board

### **Board Description**

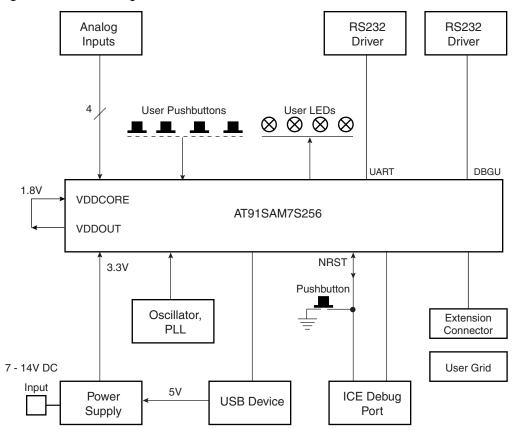

## 3.1 AT91SAM7S256 Microcontroller

- Incorporates the ARM7TDMI® ARM® Thumb® Processor

- High-performance 32-bit RISC Architecture

- High-density 16-bit Instruction Set

- Leader in MIPS/Watt

- EmbeddedICE<sup>™</sup> In-circuit Emulation, Debug Communication Channel Support

- 256 Kbytes of Internal High-speed Flash, Organized in 1024 Pages of 256 Bytes

- Single Cycle Access at Up to 30 MHz in Worst Case Conditions,

Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed

- Page Programming Time: 4 ms, Including Page Auto-erase, Full Erase Time: 10 ms

- 10,000 Write Cycles, 10-year Data Retention Capability, Sector Lock Capabilities, Flash Security Bit

- Fast Flash Programming Interface for High Volume Production

- 64 Kbytes of Internal High-speed SRAM, Single-cycle Access at Maximum Speed

- Memory Controller (MC)

- Embedded Flash Controller, Abort Status and Misalignment Detection

- Reset Controller (RSTC)

- Based on Power-on Reset and Low-power Factory-calibrated Brown-out Detector

- Provides External Reset Signal Shaping and Reset Source Status

- Clock Generator (CKGR)

- Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL

- Power Management Controller (PMC)

- Software Power Optimization Capabilities, Including Slow Clock Mode (Down to 500 Hz) and Idle Mode

- Three Programmable External Clock Signals

- Advanced Interrupt Controller (AIC)

- Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

- Two External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected

- Debug Unit (DBGU)

- 2-wire UART and Support for Debug Communication Channel interrupt,

Programmable ICE Access Prevention

- Periodic Interval Timer (PIT)

- 20-bit Programmable Counter plus 12-bit Interval Counter

- Windowed Watchdog (WDT)

- 12-bit key-protected Programmable Counter

- Provides Reset or Interrupt Signals to the System

- Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

- Real-time Timer (RTT)

- 32-bit Free-running Counter with Alarm

- Runs Off the Internal RC Oscillator

- One Parallel Input/Output Controller (PIOA)

- Thirty-Two Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

- Input Change Interrupt Capability on Each I/O Line

- Individually Programmable Open-drain, Pull-up resistor and Synchronous Output

- Eleven Peripheral Data Controller (PDC) Channels

- One USB 2.0 Full Speed (12 Mbits per second) Device Port

- On-chip Transceiver, 328-byte Configurable Integrated FIFOs

- One Synchronous Serial Controller (SSC)

- Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

- I<sup>2</sup>S Analog Interface Support, Time Division Multiplex Support

- High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

- Two Universal Synchronous/Asynchronous Receiver Transmitters (USART)

- Individual Baud Rate Generator, IrDA® Infrared Modulation/Demodulation

- Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

- Manchester Encoder/Decoder

- Full Modem Line Support on USART1

- One Master/Slave Serial Peripheral Interface (SPI)

- 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

- One Three-channel 16-bit Timer/Counter (TC)

- Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel

- Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

- One Four-channel 16-bit PWM Controller (PWMC)

- One Two-wire Interface (TWI)

- Master Mode Support Only, All Two-wire Atmel EEPROMs Supported

- One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os

- IEEE® 1149.1 JTAG Boundary Scan on All Digital Pins

- 5V-tolerant I/Os, including Four High-current Drive I/O lines, Up to 16 mA Each

- Power Supplies

- Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components

- 1.8V or 3.3V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply

- 1.8V VDDCORE Core Power Supply with Brown-out Detector

- 3.3V VDDANA Analog Voltage Supply

- Fully Static Operation: Up to 55 MHz at 1.65V and 85° C Worst Case Conditions

- Available in a 64-lead TQFP Package

### 3.2 AT91SAM7S256 Block Diagram

Figure 3-1. AT91SAM7S256 Block Diagram

### 3.3 Memory

- 256 Kbytes of internal high-speed Flash

- 64 Kbytes of internal high-speed SRAM

### 3.4 Clock Circuitry

■ 18.432 MHz standard crystal for the embedded oscillator

### 3.5 **Reset Circuitry** ■ Internal bi-directional reset controller with brown out detector External reset pushbutton 3.6 **Power Supply** USB powered. The dynamic power consumption on VDDCORE is less than 50 mA at Circuitry full speed when running out of the Flash. The total current drawn by all the I/O lines cannot exceed 200 mA. External power can be applied via the 2.1 mm connector to the regulator in either polarity because of the diode-rectifying circuit (CR3 to CR6). The minimum voltage required is 7V. The board has a voltage regulator providing +3.3V. The regulator allows the input voltage to be from 7V to 14V (REG1). ■ The two power supplies are separated from each other by the diodes CR1 and CR2. ■ On-chip embedded VDDCORE 1.8V regulator 3.7 Remote ■ Two serial interface via RS-232 DB9 male sockets Communication - DBGU COM Port UART COM Port with RTS/CTS handshake control possibility (USART 0) ■ USB V2.0 full-speed compliant, 12 Mbits per second (UDP) 3.8 **Analog Interface** ■ Four analog inputs (0V to 3.3V) via J7, J8, J9, J10 footprints **User Interface** 3.9 ■ Four pushbuttons via general PIO lines ■ Four LEDs via high current PIO lines 3.10 **Debug Interface** ■ 20-pin JTAG/ICE interface connector ■ DBGU COM port 3.11 **Expansion** One expansion connector (J5) gives access to all the microcontroller's signals. Connector All I/Os of the AT91SAM7S256 are routed to this connector. This allows the developer to check the integrity of the components and to extend the features of the board by adding external hardware components or boards. 3.12 Wrapping User This allows the developer to fit additional components for prototyping use. Area

## **Configuration Straps**

## 4.1 Configuration Strap

Table 4-1 gives details on configuration straps on the AT91SAM7S-EK evaluation board and their default settings.

Table 4-1. Configuration Straps

| Designation         | Default<br>Setting | Feature                                                                          |

|---------------------|--------------------|----------------------------------------------------------------------------------|

| JP1                 | Closed             | Enables the use of the remote DP pull-up (USB)                                   |

| JP2                 | Closed             | Enables the use of the VBUS detect (USB)                                         |

| JP3                 | Opened             | Disable external VCC on the expansion connector J5 (pin 1, 2)                    |

| JP4                 | Closed             | The System Reset signal (NRST) is connected to the ICE/JTAG socket (J4, pin 15). |

| JP5                 | Opened             | Do not use: Factory test mode                                                    |

| JP6                 | Closed             | Enables the use of the CTS signal (UART)                                         |

| JP7                 | Closed             | Enables the use of the TXD signal (UART)                                         |

| JP8                 | Closed             | Enables the use of the RTS signal (UART)                                         |

| JP9                 | Closed             | Enables the use of the RXD signal (UART)                                         |

| JP10                | Closed             |                                                                                  |

| JP11                | Closed             | Enables the use of the RXD signal (DBGU)                                         |

| JP12                | Closed             | Enables the use of the TXD signal (DBGU)                                         |

| JP13 <sup>(1)</sup> | Closed             | VDDFLASH Jumper                                                                  |

| JP14 <sup>(1)</sup> | Closed             | VDDIO Jumper                                                                     |

| JP15                | Closed             | Enables the use of the User LED (DS1)                                            |

| JP16                | Closed             | Enables the use of the User LED (DS2)                                            |

| JP17                | Closed             | Enables the use of the User LED (DS3)                                            |

| JP18                | Closed             | Enables the use of the User LED (DS4)                                            |

| JP19                | Opened             | Select ICE mode or JTAG mode (Closed)                                            |

| JP20 <sup>(1)</sup> | Closed             | ADVREFP Jumper                                                                   |

| JP21 <sup>(1)</sup> | Closed             | VDDPLL Jumper                                                                    |

Table 4-1. Configuration Straps

| Designation         | Default<br>Setting | Feature                                                                                                           |

|---------------------|--------------------|-------------------------------------------------------------------------------------------------------------------|

| JP22 <sup>(1)</sup> | Closed             | VDDIN Jumper                                                                                                      |

| JP23 <sup>(1)</sup> | Closed             | VDDCORE Jumper                                                                                                    |

| JP24                | Closed             | Enables the use of the EXT_AD0 (Analog Input 0)                                                                   |

| JP25                | Closed             | Enables the use of the EXT_AD1 (Analog Input 1)                                                                   |

| JP26                | Closed             | Enables the use of the EXT_AD4 (Analog Input 4)                                                                   |

| JP27                | Closed             | Enables the use of the EXT_AD5 (Analog Input 5)                                                                   |

| JP28                | Opened             | Erases all internal Flash memory when the board is powered. To do so, the user must close J28 for at least 10 ms. |

| TP1                 | N.A                | GND Test point                                                                                                    |

| TP3                 | N.A                | GND Test point                                                                                                    |

| TP5                 | N.A                | GND Test point                                                                                                    |

| TP6                 | N.A                | GND Test point                                                                                                    |

Note:

1. These jumpers are dedicated to power consumption measurement use. The user has to open the jumper and insert an anmeter.

If these jumpers are not populated (previous revisions of the kit), the related straps are wired on board. In this case and in order to use the power consumption measurement feature, the user has to open the strap by cutting it before soldering a jumper and inserting an anmeter.

## **Schematics**

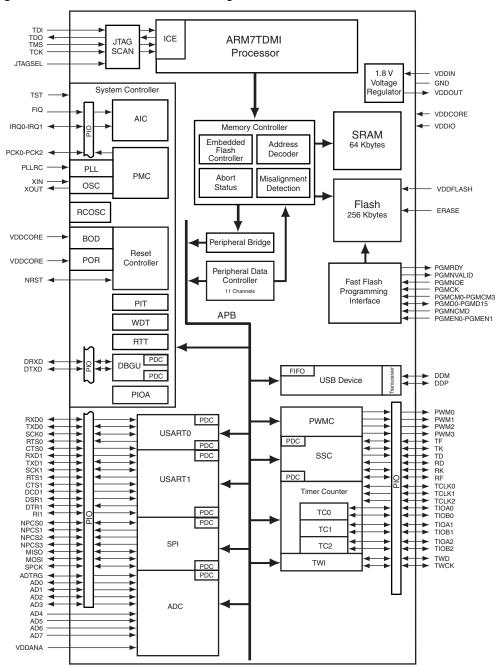

### 5.1 Schematics

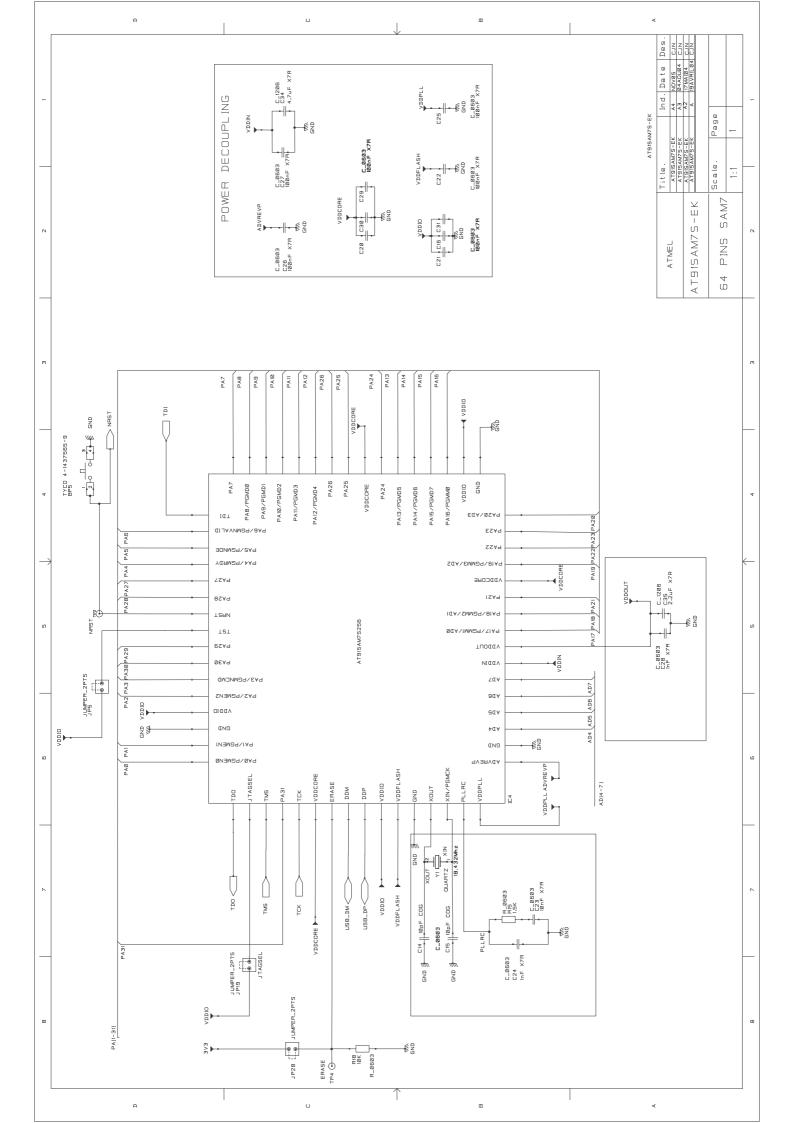

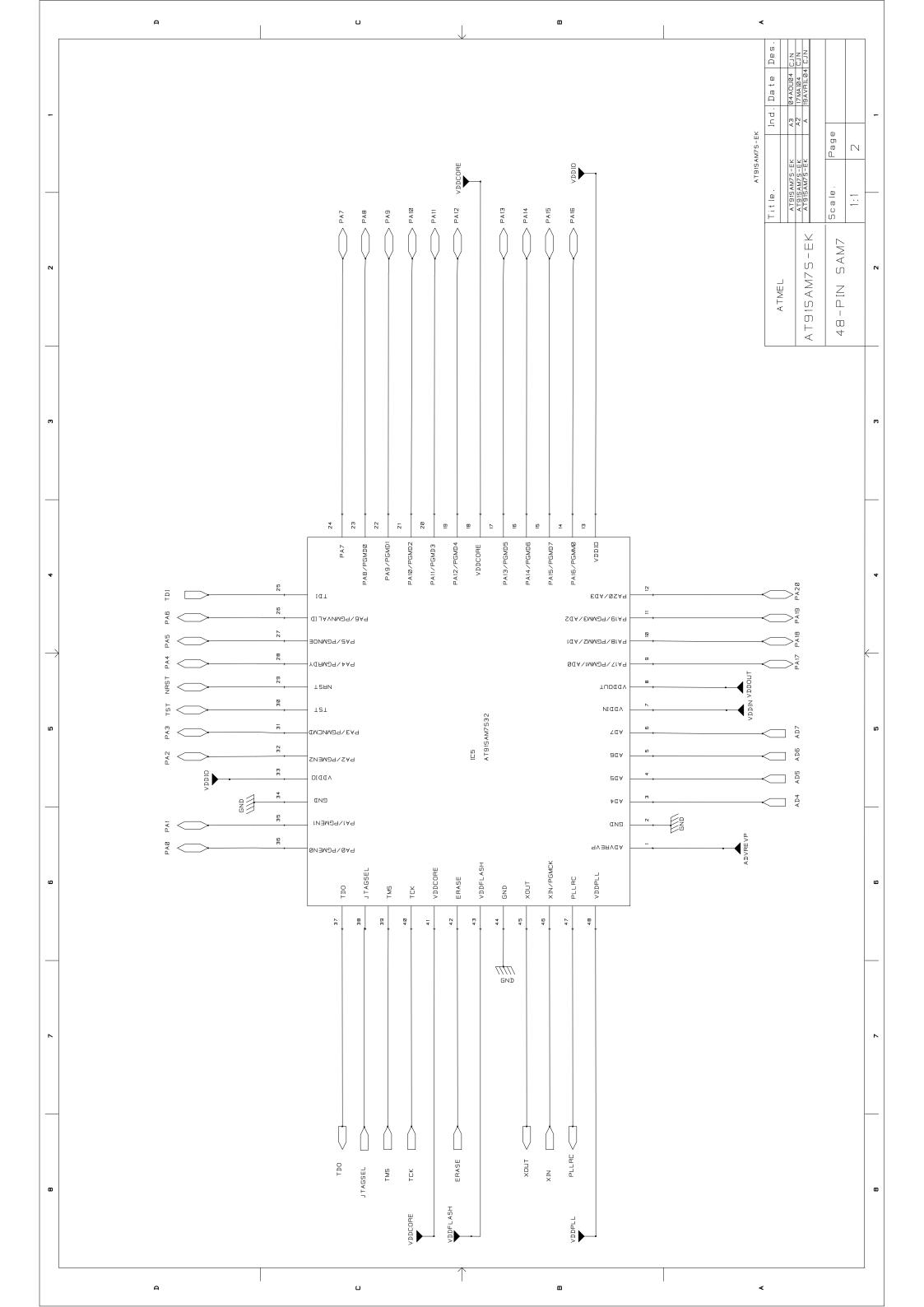

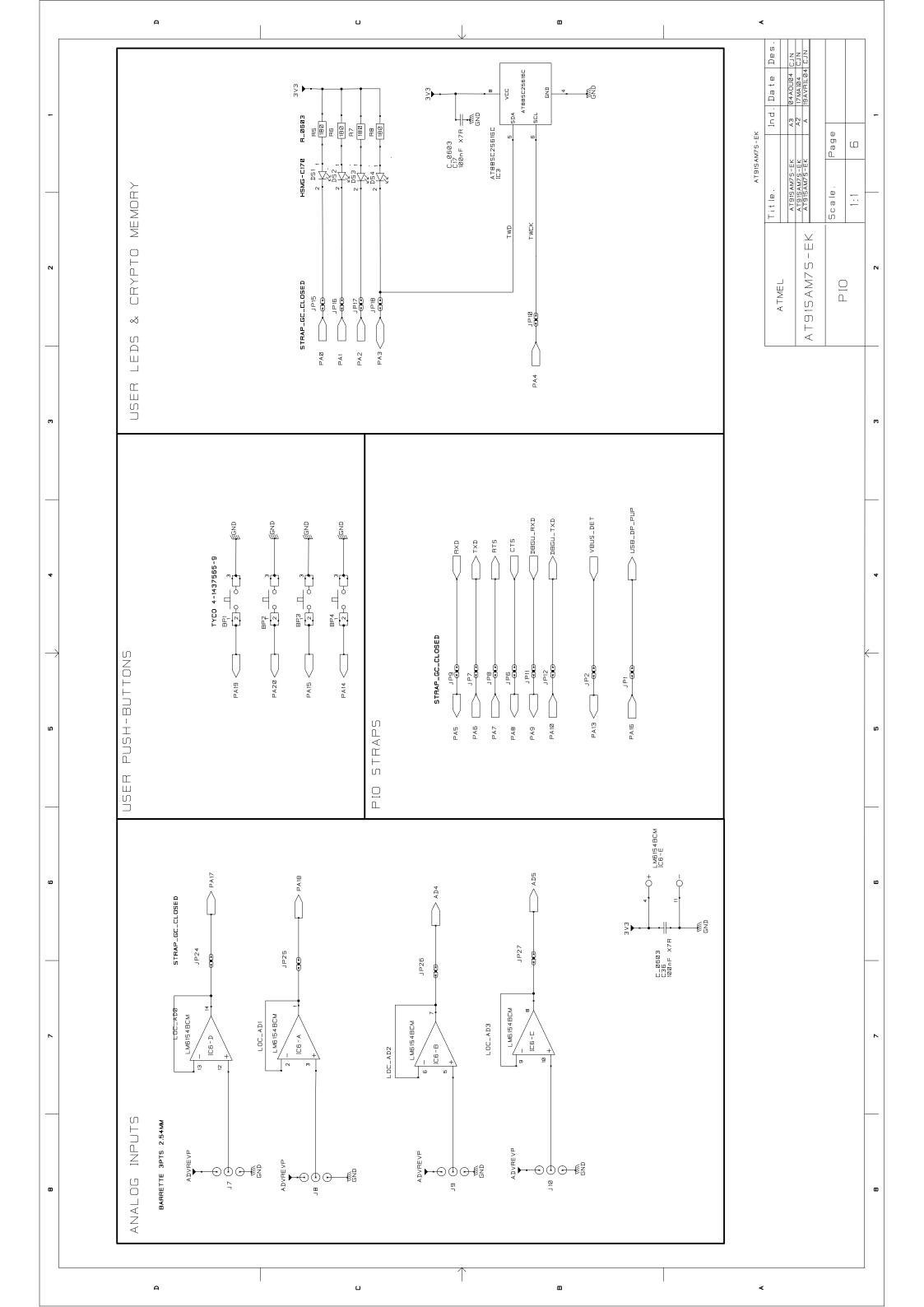

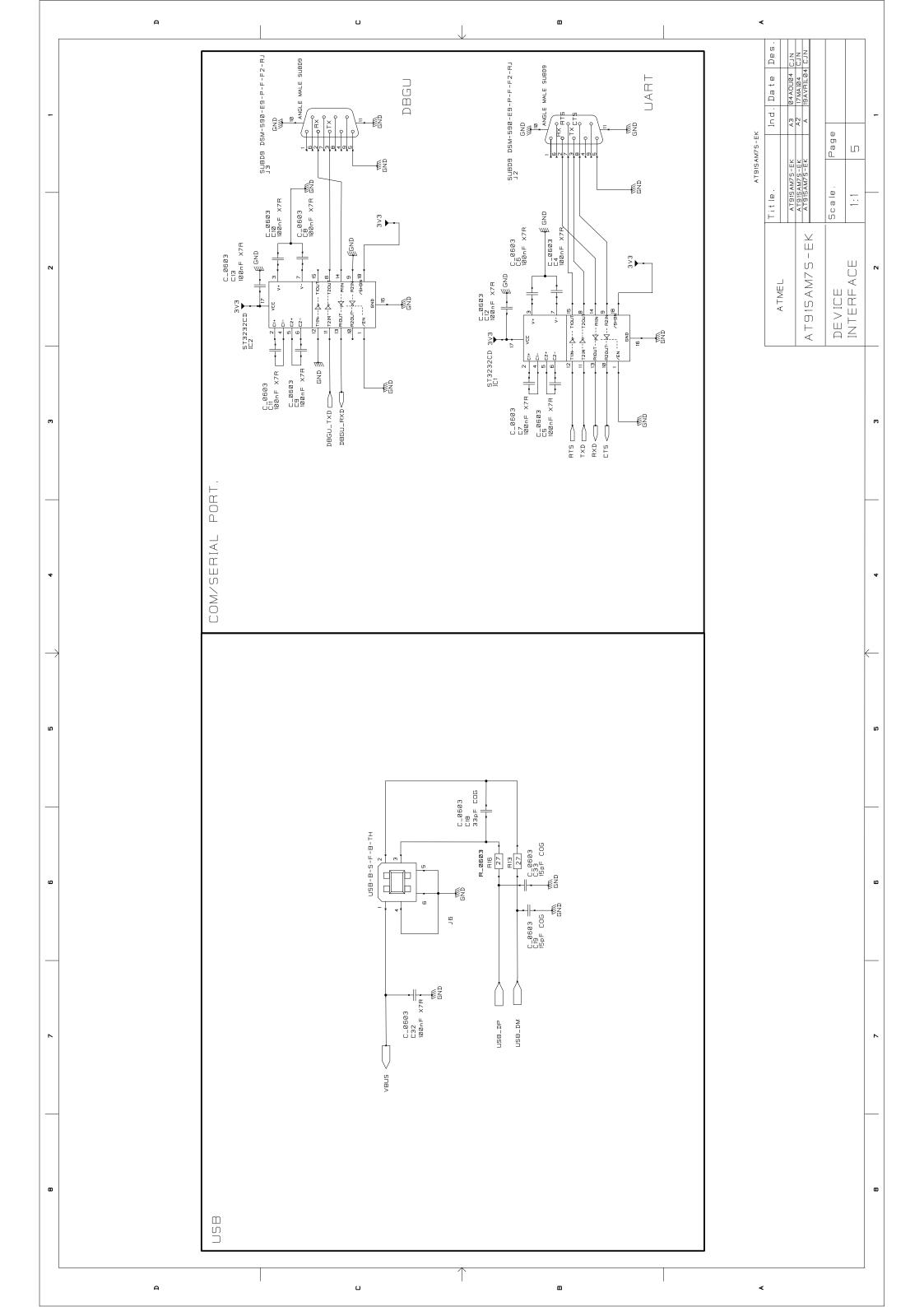

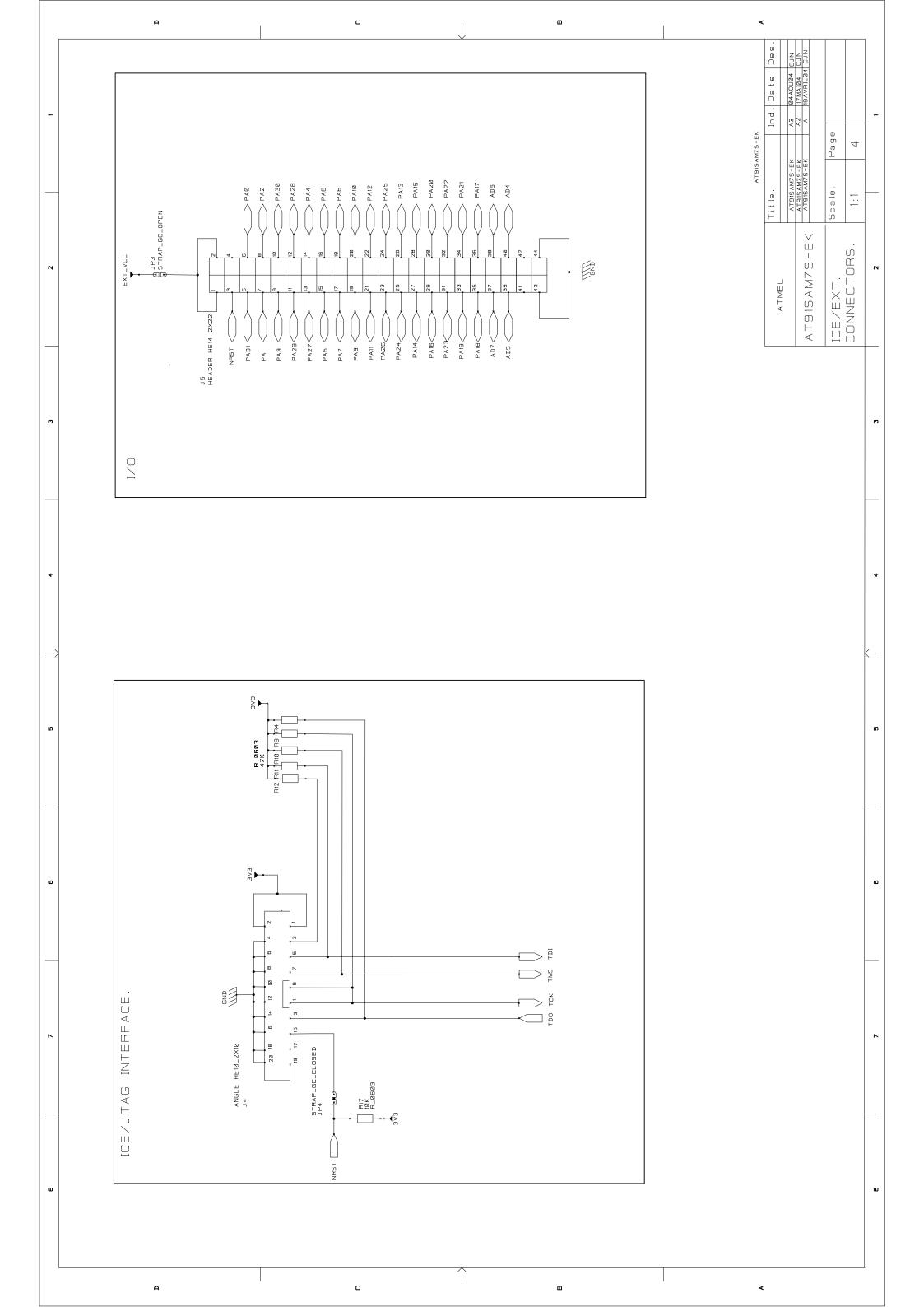

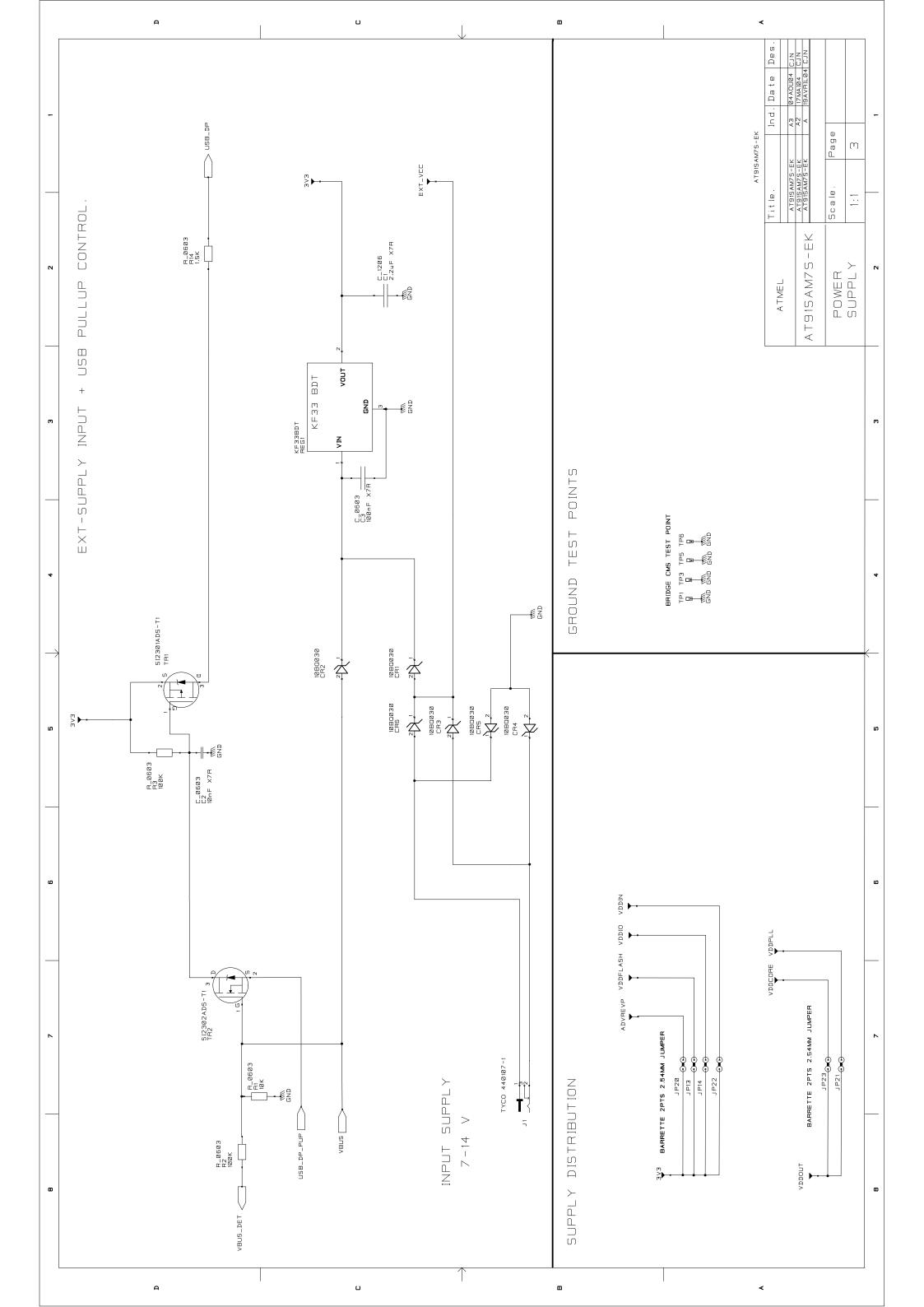

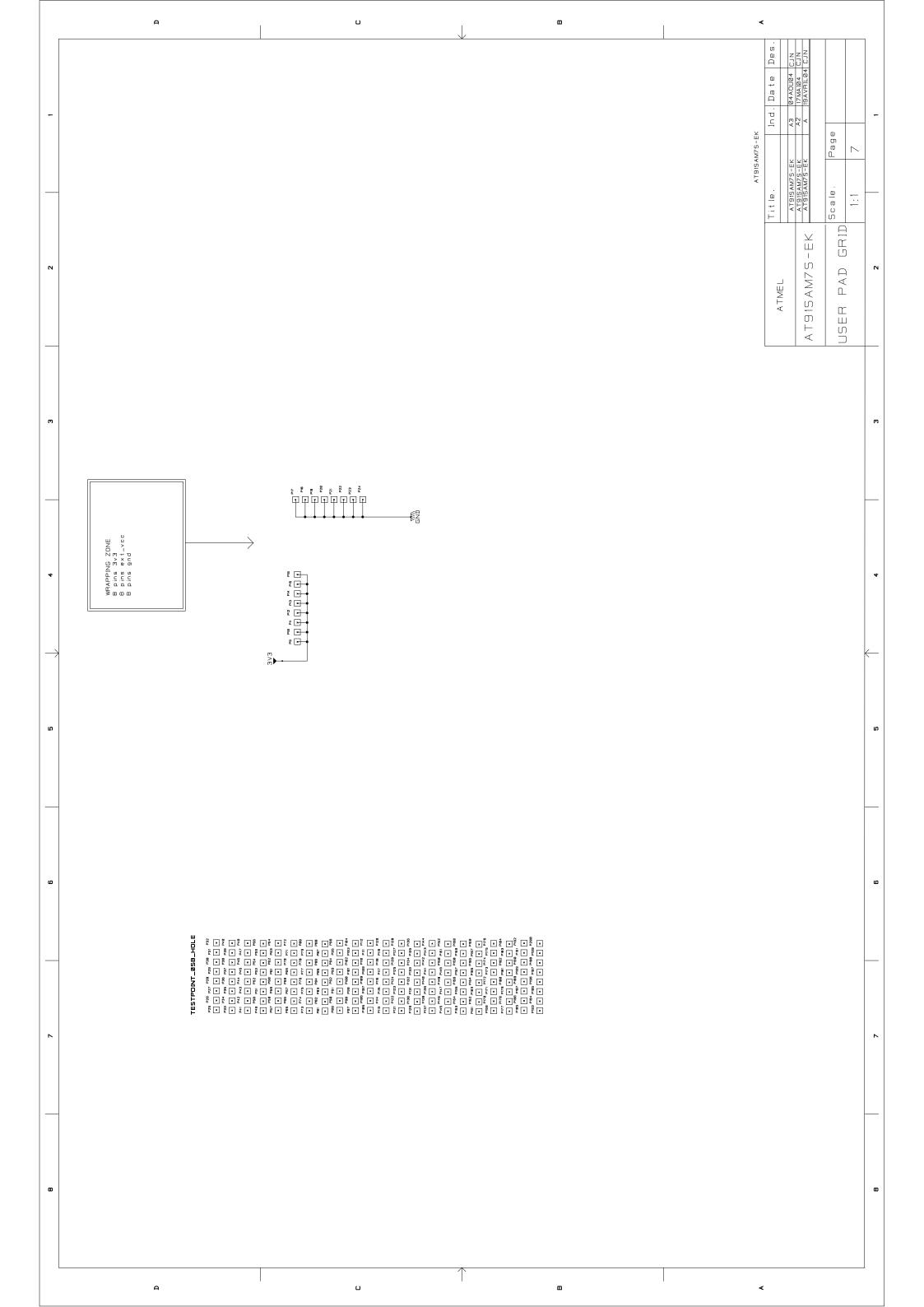

This section contains the following schematics:

- Board Layout And Silkscreen Printing Top View

- 64-pin SAM7 Microcontroller (dual footprint)

- 48-pin SAM7 Microcontroller

- Power Supply

- ICE/EXT Connectors

- Device Interface

- PIO

- User PAD Grid

| ΑЗ | 4 AUG 04     |                 |

|----|--------------|-----------------|

| Α2 | 9 JUNEØ4     |                 |

| А  | 15 A P R Ø 4 | Initial version |

**Schematics**

## **Revision History**

### 6.1 Revision History

### Table 6-1.

| Document | Comments                                                                   | Change<br>Request Ref. |

|----------|----------------------------------------------------------------------------|------------------------|

| 6112A    | First issue.                                                               |                        |

| 6112B    | New schematics.                                                            | 1457                   |

| 6112C    | Corrected features for JP26 and JP27 in Table 4-1, "Configuration Straps". | 3849                   |

|          | Corrected device label in 64-pin SAM7 schematic.                           | 2734                   |

Revision History

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602

44306 Nantes Cedex 3, France

Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00

Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0

Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### **Biometrics**

Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-47-50 Fax: (33) 4-76-58-47-60

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2007 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM<sup>®</sup>, Thumb<sup>®</sup> and ARM Powered<sup>®</sup> are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.