## 4:1, SINGLE-ENDED MULTIPLEXER

ICS830541

## GENERAL DESCRIPTION

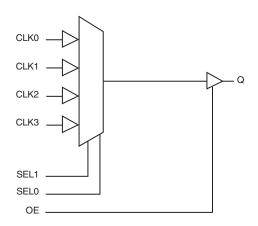

The ICS83054I is a low skew, 4:1, Single-ended Multiplexer and a member of the HiPerClockS™ family of High Performance Clock Solutions from IDT. The ICS83054I has four selectable single-ended clock inputs and one single-ended clock

output. The output has a  $V_{\text{DDO}}$  pin which may be set at 3.3V, 2.5V, or 1.8V, making the device ideal for use in voltage translation applications. An output enable pin places the output in a high impedance state which may be useful for testing or debug purposes. The device operates up to 250MHz and is packaged in a 16 TSSOP package.

## **FEATURES**

- 4:1 single-ended multiplexer

- Q nominal output impedance:  $7\Omega (V_{DDO} = 3.3V)$

- · Maximum output frequency: 250MHz

- Propagation delay: 3ns (maximum), V<sub>DD</sub> = V<sub>DDO</sub> = 3.3V

- Input skew: 225ps (maximum),  $V_{DD} = V_{DDO} = 3.3V$

- Part-to-part skew: 780ps (maximum), V<sub>DD</sub> = V<sub>DDQ</sub> = 3.3V

- Additive phase jitter, RMS: 0.19ps (typical), 3.3V/3.3V

- · Operating supply modes:

V<sub>DD</sub>/V<sub>DDO</sub>

3.3V/3.3V 3.3V/2.5V

3.3V/1.8V

2.5V/2.5V

2.5V/1.8V

- -40°C to 85°C ambient operating temperature

- Available in both standard (RoHS 5) and lead-free (RoHS 6) packages

## **BLOCK DIAGRAM**

## PIN ASSIGNMENT

#### ICS830541

16-Lead TSSOP

4.4mm x 5.0mm x 0.92mm package body

G Package

Top View

TABLE 1. PIN DESCRIPTIONS

| Number           | Name                      | Ty     | уре      | Description                                                                                                                   |

|------------------|---------------------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------|

| 1                | Q                         | Output |          | Single-ended clock output. LVCMOS/LVTTL interface levels.                                                                     |

| 3                | OE                        | Input  | Pullup   | Output enable. When LOW, outputs are in HIGH impedance state. When HIGH, outputs are active. LVCMOS / LVTTL interface levels. |

| 4, 8,<br>10, 14  | CLK3, CLK2,<br>CLK1, CLK0 | Input  | Pulldown | Single-ended clock inputs. LVCMOS/LVTTL interface levels.                                                                     |

| 5                | GND                       | Power  |          | Power supply ground.                                                                                                          |

| 7, 9             | SEL1, SEL0                | Input  | Pulldown | Clock select input. See Control Input Function Table. LVCMOS / LVTTL interface levels.                                        |

| 2, 6, 11, 13, 15 | nc                        | Unused |          | No connect.                                                                                                                   |

| 12               | V <sub>DD</sub>           | Power  |          | Power and input supply pin.                                                                                                   |

| 16               | V <sub>DDO</sub>          | Power  |          | Output supply pin.                                                                                                            |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

TABLE 2. PIN CHARACTERISTICS

| Symbol                | Parameter                                  | Test Conditions    | Minimum | Typical | Maximum | Units |

|-----------------------|--------------------------------------------|--------------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance                          |                    |         | 4       |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor                      |                    |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor                    |                    |         | 51      |         | kΩ    |

|                       |                                            | $V_{DDO} = 3.465V$ |         | 18      |         | pF    |

| C <sub>PD</sub>       | Power Dissipation Capacitance (per output) | $V_{DDO} = 2.625V$ |         | 20      |         | pF    |

|                       | (por output)                               | $V_{DDO} = 1.89V$  |         | 30      |         | pF    |

|                       |                                            | $V_{DDO} = 3.465V$ |         | 7       |         | Ω     |

| R <sub>out</sub>      | Output Impedance                           | $V_{DDO} = 2.625V$ |         | 7       |         | Ω     |

|                       |                                            | $V_{DDO} = 1.89V$  |         | 10      |         | Ω     |

TABLE 3. CONTROL INPUT FUNCTION TABLE

| Contro | l Inputs | Input Selected to Q |  |  |

|--------|----------|---------------------|--|--|

| SEL1   | SEL0     | input Selected to Q |  |  |

| 0      | 0        | CLK0                |  |  |

| 0      | 1        | CLK1                |  |  |

| 1      | 0        | CLK2                |  |  |

| 1      | 1        | CLK3                |  |  |

#### ABSOLUTE MAXIMUM RATINGS

Storage Temperature,  $T_{STG}$

Supply Voltage, V<sub>DD</sub> 4.6V

Inputs,  $V_{l}$  -0.5V to  $V_{DD}$  + 0.5 V Outputs,  $V_{O}$  -0.5V to  $V_{DDO}$  + 0.5V Package Thermal Impedance,  $\theta_{JA}$  89°C/W (0 Ifpm)

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

Table 4A. Power Supply DC Characteristics,  $V_{DD} = V_{DDO} = 3.3V \pm 5\%$ , Ta = -40°C to 85°C

-65°C to 150°C

| Symbol           | Parameter             | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-----------------------|-----------------|---------|---------|---------|-------|

| V <sub>DD</sub>  | Power Supply Voltage  |                 | 3.135   | 3.3     | 3.465   | V     |

| V <sub>DDO</sub> | Output Supply Voltage |                 | 3.135   | 3.3     | 3.465   | V     |

| I <sub>DD</sub>  | Power Supply Current  |                 |         |         | 40      | mA    |

| I <sub>DDO</sub> | Output Supply Current |                 |         |         | 5       | mA    |

## Table 4B. Power Supply DC Characteristics, $V_{DD} = 3.3V \pm 5\%$ , $V_{DDO} = 2.5V \pm 5\%$ , Ta = -40°C to 85°C

| Symbol           | Parameter             | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-----------------------|-----------------|---------|---------|---------|-------|

| V <sub>DD</sub>  | Power Supply Voltage  |                 | 3.135   | 3.3     | 3.465   | V     |

| V <sub>DDO</sub> | Output Supply Voltage |                 | 2.375   | 2.5     | 2.625   | V     |

| I <sub>DD</sub>  | Power Supply Current  |                 |         |         | 40      | mA    |

| I <sub>DDO</sub> | Output Supply Current |                 |         |         | 5       | mA    |

# Table 4C. Power Supply DC Characteristics, $V_{DD} = 3.3V \pm 5\%$ , $V_{DDO} = 1.8V \pm 0.2V$ , Ta = -40°C to $85^{\circ}$ C

| Symbol           | Parameter             | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-----------------------|-----------------|---------|---------|---------|-------|

| V <sub>DD</sub>  | Power Supply Voltage  |                 | 3.135   | 3.3     | 3.465   | V     |

| V <sub>DDO</sub> | Output Supply Voltage |                 | 1.71    | 1.8     | 1.89    | V     |

| I <sub>DD</sub>  | Power Supply Current  |                 |         |         | 40      | mA    |

| I <sub>DDO</sub> | Output Supply Current |                 |         |         | 5       | mA    |

## Table 4D. Power Supply DC Characteristics, $V_{DD} = V_{DDO} = 2.5V \pm 5\%$ , Ta = -40°C to 85°C

| Symbol           | Parameter             | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-----------------------|-----------------|---------|---------|---------|-------|

| V <sub>DD</sub>  | Power Supply Voltage  |                 | 2.375   | 2.5     | 2.625   | V     |

| V <sub>DDO</sub> | Output Supply Voltage |                 | 2.375   | 2.5     | 2.625   | V     |

| I <sub>DD</sub>  | Power Supply Current  |                 |         |         | 35      | mA    |

| I <sub>DDO</sub> | Output Supply Current |                 |         |         | 5       | mA    |

## Table 4E. Power Supply DC Characteristics, $V_{DD} = 2.5V \pm 5\%$ , $V_{DDO} = 1.8V \pm 0.2V$ , Ta = -40°C to 85°C

| Symbol           | Parameter             | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-----------------------|-----------------|---------|---------|---------|-------|

| V <sub>DD</sub>  | Power Supply Voltage  |                 | 2.375   | 2.5     | 2.625   | V     |

| V <sub>DDO</sub> | Output Supply Voltage |                 | 1.71    | 1.8     | 1.89    | V     |

| I <sub>DD</sub>  | Power Supply Current  |                 |         |         | 35      | mA    |

| I <sub>DDO</sub> | Output Supply Current |                 |         |         | 5       | mA    |

TABLE 4F. LVCMOS/LVTTL DC CHARACTERISTICS, TA = -40°C TO 85°C

| Symbol          | Parameter          |                          | Test Conditions                                  | Minimum               | Typical | Maximum               | Units |

|-----------------|--------------------|--------------------------|--------------------------------------------------|-----------------------|---------|-----------------------|-------|

| V               | Input High Voltage |                          | $V_{DD} = 3.3V \pm 5\%$                          | 2                     |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IH</sub> | Input High Voltage |                          | $V_{DD} = 2.5V \pm 5\%$                          | 1.7                   |         | V <sub>DD</sub> + 0.3 | V     |

| V               | Input Low Voltage  |                          | $V_{DD} = 3.3V \pm 5\%$                          | -0.3                  |         | 0.8                   | V     |

| V <sub>IL</sub> | Input Low Voltage  |                          | $V_{DD} = 2.5V \pm 5\%$                          | -0.3                  |         | 0.7                   | V     |

| I <sub>IH</sub> | Input High Current | CLK0:CLK3,<br>SEL0, SEL1 | $V_{DD} = 3.3V \text{ or } 2.5V \pm 5\%$         |                       |         | 150                   | μΑ    |

| "               |                    | OE                       | $V_{DD} = 3.3 \text{V or } 2.5 \text{V} \pm 5\%$ |                       |         | 5                     | μΑ    |

| I <sub>IL</sub> | Input Low Current  | CLK0:CLK3,<br>SEL0, SEL1 | $V_{DD} = 3.3V \text{ or } 2.5V \pm 5\%$         | -5                    |         |                       | μΑ    |

| I IL            | '                  | OE                       | $V_{DD} = 3.3 \text{V or } 2.5 \text{V} \pm 5\%$ | -150                  |         |                       | μΑ    |

|                 |                    |                          | $V_{DDO} = 3.3V \pm 5\%$ ; NOTE 1                | 2.6                   |         |                       | V     |

| V <sub>OH</sub> | Output HighVoltage |                          | $V_{DDO} = 2.5V \pm 5\%$ ; NOTE 1                | 1.8                   |         |                       | V     |

|                 |                    |                          | $V_{DDO} = 1.8V \pm 5\%$ ; NOTE 1                | V <sub>DD</sub> - 0.3 |         |                       | V     |

|                 | Output Low Voltage |                          | $V_{DDO} = 3.3V \pm 5\%$ ; NOTE 1                |                       |         | 0.5                   | V     |

| V <sub>OL</sub> |                    |                          | $V_{DDO} = 2.5V \pm 5\%$ ; NOTE 1                |                       |         | 0.45                  | V     |

|                 |                    |                          | $V_{DDO} = 1.8V \pm 5\%; NOTE 1$                 |                       |         | 0.35                  | V     |

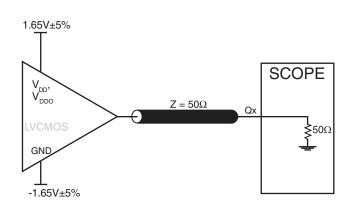

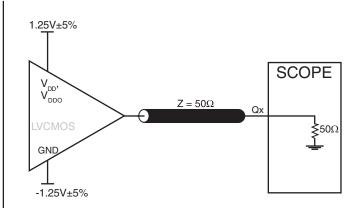

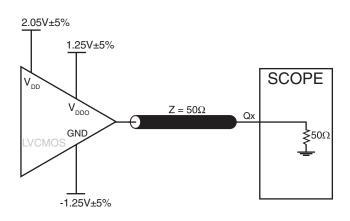

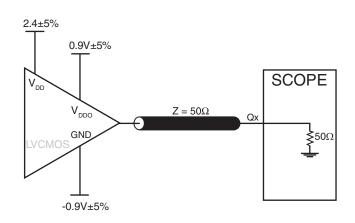

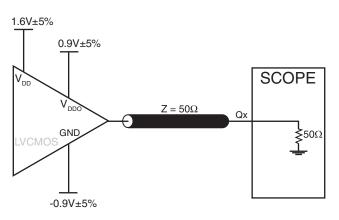

NOTE 1: Outputs terminated with  $50\Omega$  to  $V_{DDO}/2$ . See Parameter Measurement section, "Load Test Circuit" diagrams.

**Table 5A. AC Characteristics,**  $V_{DD} = V_{DDO} = 3.3V \pm 5\%$ , Ta = -40°C to 85°C

| Symbol                          | Parameter                                                                               | Test Conditions                | Minimum | Typical | Maximum | Units |

|---------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub>                | Output Frequency                                                                        |                                |         |         | 250     | MHz   |

| tp <sub>LH</sub>                | Propagation Delay, Low to High; NOTE 1                                                  |                                | 2.4     | 2.7     | 3.0     | ns    |

| tp <sub>HL</sub>                | Propagation Delay, High to Low; NOTE 1                                                  |                                | 2.5     | 2.7     | 2.9     | ns    |

| tsk(i)                          | Input Skew; NOTE 2                                                                      |                                |         | 55      | 225     | ps    |

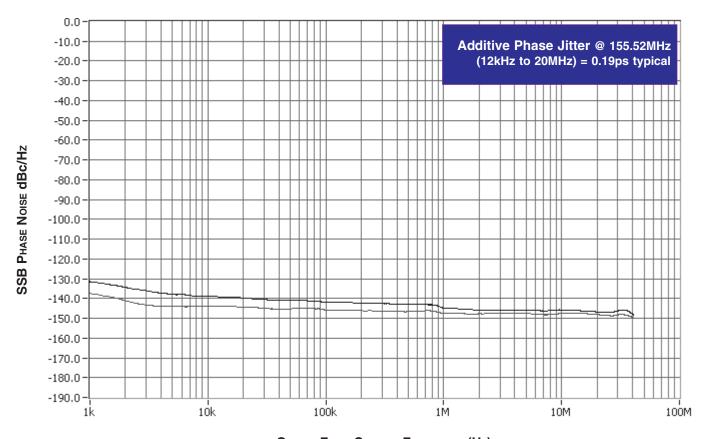

| <i>t</i> jit                    | Buffer Additive Phase Jitter, RMS;<br>refer to Additive Phase Jitter Section;<br>NOTE 3 | 155.52MHz,<br>(12kHz to 20MHz) |         | 0.19    |         | ps    |

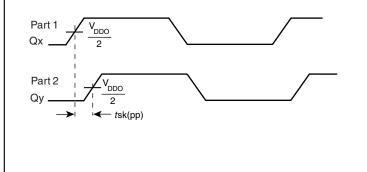

| tsk(pp)                         | Part-to-Part Skew; NOTE 2, 4                                                            |                                |         |         | 780     | ps    |

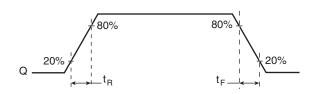

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time                                                                   | 20% to 80%                     | 50      |         | 500     | ps    |

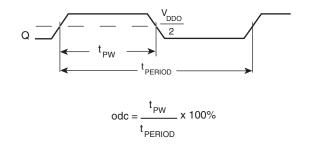

| odc                             | Output Duty Cycle                                                                       |                                | 45      |         | 55      | %     |

| MUX <sub>ISOL</sub>             | MUX Isolation                                                                           | @ 100MHz                       |         | 45      |         | dB    |

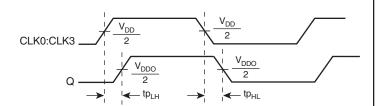

NOTE 1: Measured from  $V_{DD}/2$  of the input to  $V_{DDO}/2$  of the output. NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Driving only one input clock.

NOTE 4: Defined as skew between outputs on different devices operating a the same supply voltages and with equal load conditions. Using the same type of input on each device, the output is measured at  $V_{\rm npo}/2$ .

Table 5B. AC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ ,  $V_{DDO} = 2.5V \pm 5\%$ , Ta = -40°C to  $85^{\circ}$ C

| Symbol                          | Parameter                                                                               | Test Conditions                | Minimum | Typical | Maximum | Units |

|---------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub>                | Output Frequency                                                                        |                                |         |         | 250     | MHz   |

| tp <sub>LH</sub>                | Propagation Delay, Low to High; NOTE 1                                                  |                                | 2.5     | 2.8     | 3.1     | ns    |

| tp <sub>HL</sub>                | Propagation Delay, High to Low; NOTE 1                                                  |                                | 2.6     | 2.8     | 3.0     | ns    |

| tsk(i)                          | Input Skew; NOTE 2                                                                      |                                |         | 45      | 150     | ps    |

| <i>t</i> jit                    | Buffer Additive Phase Jitter, RMS;<br>refer to Additive Phase Jitter Section;<br>NOTE 3 | 155.52MHz,<br>(12kHz to 20MHz) |         | 0.14    |         | ps    |

| tsk(pp)                         | Part-to-Part Skew; NOTE 2, 4                                                            |                                |         |         | 780     | ps    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time                                                                   | 20% to 80%                     | 50      |         | 500     | ps    |

| odc                             | Output Duty Cycle                                                                       |                                | 45      |         | 55      | %     |

| MUX <sub>ISOL</sub>             | MUX Isolation                                                                           | @ 100MHz                       |         | 45      |         | dB    |

NOTE 1: Measured from  $V_{\rm DD}/2$  of the input to  $V_{\rm DDO}/2$  of the output.

NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Driving only one input clock.

NOTE 4: Defined as skew between outputs on different devices operating a the same supply voltages and with equal load conditions. Using the same type of input on each device, the output is measured at  $V_{\rm DDO}/2$ .

Table 5C. AC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ ,  $V_{DDO} = 1.8V \pm 5\%$ , Ta = -40°C to 85°C

| Symbol                          | Parameter                                                                               | Test Conditions                | Minimum | Typical | Maximum | Units |

|---------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub>                | Output Frequency                                                                        |                                |         |         | 250     | MHz   |

| tp <sub>LH</sub>                | Propagation Delay, Low to High; NOTE 1                                                  |                                | 2.7     | 3.2     | 3.8     | ns    |

| tp <sub>HL</sub>                | Propagation Delay, High to Low; NOTE 1                                                  |                                | 2.8     | 3.3     | 3.8     | ns    |

| tsk(i)                          | Input Skew; NOTE 2                                                                      |                                |         | 50      | 150     | ps    |

| <i>t</i> jit                    | Buffer Additive Phase Jitter, RMS;<br>refer to Additive Phase Jitter Section;<br>NOTE 3 | 155.52MHz,<br>(12kHz to 20MHz) |         | 0.16    |         | ps    |

| tsk(pp)                         | Part-to-Part Skew; NOTE 2, 4                                                            |                                |         |         | 780     | ps    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time                                                                   | 20% to 80%                     | 100     |         | 700     | ps    |

| odc                             | Output Duty Cycle                                                                       |                                | 45      |         | 55      | %     |

| MUX <sub>ISOL</sub>             | MUX Isolation                                                                           | @ 100MHz                       |         | 45      |         | dB    |

NOTE 1: Measured from  $V_{\text{DD}}/2$  of the input to  $V_{\text{DDO}}/2$  of the output.

NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Driving only one input clock.

NOTE 4: Defined as skew between outputs on different devices operating a the same supply voltages and with equal load conditions. Using the same type of input on each device, the output is measured at  $V_{ppo}/2$ .

**Table 5D. AC Characteristics,**  $V_{DD} = V_{DDO} = 2.5V \pm 5\%$ , Ta = -40°C to 85°C

| Symbol              | Parameter                                                                               | Test Conditions                | Minimum | Typical | Maximum | Units |

|---------------------|-----------------------------------------------------------------------------------------|--------------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub>    | Output Frequency                                                                        |                                |         |         | 250     | MHz   |

| tp <sub>LH</sub>    | Propagation Delay, Low to High; NOTE 1                                                  |                                | 2.5     | 3.0     | 3.5     | ns    |

| tp <sub>HL</sub>    | Propagation Delay, High to Low; NOTE 1                                                  |                                | 2.5     | 2.9     | 3.4     | ns    |

| tsk(i)              | Input Skew; NOTE 2                                                                      |                                |         | 60      | 175     | ps    |

| tjit                | Buffer Additive Phase Jitter, RMS;<br>refer to Additive Phase Jitter Section;<br>NOTE 3 | 155.52MHz,<br>(12kHz to 20MHz) |         | 0.21    |         | ps    |

| tsk(pp)             | Part-to-Part Skew; NOTE 2, 4                                                            |                                |         |         | 780     | ps    |

| $t_{R}/t_{F}$       | Output Rise/Fall Time                                                                   | 20% to 80%                     | 100     |         | 500     | ps    |

| odc                 | Output Duty Cycle                                                                       |                                | 40      |         | 60      | %     |

| MUX <sub>ISOL</sub> | MUX Isolation                                                                           | @ 100MHz                       |         | 45      |         | dB    |

NOTE 1: Measured from  $V_{DD}/2$  of the input to  $V_{DDO}/2$  of the output. NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Driving only one input clock.

NOTE 4: Defined as skew between outputs on different devices operating a the same supply voltages and with equal load conditions. Using the same type of input on each device, the output is measured at  $V_{ppo}/2$ .

**Table 5E. AC Characteristics,**  $V_{DD} = 2.5V \pm 5\%$ ,  $V_{DDO} = 1.8V \pm -5\%$ , Ta = -40°C to 85°C

| Symbol                          | Parameter                                                                               | Test Conditions                | Minimum | Typical | Maximum | Units |

|---------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub>                | Output Frequency                                                                        |                                |         |         | 250     | MHz   |

| tp <sub>LH</sub>                | Propagation Delay, Low to High; NOTE 1                                                  |                                | 2.6     | 3.3     | 4.0     | ns    |

| tp <sub>HL</sub>                | Propagation Delay, High to Low; NOTE 1                                                  |                                | 2.7     | 3.3     | 4.0     | ns    |

| tsk(i)                          | Input Skew; NOTE 2                                                                      |                                |         | 50      | 150     | ps    |

| tjit                            | Buffer Additive Phase Jitter, RMS;<br>refer to Additive Phase Jitter Section;<br>NOTE 3 | 155.52MHz,<br>(12kHz to 20MHz) |         | 0.17    |         | ps    |

| tsk(pp)                         | Part-to-Part Skew; NOTE 2, 4                                                            |                                |         |         | 780     | ps    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time                                                                   | 20% to 80%                     | 100     |         | 700     | ps    |

| odc                             | Output Duty Cycle                                                                       |                                | 40      |         | 60      | %     |

| MUX <sub>ISOL</sub>             | MUX Isolation                                                                           | @ 100MHz                       |         | 45      |         | dB    |

NOTE 1: Measured from  $V_{\rm DD}/2$  of the input to  $V_{\rm DDO}/2$  of the output.

NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Driving only one input clock.

NOTE 4: Defined as skew between outputs on different devices operating a the same supply voltages and with equal load conditions. Using the same type of input on each device, the output is measured at  $V_{\rm DDO}/2$ .

## **ADDITIVE PHASE JITTER**

The spectral purity in a band at a specific offset from the fundamental compared to the power of the fundamental is called the *dBc Phase Noise*. This value is normally expressed using a Phase noise plot and is most often the specified plot in many applications. Phase noise is defined as the ratio of the noise power present in a 1Hz band at a specified offset from the fundamental frequency to the power value of the fundamental. This ratio is expressed in decibels (dBm) or a ratio of the power in the 1Hz

band to the power in the fundamental. When the required offset is specified, the phase noise is called a *dBc* value, which simply means dBm at a specified offset from the fundamental. By investigating jitter in the frequency domain, we get a better understanding of its effects on the desired application over the entire time record of the signal. It is mathematically possible to calculate an expected bit error rate given a phase noise plot.

OFFSET FROM CARRIER FREQUENCY (Hz)

As with most timing specifications, phase noise measurements has issues relating to the limitations of the equipment. Often the noise floor of the equipment is higher than the noise floor of the device. This is illustrated above. The device meets the noise floor of what is shown, but can actually be lower. The phase noise is dependent on the input source and measurement equipment.

# PARAMETER MEASUREMENT INFORMATION

#### 3.3V CORE/3.3V OUTPUT LOAD AC TEST CIRCUIT

#### 2.5V CORE/2.5V OUTPUT LOAD AC TEST CIRCUIT

### 3.3V Core/2.5V OUTPUT LOAD AC TEST CIRCUIT

3.3V CORE/1.8V OUTPUT LOAD AC TEST CIRCUIT

2.5 CORE/1.8V OUTPUT LOAD AC TEST CIRCUIT

PART-TO-PART SKEW

## PROPAGATION DELAY

INPUT SKEW

# CLKy Q $t_{PD1}$ CLKy $t_{PD2}$ $t_{PD2}$ $t_{PD2}$

## OUTPUT RISE/FALL TIME

OUTPUT DUTY CYCLE/PULSE WIDTH/PERIOD

# **APPLICATION INFORMATION**

## RECOMMENDATIONS FOR UNUSED INPUT PINS

#### INPUTS:

#### **CLK INPUTS**

For applications not requiring the use of a clock input, it can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from the CLK input to ground.

#### LVCMOS CONTROL PINS

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

# RELIABILITY INFORMATION

Table 6.  $\theta_{_{JA}} \text{vs. Air Flow Table for 16 Lead TSSOP}$

# $\theta_{M}$ by Velocity (Linear Feet per Minute)

O200500Single-Layer PCB, JEDEC Standard Test Boards137.1°C/W118.2°C/W106.8°C/WMulti-Layer PCB, JEDEC Standard Test Boards89.0°C/W81.8°C/W78.1°C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

#### TRANSISTOR COUNT

The transistor count for ICS83054I is: 874

# PACKAGE OUTLINE AND PACKAGE DIMENSIONS

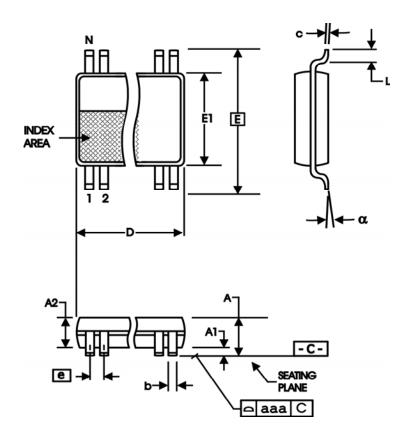

PACKAGE OUTLINE - G SUFFIX FOR 16 LEAD TSSOP

TABLE 7. PACKAGE DIMENSIONS

| SYMBOL   | Millimeters |         |  |

|----------|-------------|---------|--|

| STIVIBUL | Minimum     | Maximum |  |

| N        | 1           | 6       |  |

| Α        |             | 1.20    |  |

| A1       | 0.05        | 0.15    |  |

| A2       | 0.80        | 1.05    |  |

| b        | 0.19        | 0.30    |  |

| С        | 0.09        | 0.20    |  |

| D        | 4.90        | 5.10    |  |

| E        | 6.40 E      | BASIC   |  |

| E1       | 4.30        | 4.50    |  |

| е        | 0.65 E      | BASIC   |  |

| L        | 0.45        | 0.75    |  |

| α        | 0°          | 8°      |  |

| aaa      |             | 0.10    |  |

Reference Document: JEDEC Publication 95, MO-153

Table 8. Ordering Information

| Part/Order Number | Marking  | Package                   | Shipping Packaging | Temperature   |

|-------------------|----------|---------------------------|--------------------|---------------|

| 83054AGI          | 83054AGI | 16 Lead TSSOP             | tube               | -40°C to 85°C |

| 83054AGIT         | 83054AGI | 16 Lead TSSOP             | 2500 tape & reel   | -40°C to 85°C |

| 83054AGILF        | 83054AIL | 16 Lead "Lead-Free" TSSOP | tube               | -40°C to 85°C |

| 83054AGILFT       | 83054AIL | 16 Lead "Lead-Free" TSSOP | 2500 tape & reel   | -40°C to 85°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology, Incorporated (IDT) assumes no responsibility for either its use or for infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial and industrial applications. Any other applications such as those requiring high reliability or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

|     | REVISION HISTORY SHEET                    |                 |                                                                                                                                                  |          |  |

|-----|-------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| Rev | Rev Table Page Description of Change Date |                 |                                                                                                                                                  |          |  |

| Α   | T8                                        | 12              | Ordering Information Table - corrected Part/Order Numbers.                                                                                       | 1/3/06   |  |

| В   | T5A - T5E                                 | 1<br>4 - 6<br>7 | Features Section - added Additive Phase Jitter bullet. AC Characteristics Tables - added tjit row and spec. Added Additive Phase Jitter section. | 01/04/07 |  |

| С   | T5A - T5E                                 | 4 - 6           | AC Characteristics Tables - changed part-to-part skew specs.                                                                                     | 03/07/08 |  |

# Innovate with IDT and accelerate your future networks. Contact:

www.IDT.com

For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775 For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Japan

NIPPON IDT KK Sanbancho Tokyu Bld. 7F, 8-1 Sanbancho Chiyoda-ku, Tokyo 102-0075 +81 3 3221 9822 +81 3 3221 9824 (fax)

#### **Asia**

Integrated Device Technology IDT (S) Pte. Ltd. 1 Kallang Sector, #07-01/06 Kolam Ayer Industrial Park Singapore 349276 +65 6 744 3356 +65 6 744 1764 (fax)

#### **Europe**

IDT Europe, Limited 321 Kingston Road Leatherhead, Surrey KT22 7TU England +44 (0) 1372 363 339 +44 (0) 1372 378851 (fax)