# FM RADIO TRANSMITTER WITH RECEIVE POWER SCAN

#### **Features**

- Integrated receive power measurement

- Worldwide FM band support (76–108 MHz)

- Requires only two external components

- Frequency synthesizer with integrated VCO

- Digital stereo modulator

- Programmable pre-emphasis

- Analog/digital audio interface

- Audio silence detector

- Programmable reference clock

- RDS/RBDS encoder (Si4713 only)

- PCB loop and stub antenna support with self-calibrated capacitor tuning

- Programmable transmit level

- Audio dynamic range control

- Advanced modulation control

- 2.7 to 5.5 V supply voltage

- Integrated LDO regulator

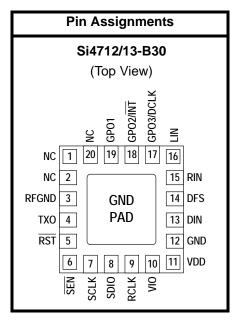

- 3 x 3 x 0.55 mm 20-pin QFN

- Pb-free and RoHS Compliant

- Designed for compatibility with cellular operation

Ordering Information: See page 34.

## **Applications**

- Cellular handsets/hands-free

- MP3 players

- Portable media players

- Wireless speakers/microphone

- Satellite digital audio radios

- Personal computers/notebooks

# **Description**

The Si4712/13-B30 integrates the complete transmit functions for standards-compliant unlicensed FM broadcast stereo transmission. The chip also allows integrated receive power scanning to identify low signal power FM channels. Users must comply with local regulations on radio frequency (RF) transmission.

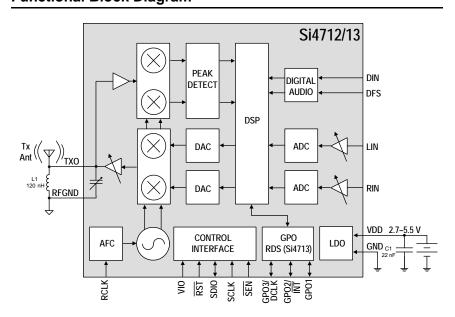

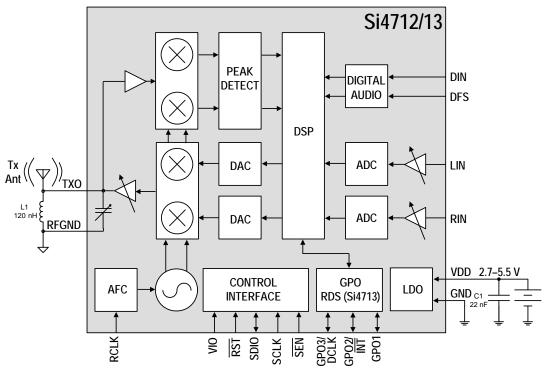

## **Functional Block Diagram**

## Patents pending

Note: To ensure proper operation and performance, follow the guidelines in "AN383: Universal Antenna Selection and Layout Guidelines." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

2

# TABLE OF CONTENTS

| <u>Section</u>                                       | <u>Page</u> |

|------------------------------------------------------|-------------|

| 1. Electrical Specifications                         | 4           |

| 2. Test Circuit                                      |             |

| 2.1. Test Circuit Schematic                          | 15          |

| 2.2. Test Circuit Bill of Materials                  | 15          |

| 3. Typical Application Schematics                    | 16          |

| 3.1. Analog Audio Inputs                             | 16          |

| 3.2. Digital Audio Inputs                            | 17          |

| 3.3. Typical Application Schematic Bill of Materials | 17          |

| 4. Universal AM/FM RX/FM TX Application Schematic    | 18          |

| 4.1. Universal AM/FM RX/FM TX Bill of Materials      | 19          |

| 5. Functional Description                            | 20          |

| 5.1. Overview                                        | 20          |

| 5.2. FM Transmitter                                  | 21          |

| 5.3. Receive Power Scan                              |             |

| 5.4. Digital Audio Interface                         |             |

| 5.5. Line Input                                      |             |

| 5.6. Audio Dynamic Range Control                     |             |

| 5.7. Audio Limiter                                   |             |

| 5.8. Pre-emphasis and De-emphasis                    |             |

| 5.9. RDS/RBDS Processor (Si4713 Only)                |             |

| 5.10. Tuning                                         |             |

| 5.11. Reference Clock                                |             |

| 5.12. Control Interface                              |             |

| 5.13. GPO Outputs                                    |             |

| 5.14. Reset, Powerup, and Powerdown                  |             |

| 5.15. Programming with Commands                      |             |

| 6. Commands and Properties                           |             |

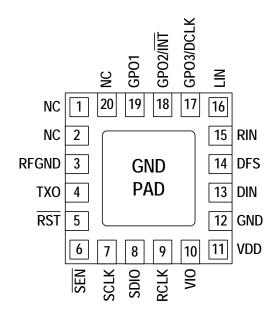

| 7. Pin Descriptions: Si4712/13-GM                    |             |

| 8. Ordering Guide                                    |             |

| 9. Package Markings (Top Marks)                      |             |

| 9.1. Si4712 Top Mark                                 |             |

| 9.2. Si4713 Top Mark                                 |             |

| 9.3. Top Mark Explanation                            | 35          |

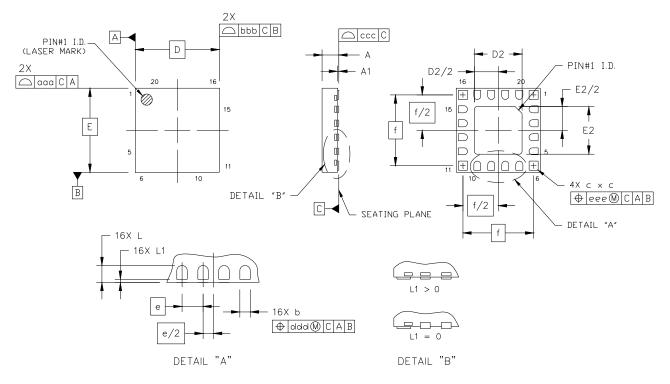

| 10. Package Outline: Si4712/13-GM                    |             |

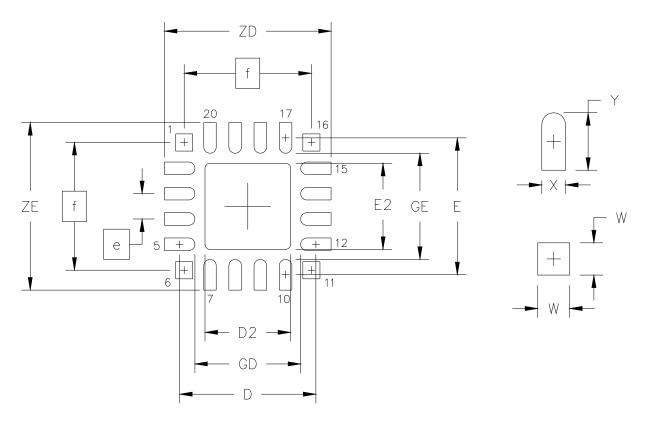

| 11. PCB Land Pattern: Si4712/13-GM                   |             |

| 12. Additional Reference Resources                   |             |

| Document Change List                                 |             |

| Contact Information                                  | 42          |

# 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter                          | Symbol              | Test Condition | Min | Тур | Max | Unit |

|------------------------------------|---------------------|----------------|-----|-----|-----|------|

| Supply Voltage                     | $V_{DD}$            |                | 2.7 | _   | 5.5 | V    |

| Interface Supply Voltage           | V <sub>IO</sub>     |                | 1.5 |     | 3.6 | V    |

| Power Supply Powerup Rise Time     | V <sub>DDRISE</sub> |                | 10  |     | _   | μs   |

| Interface Supply Powerup Rise Time | V <sub>IORISE</sub> |                | 10  | _   | _   | μs   |

| Ambient Temperature                | T <sub>A</sub>      |                | -20 | 25  | 85  | °C   |

**Note:** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at V<sub>DD</sub> = 3.3 V and 25 °C unless otherwise stated. Parameters are tested in production unless otherwise stated.

Table 2. Absolute Maximum Ratings<sup>1,2</sup>

| Parameter                   | Symbol           | Value                           | Unit            |

|-----------------------------|------------------|---------------------------------|-----------------|

| Supply Voltage              | V <sub>DD</sub>  | -0.5 to 5.8                     | V               |

| Interface Supply Voltage    | V <sub>IO</sub>  | -0.5 to 3.9                     | V               |

| Input Current <sup>3</sup>  | I <sub>IN</sub>  | 10                              | mA              |

| Input Voltage <sup>3</sup>  | V <sub>IN</sub>  | -0.3 to (V <sub>IO</sub> + 0.3) | V               |

| Operating Temperature       | T <sub>OP</sub>  | -40 to 95                       | °C              |

| Storage Temperature         | T <sub>STG</sub> | -55 to 150                      | °C              |

| RF Input Level <sup>4</sup> |                  | 0.4                             | V <sub>PK</sub> |

#### Notes:

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure beyond recommended operating conditions for extended periods may affect device reliability.

- 2. The Si4712/13 devices are high-performance RF integrated circuits with certain pins having an ESD rating of < 2 kV HBM. Handling and assembly of these devices should only be done at ESD-protected workstations.

- 3. For input pins SCLK, SEN, SDIO, RST, RCLK, DCLK, DFS, DIN, GPO1, GPO2/INT, and GPO3.

- 4. At RF input pin, TXO.

## **Table 3. DC Characteristics**

Test conditions:  $V_{RF}$  = 118 dB $\mu$ V, stereo,  $\Delta f$  = 68.25 kHz,  $\Delta f$ pilot = 6.75 kHz, REFCLK = 32.768 kHz, unless otherwise specified.

Production test conditions:  $V_{DD}$  = 3.3 V,  $V_{IO}$  = 3.3 V,  $T_{A}$  = 25 °C,  $F_{RF}$  = 98 MHz.

Characterization test conditions:  $V_{DD}$  = 2.7 to 5.5 V,  $V_{IO}$  = 1.5 to 3.6 V,  $T_A$  = -20 to 85 °C,  $F_{RF}$  = 76–108 MHz.

| Parameter                                   | Symbol           | Test Condition                                 | Min                   | Тур  | Max                   | Unit |  |

|---------------------------------------------|------------------|------------------------------------------------|-----------------------|------|-----------------------|------|--|

| FM Transmitter from Line Input              |                  |                                                |                       |      |                       |      |  |

| TX Supply Current                           | $I_{TX}$         |                                                | _                     | 18.8 | 22.8                  | mA   |  |

| TX Interface Supply Current                 | I <sub>IO</sub>  |                                                | _                     | 320  | 600                   | μA   |  |

| FM Transmitter from Digital Audio Input     |                  |                                                |                       |      |                       |      |  |

| TX Supply Current                           | I <sub>DTX</sub> | DCLK = 3.072 MHz                               | _                     | 18.3 | _                     | mA   |  |

| TX Interface Supply Current                 | I <sub>DIO</sub> | DCLK = 3.072 MHz                               | _                     | 320  | _                     | μΑ   |  |

| FM Transmitter in Receive Power             | er Scan M        | ode                                            |                       |      |                       |      |  |

| RX Supply Current                           | I <sub>RX</sub>  |                                                | _                     | 16.8 | _                     | mA   |  |

| RX Interface Supply Current                 | I <sub>IO</sub>  |                                                | _                     | 320  | _                     | μΑ   |  |

| Supplies and Interface                      |                  |                                                |                       |      |                       |      |  |

| V <sub>DD</sub> Powerdown Current           | I <sub>DD</sub>  | Powerdown mode                                 | _                     | 10   | 20                    | μA   |  |

| V <sub>IO</sub> Interface Powerdown Current | I <sub>IO</sub>  | SCLK, RCLK inactive<br>Powerdown mode          | _                     | 3    | 10                    | μΑ   |  |

| High Level Input Voltage <sup>1</sup>       | V <sub>IH</sub>  |                                                | 0.7 x V <sub>IO</sub> | _    | V <sub>IO</sub> + 0.3 | V    |  |

| Low Level Input Voltage <sup>1</sup>        | $V_{IL}$         |                                                | -0.3                  | _    | 0.3 x V <sub>IO</sub> | V    |  |

| High Level Input Current <sup>1</sup>       | I <sub>IH</sub>  | $V_{IN} = V_{IO} = 3.6 \text{ V}$              | -10                   | _    | 10                    | μΑ   |  |

| Low Level Input Current <sup>1</sup>        | I <sub>IL</sub>  | $V_{IN} = 0 \text{ V}, V_{IO} = 3.6 \text{ V}$ | -10                   | _    | 10                    | μΑ   |  |

| High Level Output Voltage <sup>2</sup>      | V <sub>OH</sub>  | I <sub>OUT</sub> = 500 μA                      | 0.8 x V <sub>IO</sub> | _    | _                     | V    |  |

| Low Level Output Voltage <sup>2</sup>       | V <sub>OL</sub>  | I <sub>OUT</sub> = -500 μA                     |                       |      | 0.2 x V <sub>IO</sub> | V    |  |

#### Notes:

- 1. For input pins SCLK, SEN, SDIO, RST, RCLK, DCLK, DFS, DIN, GPO1, GPO2/INT, and GPO3.

- 2. For output pins SDIO, GPO1, GPO2/INT, and GPO3.

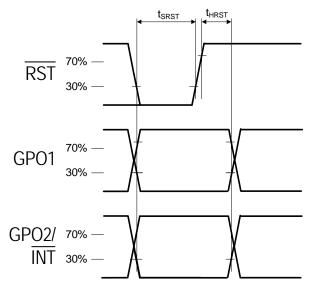

# Table 4. Reset Timing Characteristics 1,2,3

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_A = -20 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                                                     | Symbol            | Min | Тур | Max | Unit |

|---------------------------------------------------------------|-------------------|-----|-----|-----|------|

| RST Pulse Width and GPO1, GPO2/INT Setup to RST <sup>↑4</sup> | t <sub>SRST</sub> | 100 | _   | _   | μs   |

| GPO1, GPO2/INT Hold from RST↑                                 | t <sub>HRST</sub> | 30  | _   | _   | ns   |

#### **Important Notes:**

- 1. When selecting 2-wire mode, the user must ensure that a 2-wire start condition (falling edge of SDIO while SCLK is high) does not occur within 300 ns before the rising edge of RST.

- 2. When selecting 2-wire mode, the user must ensure that SCLK is high during the rising edge of RST, and stays high until after the 1st start condition.

- 3. When selecting 3-wire or <u>SPI</u> modes, the user must ensure that a rising edge of SCLK does not occur within 300 ns before the rising edge of RST.

- 4. If GPO1 and GPO2 are actively driven by the user, then minimum  $t_{SRST}$  is only 30 ns. If GPO1 or GPO2 is hi-Z, then minimum  $t_{SRST}$  is 100  $\mu$ s, to provide time for on-chip 1 M $\Omega$  devices (active while  $\overline{RST}$  is low) to pull GPO1 high and GPO2 low.

Figure 1. Reset Timing Parameters for Busmode Select

SHIPPN LADS

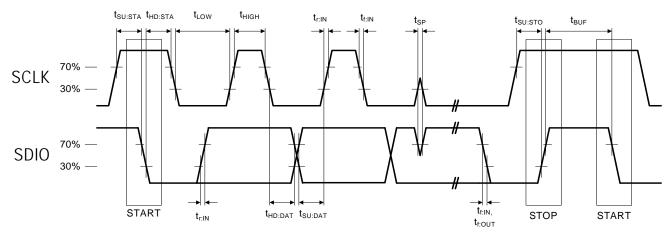

Table 5. 2-Wire Control Interface Characteristics 1,2,3

(V<sub>DD</sub> = 2.7 to 5.5 V, V<sub>IO</sub> = 1.5 to 3.6 V,  $T_A$  = -20 to 85 °C)

| Parameter                                    | Symbol                                 | Test Condition | Min                                 | Тур | Max | Unit |

|----------------------------------------------|----------------------------------------|----------------|-------------------------------------|-----|-----|------|

| SCLK Frequency                               | f <sub>SCL</sub>                       |                | 0                                   | _   | 400 | kHz  |

| SCLK Low Time                                | t <sub>LOW</sub>                       |                | 1.3                                 | _   | _   | μs   |

| SCLK High Time                               | t <sub>HIGH</sub>                      |                | 0.6                                 | _   | _   | μs   |

| SCLK Input to SDIO↓ Setup<br>(START)         | t <sub>SU:STA</sub>                    |                | 0.6                                 | _   | _   | μs   |

| SCLK Input to SDIO                           | t <sub>HD:STA</sub>                    |                | 0.6                                 | _   | _   | μs   |

| SDIO Input to SCLK <sup>↑</sup> Setup        | t <sub>SU:DAT</sub>                    |                | 100                                 | _   | _   | ns   |

| SDIO Input to SCLK↓ Hold <sup>4,5</sup>      | t <sub>HD:DAT</sub>                    |                | 0                                   | _   | 900 | ns   |

| SCLK input to SDIO <sup>↑</sup> Setup (STOP) | t <sub>SU:STO</sub>                    |                | 0.6                                 | _   | _   | μs   |

| STOP to START Time                           | t <sub>BUF</sub>                       |                | 1.3                                 | _   | _   | μs   |

| SDIO Output Fall Time                        | t <sub>f:OUT</sub>                     |                | $20 + 0.1 \frac{C_b}{1 \text{ pF}}$ | _   | 250 | ns   |

| SDIO Input, SCLK Rise/Fall Time              | t <sub>f:IN</sub><br>t <sub>r:IN</sub> |                | $20 + 0.1 \frac{C_b}{1 \text{ pF}}$ | _   | 300 | ns   |

| SCLK, SDIO Capacitive Loading                | C <sub>b</sub>                         |                | _                                   | _   | 50  | pF   |

| Input Filter Pulse Suppression               | t <sub>SP</sub>                        |                | _                                   | _   | 50  | ns   |

#### **Notes**

- 1. When  $V_{IO}$  = 0 V, SCLK and SDIO are low-impedance. 2-wire control interface is  $I^2C$  compatible.

- 2. When selecting 2-wire mode, the user must ensure that a 2-wire start condition (falling edge of SDIO while SCLK is high) does not occur within 300 ns before the rising edge of RST.

- 3. When selecting 2-wire mode, the user must ensure that SCLK is high during the rising edge of RST, and stays high until after the first start condition.

- 4. The Si4712/13 delays SDIO by a minimum of 300 ns from the  $V_{IH}$  threshold of SCLK to comply with the minimum  $t_{HD:DAT}$  specification.

- 5. The maximum t<sub>HD:DAT</sub> has only to be met when f<sub>SCL</sub> = 400 kHz. At frequencies below 400 KHz, t<sub>HD:DAT</sub> may be violated as long as all other timing parameters are met.

7

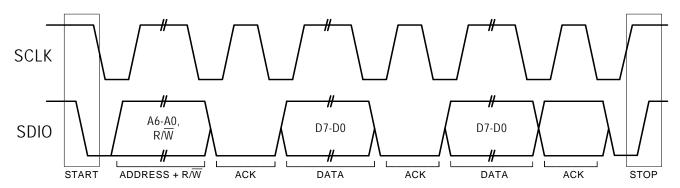

Figure 2. 2-Wire Control Interface Read and Write Timing Parameters

Figure 3. 2-Wire Control Interface Read and Write Timing Diagram

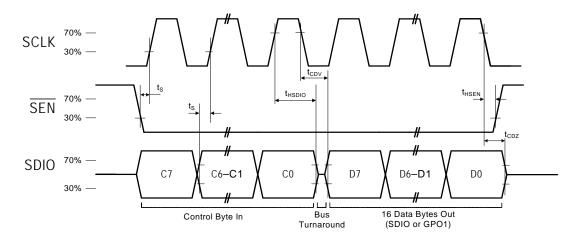

**Table 6. 3-Wire Control Interface Characteristics**

(V<sub>DD</sub> = 2.7 to 5.5 V, V<sub>IO</sub> = 1.5 to 3.6 V,  $T_A$  = -20 to 85 °C)

| Parameter                               | Symbol                           | Test Condition | Min | Тур | Max | Unit |

|-----------------------------------------|----------------------------------|----------------|-----|-----|-----|------|

| SCLK Frequency                          | f <sub>CLK</sub>                 |                | 0   | _   | 2.5 | MHz  |

| SCLK High Time                          | t <sub>HIGH</sub>                |                | 25  | _   | _   | ns   |

| SCLK Low Time                           | t <sub>LOW</sub>                 |                | 25  | _   | _   | ns   |

| SDIO Input, SEN to SCLK↑ Setup          | t <sub>S</sub>                   |                | 20  | _   | _   | ns   |

| SDIO Input to SCLK↑ Hold                | t <sub>HSDIO</sub>               |                | 10  | _   | _   | ns   |

| SEN Input to SCLK↓ Hold                 | t <sub>HSEN</sub>                |                | 10  | _   | _   | ns   |

| SCLK <sup>↑</sup> to SDIO Output Valid  | t <sub>CDV</sub>                 | Read           | 2   | _   | 25  | ns   |

| SCLK <sup>↑</sup> to SDIO Output High Z | t <sub>CDZ</sub>                 | Read           | 2   | _   | 25  | ns   |

| SCLK, SEN, SDIO, Rise/Fall time         | t <sub>R</sub><br>t <sub>F</sub> |                | _   | _   | 10  | ns   |

**Note:** When selecting 3-wire mode, the user must ensure that a rising edge of SCLK does not occur within 300 ns before the rising edge of RST.

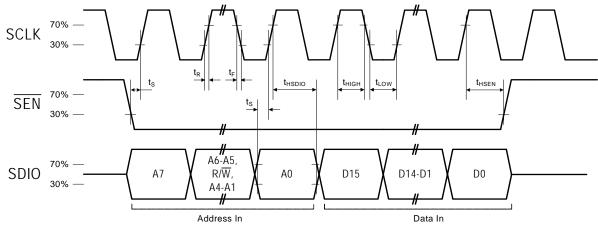

Figure 4. 3-Wire Control Interface Write Timing Parameters

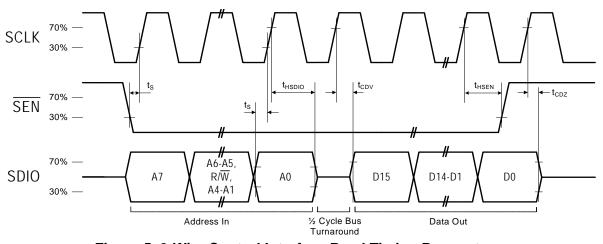

Figure 5. 3-Wire Control Interface Read Timing Parameters

**Table 7. SPI Control Interface Characteristics**

(V<sub>DD</sub> = 2.7 to 5.5 V, V<sub>IO</sub> = 1.5 to 3.6 V,  $T_A$  = -20 to 85 °C)

| Parameter                       | Symbol                         | Test Condition | Min | Тур | Max | Unit |

|---------------------------------|--------------------------------|----------------|-----|-----|-----|------|

| SCLK Frequency                  | f <sub>CLK</sub>               |                | 0   | _   | 2.5 | MHz  |

| SCLK High Time                  | t <sub>HIGH</sub>              |                | 25  | _   | _   | ns   |

| SCLK Low Time                   | t <sub>LOW</sub>               |                | 25  | _   | _   | ns   |

| SDIO Input, SEN to SCLK↑ Setup  | t <sub>S</sub>                 |                | 15  | _   | _   | ns   |

| SDIO Input to SCLK↑ Hold        | t <sub>HSDIO</sub>             |                | 10  | _   | _   | ns   |

| SEN Input to SCLK↓ Hold         | t <sub>HSEN</sub>              |                | 5   | _   | _   | ns   |

| SCLK√ to SDIO Output Valid      | t <sub>CDV</sub>               | Read           | 2   | _   | 25  | ns   |

| SCLK↓ to SDIO Output High Z     | t <sub>CDZ</sub>               | Read           | 2   | _   | 25  | ns   |

| SCLK, SEN, SDIO, Rise/Fall time | t <sub>R,</sub> t <sub>F</sub> |                | _   |     | 10  | ns   |

**Note:** When selecting <u>SPI</u> mode, the user must ensure that a rising edge of SCLK does not occur within 300 ns before the rising edge of RST.

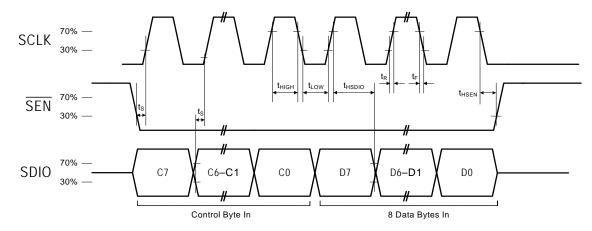

**Figure 6. SPI Control Interface Write Timing Parameters**

Figure 7. SPI Control Interface Read Timing Parameters

SHIPPN LAPS

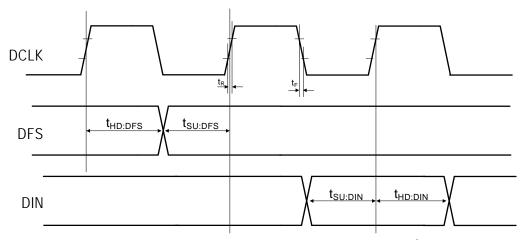

## **Table 8. Digital Audio Interface Characteristics**

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_A = -20 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                             | Symbol                           | Test Condition | Min | Тур | Max  | Unit |

|---------------------------------------|----------------------------------|----------------|-----|-----|------|------|

| DCLK pulse width high                 | t <sub>DCH</sub>                 |                | 10  | _   | _    | ns   |

| DCLK pulse width low                  | t <sub>DCL</sub>                 |                | 10  | _   |      | ns   |

| DFS set-up time to DCLK rising edge   | t <sub>SU:DFS</sub>              |                | 5   | _   |      | ns   |

| DFS hold time from DCLK rising edge   | t <sub>HD:DFS</sub>              |                | 5   | _   |      | ns   |

| DIN set-up time from DCLK rising edge | t <sub>SU:DIN</sub>              |                | 5   | _   |      | ns   |

| DIN hold time from DCLK rising edge   | t <sub>HD:DIN</sub>              |                | 5   | _   |      | ns   |

| DCLK, DFS, DIN, Rise/Fall time        | t <sub>R</sub><br>t <sub>F</sub> |                | _   | _   | 10   | ns   |

| DCLK Tx Frequency <sup>1,2</sup>      |                                  |                | 1.0 | _   | 40.0 | MHz  |

## Notes:

- 1. Guaranteed by characterization.

- 2. The DCLK frequency may be set below the minimum specification if DIGITAL\_INPUT\_SAMPLE\_RATE is first set to 0 (disable).

Figure 8. Digital Audio Interface Timing Parameters, I<sup>2</sup>S Mode

# Table 9. FM Transmitter Characteristics<sup>1</sup>

(Test conditions:  $V_{RF}$  = 118 dB $\mu$ V, stereo,  $\Delta$ f = 68.25 kHz,  $\Delta$ fpilot = 6.75 kHz, REFCLK = 32.768 kHz, 75  $\mu$ s pre-emphasis, unless otherwise specified.

Production test conditions:  $V_{DD} = 3.3 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}$ ,  $T_{A} = 25 \,^{\circ}\text{C}$ ,  $F_{RF} = 98 \, \text{MHz}$ .

Characterization test conditions:  $V_{DD} = 2.7$  to 5.5 V,  $V_{IO} = 1.5$  to 3.6 V,  $T_{A} = -20$  to 85 °C,  $F_{RF} = 76-108$  MHz.

All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at  $V_{DD}$  = 3.3 V and 25 °C unless otherwise stated.

Parameters are tested in production unless otherwise specified.)

| Parameter                                                | Symbol            | Test Condition                                                                | Min    | Тур | Max    | Unit  |

|----------------------------------------------------------|-------------------|-------------------------------------------------------------------------------|--------|-----|--------|-------|

| Transmit Frequency Range <sup>2</sup>                    | f <sub>RF</sub>   |                                                                               | 76     | _   | 108    | MHz   |

| Transmit Frequency Accuracy and Stability <sup>2,3</sup> |                   |                                                                               | -3.5   | _   | 3.5    | kHz   |

| Transmit Voltage Accuracy <sup>2</sup>                   |                   | V <sub>RF</sub> = 103–117 dBμV                                                | -2.5   | _   | 2.5    | dB    |

| Transmit Voltage Accuracy                                |                   | V <sub>RF</sub> = 102, 118 dBμV                                               | -2.5   |     | 2.5    | dB    |

| Transmit Voltage Temperature Coefficient <sup>2</sup>    |                   |                                                                               | -0.075 | _   | -0.025 | dB/ºC |

| Transmit Channel Edge Power                              |                   | > ±100 kHz,<br>pre-emphasis off                                               | _      | _   | -20    | dBc   |

| Transmit Adjacent Channel Power                          |                   | > ±200 kHz,<br>pre-emphasis off                                               | _      | -30 | -26    | dBc   |

| Transmit Alternate Channel Power                         |                   | > ±400 kHz,<br>pre-emphasis off                                               | _      | -30 | -26    | dBc   |

| Transmit Emissions                                       |                   | In-band (76–108 MHz)                                                          | _      | _   | -30    | dBc   |

| Output Capacitance Max <sup>2</sup>                      | C <sub>TUNE</sub> |                                                                               | _      | 53  | _      | pF    |

| Output Capacitance Min <sup>2</sup>                      | C <sub>TUNE</sub> |                                                                               | _      | 5   | _      | pF    |

| Pre-emphasis Time Constant <sup>2</sup>                  |                   | TX_PREMPHASIS = 75 µs                                                         | 70     | 75  | 80     | μs    |

|                                                          |                   | TX_PREMPHASIS = 50 µs                                                         | 45     | 50  | 54     | μs    |

| Audio SNR Mono <sup>2</sup>                              |                   | $\Delta f$ = 22.5 kHz, Mono, limiter off                                      | 58     | 63  | _      | dB    |

| Audio SNR Stereo                                         |                   | $\Delta f$ = 22.5 kHz,<br>$\Delta f$ pilot = 6.75 kHz, Stereo,<br>limiter off | 53     | 58  | _      | dB    |

| Audio THD Mono                                           |                   | $\Delta f$ = 75 kHz, Mono, limiter off                                        | _      | 0.1 | 0.5    | %     |

| Audio THD Stereo <sup>2</sup>                            |                   | $\Delta f$ = 22.5 kHz,<br>$\Delta f$ pilot = 6.75 kHz, Stereo,<br>limiter off | _      | 0.1 | 0.5    | %     |

#### Notes

- FM transmitter performance specifications are subject to adherence to Silicon Laboratories guidelines in "AN383:

Universal Antenna Selection and Layout Guidelines." Silicon Laboratories will evaluate schematics and layouts for

qualified customers. Tested with test schematic (L = 120 nH, Q ≥ 30) shown in Figure 9 on page 15.

- 2. Guaranteed by characterization.

- 3. No measurable  $\Delta fRF/\Delta V_{DD}$  at  $\Delta V_{DD}$  of 500 mVpk-pk at 100 Hz to 10 kHz.

# Table 9. FM Transmitter Characteristics<sup>1</sup> (Continued)

(Test conditions:  $V_{RF}$  = 118 dB $\mu$ V, stereo,  $\Delta$ f = 68.25 kHz,  $\Delta$ fpilot = 6.75 kHz, REFCLK = 32.768 kHz, 75  $\mu$ s pre-emphasis, unless otherwise specified.

Production test conditions:  $V_{DD}$  = 3.3 V,  $V_{IO}$  = 3.3 V,  $T_{A}$  = 25 °C,  $F_{RF}$  = 98 MHz.

Characterization test conditions:  $V_{DD} = 2.7$  to 5.5 V,  $V_{IO} = 1.5$  to 3.6 V,  $T_{A} = -20$  to 85 °C,  $F_{RF} = 76-108$  MHz.

All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at  $V_{DD} = 3.3 \text{ V}$  and 25 °C unless otherwise stated.

Parameters are tested in production unless otherwise specified.)

| Parameter                                                      | Symbol          | Test Condition                                                                                | Min  | Тур | Max   | Unit            |

|----------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------|------|-----|-------|-----------------|

| Audio Stereo Separation <sup>2</sup>                           |                 | left channel only                                                                             | 30   | 35  | _     | dB              |

| Sub Carrier Rejection Ratio                                    | SCR             |                                                                                               | 40   | 50  | _     | dB              |

| Powerup Settling Time <sup>2</sup>                             |                 |                                                                                               | _    | _   | 110   | ms              |

| Input Signal Level <sup>2</sup>                                | V <sub>AI</sub> |                                                                                               |      | _   | 0.636 | V <sub>PK</sub> |

| Frequency Flatness <sup>2</sup>                                |                 | Mono, ±1.5 dB,<br>$\Delta f = 75$ kHz, 0, 50, 75 $\mu$ s<br>pre-emphasis, limiter off         | 30   | _   | 15 k  | Hz              |

| High Pass Corner Frequency <sup>2</sup>                        |                 | Mono, $-3$ dB, $\Delta f = 75$ kHz, 0, 50, 75 $\mu$ s pre-emphasis, limiter off               | 5    | _   | 30    | Hz              |

| Low Pass Corner Frequency <sup>2</sup>                         |                 | Mono, $-3$ dB, $\Delta f = 75$ kHz, 0, 50, 75 $\mu$ s pre-emphasis, limiter off               | 15 k | _   | 16 k  | Hz              |

| Audio Imbalance                                                |                 | Mono                                                                                          | -1   | _   | 1     | dB              |

| Pilot Modulation Rate Accuracy <sup>2</sup>                    |                 | $\Delta f = 68.25 \text{ kHz},$<br>$\Delta f \text{pilot} = 6.75 \text{ kHz}, \text{ Stereo}$ | -10  | _   | 10    | %               |

| Audio Modulation Rate Accuracy <sup>2</sup>                    |                 | $\Delta f = 68.25 \text{ kHz},$<br>$\Delta f \text{pilot} = 6.75 \text{ kHz}, \text{ Stereo}$ | -10  | _   | 10    | %               |

| Input Resistance <sup>2</sup>                                  |                 | LIATTEN[1:0] = 11                                                                             | 50   | 60  | _     | kΩ              |

| Input Capacitance <sup>2</sup>                                 |                 |                                                                                               | _    | 10  | _     | pF              |

| Received Noise Level Accuracy<br>(Si4712/13 Only) <sup>2</sup> |                 | 60 dBμV input, T <sub>A</sub> = 25 °C                                                         | _    | 54  | _     | dBuV            |

#### Notes:

- FM transmitter performance specifications are subject to adherence to Silicon Laboratories guidelines in "AN383:

Universal Antenna Selection and Layout Guidelines." Silicon Laboratories will evaluate schematics and layouts for

qualified customers. Tested with test schematic (L = 120 nH, Q ≥ 30) shown in Figure 9 on page 15.

- 2. Guaranteed by characterization.

- 3. No measurable  $\Delta fRF/\Delta V_{DD}$  at  $\Delta V_{DD}$  of 500 mVpk-pk at 100 Hz to 10 kHz.

# Table 10. FM Receive Power Scan Characteristics 1,2

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_{A} = -20 \text{ to } 85 ^{\circ}\text{C}, F_{RF} = 76-108 \text{ MHz})$

| Parameter                                             | Symbol | Test Condition | Min | Тур | Max | Unit |

|-------------------------------------------------------|--------|----------------|-----|-----|-----|------|

| Tune and Signal Strength Measurement Time per Channel |        |                | _   | _   | 80  | ms   |

#### Notes:

- 1. Settling time for ac coupling capacitors on the audio input pins after Receive to Transmit transition can take a few hundred milliseconds. The actual settling time depends on the values of the ac-coupling capacitors. Using digital audio input mode avoids this settling time.

- 2. Guaranteed by characterization.

## **Table 11. Reference Clock Characteristics**

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_{A} = -20 \text{ to } 85 \text{ °C}, F_{RF} = 76-108 \text{ MHz})$

| Supported Parameter                 | Symbol | Test Condition | Min    | Тур    | Max    | Unit |

|-------------------------------------|--------|----------------|--------|--------|--------|------|

| RCLK Frequency Range <sup>1,2</sup> |        |                | 31.130 | 32.768 | 40,000 | kHz  |

| Frequency Tolerance <sup>1</sup>    |        |                | -50    | _      | 50     | ppm  |

#### Notes:

- 1. Guaranteed by characterization.

- 2. The RCLK frequency divided by an integer number (the prescaler value) must fall in the range of 31,130 to 34,406 Hz. Therefore, the range of RCLK frequencies is not continuous below frequencies of 311.3 kHz.

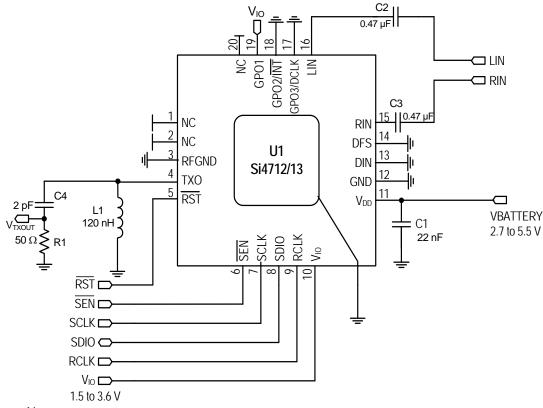

## 2. Test Circuit

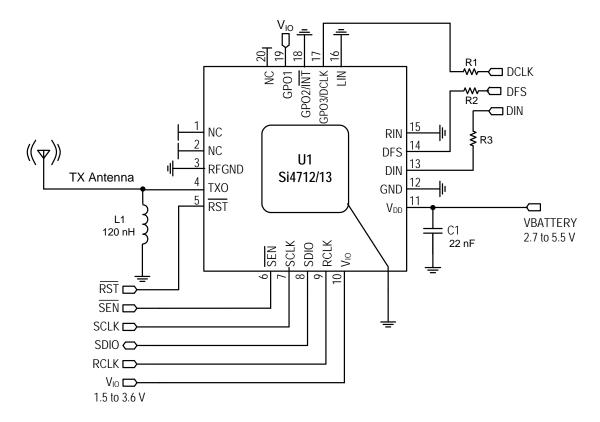

## 2.1. Test Circuit Schematic

#### Notes:

- 1. Si4712/13 is shown configured in I<sup>2</sup>C compatible bus mode.

- 2. GPO2/INT can be configured for interrupts with the powerup command.

- 3. To ensure proper operation and FM transmitter performance, follow the guidelines in "AN383: 3 mm x 3 mm QFN Universal Layout Guide." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- 4. LIN, RIN line inputs must be ac-coupled.

Figure 9. Test Circuit Schematic

# 2.2. Test Circuit Bill of Materials

Table 12. Si4712/13 Test Circuit Bill of Materials

| Component(s) | Value/Description Supplier(s)                       |  |

|--------------|-----------------------------------------------------|--|

| C1           | Supply bypass capacitor, 22 nF, 20%, Z5U/X7R Murata |  |

| C2, C3       | AC Coupling Capacitor, 0.47 μF Murata               |  |

| C4           | 2 pF, ±.05 pF, 06035JZR0AB AVX                      |  |

| L1           | 120 nH inductor, Qmin = 30 Murata                   |  |

| R1           | 49.9 Ω, 5% Murata                                   |  |

| U1           | Si4712/13 FM Radio Transmitter Silicon Laboratories |  |

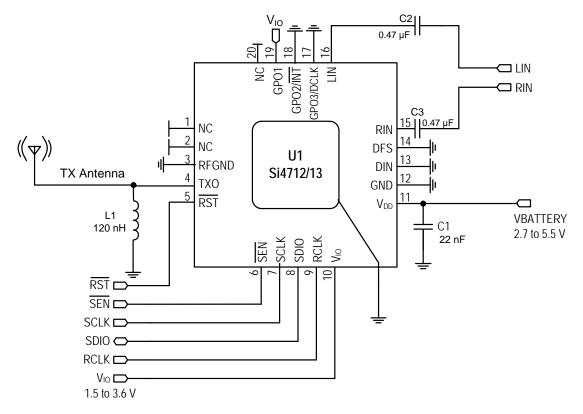

# 3. Typical Application Schematics

# 3.1. Analog Audio Inputs

#### Notes:

- 1. Si4712/13 is shown configured in I<sup>2</sup>C compatible bus mode.

- 2. GPO2/INT can be configured for interrupts with the powerup command.

- 3. To ensure proper operation and FM transmitter performance, follow the guidelines in "AN383: 3 mm x 3 mm QFN Universal Layout Guide." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- 4. LIN, RIN line inputs must be ac-coupled.

Figure 10. Analog Audio Inputs (LIN, RIN)

# 3.2. Digital Audio Inputs

#### Notes:

- 1. Si4712/13 is shown configured in I<sup>2</sup>C compatible bus mode.

- 2. GPO2/INT can be configured for interrupts with the powerup command.

- 3. To ensure proper operation and FM transmitter performance, follow the guidelines in "AN383: Si47xx 3 mm x 3 mm QFN Universal Layout Guide." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

Figure 11. Digital Audio Inputs (DIN, DFS, DCLK)

# 3.3. Typical Application Schematic Bill of Materials

Table 13. Si4712/13 Bill of Materials

| Component(s) | Value/Description                                  | Supplier(s) |

|--------------|----------------------------------------------------|-------------|

| C1           | Supply bypass capacitor, 22 nF, 20%, Z5U/X7R       | Murata      |

| C2, C3       | AC Coupling Capacitor, 0.47 μF Murata              |             |

| L1           | 120 nH inductor, Qmin = 30 Murata                  |             |

| R1, R2       | 2 kΩ Resistor Any                                  |             |

| R3           | 600 Ω Resistor Any                                 |             |

| U1           | Si4712/13 FM Radio Transmitter Silicon Laboratorie |             |

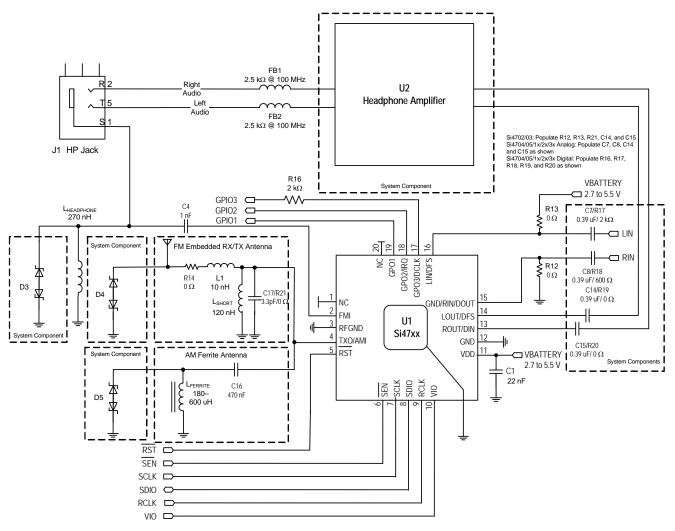

# 4. Universal AM/FM RX/FM TX Application Schematic

Figure 12 shows an application schematic that supports the Si47xx family of 3 mm x 3 mm QFN products, including the Si4702/3/4/5 FM receivers, Si471x FM transmitters, Si472x FM transceivers, and Si473x AM/FM receivers.

Figure 12. Universal AM/FM RX/FM TX Application Schematic

Following the schematic and layout recommendations detailed in "AN383: Universal Antenna Selection and Layout Guidelines" will result in optimal performance with the minimal application schematic shown in Figure 12. "Universal AM/FM RX/FM TX Application Schematic". System components are those that are likely to be present for any tuner or transmitter design.

## 4.1. Universal AM/FM RX/FM TX Bill of Materials

The bill of materials for the expanded application schematic shown in Figure 12 is provided in Table 14. Refer to the individual device layout guides and antenna interface guides for a discussion of the purpose of each component.

Table 14. Universal AM/FM RX/FM TX Bill of Materials

| Designator                 | Description                                                                    | Note                                 |

|----------------------------|--------------------------------------------------------------------------------|--------------------------------------|

| C1                         | Supply bypass capacitor, 22 nF, 10%, Z5U/X7R, 0402                             |                                      |

| U1                         | Silicon Laboratories Si47xx, 3 mm x 3 mm, 20 pin, QFN                          |                                      |

| R12, R13, R19,<br>R20, R21 | 0 $\Omega$ jumper, 0402                                                        | R12, R13, and R21 for Si4702/03 Only |

| C16                        | AM antenna ac coupling capacitor, 470 nF, 20%, Z5U/X7R                         | AM Ferrite Antenna                   |

| LFERRITE                   | AM Ferrite loop stick, 180–600 μH                                              | AM Ferrite Antenna                   |

| FB1,FB2                    | Ferrite bead, 2.5 kΩ @ 100 MHZ, 0603, Murata BLM18BD252SN1D                    | Headphone Antenna                    |

| LHEADPHONE                 | Headphone antenna matching inductor, 270 nH, 0603, Q>15, Murata LQW18ANR27J00D | Headphone Antenna                    |

| LSHORT                     | Embedded antenna matching inductor, 120 nH, 0603, Q>30, Murata LQW18ANR12J00D  | Embedded Antenna                     |

| R14                        | Embedded antenna jumper, 2.2 $\Omega$ , 0402                                   | Optional                             |

| C2                         | Supply bypass capacitor, 22 nF, 10%, Z5U/X7R, 0402                             | Optional                             |

| C3                         | Supply bypass capacitor, 100 nF, 10%, Z5U/X7R, 0402                            | Optional                             |

| C5, C6                     | Headphone amp output shunt capacitor, 100 pF, 10%, Z5U/X7R, 0402               | Optional                             |

| R7-R11                     | Current limiting resistor, 20 Ω–2 kΩ, 0402                                     | Optional                             |

| C12, C13                   | Crystal load capacitor, 22 pF, 5%, COG                                         | Optional                             |

| X1                         | Crystal, Epson FC-135                                                          | Optional                             |

| C7, C8                     | Si47xx input ac coupling capacitor, 0.39 μF, X7R/X5R, 0402                     | System Component                     |

| D1-D5                      | ESD Diode, SOT23-3, California Micro Devices CM1214-01ST                       | System Component                     |

| C11                        | Supply bypass capacitor, 100 nF, 10%, Z5U/X7R, 0402                            | Headphone Amplifier                  |

| C4                         | Headphone antenna ac coupling capacitor, 1 nF, 10%, Z5U/X7R, 0402              | Headphone Antenna                    |

| C9, C10                    | Headphone amp output ac coupling capacitor, 125 uF, X7R, 0805                  | Headphone Amplifier                  |

| C14, C15                   | Headphone amp input ac coupling capacitor, 0.39 μF, X7R/X5R, 0402              | Headphone Amplifier                  |

| R1,R2,R3,R4                | Headphone amp feedback/gain resistor, 20 kΩ, 0402                              | Headphone Amplifier                  |

| R5, R6                     | Headphone amp bleed resistor, 100 k $\Omega$ , 0402                            | Headphone Amplifier                  |

| U2                         | Headphone amplifier, National Semiconductor, LM4910MA                          | Headphone Amplifier                  |

| R16, R17                   | Current limiting resistor, 2 k $\Omega$ , 0402                                 | System Component                     |

| R18                        | Current limiting resistor, 600 $\Omega$ , 0402                                 | System Component                     |

| L1                         | VCO filter inductor, 10 nH, 0603, Q>30, Murata, LQW18ANR01J00D                 | Optional                             |

| C17                        | VCO filter capacitor, 3.3 pF, 0402, COG, Venkel, C0402COG2503R3JN              | Optional                             |

# 5. Functional Description

### 5.1. Overview

Figure 13. Functional Block Diagram

The Si4712/13 is the first 100% CMOS FM radio transmitter with integrated receive functionality to measure received signal strength. The device leverages Silicon Labs' highly successful and proven Si4700/01 FM receiver patent family and offers unmatched integration and performance, allowing FM transmit to be added to any portable device with a single chip. The Si4712/13 offers industry-leading size, performance, low power consumption, flexibility, and ease of use.

The Si4712/13's digital integration reduces the required external components of traditional offerings, resulting in a solution requiring only an external inductor and bypass capacitor, and PCB space of approximately 15 mm<sup>2</sup>. This increases the device reliability and simplifies the design and manufacturing for companies adopting this technology.

The Si4712/13's integrated receive power scan function shares the same antenna as the transmitter allowing for a compact printed circuit board design. The device operates in half duplex mode, meaning the transmitter and receiver do not operate at the same time.

The Si4712/13 performs FM modulation in the digital domain to achieve high fidelity, optimal performance versus power consumption, and flexibility of design. The

onboard DSP provides modulation adjustment and audio dynamic range control for optimum sound quality.

The Si4713 supports the European Radio Data System (RDS) and the US Radio Broadcast Data System (RBDS) including all the symbol encoding, block synchronization, and error correction functions. Using this feature, the Si4713 enables data such as artist name and song title to be transmitted to an RDS/RBDS receiver.

The transmit output (TXO) connects directly to the transmit antenna with only one external inductor to provide harmonic filtering. The output is programmable over a 10 dB voltage range in 1 dB steps. The TXO output pin can also be configured for loop antenna support. Users are responsible for complying with local regulations on RF transmission (FCC, ETSI, ARIB, etc.).

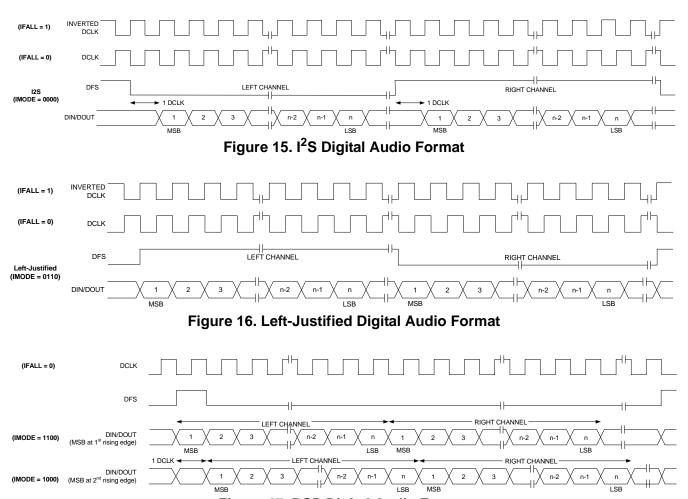

The digital audio interface operates in slave mode and supports a variety of MSB-first audio data formats including I<sup>2</sup>S and left-justified modes. The interface has three pins: digital data input (DIN), digital frame synchronization input (DFS), and a digital bit synchronization input clock (DCLK). The Si4712/13 supports a number of industry-standard sampling rates

including 32, 40, 44.1, and 48 kHz. The digital audio interface enables low-power operation by eliminating the need for redundant DACs and ADCs on the audio baseband processor.

The Si4712/13 includes a low-noise stereo line input (LIN/RIN) with programmable attenuation. To ensure optimal audio performance, the Si4712/13 has a transmit line input property that allows the user to specify the peak amplitude of the analog input required to reach maximum deviation level. The deviation levels of the audio, pilot, and RDS/RBDS signals can be independently programmed to customize FM transmitter designs. The Si4712/13 has a programmable low audio level and high audio level indicators that allows the user to selectively enable and disable the carrier based on the presence of audio content. In addition, the device provides an overmodulation indicator to allow the user to dynamically set the maximum deviation level. The Si4712/13 has a programmable audio dynamic range control that can be used to reduce the dynamic range of the audio input signal and increase the volume at the receiver. These features can dramatically improve the end user's listening experience.

The Si4712/13 is reset by applying a logic low on the RST pin. This causes all register values to be reset to their default values. The digital input/output interface supply ( $V_{\rm IO}$ ) provides voltage to the RST, SEN, SDIO, RCLK, DIN, DFS, and DCLK pins and can be connected to the audio baseband processor's supply voltage to save power and remove the need for voltage level translators. RCLK is not required for register operation.

The Si4712/13 reference clock is programmable, supporting many RCLK inputs as shown in Table 9.

The S4712/13 are part of a family of broadcast audio solutions offered in standard, 3 x 3 mm 20-pin QFN packages. All solutions are layout compatible, allowing a single PCB to accommodate various feature offerings. The Si4712/13 includes line inputs to the on-chip analog-to-digital converters (ADC), a programmable reference clock input, and a configurable digital audio interface. The chip supports I<sup>2</sup>C-compliant 2-wire, 8-bit SPI, and a 3-wire control interface.

#### 5.2. FM Transmitter

The transmitter (TX) integrates a stereo audio ADC to convert analog audio signals to high fidelity digital signals. Alternatively, digital audio signals can be applied to the Si4712/13 directly to reduce power consumption by eliminating the need to convert audio baseband signals to analog and back again to digital. Digital signal processing is used to perform the stereo MPX encoding and FM modulation to a low digital IF. Transmit baseband filters suppress out-of-channel noise and images from the digital low-IF signal. A quadrature single-sideband mixer up-converts the digital IF signal to RF, and internal RF filters suppress noise and harmonics to support the harmonic emission requirements of cellular phones, GPS, WLAN, and other wireless standards.

The TXO output has over 10 dB of output level control, programmable in approximately 1 dB steps. This large output range enables a variety of antennas to be used for transmit, such as a monopole stub antenna or a loop antenna. The 1 dB step size provides fine adjustment of the output voltage.

The TXO output requires only one external 120 nH inductor. The inductor is used to resonate the antenna and is automatically calibrated within the integrated circuit to provide the optimum output level and frequency response for supported transmit frequencies. Users are responsible for adjusting their system's radiated power levels to comply with local regulations on RF transmission (FCC, ETSI, ARIB, etc.).

### 5.3. Receive Power Scan

The Si4712/13 is the industry's first FM transmitter with integrated receive functionality to measure received signal strength. This has been designed to specifically handle various antenna lengths including integrated PCB antennas, wire antennas, and loop antennas, allowing it to share the same antenna as the transmitter. The receive function reuses the on-chip varactor from the transmitter to optimize the receive signal power applied to the front-end amplifier. Auto-calibration of the varactor occurs with each tune command for consistent performance across the FM band.

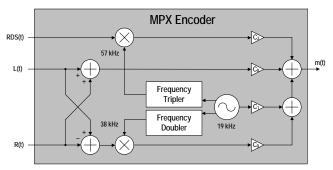

#### 5.3.1. Stereo Encoder

Figure 14 shows an example modulation level breakdown for the various components of a typical MPX signal.

The total modulation level for the MPX signal shown in Figure 14, assuming no correlation, is equal to the arithmetic sum of each of the subchannel levels resulting in 102.67 percent modulation or a peak frequency deviation of 77.0025 kHz (an instantaneous frequency deviation of 75 kHz corresponds to 100 percent modulation). Frequency deviation is related to the amplitude of the MPX signal by a gain constant,  $K_{VCO}$ , as given by the following equation:

$$\Delta f = K_{VCO}A_m$$

where  $\Delta f$  is the frequency deviation;  $K_{VCO}$  is the voltage-to-frequency gain constant, and  $A_m$  is the amplitude of the MPX message signal. For a fixed  $K_{VCO}$ , the amplitude of all the subchannel signals within the MPX message signal must be scaled to give the appropriate total frequency deviation.

Figure 14. MPX Encoder

Figure 14 shows a conceptual block diagram of an MPX encoder used to generate the MPX signal. L(t) and R(t) denote the time domain waveforms from the left and right audio channels, and RDS(t) denotes the time domain waveform of the RDS/RBDS signal.

The MPX message signal can be expressed as follows:

$m(t) = C_0[L(t) + R(t)] + C_1 \cos(2\pi 19 \text{ kHz})$

- +  $C_0[L(t) R(t)] \cos(2\pi 38 \text{ kHz})$

- +  $C_2RDS(t) \cos(2\pi 57 \text{ kHz})$

where C<sub>0</sub>, C<sub>1</sub>, and C<sub>2</sub> are gains used to scale the amplitudes of the audio signals (L(t)  $\pm$  R(t)), the 19 kHz pilot tone, and the RDS subcarrier respectively, to generate the appropriate modulation level. To achieve Figure 14 the modulation levels of  $K_{VCO} = 75 \text{ kHz/V}$ ,  $C_0$  would be set to 0.45;  $C_1$  would be set to 0.1, and C2 would be set to 0.0267 giving a peak audio frequency deviation of 0.9 x 75 kHz = 67.5 kHz, a peak pilot frequency deviation Ωf 0.1 x 75 kHz = 7.5 kHz, and a peak RDS frequency deviation of 0.0267 x 75 kHz = 2.0025 kHz for a total peak frequency deviation of 77.0025 kHz.

In the Si4712/13, the peak audio, pilot, and RDS frequency deviations can be programmed directly with the Transmit Audio, Pilot, and RDS Deviation commands with an accuracy of 10 Hz. For the example in Figure 14, the Transmit Audio Deviation is programmed with the value 6750, the Transmit Pilot Deviation with 750, and the Transmit RDS Deviation with 200, generating peak audio frequency deviations of 67.5 kHz, peak pilot deviations of 7.5 kHz, and peak RDS deviations of 2.0 kHz for a total peak frequency deviation of 77 kHz. The total peak transmit frequency deviation of the Si4712/13 can range from 0 to 100 kHz and is equal to the arithmetic sum of the Transmit Audio, Pilot, and RDS deviations. Users must comply with local regulations on radio frequency transmissions.

Each of the individual deviations (transmit audio, pilot, and RDS) can be independently programmed; however, the total peak frequency deviation cannot exceed 100 kHz.

The Si4712/13 provides an overmodulation indicator to allow the user to dynamically set the maximum deviation level. If the instantaneous frequency exceeds the deviation level specified by the TX\_AUDIO\_DEVIATION property, the SQINT interrupt bit (and optional interrupt) will be set.

CHICAN LARG

## 5.4. Digital Audio Interface

The digital audio interface operates in slave mode and supports 3 different audio data formats:

- 1. I<sup>2</sup>S

- 2. Left-Justified

- 3. DSP Mode

#### 5.4.1. Audio Data Formats

In I<sup>2</sup>S mode, the MSB is captured on the second rising edge of DCLK following each DFS transition. The remaining bits of the word are sent in order, down to the LSB. The Left Channel is transferred first when the DFS is low, and the Right Channel is transferred when the DFS is high.

In Left-Justified mode, the MSB is captured on the first rising edge of DCLK following each DFS transition. The remaining bits of the word are sent in order, down to the LSB. The Left Channel is transferred first when the DFS is high, and the Right Channel is transferred when the DFS is low.

In DSP mode, the DFS becomes a pulse with a width of 1 DCLK period. The Left Channel is transferred first, followed right away by the Right Channel. There are two options in transferring the digital audio data in DSP mode: the MSB of the left channel can be transferred on the first rising edge of DCLK following the DFS pulse or on the second rising edge.

In all audio formats, depending on the word size, DCLK frequency and sample rates, there may be unused DCLK cycles after the LSB of each word before the next DFS transition and MSB of the next word.

The number of audio bits can be configured for 8, 16, 20, or 24 bits.

#### 5.4.2. Audio Sample Rates

The device supports a number of industry-standard sampling rates including 32, 40, 44.1, and 48 kHz. The digital audio interface enables low-power operation by eliminating the need for redundant DACs and ADCs on the audio baseband processor. The sampling rate is selected using the DIGITAL\_INPUT\_SAMPLE\_RATE property.

The device supports DCLK frequencies above 1 MHz. After powerup the DIGITAL INPUT SAMPLE RATE property defaults to 0 (disabled). After DCLK is supplied, the DIGITAL INPUT SAMPLE RATE property should be set to the desired audio sample rate 48 kHz. such as 32, 40, 44.1, or DIGITAL INPUT SAMPLE RATE property must be set to 0 before DCLK is removed or the DCLK frequency drops below 1 MHz. A device reset is required if this requirement is not followed.

Figure 17. DSP Digital Audio Format

## 5.5. Line Input

The Si4712/13 provides left and right channel line inputs (LIN and RIN). The inputs are high-impedance and low-capacitance, suited to receiving line level signals from external audio baseband processors. Both line inputs are low-noise inputs with programmable attenuation. Passive and active anti-aliasing filters are incorporated to prevent high frequencies from aliasing into the audio band and degrading performance.

To ensure optimal audio performance, the Si4712/13 has a TX\_LINE\_INPUT\_LEVEL property that allows the user to specify the peak amplitude of the analog input (LILEVEL[9:0]) required to reach the maximum deviation level programmed in the audio deviation property, TX\_AUDIO\_DEVIATION. A corresponding line input attenuation code, LIATTEN[1:0], is also selected by the expected peak amplitude level. Table 15 shows the line attenuation codes.

**Table 15. Line Attenuation Codes**

| LIATTEN[1:0] | Peak Input<br>Voltage [mV] | RIN/LIN Input<br>Resistance [kΩ] |

|--------------|----------------------------|----------------------------------|

| 00           | 190                        | 396                              |

| 01           | 301                        | 100                              |

| 10           | 416                        | 74                               |

| 11           | 636                        | 60                               |

The line attenuation code is chosen by picking the lowest Peak Input Voltage in Table 15 that is just above the expected peak input voltage coming from the audio baseband processor. For example, if the expected peak input voltage from the audio baseband processor is 400 mV, the user chooses LIATTEN[1:0] = 10 since the Peak Input Voltage of 416 mV associated with LIATTEN[1:0] = 10 is just greater than the expected peak input voltage of 400 mV. The user also enters 400 mV into the LILEVEL[9:0] to associate this input level to the maximum frequency deviation level programmed into the audio deviation property. Note that selecting a particular value of LIATTEN[1:0] changes the input resistance of the LIN and RIN pins. This feature is used for cases where the expected peak input level exceeds the maximum input level of the LIN and RIN pins.

The maximum analog input level is 636 mVpK. If the analog input level from the audio baseband processor exceeds this voltage, series resistors must be inserted in front of the LIN and RIN pins to attenuate the voltage such that it is within the allowable operating range. For example, if the audio baseband's expected peak amplitude is 900 mV and the V<sub>IO</sub> supply voltage is 1.8 V, the designer can use 30 k $\Omega$  series resistors in front of the LIN and RIN pins and select LIATTEN[1:0] = 11. The resulting expected peak input voltage at the LIN/RIN pins is 600 mV, since this is just a voltage divider between the LIN/RIN input resistance (see Table 15,  $60 \text{ k}\Omega$  for this example) and the external resistor. Note that the Peak Input Voltage corresponding to the chosen LIATTEN[1:0] code still needs to satisfy the condition of being just greater than the attenuated voltage. In this example, a line attenuation code of LIATTEN[1:0] = 11 has a Peak Input Voltage of 636 mV, which is just greater than the expected peak attenuated voltage of 600 mV. Also, the expected peak attenuated voltage is entered into the LILEVEL[9:0] parameter. Again, in this example, 600 mV is entered into LILVEVEL[9:0]. This example shows one possible solution, but many other solutions exist. The optimal solution is to apply the largest possible voltage to the LIN and RIN pins for signal-to-noise considerations; however, practical resistor values may limit the choices.

Note that the TX\_LINE\_INPUT\_LEVEL parameter will affect the high-pass filter characteristics of the accoupling capacitors and the resistance of the audio inputs.

The Si4712/13 has a programmable low audio level and high audio level indicators that allows the user to selectively enable and disable the carrier based on the presence of audio content. The TX\_ASQ\_LEVEL\_LOW and TX\_ASQ\_LEVEL\_HIGH parameters set the low level and high level thresholds in dBFS, respectively. The time required for the audio level to be below the low threshold is set with the TX\_ASQ\_DURATION\_LOW parameter, and similarly, the time required for the audio level to be above the high threshold is set with the TX\_ASQ\_DURATION\_HIGH parameter.

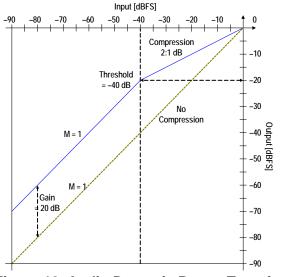

## 5.6. Audio Dynamic Range Control

The Si4712/13 includes digital audio dynamic range control with programmable gain, threshold, attack rate, and release rate. The total dynamic range reduction is set by the gain value and the audio output compression above the threshold is equal to Threshold/(Gain + Threshold) in dB. The gain specified cannot be larger than the absolute value of the threshold. This feature can also be disabled if audio compression is not desired.

The audio dynamic range control can be used to reduce the dynamic range of the audio signal, which improves the listening experience on the FM receiver. Audio dynamic range reduction increases the transmit volume by decreasing the peak amplitudes of audio signals and increasing the root mean square content of the audio signal. In other words, it amplifies signals below a threshold by a fixed gain and compresses audio signals above threshold by the ratio а Threshold/(Gain + Threshold). Figure 18 shows example transfer function of an audio dynamic range controller with the threshold set at -40 dBFS and a Gain = 20 dB relative to an uncompressed transfer function.

Figure 18. Audio Dynamic Range Transfer Function

For input signals below the threshold of –40 dBFS, the output signal is amplified or gained up by 20 dB relative to an uncompressed signal. Audio inputs above the threshold are compressed by a 2 to 1 dB ratio, meaning that every 2 dB increase in audio input level above the threshold results in an audio output increase of 1 dB. In this example, the input dynamic range of 90 dB is reduced to an output dynamic range of 70 dB.

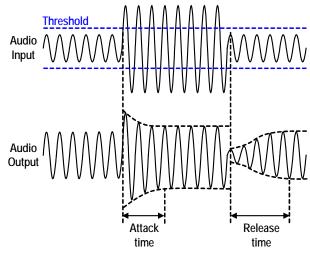

Figure 19 shows the time domain characteristics of the audio dynamic range controller. The attack rate sets the speed with which the audio dynamic range controller responds to changes in the input level, and the release rate sets the speed with which the audio dynamic range controller returns to no compression once the audio input level drops below the threshold.

Figure 19. Time Domain Characteristics of the Audio Dynamic Range Controller

#### 5.7. Audio Limiter

The 4712/13 also includes a digital audio limiter. The audio limiter prevents over-modulation of the FM transmit output by dynamically attenuating peaks in the audio input signal that exceed a programmable threshold. The limiter threshold is set to the programmed audio deviation + ten percent. The threshold ensures that the output signal audio deviation does not exceed the programmed levels, avoiding audible artifacts or distortion in the target FM receiver, and complying with FCC or ETSI regulatory standards.

The limiter performs as a peak detector with an attack rate set to one audio sample, resulting in an almost immediate attenuation of the input peak. The recover rate is programmable to the customer's preference, and is set by default to 5 ms. This is the recommended setting to avoid audible pumping or popping. Refer to "AN332: Universal Programming Guide."

## 5.8. Pre-emphasis and De-emphasis

Pre-emphasis and de-emphasis is a technique used by FM broadcasters to improve the signal-to-noise ratio of FM receivers by reducing the effects of high-frequency interference and noise. When the FM signal is transmitted, a pre-emphasis filter is applied to accentuate the high audio frequencies. All FM receivers incorporate a de-emphasis filter that attenuates high frequencies to restore a flat frequency response. Two time constants are used in various regions. The pre-emphasis time constant is programmable to 50 or 75 µs and is set by using the TX PREEMPHASIS property.

# 5.9. RDS/RBDS Processor (Si4713 Only)

The Si4713 implements an RDS/RBDS\* processor for symbol encoding, block synchronization, and error correction. Digital data can be transmitted with the Si4713 RDS/RBDS encoding feature.

RDS transmission is supported with three different modes. The first mode is the simplest mode and requires no additional user support except for preloading the desired RDS PI and PTY codes and up to 12 8-byte PS character strings. The Si4713 will transmit the PI code and rotate through the transmission of the PS character strings with no further control required from outside the device. The second mode allows for more complicated transmissions. The PI and PTY codes are written to the device as in mode 1. The remaining blocks (B, C, and D) are written to a 252 byte buffer. This buffer can hold 42 sets of BCD blocks. The Si4713 creates RDS groups by creating block A from the PI code, concatenating blocks BCD from the buffer, and rotating through the buffer. The BCD buffer is circular; so, the pattern is repeated until the buffer is changed. Finally, the third mode allows the outside controller to burst data into the BCD buffer, which emulates a FIFO. The data does not repeat, but, when the buffer is nearly empty, the Si4713 signals the outside device to initiate another data burst. This mode permits the outside device to use any RDS functionality (including open data applications) that it wants.

\*Note: RDS/RBDS is referred to only as RDS throughout the remainder of this document.

#### **5.10.** Tuning

The frequency synthesizer uses Silicon Laboratories' proven technology including a completely integrated VCO. The frequency synthesizer generates the quadrature local oscillator signal used to upconvert the low intermediate frequency to RF. The VCO frequency is locked to the reference clock and adjusted with an automatic frequency control (AFC) servo loop during transmission.

The tuning frequency can be directly programmed with commands. For example, to tune to 98.1 MHz, the user writes the TX\_TUNE\_FREQ command with an argument = 9810.

The Si4712/13 supports channel spacing of 50, 100, or 200 kHz.

#### 5.11. Reference Clock

The Si4712/13 reference clock is programmable, supporting RCLK frequencies from 31.130 kHz to 40 MHz. The RCLK frequency divided by an integer number (the prescaler value) must fall in the range of 31,130 to 34,406 Hz. Therefore, the range of RCLK frequencies is not continuous below frequencies of 311.3 kHz. The default RCLK frequency is 32.768 kHz. Please refer to "AN332: Universal Programming Guide" for using other RCLK frequencies.

#### 5.12. Control Interface

A serial port slave interface is provided; this allows an external controller to send commands to the Si4712/13 and receive responses from the device. The serial port can operate in three bus modes: 2-wire mode, SPI mode, or 3-wire mode. The Si4712/13 selects the bus mode by sampling the state of the GPO1 and GPO2/INT pins on the rising edge of RST. The GPO1 pin includes an internal pull-up resistor that is connected while RST is low, and the GPO2/INT pin includes an internal pull-down resistor that is connected while RST is low. Therefore, it is only necessary for the user to actively drive pins that differ from these states.

Table 16. Bus Mode Select on Rising Edge of RST

| Bus Mode | GPO1           | GPO2/INT       |

|----------|----------------|----------------|

| 2-Wire   | 1              | 0              |

| SPI      | 1              | 1 (must drive) |

| 3-Wire   | 0 (must drive) | 0              |

After the rising edge of  $\overline{RST}$ , the pins, GPO1 and GPO2/INT, are used as general-purpose output (O) pins as described in Section "5.13. GPO Outputs". In any bus mode, commands may only be sent after  $V_{IO}$  and  $V_{DD}$  supplies are applied.

#### 5.12.1. 2-Wire Control Interface Mode

When selecting 2-wire mode, the user  $\underline{\text{must}}$  ensure that SCLK is high during the rising edge of  $\overline{\text{RST}}$ , and stays high until after the first start condition. Also, a start condition must not occur within 300 ns before the rising edge of  $\overline{\text{RST}}$ .

2-wire bus mode uses only the SCLK and SDIO pins for signaling. A transaction begins with the START condition, which occurs when SDIO falls while SCLK is high. Next, the user drives an 8-bit control word serially on SDIO, which is captured by the device on rising edges of SCLK. The control word consists of a seven bit device address followed by a read/write bit (read = 1, write = 0). The Si4712/13 acknowledges the control word by driving SDIO low on the next falling edge of SCLK.

Although the Si4712/13 responds to only a single device address, this address can be changed with the  $\overline{SEN}$  pin (note that the  $\overline{SEN}$  pin is not used for signaling in 2-wire mode). When  $\overline{SEN} = 0$ , the seven-bit device address is 0010001. When  $\overline{SEN} = 1$ , the address is 1100011.

For write operations, the user then sends an eight bit data byte on SDIO, which is captured by the device on rising edges of SCLK. The Si4712/13 acknowledges each data byte by driving SDIO low for one cycle, on the next falling edge of SCLK. The user may write up to eight data bytes in a single two-wire transaction. The first byte is a command, and the next seven bytes are arguments.

For read operations, after the Si4712/13 has acknowledged the control byte, it drives an eight-bit data byte on SDIO, changing the state of SDIO on the falling edge of SCLK. The user acknowledges each data byte by driving SDIO low for one cycle, on the next falling edge of SCLK. If a data byte is not acknowledged, the transaction ends. The user may read up to 16 data bytes in a single two-wire

transaction. These bytes contain the response data from the Si4712/13.

A 2-wire transaction ends with the STOP condition, which occurs when SDIO rises while SCLK is high.

For details on timing specifications and diagrams, refer to Table 5, "2-Wire Control Interface Characteristics<sup>1,2,3</sup>," on page 7, Figure 2, "2-Wire Control Interface Read and Write Timing Parameters," on page 8, and Figure 3, "2-Wire Control Interface Read and Write Timing Diagram," on page 8.

#### 5.12.2. SPI Control Interface Mode

When selecting SPI mode, the user must ensure that a rising edge of SCLK does not occur within 300 ns before the rising edge of RST.

SPI bus mode uses the SCLK, SDIO, and SEN pins for read/write operations. For reads, the user can choose to receive data from the device on either SDIO or GPO1. A transaction begins when the user drives SEN low. The user then pulses SCLK eight times while driving an 8-bit control byte (MSB first) serially on SDIO. The device captures the data on rising edges of SCLK. The control byte must have one of these values:

0x48 = write eight command/argument bytes (user drives write data on SDIO)

0x80 = read status byte (device drives read data on SDIO)

0xA0 = read status byte (device drives read data on GPO1)

0xC0 = read 16 response bytes (device drives read data on SDIO)

0xE0 = read 16 response bytes (device drives read data on GPO1)

When writing a command, after the control byte has been written, the user must drive exactly eight data bytes (a command byte and seven argument bytes) on SDIO. The data will be captured by the device on the rising edges of SCLK. After all eight data bytes have been written, the user raises SEN after the last falling edge of SCLK to end the transaction.

In any bus mode, before sending a command or reading a response, the user must first read the status byte to ensure that the device is ready (CTS bit is high). In SPI mode, this is done by sending control byte 0x80 or 0xA0, followed by reading a single byte on SDIO or GPO1. The Si4712/13 changes the state of SDIO or GPO1 after the falling edges of SCLK. Data should be captured by the user on the rising edges of SCLK. After the status byte has been read, the user raises SEN after the last falling edge of SCLK to end the transaction.

When reading a response, the user must read exactly 16 data bytes after sending the control byte. It is

CHICAN LARG

recommended that the user keep SEN low until all bytes have transferred. However, it will not disrupt the protocol if SEN temporarily goes high at any time, as long as the user does not change the state of SCLK while SEN is high. After 16 bytes have been read, the user raises SEN after the last falling edge of SCLK to end the transaction.

At the end of any SPI transaction, the user must drive SEN high after the final falling edge of SCLK. At any time during a transaction, if SEN is sampled high by the device on a rising edge of SCLK, the transaction will be aborted. When SEN is high, SCLK may toggle without affecting the device.

For details on timing specifications and diagrams, refer to Figure 6 and Figure 7 on page 10.

#### 5.12.3. 3-Wire Control Interface Mode

When selecting 3-wire mode, the user must ensure that a rising edge of SCLK <u>does</u> not occur within 300 ns before the rising edge of RST.

3-wire bus mode uses the SCLK, SDIO and SEN pins. A transaction begins when the system controller drives  $\overline{\text{SEN}}$  low. Next, the system controller drives a 9-bit control word on SDIO, which is captured by the device on rising edges of SCLK. The control word is comprised of a three bit chip address (A7:A5 = 101b), a read/write bit (write = 0, read = 1), the chip address (A4 = 0), and a four bit register address (A3:A0).

For write operations, the control word is followed by a 16-bit data word, which is captured by the device on rising edges of SCLK.

For read operations, the control word is followed by a delay of one-half SCLK cycle for bus turnaround. Next, the Si4712/13 drives the 16-bit read data word serially on SDIO, changing the state of SDIO on each rising edge of SCLK.

A transaction ends when the user sets SEN high, then pulses SCLK high and low one final <u>time</u>. SCLK may either stop or continue to toggle while SEN is high.

In 3-wire mode, commands are sent by first writing each argument to register(s) 0xA1-0xA3, then writing the command word to register 0xA0. A response is retrieved by reading registers 0xA8-0xAF.

For details on timing specifications and diagrams, refer to Table 6, "3-Wire Control Interface Characteristics," on page 9, Figure 4, "3-Wire Control Interface Write Timing Parameters," on page 9, and Figure 5, "3-Wire Control Interface Read Timing Parameters," on page 9.

### 5.13. GPO Outputs

The Si4712/13 provides three general-purpose output pins. The GPO pins can be configured to output a constant low, constant high, or high-Z. The GPO pins are multiplexed with the bus mode pins or DCLK depending on the application schematic of the transmitter. GPO2/INT can be configured to provide interrupts.

## 5.14. Reset, Powerup, and Powerdown

Setting the RST pin low will disable analog and digital circuitry, reset the registers to their default settings, and disable the bus. Setting the RST pin high will bring the device out of reset and place it in powerdown mode.

A powerdown mode is available to reduce power consumption when the part is idle. Putting the device in powerdown mode will disable analog and digital circuitry and keep the bus active. For more information concerning Reset, Powerup, Powerdown, and Initialization, refer to "AN332: Universal Programming Guide."

## **5.15. Programming with Commands**

To ease development time and offer maximum customization, the Si4712/13 provides a simple yet powerful software interface to program the transmitter. The device is programmed using commands, arguments, properties, and responses.

To perform an action, the user writes a command byte and associated arguments causing the chip to execute the given command. Commands control actions, such as powering up the device, shutting down the device, or tuning to a station. Arguments are specific to a given command and are used to modify the command. For example, after the TX\_TUNE\_FREQ command, arguments are required to set the tune frequency. A complete list of commands is available in Table 17, "Si471x Command Summary," on page 30.

Properties are a special command argument used to modify the default chip operation and are generally configured immediately after powerup. Examples of properties are TX\_PREEMPHASIS and GPO\_CONFIGURE. A complete list of properties is available in Table 18, "Si471x Property Summary," on page 31.

Responses provide the user information and are echoed after a command and associated arguments are issued. At a minimum, all commands provide a one-byte status update indicating interrupt and clear-to-send status information. For a detailed description of using the commands and properties of the Si4712/13, see "AN332: Universal Programming Guide."

# 6. Commands and Properties

**Table 17. Si471x Command Summary**

| Cmd  | Name            | Description                                                                                                     |

|------|-----------------|-----------------------------------------------------------------------------------------------------------------|

| 0x01 | POWER_UP        | Power up device and mode selection. Modes include FM transmit and analog/digital audio interface configuration. |

| 0x10 | GET_REV         | Returns revision information on the device.                                                                     |

| 0x11 | POWER_DOWN      | Power down device.                                                                                              |

| 0x12 | SET_PROPERTY    | Sets the value of a property.                                                                                   |

| 0x13 | GET_PROPERTY    | Retrieves a property's value.                                                                                   |

| 0x14 | GET_INT_STATUS  | Read interrupt status bits.                                                                                     |

| 0x15 | PATCH_ARGS      | Reserved command used for patch file downloads.                                                                 |

| 0x16 | PATCH_DATA      | Reserved command used for patch file downloads.                                                                 |

| 0x30 | TX_TUNE_FREQ    | Tunes to given transmit frequency.                                                                              |

| 0x31 | TX_TUNE_POWER   | Sets the output power level and tunes the antenna capacitor                                                     |

| 0x32 | TX_TUNE_MEASURE | Measure the received noise level at the specified frequency.                                                    |

| 0x33 | TX_TUNE_STATUS  | Queries the status of a previously sent TX Tune Freq, TX Tune Power, or TX Tune Measure command.                |

| 0x34 | TX_ASQ_STATUS   | Queries the TX status and input audio signal metrics.                                                           |

| 0x35 | TX_RDS_BUFF     | <b>Si4713 Only</b> . Queries the status of the RDS Group Buffer and loads new data into buffer.                 |

| 0x36 | TX_RDS_PS       | Si4713 Only. Set up default PS strings.                                                                         |

| 0x80 | GPO_CTL         | Configures GPO3 as output or Hi-Z.                                                                              |