## 1.5MHz, 600mA Synchronous Step-Down Regulator with Bypass Transistor

January 2003

#### **FEATURES**

- Dynamically Adjustable Output from 0.3V to 3.5V

- Very Low Quiescent Current: Only 20µA During Operation

- 600mA Output Current

- P-Channel MOSFET Bypass Transistor

- High Efficiency: Up to 96%

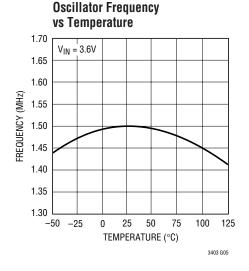

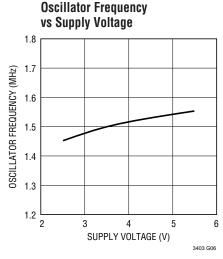

- 1.5MHz Constant Frequency Operation

- No Schottky Diode Required

- Low Dropout Operation: 100% Duty Cycle

- 2.5V to 5V Input Voltage Range

- Shutdown Mode Draws < 1µA Supply Current

- Current Mode Operation for Excellent Line and Load Transient Response

- Overtemperature Protected

- Available in 8-Lead 3mm × 3mm DFN Package

### **APPLICATIONS**

- WCDMA Cell Phone Power Amplifiers

- Wireless Modems

#### DESCRIPTION

The LTC®3403 is a high efficiency monolithic synchronous buck regulator optimized for WCDMA power amplifier applications. The output voltage can be dynamically programmed from 0.3V to 3.5V. At  $V_{OUT} > 3.6V$  an internal bypass P-channel MOSFET transistor connects  $V_{OUT}$  directly to  $V_{IN}$  eliminating power loss through the inductor. Selectable forced continuous mode enables fast  $V_{OUT}$  response to the controlling input.

Supply current is only  $20\mu A$  in Burst Mode® operation and drops to  $<\!1\mu A$  in shutdown. The 2.5V to 5V input voltage range makes the LTC3403 ideally suited for single Li-Ion battery-powered applications. 100% duty cycle provides low dropout operation, extending battery life in portable systems.

Switching frequency is internally set at 1.5MHz, allowing the use of small surface mount inductors and capacitors. The internal synchronous switch increases efficiency and eliminates the need for an external Schottky diode.

The LTC3403 is available in a low profile 8-lead 3mm  $\times$  3mm DFN package.

(T), LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode is a registered trademark of Linear Technology Corporation.

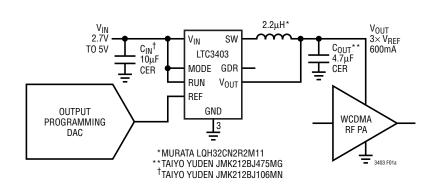

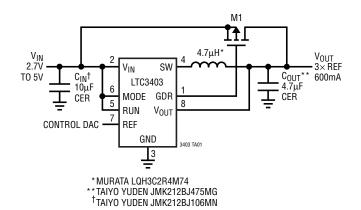

### TYPICAL APPLICATION

Figure 1a. WCDMA Transmitter Power Supply

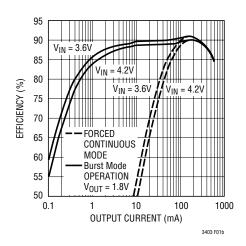

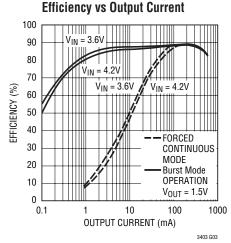

Figure 1b. Efficiency vs Output Current

3403i

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

### PACKAGE/ORDER INFORMATION

| TOP VIEW        |                                                                                      |                  | ORDER PART<br>NUMBER |

|-----------------|--------------------------------------------------------------------------------------|------------------|----------------------|

| GDR             | 1] [3                                                                                | V <sub>OUT</sub> | NOMBER               |

| V <sub>IN</sub> | 2]                                                                                   | REF              | LTC3403EDD           |

| GND             | 3 [6                                                                                 | MODE             |                      |

| SW              | DD PACKAGE                                                                           | RUN              | DD PART MARKING      |

|                 | DD PACKAGE<br>O (3mm × 3mm) PLA<br>$_{MAX} = 125^{\circ}\text{C},  \theta_{JA} = 43$ | LAAX             |                      |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

### **ELECTRICAL CHARACTERISTICS**

The ullet denotes specifications which apply over the full operating temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ .  $V_{IN} = 3.6V$  unless otherwise specified.

| SYMBOL               | PARAMETER                                                                                 | CONDITIONS                                                                                                                                                                                                     |   | MIN          | TYP              | MAX            | UNITS          |

|----------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|------------------|----------------|----------------|

| V <sub>OUT</sub>     | Regulated Output Voltage                                                                  | $V_{REF} = 1.1V$ , MODE = $V_{IN}$<br>$V_{REF} = 0.1V$ , MODE = $V_{IN}$                                                                                                                                       | • | 3.23<br>0.25 | 3.3<br>0.3       | 3.37<br>0.35   | V              |

| $\Delta V_{OUT}$     | Output Voltage Line Regulation                                                            | V <sub>IN</sub> = 2.5V to 5V                                                                                                                                                                                   | • |              | 0.1              | 0.4            | %/V            |

| I <sub>PK</sub>      | Peak Inductor Current                                                                     | $V_{IN} = 3V$ , $V_{REF} = 0.9V$                                                                                                                                                                               |   | 0.70         | 1                | 1.25           | А              |

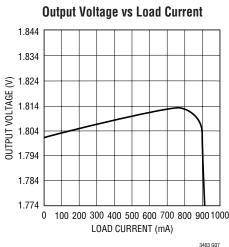

| V <sub>LOADREG</sub> | Output Voltage Load Regulation                                                            |                                                                                                                                                                                                                |   |              | 0.7              |                | %              |

| $V_{IN}$             | Input Voltage Range                                                                       |                                                                                                                                                                                                                | • | 2.5          |                  | 5              | V              |

| Is                   | Input DC Operating Current Burst Mode Operation Forced Continuous Mode Operation Shutdown | $\begin{aligned} &\text{MODE} = \text{OV, SW} = \text{Open} \\ &\text{MODE} = \text{V}_{\text{IN}}, \text{SW} = \text{Open} \\ &\text{V}_{\text{RUN}} = \text{OV, V}_{\text{IN}} = 5.5 \text{V} \end{aligned}$ |   |              | 20<br>1.5<br>0.1 | 35<br>2.5<br>1 | μΑ<br>mA<br>μΑ |

| f <sub>OSC</sub>     | Oscillator Frequency                                                                      | $\begin{aligned} V_{REF} &\geq 0.25V \\ V_{REF} &\leq 0.1V \end{aligned}$                                                                                                                                      | • | 1.2<br>550   | 1.5<br>700       | 1.8<br>850     | MHz<br>kHz     |

| V <sub>REF</sub>     | Bypass PFET Turn-Off Threshold                                                            | V <sub>REF</sub> = Y                                                                                                                                                                                           |   | 1.167        | 1.2              |                | V              |

|                      | Bypass PFET Turn-On Threshold                                                             | V <sub>REF</sub> = <u></u> √                                                                                                                                                                                   |   |              | 1.21             | 1.26           | V              |

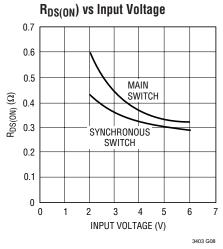

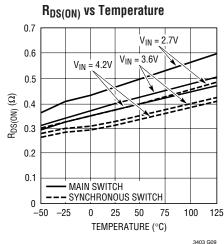

| R <sub>PFET</sub>    | R <sub>DS(ON)</sub> of P-Channel FET                                                      | I <sub>SW</sub> = 100mA, Wafer Level<br>I <sub>SW</sub> = 100mA, DD Package                                                                                                                                    |   |              | 0.3<br>0.4       | 0.4            | $\Omega$       |

| R <sub>NFET</sub>    | R <sub>DS(ON)</sub> of N-Channel FET                                                      | I <sub>SW</sub> = -100mA, Wafer Level<br>I <sub>SW</sub> = -100mA, DD Package                                                                                                                                  |   |              | 0.3<br>0.4       | 0.4            | $\Omega$       |

| R <sub>BYPASS</sub>  | R <sub>DS(ON)</sub> of Bypass P-Channel FET                                               | I <sub>OUT</sub> = 100mA, V <sub>IN</sub> = 3V, Wafer Level<br>I <sub>OUT</sub> = 100mA, V <sub>IN</sub> = 3V, DD Package                                                                                      |   |              | 0.15<br>0.20     | 0.18           | $\Omega$       |

| $I_{LSW}$            | SW Leakage                                                                                | $V_{RUN} = 0V$ , $V_{SW} = 0V$ or $5V$ , $V_{IN} = 5V$                                                                                                                                                         |   |              | ±0.01            | ±1             | μА             |

| I <sub>LBYP</sub>    | Bypass PFET Leakage                                                                       | V <sub>OUT</sub> = 0V, V <sub>IN</sub> = 5V, V <sub>REF</sub> = 0V                                                                                                                                             |   |              | ±0.01            | ±1             | μА             |

| $V_{RUN}$            | RUN Threshold                                                                             |                                                                                                                                                                                                                | • | 0.3          | 1                | 1.5            | V              |

| I <sub>RUN</sub>     | RUN Input Current                                                                         |                                                                                                                                                                                                                | • |              | ±0.01            | ±1             | μА             |

| V <sub>MODE</sub>    | MODE Threshold                                                                            |                                                                                                                                                                                                                | • | 0.3          | 1.5              | 2              | V              |

| I <sub>MODE</sub>    | MODE Input Current                                                                        |                                                                                                                                                                                                                | • |              | ±0.01            | ±1             | μΑ             |

| I <sub>REF</sub>     | REF Input Current                                                                         |                                                                                                                                                                                                                | • |              | ±0.01            | ±1             | μА             |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The LTC3403E is guaranteed to meet performance specifications from  $0^{\circ}$ C to  $70^{\circ}$ C. Specifications over the  $-40^{\circ}$ C to  $85^{\circ}$ C operating

temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

LTC3403:  $T_J = T_A + (P_D)(???^{\circ}C/W)$

3403i

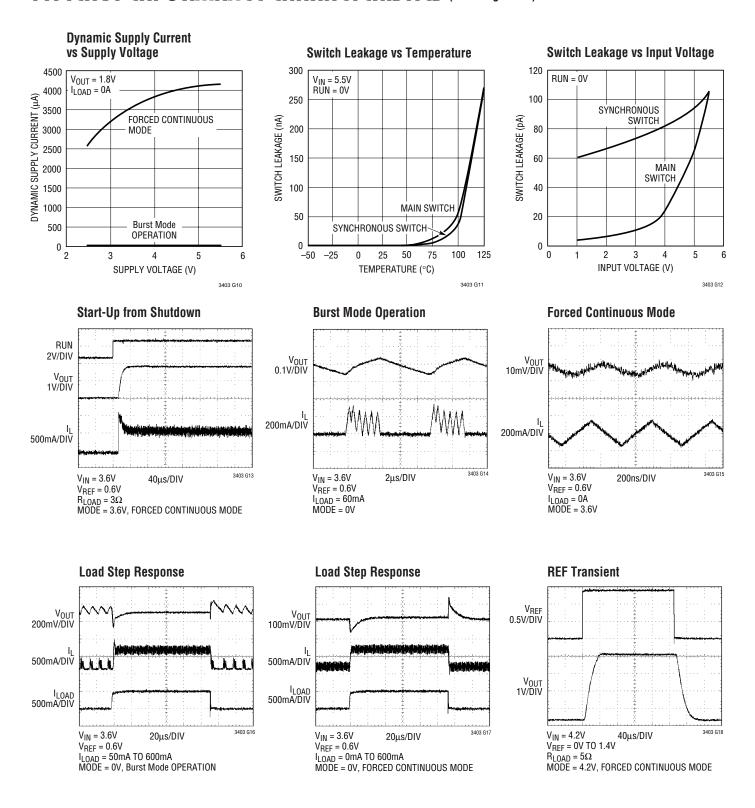

### TYPICAL PERFORMANCE CHARACTERISTICS (From Figure 1a)

#### 100 90 80 70 70 80 V<sub>IN</sub> = 3.6V V<sub>IN</sub> = 4.2V V<sub>IN</sub> = 4.2V V<sub>IN</sub> = 4.2V TO CONTINUOUS MODE

10

OUTPUT CURRENT (mA)

Burst Mode

OPERATION

$V_{OUT} = 2.5V$

1000

3403 G04

100

20

10

0

0.1

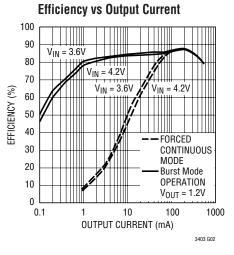

**Efficiency vs Output Current**

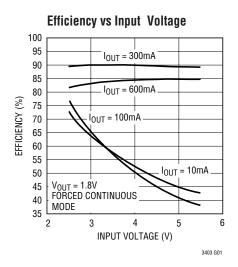

## TYPICAL PERFORMANCE CHARACTERISTICS (From Figure 1a)

### PIN FUNCTIONS

**GDR (Pin 1):** MOSFET Gate Driver. Drives a small external P-channel MOSFET.

$V_{IN}$  (Pin 2): Main Supply Pin. Must be closely decoupled to GND, Pin 3, with a  $10\mu F$  or greater ceramic capacitor.

GND (Pin 3): Ground Pin.

**SW (Pin 4):** Switch Node Connection to Inductor. This pin connects to the drains of the internal main and synchronous power MOSFET switches.

**RUN (Pin 5):** Run Control Input. Forcing this pin above 1.5V enables the part. Forcing this pin below 0.3V shuts down the device. In shutdown, all functions are disabled drawing <1μA supply current. Do not leave RUN floating.

**MODE (Pin 6):** Mode Select Input. To select forced continuous mode, tie to  $V_{IN}$ . Grounding this pin selects Burst Mode operation. Do not leave this pin floating.

**REF (Pin 7):** External Reference Input. Controls the output voltage to  $3\times$  the applied voltage at REF. Also turns on the bypass MOSFET when  $V_{RFF} > 1.2V$ .

**V**<sub>OUT</sub> (**Pin 8**): Output Voltage Feedback Pin. An internal resistive divider divides the output voltage down by 3 for comparison to the external reference voltage. The drain of the P-channel bypass MOSFET is connected to this pin.

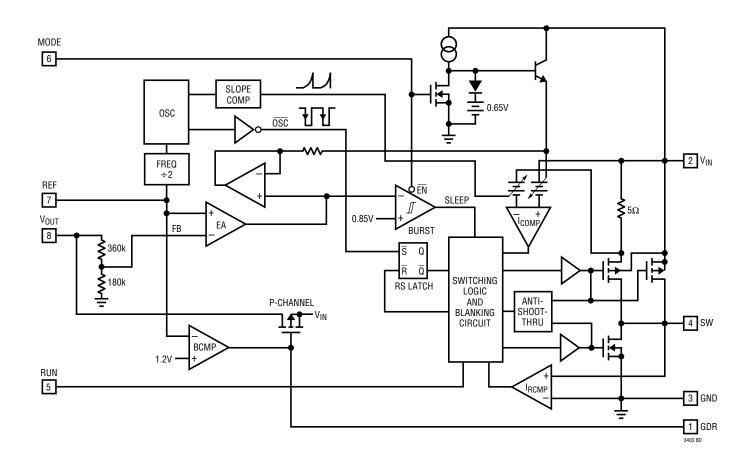

#### **FUNCTIONAL DIAGRAM**

### **OPERATION** (Refer to Functional Diagram)

#### **Main Control Loop**

The LTC3403 uses a constant frequency, current mode step-down architecture. The main (P-channel MOSFET), synchronous (N-channel MOSFET) and bypass (P-channel MOSFET) switches are internal. During normal operation, the internal main switch is turned on each cycle when the oscillator sets the RS latch, and turned off when the current comparator, I<sub>COMP</sub>, resets the RS latch. The peak inductor current at which I<sub>COMP</sub> resets the RS latch, is controlled by the output of error amplifier EA. When the load current increases, it causes a slight decrease in the feedback voltage, FB, relative to the external reference, which in turn, causes the EA amplifier's output voltage to increase until the average inductor current matches the new load current. While the main switch is off, the synchronous switch is turned on until the beginning of the next clock cycle.

The inductor current is constantly cycled in a forced continuous mode. In this mode, the output voltage can respond quickly to the external reference voltage by sourcing or sinking current as needed.

### **Burst Mode Operation**

The LTC3403 is capable of Burst Mode operation in which the internal power switches operate intermittently based on load demand.

In Burst Mode operation, the peak current of the inductor is set to approximately 200mA regardless of the output load. Each burst event can last from a few cycles at light loads to almost continuously cycling with short sleep intervals at moderate loads. In between these burst events, the power switches and any unneeded circuitry are turned off, reducing the quiescent current to  $20\mu A$ . In this sleep state, the load current is being supplied solely from the output capacitor. As the output voltage droops, the EA amplifier's output rises above the sleep threshold signaling the BURST comparator to trip and turn the top switch

on. This process repeats at a rate that is dependent on the load demand.

#### **Controlling the Output Voltage**

The output voltage can be dynamically programmed from 0.3V to 3.5V using the REF input. Because the gain to  $V_{OUT}$  from REF is internally set to 3, the corresponding input range at REF is 0.1V to 1.167V.  $V_{OUT}$  can be modulated during operation by driving REF with an external DAC.

When REF exceeds 1.2V, an internal bypass P-channel MOSFET connects  $V_{\text{IN}}$  to  $V_{\text{OUT}}$ , dramatically reducing the drop across the inductor and the main switch.

#### **Dropout Operation**

The LTC3403 will enter dropout operation when  $V_{OUT}$  is commanded to greater than or equal to the input voltage. During dropout, the main switch remains on continuously and operates at 100% duty cycle. If the voltage at REF is less than 1.2V, the bypass P-channel MOSFET will stay OFF even in dropout operation. The output voltage is then determined by the input voltage minus the voltage drop across the main switch and the inductor.

An important detail to remember is that at low input supply voltages, the  $R_{DS(ON)}$  of the P-channel switch increases (see Typical Performance Characteristics). Therefore, the user should calculate the power dissipation when the LTC3403 is used at 100% duty cycle with low input voltage (See Thermal Considerations in the Applications Information section).

#### **Low Supply Operation**

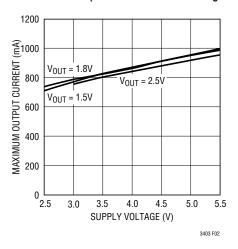

The LTC3403 will operate with input supply voltages as low as 2.5V, but the maximum allowable output current is reduced at this low voltage. Figure 2 shows the reduction in the maximum output current as a function of input voltage for various output voltages.

# **OPERATION** (Refer to Functional Diagram)

Figure 2. Maximum Output Current vs Input Voltage

#### **Slope Compensation and Inductor Peak Current**

Slope compensation provides stability in constant frequency architectures by preventing subharmonic oscillations at high duty cycles. It is accomplished internally by adding a compensating ramp to the inductor current signal at duty cycles in excess of 40%. Normally, this results in a reduction of maximum inductor peak current for duty cycles >40%. However, the LTC3403 uses a patent-pending scheme that counteracts this compensating ramp, which allows the maximum inductor peak current to remain unaffected throughout all duty cycles.

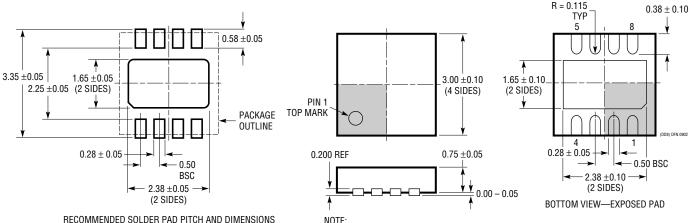

#### PACKAGE DESCRIPTION

#### **DD Package** 8-Lead Plastic DFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1698)

- 1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE MO-229 VARIATION OF (WEED-1)

- 2. ALL DIMENSIONS ARE IN MILLIMETERS

- 3. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 4. EXPOSED PAD SHALL BE SOLDER PLATED

## TYPICAL APPLICATION

#### High Efficiency Step-Down Converter with External Bypass MOSFET

## **RELATED PARTS**

| PART NUMBER DESCRIPTION                          |                                                                                                                | COMMENTS                                                                                                                            |  |  |  |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LT1616                                           | 1.4MHz, 600mA Step Down DC/DC Converter                                                                        | V <sub>IN</sub> : 3.6V to 25V, I <sub>Q</sub> = 1.9mA, ThinSOT <sup>™</sup> Package                                                 |  |  |  |  |

| LTC1701                                          | 1MHz, 500mA (I <sub>OUT</sub> ) Step-Down DC/DC Converter                                                      | V <sub>IN</sub> : 2.5V to 5.5V, Constant Off-Time, I <sub>Q</sub> = 135μA, ThinSOT Package                                          |  |  |  |  |

| LTC1767                                          | 1.5A, 1.25MHz Step-Down Switching Regulator                                                                    | V <sub>IN</sub> : 3V to 25V, I <sub>Q</sub> = 1mA, MS8/E Packages                                                                   |  |  |  |  |

| LTC1779                                          | 550kHz, 250mA (I <sub>OUT</sub> ) Step-Down Switching Regulator                                                | V <sub>IN</sub> : 2.5V to 9.8V, I <sub>Q</sub> = 135μA, ThinSOT Package                                                             |  |  |  |  |

| LTC1877                                          | 550kHz, 600mA (I <sub>OUT</sub> ) Synchronous Step-Down Regulator                                              | V <sub>IN</sub> : 2.65V to 10V, I <sub>Q</sub> = 10μA, MS8 Package                                                                  |  |  |  |  |

| LTC1878                                          | 550kHz, 600mA (I <sub>OUT</sub> ) Synchronous Step-Down Regulator                                              | V <sub>IN</sub> : 2.65V to 6V, I <sub>Q</sub> = 10μA, MS8 Package                                                                   |  |  |  |  |

| LTC3404                                          | 1.4MHz, 600mA (I <sub>OUT</sub> ) Synchronous<br>Monolithic Step-Down Regulator                                | Up to 95% Efficiency, $V_{IN}$ : 2.65V to 6V, $I_Q$ = 10 $\mu$ A, MS8 Package                                                       |  |  |  |  |

| LTC3405/LTC3405A<br>LTC3405A-1.5<br>LTC3405A-1.8 | 1.5MHz, 300mA (I <sub>OUT</sub> ) Synchronous<br>Monolithic Step-Down Regulators                               | Up to 95% Efficiency, V <sub>IN</sub> : 2.5V to 5.5V, I <sub>Q</sub> = 20μA, Fixed Output Voltages Available, ThinSOT Package       |  |  |  |  |

| LTC3406<br>LTC3406-1.5<br>LTC3406-1.8            | 1.5MHz, 600mA, (I <sub>OUT</sub> ) Synchronous<br>Monolithic Step-Down Regulators with Burst Mode<br>Operation | Up to 95% Efficiency, with Automatic Burst Mode Operation Enabled, Fixed Output Voltages Available, ThinSOT Package                 |  |  |  |  |

| LTC3406B<br>LTC3406B-1.5<br>LTC3406B-1.8         | 1.5MHz, 600mA, (I <sub>OUT</sub> ) Synchronous<br>Monolithic Step-Down Regulators with Burst Mode<br>Defeat    | Up to 95% Efficiency, with Pulse Skipping Mode Enabled, Fixed Output Voltages Available, ThinSOT Package                            |  |  |  |  |

| LTC3411                                          | 4MHz, 1.25A (I <sub>OUT</sub> ) Synchronous<br>Monolithic Step-Down Regulator                                  | Up to 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $I_Q$ = 60 $\mu$ A, MS10 Package                                                     |  |  |  |  |

| LTC3412                                          | 4MHz, 2.5A (I <sub>OUT</sub> ) Synchronous<br>Monolithic Step-Down Regulator                                   | Up to 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $I_Q$ = 60 $\mu$ A, TSSOP16 Package                                                  |  |  |  |  |

| LTC5505                                          | ThinSOT RF Power Detector with Buffered<br>Output and >40dB Dynamic Range                                      | 300MHz to 3GHz, Temperatrue Compensated, LTC5505-1: $-28$ dBm to 18dBm, LTC5505-2: $-32$ dBm to 12dBm, V <sub>CC</sub> = 2.7V to 6V |  |  |  |  |

ThinSOT is a trademark of Linear Technology Corporation.