#### **General Description**

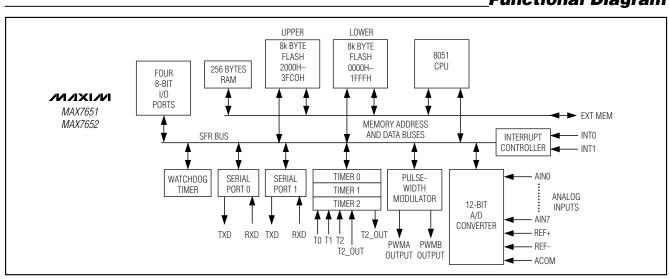

The MAX7651/MAX7652 are complete 12-bit data-acquisition systems featuring an algorithmic, switched-capacitor, analog-to-digital converter (ADC), a pulsewidth-modulated digital-to-analog converter (DAC), three timer/counters, and an industry-standard 8051 microprocessor core with a variety of I/O peripherals. Powerdown capability and full functionality with supply voltages as low as +3V make the MAX7651/MAX7652 suitable for portable and power-sensitive applications.

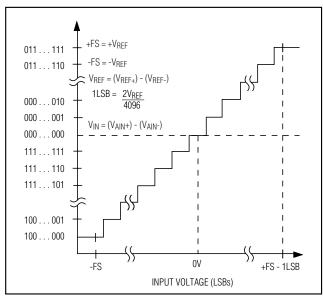

The MAX7651/MAX7652 perform fully differential voltage measurements with 12-bit resolution, programmable gain, and separate track-and-hold for both positive and negative inputs. The converter accepts versatile input modes consisting of four 2-channel signal pairs or eight 1-channel signals relative to a floating common.

The MAX7651/MAX7652 microprocessor systems feature a CPU, 256 bytes of RAM, two 8kB flash memory, four 8-bit I/O ports, two UARTs, an interrupt controller, and a watchdog timer. Only four clock cycles are required to complete each microprocessor instruction.

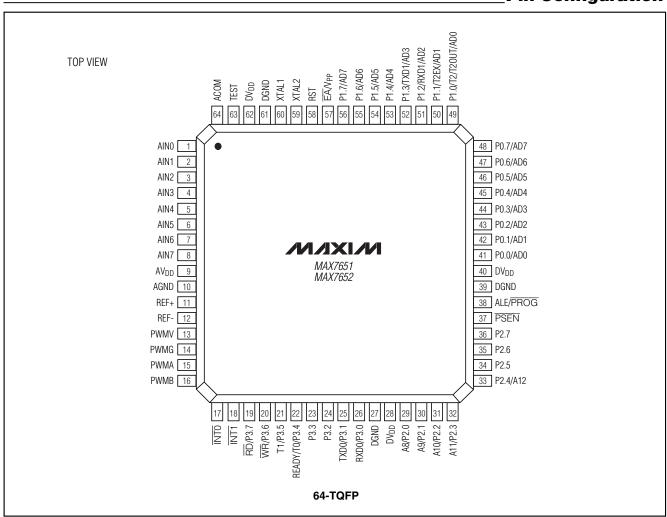

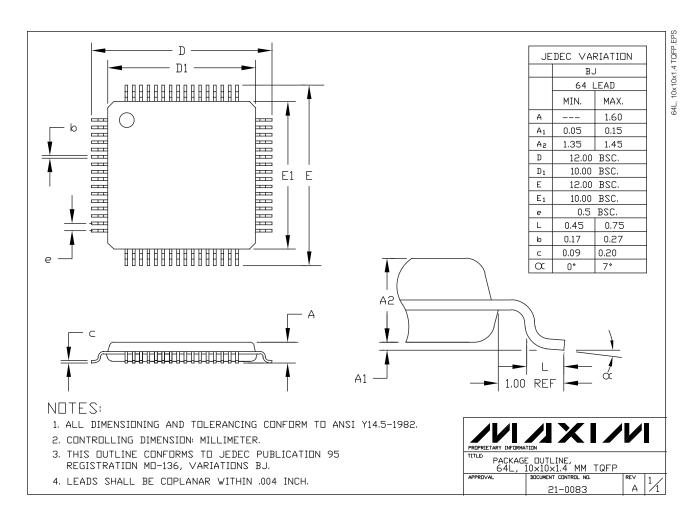

The MAX7651/MAX7652 are available in 64-pin TQFP packages.

## **Applications**

Hand-Held Instruments Portable Data-Acquisition Systems **Temperature Controllers Smart Transmitters Data Loggers** Multi-Channel Data-Acquisition with Data Formatting

#### **Ordering Information** TEMP. RANGE **PART PIN-PACKAGE** MAX7651CCB 0°C to +70°C 64 TQFP MAX7651ECB -40°C to +85°C 64 TQFP MAX7652CCB 0°C to +70°C 64 TQFP -40°C to +85°C MAX7652ECB 64 TQFP

Pin configuration appears at end of data sheet.

#### Features

- ♦ 12-Bit 53ksps ADC with Fully Differential Inputs

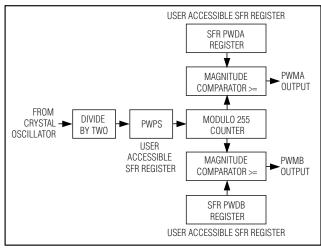

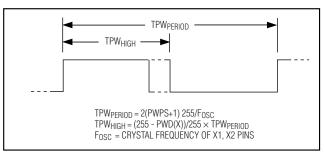

- ◆ Dual 8-Bit PWM DAC Outputs

- **♦ Three Timers**

- ♦ 4-Clock Cycle 8051-Compatible Instruction Set with Dual Data Pointers

- ♦ Programmable Watchdog Supervisor

- ♦ Four Parallel I/O Ports

- ◆ Dual Serial I/O Ports (up to 375kb)

- ♦ +3V or +5V Single-Supply Operation

- ♦ DC to 12MHz Clock Speed

- ♦ 64-Pin TQFP Package

## **Functional Diagram**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| 6V  |

|-----|

| 6V  |

| .3V |

| 3V  |

|     |

| .3V |

|     |

| .3V |

|     |

| .3V |

|     |

| REF+, REF- to AGND                                    |    |

|-------------------------------------------------------|----|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |    |

| 64-Pin TQFP (derate 5.00mW/°C above +70°C)500m        | W  |

| Operating Temperature Range                           |    |

| MAX765_CCB0°C to +70°                                 | °C |

| MAX765_ECB40°C to +85°                                | °C |

| Junction Temperature+150°                             | °C |

| Storage Temperature Range65°C to +150°                | °C |

| Lead Temperature (soldering, 10s)+300                 | °C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(MAX7651 \text{ AV}_{DD} = V_{PWMV} = DV_{DD} = V_{REF+} = +4.5V \text{ to } +5.5V, V_{REF-} = 0, f_{XTAL} = 12MHz. MAX7652 \text{ AV}_{DD} = V_{PWMV} = DV_{DD} = +2.7V \text{ to } +3.6V, V_{REF+} = +2.5V, V_{REF-} = 0, A_{COM} = A_{VDD}/2, f_{XTAL} = 12MHz. T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}C.)$

| PARAMETER                               | SYMBOL       | CONDITIONS              |                         |             | TYP   | MAX  | UNITS  |  |

|-----------------------------------------|--------------|-------------------------|-------------------------|-------------|-------|------|--------|--|

| DC ACCURACY                             |              |                         |                         | •           |       |      | •      |  |

| Resolution                              | RES          |                         |                         | 12          |       |      | bits   |  |

|                                         |              | Differential            | MAX7651                 |             |       | ±1.5 |        |  |

| Relative Accuracy (Note 1)              | INL          | Dillerential            | MAX7652                 |             |       | ±1.0 | LSB    |  |

| Helative Accuracy (Note 1)              | IINL         | Single-ended            | MAX7651                 |             |       | ±4.0 | LOD    |  |

|                                         |              | origic crided           | MAX7652                 |             |       | ±1.5 |        |  |

| Differential Nonlinearity               | DNL          | Differential            |                         |             | ±0.5  | ±1   | LSB    |  |

| (Note2)                                 | DIVL         | Single-ended            |                         |             | ±0.5  | ±1   | LOD    |  |

| Offset Error (Note 2)                   |              |                         |                         |             | ±2.3  | ±7   | LSB    |  |

| Offset Temperature<br>Coefficient       |              |                         |                         |             | ±0.25 |      | LSB/°C |  |

| Gain Error (Note 2)                     |              |                         |                         |             |       | 3    | %      |  |

| Gain Temperature<br>Coefficient         |              |                         |                         |             | ±3    |      | ppm/°C |  |

| Channel-to-Channel<br>Matching (Note 2) |              | Offset and gain         |                         |             | ±0.25 |      | LSB    |  |

| DYNAMIC SPECIFICATIO                    | NS (53ksps   | , 1kHz SINE-WAVE INPUT  | , 5Vp-p (MAX7651), 2.5\ | /p-p (MAX76 | 52))  |      |        |  |

| Signal-to-Noise +                       | CINIAD       | Differential            |                         |             | 71    |      | dB     |  |

| Distortion                              | SINAD        | Single-ended            |                         |             | 67    |      | UD UD  |  |

| Total Harmonic Distortion               | THD          | All unaliased harmonics | Differential            |             | -78   |      | dB     |  |

| Total Harmonic Distortion               | Single-ended |                         | -73                     |             | uВ    |      |        |  |

| Spurious-Free Dynamic                   | SFDR         | Differential            |                         |             | 81    |      | dB     |  |

| Range                                   | OI DIT       | Single-ended            |                         |             | 79    |      | QD.    |  |

| Channel-to-Channel<br>Crosstalk         |              | (Note 3)                |                         |             | -85   |      | dB     |  |

| Small-Signal Bandwidth                  |              | -3dB rolloff            |                         |             | 1     |      | MHz    |  |

| Full-Power Bandwidth                    |              |                         |                         |             | 1     |      | MHz    |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(MAX7651\ AV_{DD} = V_{PWMV} = DV_{DD} = V_{REF+} = +4.5V\ to\ +5.5V,\ V_{REF-} = 0,\ f_{XTAL} = 12MHz.\ MAX7652\ AV_{DD} = V_{PWMV} = DV_{DD} = +2.7V\ to\ +3.6V,\ V_{REF+} = +2.5V,\ V_{REF-} = 0,\ A_{COM} = A_{VDD}/2,\ f_{XTAL} = 12MHz.\ T_{A} = T_{MIN}\ to\ T_{MAX},\ unless otherwise\ noted.\ Typical\ values\ are\ at\ T_{A} = +25^{\circ}C.)$

| PARAMETER                                                     | SYMBOL                 | CONDITIONS                              | MIN                                  | TYP                                 | MAX                           | UNITS                     |   |

|---------------------------------------------------------------|------------------------|-----------------------------------------|--------------------------------------|-------------------------------------|-------------------------------|---------------------------|---|

| CONVERSION RATE                                               | •                      |                                         |                                      |                                     |                               |                           |   |

| Conversion Time                                               | tCONV                  | $f_{XTAL} = 12MHz$                      | 18.7                                 |                                     |                               | μs                        |   |

| Conversion Rate                                               |                        | f <sub>XTAL</sub> = 12MHz               |                                      |                                     | 53.6                          | ksps                      |   |

| ANALOG INPUTS (AIN0-                                          | AIN7, ACOM             | 1)                                      |                                      |                                     |                               |                           |   |

| Input Voltage Range                                           |                        |                                         | 0                                    |                                     | $AV_{DD}$                     | V                         |   |

| Common-Mode Range                                             |                        |                                         | 0                                    |                                     | $AV_{DD}$                     | V                         |   |

| Input Current                                                 |                        |                                         |                                      |                                     | 1                             | μΑ                        |   |

| Input Capacitance                                             | C <sub>IN</sub>        |                                         |                                      | 10                                  |                               | рF                        |   |

| DIGITAL INPUTS                                                | •                      |                                         | <u>.</u>                             |                                     |                               |                           |   |

| Input Voltage Low                                             | VIL                    |                                         | -0.5                                 | ([                                  | 0.2 x<br>V <sub>DD</sub> - 1) | V                         |   |

| Input Voltage High                                            | V                      | Input high voltage, except XTAL and RST | 0.2 x<br>(DV <sub>DD</sub><br>+ 0.9) |                                     | DV <sub>DD</sub><br>+ 0.5     | V                         |   |

|                                                               | iput voltage mign      | V <sub>IH</sub>                         | Input high voltage, XTAL and RST     | 0.7 x<br>(DV <sub>DD</sub><br>+ 0.1 |                               | DV <sub>DD</sub><br>+ 0.5 | V |

| Internal Reset Pulldown                                       |                        | MAX7651                                 | 90                                   |                                     | 409                           | 1.0                       |   |

| Resistance                                                    | R <sub>RST</sub>       | MAX7652                                 | 170                                  |                                     | 490                           | kΩ                        |   |

| Logical High-to-Low<br>Transition Current                     | I <sub>TL</sub>        | Guaranteed by design                    |                                      |                                     | 750                           | μΑ                        |   |

| Logical Zero Input Current,<br>Ports 1, 2, and 3 ALE,<br>PSEN |                        | (Note 4)                                |                                      |                                     | 75                            | μΑ                        |   |

| Input Leakage Current,<br>Port 0                              | I <sub>IN</sub>        | $V_{IN} = DV_{DD}$ or DGND              |                                      |                                     | ±10                           | μΑ                        |   |

| Input Capacitance                                             |                        |                                         |                                      | 10                                  |                               | рF                        |   |

| DIGITAL OUTPUTS                                               |                        |                                         | •                                    |                                     |                               |                           |   |

| Output Low Voltage                                            | VoL                    | I <sub>SINK</sub> = 4mA                 |                                      |                                     | 0.45                          | V                         |   |

| 0 1 112 1 11 11                                               | MAX7651: ISOURCE = 4mA |                                         | 2.4                                  |                                     |                               |                           |   |

| Output High Voltage                                           | Voh                    | MAX7652: Isource = 2mA                  | 2.4                                  |                                     |                               | V                         |   |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(MAX7651: AV_{DD} = V_{PWMV} = DV_{DD} = V_{REF+} = +4.5V \text{ to } +5.5V, V_{REF-} = 0, f_{XTAL} = 12MHz. MAX7652: AV_{DD} = V_{PWMV} = DV_{DD} = +2.7V \text{ to } +3.6V, V_{REF+} = +2.5V, V_{REF-} = 0, A_{COM} = A_{VDD}/2, f_{XTAL} = 12MHz. T_{A} = T_{MIN} \text{ to } T_{MAX}, unless \text{ otherwise noted. Typical values are at } T_{A} = +25^{\circ}C.)$

| PARAMETER                              | SYMBOL                 | CONDITIONS                                            | MIN TY                      | P MAX                        | UNITS |

|----------------------------------------|------------------------|-------------------------------------------------------|-----------------------------|------------------------------|-------|

| EXTERNAL VOLTAGE R                     | EFERENCE (             | CHARACTERISTICS (REF+, REF-)                          | ·                           |                              |       |

| Reference Voltage<br>Range             |                        | V <sub>REF+</sub> - V <sub>REF-</sub>                 | 0                           | $AV_{DD}$                    | V     |

| Reference Input Current                |                        |                                                       |                             | 35                           | μΑ    |

| Reference Input<br>Capacitance         |                        |                                                       | 10                          | )                            | pF    |

| POWER REQUIREMENTS                     | S                      |                                                       |                             |                              |       |

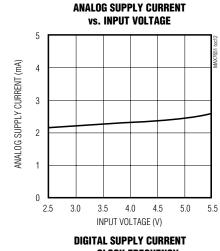

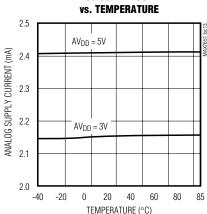

| Analog Supply Current                  |                        |                                                       |                             | 5                            | mA    |

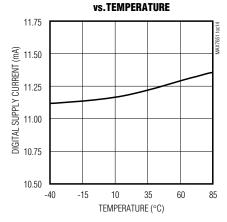

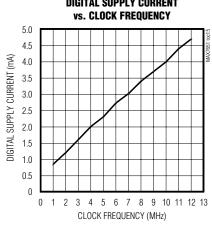

| Digital Supply Current                 |                        | MAX7651, during page erase MAX7652, during page erase |                             | 55<br>40                     | mA    |

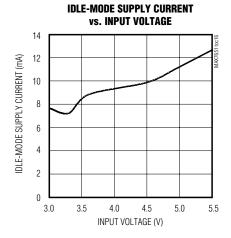

| Idle-Mode Digital<br>Supply Current    |                        | MAX7651<br>MAX7652                                    | 13                          |                              | mA    |

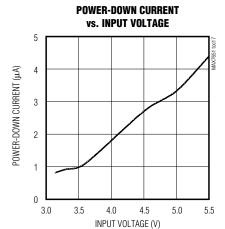

| Stop-Mode Supply Current               |                        | I <sub>AVDD</sub> + I <sub>DVDD</sub> (Note 5)        | <u> </u>                    | 10                           | μΑ    |

| Analog Power-Supply<br>Rejection Ratio | PSRR                   |                                                       | -4                          | 0                            | dB    |

| PWM OUTPUTS                            |                        |                                                       | ·                           |                              |       |

| Output Low Voltage                     |                        | ISINK = 2mA                                           |                             | 0.4                          | V     |

| Output High Voltage                    |                        | ISOURCE = 2mA                                         | 2.4                         |                              | V     |

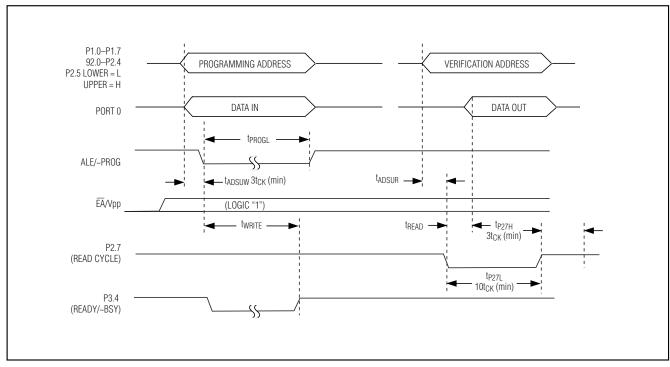

| FLASH EXTERNAL PRO                     | GRAMMING               | (FIGURE 1, NOTE 6)                                    |                             |                              |       |

| Program Pulse Width                    | tprogl                 |                                                       | 10t <sub>CK</sub>           |                              | ns    |

| Program Address and<br>Data Setup      | tasuw                  | Guaranteed by design                                  | 3t <sub>CK</sub>            |                              | ns    |

| Program Cycle Time                     | twoite                 | MAX7651                                               | 7t <sub>CK</sub><br>+ 54000 | 16t <sub>CK</sub><br>+ 72000 | no    |

| Frogram Cycle Time                     | twrite                 | MAX7652                                               | 7t <sub>CK</sub><br>+ 54000 | 32t <sub>CK</sub><br>+ 72000 | ns    |

| Verify Address and<br>Data Set         | tadsur                 |                                                       | 3t <sub>CK</sub>            |                              | ns    |

| Verify Access Time                     | t <sub>READ</sub>      |                                                       |                             | 9t <sub>CK</sub><br>+ 50     | ns    |

| Minimum P2.7 Pulse<br>Width Low        | t <sub>P27L</sub>      |                                                       | 10t <sub>CK</sub>           |                              | ns    |

| Minimum P2.7 Pulse<br>Width High       | tP27H                  | Guaranteed by design                                  | 3t <sub>CK</sub>            |                              | ns    |

| Clock Period                           | tck                    |                                                       | 83                          | 250                          | ns    |

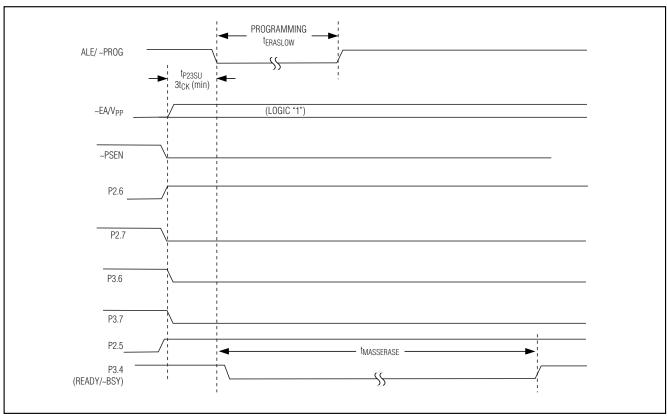

| FLASH EXTERNAL MAS                     | S ERASE (FI            | GURE 2, NOTE 6)                                       |                             |                              |       |

| Erase Mode Setup                       | t <sub>P23SU</sub>     |                                                       | 3t <sub>CK</sub>            |                              | ns    |

| Program Pulse Width                    | teraslow               |                                                       | 10t <sub>CK</sub>           |                              | ns    |

| Erase Cycle Time                       | <sup>t</sup> MASSERASE |                                                       | 8.29                        | 11                           | ms    |

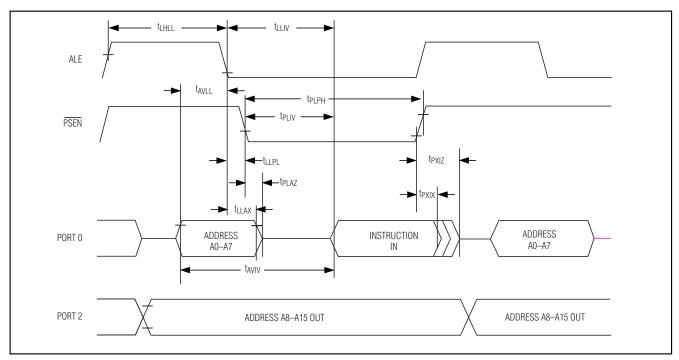

#### **TIMING CHARACTERISTICS**

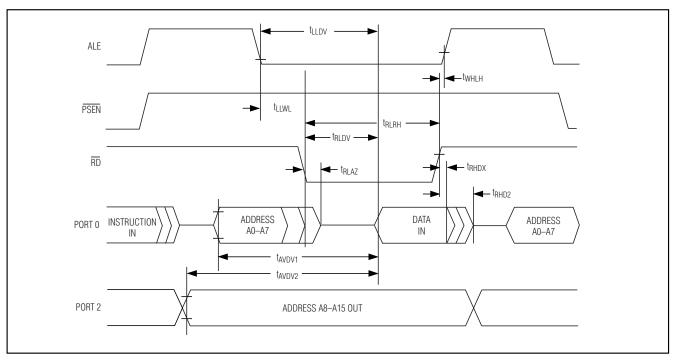

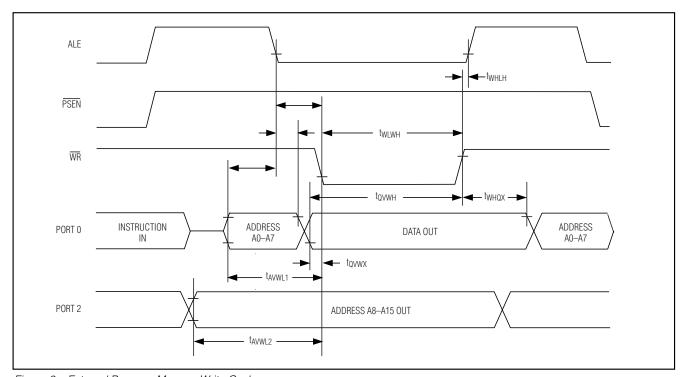

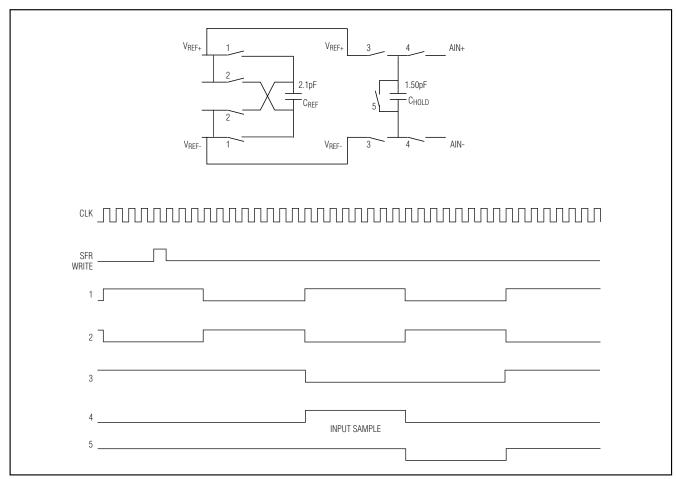

$(MAX7651: AVDD = VPWMV = DVDD = VREF_+ = +4.5 \text{ to } +5.5 \text{V}, VREF_- = 0, \text{ } f_{XTAL} = 12 \text{MHz}. \text{ } MAX7652: \text{ } AVDD = VPWMV = DVDD = +2.7 \text{V to } +3.6 \text{V}, \text{ } V_{REF_+} = +2.5 \text{V}, \text{ } V_{REF_-} = 0, \text{ } ACOM = AV_{DD}/2, \text{ } f_{XTAL} = 12 \text{MHz}. \text{ } T_A = T_{MIN} \text{ to } T_{MAX}, \text{ } unless \text{ } otherwise \text{ } noted. \text{ } Typical \text{ } values \text{ } are \text{ } at \text{ } T_A = +25 ^{\circ}\text{C.}) \text{ } (\text{Figure } 3)$

| PARAMETER                          | SYMBOL            | CONDITIONS           | MIN TY                       | P MAX                         | UNITS |

|------------------------------------|-------------------|----------------------|------------------------------|-------------------------------|-------|

| RST Pulse Width (High)             |                   |                      | 100 +                        |                               | μs    |

| , , ,                              |                   |                      | (64 x t <sub>CK</sub> )      |                               | μο    |

| EXTERNAL CLOCK                     |                   |                      |                              |                               |       |

| Clock Frequency                    | fcK               |                      |                              | 12                            | MHz   |

| Clock Period                       | tclcl             |                      | 83                           |                               | ns    |

| Clock High Time                    | tCHCX             |                      | 25                           |                               | ns    |

| Clock Low Time                     | tclcx             |                      | 25                           |                               | ns    |

| Clock Rise Time                    | tCLCH             | Guaranteed by design |                              | 10                            | ns    |

| Clock Fall Time                    | tCHCL             | Guaranteed by design |                              | 10                            | ns    |

| INSTRUCTION TIMING CHA             | RACTERIST         | ICS                  |                              |                               |       |

| ALE Pulse Width                    | tLHLL             |                      | 1.5t <sub>CLCL</sub> - 20    |                               | ns    |

| Address Valid to ALE Low           | tavll             |                      | 0.5t <sub>CLCL</sub> -<br>15 |                               | ns    |

| Address Hold after ALE<br>Low      | t <sub>LLAX</sub> |                      | 0.5t <sub>CLCL</sub> - 20    |                               | ns    |

| ALE Low to Valid<br>Instruction In | t <sub>LLIV</sub> |                      |                              | 2.5t <sub>CLC</sub><br>L - 35 | ns    |

| ALE Low to PSEN Low                | tLLPL             |                      | 0.5t <sub>CLCL</sub><br>- 10 |                               | ns    |

| PSEN Pulse Width                   | tplph             |                      | 2t <sub>CLCL</sub><br>- 15   |                               | ns    |

| PSEN Low to Valid Instruction In   | tpLIV             |                      |                              | 2t <sub>CLCL</sub> -<br>35    | ns    |

| Input Instruction Hold after PSEN  | t <sub>PXIX</sub> |                      | 0                            |                               | ns    |

| Input Instruction Float after PSEN | t <sub>PXIZ</sub> |                      |                              | tclcl -<br>15                 | ns    |

| Address to Valid Instruction In    | taviv             |                      |                              | 3t <sub>CLCL</sub> -<br>50    | ns    |

| PSEN Low to Address Float          | tplaz             |                      |                              | 10                            | ns    |

## **TIMING CHARACTERISTICS (continued)**

$(MAX7651: AVDD = VPWMV = DVDD = VREF_+ = +4.5 \text{ to } +5.5 \text{V}, VREF_- = 0, \text{ } f_{XTAL} = 12 \text{MHz}. \text{ } MAX7652: \text{ } AVDD = VPWMV = DVDD = +2.7 \text{V} \text{ to } +3.6 \text{V}, \text{ } V_{REF_+} = +2.5 \text{V}, \text{ } V_{REF_-} = 0, \text{ } ACOM = AV_{DD}/2, \text{ } f_{XTAL} = 12 \text{MHz}. \text{ } T_A = T_{MIN} \text{ to } T_{MAX}, \text{ } unless \text{ } otherwise \text{ } noted. \text{ } Typical \text{ } values \text{ } are \text{ } at \text{ } T_A = +25 \text{°C.}) \text{ } (\text{Figure 3})$

| PARAMETER                            | SYMBOL             | CONDITIONS                                 | MIN TY                      | P MAX                                           | UNITS |

|--------------------------------------|--------------------|--------------------------------------------|-----------------------------|-------------------------------------------------|-------|

| MOVX TIMING CHARACTER                | RISTICS (Not       | te 6)                                      | •                           |                                                 | •     |

| DD Dula - Wilde                      |                    | t <sub>MCS</sub> = 0, Guaranteed by design | 2t <sub>CLCL</sub> - 20     |                                                 |       |

| RD Pulse Width                       | trlrh              | t <sub>MCS</sub> > 0, Guaranteed by design | t <sub>MCS</sub> - 20       |                                                 | ns    |

| WR Pulse Width                       | ********           | t <sub>MCS</sub> = 0                       | 2t <sub>CLCL</sub> - 20     |                                                 | 20    |

| WH Pulse Width                       | twLwH              | t <sub>MCS</sub> > 0                       | t <sub>MCS</sub> - 20       |                                                 | ns    |

| RD Low to Valid Data In              | t <sub>RLDV</sub>  | $t_{MCS} = 0$                              |                             | 2t <sub>CLCL</sub><br>- 55                      | ns    |

|                                      |                    | t <sub>MCS</sub> > 0                       |                             | t <sub>MCS</sub> - 55                           |       |

| Data Hold After RD                   | trhdx              |                                            | 0                           |                                                 | ns    |

| Data Flant Affair DD                 |                    | $t_{MCS} = 0$                              |                             | tCLCL -<br>10                                   |       |

| Data Float After RD                  | tRHDZ              | t <sub>MCS</sub> > 0                       |                             | 2t <sub>CLCL</sub><br>- 10                      | ns    |

| ALEL LA VILLE LA                     |                    | t <sub>MCS</sub> = 0                       |                             | 2.5t <sub>CLCL</sub><br>- 58                    |       |

| ALE Low to Valid Data In             | tLLDV              | t <sub>MCS</sub> > 0                       |                             | 1.5t <sub>CLCL</sub><br>- 58 + t <sub>MCS</sub> | ns    |

| Port 0 Address to Valid              |                    | t <sub>MCS</sub> = 0                       |                             | 3t <sub>CLCL</sub><br>- 60                      |       |

| Data In                              | tavdv1             | t <sub>MCS</sub> > 0                       |                             | 2t <sub>CLCL</sub> -<br>61 + t <sub>MCS</sub>   | ns    |

| Port 2 Address to Valid              |                    | t <sub>MCS</sub> = 0                       |                             | 3t <sub>CLCL</sub><br>- 60                      |       |

| Data In                              | t <sub>AVDV2</sub> | t <sub>MCS</sub> > 0                       |                             | 2t <sub>CLCL</sub> - 64<br>+ t <sub>MCS</sub>   | ns    |

| ALE Low to RD or WR Low              |                    | t <sub>MCS</sub> = 0                       | 0.5t <sub>CLCL</sub><br>- 5 | 0.5t <sub>CLCL</sub><br>+ 10                    |       |

| ALE LOW TO RD OF WR LOW              | tLLWL              | t <sub>MCS</sub> > 0                       | 1.5t <sub>CLCL</sub><br>- 5 | 1.5t <sub>CLCL</sub><br>+ 10                    | ns    |

| Port 0 Address Valid to RD or WR Low |                    | t <sub>MCS</sub> = 0                       | tclcl<br>- 10               |                                                 |       |

|                                      | t <sub>AVWL1</sub> | t <sub>MCS</sub> > 0                       | 2taLaL -<br>10              |                                                 | ns    |

| Port 2 Address Valid to RD           |                    | t <sub>MCS</sub> = 0                       | tCLCL<br>- 10               |                                                 |       |

| or WR Low                            | tavwl2             | t <sub>MCS</sub> > 0                       | 2t <sub>CLCL</sub> -        |                                                 | ns    |

#### **TIMING CHARACTERISTICS (continued)**

$(MAX7651: AVDD = VPWMV = DVDD = VREF_+ = +4.5 \text{ to } +5.5 \text{V}, VREF_- = 0, \text{ } f_{XTAL} = 12 \text{MHz}. \text{ } MAX7652: AVDD = VPWMV = DVDD = +2.7 \text{V} \text{ to } +3.6 \text{V}, VREF_+ = +2.5 \text{V}, VREF_- = 0, ACOM = AVDD/2, } f_{XTAL} = 12 \text{MHz}. \text{ } T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted}. \text{ } T_{YDD} = 12 \text{MHz}.$

| PARAMETER                                | SYMBOL            | CONDITIONS                                            | MIN                        | TYP                                       | MAX          | UNITS |

|------------------------------------------|-------------------|-------------------------------------------------------|----------------------------|-------------------------------------------|--------------|-------|

|                                          |                   | $t_{MCS} = 0$                                         | -9                         |                                           |              |       |

| Data Valid to WR Transition              | t <sub>QVWX</sub> | t <sub>MCS</sub> > 0                                  | t <sub>CLCL</sub>          |                                           |              | ns    |

| Data Valid Before WR High                | +0.000            | $t_{MCS} = 0$                                         | 2t <sub>CLCL</sub><br>- 20 |                                           |              | 200   |

| Data valid belore Wh high                | tQVWH             | t <sub>MCS</sub> > 0                                  | tMCs<br>- 30               |                                           |              | ns    |

| Data Hald After MD High                  |                   | $t_{MCS} = 0$                                         | t <sub>CLCL</sub>          |                                           |              | -     |

| Data Hold After WR High                  | twhqx             | t <sub>MCS</sub> > 0                                  | 2t <sub>CLCL</sub> - 18    |                                           |              | ns    |

| RD Low to Address Float                  | tRLAZ             |                                                       |                            |                                           | 0            | ns    |

|                                          |                   | t <sub>MCS</sub> = 0                                  | 0                          |                                           | 10           | 200   |

| RD or WR High to ALE High                | twhlh             | t <sub>MCS</sub> > 0                                  | tCLCL<br>- 5               |                                           | tCLCL<br>+11 | ns    |

| SERIAL PORT TIMING CHAI                  | RACTERISTI        | cs                                                    | -                          |                                           |              | •     |

| Serial Port Clock Cycle                  | txLxL             | SM2 = 0 (12 clocks/cycle)                             |                            | 12 t <sub>CLCL</sub>                      |              | ns    |

| Time                                     | 1XLXL             | SM2 = 1 (4 clocks/cycle)                              |                            | 4 tolol                                   |              | 110   |

| Output Data Setup to Clock               | tQVXH             | SM2 = 0 (12 clocks/cycle)                             |                            | 10 t <sub>CLCL</sub>                      |              | ns    |

| Rising Edge                              | *QVXIII           | SM2 = 1 (4 clocks/cycle)                              |                            | 3 t <sub>CLCL</sub>                       |              | 1.0   |

| Output Data Hold after                   | txhqx             | SM2 = 0 (12 clocks/cycle)                             |                            | 2tclcl                                    |              | ns    |

| Clock Rising Edge                        |                   | SM2 = 1 (4 clocks/cycle)                              |                            | tolol                                     |              |       |

| Input Data Hold after Clock              | txhdx             | SM2 = 0 (12 clocks/cycle)                             |                            | tclcl                                     |              | ns    |

| Rising Edge                              | ,,,,,,,,          | SM2 = 1 (4 clocks/cycle)                              |                            | tclcl                                     |              |       |

| Clock Rising Edge to Input<br>Data Valid | txhdv             | SM2 = 0 (12 clocks/cycle)<br>SM2 = 1 (4 clocks/cycle) |                            | 11t <sub>CLCL</sub><br>3t <sub>CLCL</sub> |              | ns    |

- Note 1: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the offset and gain errors have been nullified.

- **Note 2:**  $A_{VDD} = +5.0V$ ,  $(V_{REF}+) (V_{REF}-) = +5.0V$  or  $A_{VDD} = +3.0V$ ,  $(V_{REF}+) (V_{REF}-) = +2.5V$ .

- Note 3: Ground at "ON" channel; 10kHz sine-wave applied to all "off" channels.

- Note 4: ALE and PSEN are in reset cycle.

- Note 5: All digital inputs are at DGND or DVDD. fxTAL = 0.

- Note 6: Table 1. Data Memory Stretch Values.

- Note 7: The minimum frequency when writing to the internal flash is 4MHz.

**Table 1. Data Memory Stretch Values**

| MD2 | MD1 | MD0 | MEMORY CYCLES | READ/WRITE STROBE<br>WIDTH (CLOCKS) | STROBE WIDTH TIME<br>AT 12MHz | tMCS                |

|-----|-----|-----|---------------|-------------------------------------|-------------------------------|---------------------|

| 0   | 0   | 0   | 2             | 2                                   | 167ns                         | 0t <sub>CLCL</sub>  |

| 0   | 0   | 1   | 3 (default)   | 4                                   | 334ns                         | 4tCLCL              |

| 0   | 1   | 0   | 4             | 8                                   | 668ns                         | 8t <sub>CLCL</sub>  |

| 0   | 1   | 1   | 5             | 12                                  | 997ns                         | 12t <sub>CLCL</sub> |

| 1   | 0   | 0   | 6             | 16                                  | 1330ns                        | 16t <sub>CLCL</sub> |

| 1   | 0   | 1   | 7             | 20                                  | 1666ns                        | 20t <sub>CLCL</sub> |

| 1   | 1   | 0   | 8             | 24                                  | 2000ns                        | 24t <sub>CLCL</sub> |

| 1   | 1   | 1   | 9             | 28                                  | 2333ns                        | 28t <sub>CLCL</sub> |

**Table 2. External Flash Programming Modes**

| MODE              | RST | PSEN | ALE/PROG             | EA/V <sub>PP</sub> | P2.6 | P2.7                 | P3.6 | P3.7 | P2.5 |

|-------------------|-----|------|----------------------|--------------------|------|----------------------|------|------|------|

| Write Lower FLASH | Н   | L    | $\uparrow\downarrow$ | Н                  | L    | Н                    | Н    | Н    | L    |

| Read Lower FLASH  | Н   | L    | Н                    | Н                  | L    | $\uparrow\downarrow$ | Н    | Н    | L    |

| Write Lock Bit 1  | Н   | L    | $\uparrow\downarrow$ | Н                  | Н    | Н                    | Н    | Н    | Н    |

| Write Lock Bit 2  | Н   | L    | $\uparrow\downarrow$ | Н                  | Н    | Н                    | L    | L    | Н    |

| Write Lock Bit 3  | Н   | L    | $\uparrow\downarrow$ | Н                  | Н    | L                    | Н    | L    | Н    |

| Mass Erase        | Н   | L    | $\uparrow\downarrow$ | Н                  | Н    | L                    | L    | L    | Н    |

| Read Sig Bytes    | Н   | L    | Н                    | Н                  | L    | L                    | L    | L    | L    |

| Write Upper FLASH | Н   | L    | $\uparrow\downarrow$ | Н                  | L    | Н                    | Н    | Н    | Н    |

| Read Upper FLASH  | Н   | L    | Н                    | Н                  | L    | $\uparrow\downarrow$ | Н    | Н    | Н    |

|                   |     |      |                      |                    |      |                      |      |      |      |

Note 1: To program the lock bits, ALE must be low for duration of "Write Lockbit" cycle.

**Note 2:**  $\overline{\text{INTO}}$  and  $\overline{\text{INT1}}$  are open-drain and must either be driven or require a pullup (typically 10k $\Omega$ ) to DV<sub>DD</sub>.

Figure 1. FLASH External Mass Erase Waveforms

Figure 2. FLASH External Programming and Verification Waveforms

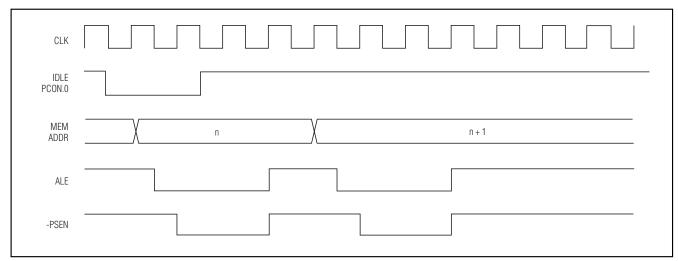

Figure 3a. External Program Memory Read Cycle

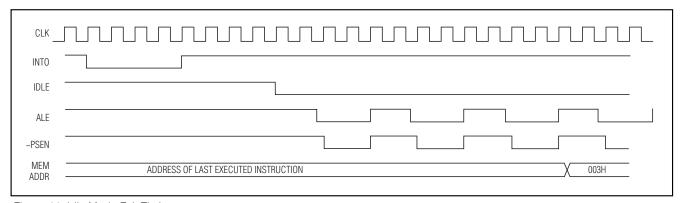

Figure 3b. External Data Memory Read Cycle

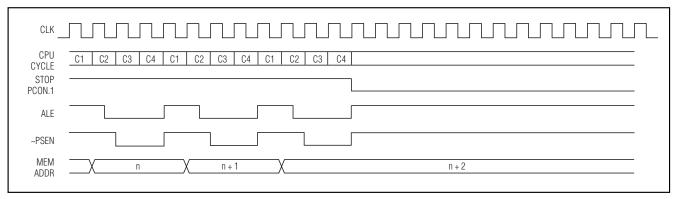

Figure 3c. External Program Memory Write Cycle

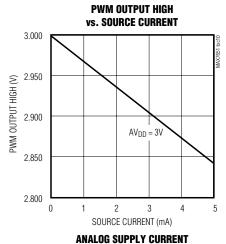

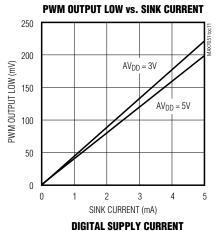

#### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$ MAX7651: AVDD = VPWMV = DVDD = VREF+ = 5.0V, VREF- = 0, VCOM = AVDD/2, fXTAL = 12MHz. MAX7652: AVDD = VPWMV = DVDD = VREF+ = 3.0V, VREF- = 0, VCOM = AVDD/2, fXTAL = 12MHz. **NEGATIVE GAIN ERROR vs.** SINGLE-ENDED INL vs. OUTPUT CODE **DNL vs. OUTPUT CODE SUPPLY VOLTAGE** 1.0 1.0 0.3 SINGLE-ENDED 0.8 8.0 0.2 0.6 0.6 0.1 0.4 0.4 0.2 0.2 DNL (LSB) (LSB) -0.1 DIFFERENTIAL 0 0 봄 -0.2 -0.2 -0.2 -0.3 -0.4 -0.4 -0.4 -0.6 -0.6 -0.5 -0.8 -0.8 -0.6 -1.0 -1.0 500 1000 1500 2000 2500 3000 3500 4000 4500 -2000-1500-1000 -500 0 500 1000 1500 2000 -2000 -1500 -1000 -500 0 500 1000 1500 2000 0 CODE CODE CODE OFFSET ERROR vs. **POSITIVE GAIN ERROR vs. SUPPLT VOLTAGE OFFSET ERROR vs.TEMPERATURE SUPPLY VOLTAGE** 1.0 0 1.0 -0.1 DIFFERENTIAL 0.5 0.5 -0.2 OFFSET ERROR (LSB) OFFSET ERROR (LSB) GAIN ERROR (LSB) -0.3 SINGLE-ENDED 0 SINGLE-ENDED 0 SINGLE-ENDED -0.4 -0.5 -0.5 -0.5 -0.6DIFFERENTIAL DIFFERENTIAL -1.0 -1.0 2.5 3.0 4.0 4.5 5.0 5.5 3.5 -40 35 60 85 2.5 3.0 4.0 SUPPLY VOLTAGE (V) TEMPERATURE (°C) SUPPLY VOLTAGE (V) **NEGATIVE GAIN ERROR POSITIVE GAIN ERROR PWM OUTPUT HIGH** vs. TEMPERATURE vs. TEMPERATURE vs. SOURCE CURRENT 0.4 1.4 5.000 1.2 0.2 DIFFERENTIAL 4.950 DIFFERENTIAL PWM OUTPUT HIGH (V) GAIN ERROR (LSB) 0 GAIN ERROR (LSB)  $AV_{DD} = 5V$ 0.8 -0.2 4.900 0.6 -0.4 SINGLE-ENDED 0.4 4.850 SINGLE-ENDED -0.6 0.2 4 800 -0.8 0 -40 -15 10 35 .-40 -15 10 35 0 2 3 TEMPERATURE (°C) TEMPERATURE (°C)

SOURCE CURRENT (mA)

## Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, unless otherwise noted.)$

MAX7651: AV<sub>DD</sub> = V<sub>PWMV</sub> = DV<sub>DD</sub> = V<sub>REF+</sub> = 5.0V, V<sub>REF-</sub> = 0, V<sub>COM</sub> = AV<sub>DD</sub>/2, f<sub>XTAL</sub> = 12MHz.

MAX7652:  $AV_{DD} = V_{PWMV} = DV_{DD} = V_{REF+} = 3.0V$ ,  $V_{REF-} = 0$ ,  $V_{COM} = AV_{DD}/2$ ,  $f_{XTAL} = 12MHz$ .

## **Pin Description**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1   | AIN0             | Analog Input 0. Negative differential input relative to AIN1 or positive differential input relative to ACOM. (See Table 6)                                                                                                  |  |  |  |  |  |  |

| 2   | AIN1             | Analog Input 1. Positive differential input relative to AIN0 or positive differential input relative to ACOM. (See Table 6)                                                                                                  |  |  |  |  |  |  |

| 3   | AIN2             | Analog Input 2. Negative differential input relative to AIN3 or positive differential input relative to ACOM. (See Table 6)                                                                                                  |  |  |  |  |  |  |

| 4   | AIN3             | Analog Input 3. Positive differential input relative to AIN2 or positive differential input relative to ACOM. (See Table 6)                                                                                                  |  |  |  |  |  |  |

| 5   | AIN4             | Analog Input 4. Negative differential input relative to AIN5 or positive differential input relative to ACOM. (See Table 6)                                                                                                  |  |  |  |  |  |  |

| 6   | AIN5             | Analog Input 5. Positive differential input relative to AIN4 or positive differential input relative to ACOM. (See Table 6)                                                                                                  |  |  |  |  |  |  |

| 7   | AIN6             | Analog Input 6. Negative differential input relative to AIN7 or positive differential input relative to ACOM. (See Table 6)                                                                                                  |  |  |  |  |  |  |

| 8   | AIN7             | Analog Input 7. Positive differential input relative to AIN6 or positive differential input relative to ACOM. (See Table 6)                                                                                                  |  |  |  |  |  |  |

| 9   | AV <sub>DD</sub> | Positive Analog Supply Voltage. Analog power source for the A/D converter and other analog functions excluding the PWM D/A converter. Bypass with a 0.1µF in parallel with a 10µF low ESR capacitor to AGND.                 |  |  |  |  |  |  |

| 10  | AGND             | Analog Ground. Connect PWMG to AGND.                                                                                                                                                                                         |  |  |  |  |  |  |

| 11  | REF+             | High-Side Reference Input. High-side reference voltage for A/D conversions. Must be between AV <sub>DD</sub> and AGND. Bypass to AGND with a 0.1µF in parallel with a 10µF low ESR capacitor to AGND.                        |  |  |  |  |  |  |

| 12  | REF-             | Low-Side Reference Input. Low-side reference voltage for A/D conversions. Must be between AV <sub>DD</sub> and AGND. If not connected to AGND bypass to AGND with a 0.1µF in parallel with a 10µF low ESR capacitor to AGND. |  |  |  |  |  |  |

| 13  | PWMV             | Positive Analog Supply Voltage 2. Analog power source for the the PWM D/A converter outputs. Bypass with a 0.1µF in parallel with a 10µF low ESR capacitor to PWMG.                                                          |  |  |  |  |  |  |

| 14  | PWMG             | Ground for PWM. Connect to AGND.                                                                                                                                                                                             |  |  |  |  |  |  |

| 15  | PWMA             | PWM Output A. Output of PWM D/A Converter A. See PWM Digital-to-Analog Conversions.                                                                                                                                          |  |  |  |  |  |  |

| 16  | PWMB             | PWM Output B. Output of PWM D/A Converter B. See PWM Digital-to-Analog Conversions.                                                                                                                                          |  |  |  |  |  |  |

| 17  | ĪNT0             | External Interrupt 0 Input (active-low)                                                                                                                                                                                      |  |  |  |  |  |  |

| 18  | ĪNT1             | External Interrupt 1 Input (active-low)                                                                                                                                                                                      |  |  |  |  |  |  |

| 10  | P3.7/RD          | P3.7: Bit 7 for General Purpose I/O Port 3 (most significant bit)                                                                                                                                                            |  |  |  |  |  |  |

| 19  | P3.7/RD          | RD: Read Output. Read strobe for accessing external data memory (active-low)                                                                                                                                                 |  |  |  |  |  |  |

| 20  | P3.6/WR          | P3.6: Bit 6 for General Purpose I/O Port 3                                                                                                                                                                                   |  |  |  |  |  |  |

| 20  | P3.6/WA          | WR: Write Output. Write strobe for writing to external data memory (active-low)                                                                                                                                              |  |  |  |  |  |  |

| 01  | P3.5/T1          | P3.5: Bit 5 for General Purpose I/O Port 3                                                                                                                                                                                   |  |  |  |  |  |  |

| 21  | P3.3/11          | T1: Timer 1 External Input                                                                                                                                                                                                   |  |  |  |  |  |  |

|     | Do 1/701         | P3.4: Bit 4 for General Purpose I/O Port 3                                                                                                                                                                                   |  |  |  |  |  |  |

| 22  | P3.4/T0/         | T0: Timer 0 External Input                                                                                                                                                                                                   |  |  |  |  |  |  |

|     | READY            | READY: Ready State Output (external flash programming mode only)                                                                                                                                                             |  |  |  |  |  |  |

| 23  | P3.3             | P3.3: Bit 3 for General Purpose I/O Port 3                                                                                                                                                                                   |  |  |  |  |  |  |

| 24  | P3.2             | P3.2: Bit 2 for General Purpose I/O Port 3                                                                                                                                                                                   |  |  |  |  |  |  |

| L   | L                |                                                                                                                                                                                                                              |  |  |  |  |  |  |

## Pin Description (continued)

| PIN  | NAME             | FUNCTION                                                                                                                                                                                          |

|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | P3.1/            | P3.1: Bit 1 for General Purpose I/O Port 3                                                                                                                                                        |

| 25   | TXD0             | TXD0: Transmit Serial Output for Serial Port                                                                                                                                                      |

|      | P3.0/            | P3.0: Bit 0 for General Purpose I/O Port 3 (least significant bit)                                                                                                                                |

| 26   | RXD0             | RXD0: Receive Serial Input for Serial Port                                                                                                                                                        |

| 27   | DGND             | Digital Ground. Connect DGND to AGND at the power source. Connect pins 27, 39, and 61 together.                                                                                                   |

| 28   | DV <sub>DD</sub> | Positive Digital Supply Voltage. Bypass with a 0.1µF in parallel with a 10µF low ESR capacitor to DGND. Connect pins 28, 40, and 62 together.                                                     |

|      | D0.0/4.0         | P2.0: Bit 0 for General Purpose I/O Port 2 (least significant bit)                                                                                                                                |

| 29   | P2.0/A8          | A8: Bit 8 for Internal Flash Memory Address                                                                                                                                                       |

| 00   | D0 4/40          | P2.1: Bit 1 for General Purpose I/O Port 2                                                                                                                                                        |

| 30   | P2.1/A9          | A9: Bit 9 for Internal Flash Memory Address                                                                                                                                                       |

| 0.1  | D0 0/440         | P2.2: Bit 2 for General Purpose I/O Port 2                                                                                                                                                        |

| 31   | P2.2/A10         | A10: Bit 10 for Internal Flash Memory Address                                                                                                                                                     |

| 00   | D0.0/4.11        | P2.3: Bit 3 for General Purpose I/O Port 2                                                                                                                                                        |

| 32   | P2.3/A11         | A11: Bit 11 for Internal Flash Memory Address                                                                                                                                                     |

| 00   | DO 4/440         | P2.4: Bit 4 for General Purpose I/O Port 2                                                                                                                                                        |

| 33   | P2.4/A12         | A12: Bit 12 for Internal Flash Memory Address                                                                                                                                                     |

| 0.4  | D0.5             | P2.5: Bit 5 for General Purpose I/O Port 2                                                                                                                                                        |

| 34   | P2.5             | Upper and Lower Internal Flash Memory Select (see Table 2)                                                                                                                                        |

| O.E. | DO 6             | P2.6: Bit 6 for General Purpose I/O Port 2                                                                                                                                                        |

| 35   | P2.6             | Flash Programming Mode Select (see Table 2)                                                                                                                                                       |

| 36   | P2.7             | P2.7: Bit 7 for General Purpose I/O Port 2 (most significant bit)                                                                                                                                 |

| 30   | 1 2.7            | Flash Programming Mode Select (see Table 2)                                                                                                                                                       |

| 37   | PSEN             | Program Store Enable (active-low). Qualifies program read from external devices. To ensure flash data integrity during RST insertions, $R_{LOAD}$ must be greater than or equal to $200k\Omega$ . |

| 38   | ALE/             | ALE: Address Latch Enable. To ensure flash data integrity during RST insertions, $R_{LOAD}$ must be greater than or equal to $200k\Omega$ .                                                       |

|      | PROG             | PROG: Flash Memory Program Pulse                                                                                                                                                                  |

| 39   | DGND             | Digital Ground. Connect pins 27, 39, and 61 together.                                                                                                                                             |

| 40   | DV <sub>DD</sub> | Positive Digital Supply Voltage. Bypass with a 0.1µF in parallel with a 10µF low ESR capacitor to DGND. Connect pins 28, 40 and 62 together.                                                      |

| 44   | DO 0/A DO        | P0.0: Bit 0 for General Purpose I/O Port 0 (least significant bit)                                                                                                                                |

| 41   | P0.0/AD0         | AD0: Bit 0 for Internal Flash Memory Data or External Memory I/O Data (least significant bit)                                                                                                     |

| 42   | P0.1/AD1         | P0.1: Bit 1 for General Purpose I/O Port 0                                                                                                                                                        |

| 42   | FU. 1/AD1        | AD1: Bit 1 for Internal Flash Memory Data or External Memory I/O Data                                                                                                                             |

| 43   | P0.2/AD2         | P0.2: Bit 2 for General Purpose I/O Port 0                                                                                                                                                        |

| 40   | 1 0.2/ADZ        | AD2: Bit 2 for Internal Flash Memory Data or External Memory I/O Data                                                                                                                             |

| 44   | P0.3/AD3         | P0.3: Bit 3 for General Purpose I/O Port 0                                                                                                                                                        |

| 44   | 1 0.3/AD3        | AD3: Bit 3 for Internal Flash Memory Data or External Memory I/O Data                                                                                                                             |

| 45   | P0.4/AD4         | P0.4: Bit 4 for General Purpose I/O Port 0                                                                                                                                                        |

| 40   | FU.4/AD4         | AD4: Bit 4 for Internal Flash Memory Data or External Memory I/O Data                                                                                                                             |

## Pin Description (continued)

| PIN | NAME               | FUNCTION                                                                                                                                                                         |

|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | P0.5/              | P0.5: Bit 5 for General Purpose I/O Port 0                                                                                                                                       |

| 46  | AD5                | AD5: Bit 5 for Internal Flash Memory Data or external memory I/O                                                                                                                 |

|     | P0.6/              | P0.6: Bit 6 for General Purpose I/O Port 0                                                                                                                                       |

| 47  | AD6                | AD6: Bit 6 for Internal Flash Memory Data or external memory I/O                                                                                                                 |

| 40  | P0.7/              | P0.7: Bit 7 for General Purpose I/O Port 0 (most significant bit)                                                                                                                |

| 48  | AD7                | AD7: Bit 7 for Internal Flash Memory Data or external memory I/O                                                                                                                 |

|     |                    | P1.0: Bit 0 for General Purpose I/O Port 1 (least significant bit)                                                                                                               |

| 10  | P1.0/T2/           | T2: Timer 2 External Input                                                                                                                                                       |

| 49  | T2OUT/<br>AD0      | T2OUT: Timer 2 External Output                                                                                                                                                   |

|     | 7100               | AD0: Bit 0 for Internal Flash Memory Address                                                                                                                                     |

|     | P1.1/              | P1.1: Bit 1 for General Purpose I/O Port 1                                                                                                                                       |

| 50  | T2EX/              | T2EX: Timer 2 External Capture/Reload Trigger                                                                                                                                    |

|     | AD1                | AD1: Bit 1 for Internal Flash Memory Address                                                                                                                                     |

|     | P1.2/              | P1.2: Bit 2 for General Purpose I/O Port 1                                                                                                                                       |

| 51  | RXD1/              | RXD1: Receive Serial Input for UART 1                                                                                                                                            |

|     | AD2                | AD2: Bit 2 for Internal Flash memory Address                                                                                                                                     |

|     | P1.3/              | P1.3: Bit 3 for General Purpose I/O Port 1                                                                                                                                       |

| 52  | TXD1/              | TXD1: Transmit Serial Input for UART 1                                                                                                                                           |

|     | AD3                | AD3: Bit 3 for Internal Flash Memory Address                                                                                                                                     |

| F0  | P1.4/              | P1.4: Bit 4 for General Purpose I/O Port 1                                                                                                                                       |

| 53  | AD4                | AD4: Bit 4 for Internal Flash Memory Address                                                                                                                                     |

| 54  | P1.5/              | P1.5: Bit 5 for General Purpose I/O Port 1                                                                                                                                       |

| 54  | AD5                | AD5: Bit 5 for Internal Flash Memory Address                                                                                                                                     |

| 55  | P1.6/              | P1.6: Bit 6 for General Purpose I/O Port 1                                                                                                                                       |

| 55  | AD6                | AD6: Bit 6 for Internal Flash Memory Address                                                                                                                                     |

| 56  | P1.7/              | P1.7: Bit 7 for General Purpose I/O Port 1                                                                                                                                       |

| 50  | AD7                | AD7: Bit 7 for Internal Flash Memory Address                                                                                                                                     |

| 57  | EA/V <sub>PP</sub> | EA: Connect to DGND to use external ROM. Connect EA to DVDD for internal flash memory.                                                                                           |

| 57  | EA/VPP             | V <sub>PP</sub> : Flash Programming Voltage (external flash programming mode only)                                                                                               |

| 58  | RST                | Active High Reset. Connected to an internal $130k\Omega$ pulldown resistor. Connect a $2.2\mu\text{F}$ (typ) capacitor from DV <sub>DD</sub> to RST.                             |

| 59  | XTAL2              | Clock Output. Connect a crystal across XTAL1 and XTAL2. The on-chip clock signal is not available at XTAL2. Leave XTAL2 unconnected when XTAL1 is driven with an external clock. |

| 60  | XTAL1              | Clock Input. Connect a crystal across XTAL1 and XTAL2. Alternatively, drive XTAL1 with a CMOS-compatible clock and leave XTAL2 unconnected.                                      |

| 61  | DGND               | Digital Ground. Connect pins 27, 39, and 61 together.                                                                                                                            |

| 62  | DV <sub>DD</sub>   | Positive Digital Supply Voltage. Bypass with a 0.1µF in parallel with a 10µF low ESR capacitor to DGND. Connect pins 28, 40 and 62 together.                                     |

| 63  | TEST               | Test Point. Must be connected to DGND.                                                                                                                                           |

| 64  | ACOM               | Analog Common Input. Negative differential input relative to AIN_ for single-ended measurements (see Table 6). Connect to AVDD/2 for maximum input range.                        |

#### Detailed Description

#### MAX7651/MAX7652 Architecture

The MAX7651/MAX7652 are complete 12-bit data-acquisition systems featuring an algorithmic, switched-capacitor, analog-to-digital converter (ADC), dual pulse-width-modulated digital-to-analog converter (DAC), and an industry-standard 8051 microprocessor core with a variety of I/O and timing peripherals.

Using an external oscillator with an operating frequency between 1MHz and 12MHz, the MAX7651/MAX7652 execute the majority of its commands in only four clock periods to yield an average speed improvement of 2.5 times over typical 8051 microprocessors requiring 12 clock periods instructions. See the MAX7651/MAX7652 *Programmer's Reference Manual* for further details.

On-chip peripherals include four 8-bit parallel ports, two serial ports, three general-purpose timers, and a watchdog timer. The MAX7651/MAX7652 also feature 16kB in two banks of 8kB flash memory and 256 bytes of high-speed random access memory.

#### **Memory Organization**

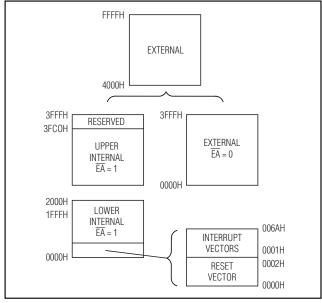

The MAX7651/MAX7652 support up to 64kB of external program (read-only) memory and data (random-access) memory in conformance with the 8051 industry standard.

Figure  $\underline{4}$  shows the program memory organization. When  $\overline{EA}$  is high, the CPU has access to two internal 8kB blocks of flash memory beginning at addresses 0000H (lower block) and 2000H (upper block). Addresses 0000H–0002H and 0003H–006AH of the lower block are reserved for the CPU reset vector and a set of interrupt vectors, respectively (see Table 3). Addresses 3FC0H–3FFFH of the upper block are also reserved and cannot be accessed by the CPU. Addresses 4000H–FFFFH are for external ROM. When  $\overline{EA}$  is low, the external ROM must be used for all program addresses (0000H–FFFFH).

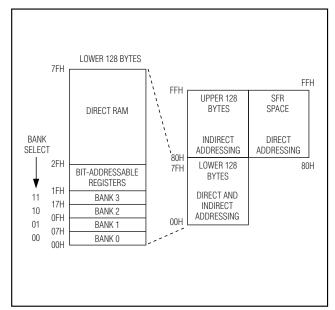

Figure 5 shows the data memory (RAM) organization. The first 256 bytes are partitioned between two internal 128-byte blocks. The lower block (addresses 0000H–007FH) is used for registers or scratchpad memory and can be accessed either directly or indirectly (see the MAX7651/MAX7652 *Programmer's Reference Manual*). The upper block (addresses 0080H–00FFH) reflects a set of special function registers (SFRs) when accessed directly, and separate scratchpad memory when accessed indirectly. Addresses 0100H–FFFFH are reserved for external RAM.

Table 4 shows the SFR mapping to memory and Table 5 shows the SFR contents on power-up or reset. Unshaded register designations are consistent with the industry standard 8051. Shaded register designations

Figure 4. Program Memory Organization

Figure 5. Data Memory (RAM) Organization

**Table 3. Reset and Interrupt Vector Locations**

| ADDRESS RANGE | FUNCTION                       | NATURAL PRIORITY* |

|---------------|--------------------------------|-------------------|

| 0000H-0002H   | Reset Vector                   | 0                 |

|               | INTERRUPT VECTORS              | ·                 |

| 0003H-000AH   | INTO (external interrupt 0)    | 1                 |

| 000BH-0012H   | Timer 0                        | 2                 |

| 0013H-001AH   | INT1 (external interrupt 1)    | 3                 |

| 001BH-0022H   | Timer 1                        | 4                 |

| 0023H-002AH   | Serial Port 0 transmit/receive | 5                 |

| 002BH-0032H   | Timer 2                        | 6                 |

| 0033H-003AH   | Reserved                       | _                 |

| 003BH-0042H   | Serial Port 1 transmit/receive | 7                 |

| 0043H-004AH   | Flash memory write/page erase  | 8                 |

| 004BH-0052H   | ADC (end of conversion)        | 9                 |

| 0053H-005AH   | Reserved                       | 10                |

| 005BH-0062H   | Reserved                       | 11                |

| 0063H-006AH   | Watchdog timer                 | 12                |

<sup>\*</sup>Lower priority number takes precedence.

**Table 4. SFR Memory Organization**

| HEX<br>ADDRESS | 0/8   | 1/9   | 2/A      | 3/B      | 4/C      | 5/D     | 6/E   | 7/F      |

|----------------|-------|-------|----------|----------|----------|---------|-------|----------|

| F8             | EIP   |       |          |          |          |         | PWMC  |          |

| F0             | В     |       |          |          |          |         |       |          |

| E8             | EIE   |       | EEAL     | EEAH     | EEDAT    | EESTCMD |       |          |

| E0             | ACC   |       |          |          |          |         |       |          |

| D8             | EICON |       | PWPS     | PWDA     | PWDB     | WDT     |       |          |

| D0             | PSW   |       |          |          |          |         |       |          |

| C8             | T2CON |       | RCAP2L   | RCAP2H   | TL2      | TH2     |       |          |

| C0             | SCON1 | SBUF1 | ADDAT0   | ADDAT1   | Reserved | ADCON   |       |          |

| B8             | IΡ    |       | Reserved | Reserved |          |         |       |          |

| В0             | P3    |       | VERSION  | Reserved | Reserved |         |       |          |

| A8             | ΙΕ    |       |          |          |          |         |       |          |

| A0             | P2    |       |          |          |          |         |       |          |

| 98             | SCON0 | SBUF0 |          |          |          |         |       |          |

| 90             | P1    | EXIF  |          |          |          |         |       |          |

| 88             | TCON  | TMOD  | TL0      | TH0      | TL1      | TH1     | CKCON | Reserved |

| 80             | P0    | SP    | DPL0     | DPH0     | DPL1     | DPH1    | DPS   | PCON     |

Note 1: SFRs in column 0/8 are bit addressable. Other SFRs are not bit addressable.

Note 2: The VERSION SFR contains the silicon ID and will change for future MAX7651/MAX7652 revisions.

**Table 5. SFR Contents on Power-Up or Reset**

| REGISTER | ADDRESS | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|----------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| P0       | 80      | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| SP       | 81      | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

| DPL0     | 82      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| DPH0     | 83      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| DPL1     | 84      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| DPH1     | 85      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| DPS      | 86      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| PCON     | 87      | 0     | 0     | 1     | 1     | 0     | 0     | 0     | 0     |

| TCON     | 88      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| TMOD     | 89      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| TL0      | 8A      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| TH0      | 8B      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| TL1      | 8C      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| TH1      | 8D      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| CKCON    | 8E      |       |       |       |       |       |       |       |       |

| P1       | 90      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| EXIF     | 91      | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| SCON0    | 98      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| SBUF0    | 99      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| P2       | A0      | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| ΙE       | A8      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| P3       | В0      | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| IP       | B8      | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| SCON1    | C0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| SBUF1    | C1      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| ADDAT0   | C2      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| ADDAT1   | C3      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| ADCON    | C5      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| T2CON    | C8      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| RCAP2L   | CA      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| RCAP2H   | СВ      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| TL2      | CC      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| TH2      | CD      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| PSW      | D0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| EICON    | D8      | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| PWPS     | DA      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| PWDTA    | DB      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| PWDTB    | DC      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| WDT      | DD      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Table 5. SFR Contents on Power-Up or Reset (continued)

| REGISTER | ADDRESS | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|----------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| ACC      | E0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| EIE      | E8      | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     |

| EEAL     | EA      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| EEAH     | EB      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| EEDAT    | EC      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| EESTCMD  | ED      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| В        | F0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| EIP      | F8      | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     |

| PWMC     | FE      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

are unique to the MAX7651/MAX7652. Subsequent sections of this data sheet explain the SFR functions.

RESERVED SFR addresses are used for MAX7651/MAX7652 testing and should not be accessed by user software. Undesignated SFR addresses are not implemented and will return indefinite data when read.

#### Special Function Registers for Microprocessor Operations and Control

#### Accumulator SFR

The Accumulator SFR is used for arithmetic operations including addition, subtraction, multiplication, division, and Boolean bit manipulation. Accumulator specific instructions designate the accumulator as "A".

#### B SFR

The B SFR is used for multiply and divide operations. It is otherwise available as a scratchpad register.

#### **Program Status Word SFR**