To our customers,

---

## Old Company Name in Catalogs and Other Documents

---

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <http://www.renesas.com>

April 1<sup>st</sup>, 2010

Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<http://www.renesas.com>)

Send any inquiries to <http://www.renesas.com/inquiry>.

## Notice

1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

SMALL, GENERAL-PURPOSE

4 BIT SINGLE-CHIP MICROCONTROLLER

The  $\mu$ PD17P149 is a one-time PROM version of the  $\mu$ PD17149. It uses a one-time PROM, which can be written just once, instead of internal masked ROM of the  $\mu$ PD17149.

Since a user program can be written into the PROM, this microcontroller is suited for program evaluation and low-volume production of the  $\mu$ PD17145,  $\mu$ PD17147,  $\mu$ PD17149, or for program evaluation of the  $\mu$ PD17145(A),  $\mu$ PD17147(A),  $\mu$ PD17149(A),  $\mu$ PD17145(A1),  $\mu$ PD17147(A1), and  $\mu$ PD17149(A1). \*

The following user's manual completely describes the functions of the  $\mu$ PD17P149. Be sure to read it before designing an application system.

$\mu$ PD17145 Sub-Series User's Manual: U10261E

#### FEATURES

- 17K architecture : General registers, 16-bit instructions

- Pin compatible with the  $\mu$ PD17149 (except for PROM programming function)

- Internal one-time PROM : 8K bytes (4096  $\times$  16 bits)

- Supply voltage :  $V_{DD} = 2.7$  to 5.5 V (when operating at the range between 400 kHz and 2 MHz with ceramic oscillation)

$V_{DD} = 4.5$  to 5.5 V (when operating at the range between 400 kHz and 8 MHz with ceramic oscillation)

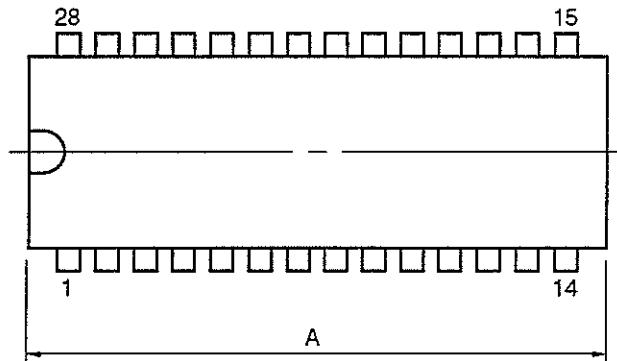

#### ORDERING INFORMATION

| Part number      | Package                             |

|------------------|-------------------------------------|

| $\mu$ PD17P149CT | 28-pin plastic shrink DIP (400 mil) |

| $\mu$ PD17P149GT | 28-pin plastic SOP (375 mil)        |

In the program memory write/verify mode, the voltage used for programming is applied to pin No. 23,  $P0F0/RLS/VPP$ . If a voltage of  $V_{DD}$  plus 0.3 V or more is applied to this pin in the normal operation mode, the microcontroller may crash. Design the circuit so that a voltage of this magnitude is never applied to the pin.

The information in this document is subject to change without notice.

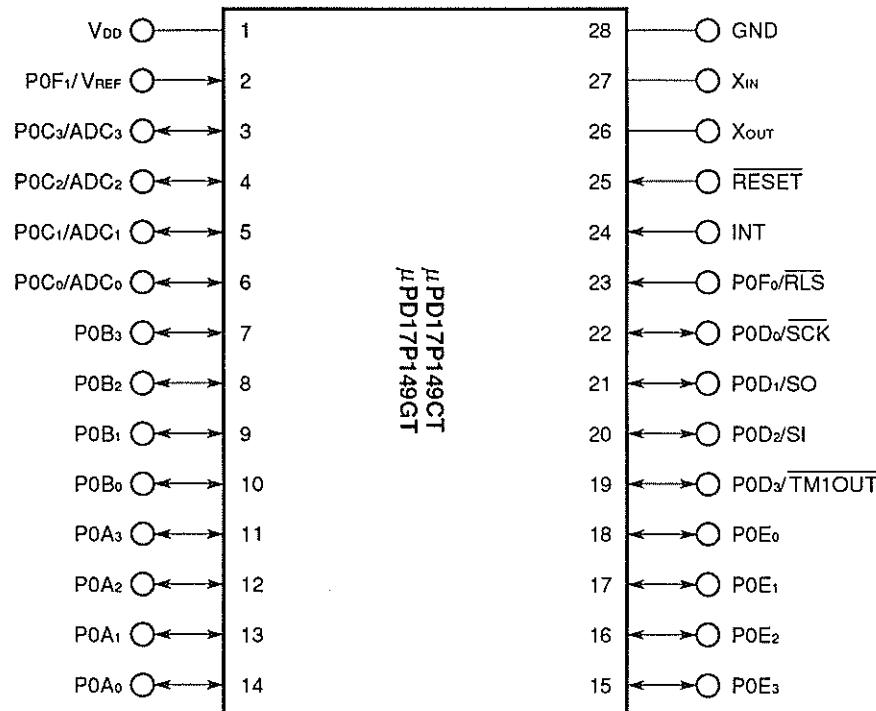

## PIN CONFIGURATION (TOP VIEW)

## (1) Normal operation mode

ADC<sub>0</sub> - ADC<sub>3</sub> : Analog input

GND : Ground

INT : External interrupt input

P0A<sub>0</sub> - P0A<sub>3</sub> : Port 0A

P0B<sub>0</sub> - P0B<sub>3</sub> : Port 0B

P0C<sub>0</sub> - P0C<sub>3</sub> : Port 0C

P0D<sub>0</sub> - P0D<sub>3</sub> : Port 0D

P0E<sub>0</sub> - P0E<sub>3</sub> : Port 0E

P0F<sub>0</sub> and P0F<sub>1</sub> : Port 0F

RESET : Reset input

RLS : Standby release signal input

SCK : Serial clock input/output

SI : Serial data input

SO : Serial data output

TM1OUT : Timer 1 carry output

VDD : Power supply

VREF : Reference voltage for the A/D converter

XIN, XOUT : System clock oscillation

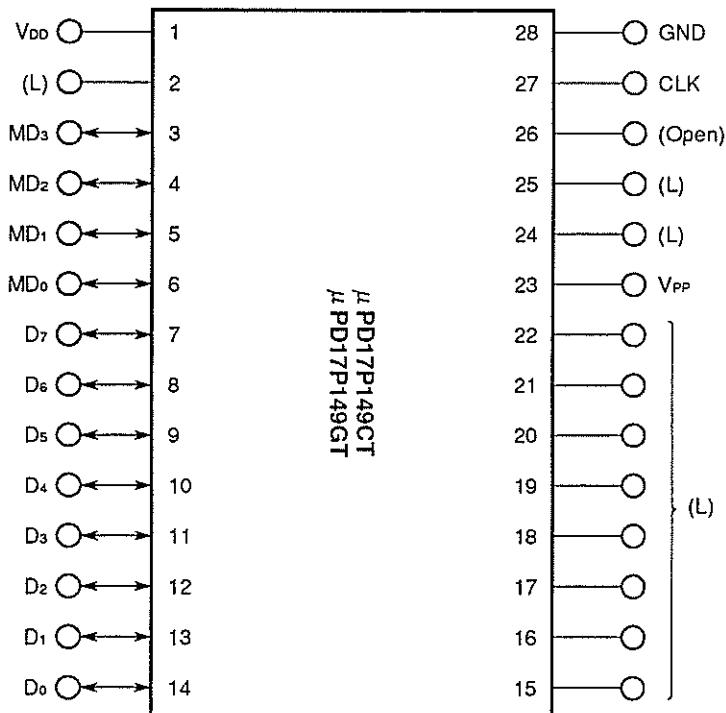

## (2) Program memory write/verify mode

CLK : Input clock for address update

MD0 - MD3 : Operating mode selection

D0 - D7 : Data

VDD : Power supply

GND : Ground

VPP : Programming power supply

**Caution** Symbols in parentheses denote processing for pins not used in the program memory write/verify mode.

**L** : Connect these pins separately to the GND pin through pull-down resistors.

**Open** : Nothing should be connected on these pins.

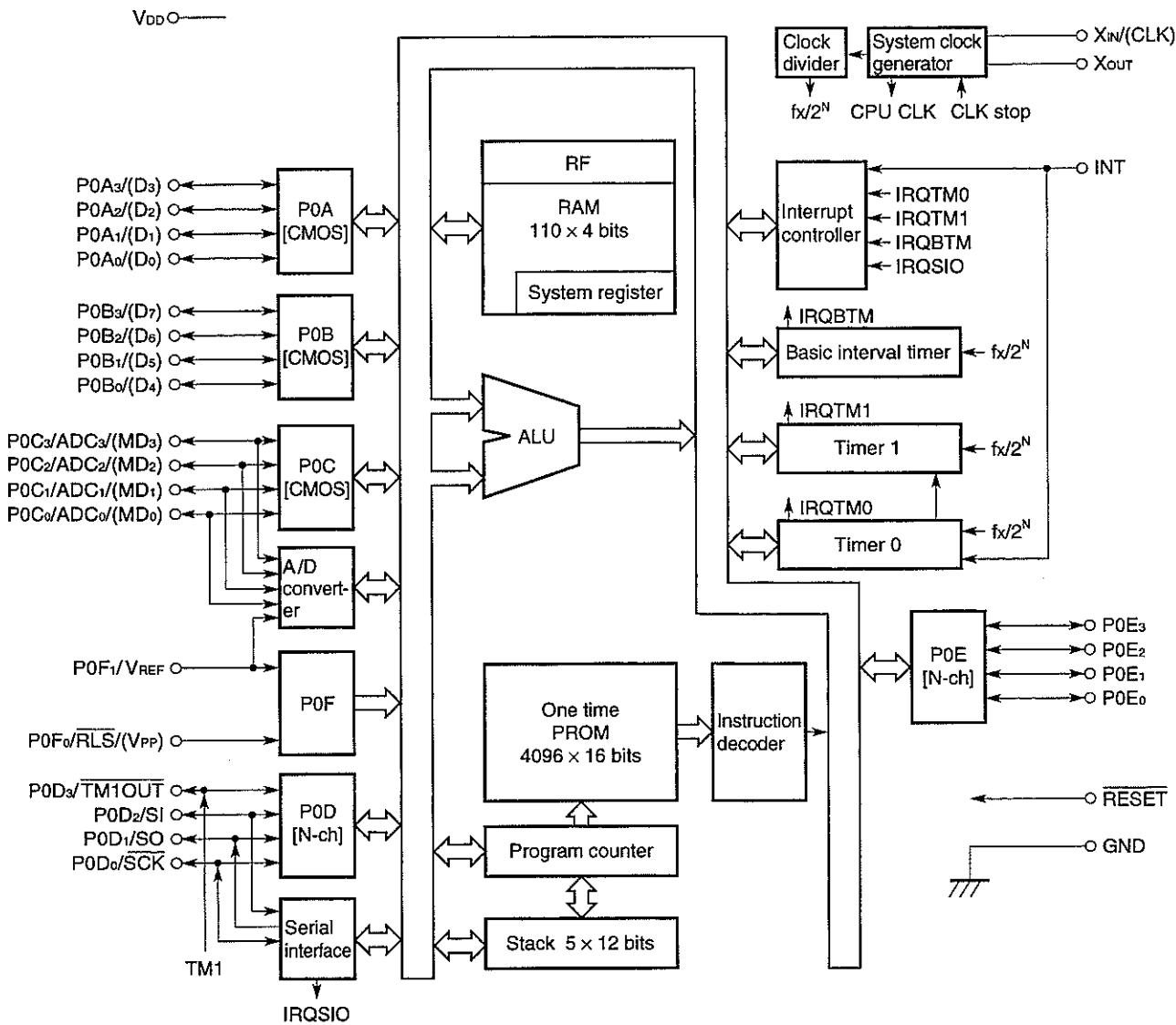

## BLOCK DIAGRAM

Remark ( ) : PROM programming mode

The terms CMOS and N-ch in brackets indicate the output form of the port.

CMOS : CMOS push-pull output

N-ch : N-channel open-drain output

## CONTENTS

|                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------|----|

| 1. PIN FUNCTIONS .....                                                                                      | 6  |

| 1.1    NORMAL OPERATION MODE.....                                                                           | 6  |

| 1.2    PROGRAM MEMORY WRITE/VERIFY MODE .....                                                               | 8  |

| 1.3    EQUIVALENT INPUT/OUTPUT CIRCUITS .....                                                               | 9  |

| 1.4    HANDLING UNUSED PINS .....                                                                           | 13 |

| 1.5    NOTES ON USE OF THE RESET AND P0F <sub>0</sub> /RLS PINS (ONLY AT THE NORMAL<br>OPERATION MODE)..... | 14 |

| 2. DIFFERENCES BETWEEN THE μPD17145, μPD17147, μPD17149, AND<br>μPD17P149 .....                             | 15 |

| 3. WRITING TO AND VERIFYING ONE-TIME PROM (PROGRAM MEMORY) .....                                            | 16 |

| 3.1    PROGRAM MEMORY WRITE/VERIFY MODES .....                                                              | 16 |

| 3.2    WRITING TO PROGRAM MEMORY .....                                                                      | 17 |

| 3.3    READING PROGRAM MEMORY .....                                                                         | 18 |

| 4. ELECTRICAL CHARACTERISTICS .....                                                                         | 19 |

| 5. PACKAGE DRAWINGS.....                                                                                    | 27 |

| 6. RECOMMENDED SOLDERING CONDITIONS.....                                                                    | 29 |

| APPENDIX A. μPD17145 SUB-SERIES PRODUCTS LIST .....                                                         | 30 |

| APPENDIX B. DEVELOPMENT TOOLS .....                                                                         | 31 |

## 1. PIN FUNCTIONS

### 1.1 NORMAL OPERATION MODE

| Pin No.              | Symbol                                                                       | Function                                                                                                                                                                                                                                                                                | Output          | Upon reset                |

|----------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|

| 1                    | V <sub>DD</sub>                                                              | Power supply                                                                                                                                                                                                                                                                            | —               | —                         |

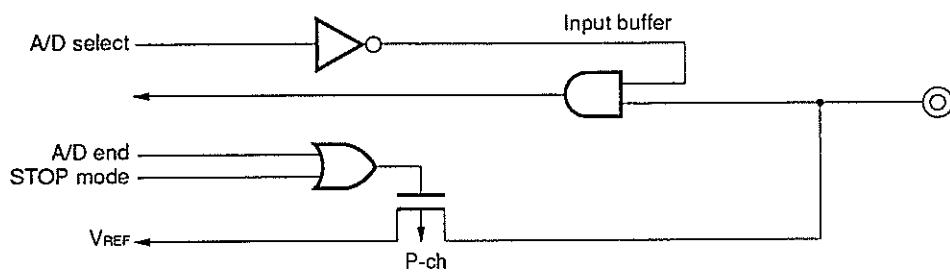

| 2                    | P0F <sub>1</sub> /V <sub>REF</sub>                                           | Port 0F. The reference voltage is supplied to the A/D converter through this pin.<br>• P0F <sub>1</sub><br>• Bit 1 of 2-bit input port P0F<br>• V <sub>REF</sub><br>• Reference voltage input for the A/D converter                                                                     | Input           | Input (P0F <sub>1</sub> ) |

| 3 - 6                | P0C <sub>3</sub> /ADC <sub>3</sub> - P0C <sub>0</sub> /ADC <sub>0</sub>      | Port 0C. Analog voltage is supplied to the A/D converter through these pins.<br>• P0C <sub>3</sub> - P0C <sub>0</sub><br>• 4-bit input/output port<br>• Input/output setting allowed in units of 1 bit<br>• ADC <sub>3</sub> - ADC <sub>0</sub><br>• Analog input for the A/D converter | CMOS push-pull  | Input (P0C)               |

| 7<br>8<br>9<br>10    | P0B <sub>3</sub><br>P0B <sub>2</sub><br>P0B <sub>1</sub><br>P0B <sub>0</sub> | Port 0B<br>• 4-bit input/output port<br>• Input/output setting allowed in units of 4 bits<br>• Pull-up resistor incorporation specifiable by program in units of 4 bits                                                                                                                 | CMOS push-pull  | Input                     |

| 11<br>12<br>13<br>14 | P0A <sub>3</sub><br>P0A <sub>2</sub><br>P0A <sub>1</sub><br>P0A <sub>0</sub> | Port 0A<br>• 4-bit input/output port<br>• Input/output setting allowed in units of 4 bits<br>• Pull-up resistor incorporation specifiable by program in units of 4 bits                                                                                                                 | CMOS push-pull  | Input                     |

| 15<br>16<br>17<br>18 | P0E <sub>3</sub><br>P0E <sub>2</sub><br>P0E <sub>1</sub><br>P0E <sub>0</sub> | Port 0E<br>• Withstand voltage is V <sub>DD</sub> (Max.).<br>• 4-bit input/output port<br>• Input/output setting allowed in units of 4 bits<br>• Pull-up resistor incorporation specifiable by program in units of 4 bits                                                               | N-ch open drain | Input                     |

| Pin No. | Symbol                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Output          | Upon reset                |

|---------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|

| 19      | P0D <sub>3</sub> /TM1OUT | Pin for port 0D, timer 1 output, serial data input, serial data output, and serial clock input/output <ul style="list-style-type: none"> <li>• Pull-up resistor incorporation specified by program bit by bit</li> <li>• Withstand voltage is V<sub>DD</sub> (Max.).</li> <li>• P0D<sub>3</sub> - P0D<sub>0</sub> <ul style="list-style-type: none"> <li>• 4-bit input/output port</li> <li>• Input/output setting allowed bit by bit</li> </ul> </li> <li>• TM1OUT               <ul style="list-style-type: none"> <li>• Timer 1 output</li> </ul> </li> </ul> | N-ch open drain | Input (P0D)               |

| 20      | P0D <sub>2</sub> /SI     | <ul style="list-style-type: none"> <li>• SI                   <ul style="list-style-type: none"> <li>• Serial data input</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                           |

| 21      | P0D <sub>1</sub> /SO     | <ul style="list-style-type: none"> <li>• SO                   <ul style="list-style-type: none"> <li>• Serial data output</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                           |

| 22      | P0D <sub>0</sub> /SCK    | <ul style="list-style-type: none"> <li>• SCK                   <ul style="list-style-type: none"> <li>• Serial clock input/output</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |                 |                           |

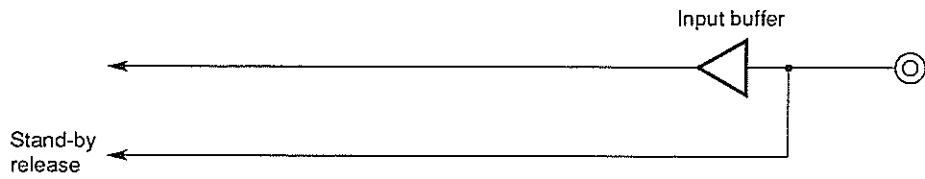

| 23      | P0F <sub>0</sub> /RLS    | Pin for port 0F and input for standby mode release signal <ul style="list-style-type: none"> <li>• P0F<sub>0</sub> <ul style="list-style-type: none"> <li>• Bit 0 of 2-bit input port P0F</li> </ul> </li> <li>• RLS               <ul style="list-style-type: none"> <li>• Input for standby mode release signal</li> </ul> </li> </ul>                                                                                                                                                                                                                         | Input           | Input (P0F <sub>0</sub> ) |

| 24      | INT                      | Input for an external interrupt request signal and standby mode release signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input           | Input                     |

| 25      | RESET                    | System reset input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input           | Input                     |

| 26      | X <sub>OUT</sub>         | For system clock oscillation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —               | —                         |

| 27      | X <sub>IN</sub>          | The ceramic resonator is connected between X <sub>IN</sub> and X <sub>OUT</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —               | —                         |

| 28      | GND                      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —               | —                         |

## 1.2 PROGRAM MEMORY WRITE/VERIFY MODE

| Pin No.       | Pin name                                 | Function                                                                                                   | Input/output |

|---------------|------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------|

| 1             | V <sub>DD</sub>                          | Power supply pin.<br>+6 V is applied to this pin when writing to program memory or verifying its contents. | -            |

| 3<br>to<br>6  | MD <sub>3</sub><br>to<br>MD <sub>0</sub> | Input pins that select an operation mode when writing to program memory or verifying its contents          | Input        |

| 7<br>to<br>14 | D <sub>7</sub><br>to<br>D <sub>0</sub>   | Input/output pins for 8-bit data used when writing to program memory or verifying its contents             | Input/output |

| 23            | V <sub>PP</sub>                          | Voltage (+12.5 V) is applied to this pin when writing to program memory or verifying its contents.         | -            |

| 27            | CLK                                      | Input pin for address update clocks used when writing to program memory or verifying its contents          | Input        |

| 28            | GND                                      | Ground                                                                                                     | -            |

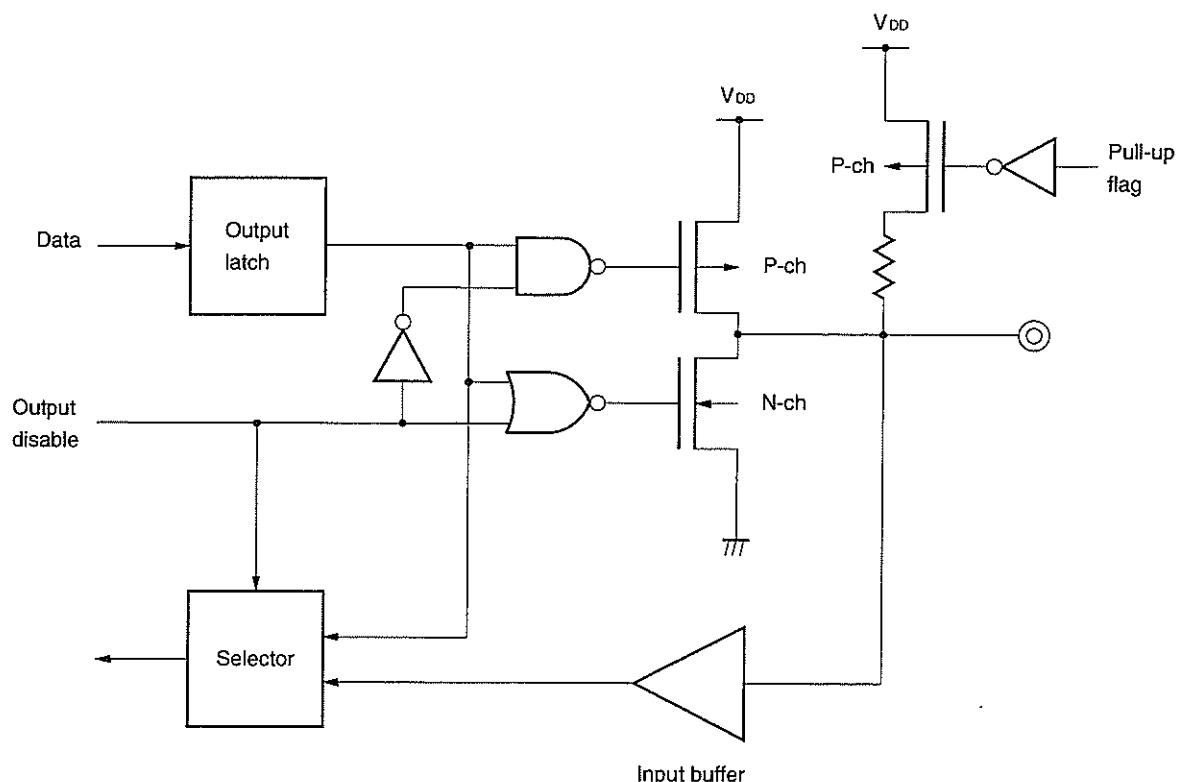

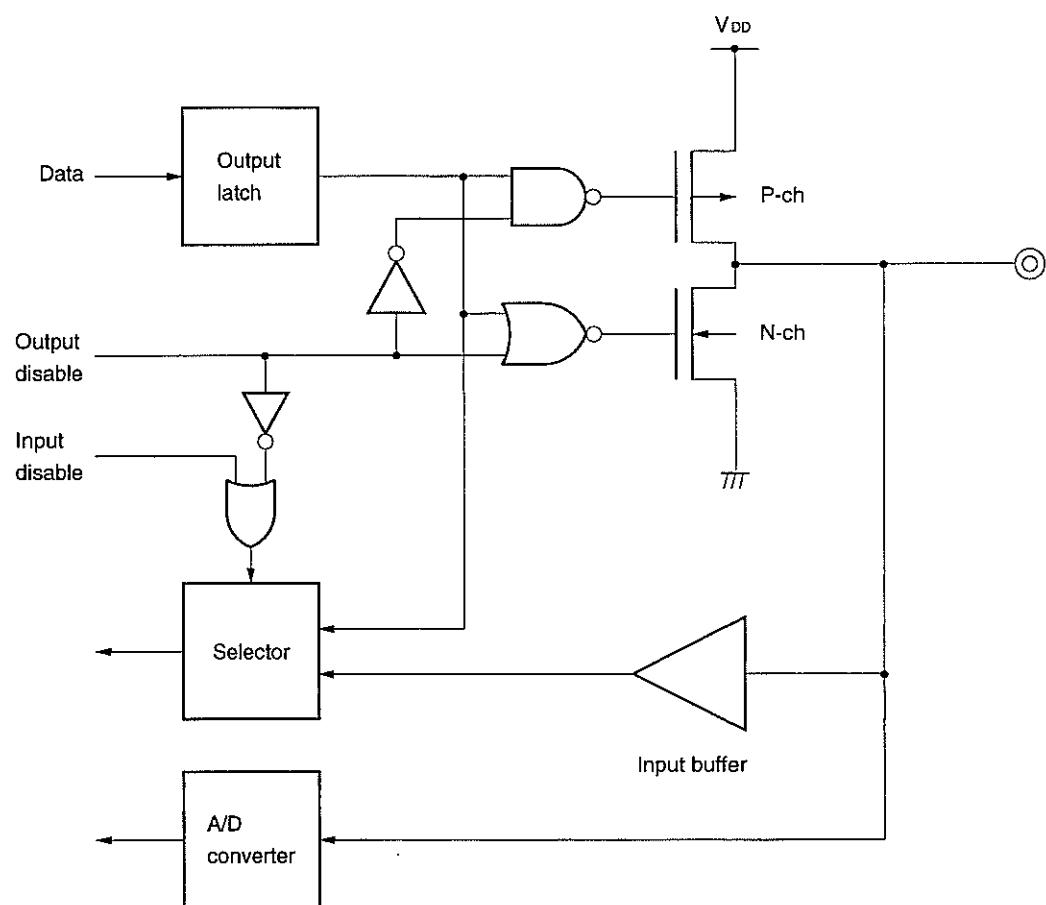

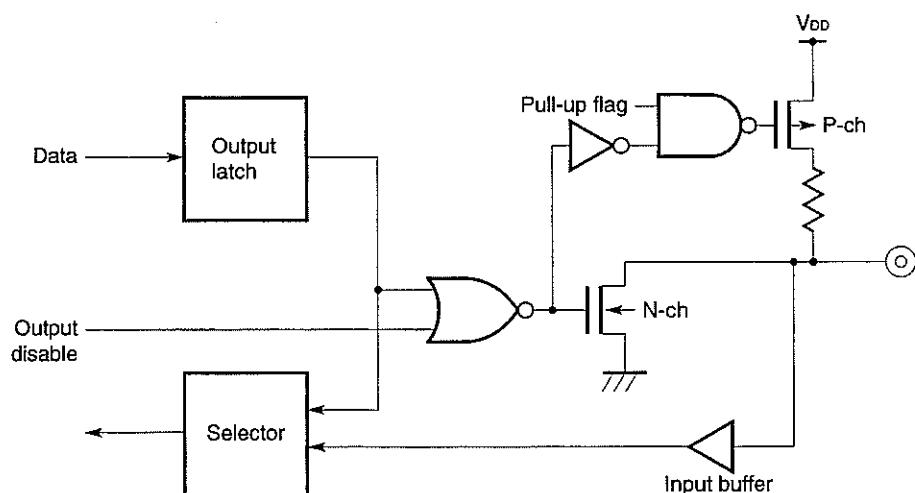

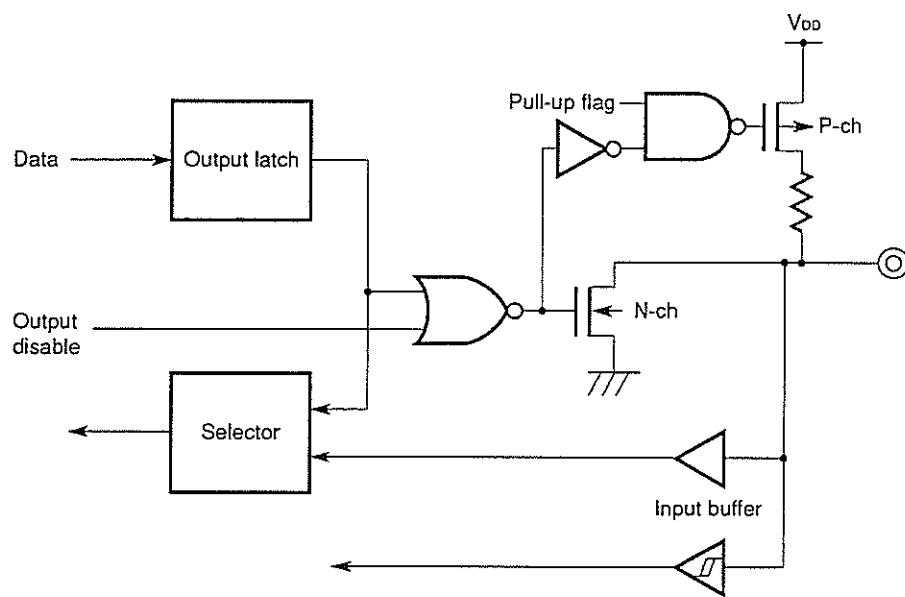

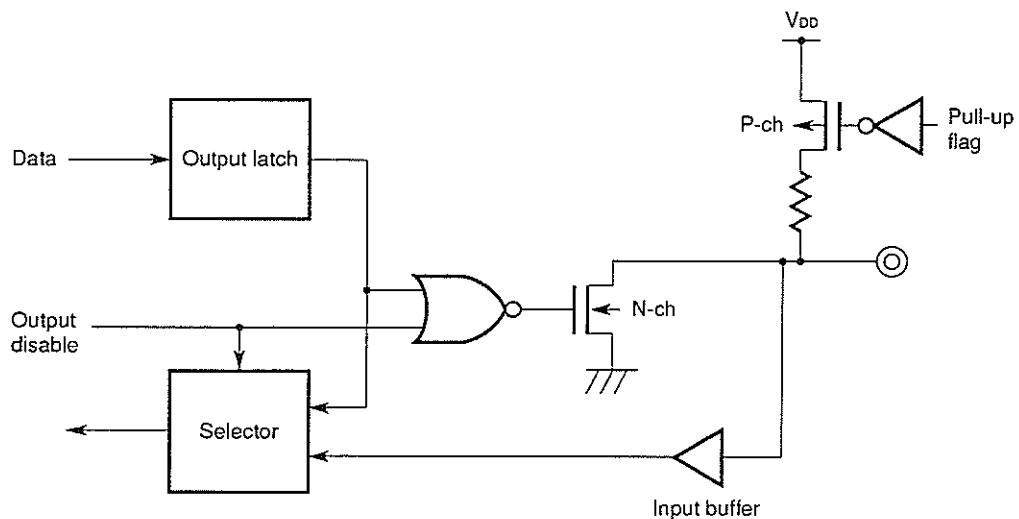

### 1.3 EQUIVALENT INPUT/OUTPUT CIRCUITS

Below are simplified diagrams of the input/output circuits for each pin.

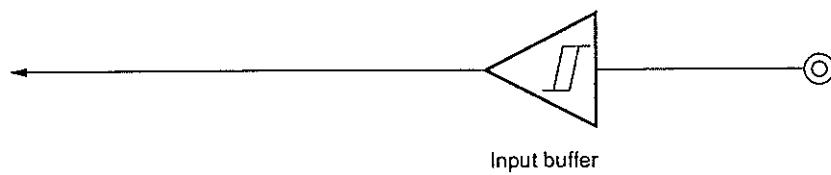

#### (1) P0A<sub>0</sub> - P0A<sub>3</sub>, P0B<sub>0</sub> - P0B<sub>3</sub>

(2)  $P0C_0/ADC_0 - P0C_3/ADC_3$

(3) P0D<sub>3</sub>/TM1OUT, P0D<sub>1</sub>/SO

(4) P0D<sub>2</sub>/SI, P0D<sub>0</sub>/SCK(5) P0E<sub>0</sub> - P0E<sub>3</sub>(6) P0F<sub>0</sub>/RLS

(7)  $P0F_1/V_{REF}$ (8)  $\overline{RESET}$ ,  $INT$

#### 1.4 HANDLING UNUSED PINS

Connect unused pins at the normal operation mode as follows:

Table 1-1 Handling Unused Pins

| Pin                      |             |                                    | Conditions and handling                                                              |                                                                                        |

|--------------------------|-------------|------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                          |             |                                    | Internal                                                                             | External                                                                               |

| Port                     | Input mode  | P0A, P0B, P0D, P0E                 | Pull-up resistors that can be specified with the software are incorporated.          | Leave open.                                                                            |

|                          |             | P0C                                | —                                                                                    | Connect to V <sub>DD</sub> or ground through resistors for each pin. <sup>Note 1</sup> |

|                          |             | P0F <sub>1</sub>                   | —                                                                                    | Connect directly to V <sub>DD</sub> or ground.                                         |

|                          |             | P0F <sub>0</sub> <sup>Note 2</sup> | —                                                                                    | Connect directly to ground.                                                            |

| Port                     | Output mode | P0A, P0B, P0C (CMOS ports)         | —                                                                                    | Leave open.                                                                            |

|                          |             | P0D (N-ch open-drain port)         | Outputs low level.                                                                   |                                                                                        |

|                          |             | P0E (N-ch open-drain port)         | Outputs low level without pull-up resistors that can be specified with the software. |                                                                                        |

|                          |             |                                    | Outputs low level with pull-up resistors that can be specified with the software.    |                                                                                        |

| External interrupt (INT) |             |                                    | —                                                                                    | Connect directly to V <sub>DD</sub> or ground.                                         |

**Notes 1.** When a pin is pulled up to V<sub>DD</sub> (connected to V<sub>DD</sub> through a resistor) or pulled down to ground (connected to ground through a resistor) outside the chip, take the driving capacity and maximum current consumption of a port into consideration. When using high-resistance pull-up or pull-down resistors, apply appropriate countermeasures to ensure that noise is not attracted by the resistors. Although the optimum pull-up or pull-down resistor varies with the application circuit, in general, a resistor of 10 to 100 kilohms is suitable.

**2.** Since the P0F<sub>0</sub>/RLS pin is also used as the V<sub>PP</sub> pin for writing and verifying the program memory, connect directly to ground when the pin is not used.

**Caution** To fix the I/O mode, pull-up resistors that can be specified with the software, and output level of a pin, it is recommended that they should be specified repeatedly within a loop in a program.

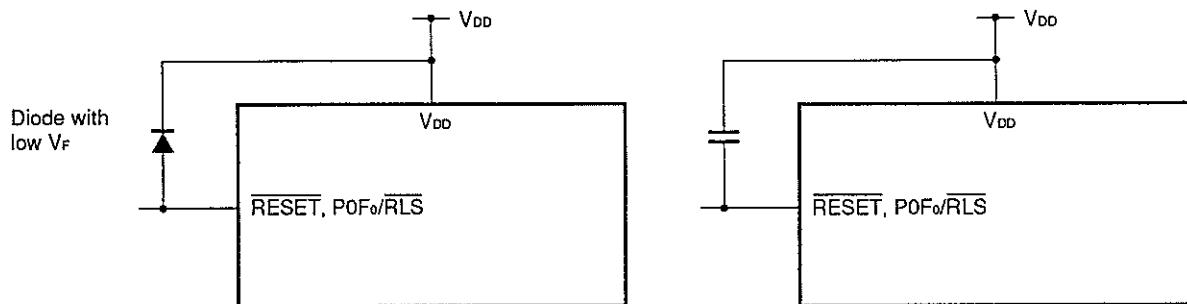

### 1.5 NOTES ON USE OF THE RESET AND P0F<sub>0</sub>/RLS PINS (ONLY AT THE NORMAL OPERATION MODE)

The RESET pin can be used as the test mode selection pin for testing the internal operation of the μPD17P149 (IC test), besides the usage shown in Section 1.1.

The P0F<sub>0</sub>/RLS pin can be used as the V<sub>PP</sub> pin in the program memory write/verify mode.

Applying a voltage exceeding V<sub>DD</sub> to the RESET or P0F<sub>0</sub>/RLS pin causes the μPD17P149 to enter the test mode or program memory write/verify mode. When noise exceeding V<sub>DD</sub> comes in during normal operation, the device may not operate normally.

For example, if the wiring from the RESET or P0F<sub>0</sub>/RLS pin is too long, noise may be induced on the wiring, causing this mode switching.

When installing the wiring, lay the wiring in such a way that noise is suppressed as much as possible. If noise yet arises, use an external part to suppress it as shown below.

- Connect a diode with low  $V_F$  between the pin and  $V_{DD}$ .

- Connect a capacitor between the pin and  $V_{DD}$ .

## 2. DIFFERENCES BETWEEN THE μPD17145, μPD17147, μPD17149, AND μPD17P149

The μPD17P149 is a one-time PROM version of the μPD17149, in which the internal mask ROM is replaced with a one-time PROM.

Table 2-1 lists the differences between the μPD17145, μPD17147, μPD17149, and μPD17P149.

The μPD17P149 has the same CPU functions and internal peripheral hardwares as those of μPD17145, μPD17147, and μPD17149 except for its program memory, program size, address register size, and mask option.

Part of electrical characteristics is also different between those products. For details of the electrical characteristics, refer to the data sheet of each product.

**Table 2-1 Differences between the μPD17145, μPD17147, μPD17149, and μPD17P149**

| Item                                                 | μPD17145                                                                                          | μPD17147                                                             | μPD17149                                                             | μPD17P149    |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|--------------|

| Program memory (ROM)                                 | Masked ROM                                                                                        |                                                                      | One-time PROM                                                        |              |

|                                                      | 1024 × 16 bits<br>(0000H-03FFH)                                                                   |                                                                      | 2048 × 16 bits<br>(0000H-07FFH)                                      |              |

| Program counter (PC)                                 | 10 bits                                                                                           |                                                                      | 11 bits                                                              |              |

| Address register (AR)                                |                                                                                                   |                                                                      |                                                                      |              |

| Address stack register                               |                                                                                                   |                                                                      |                                                                      |              |

| Pull-up resistors of P0F, RESET, and INT pins        | Mask option                                                                                       |                                                                      |                                                                      | Not provided |

| Internal POC circuit                                 | Mask option                                                                                       |                                                                      |                                                                      | Not provided |

| V <sub>PP</sub> pin and operating mode selection pin | Not provided                                                                                      |                                                                      |                                                                      | Provided     |

| Quality grade                                        | • Standard<br>μPD17145<br>• Special<br>μPD17145 (A)<br>μPD17145 (A1)                              | • Standard<br>μPD17147<br>• Special<br>μPD17147 (A)<br>μPD17147 (A1) | • Standard<br>μPD17149<br>• Special<br>μPD17147 (A)<br>μPD17147 (A1) | Standard     |

| Electrical characteristics                           | Partially differs between these products.<br>Refer to the data sheet of each product for details. |                                                                      |                                                                      |              |

**Caution** Although a PROM product is highly compatible with a mask ROM product in respect of functions, they differ in internal ROM circuits and part of electrical characteristics. Before changing the PROM product to the mask ROM product in an application system, evaluate the system carefully using the mask ROM product.

### 3. WRITING TO AND VERIFYING ONE-TIME PROM (PROGRAM MEMORY)

The μPD17P149's internal program memory consists of a  $4096 \times 16$  bit one-time PROM.

Writing to the one-time PROM or verifying the contents of the PROM is accomplished using the pins shown in Table 3-1. Note that address inputs are not used; instead, the address is updated using the clock input from the CLK pin.

**Caution** The  $\overline{P0F_0/RLS/V_{PP}}$  pin is used as the  $V_{PP}$  pin when writing to program memory or verifying its contents. If a voltage equal to or more than  $V_{DD} + 0.3$  V is applied to the  $\overline{P0F_0/RLS}$  pin in normal operation mode, the microcontroller may cause a system crash. Protect the pins from high voltages.

Table 3-1 Pins Used When Writing to Program Memory or Verifying Its Contents

| Pin           | Function                                                                                                            |

|---------------|---------------------------------------------------------------------------------------------------------------------|

| $V_{PP}$      | Pin for applying programming supply voltage.<br>Voltage (+12.5 V) is applied to this pin.                           |

| $V_{DD}$      | Positive power supply pin.<br>+6 V is applied to this pin.                                                          |

| CLK           | Input pin for address update clocks.<br>Input of four pulses to this pin updates the address of the program memory. |

| $MD_0 - MD_3$ | Input pins that select an operation mode                                                                            |

| $D_0 - D_7$   | Input/output pins for 8-bit data                                                                                    |

#### 3.1 PROGRAM MEMORY WRITE/VERIFY MODES

If +6 V is applied to the  $V_{DD}$  pin and +12.5 V is applied to the  $V_{PP}$  pin after a certain duration of reset status ( $V_{DD} = 5$  V,  $\overline{RESET} = 0$  V), the μPD17P149 enters program memory write/verify mode. A specific operating mode is then selected by setting the  $MD_0$  through  $MD_3$  pins as follows. The  $X_{OUT}$  pin must be left open. Connect each pin not listed in Table 3-1 (including the  $\overline{RESET}$  pin) to ground through a resistor.

Table 3-2 Specification of Operating Modes

| Operating mode specification |          |        |        |        |        | Operating mode                    |

|------------------------------|----------|--------|--------|--------|--------|-----------------------------------|

| $V_{PP}$                     | $V_{DD}$ | $MD_0$ | $MD_1$ | $MD_2$ | $MD_3$ |                                   |

| +12.5 V                      | +6 V     | H      | L      | H      | L      | Program memory address clear mode |

|                              |          | L      | H      | H      | H      | Write mode                        |

|                              |          | L      | L      | H      | H      | Verify mode                       |

|                              |          | H      | x      | H      | H      | Program inhibit mode              |

**Remark** x: Don't care. L (low) or H (high)

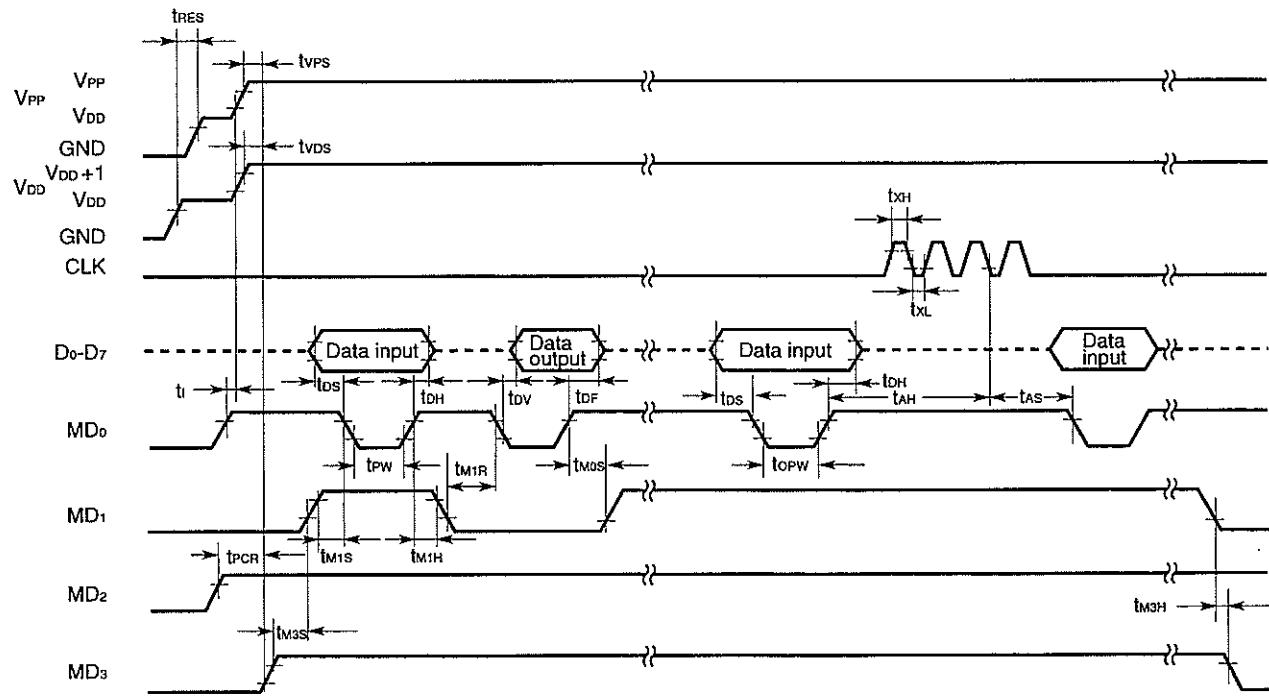

### 3.2 WRITING TO PROGRAM MEMORY

The procedure for writing to program memory is described below.

- (1) Connect all unused pins to GND through resistors (the X<sub>OUT</sub> pin is left open). Apply a low-level signal to the CLK pin.

- (2) Apply 5 V to V<sub>DD</sub> and apply a low-level signal to the V<sub>PP</sub> pin.

- (3) Wait 10  $\mu$ s. Then apply 5 V to V<sub>PP</sub>.

- (4) Set the mode selection pins to program memory address clear mode.

- (5) Apply 6 V to V<sub>DD</sub> and 12.5 V to V<sub>PP</sub>.

- (6) Select program inhibit mode.

- (7) Write data in 1-ms write mode.

- (8) Select program inhibit mode.

- (9) Select verify mode. If the write operation is found successful, proceed to step (10). If the operation is found unsuccessful, repeat steps (7) to (9).

- (10) Perform additional write for X (number of repetitions of steps (7) to (9))  $\times$  1 ms.

- (11) Select program inhibit mode.

- (12) Increment the program memory address by one on reception of four pulses on the CLK pin.

- (13) Repeat steps (7) to (12) until the last address is reached.

- (14) Select program memory address clear mode.

- (15) Apply 5 V to the V<sub>DD</sub> and V<sub>PP</sub> pins.

- (16) Turn power off.

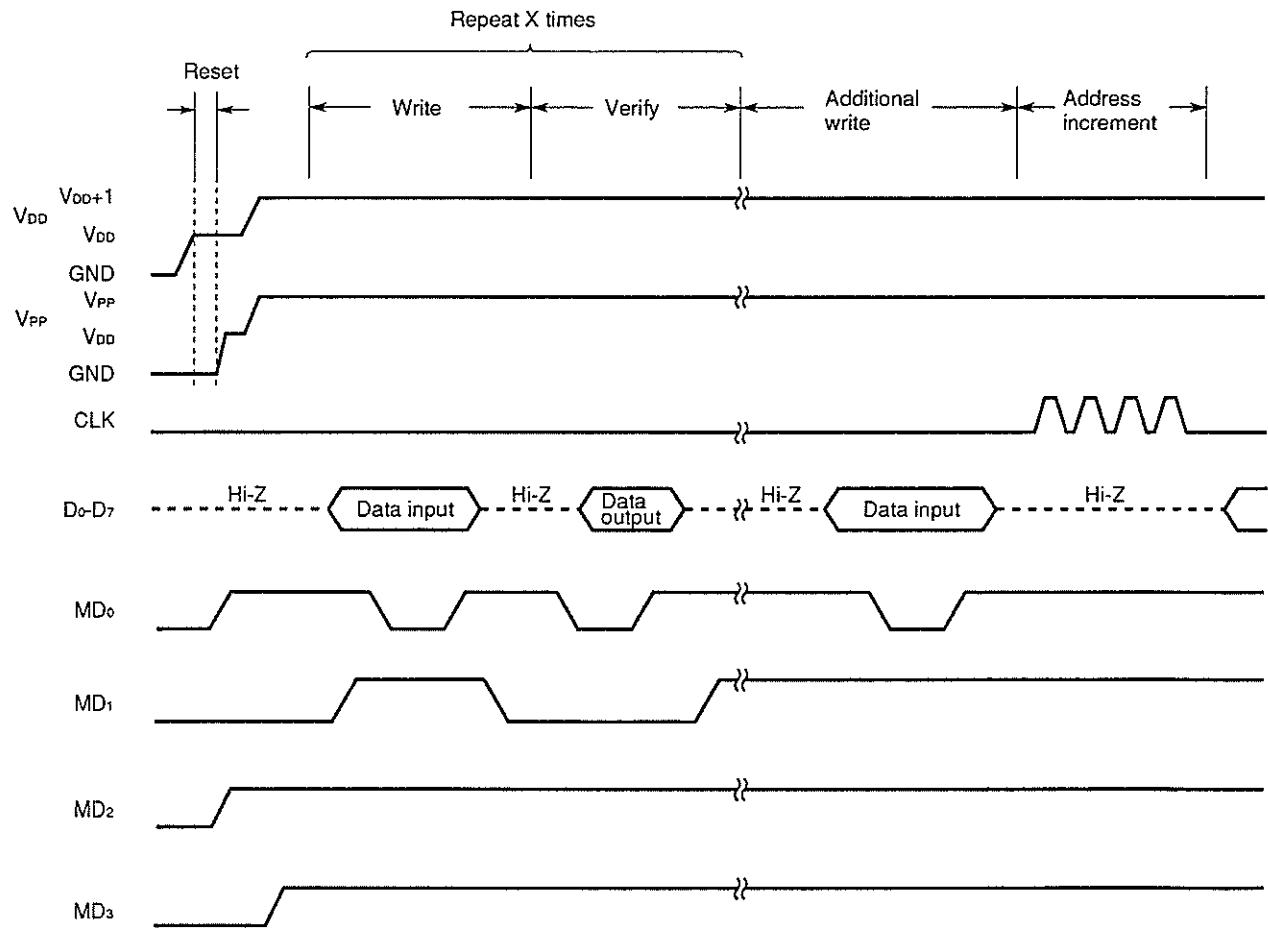

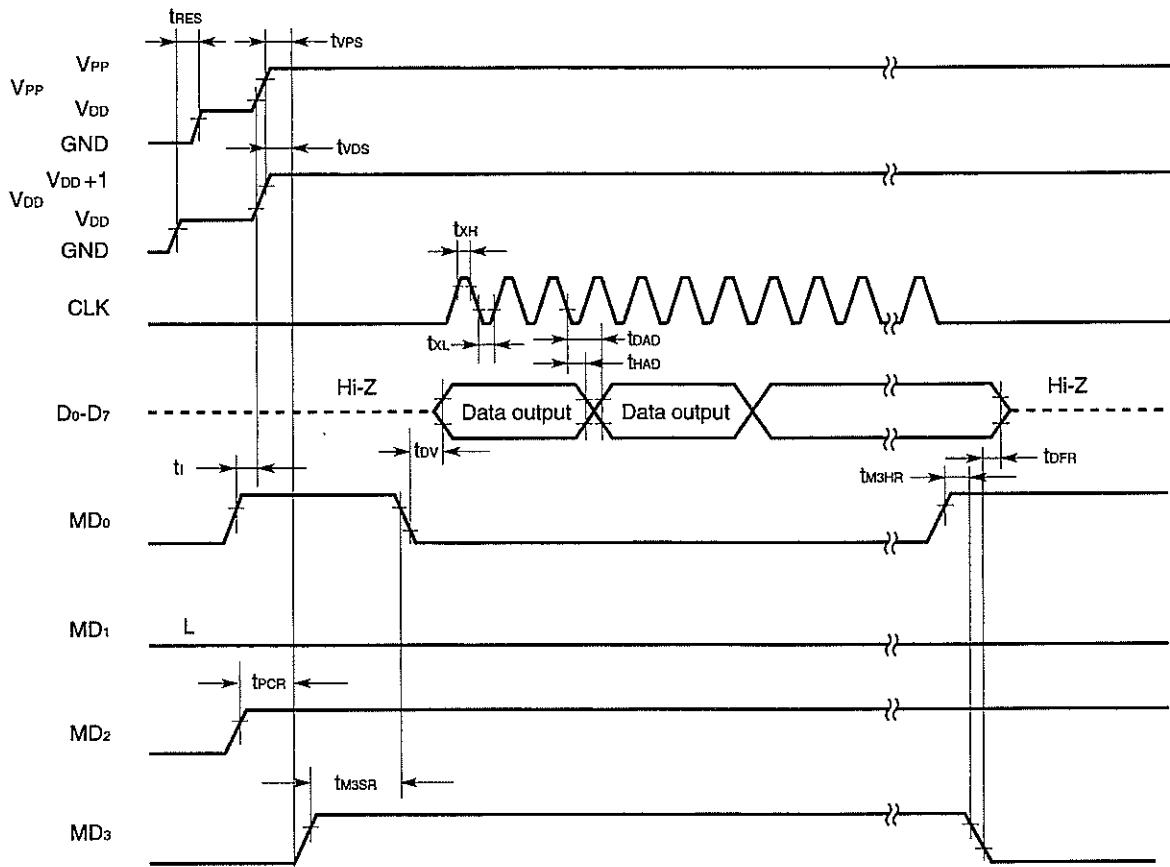

A timing chart for program memory writing steps (2) to (12) is shown in Fig. 3-1.

Fig. 3-1 Timing Chart for Program Memory Writing Steps

### 3.3 READING PROGRAM MEMORY

- (1) Connect all unused pins to GND through resistors (the X<sub>out</sub> pin is left open). Apply a low-level signal to the CLK pin.

- (2) Apply 5 V to V<sub>DD</sub> and apply a low-level signal to the V<sub>PP</sub> pin.

- (3) Wait 10  $\mu$ s. Then apply 5 V to V<sub>PP</sub>.

- (4) Set the mode selection pins to program memory address clear mode.

- (5) Apply 6 V to V<sub>DD</sub> and 12.5 V to V<sub>PP</sub>.

- (6) Select program inhibit mode.

- (7) Select verify mode. Data is output sequentially one address at a time for every four input clock pulses on the CLK.

- (8) Select program inhibit mode.

- (9) Select program memory address clear mode.

- (10) Apply 5 V to the V<sub>DD</sub> and V<sub>PP</sub> pins.

- (11) Turn power off.

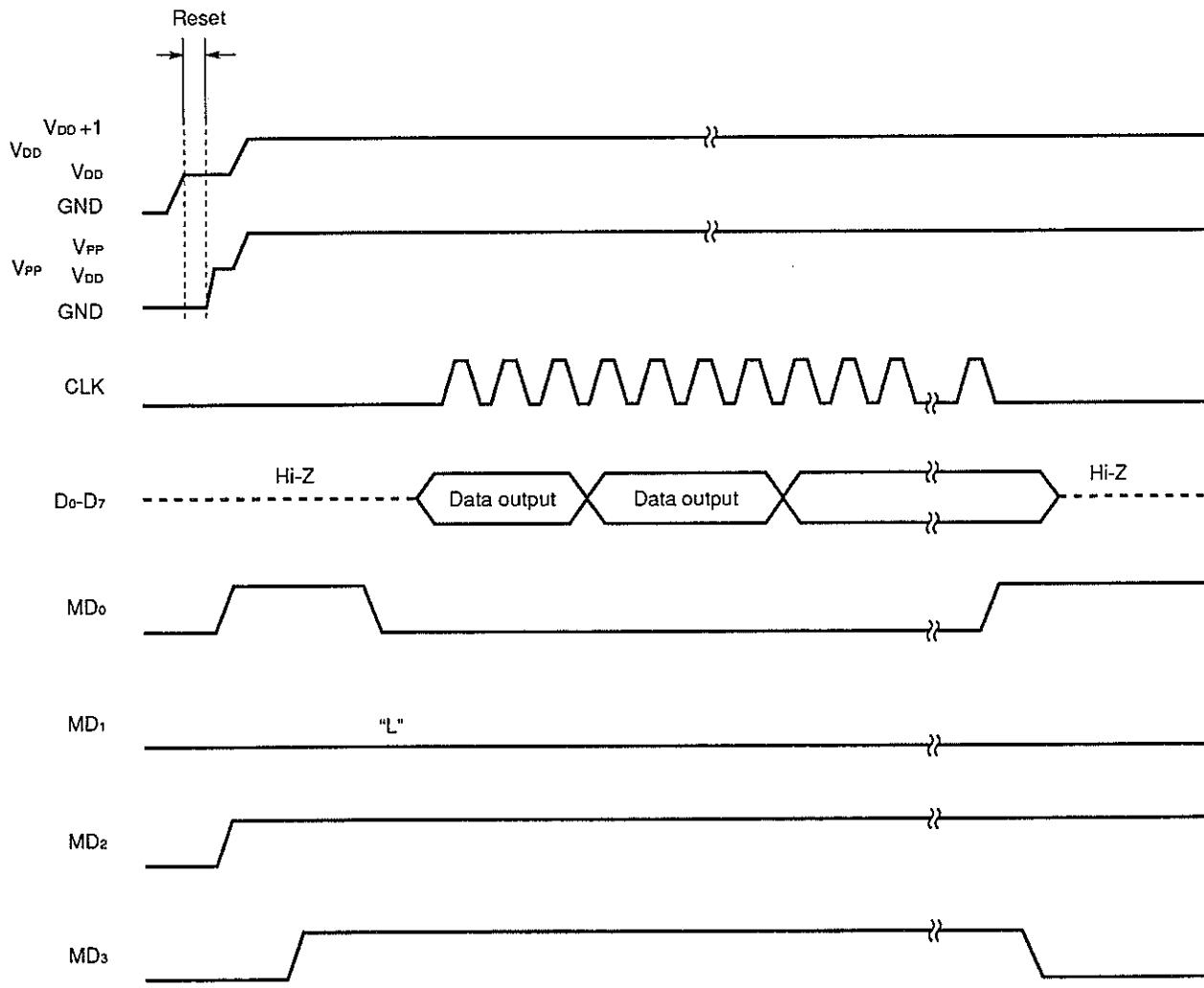

A timing chart for program memory reading steps (2) to (9) is shown below.

★ Fig. 3-2 Timing Chart for Program Memory Reading Steps

## 4. ELECTRICAL CHARACTERISTICS

ABSOLUTE MAXIMUM RATINGS ( $T_A = 25^\circ\text{C}$ )

| Parameter                       | Symbol                   | Conditions                                             |  | Rated value               | Unit             |    |

|---------------------------------|--------------------------|--------------------------------------------------------|--|---------------------------|------------------|----|

| Supply voltage                  | $V_{DD}$                 |                                                        |  | −0.3 to +7.0              | V                |    |

| PROM supply voltage             | $V_{PP}$                 |                                                        |  | −0.3 to +13.5             | V                |    |

| A/D converter reference voltage | $V_{REF}$                |                                                        |  | −0.3 to $V_{DD} + 0.3$    | V                |    |

| Input voltage                   | $V_I$                    | P0A, P0B, P0C, P0D, P0E, P0F, INT, RESET, and $X_{IN}$ |  | −0.3 to $V_{DD} + 0.3$    | V                |    |

| Output voltage                  | $V_O$                    |                                                        |  | −0.3 to $V_{DD} + 0.3$    | V                |    |

| High-level output current       | $I_{OH}$ <sup>Note</sup> | Each of P0A, P0B, and P0C pins                         |  | Peak value                | −15              | mA |

|                                 |                          |                                                        |  | rms                       | −7.5             | mA |

|                                 |                          | Total of P0A, P0B, and P0C pins                        |  | Peak value                | −30              | mA |

|                                 |                          |                                                        |  | rms                       | −15              | mA |

| Low-level output current        | $I_{OL}$ <sup>Note</sup> | Each of P0A, P0B, and P0C                              |  | Peak value                | 15               | mA |

|                                 |                          |                                                        |  | rms                       | 7.5              | mA |

|                                 |                          | Each of P0D and P0E                                    |  | Peak value                | 30               | mA |

|                                 |                          |                                                        |  | rms                       | 15               | mA |

|                                 |                          | Total of P0A, P0B, P0C, P0D, and P0E pins              |  | Peak value                | 100              | mA |

|                                 |                          |                                                        |  | rms                       | 50               | mA |

| Operating ambient temperature   | $T_A$                    |                                                        |  | −40 to +85                | $^\circ\text{C}$ |    |

| Storage temperature             | $T_{STG}$                |                                                        |  | −65 to +150               | $^\circ\text{C}$ |    |

| Allowable dissipation           | $P_d$                    | $T_A = 85^\circ\text{C}$                               |  | 28-pin plastic shrink DIP | 140              | mW |

|                                 |                          |                                                        |  | 28-pin plastic SOP        | 85               | mW |

**Note** Calculate a root-mean-square value as follows: [rms value] = [peak value]  $\times \sqrt{\text{duty}}$ .

**Caution** Absolute maximum ratings are rated values beyond which some physical damages may be caused to the product; if any of the parameters in the table above exceeds its rated value even for a moment, the quality of the product may deteriorate. Be sure to use the product within the rated values.

RECOMMENDED POWER VOLTAGE RANGE ( $T_A = −40$  to  $+85^\circ\text{C}$ )

| Parameter      | Symbol   | Conditions                    |                                                                                      | Min. | Typ. | Max. | Unit |

|----------------|----------|-------------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| Supply voltage | $V_{DD}$ | CPU<br>(except A/D converter) | $f_x = 400\text{ kHz to } 2\text{ MHz}$                                              | 2.7  |      | 5.5  | V    |

|                |          |                               | $f_x = 400\text{ kHz to } 4\text{ MHz}$                                              | 3.6  |      | 5.5  | V    |

|                |          |                               | $f_x = 400\text{ kHz to } 8\text{ MHz}$                                              | 4.5  |      | 5.5  | V    |

|                |          | A/D converter                 | Absolute accuracy: $\pm 1.5\text{ LSB}$ ,<br>$2.5\text{ V} \leq V_{REF} \leq V_{DD}$ | 4.0  |      | 5.5  | V    |

DC CHARACTERISTICS (V<sub>DD</sub> = 2.7 to 5.5 V, T<sub>A</sub> = -40 to +85 °C)

| Parameter                             | Symbol            | Conditions                                                                        |                                                          | Min.                       | Typ. | Max.               | Unit |

|---------------------------------------|-------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------|------|--------------------|------|

| High-level input voltage              | V <sub>IH1</sub>  | P0A, P0B, P0C, P0D, P0E, and P0F                                                  |                                                          | 0.7V <sub>DD</sub>         |      | V <sub>DD</sub>    | V    |

|                                       | V <sub>IH2</sub>  | RESET, SCK, SI, and INT                                                           |                                                          | 0.8V <sub>DD</sub>         |      | V <sub>DD</sub>    | V    |

|                                       | V <sub>IH3</sub>  | X <sub>IN</sub>                                                                   |                                                          | V <sub>DD</sub> - 0.5      |      | V <sub>DD</sub>    | V    |

| Low-level input voltage               | V <sub>IL1</sub>  | P0A, P0B, P0C, P0D, P0E, and P0F                                                  |                                                          | 0                          |      | 0.3V <sub>DD</sub> | V    |

|                                       | V <sub>IL2</sub>  | RESET, SCK, SI, and INT                                                           |                                                          | 0                          |      | 0.2V <sub>DD</sub> | V    |

|                                       | V <sub>IL3</sub>  | X <sub>IN</sub>                                                                   |                                                          | 0                          |      | 0.4                | V    |

| High-level output voltage             | V <sub>OH</sub>   | P0A, P0B, and P0C                                                                 | 4.5 ≤ V <sub>DD</sub> ≤ 5.5<br>I <sub>OH</sub> = -1.0 mA | V <sub>DD</sub> - 0.3      |      |                    | V    |

|                                       |                   |                                                                                   | 2.7 ≤ V <sub>DD</sub> < 4.5<br>I <sub>OH</sub> = -0.5 mA | V <sub>DD</sub> - 0.3      |      |                    | V    |

| Low-level output voltage              | V <sub>OL1</sub>  | P0A, P0B, P0C, P0D, and P0E                                                       | 4.5 ≤ V <sub>DD</sub> ≤ 5.5<br>I <sub>OL</sub> = 1.0 mA  |                            |      | 0.3                | V    |

|                                       |                   |                                                                                   | 2.7 ≤ V <sub>DD</sub> < 4.5<br>I <sub>OL</sub> = 0.5 mA  |                            |      | 0.3                | V    |

|                                       | V <sub>OL2</sub>  | P0D and P0E<br>I <sub>OL</sub> = 15 mA                                            | 4.5 ≤ V <sub>DD</sub> ≤ 5.5                              |                            |      | 1.0                | V    |

|                                       |                   |                                                                                   | 2.7 ≤ V <sub>DD</sub> < 4.5                              |                            |      | 2.0                | V    |

| ★<br>High-level input leakage current | I <sub>LIH</sub>  | P0A, P0B, P0C, P0D, P0E, P0F, RESET, and INT<br>V <sub>IN</sub> = V <sub>DD</sub> |                                                          |                            |      | 3                  | μA   |

| ★<br>Low-level input leakage current  | I <sub>LIL</sub>  | P0A, P0B, P0C, P0D, P0E, P0F, RESET, and INT<br>V <sub>IN</sub> = 0 V             |                                                          |                            |      | -3                 | μA   |

| High-level output leakage current     | I <sub>LOH</sub>  | P0A, P0B, P0C, P0D, and P0E<br>V <sub>OUT</sub> = V <sub>DD</sub>                 |                                                          |                            |      | 3                  | μA   |

| Low-level output leakage current      | I <sub>LOL</sub>  | P0A, P0B, P0C, P0D, and P0E<br>V <sub>OUT</sub> = 0 V                             |                                                          |                            |      | -3                 | μA   |

| Built-in pull-up resistance<br>Note 1 | R <sub>PULL</sub> | P0A, P0B, and P0E                                                                 |                                                          | 50                         | 100  | 200                | kΩ   |

|                                       |                   | P0D                                                                               |                                                          | 3                          | 10   | 30                 | kΩ   |

| Power supply current<br>Note 2        | I <sub>DD1</sub>  | Normal operation mode                                                             | fx = 8.0 MHz, V <sub>DD</sub> = 5 V ±10%                 |                            | 5.5  | 8.0                | mA   |

|                                       |                   |                                                                                   | fx = 4.0 MHz, V <sub>DD</sub> = 5 V ±10%                 |                            | 3.3  | 5.5                | mA   |

|                                       |                   |                                                                                   | fx = 2.0 MHz, V <sub>DD</sub> = 3 V ±10%                 |                            | 1.0  | 2.5                | mA   |

|                                       |                   |                                                                                   | fx = 400 kHz                                             | V <sub>DD</sub> = 5 V ±10% | 2.0  | 4.7                | mA   |

|                                       |                   |                                                                                   |                                                          | V <sub>DD</sub> = 3 V ±10% | 0.7  | 2.4                | mA   |

|                                       | I <sub>DD2</sub>  | HALT mode                                                                         | fx = 8.0 MHz, V <sub>DD</sub> = 5 V ±10%                 |                            | 3.5  | 5.0                | mA   |

|                                       |                   |                                                                                   | fx = 4.0 MHz, V <sub>DD</sub> = 5 V ±10%                 |                            | 2.7  | 4.1                | mA   |

|                                       |                   |                                                                                   | fx = 2.0 MHz, V <sub>DD</sub> = 3 V ±10%                 |                            | 0.8  | 2.0                | mA   |

|                                       |                   |                                                                                   | fx = 400 kHz                                             | V <sub>DD</sub> = 5 V ±10% | 1.8  | 3.8                | mA   |

|                                       |                   |                                                                                   |                                                          | V <sub>DD</sub> = 3 V ±10% | 0.6  | 2.2                | mA   |

|                                       | I <sub>DD3</sub>  | STOP mode                                                                         | V <sub>DD</sub> = 5 V ±10%                               |                            | 12   | 50                 | μA   |

|                                       |                   |                                                                                   | V <sub>DD</sub> = 3 V ±10%                               |                            | 10   | 45                 | μA   |

Notes 1. Pull-up resistors are not incorporated for the P0F, RESET, and INT pins.

2. This current excludes the current which flows through the A/D converter and built-in pull-up resistors.

AC CHARACTERISTICS ( $V_{DD} = 2.7$  to  $5.5$  V,  $T_A = -40$  to  $+85$  °C)

| Parameter                                              | Symbol                     | Conditions                | Min. | Typ. | Max. | Unit    |

|--------------------------------------------------------|----------------------------|---------------------------|------|------|------|---------|

| CPU clock cycle time<br>(instruction execution time)   | $t_{CY}$                   | $V_{DD} = 4.5$ to $5.5$ V | 1.9  |      | 41   | $\mu$ s |

|                                                        |                            | $V_{DD} = 3.6$ to $5.5$ V | 3.9  |      | 41   | $\mu$ s |

|                                                        |                            |                           | 7.9  |      | 41   | $\mu$ s |

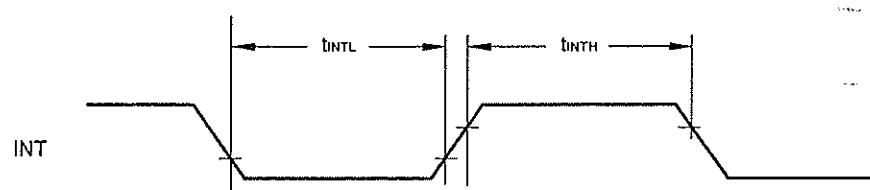

| INT input frequency (TM0<br>count clock input)         | $f_{INT}$                  |                           | 0    |      | 400  | kHz     |

| INT high/low level width<br>(external interrupt input) | $t_{INTL}$ ,<br>$t_{INTH}$ | $V_{DD} = 4.5$ to $5.5$ V | 10   |      |      | $\mu$ s |

|                                                        |                            |                           | 50   |      |      | $\mu$ s |

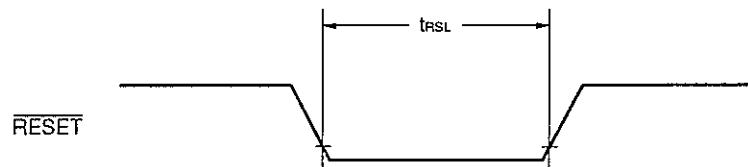

| RESET low-level width                                  | $t_{RSL}$                  | $V_{DD} = 4.5$ to $5.5$ V | 10   |      |      | $\mu$ s |

|                                                        |                            |                           | 50   |      |      | $\mu$ s |

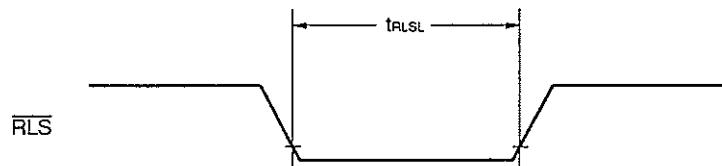

| $\overline{RLS}$ low-level width                       | $t_{RLSL}$                 | $V_{DD} = 4.5$ to $5.5$ V | 10   |      |      | $\mu$ s |

|                                                        |                            |                           | 50   |      |      | $\mu$ s |

Remark  $t_{CY} = 16/f_x$  ( $f_x$ : frequency of system clock oscillator)

## Interrupt input timing

## RESET input timing

$\overline{RLS}$  input timing

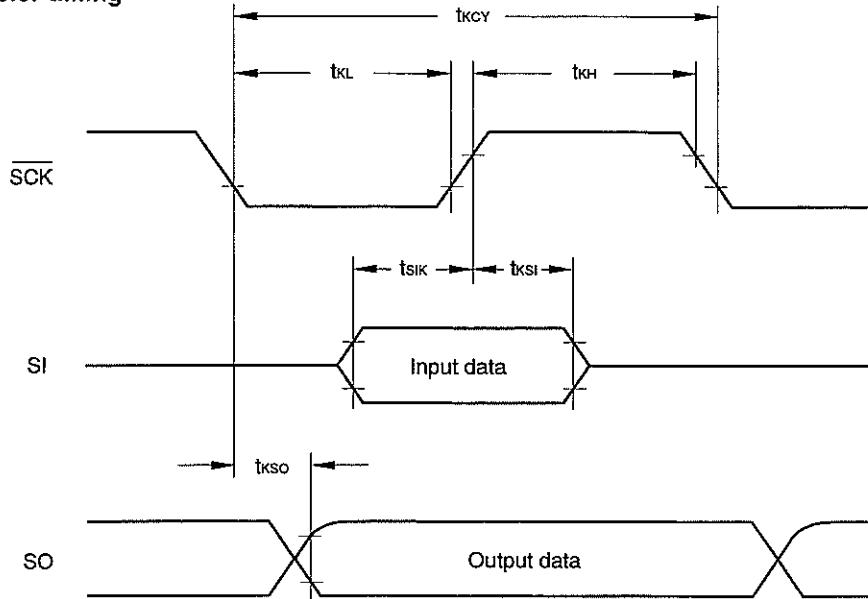

SERIAL TRANSFER OPERATION ( $V_{DD} = 2.7$  to  $5.5$  V,  $T_A = -40$  to  $+85$  °C)

| Parameter                                                 | Symbol      | Conditions                                   |                              | Min.                      | Typ.         | Max. | Unit |

|-----------------------------------------------------------|-------------|----------------------------------------------|------------------------------|---------------------------|--------------|------|------|

| SCK cycle time                                            | tkcy        | Input                                        | $V_{DD} = 4.5$ to $5.5$ V    | 2.0                       |              |      | μs   |

|                                                           |             |                                              |                              | 10                        |              |      | μs   |

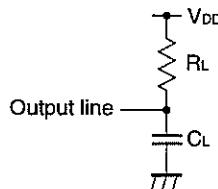

|                                                           |             | Output                                       | $R_L = 1$ kΩ, $C_L = 100$ pF | $V_{DD} = 4.5$ to $5.5$ V | 2.0          |      | μs   |

|                                                           |             |                                              |                              |                           | 8            |      | μs   |

|                                                           |             | Built-in pull-up resistor,<br>$C_L = 100$ pF |                              | $V_{DD} = 4.5$ to $5.5$ V | 32           |      | μs   |

|                                                           |             |                                              |                              |                           | 64           |      | μs   |

| SCK high/low level width                                  | tkh,<br>tkl | Input                                        | $V_{DD} = 4.5$ to $5.5$ V    | 1.0                       |              |      | μs   |

|                                                           |             |                                              |                              | 5.0                       |              |      | μs   |

|                                                           |             | Output                                       | $R_L = 1$ kΩ, $C_L = 100$ pF | $V_{DD} = 4.5$ to $5.5$ V | $tkcy/2-0.6$ |      | μs   |

|                                                           |             |                                              |                              |                           | $tkcy/2-1.2$ |      | μs   |

|                                                           |             | Built-in pull-up resistor,<br>$C_L = 100$ pF |                              | $V_{DD} = 4.5$ to $5.5$ V | $tkcy/2-12$  |      | μs   |

|                                                           |             |                                              |                              |                           | $tkcy/2-24$  |      | μs   |

| SI setup time (with respect to $\overline{SCK}\uparrow$ ) | tsik        |                                              |                              | 100                       |              |      | ns   |

| SI hold time (with respect to $\overline{SCK}\uparrow$ )  | tksi        |                                              |                              | 100                       |              |      | ns   |

| Delay from $\overline{SCK}\downarrow$ to SO               | tkso        | $R_L = 1$ kΩ, $C_L = 100$ pF                 | $V_{DD} = 4.5$ to $5.5$ V    |                           |              | 0.8  | μs   |

|                                                           |             |                                              |                              |                           |              | 1.4  | μs   |

|                                                           |             | Built-in pull-up resistor,<br>$C_L = 100$ pF | $V_{DD} = 4.5$ to $5.5$ V    |                           |              | 14   | μs   |

|                                                           |             |                                              |                              |                           |              | 26   | μs   |

Remark  $R_L$ : a resistive load for the output line $C_L$ : a capacitive load for the output line

## Serial transfer timing

A/D CONVERTER CHARACTERISTICS ( $V_{DD} = 4.5$  to  $5.5$  V,  $T_A = -40$  to  $+85$  °C)

| Parameter                           | Symbol     | Conditions                         | Min. | Typ. | Max.       | Unit    |

|-------------------------------------|------------|------------------------------------|------|------|------------|---------|

| Resolution                          |            |                                    | 8    | 8    | 8          | bit     |

| Absolute accuracy <sup>Note 1</sup> |            | $2.5$ V $\leq V_{REF} \leq V_{DD}$ |      |      | $\pm 1.5$  | LSB     |

| Conversion time <sup>Note 2</sup>   | $t_{CONV}$ |                                    |      |      | $25t_{CY}$ | $\mu$ s |

| Analog signal input voltage         | $V_{ADIN}$ |                                    | 0    |      | $V_{REF}$  | V       |

| Reference input voltage             | $V_{REF}$  |                                    | 2.5  |      | $V_{DD}$   | V       |

| A/D converter circuit current       | $I_{ADC}$  | When A/D converter is operating    |      | 1.0  | 2.0        | mA      |

| $V_{REF}$ pin current               | $I_{REF}$  |                                    |      | 0.1  | 0.3        | mA      |

Notes 1. Absolute accuracy excluding quantization error ( $\pm 0.5$  LSB)

2. Time from conversion start instruction execution to conversion end (ADCEND = 1) (at  $f_x = 8$  MHz, 50  $\mu$ s)

Remark  $t_{CY} = 16/f_x$  ( $f_x$ : frequency of system clock oscillator)

SYSTEM CLOCK OSCILLATOR CHARACTERISTICS ( $V_{DD} = 2.7$  to  $5.5$  V,  $T_A = -40$  to  $+85$  °C)

| Resonator <sup>Note</sup> | Parameter                       | Conditions                | Min. | Typ. | Max. | Unit |

|---------------------------|---------------------------------|---------------------------|------|------|------|------|

| Ceramic resonator         | Oscillation frequency ( $f_x$ ) |                           | 0.39 |      | 2.04 | MHz  |

|                           |                                 | $V_{DD} = 3.6$ to $5.5$ V | 0.39 |      | 4.08 | MHz  |

|                           |                                 | $V_{DD} = 4.5$ to $5.5$ V | 0.39 |      | 8.16 | MHz  |

Note Do not use a resonator having an oscillation generation time of 2 ms or more.

DC PROGRAMMING CHARACTERISTICS ( $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 6.0 \pm 0.25 \text{ V}$ ,  $V_{PP} = 12.5 \pm 0.5 \text{ V}$ )

| Parameter                     | Symbol    | Conditions                        | Min.           | Typ. | Max.        | Unit          |

|-------------------------------|-----------|-----------------------------------|----------------|------|-------------|---------------|

| High-level input voltage      | $V_{IH1}$ | Except CLK                        | $0.7V_{DD}$    |      | $V_{DD}$    | V             |

|                               | $V_{IH2}$ | CLK                               | $V_{DD} - 0.5$ |      | $V_{DD}$    | V             |

| Low-level input voltage       | $V_{IL1}$ | Except CLK                        | 0              |      | $0.3V_{DD}$ | V             |

|                               | $V_{IL2}$ | CLK                               | 0              |      | 0.4         | V             |

| Input leakage current         | $I_{IL}$  | $V_{IN} = V_{IL}$ or $V_{IH}$     |                |      | 10          | $\mu\text{A}$ |

| High-level output voltage     | $V_{OH}$  | $I_{OH} = -1 \text{ mA}$          | $V_{DD} - 1.0$ |      |             | V             |

| Low-level output voltage      | $V_{OL}$  | $I_{OL} = 1.6 \text{ mA}$         |                |      | 0.4         | V             |

| $V_{DD}$ power supply current | $I_{DD}$  |                                   |                |      | 30          | mA            |

| $V_{PP}$ power supply current | $I_{PP}$  | $MD_0 = V_{IL}$ , $MD_1 = V_{IH}$ |                |      | 30          | mA            |

**Cautions 1.**  $V_{PP}$  must be under +13.5 V including overshoot.

**2.**  $V_{DD}$  must be applied before  $V_{PP}$  on and must be off after  $V_{PP}$  off.

AC PROGRAMMING CHARACTERISTICS ( $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 6.0 \pm 0.25\text{ V}$ ,  $V_{PP} = 12.5 \pm 0.5\text{ V}$ )

| Parameter                                                 | Symbol              | Note 1    | Conditions                               | Min.  | Typ. | Max. | Unit          |

|-----------------------------------------------------------|---------------------|-----------|------------------------------------------|-------|------|------|---------------|

| Address setup time <sup>Note 2</sup> to $MD_0 \downarrow$ | $t_{AS}$            | $t_{AS}$  |                                          | 2     |      |      | $\mu\text{s}$ |

| $MD_1$ setup time to $MD_0 \downarrow$                    | $t_{M1S}$           | $t_{OES}$ |                                          | 2     |      |      | $\mu\text{s}$ |

| Data setup time to $MD_0 \downarrow$                      | $t_{DS}$            | $t_{DS}$  |                                          | 2     |      |      | $\mu\text{s}$ |

| Address hold time <sup>Note 2</sup> to $MD_0 \uparrow$    | $t_{AH}$            | $t_{AH}$  |                                          | 2     |      |      | $\mu\text{s}$ |

| Data hold time to $MD_0 \uparrow$                         | $t_{DH}$            | $t_{DH}$  |                                          | 2     |      |      | $\mu\text{s}$ |

| Data output float delay time from $MD_0 \uparrow$         | $t_{DF}$            | $t_{DF}$  |                                          | 0     |      | 130  | ns            |

| $V_{PP}$ setup time to $MD_3 \uparrow$                    | $t_{VPS}$           | $t_{VPS}$ |                                          | 2     |      |      | $\mu\text{s}$ |

| $V_{DD}$ setup time to $MD_3 \uparrow$                    | $t_{VDS}$           | $t_{VCS}$ |                                          | 2     |      |      | $\mu\text{s}$ |

| Initial program pulse width                               | $t_{PW}$            | $t_{PW}$  |                                          | 0.95  | 1.0  | 1.05 | ms            |

| Additional program pulse width                            | $t_{OPW}$           | $t_{OPW}$ |                                          | 0.95  |      | 21.0 | ms            |

| $MD_0$ setup time to $MD_1 \uparrow$                      | $t_{M0S}$           | $t_{CES}$ |                                          | 2     |      |      | $\mu\text{s}$ |

| Data output delay time from $MD_0 \downarrow$             | $t_{DV}$            | $t_{DV}$  | $MD_0 = MD_1 = V_{IL}$                   |       |      | 1    | $\mu\text{s}$ |

| $MD_1$ hold time to $MD_0 \uparrow$                       | $t_{M1H}$           | $t_{OEH}$ | $t_{M1H} + t_{M1R} \geq 50\ \mu\text{s}$ | 2     |      |      | $\mu\text{s}$ |

| $MD_1$ recovery time to $MD_0 \downarrow$                 | $t_{M1R}$           | $t_{OR}$  |                                          | 2     |      |      | $\mu\text{s}$ |

| Program counter reset time                                | $t_{PCR}$           | —         |                                          | 10    |      |      | $\mu\text{s}$ |

| CLK input high, low level range                           | $t_{XH}$ , $t_{XL}$ | —         |                                          | 0.125 |      |      | $\mu\text{s}$ |

| CLK input frequency                                       | $f_X$               | —         |                                          |       |      | 2    | MHz           |

| Initial mode set time                                     | $t_I$               | —         |                                          | 2     |      |      | $\mu\text{s}$ |

| $MD_3$ setup time to $MD_1 \uparrow$                      | $t_{M3S}$           | —         |                                          | 2     |      |      | $\mu\text{s}$ |

| $MD_3$ hold time to $MD_1 \downarrow$                     | $t_{M3H}$           | —         |                                          | 2     |      |      | $\mu\text{s}$ |

| $MD_3$ setup time to $MD_0 \downarrow$                    | $t_{M3SR}$          | —         | When reading program memory              | 2     |      |      | $\mu\text{s}$ |

| Data output delay time from address <sup>Note 2</sup>     | $t_{DAD}$           | $t_{ACC}$ |                                          |       |      | 2    | $\mu\text{s}$ |

| Data output hold time from address <sup>Note 2</sup>      | $t_{HAD}$           | $t_{OH}$  |                                          | 0     |      | 130  | ns            |

| $MD_3$ hold time to $MD_0 \uparrow$                       | $t_{M3HR}$          | —         |                                          | 2     |      |      | $\mu\text{s}$ |

| Data output float delay time from $MD_3 \downarrow$       | $t_{DFR}$           | —         |                                          |       |      | 2    | $\mu\text{s}$ |

| Reset setup time                                          | $t_{RES}$           | —         |                                          | 10    |      |      | $\mu\text{s}$ |

**Notes** 1. Symbols used for  $\mu\text{PD}27\text{C}256\text{A}$  (The  $\mu\text{PD}27\text{C}256\text{A}$  is used only for maintenance.)

2. Internal address signal is incremented by one at the falling edge of the third CLK input.

## Write program memory timing

**Remark** The dashed line indicates high-impedance.

## Read program memory timing

## 5. PACKAGE DRAWINGS

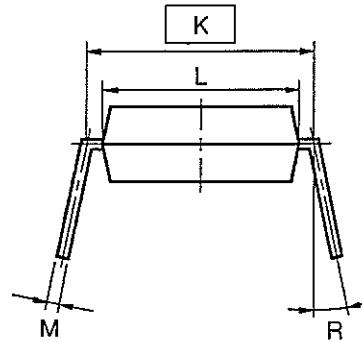

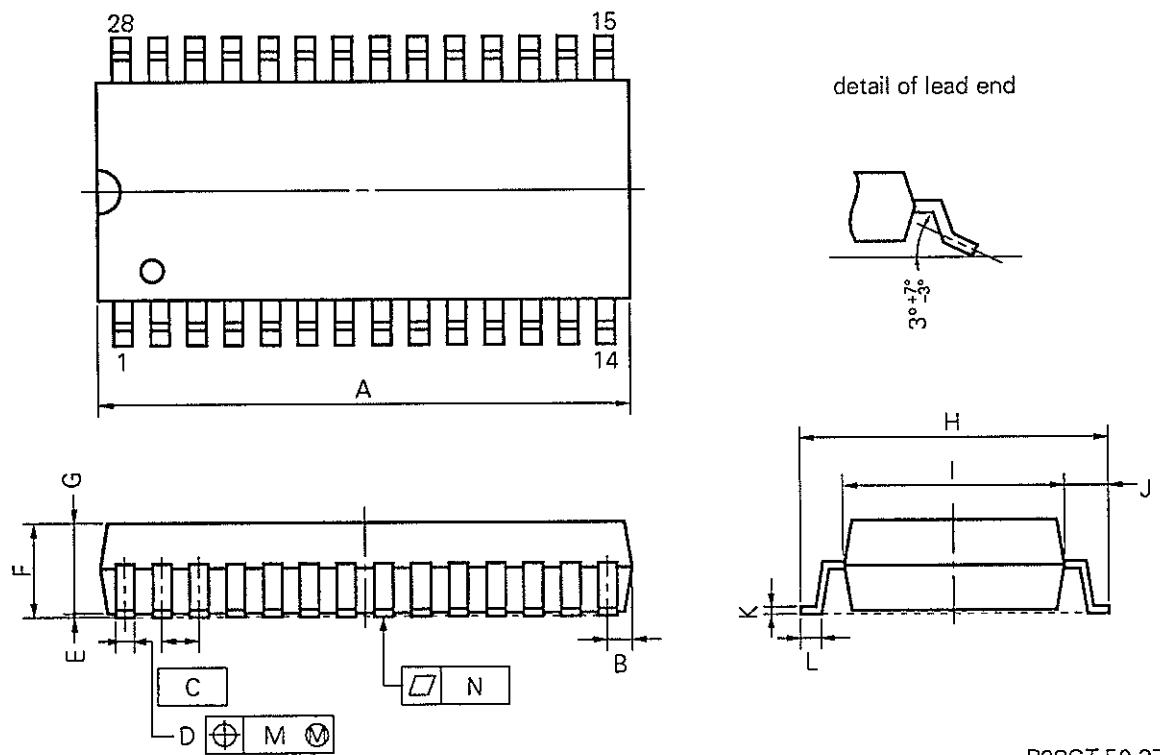

## 28 PIN PLASTIC SHRINK DIP (400 mil)

## NOTES

- 1) Each lead centerline is located within 0.17 mm (0.007 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS              | INCHES                      |

|------|--------------------------|-----------------------------|

| A    | 28.46 MAX.               | 1.121 MAX.                  |

| B    | 2.67 MAX.                | 0.106 MAX.                  |

| C    | 1.778 (T.P.)             | 0.070 (T.P.)                |

| D    | 0.50 $\pm$ 0.10          | 0.020 $\pm$ 0.005           |

| F    | 0.85 MIN.                | 0.033 MIN.                  |

| G    | 3.2 $\pm$ 0.3            | 0.126 $\pm$ 0.012           |

| H    | 0.51 MIN.                | 0.020 MIN.                  |

| I    | 4.31 MAX.                | 0.170 MAX.                  |

| J    | 5.08 MAX.                | 0.200 MAX.                  |

| K    | 10.16 (T.P.)             | 0.400 (T.P.)                |

| L    | 8.6                      | 0.339                       |

| M    | 0.25 $\pm$ 0.10<br>-0.05 | 0.010 $\pm$ 0.004<br>-0.003 |

| N    | 0.17                     | 0.007                       |

| R    | 0~15°                    | 0~15°                       |

S28C-70-400B-1

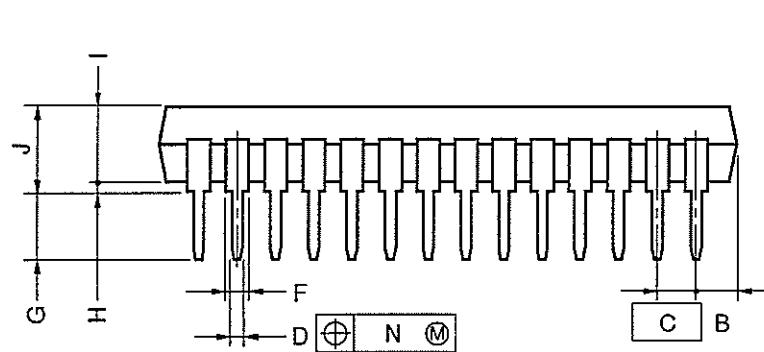

## 28 PIN PLASTIC SOP (375 mil)

## NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

P28GT-50-375B-1

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| A    | 18.2 MAX.              | 0.717 MAX.                |

| B    | 0.845 MAX.             | 0.034 MAX.                |

| C    | 1.27 (T.P.)            | 0.050 (T.P.)              |

| D    | $0.40^{+0.10}_{-0.05}$ | $0.016^{+0.004}_{-0.003}$ |

| E    | $0.125 \pm 0.075$      | $0.005 \pm 0.003$         |

| F    | 2.9 MAX.               | 0.115 MAX.                |

| G    | $2.50 \pm 0.2$         | $0.098^{+0.008}_{-0.008}$ |

| H    | $10.3 \pm 0.3$         | $0.406^{+0.012}_{-0.013}$ |

| I    | $7.2 \pm 0.2$          | $0.283^{+0.009}_{-0.008}$ |

| J    | $1.6 \pm 0.2$          | $0.063 \pm 0.008$         |

| K    | $0.15^{+0.10}_{-0.05}$ | $0.006^{+0.004}_{-0.002}$ |

| L    | $0.8 \pm 0.2$          | $0.031^{+0.009}_{-0.008}$ |

| M    | 0.12                   | 0.005                     |

| N    | 0.10                   | 0.004                     |

## 6. RECOMMENDED SOLDERING CONDITIONS

★

The conditions listed below shall be met when soldering the μPD17P149.

For details of the recommended soldering conditions, refer to our document *SMD Surface Mount Technology Manual* (IEI-1207).

Please consult with our sales offices in case any other soldering process is used, or in case soldering is done under different conditions.

Table 6-1 Soldering Conditions for Surface-Mount Devices

μPD17P149GT: 28-pin plastic SOP (375 mil)

| Soldering process      | Soldering conditions                                                                                                                                                                                                                                                               | Recommended conditions |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Infrared ray reflow    | Peak package's surface temperature: 230 °C<br>Reflow time: 30 seconds or less (at 210 °C or more)<br>Number of reflow processes: 1<br>Exposure limit <small>Note:</small> 3 days (20 hours of pre-baking is required at 125 °C afterward.)                                         | IR30-203-1             |

| VPS                    | Peak package's surface temperature: 215 °C<br>Reflow time: 40 seconds or less (at 200 °C or more)<br>Number of reflow processes: 1<br>Exposure limit <small>Note:</small> 3 days (20 hours of pre-baking is required at 125 °C afterward.)                                         | VP15-203-1             |

| Wave soldering         | Solder temperature: 260 °C or less<br>Flow time: 10 seconds or less<br>Number of flow processes: 1<br>Preheating temperature: 120°C max. (measured on the package surface)<br>Exposure limit <small>Note:</small> 3 days (20 hours of pre-baking is required at 125 °C afterward.) | WS60-203-1             |

| Partial heating method | Terminal temperature: 300 °C or less<br>Heat time: 3 seconds or less (for one side of a device)                                                                                                                                                                                    | —                      |

**Note** Exposure limit before soldering after dry-pack package is opened.

Storage conditions: Temperature of 25 °C and maximum relative humidity at 65 % or less

**Caution** Do not apply more than a single process at once, except for "Partial heating method."

Table 6-2 Soldering Conditions for Through Hole Mount Devices

μPD17P149CT: 28-pin plastic shrink DIP (400 mil)

| Soldering process                      | Soldering conditions                                                                     |