# IS61NW6432

# 64K x 32 SYNCHRONOUS STATIC RAM WITH NO-WAIT STATE BUS FEATURE

## **FEATURES**

- Fast access time:

- 5 ns-100 MHz; 6 ns-83 MHz;

- 7 ns-75 MHz; 8ns-66 MHz;

- · No wait cycles between Read and write

- · Internal self-timed write cycle

- Individual byte write Control

- Clock controlled, registered address, data and control

- Pentium<sup>™</sup> or Inear burst sequence control using MODE input

- Three chip enables for simple depth depth expansion and adress pipelining

- · Common data inputs and data outputs

- JEDEC 100-pin LQFP and PQFP package

- Single+3.3V power supply

- Optional data strobe pin (#80) for latching data (See page 12 for detailed timing)

### **DESCRIPTION**

The IS61NW6432 is a high-speed, low-power synchronous static RAM designed to provide a burstable, high-performance, no-wait bus, secondary cache for the Pentium, 680X0, and Power PC microprocessors. It is organized as 65,536 words by 32 bits, fabricated with ICSI's advanced CMOS technology.

Incorporating a no-wait bus, wait cycles are eliminated when the bus switches from read to write, or write to read. This device integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit.

All synchronous inputs pass through registers controlled by a Positive-edge-trggered clock input. Operations may be suspended and all synchronous inputs ignored when Clock Enable,  $\overline{\text{CEN}}$  is HIGH. In this state the internal device will hold their previous values.

When the ADV/ $\overline{\text{LD}}$  is HIGH the internal burst counter is incremented. New external addresses can be loaded when ADV/ $\overline{\text{LD}}$  is LOW.

Write cycles are internally self-timed and are initiated by the rising edge of the clock inputs and when RD/ $\overline{WE}$  is LOW. Separate byte enables allow indiviual bytes to be written.  $\overline{BW1}$  controls I/O1-I/P8;  $\overline{BW2}$  controls I/O9-I/O16; $\overline{BW3}$  controls I/O17-I/O24;  $\overline{BW4}$  controls I/O25-I/O32. All Bytes are written when  $\overline{BW1}$ ,  $\overline{BW2}$ ,  $\overline{BW3}$ , and  $\overline{BW4}$  are LOW.

MODE pin upon power up is in interleave burst mode. It can be connected to GND or Vccq to alter power up state.

ICSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Circuit Solution Inc.

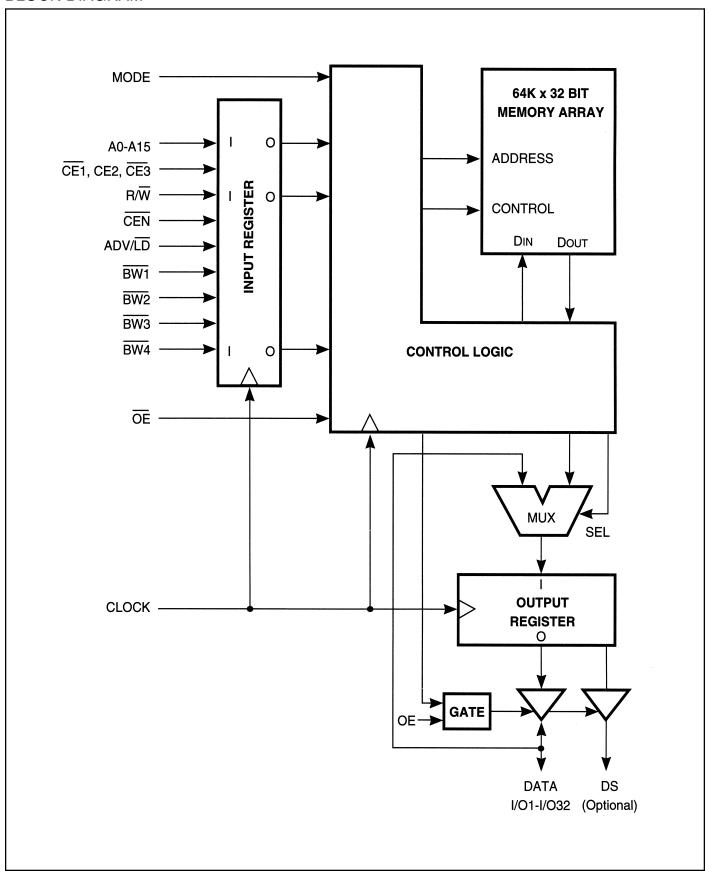

## **BLOCK DIAGRAM**

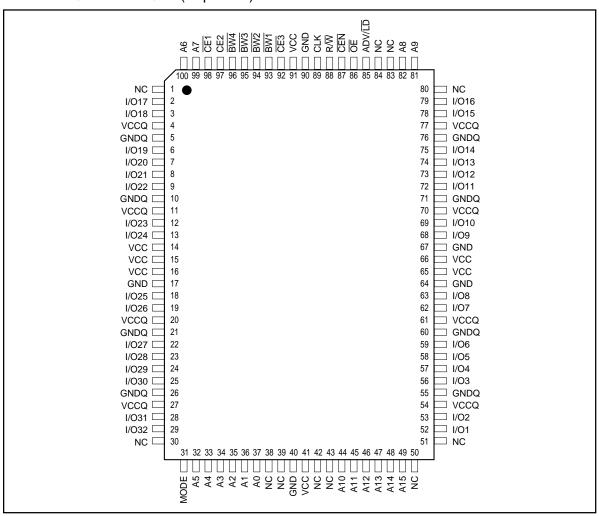

# PIN CONFIGURATION 100-Pin LQFP and PQFP (Top View)

# PIN DESCRIPTIONS

| A0-A15            | Address Inputs                |

|-------------------|-------------------------------|

| CLK               | Clock                         |

| CEN               | Clock Enale                   |

| ADV/CD            | Advance Load                  |

| BW1-BW4           | Synchronous Byte Write Enable |

| R/W               | Read / Write                  |

| CE1, CE2, CE3     | Synchronous Chip Enable       |

| ŌĒ                | Output Enable                 |

| DS <sup>(1)</sup> | Data Strobe                   |

| Data Input/Output                    |

|--------------------------------------|

| Burst Sequence Mode                  |

| +3.3V Power Supply                   |

| Ground                               |

| Isolated Output Buffer Supply: +3.3V |

| Isolated Output Buffer Ground        |

| No Connect                           |

|                                      |

#### Notes:

1. Optional, NC or DS.

## TRUTH TABLE(1)

| Operation                | Address<br>Used | <b>R/</b> ₩ | CEx | ADV/ <b>LD</b> | CEN | <del>BW</del> x | CLK |

|--------------------------|-----------------|-------------|-----|----------------|-----|-----------------|-----|

| Bein New Write Cycle     | External        | L           | L   | L              | L   | Valid           | L-H |

| Begin New Read Cycle     | External        | Н           | L   | L              | L   | Χ               | L-H |

| Advance Burst Counter(2) | Internal        | Χ           | Χ   | Н              | L   | Valid           | L-H |

| (Burst Write)            |                 |             |     |                |     |                 |     |

| Advance Burst Counter    | Internal        | Χ           | Χ   | Н              | L   | Χ               | L-H |

| (BurstRead)              |                 |             |     |                |     |                 |     |

| Deselect (2 Cycle)       | Х               | Х           | Н   | L              | L   | Χ               | L-H |

| Hold/NOOP <sup>(4)</sup> | Х               | Χ           | Х   | Х              | Н   | Χ               | L-H |

#### Notes:

- 1. "X" Means don't care.

- 2. When ADV/\(\overline{LD}\) signal is sampled HIIGH, the internal burst counter is incremented. The R/\(\overline{W}\) signal is ignored when the counter is advanced, Therefore, the nature of the burst cycle (Read or Write) is determined by the status of the R/\(\overline{W}\) signal when the first address is loaded at the beginning of the burst cycle.

- 3. Deselect cycle is initiated when CEx is sampled HIGH and ADV/LD sampled LOW at rising edge of clock. The data bus will tristate two cycles after deselect is initiated.

- 4. When  $\overline{\text{CEN}}$  is sampled high at the rising edge of clock, that clock edge is blocked form propagating through the part. The state of all the internal registers remains unchanged.

# PARTIAL TRUTH TABLE(Non-burst)

| Function        | Ġ₩ | BW1 | BW2 | BW3 | BW4 | CEx | ADV/ <b>LD</b> |

|-----------------|----|-----|-----|-----|-----|-----|----------------|

| READ            | Н  | Χ   | Х   | Χ   | Χ   | L   | L              |

| WRITE Byte 1    | L  | L   | Н   | Н   | Н   | L   | L              |

| WRITE Byte 2    | L  | Н   | L   | Н   | Н   | L   | L              |

| WRITE Byte 3    | L  | Н   | Н   | L   | Н   | L   | L              |

| WRITE Byte 4    | L  | Н   | Н   | Н   | L   | L   | L              |

| WRITE All Bytes | L  | L   | L   | L   | L   | Χ   | L              |

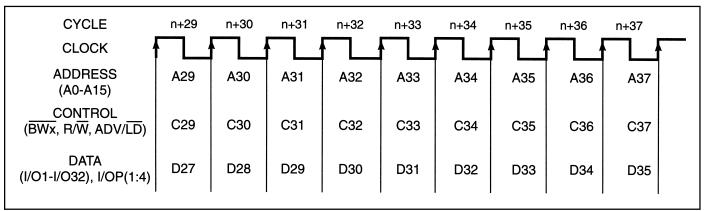

## FUNCTIONAL TIMING DIAGRAM

# TYPICAL OPERATION $\overline{\text{CE1}}$ , $\overline{\text{CE3}}$ and $\overline{\text{CEN}}$ are LOW, CE2 is HIGH, Non-Burst Operation

| Cycle | Address    | R/W | ADV/LD | CEX | CEN | BWX | ŌĒ | I/O | Comments |

|-------|------------|-----|--------|-----|-----|-----|----|-----|----------|

| n     | A0         | Н   | L      | L   | L   | Х   | ?  | D-2 | ?        |

| n+1   | A1         | L   | L      | L   | L   | L   | ?  | D-1 | ?        |

| n+2   | A2         | Н   | L      | L   | L   | Х   | L  | D0  | Data Out |

| n+3   | A3         | L   | L      | L   | L   | L   | Χ  | D1  | Data In  |

| n+4   | A4         | Н   | L      | L   | L   | Χ   | L  | D2  | Data Out |

| n+5   | <b>A</b> 5 | L   | L      | L   | L   | L   | Χ  | D3  | Data In  |

| n+6   | A6         | Н   | L      | L   | L   | Χ   | L  | D4  | Data Out |

| n+7   | A7         | L   | L      | L   | L   | L   | Χ  | D5  | Data In  |

| n+8   | A8         | Н   | L      | L   | L   | Х   | L  | D6  | Data Out |

| n+9   | A9         | L   | L      | L   | L   | L   | Χ  | D7  | Data In  |

| n+10  | A10        | Н   | L      | L   | L   | Χ   | L  | D8  | Data Out |

| n+11  | A11        | Н   | L      | L   | L   | Χ   | Χ  | D9  | Data In  |

| n+12  | A12        | L   | L      | L   | L   | L   | L  | D10 | Data Out |

| n+13  | A13        | L   | L      | L   | L   | L   | L  | D11 | Data Out |

| n+14  | A14        | Н   | L      | L   | L   | Χ   | Χ  | D12 | Data In  |

| n+15  | A15        | Н   | L      | L   | L   | Χ   | Χ  | D13 | Data In  |

| n+16  | A16        | Н   | L      | L   | L   | Χ   | L  | D14 | Data Out |

| n+17  | A17        | L   | L      | L   | L   | L   | L  | D15 | Data Out |

| n+18  | A18        | L   | L      | L   | L   | L   | L  | D16 | Data Out |

| n+19  | A19        | L   | L      | L   | L   | L   | Х  | D17 | Data In  |

| n+20  | A20        | Н   | L      | L   | L   | Х   | Х  | D18 | Data In  |

| n+21  | A21        | Н   | L      | L   | L   | Х   | Χ  | D19 | Data In  |

#### Notes

<sup>1.</sup> H=High; L=Low; X=Don't Care;?=Don't Know; Z=High Impedance

# **READ OPERATION**

| Cycle | Address | R/W | ADV/ <b>LD</b> | CEX | CEN | BWX | ŌĒ | I/O | Comments                        |

|-------|---------|-----|----------------|-----|-----|-----|----|-----|---------------------------------|

| n     | A0      | Н   | L              | L   | Х   | Х   | Χ  | Χ   | Address and Control meet setup  |

| n+1   | Х       | Х   | Х              | L   | L   | Х   | Χ  | Х   | Clock Setup valid               |

| n+2   | Х       | Х   | Х              | Х   | Х   | Х   | L  | D0  | Contents of Address A0 Read Out |

# **BURST READ OPERATION**

| Cycle | Address | R/W | ADV/ <b>LD</b> | CEX | CEN | BWX | ŌĒ | I/O  | Comments                           |

|-------|---------|-----|----------------|-----|-----|-----|----|------|------------------------------------|

| n     | A0      | Н   | L              | L   | Х   | Х   | Χ  | Х    | Address and Control meet setup     |

| n+1   | Х       | Χ   | Н              | Х   | L   | Х   | Χ  | Х    | Clock Setup valid, Advance Counter |

| n+2   | Х       | Х   | Н              | Х   | L   | Х   | L  | D0   | Address A0 Read Out, Inc. Count    |

| n+3   | Х       | Х   | Н              | Х   | L   | Х   | L  | D0+1 | Address A0+1 Read Out, Inc. Count  |

| n+4   | Х       | Х   | Н              | Х   | L   | Х   | L  | D0+2 | Address A0+2 Read Out, Inc. Count  |

| n+5   | A1      | Н   | L              | L   | L   | Х   | L  | D0+3 | Address A0+3 Read Out, Load A1     |

| n+6   | Х       | Х   | Н              | Х   | L   | Х   | L  | D0   | Address A0 Read Out, Inc. Count    |

| n+7   | Х       | Х   | Н              | Х   | L   | Х   | L  | D1   | Address A1 Read Out, Inc. Count    |

| n+8   | A2      | Н   | L              | L   | L   | Х   | L  | D0+1 | Address A0+1 Read Out, Load A2     |

# WRITE OPERATION

| Cycle | Address | R/W | ADV/ <b>LD</b> | CEX | CEN | BWX | ŌĒ | I/O | Comments                       |

|-------|---------|-----|----------------|-----|-----|-----|----|-----|--------------------------------|

| n     | A0      | L   | L              | L   | L   | L   | Χ  | Х   | Address and Control meet setup |

| n+1   | Х       | Х   | Х              | L   | L   | Х   | Х  | Х   | Clock Setup valid              |

| n+2   | Х       | Х   | Х              | Х   | L   | Х   | Х  | D0  | Write D0 to Address A0         |

## **BURST WRITE OPERATION**

| Cycle | Address | R/W | ADV/ <b>LD</b> | CEX | CEN | BWX | ŌĒ | I/O  | Comments                           |

|-------|---------|-----|----------------|-----|-----|-----|----|------|------------------------------------|

| n     | A0      | Н   | L              | L   | L   | L   | Χ  | Х    | Address and Control meet setup     |

| n+1   | Х       | Х   | Н              | Х   | L   | L   | Х  | Х    | Clock Setup valid, Inc. Count      |

| n+2   | Х       | Х   | Н              | Х   | L   | L   | Х  | D0   | Address A0 Write Out, Inc. Count   |

| n+3   | Х       | Н   | Н              | L   | L   | Х   | L  | D0+1 | Address A0+1 Write Out, Inc. Count |

| n+4   | Х       | Χ   | Н              | Χ   | L   | L   | Χ  | D0+2 | Address A0+2 Write Out, Inc. Count |

| n+5   | A1      | L   | L              | L   | L   | L   | Χ  | D0+3 | Address A0+3 Write Out, Load A1    |

| n+6   | Х       | Х   | Н              | Х   | L   | L   | Х  | D0   | Address A0 Write Out, Inc. Count   |

| n+7   | Х       | Х   | Н              | Х   | L   | L   | Х  | D1   | Address A1 Write Out, Inc. Count   |

| n+8   | A2      | L   | L              | L   | L   | L   | Χ  | D0+1 | Address A0+1 Write Out, Load A2    |

#### Notes

1. H=High; L=Low; X=Don't Care;?=Don't Know; Z=High Impedance

# READ OPERATION WITH CLOCK ENABLE USED

| Cycle | Address | R/W | ADV/ <b>LD</b> | CEX | CEN | BWX | ŌĒ | I/O | Comments                             |

|-------|---------|-----|----------------|-----|-----|-----|----|-----|--------------------------------------|

| n     | A0      | Н   | L              | L   | L   | Х   | Х  | Х   | Address and Control meet setup       |

| n+1   | Х       | Х   | Х              | Х   | Н   | Х   | Х  | Х   | Clock n+1 Ignored                    |

| n+2   | A1      | Н   | L              | L   | L   | Х   | Χ  | Х   | Clock Valid                          |

| n+3   | Х       | Х   | Х              | Х   | Н   | Х   | L  | D0  | Clock Ignored, Data D0 is on the bus |

| n+4   | Х       | Х   | Х              | Х   | Н   | Х   | L  | D0  | Clock Ignored, Data D0 is on the bus |

| n+5   | A2      | Н   | L              | L   | L   | Х   | L  | D0  | Address A0 Read Out (bus trans.)     |

| n+6   | АЗ      | ?   | L              | L   | L   | Х   | L  | D1  | Address A1 Read Out (bus trans.)     |

| n+7   | A4      | ?   | L              | L   | L   | Х   | L  | D2  | Address A2 Read Out (bus trans.)     |

# READ OPERATION WITH CLOCK ENABLE USED

| Cycle | Address | R/W | ADV/ <b>LD</b> | CEX | CEN | BWX | ŌĒ | I/O | Comments                       |

|-------|---------|-----|----------------|-----|-----|-----|----|-----|--------------------------------|

| n     | A0      | L   | L              | L   | L   | L   | Χ  | Х   | Address and Control meet setup |

| n+1   | Х       | Х   | Х              | Х   | Н   | Х   | Х  | Х   | Clock n+1 Ignored              |

| n+2   | A1      | L   | L              | L   | L   | L   | Х  | Х   | Clock Valid                    |

| n+3   | Х       | Х   | Х              | Χ   | Н   | Х   | L  | di  | Clock Ignored.                 |

| n+4   | Х       | Χ   | Х              | Χ   | Н   | Х   | L  | di  | Clock Ignored.                 |

| n+5   | A2      | L   | L              | L   | L   | L   | L  | D0  | Write data D0 (bus trans.)     |

| n+6   | A3      | ?   | L              | L   | L   | L   | L  | D1  | Write data D1 (bus trans.)     |

| n+7   | A4      | ?   | L              | L   | L   | L   | L  | D2  | Write data D2 (bus trans.)     |

#### Notes

<sup>1.</sup> H=High; L=Low; X=Don't Care;?=Don't Know; Z=High Impedance

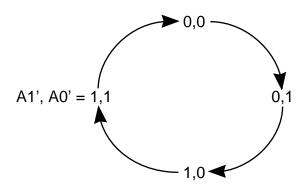

## INTERLEAVED BURST ADDRESS TABLE (MODE=Vccq or No connect)

| External Address | 1st Burst Address | 2nd Burst Address | 3rd Burst Addres |  |

|------------------|-------------------|-------------------|------------------|--|

| A1 A0            | A1 A0             | A1 A0             | A1 A0            |  |

| 00               | 01                | 10                | 11               |  |

| 01               | 00                | 11                | 10               |  |

| 10               | 11                | 00                | 01               |  |

| 11               | 10                | 01                | 00               |  |

# LINEAR BURST ADDRESS TABLE (MODE=GNDQ)

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol    | Parameter                                                  | Value              | Unit |

|-----------|------------------------------------------------------------|--------------------|------|

| TBIAS     | Temperature Under Bias                                     | -10 to +85         | °C   |

| Тѕтс      | Storage Temperature                                        | -55 to +150        | °C   |

| PD        | Power Dissipation                                          | 1.8                | W    |

| Іоит      | Output Current (per I/O)                                   | 100                | mA   |

| VIN, VOUT | Voltage Relative to GND for I/O Pins                       | -0.5 to Vccq + 0.3 | V    |

| Vin       | Voltage Relative to GND for for Address and Control Inputs | -0.5 to 5.5        | V    |

#### Notes:

- Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation of the

device at these or any other conditions above those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

- 2. This device contains circuity to protect the inputs against damage due to high static voltages or electric fields; however, precautions may be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

- 3. This device contains circuitry that will ensure the output devices are in High-Z at power up.

## **OPERATING RANGE**

| Range      | Ambient Temperature | Vcc            |

|------------|---------------------|----------------|

| Commercial | 0°C to +70°C        | 3.3V +10%, -5% |

# DC ELECTRICAL CHARACTERISTICS(1) (Over Operating Range)

| Symbol | Parameter              | Test Conditions                              |      | Min.       | Max.       | Unit |

|--------|------------------------|----------------------------------------------|------|------------|------------|------|

| Vон    | Output HIGH Voltage    | Iон = -5.0 mA                                |      | 2.4        | _          | V    |

| Vol    | Output LOW Voltage     | loL = 5.0 mA                                 |      | _          | 0.4        | V    |

| VIH    | Input HIGH Voltage     |                                              |      | 1.7        | Vccq + 0.3 | V    |

| VIL    | Input LOW Voltage      |                                              |      | -0.3       | 0.8        | V    |

| lu     | Input Leakage Current  | $GND \leq Vin \leq Vccq^{(2)}$               | Com. | <b>–</b> 5 | 5          | μΑ   |

| ILO    | Output Leakage Current | $GND \le VOUT \le VCCQ, \overline{OE} = VIH$ | Com. | <b>–</b> 5 | 5          | μΑ   |

# POWER SUPPLY CHARACTERISTICS (Over Operating Range)

| Symbol | Parameter                      | Test Conditions                                                                                                                       | -5<br>Min.Typ. Max. | -6<br>Min.Typ.Max. | -7<br>Min.Typ.Max. | -8<br>Min.Typ.Max. | Unit |

|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|--------------------|--------------------|------|

| Icc    | AC Operating<br>Supply Current | Device Selected, Com. All Inputs = $V_{\parallel}$ or $V_{\parallel}$ H $\overline{OE}$ = $V_{\parallel}$ H,Cycle Time $\geq$ tkc min | 230                 | 220                | 210                | 200                | mA   |

| ISB    | Standby Current                | Device Deselected, Com. Vcc = Max., All Inputs= V <sub>IH</sub> or V <sub>IL</sub> CLK Cycle Time ≥ txc min. CEN=V <sub>IH</sub>      | 60                  | 60                 | 60                 | 60                 | mA   |

## Note:

<sup>1.</sup> MODE pin has an internal pull up. This pin may be a No Connect, tied to GND, or tied to Vccq.

<sup>2.</sup> MODE pin should be tied to Vcc or GND. It exhibit  $\pm 30~\mu$ A maximum leakage current when tied to  $\leq$  GND + 0.2V or  $\geq$  Vcc - 0. 2V.

## CAPACITANCE(1,2)

| Symbol | Parameter                | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| Cin    | Input Capacitance        | VIN = 0V   | 6    | pF   |

| Соит   | Input/Output Capacitance | Vout = 0V  | 8    | pF   |

### Notes:

- 1. Tested initially and after any design or process changes that may affect these parameters.

- 2. Test conditions: T<sub>A</sub> = 25°C, f = 1 MHz, Vcc = 3.3V.

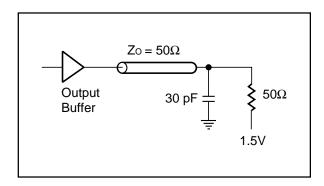

# **AC TEST CONDITIONS**

| Parameter                                   | Unit          |

|---------------------------------------------|---------------|

| Input Pulse Level                           | 0V to 3.0V    |

| Input Rise and Fall Times                   | 1.5 ns        |

| Input and Output Timing and Reference Level | 1.5V          |

| Output Load                                 | See Figures 1 |

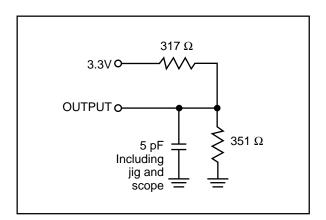

# AC TEST LOADS

Figure 1

Figure 2

# READ /WRITE CYCLE SWITCHING CHARACTERISTICS (Over Operating Range)

|                      |                                  |        | -5   | -(   | -    |      | -7  | -8   |      |      |

|----------------------|----------------------------------|--------|------|------|------|------|-----|------|------|------|

| Symbol               | Parameter                        | Min.   | Max. | Min. | Max. | Min. | Max | Min. | Max. | Unit |

| fmax                 | Clock Frequency                  | _      | 100  | _    | 83   | _    | 75  | _    | 66   | MHz  |

| tĸc                  | Cycle Time                       | 10     | _    | 12   | _    | 13   | _   | 15   | _    | ns   |

| tкн                  | Clock High Time                  | 4      | _    | 4    | _    | 6    | -   | 6    | -    | ns   |

| tkl                  | Clock Low Time                   | 4      | _    | 4    | _    | 6    | _   | 6    | _    | ns   |

| tka                  | Clock Access Time                | _      | 5    | _    | 6    | _    | 7   | _    | 8    | ns   |

| tkqx <sup>(2)</sup>  | Clock High to Output Invalid     | 1.5    | _    | 1.5  | _    | 1.5  | _   | 1.5  | _    | ns   |

| tkqlz <sup>(2)</sup> | Clock High to Output Low-Z       | 2.0    | _    | 2.0  | _    | 2.0  | _   | 2.0  | _    | ns   |

| tkqhz <sup>(2)</sup> | Clock High to Output High-Z      | 1.5    | 3.5  | 2    | 3.5  | 2    | 3.5 | 2    | 3.5  | ns   |

| toeq                 | Output Enable to Output Valid    | _      | 5    | _    | 6    | _    | 6   | _    | 6    | ns   |

| toeqx(2)             | Output Disable to Output Invalid | 0      | _    | 0    | _    | 0    | _   | 0    | _    | ns   |

| toelz(2)             | Output Enable to Output Low-Z    | 0      | _    | 0    | _    | 0    | _   | 0    | _    | ns   |

| toehz(2)             | Output Disable to Output High-Z  | _      | 3.5  | _    | 3.5  | _    | 3.5 | _    | 3.5  | ns   |

| tas                  | Address Setup Time               | 2.0    | _    | 2.0  | _    | 2.0  | _   | 2.0  | _    | ns   |

| tws                  | Read/Write Setup Time            | 2.0    | _    | 2.0  | _    | 2.0  | _   | 2.0  | _    | ns   |

| tces                 | Chip Enable Setup Time           | 2.0    | _    | 2.0  | _    | 2.0  | _   | 2.0  | _    | ns   |

| tse                  | Clock Enable Setup Time          | 2.0    | _    | 2.0  | _    | 2.0  | _   | 2.0  | _    | ns   |

| tavs                 | Address Advance Setup Time       | 2.0    | _    | 2.0  | _    | 2.0  | _   | 2.0  | _    | ns   |

| tae                  | Address Hold Time                | 0.5    | _    | 0.5  | _    | 0.5  | _   | 0.5  | _    | ns   |

| the                  | Clock EnableHold Time            | 0.5    | _    | 0.5  | _    | 0.5  | _   | 0.5  | _    | ns   |

| twн                  | Write Hold Time                  | 0.5    | _    | 0.5  | _    | 0.5  | _   | 0.5  | _    | ns   |

| tceh                 | Chip Enable Hold Time            | 0.5    | _    | 0.5  | _    | 0.5  | _   | 0.5  | _    | ns   |

| tals                 | Advance/Load (ADV/LD) Setup Tii  | me2.0  | _    | 2.0  | _    | 2.0  | _   | 2.0  | _    | ns   |

| talh                 | Advance/Load (ADV/LD) Hold Tin   | ne 0.5 | _    | 0.5  | _    | 0.5  | _   | 0.5  | _    | ns   |

| tds                  | Data Setup Time                  | 2.0    | _    | 2.0  | _    | 2.0  | _   | 2.0  | _    | ns   |

| tdh                  | Data Hold Time                   | 0.5    | _    | 0.5  | _    | 0.5  | _   | 0.5  | _    | ns   |

| tzp                  | I/O From Tri-State to Valid      | 1.5    | _    | 1.5  | 2.5  | 1.5  | 2.5 | 1.5  | 2.5  | ns   |

## Notes:

<sup>1.</sup> Configuration signal MODE is static and must not change during normal operation.

<sup>2.</sup> Guaranteed but not 100% tested. This parameter is periodically sampled.

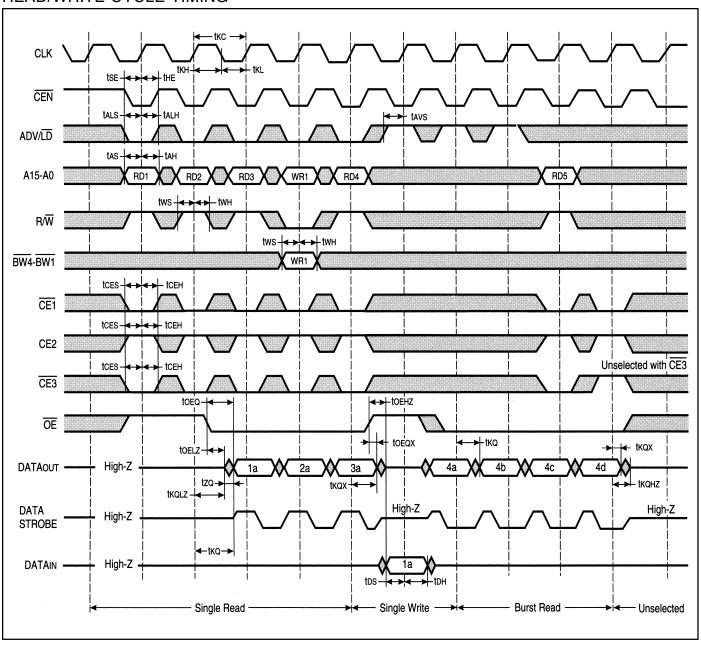

# **READ/WRITE CYCLE TIMING**

## ORDERING INFORMATION

Commercial Range: 0°C to +70°C

| Frequency (MHz) | Order Part Number | Package                              |

|-----------------|-------------------|--------------------------------------|

| 5               |                   | 14*20*1.4mm LQFP<br>14*20*2.7mm PQFP |

| 6               |                   | 14*20*1.4mm LQFP<br>14*20*2.7mm PQFP |

| 7               |                   | 14*20*1.4mm LQFP<br>14*20*2.7mm PQFP |

| 8               |                   | 14*20*1.4mm LQFP<br>14*20*2.7mm PQFP |

# Integrated Circuit Solution Inc.

**HEADQUARTER:**

NO.2, TECHNOLOGY RD. V, SCIENCE-BASED INDUSTRIAL PARK,

HSIN-CHU, TAIWAN, R.O.C.

TEL: 886-3-5780333 Fax: 886-3-5783000

**BRANCH OFFICE:**

7F, NO. 106, SEC. 1, HSIN-TAI 5<sup>TH</sup> ROAD,

HSICHIH TAIPEI COUNTY, TAIWAN, R.O.C.

TEL: 886-2-26962140

FAX: 886-2-26962252