## DS34C87T

### CMOS Quad TRI-STATE Differential Line Driver

#### General Description

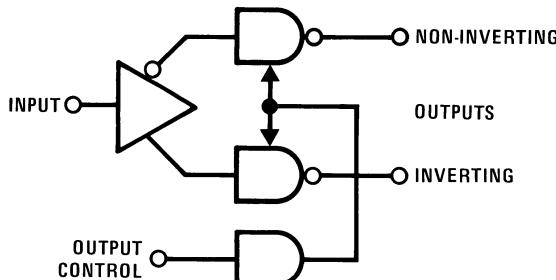

The DS34C87T is a quad differential line driver designed for digital data transmission over balanced lines. The DS34C87T meets all the requirements of EIA standard RS-422 while retaining the low power characteristics of CMOS. This enables the construction of serial and terminal interfaces while maintaining minimal power consumption.

The DS34C87T accepts TTL or CMOS input levels and translates these to RS-422 output levels. This part uses special output circuitry that enables the individual drivers to power down without loading down the bus. This device has separate enable circuitry for each pair of the four drivers. The DS34C87T is pin compatible to the DS3487T.

All inputs are protected against damage due to electrostatic discharge by diodes to  $V_{CC}$  and ground.

#### Features

- TTL input compatible

- Typical propagation delays: 6 ns

- Typical output skew: 0.5 ns

- Outputs won't load line when  $V_{CC} = 0V$

- Meets the requirements of EIA standard RS-422

- Operation from single 5V supply

- TRI-STATE outputs for connection to system buses

- Low quiescent current

- Available in surface mount

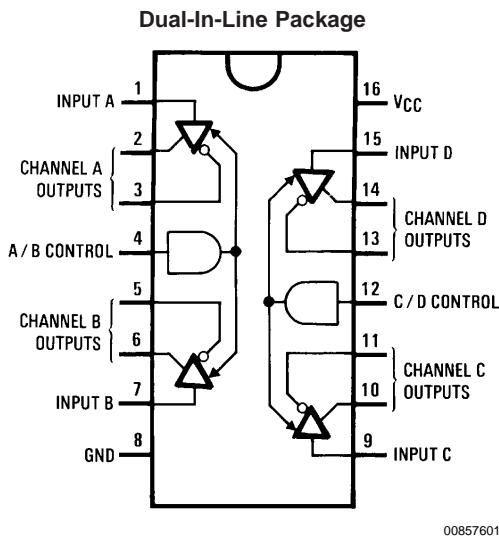

#### Connection and Logic Diagrams

See Pin Description Table for details

Top View

Order Number DS34C87TM or DS34C87TN

See NS Package Number M16A or N16E

#### Truth Table

| Input | Control Input | Non-Inverting Output | Inverting Output |

|-------|---------------|----------------------|------------------|

| H     | H             | H                    | L                |

| L     | H             | L                    | H                |

| X     | L             | Z                    | Z                |

L = Low logic state

H = High logic state

X = irrelevant

Z = TRI-STATE (high performance)

**Absolute Maximum Ratings** (Notes 1,

2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

|                                                     |                           |

|-----------------------------------------------------|---------------------------|

| Supply Voltage ( $V_{CC}$ )                         | -0.5 to 7.0V              |

| DC Voltage ( $V_{IN}$ )                             | -1.5 to $V_{CC}$<br>+1.5V |

| DC Output Voltage ( $V_{OUT}$ )                     | -0.5 to 7V                |

| Clamp Diode Current ( $I_{IK}$ , $I_{OK}$ )         | $\pm 20$ mA               |

| DC Output Current, per pin ( $I_{OUT}$ )            | $\pm 150$ mA              |

| DC $V_{CC}$ or GND Current ( $I_{CC}$ )             | $\pm 150$ mA              |

| Storage Temperature Range ( $T_{STG}$ )             | -65°C to +150°C           |

| Maximum Power Dissipation ( $P_D$ ) @ 25°C (Note 3) |                           |

Plastic "N" Package

1736 mW

SOIC Package

1226 mW

Lead Temperature ( $T_L$ )

260°C

(Soldering 4 sec)

This device does not meet 2000V ESD rating. (Note 12)

**Operating Conditions**

|                                                     | Min  | Max      | Units |

|-----------------------------------------------------|------|----------|-------|

| Supply Voltage ( $V_{CC}$ )                         | 4.50 | 5.50     | V     |

| DC Input or Output Voltage ( $V_{IN}$ , $V_{OUT}$ ) | 0    | $V_{CC}$ | V     |

| Operating Temperature Range ( $T_A$ )               |      |          |       |

| DS34C87T                                            | -40  | +85      | °C    |

| Input Rise or Fall Times ( $t_r$ , $t_f$ )          | 500  | ns       |       |

**DC Electrical Characteristics** (Note 4) $V_{CC} = 5V \pm 10\%$  (unless otherwise specified)

| Symbol                    | Parameter                         | Conditions                                                                              | Min | Typ        | Max         | Units              |

|---------------------------|-----------------------------------|-----------------------------------------------------------------------------------------|-----|------------|-------------|--------------------|

| $V_{IH}$                  | High Level Input Voltage          |                                                                                         | 2.0 |            |             | V                  |

| $V_{IL}$                  | Low Level Input Voltage           |                                                                                         |     |            | 0.8         | V                  |

| $V_{OH}$                  | High Level Output Voltage         | $V_{IN} = V_{IH}$ or $V_{IL}$ ,<br>$I_{OUT} = -20$ mA                                   | 2.5 | 3.4        |             | V                  |

| $V_{OL}$                  | Low Level Output Voltage          | $V_{IN} = V_{IH}$ or $V_{IL}$ ,<br>$I_{OUT} = 48$ mA                                    |     | 0.3        | 0.5         | V                  |

| $V_T$                     | Differential Output Voltage       | $R_L = 100 \Omega$<br>(Note 5)                                                          | 2.0 | 3.1        |             | V                  |

| $ V_T  -  \bar{V}_T $     | Difference In Differential Output | $R_L = 100 \Omega$<br>(Note 5)                                                          |     |            | 0.4         | V                  |

| $V_{OS}$                  | Common Mode Output Voltage        | $R_L = 100 \Omega$<br>(Note 5)                                                          |     | 2.0        | 3.0         | V                  |

| $ V_{OS} - \bar{V}_{OS} $ | Difference In Common Mode Output  | $R_L = 100 \Omega$<br>(Note 5)                                                          |     |            | 0.4         | V                  |

| $I_{IN}$                  | Input Current                     | $V_{IN} = V_{CC}$ , GND, $V_{IH}$ , or $V_{IL}$                                         |     |            | $\pm 1.0$   | $\mu A$            |

| $I_{CC}$                  | Quiescent Supply Current          | $I_{OUT} = 0 \mu A$ ,<br>$V_{IN} = V_{CC}$ or GND<br>$V_{IN} = 2.4V$ or $0.5V$ (Note 6) |     | 200<br>0.8 | 500<br>2.0  | $\mu A$<br>mA      |

| $I_{OZ}$                  | TRI-STATE™ Output Leakage Current | $V_{OUT} = V_{CC}$ or GND<br>Control = $V_{IL}$                                         |     | $\pm 0.5$  | $\pm 5.0$   | $\mu A$            |

| $I_{SC}$                  | Output Short Circuit Current      | $V_{IN} = V_{CC}$ or GND<br>(Notes 5, 7)                                                | -30 |            | -150        | mA                 |

| $I_{OFF}$                 | Power Off Output Leakage Current  | $V_{CC} = 0V$ $V_{OUT} = 6V$<br>(Note 5) $V_{OUT} = -0.25V$                             |     |            | 100<br>-100 | $\mu A$<br>$\mu A$ |

**Note 1:** Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provide conditions for actual device operation.

**Note 2:** Unless otherwise specified, all voltages are referenced to ground. All currents into device pins are positive; all currents out of device pins are negative.

**Note 3:** Ratings apply to ambient temperature at 25°C. Above this temperature derate N Package 13.89 mW/°C, and M Package 9.80 mW/°C.

**Note 4:** Unless otherwise specified, min/max limits apply across the -40°C to 85°C temperature range. All typicals are given for  $V_{CC} = 5V$  and  $T_A = 25^\circ C$ .

**Note 5:** See EIA Specification RS-422 for exact test conditions.

## DC Electrical Characteristics (Note 4) (Continued)

**Note 6:** Measured per input. All other inputs at  $V_{CC}$  or GND.

**Note 7:** This is the current sourced when a high output is shorted to ground. Only one output at a time should be shorted.

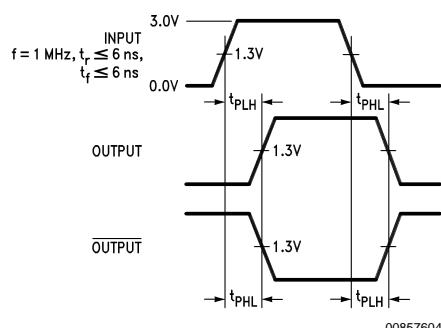

## Switching Characteristics (Note 4)

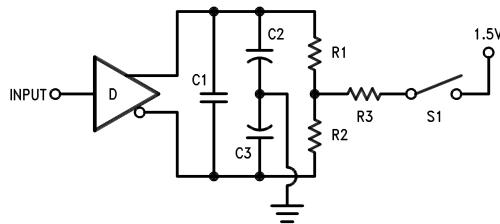

$V_{CC} = 5V \pm 10\%$ ,  $t_r, t_f \leq 6$  ns (Figures 1, 2, 3, 4)

| Symbol             | Parameter                                  | Conditions | Min | Typ | Max | Units |

|--------------------|--------------------------------------------|------------|-----|-----|-----|-------|

| $t_{PLH}, t_{PHL}$ | Propagation Delay<br>Input to Output       | S1 Open    |     | 6   | 11  | ns    |

| Skew               | (Note 8)                                   | S1 Open    |     | 0.5 | 3   | ns    |

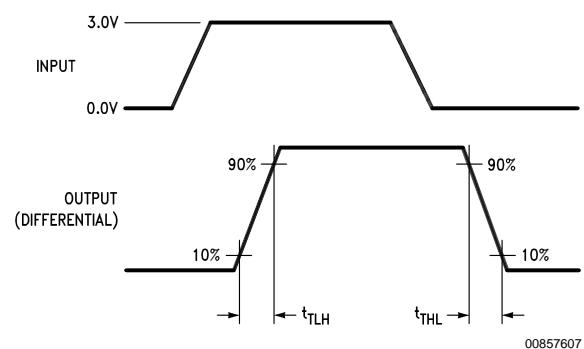

| $t_{TLH}, t_{THL}$ | Differential Output Rise<br>And Fall Times | S1 Open    |     | 6   | 10  | ns    |

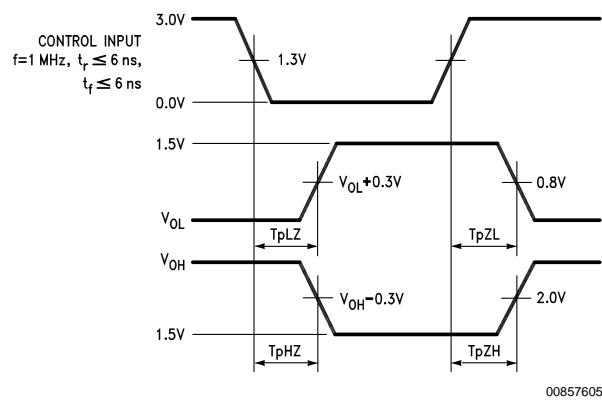

| $t_{PZH}$          | Output Enable Time                         | S1 Closed  |     | 12  | 25  | ns    |

| $t_{PZL}$          | Output Enable Time                         | S1 Closed  |     | 13  | 26  | ns    |

| $t_{PHZ}$          | Output Disable Time (Note 9)               | S1 Closed  |     | 4   | 8   | ns    |

| $t_{PLZ}$          | Output Disable Time (Note 9)               | S1 Closed  |     | 6   | 12  | ns    |

| $C_{PD}$           | Power Dissipation<br>Capacitance (Note 10) |            |     | 100 |     | pF    |

| $C_{IN}$           | Input Capacitance                          |            |     | 6   |     | pF    |

**Note 8:** Skew is defined as the difference in propagation delays between complementary outputs at the 50% point.

**Note 9:** Output disable time is the delay from the control input being switched to the output transistors turning off. The actual disable times are less than indicated due to the delay added by the RC time constant of the load.

**Note 10:**  $C_{PD}$  determines the no load dynamic power consumption,  $P_D = C_{PD} V^2 CC f + I_{CC} V_{CC}$ , and the no load dynamic current consumption,  $I_S = C_{PD} V_{CC} f + I_{CC}$ .

## Comparison Table of Switching Characteristics into “LS-Type” Load (Note 11)

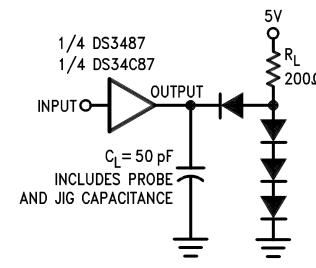

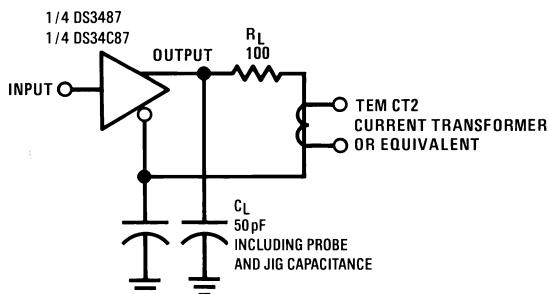

$V_{CC} = 5V$ ,  $T_A = +25^\circ C$ ,  $t_r \leq 6$  ns,  $t_f \leq 6$  ns (Figures 4, 5, 6, 7, 8, 9)

| Symbol             | Parameter                                  | Conditions                                                 | DS34C87 |     | DS3487 |     | Units |

|--------------------|--------------------------------------------|------------------------------------------------------------|---------|-----|--------|-----|-------|

|                    |                                            |                                                            | Typ     | Max | Typ    | Max |       |

| $t_{PLH}, t_{PHL}$ | Propagation Delay<br>Input to Output       |                                                            | 6       | 10  | 10     | 15  | ns    |

| Skew               | (Note 8)                                   |                                                            | 1.5     | 2.0 |        |     | ns    |

| $t_{THL}, t_{TLH}$ | Differential Output Rise<br>and Fall Times |                                                            | 4       | 7   | 10     | 15  | ns    |

| $t_{PHZ}$          | Output Disable Time<br>(Note 9)            | $C_L = 50$ pF, $R_L = 200\Omega$ ,<br>S1 Closed, S2 Closed | 8       | 11  | 17     | 25  | ns    |

| $t_{PLZ}$          | Output Disable Time<br>(Note 9)            | $C_L = 50$ pF, $R_L = 200\Omega$ ,<br>S1 Closed, S2 Closed | 7       | 10  | 15     | 25  | ns    |

| $t_{PZH}$          | Output Enable Time                         | $C_L = 50$ pF, $R_L = \infty$ ,<br>S1 Open, S2 Closed      | 11      | 19  | 11     | 25  | ns    |

| $t_{PZL}$          | Output Enable Time                         | $C_L = 50$ pF, $R_L = 200\Omega$ ,<br>S1 Closed, S2 Open   | 14      | 21  | 15     | 25  | ns    |

**Note 11:** This table is provided for comparison purposes only. The values in this table for the DS34C87 reflect the performance of the device but are not tested or guaranteed.

**Note 12:** ESD Rating: HBM (1.5 k $\Omega$ , 100 pF) Inputs  $\geq 1500V$  Outputs  $\geq 1000V$  EIAJ (0 $\Omega$ , 200 pF) All Pins  $\geq 350V$

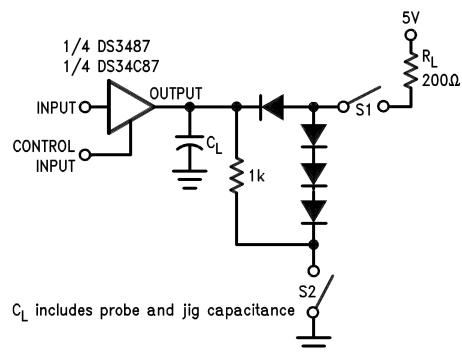

## AC Test Circuit and Switching Time Waveforms

00857603

Note:  $C_1 = C_2 = C_3 = 40 \text{ pF}$  (including Probe and Jig Capacitance),  $R_1 = R_2 = 50\Omega$ ,  $R_3 = 500\Omega$

FIGURE 1. AC Test Circuit

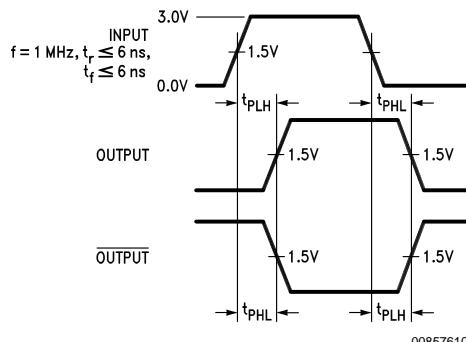

FIGURE 2. Propagation Delays

Input pulse;  $f = 1 \text{ MHz}$ , 50%,  $t_r \leq 6 \text{ ns}$ ,  $t_f \leq 6 \text{ ns}$

FIGURE 4. Differential Rise and Fall Times

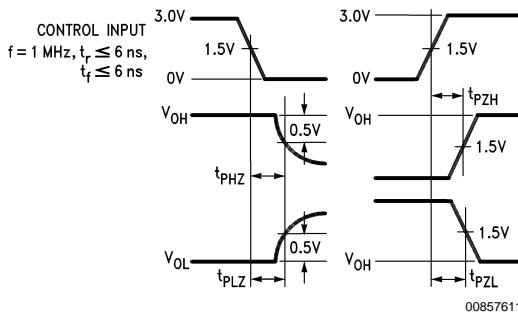

FIGURE 3. Enable and Disable Times

FIGURE 5. Propagation Delays Test Circuit for "LS-Type" Load

## AC Test Circuit and Switching Time Waveforms (Continued)

00857606

**FIGURE 6. Differential Rise and Fall Times Test Circuit for "LS-Type" Load**

00857609

**FIGURE 7. Load Enable and Disable Times Test Circuit for "LS-Type" Load**

00857610

**FIGURE 8. Load Propagation Delays for "LS-Type" Load**

00857611

**FIGURE 9. Load Enable and Disable Times for "LS-Type" Load**

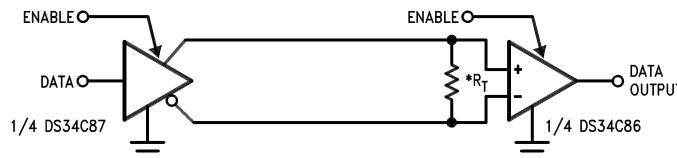

## Typical Applications

00857612

\* $R_T$  is optional although highly recommended to reduce reflection.

**Pin Description Table**

| Pin Number<br>(DIP or SOP<br>package) | Pin Name             | Function                                                         |

|---------------------------------------|----------------------|------------------------------------------------------------------|

| 1                                     | INPUT A              | Channel A - TTL/CMOS input                                       |

| 2                                     | OUTPUT A - True      | True Output for Channel A,<br>RS422 Levels                       |

| 3                                     | OUTPUT A - Inverting | Inverting Output for Channel A,<br>RS422 Levels                  |

| 4                                     | A/B CONTROL          | Enable Pin for Channels A and B,<br>Active High, TTL/CMOS Levels |

| 5                                     | OUTPUT B - Inverting | Inverting Output for Channel B,<br>RS422 Levels                  |

| 6                                     | OUTPUT B - True      | True Output for Channel B,<br>RS422 Levels                       |

| 7                                     | INPUT B              | Channel B - TTL/CMOS input                                       |

| 8                                     | GND                  | Ground Pin (0 V)                                                 |

| 9                                     | INPUT C              | Channel C - TTL/CMOS input                                       |

| 10                                    | OUTPUT C - True      | True Output for Channel C,<br>RS422 Levels                       |

| 11                                    | OUTPUT C - Inverting | Inverting Output for Channel C,<br>RS422 Levels                  |

| 12                                    | C/D CONTROL          | Enable Pin for Channels C and D,<br>Active High, TTL/CMOS Levels |

| 13                                    | OUTPUT D - Inverting | Inverting Output for Channel D,<br>RS422 Levels                  |

| 14                                    | OUTPUT D - True      | True Output for Channel D,<br>RS422 Levels                       |

| 15                                    | INPUT D              | Channel D - TTL/CMOS input                                       |

| 16                                    | V <sub>CC</sub>      | Power Supply Pin, 5.0V typical                                   |

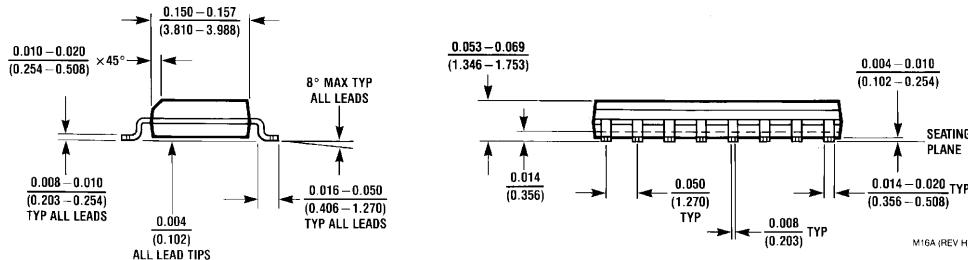

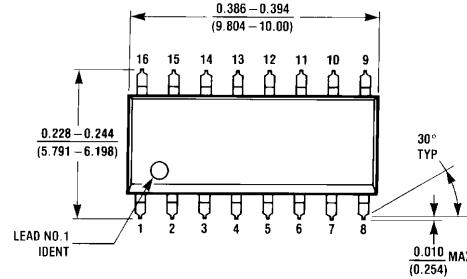

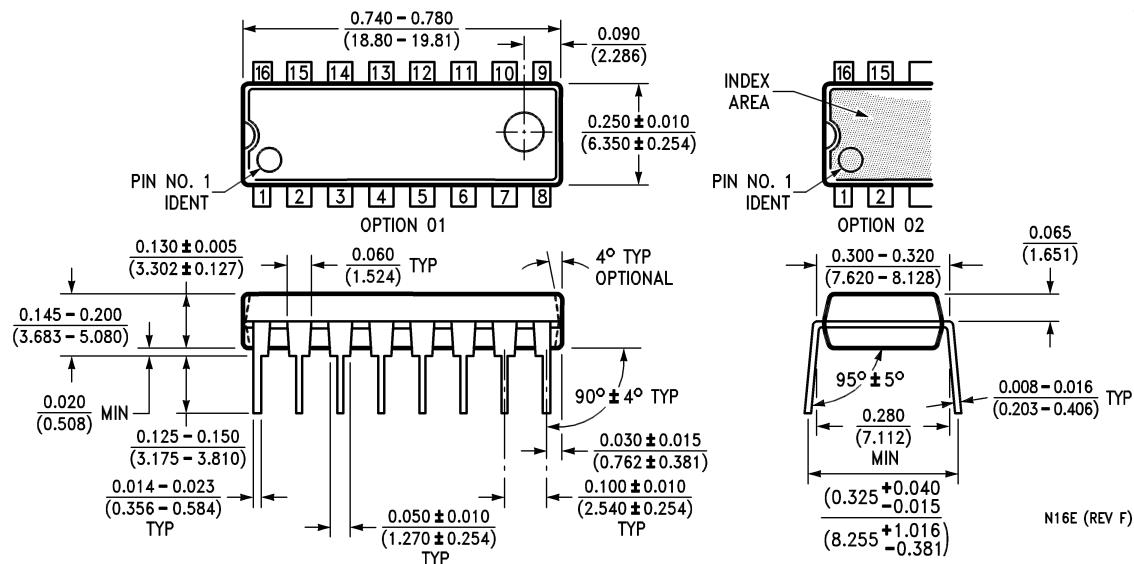

## Physical Dimensions

inches (millimeters) unless otherwise noted

**16-Lead Molded Package

Small Outline (M)**

Order Number DS34C87TM

NS Package Number M16A

**16-Lead Molded Dual-In-Line Package (N)**

Order Number DS34C87TN

NS Package Number N16E

## Notes

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor Corporation**

Americas

Email: support@nsc.com

[www.national.com](http://www.national.com)

**National Semiconductor Europe**

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor Asia Pacific Customer Response Group**

Tel: 65-2544466

Fax: 65-2504466

Email: ap.support@nsc.com

**National Semiconductor Japan Ltd.**

Tel: 81-3-5639-7560

Fax: 81-3-5639-7507