TECHNICAL DATA DATASHEET 4099, REV D

# Three-Phase IGBT BRIDGE, With Gate Driver and Optical Isolation

**DESCRIPTION:** A 1200 VOLT, 80 AMP, THREE PHASE IGBT BRIDGE

## **ELECTRICAL CHARACTERISTICS PER IGBT DEVICE**

(Tj=25°C UNLESS OTHERWISE SPECIFIED)

| PARAMETER                                                                                                                                                               |                                | SYMBOL               | MIN  | TYP | MAX      | UNIT     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------|------|-----|----------|----------|

| IGBT SPECIFICATIONS                                                                                                                                                     |                                |                      |      |     |          |          |

| Collector to Emitter Breakdown Voltage $I_C = 250 \mu A$ , $V_{GE} = 0 V$                                                                                               |                                | BV <sub>CES</sub>    | 1200 | -   | -        | V        |

| Continuous Collector Current                                                                                                                                            | $T_C = 25$ °C<br>$T_C = 90$ °C | lc                   | -    | -   | 80<br>70 | А        |

| Pulsed Collector Current, 1mS                                                                                                                                           |                                | I <sub>CM</sub>      | -    | -   | 200      | А        |

| Gate to Emitter Voltage                                                                                                                                                 |                                | $V_{\sf GE}$         | -    | -   | +/-20    | V        |

| Gate-Emitter Leakage Current , V <sub>GE</sub> = +/-20V                                                                                                                 |                                | I <sub>GES</sub>     | -    | -   | +/- 100  | nA       |

| Gate Threshold Voltage, I <sub>C</sub> =2mA                                                                                                                             |                                | V <sub>GE(TH)</sub>  | 3.0  | -   | 6.0      | V        |

| Zero Gate Voltage Collector Current $V_{CE} = 1200 \text{ V},  V_{GE} = 0V  T_i = 25^{\circ}\text{C}$ $V_{CE} = 900 \text{ V},  V_{GE} = 0V  T_i = 125^{\circ}\text{C}$ |                                | I <sub>CES</sub>     | -    | -   | 1<br>10  | mA<br>mA |

| Collector to Emitter Saturation Voltage, $I_C = 60A$ , $V_{GE} = 15V$ ,                                                                                                 | $T_C = 25$ $^{\circ}C$         | V <sub>CE(SAT)</sub> | -    | 2.5 | 2.8      | V        |

| Maximum Thermal Resistance                                                                                                                                              |                                | R <sub>eJC</sub>     | -    | -   | 0.3      | °C/W     |

| Brake IGBT SPECIFICATIONS                                                                                                                                               |                                |                      |      |     |          |          |

| Continuous Collector Current                                                                                                                                            | $T_C = 25$ °C<br>$T_C = 90$ °C | Ic                   | -    | -   | 40<br>25 | А        |

| Pulsed Collector Current, 0.5mS                                                                                                                                         | -                              | I <sub>CM</sub>      | -    | -   | 120      | А        |

## **TECHNICAL DATA**

DATASHEET 4099, REV D

| OVER-TEMPERATURE SHUTDOWN                                                                 |                   |          |     |      |         |

|-------------------------------------------------------------------------------------------|-------------------|----------|-----|------|---------|

| Over-Temperature Shutdown                                                                 | Tsd               | 100      | 110 | 120  | °C      |

| Over-Temperature Shutdown Hysteresis                                                      |                   |          | 20  |      | °C      |

| Over-Temperature Output                                                                   | Tco               |          | 10  |      | 10mV/°C |

| ULTRAFAST DIODES RATING AND CHARACTERI                                                    | STICS             | <b>.</b> |     |      |         |

| Diode Peak Inverse Voltage                                                                | PIV               | 1200     | -   | -    | V       |

| Continuous Forward Current, T <sub>C</sub> = 90 °C                                        | I <sub>F</sub>    | -        | -   | 60   | А       |

| Forward Surge Current, t <sub>p</sub> = 10 msec                                           | I <sub>FSM</sub>  | -        | -   | 250  | А       |

| Diode Forward Voltage, $I_F = 70A$                                                        | V <sub>F</sub>    | -        | 2.0 | 2.3  | V       |

| Diode Reverse Recovery Time (I <sub>F</sub> =60A, V <sub>RR</sub> =600V , di/dt=200 A/μs) | t <sub>rr</sub>   | -        | 180 | 250  | nsec    |

| Maximum Thermal Resistance                                                                | $R_{	heta JC}$    | -        | -   | 0.55 | °C/W    |

| GATE DRIVER                                                                               |                   | •        |     |      |         |

| Supply Voltage                                                                            | VCC               | 10       | 15  | 20   | V       |

| Input On Current                                                                          | HIN, LIN          | 2        |     | 5.0  | mA      |

| Opto-Isolator Logic High Input Threshold                                                  | I <sub>th</sub>   | -        | 1.6 | -    | mA      |

| Input Reverse Breakdown Voltage                                                           | BV <sub>in</sub>  | 5.0      | -   | -    | V       |

| Input Forward Voltage @ I <sub>in</sub> = 5mC                                             | V <sub>F</sub>    | -        | 1.5 | 1.7  | V       |

| Under Voltage Lockout                                                                     | VCCUV             | 11.5     | -   | 12.5 | V       |

| ITRIP Reference Voltage (1)                                                               | Itrip-ref         | 2.9      | 3.0 | 3.1  | V       |

| Desaturation Over-Current Protection Blanking time (2)                                    | tbl               | 3        | 5   | TBD  | μsec    |

| Logic Inputs Fault, Fault Clr, SD Logic "1" Input Voltage                                 |                   | 2.0      | -   | -    | V       |

| Logic Inputs Fault, Fault CIr, SD Logic "0" Input Voltage                                 |                   | -        | -   | 0.8  | V       |

| Input-to-Output Turn On Delay                                                             | t <sub>ond</sub>  | -        |     | 800  | nsec    |

| Output Turn On Rise Time                                                                  | t <sub>r</sub>    | -        |     | 100  |         |

| Input-to-Output Turn Off Delay                                                            | t <sub>offd</sub> | -        |     | 1000 |         |

| Output Turn Off Fall Time                                                                 | t <sub>f</sub>    |          |     | 100  |         |

| At VCC=300V, IC=50A, T <sub>C</sub> = 25                                                  |                   |          |     |      |         |

| Input-Output Isolation Voltage                                                            | -                 | 1000     | -   | -    | V       |

<sup>• 221</sup> West Industry Court 🗏 Deer Park, NY 11729 🗏 (631) 586 7600 FAX (631) 242 9798 •

## **SENSITRON**

## **TECHNICAL DATA**

DATASHEET 4099, REV D

| Maximum operating Junction Temperature | T <sub>jmax</sub> | -40 | ı | 150 | °C |

|----------------------------------------|-------------------|-----|---|-----|----|

| Maximum Storage Junction Temperature   | T <sub>jmax</sub> | -55 | - | 150 | °C |

# **Pin Description**

| Pin Number | Function                                       | Pin Number | Function                                                                                         |  |

|------------|------------------------------------------------|------------|--------------------------------------------------------------------------------------------------|--|

| 1          | Isolated Input for Low-side IGBT of<br>Phase A | 17         | +15V Rtn (Signal Ground)                                                                         |  |

| 2          | Return for Input at 1                          | 18         | Fault Output <sup>(3)</sup>                                                                      |  |

| 3          | Isolated Input for High-side IGBT of Phase A   | 19         | Fault Clear Input <sup>(3)</sup>                                                                 |  |

| 4          | Return for Input at 3                          | 20         | +5V Output                                                                                       |  |

| 5          | Isolated Input for Low -side IGBT of Phase B   | 21         | Over-Current Trip Set point (3)                                                                  |  |

| 6          | Return for Input at 5                          | 22         | DC Bus Current Output with Total Gain of 0.0365 V/A                                              |  |

| 7          | Isolated Input for High-side IGBT of Phase B   | 23         | Case Temperature Output with a gain of 0.010 V/°C                                                |  |

| 8          | Return for Input at 7                          | 24         | Brake IGBT Gate Input                                                                            |  |

| 9          | Isolated Input for Low-side IGBT of Phase C    | 25         | Brake IGBT Emitter Input. This input is internally connected to Signal Ground                    |  |

| 10         | Return for Input at 9                          | 26 to 30   | DC Bus return                                                                                    |  |

| 11         | Isolated Input for High-side IGBT of Phase C   | 31 , 32    | Brake Resistor Terminal. Brake Resisto<br>Shall be Connected Between These<br>Terminals and +VDC |  |

| 12         | Return for Input at 11                         | 33 to 37   | DC Bus "+VDC" input                                                                              |  |

| 13         | NC                                             | 38 to 42   | Phase C output                                                                                   |  |

| 14         | NC                                             | 43 to 47   | Phase B output                                                                                   |  |

| 15         | SD <sup>(3)</sup>                              | 48 to 52   | Phase A output                                                                                   |  |

| 16         | +15V Input                                     | Case       | Isolated                                                                                         |  |

<sup>(1)</sup> ITRIP Cycle-by cycle current limit is internally set to 70A peak. The set point can be lowered by connecting a resistor between ltrip-ref and Gnd. The set point can be increased by connecting a resistor between ltrip-ref and +5V ref

<sup>(2)</sup> Desaturation blanking maximum time is TBD and is only provided at the low-side IGBTs.

<sup>(3)</sup> See application notes on page 6.

**TECHNICAL DATA**DATASHEET 4099, REV D

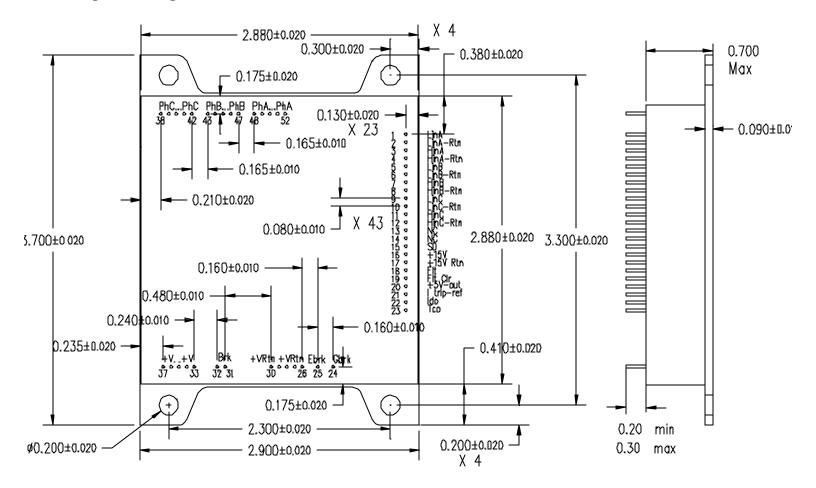

# **Package Drawing:**

#### **SENSITRON**

## **TECHNICAL DATA**

DATASHEET 4099, REV D

## **Application Notes:**

## a- Shutdown Feature:

- 1- SD is a dual function input/output, active low input. It is internally pulled high. As a low input shuts down all IGBTs regardless of the Hin and Lin signals.

- **2-** SD is also internally activated by the over-temperature shutdown, over-current limit, undervoltage shutdown, and desaturation protection.

- **3-** Over-temperature shutdown and over-current limit are not latching features.

- **4-** Under-voltage shutdown is automatically reset after 300 msec once the VCC rises above the threshold limit.

- **5-** Desaturation shutdown is a latching feature and internally reset after 300 msec.

- 6- When any of the internal protection features is activated, SD is pulled down.

- **7-** SD can be used to shutdown all IGBTs except the brake IGBT by an external command. An open collector switch shall be used to pull down SD externally.

- 8- Also, SD can be used as a fault condition output. Low output at SD indicates a fault situation.

## b- Fault Output Feature:

- **1-** Pin 18 Flt is a dual function pin. It is internally pulled high. If pulled down, it will freeze the status of all the six IGBTs regardless of the Hin and Lin signals

- **2-** Pin 18 as an output reports desaturation protection activation. When desaturation protection is activated a low output for about 9 µsec is reported.

- 3- If any other protection feature is activated, it will not be reported by Pin 18.

## c- Fault Clear Output:

- **1-** Pin 19 is a fault clear input. It can be used to reset a latching fault condition, due to desaturation protection.

- **2-** Pin 19 is internally pulled down. A latching fault due to desaturation can be cleared by pulling high this input.

- **3-** An internal fault clear is activated after 300 msec delay. If desired to clear the fault earlier, this input can be used.

#### **TECHNICAL DATA**

#### DISCLAIMER:

- 1- The information given herein, including the specifications and dimensions, is subject to change without prior notice to improve product characteristics. Before ordering, purchasers are advised to contact the Sensitron Semiconductor sales department for the latest version of the datasheet(s).

- 2- In cases where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, medical equipment, and safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of users' fail-safe precautions or other arrangement.

- 3- In no event shall Sensitron Semiconductor be liable for any damages that may result from an accident or any other cause during operation of the user's units according to the datasheet(s). Sensitron Semiconductor assumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in the datasheets.

- 4- In no event shall Sensitron Semiconductor be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.

- 5- No license is granted by the datasheet(s) under any patents or other rights of any third party or Sensitron Semiconductor.

- 6- The datasheet(s) may not be reproduced or duplicated, in any form, in whole or part, without the expressed written permission of Sensitron Semiconductor.

- 7- The products (technologies) described in the datasheet(s) are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.