TLCS-90 Series TMP90C846

#### CMOS 8-Bit Microcontroller

#### **TMP90C846F**

#### 1. Outline and Characteristics

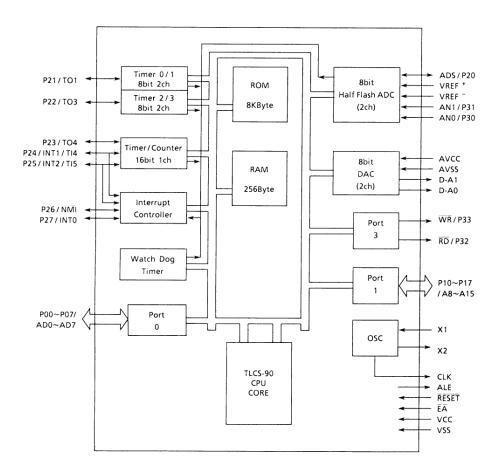

The TMP90C846 is an advanced 8-bit microcontroller developed for application in the control of HDD/FDD high-speed mechanisms. The built-in functions include a high-speed A/D converter (minimum sampling rate: 400ns @ 10MHz) with an external start function, and a D/A converter.

The TMP90C846, integrates 8-bit CPU, ROM, RAM, high-speed A/D converter, D/A converter, and multi-function timer/event counter in a single-chip.

The TMP90C846 uses a 44-pin mini flat package (QFP44-P-1414D).

The following are the features of the TMP90C846:

- (1) Highly efficient instruction set:

- 163 basic instructions

- Division and multiplication instructions, 16-bit operation instruction and bit manipulation operation instructions and bit operation instructions.

- (2) Minimum instruction executing time: 400ns (@ 10MHz)

- (3) Built-in ROM: 8K bytes

- (4) Built-in RAM: 256 bytes

- (5) Memory expansion capability

External program memory: 56K bytes

External data memory: 56K bytes

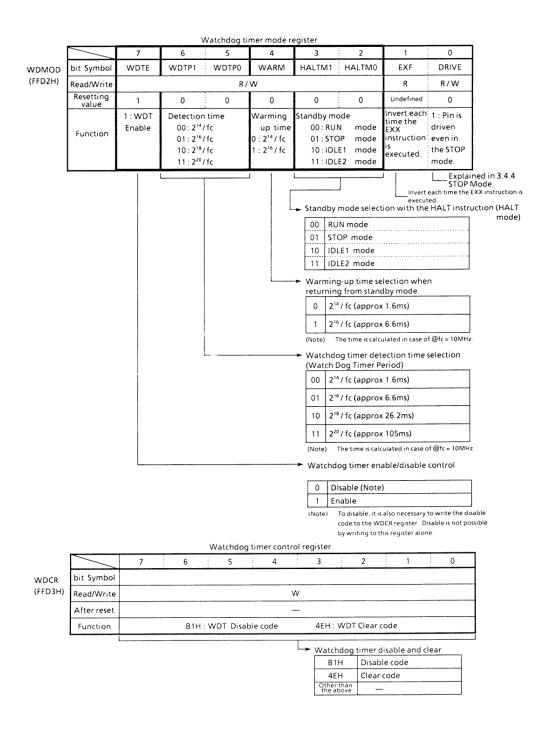

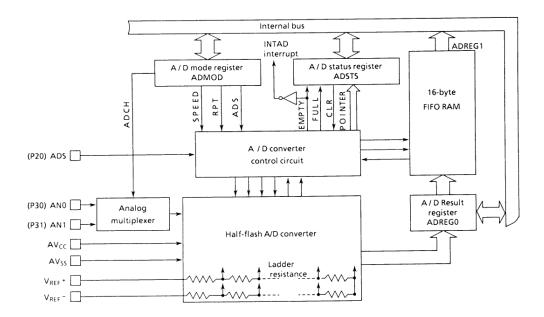

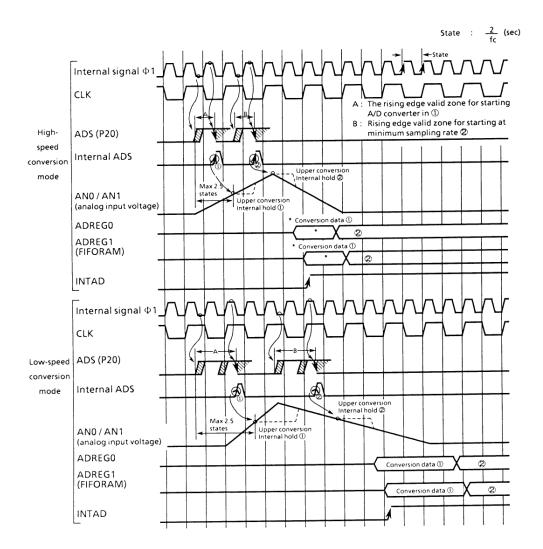

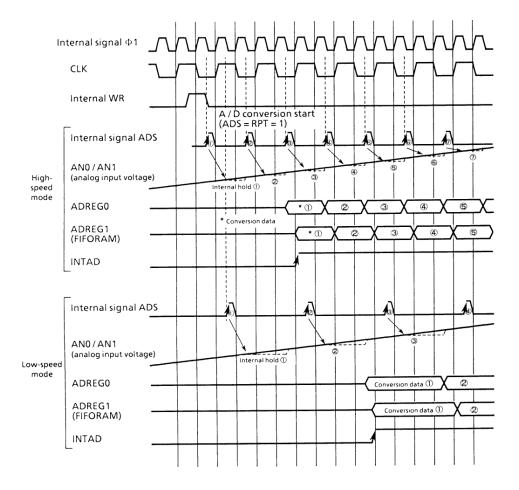

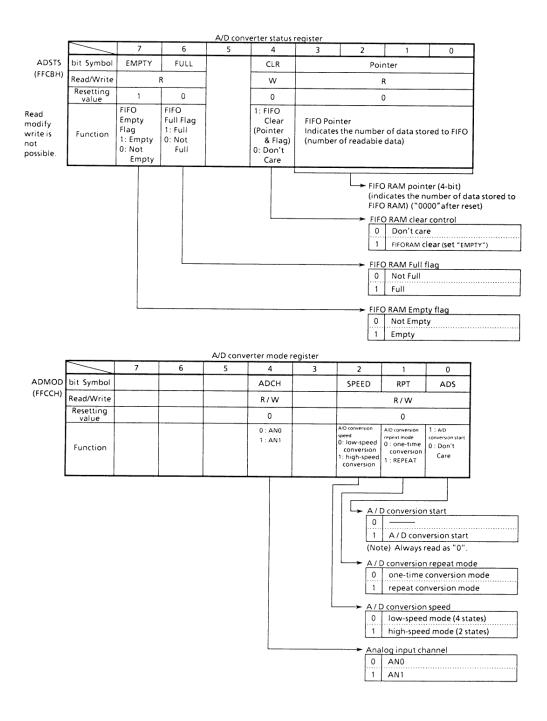

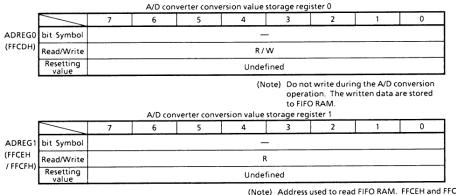

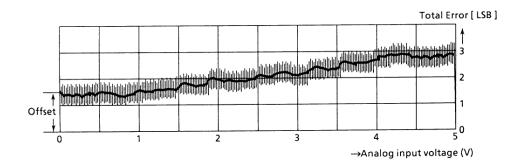

- (6) Highly-speed A/D converter (2 channels)

- Minimum sampling rate: 400ns (@ 10MHz)

- 16-byte FIFO RAM (conversion data storage)

- External start, software start (one-time conversion, repeat conversion

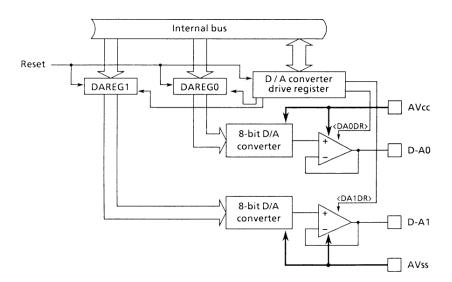

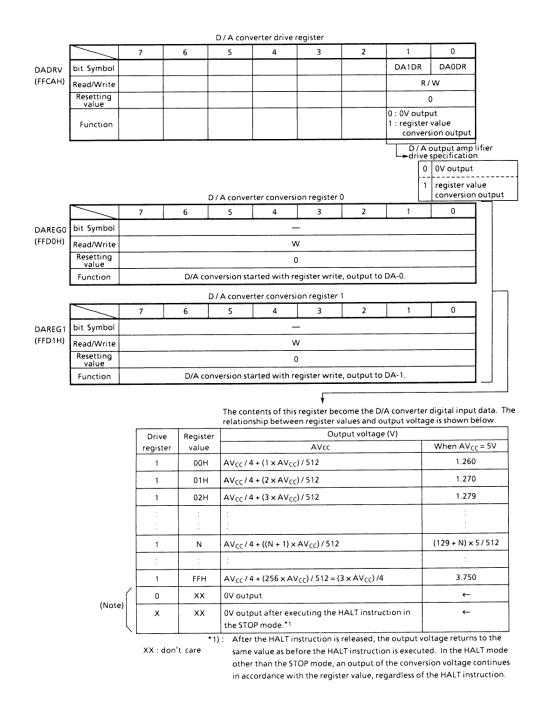

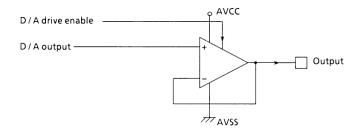

- (7) 8-bit voltage output type D/A converter (2 channels)

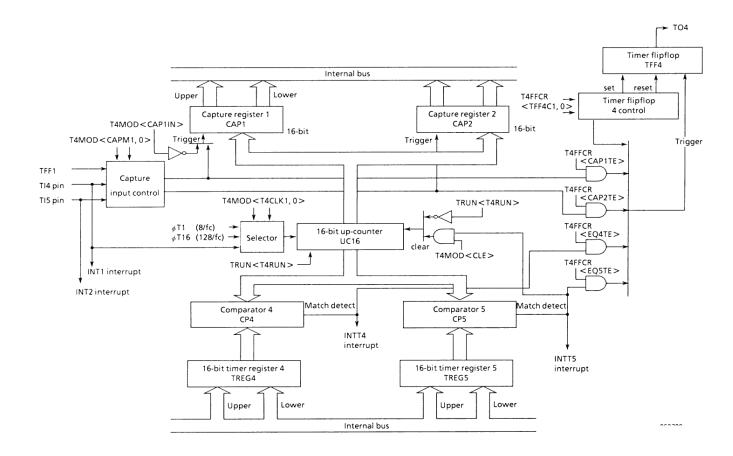

- (8) Multi-function 16-bit timer/event counter (1 channel)

- (9) 8-bit timer (4 channels)

- (10) Interrupt function: 9 internal, 4 external

- (11) Micro DMA function (10 channels)

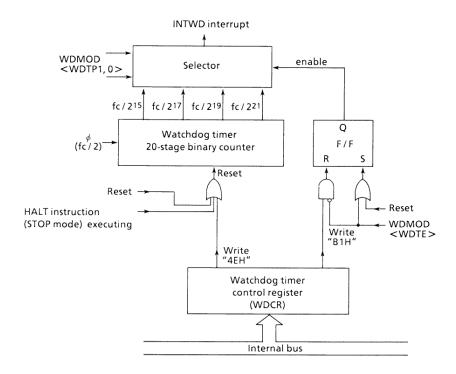

- (12) Watchdog timer function

- (13) Zero cross detector (2 pins)

- (14) I/O ports (28 pins)

- (15) Standby function (4 HALT modes)

TOSHIBA CORPORATION 1/98

The information contained here is subject to change without notice.

The information contained herein is presented only as guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. These TOSHIBA products are intended for usage in general electronic equipments (office equipment, communication equipment, measuring equipment, domestic electrification, etc.) Please make sure that you consult with us before you use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which could have major impact to the welfare of human life (atomic energy control, spaceship, traffic signal, combustion control, all types of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may occur in case these TOSHIBA products were used in the mentioned equipments without prior consultation with TOSHIBA.

Figure 1. TMP90C846 Block Diagram

2/98 TOSHIBA CORPORATION

# 2. Pin Assignments and Functions

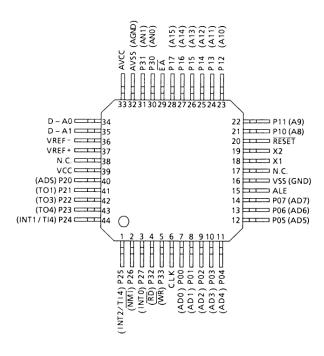

Figure 2.1 shows the TMP90C846F pin assignments.

The TMP90C846F, pin assignments, I/O pin names and functions are described in this section.

## 2.1 Pin Assignments

(Note) N.C.: No Connection

Figure 2.1. Pin Assignment (Mini Flat Package)

## 2.2 Pin Names and Functions

Table 2.2 shows the I/O pin names and functions.

**Table 2.2 Pin Assignments and Functions**

| Pin Name               | No. of pins | I/O or tristate | Function                                                                                                                                                                       |

|------------------------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00 ~ P07              | 8           | 1/0             | Port 0: An 8-bit I/O port. Each bit can be set for input or output.                                                                                                            |

| /AD0 ~ AD7             | 0           | Tristate        | Operates as an address/data bus during external program execution.                                                                                                             |

| P10 ~ P17<br>/A8 ~ A15 |             | 1/0             | Port 1: An 8-bit I/O port. Each bit can be set for input or output.                                                                                                            |

| /A8 ~ A15              | 0           | Output          | Address bus: Operates as the 8 upper bits of the address bus when using external memory.                                                                                       |

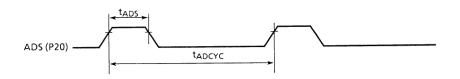

| P20<br>/ADS            | 1           | 1/0             | Port 20: A 1-bit I/O port. A/D conversion start: The input pin for the A/D conversion start signal.                                                                            |

| P21<br>/T01            | 1           | 1/0             | Port 21: A 1-bit I/O port. Timer output 1: Timer 0 or timer 1 output.                                                                                                          |

| P22<br>/T03            | 1           | 1/0             | Port 22: A 1-bit I/O port. Timer output 3: Timer 2 or timer 3 output.                                                                                                          |

| P23<br>/T04            | 1           | 1/0             | Port 23: A 1-bit I/O port.<br>Timer output 4: Timer 4 output.                                                                                                                  |

| P24<br>/INT1<br>/TI4   | 1           | 1/0             | Port 24: A 1-bit I/O port. Interrupt request pin 1: A rising/falling edge programmable interrupt request pin. Timer input 4: Timer 4 count input/capture trigger signal input. |

| P25<br>/INTT2<br>/TI5  | 1           | 1/0             | Port 25: A 1-bit I/O port. Interrupt request pin 2: A rising edge interrupt request pin. Timer input 5: Timer 4 capture trigger signal input.                                  |

| P26<br>/NMI            | 1           | 1/0             | Port 26: A 1-bit I/O port.  Non-maskable interrupt request pin: A falling edge interrupt request pin (after register setting).                                                 |

| P27<br>/INT0           | 1           | 1/0             | Port 27: A 1-bit I/O port. Interrupt request pin 0: A level/rising edge programmable interrupt request pin.                                                                    |

| P30, P31<br>/AN0, AN1  | 2           | Input           | Port 30, 31: 2-bit input ports. Analog input: Two analog inputs to the A/D converter.                                                                                          |

| P32<br>/RD             | 1           | Output          | Port 32: A 1-bit output port. Read: The strobe signal output for reading external memory.                                                                                      |

| P33<br>/WR             | 1           | Output          | Port 33: A 1-bit output port. Write: The strobe signal output for writing external memory.                                                                                     |

| D - A0,<br>D - A1      | 2           | Output          | D/A output: The analog voltage output pin for D/A converters 0/1.                                                                                                              |

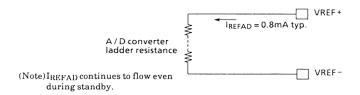

| VREF+                  | 1           | _               | A/D converter High reference voltage input.                                                                                                                                    |

| VREF-                  | 1           | -               | A/D converter Low reference voltage input.                                                                                                                                     |

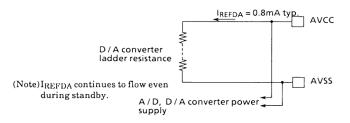

| A Vcc                  | 1           | -               | Used as both A/D converter and D/A converter power supply, and D/A reference voltage input.                                                                                    |

| A Vss                  | 1           | -               | Used as both the analog GND pin and D/A reference voltage.                                                                                                                     |

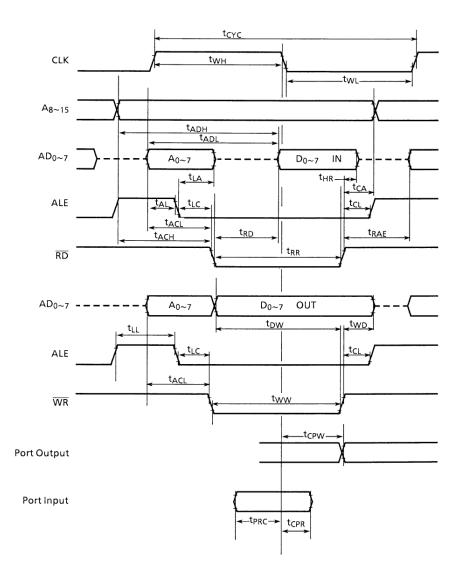

| ALE                    | 1           | Output          | Address latch enable: The falling edge of this signal is used as the timing for latching addresses on ADO - AD7 when accessing external memory.                                |

| CLK                    | 1           | Output          | Clock output: Outputs 1/4 frequency of clock oscillation. Pulled up internally during reset.                                                                                   |

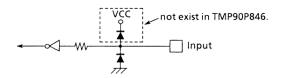

| ĒĀ                     | 1           | Input           | Connect to the $V_{CC}$ pin when the built-in ROM is used; connect to the GND pin when an external memory i used instead.                                                      |

| RESET                  | 1           | Input           | Reset: Initializes the TMP90C846. (pull-up resistor is built-in).                                                                                                              |

| X1/X2                  | 2           | 1/0             | The crystal/ceramic oscillator connection pin.                                                                                                                                 |

| V <sub>CC</sub>        | 1           | _               | Power supply (+5V)                                                                                                                                                             |

| V <sub>SS</sub> (GND)  | 1           | _               | GND pin (0V)                                                                                                                                                                   |

4/98 TOSHIBA CORPORATION

# 3. Operation

This section explains the functions and basic operations of the TMP90C846.

#### 3.1 CPU

The TMP90C846 has a built-in high-performance 8-bit CPU. Refer to the book TLCS-90 Series CPU Core Architecture concerning the CPU operation.

Following section explains the CPU functions unique to the TMP90C846 that are not explained in that book.

#### **3.1.1 Resets**

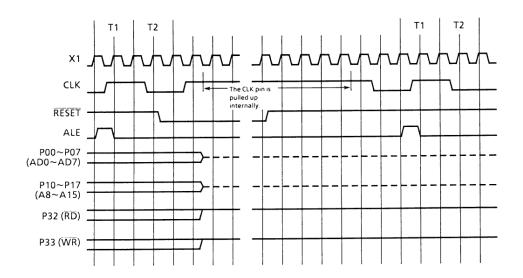

The basic reset timing is shown in Figure 3.1.

To reset the TMP90C846, it is necessary to maintain the  $\overline{\text{RESET}}$  input at "0" for at least 10 system clocks (10 states:  $2\mu\text{sec}$  @ 10MHz) with the power supply voltage within the operating range and with stabilized oscillation.

When a reset is received, I/O port 0 (address data bus AD0 ~ AD7), port 1 (address bus A8 ~ A15), and port 2 are all set to input status (high impedance). Output ports P32 ( $\overline{\text{RD}}$ ) and P33 ( $\overline{\text{WR}}$ ) and CLK are all set to "1". ALE is cleared to "0".The registers of the CPU also remain unchanged. Note, however, that the program counter PC, the interrupt enable flag IFF are cleared to "0". Register A shows an reset, because  $\overline{\text{WR}}$  is set to "1" before undefined address/data is outputted.

When the reset is released, instruction execution starts from address 0000H.

Figure 3.1. Reset Timing

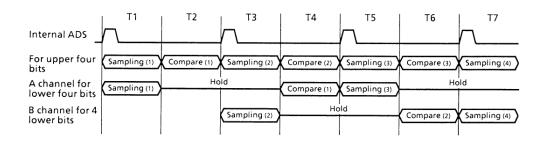

# 3.1.2 EXF (Exchange Flag)

The exchange flag <EXF> is assigned to bit 1 of memory address FFD2H. This flag is inverted when the register

exchange instruction [EXX] is executed between main registers and auxiliary registers.

|         |                 | 7                 | 6                                                                                                                | 5              | 4                                                                           | 3      | 2                        | 1                                                  | 0                                                    |

|---------|-----------------|-------------------|------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|--------|--------------------------|----------------------------------------------------|------------------------------------------------------|

| WDMOD   | bit Symbol      | WDTE              | WDTP1                                                                                                            | WDTP0          | WARM                                                                        | HALTM1 | HALTM0                   | EXF                                                | DRIVE                                                |

| (FFD2H) | Read/Write      | R/W               | R/                                                                                                               | w              | R/W                                                                         | R/V    | V                        | R                                                  | R/W                                                  |

|         | Resetting value | 1                 | 0                                                                                                                | 0              | 0                                                                           | 0      | 0                        | Indeterminate                                      | 0                                                    |

|         | Function        | 1 : WDT<br>Enable | WDT Dete<br>00 : 2 <sup>14</sup> /<br>01 : 2 <sup>16</sup> /<br>10 : 2 <sup>18</sup> /<br>11 : 2 <sup>20</sup> / | fc<br>fc<br>fc | Warming-<br>up time<br>0 : 2 <sup>14</sup> / fc<br>1 : 2 <sup>16</sup> / fc |        | mode<br>P mode<br>1 mode | Inverts each time the EXX instruction is executed. | 1 : Pin is<br>driven<br>even in<br>the STOP<br>mode. |

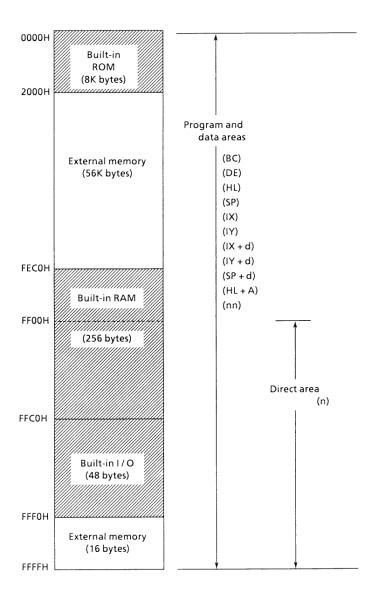

#### 3.2 Memory Map

The TMP90C846 can handle up to 64K bytes of program memory and data memory.

Program and data memory can be located at address  $00000H \sim FFFFH$ .

### (1) Built-in ROM

The TMP90C846 has 8 bytes of the built-in ROM located at addresses 0000H  $\sim$  1FFFH. After the CPU is reset, The instruction execution starts from address 0000H.

Addresses  $0010H \sim 0077H$  in the built-in ROM area are used as the entry are for interrupt processing.

#### (2) Built-in RAM

The TMP90C846 has 256 bytes of the built-in RAM

located at addresses FFCOH ~ FFBFH. In the direct addressing mode, the CPU allows the access to a certain RAM area (192 bytes at addresses FF00H ~ FFBFH) using short instruction codes.

Addresses of FF28H ~ FF77H this RAM area can be used as the parameter area for micro DMA processing. (This area can be used as RAM when not using micro DMA processing.)

## (3) Built-in I/O

The TMP90C846 uses 48 bytes of the address space as a built-in I/O area. This area is assigned to addresses FFC0H ~ FFEFH. In the direct addressing mode, the CPU can access the built-in I/O area using short instruction codes.

Figure 3.2 shows the memory map and the access ranges of the CPU for each addressing mode.

Note) The memory area is 64K bytes because there are no BX and BY registers as with the TMP90C840A.

Figure 3.2. Memory Map

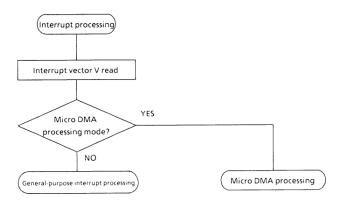

#### 3.3 Interrupt Functions

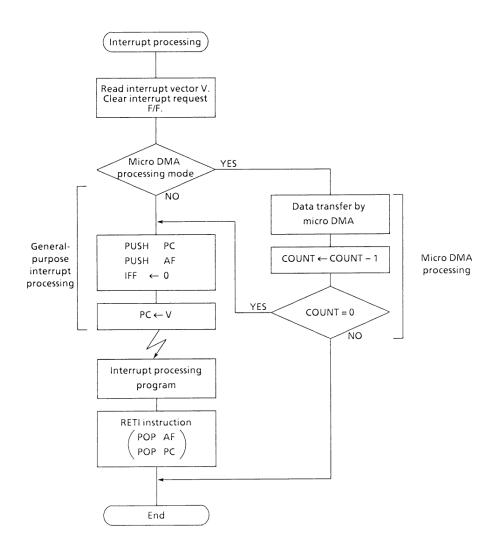

The TMP90C846 has a general-purpose interrupt processing mode and a micro DMA processing mode in which the CPU automatically transfers data for internal and external interrupt requests.

After a reset is released, all responses to interrupt requests

are set to the general-purpose interruot processing mode. The interrupt request can be set to the micro DMA processing mode with the DMA enable register which is described later.

The interrupt response flow chart is shown in Figure 3.3 (1).

Figure 3.3 (1). Interrupt Response Flow Chart

When an interrupt request is generated, this is reported to the CPU via built-in interrupt controller. The CPU starts the interrupt processing if it is a non-maskable interrupt or maskable interrupt requested in the EI state (interrupt enable flag (IFF bit of the F register) = "1"). A maskable interrupt requested in the DI state (IFF = "0") is ignored and not received. (The CPU samples interrupt requests at the falling edge of CLK signal of the last bus cycle of each instruction.)

When an interrupt is received, the CPU first reads the interrupt vector from the built-in interrupt controller to determine the interrupt request source.

Next, the CPU checks whether this request is for processed in the general-purpose interrupt processing or micro DMA processing, and performs the corresponding processing.

The interrupt vector is read in an internal operation cycle, so the bus cycle results in dummy cycle.

TOSHIBA CORPORATION 9/98

#### 3.3.1 General-Purpose Interrupt Processing

The general-purpose interrupt processing flow chart is shown in Figure 3.3 (2).

The CPU first saves the contents of the program counter PC and the register AF (including the interrupt enable flag IFF before an interrupt) to the stack, and resets the interrupt enable

flag IFF to "0" (interrupt disable). Then it transfers the content of the interrupt vector "V" to the program counter and jumps to the interrupt processing program.

There is a 20-state overhead from the time the interrupt is received until the jump is made to the interrupt processing program.

Figure 3.3 (2). General-Purpose Interrupt Processing Flowchart

The interrupt processing program ends with the RETI instruction for both maskable and non-maskable interrupts.

Executing this instruction (RETI) restores the contents of the program counter PC and the register AF from the stack. (Returns to the interrupt enable flag before the interrupt.)

When the CPU reads an interrupt vector, the interrupt request source confirms that the interrupt has been received, and clears the interrupt request.

A non-maskable interrupt cannot be disabled by program. A maskable interrupt, however, can be enabled or disabled by a program.

Bit 5 of the register F is the interrupt enable/disable flip-flop (IFF). Interrupts are enabled by setting this bit to "1" with the EI (endable interrupt) instruction and disabled by resetting to "0" with the DI (disable interrupt) instruction. IFF is reset to "0" by resetting or by receiving an interrupt (including non-maskable interrupts).

Interrupt enabled with the El instruction become effective when the next instruction after the El is executed.

The interrupt sources are shown in Table 3.3 (1).

Table 3.3 (1) Interrupt Sources

| Priority | Туре     | Interrupt request source           | Vector<br>Value<br>÷ 8 | Vector<br>Value | General-<br>purpose interrupt<br>processing<br>start address | Micro DMA<br>processing<br>parameter<br>start address |

|----------|----------|------------------------------------|------------------------|-----------------|--------------------------------------------------------------|-------------------------------------------------------|

| 1        | Non-     | SWI instruction                    | _                      | 10H             | 0010H                                                        | _                                                     |

| 2        | -        | NMI (NMI pin input (programmable)) | -                      | 18H             | 0018H                                                        | -                                                     |

| 3        | maskable | INT WD (watchdog)                  | _                      | 20H             | 0020H                                                        | -                                                     |

| 4        |          | INTO (External input 0)            | 05H                    | 28H             | 0028H                                                        | FF28H                                                 |

| 5        |          | INTTO (Timer 0)                    | 06H                    | 30H             | 0030H                                                        | FF30H                                                 |

| 6        |          | INTT1 (Timer 1)                    | 07H                    | 38H             | 0030H                                                        | FF38H                                                 |

| 7        |          | INTAD (A/D converter)              | 08H                    | 40H             | 0040H                                                        | FF40H                                                 |

| 8        | Maakabla | INTT2 (Timer 2)                    | 09H                    | 48H             | 0048H                                                        | FF48H                                                 |

| 9        | Maskable | INTT3 (Timer 3)                    | 0AH                    | 50H             | 0050H                                                        | FF50H                                                 |

| 10       |          | INTT4 (Timer 4)                    | 0BH                    | 58H             | 0058H                                                        | FF58H                                                 |

| 11       |          | INT1 (External input 1)            | 0CH                    | 60H             | 0060H                                                        | FF60H                                                 |

| 12       |          | INTT5 (Timer 5)                    | 0DH                    | 68H             | 0068H                                                        | FF68H                                                 |

| 13       |          | INT2 (External input 2)            | 0EH                    | 70H             | 0070H                                                        | FF70H                                                 |

The "priority" used in Table 3.3 (1) indicates the priority in which interrupt sources are received by the CPU when multiple interrupt requests are generated simultaneously.

For example, if the interrupt requests with the priority 4 and 5 are generated simultaneously, the CPU will receive the interrupt request with the priority 4 first. When the priority 4 interrupt processing is ended with the RETI instruction, the CPU will receive the interrupt with the priority 5. If the interrupt processing program with the priority 4 is interrupted by execting th El instruction, the CPU will receive the priority 5 interrupt request.

When multiple interrupt request are generated simultaneously, the built-in interrupt controller only determines the priority of the interrupt sources received by the CPU. There is no function for comparing the priority between the currently processed interrupt and the currently request interrupt.

Another interrupt can be enabled while an interrupt is processed by setting the interrupt enable flag IFF to enable.

TOSHIBA CORPORATION 11/98

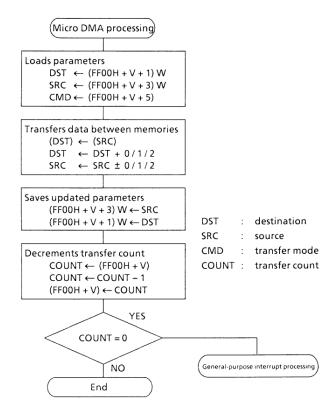

## 3.3.2 Micro DMA Processing

The micro DMA processing flow chart is shown in Figure 3.3 (3). The CPU first loads the parameters (transfer source and destination addresses, and transfer mode) for data transfer between memories from an address supplied by an interrupt vector value, and then transfers the data in accordance with those

parameters. After that, parameters are updated and saved to the original location. The transfer count is decremented, and the micro DMA processing is ended unless the count is not "0". If the count is "0", the general-purpose interrupt processing is performed as described in the previous item.

Figure 3.3 (3). Micro DMA Processing Flow Chart

The micro DMA processing is performed by using only hardware to process interrupts mostly completed by simple data transfer. Consequently, the micro DMA processing is faster than the conventional software processing, which in turn

improves the interrupt processing speed. The micro DMA processing has absolutely no influence on the CPU registers.

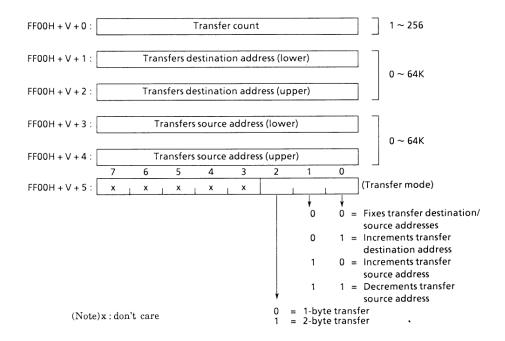

The functions of the parameters used in the micro DMA processing are shown in Figure 3.3 (4).

Figure 3.3 (4). Parameters for Micro DMA Processing

The parameters used for the micro DMA processing are located in the internal RAM (See Table 3.3 (1) Interrupt sources). The start address of each parameter is [FF00H + interrupt vector value], from which 6 bytes are used for the parameters. When micro DMA processing mode is not used, this area can be used as user memory.

The parameters include transfer count, transfer destination addresses, transfer source address, and transfer mode. The count indicates the number of data transfer accepted in the micro DMA processing. Either 1 or 2 bytes of data are transferred at one time with the micro DMA processing. Data are transferred

256 times with a transfer count of "00H". Transfer destination and transfer source addresses are each specified with 2 bytes of data. The address space 0000H - FFFFH is available for the micro DMA processing.

Bits 0 and 1 of the transfer mode specifies the mode updating the transfer source and/or destination. Bit 2 specifies the data length (1 or 2 bytes).

The relationship between the transfer mode and increment/ destination values of the transfer destination source addresses are shown in Table 3.3 (2).

TOSHIBA CORPORATION 13/98

| Transfer<br>Mode | Function                                                      | Destination address | Source<br>address |

|------------------|---------------------------------------------------------------|---------------------|-------------------|

| 000              | Transfer 1 byte: fixes transfer destination/source addresses. | 0                   | 0                 |

| 001              | Transfer 1 byte: increments transfer destination address.     | +1                  | 0                 |

| 010              | Transfer 1 byte : increments transfer source address.         | 0                   | +1                |

| 011              | Transfer 1 byte: decrements transfer source address.          | 0                   | -1                |

| 100              | Transfer 2 byte: fixes transfer destination/source addresses. | 0                   | 0                 |

| 101              | Transfer 2 byte: increments transfer destination address.     | +2                  | 0                 |

| 110              | Transfer 2 byte: increments transfer source address.          | 0                   | +2                |

| 111              | Transfer 2 byte: decrements transfer source address.          | 0                   | -2                |

In the 2-byte transfer mode, data are transferred as follows: (Destination address)  $\leftarrow$  (Source address)

(Destination address + 1)  $\leftarrow$  (Source address + 1)

Though transfers are performed as shown above in "decrement transfer source address mode", addresses are updated as shown in the Table 3.3 (2).

Address increment and decrement are used for the memory area, but fixed addresses are used for ordinary I/O addresses. Because of that, I/O to memory and memory to I/O transfers were taken into consideration during the micro DMA design.

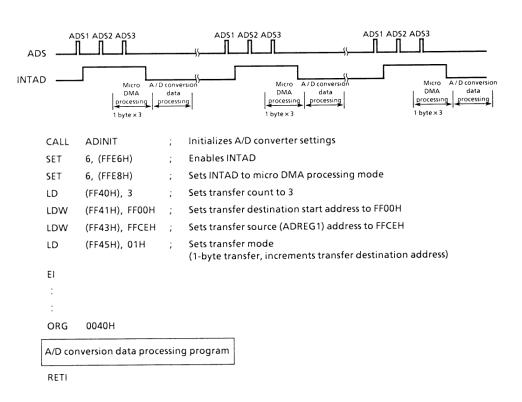

An example using the micro DMA processing mode is shown in Figure 3.3 (5). Conversion data of Built-in A/D converter are processed in this example.

This is an example of executing and "A/D conversion data processing program" after saving 3-byte conversion data into the memory addresses from FF00H to FF02H (built-in RAM area), by using INTAD which is enabled when the ADS1 conversion ends in a case where the external A/D conversion request signal (ADS) is entered as shown in Figure 3.3 (5).

Figure 3.3 (5). Micro DMA Processing Example

"Table 1.4 (2) Bus operation for each instruction" of the book TLCS-90 Series CPU Core Architecture shows the bus operations for general-purpose interrupt processing and micro DMA processing.

The execution time (when the transfer count is not 0 after decrementation) for micro DMA processing is 46 states (9.2 $\mu$ s @ 10MHz), regardless of whether the 1-byte or 2-byte transfer mode is used.

The interrupt processing flow chart is shown in Figure 3.3 (6).

Figure 3.3 (6). Interrupt Processing Flow Chart

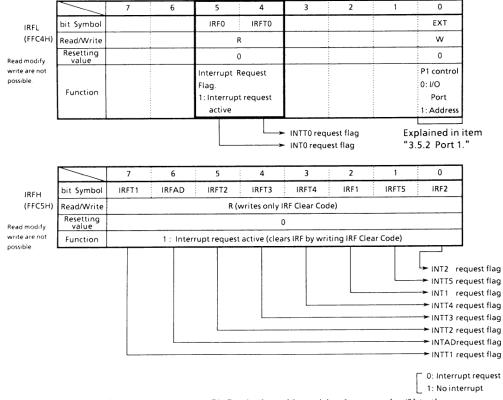

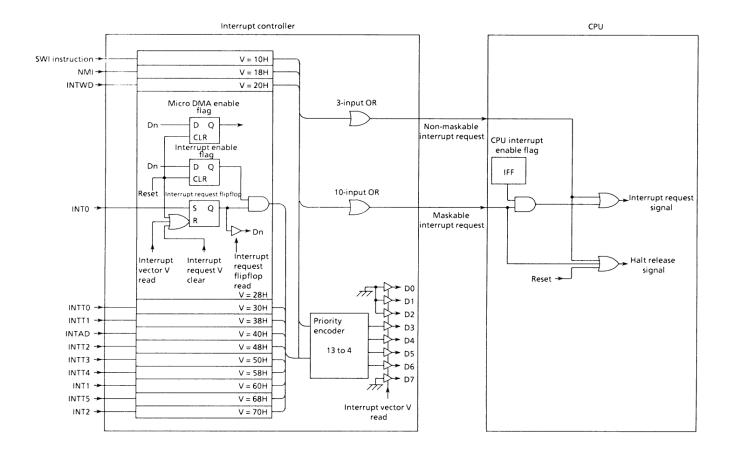

#### 3.3.3 Interrupt Controller

The interrupt circuit diagram is shown in Figure 3.3 (8). The left side of this diagram shows the interrupt controller, and the right side shows the CPU interrupt request signal circuit and halt release circuit.

The interrupt controller has an interrupt request flipflop and interrupt enable flag, and a micro DMA enable flag (10 channels) for each of 13 interrupt channels. The interrupt request flip-flop latches interrupt requests that arrive from peripherals.

This flipflop is cleared to "0", when the CPU receives a reset or an interrupt and reads the vector of that interrupt channel, or when an instruction that clears the interrupt

request (writes [vector/8] to the memory address FFC5H) for that channel is executed.

For example, when "LD (FFC5H), 38H/8" is executed, the interrupt request flip-flop for the interrupt channel [INT1] with the vector value 38H is cleared to "0" (write to FFC5H even when clearing the interrupt request flag assigned to FFC4H). When clearing an interrupt request, ensure that the interrupt source does not generate an interrupt request.

The status of the interrupt request flipflop can be checked by reading the memory address FFC4H or FFC5H. "0" means no interrupt request and "1" means an interrupt request. Figure 3.3 (7) shows the bit layout of the interrupt request flipflop.

(Note) The specified interrupt request flipflop is cleared by writing [vector value/8] to the memory address FFC5H. However, IRFAD (INTAD interrupt request flag) cannot be cleared by instructions; only by resetting or reading all FIFO data.

Figure 3.3 (7). Interrupt Request Flipflop Read

Figure 3.3 (8). Interrupt Circuit

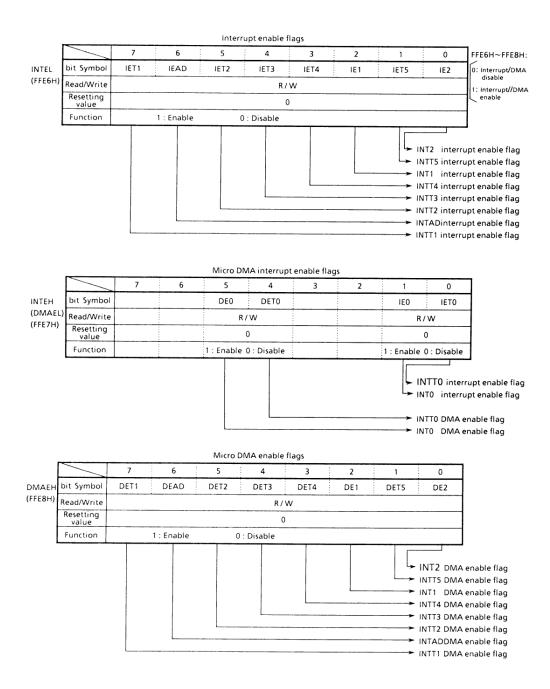

An interrupt enable flag is assigned to the memory address FFE6H or FFE7H for each interrupt request channel. Interrupts for a channel are enabled by setting a flag to "1". The flag is cleared to "0" by resetting.

Clear the interrupt enable flag in the Disable Interrupts (DI) state.

The micro DMA enable flag for each interrupt request channel is assigned to the memory address FFE7H or FFE8H.

The interrupt requests for each channel are set to the micro DMA processing mode by setting the flag to "1". The flag is cleared to "0" by resetting ("0" is the general-purpose interrupt processing mode).

Figure 3.3 (9) shows the bit layout for the interrupt enable flags and micro DMA enable flags.

The table below shows the external interrupt functions.

| Interrupt | Also Used as | Mode         | Setting Method                                      |

|-----------|--------------|--------------|-----------------------------------------------------|

| NMI       | P26          | Falling edge | NMI enable (by setting P2FR <nmic> = 1)</nmic>      |

| INTO      | D07          | Level        | P2FR <edge> = 0</edge>                              |

| INTO      | P27          | Rising edge  | P2FR <edge> = 0</edge>                              |

| INT1      | P24          | Rising edge  | T4MOD <capm1, 0=""> = 0, 0 or 0, 1 or 1, 1</capm1,> |

|           |              | Falling edge | T4M0D <capm1, 0=""> = 1, 0</capm1,>                 |

| INT2      | P25          | Rising edge  | -                                                   |

Refer to "4.8 Interrupt Operation" concerning the external

interrupt function pulse width.

Caution is required in the following two points as exceptions.

| INTO Level mode | This is not an edge-based interrupt, therefore interrupt request flipflop is cancelled. The peripheral interrupt request passes right through the flipflop S input and becomes the Q output.  When the mode is changed over (from edge type to level type), the previous interrupt request flag will be cleared automatically. When the mode is changed from level to edge, the interrupt request flag set in the level mode is not cleared. Thus, use the following sequence to clear the interrupt request flag.  DI  LD 6, (FFFC9H), 80H  LD (FFC5H), 05H  EI                                                            |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Mode change (edge to level)  Reset Interrupt request (to CPU)  Reset Interrupt request V read Interrupt request V clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | When the INTO level mode is used to clear the HALT (STOP) mode (the CPU in the EI state), an execution can be restarted from the interrupt vector address (0028H) by holding "1" until time preset by the warming-up counter. Note that if INTO is cleared to "0" during warming-up, an execution will restart from the instruction following the HALT instruction.  With the TLCS-90 and other products (TMP90C840A etc.), it is necessary to leave INTO at "1" until the second bus cycle of this interrupt response sequence is completed when INTO is set to "level". This restriction does not apply to the TMP90C846. |

| INTAD           | The interrupt request flipflop cannot be cleared by instructions; only by resetting or reading all FIFO data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 3.3 (9). Interrupt/Micro DMA Enable Flags

#### 3.4 Standby Function

The TMP90C846 can be set to the RUN, IDLE1, IDLE2 or STOP modedepending on the contents of the halt mode set register, by executing the HALT instruction. The features are shown below:

(1) RUN: Only the CPU halts, and the power consumption remains the same.

(2) IDLE1: Only the internal oscillators operate: all other internal circuits halt. The power consumption is 1/10 or less than that during the operation.

(3) IDLE2: Only the internal oscillator and specific built-in I/O operate. In this mode, the power consumption is about 1/3 or less during the operation.

(3) STOP: All internal circuits halt, including the oscillator. The power consumption is extremely reduced.

The HALT mode set register WDMOD <HALTM1, 0> is assigned to the bits 2 and 3 of memory address FFD2H in the built-in I/O register area (all other bits are used to control other functions). The RUN mode ("00") is entered by resetting.

The HALT is released by interrupt requests or resets. The methods for releasing the halt state are shown in Table 3.4 (2). The CPU receives non-maskable interrupt or maskable interrupts EI state and starts interrupt processing. If maskable interrupts are disable (DI state), the CPU restarts an execution from the instruction following the HALT instruction, but the interrupt request flag remains at "1".

When Halt state is released by a reset, the state in effect before entering the halt state (including the built-in RAM) is held. The RAM contents may not be held; however, if the HALT instruction is executed within the built-in RAM.

|         |                 | 7                 | 6                                                                             | 5                 | 4                                                                       | 3                                            | 2                             | 1                                                   | 0                                                    | ] |

|---------|-----------------|-------------------|-------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------|----------------------------------------------|-------------------------------|-----------------------------------------------------|------------------------------------------------------|---|

| WDMOD   | bit Symbol      | WDTE              | WDTP1                                                                         | WDTP0             | WARM                                                                    | HALTM1                                       | HALTM0                        | EXF                                                 | DRIVE                                                |   |

| (FFD2H) | Read/Write      | R/W               | R/                                                                            | W                 | R/W                                                                     | R                                            | w                             | R                                                   | R/W                                                  |   |

|         | Resetting value | 1                 | 0                                                                             | 0                 | 0                                                                       | 0                                            | 0                             | Undefined                                           | 0                                                    |   |

|         | Function        | 1 : WDT<br>Enable | Detectio<br>00: 2 <sup>14</sup><br>01: 2 <sup>16</sup><br>10: 2 <sup>18</sup> | /fc<br>/fc<br>/fc | Warming-<br>up time<br>0: 2 <sup>14</sup> /fc<br>1: 2 <sup>16</sup> /fc | Standby m<br>00 : RU<br>01 : ST(<br>10 : IDI | N mode<br>OP mode<br>.E1 mode | Inverted each time the EXX instruction is executed. | 1 : Pin is<br>driven<br>even in<br>the STOP<br>mode. |   |

|         |                 | Explain           | 11:2 <sup>20</sup>                                                            |                   | mer                                                                     |                                              |                               | ↓ Mo                                                | plained in 3.<br>ode<br>plained in 3.                |   |

Figure 3.4 (1). Halt Mode Set Register

## **3.4.1 RUN Mode**

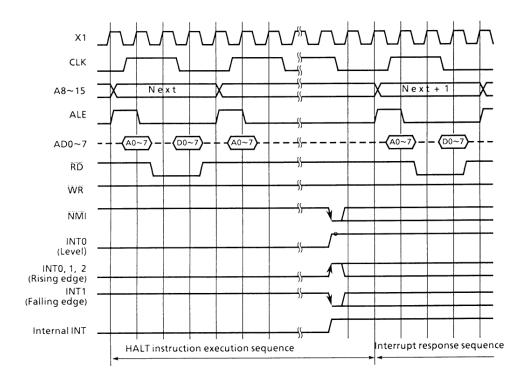

The timing for releasing the halt state by interrupts in the RUN/IDLE2 modes is shown in Figure 3.4 (2).

In the RUN mode, the system clock in the MCU does not stop even after HALT instruction is executed; the CPU merely

stops executing the instruction. The CPU repeats dummy cycles until halt state is released. In the halt state, interrupt request are sampled at the falling edge of the CLK signal.

The halt state is released by external interrupt (INT1, INT2) requests only in the RUN mode.

Figure 3.4 (2). Halt Release Timing Using Interrupts in the RUN/IDLE2 Modes

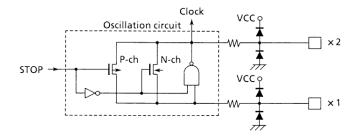

## 3.4.2 IDLE 1 Mode

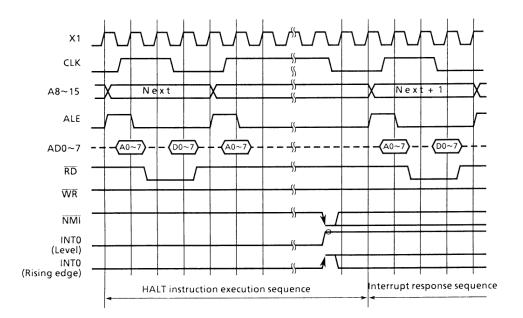

The timing for releasing the halt state by interrupts in the IDLE1 mode is shown in Figure 3.4 (3).

In the IDLE1 mode, only the internal oscillator and the watchdog timer operate. The system clock in the MCU stops, and the CLK signal is fixed at the "1".

In the HALT mode, interrupt requests are sampled

asynchronously with the system clock. However, the halt release (restart of operation) is performed synchronously with the system clock.

(Note) In this mode, only the external interrupt requests (NMI, INTO) are enabled during the halt interval in the IDLE1 mode.

Figure 3.4 (3). Halt Release Timing Using Interrupts in the IDLE1 Mode

TOSHIBA CORPORATION 23/98

#### **3.4.3 IDLE2 Mode**

The timing used for releasing the halt state by interrupts in the RUN/IDLE2 mode is shown in Figure 3.4 (2).

The timing for releasing the halt state by interrupts in the IDLE2 mode is the same as in the RUN mode. However, the internal operating mode of the MCU differs. In the RUN mode, only the execution of instruction by the CPU is halted, but the system clock is still supplied to all MCUs. In the IDLE2 mode, however, the system clock is supplied only to specific I/O. Because of that, the power consumption in the halt state of

the IDLE2 mode is about 1/3 or less of that of the RUN mode. In the IDLE2 mode, the system clock is supplied to the following built-in I/O.

- 8-bit timers

- 16-bit timers

- Watchdog Timer

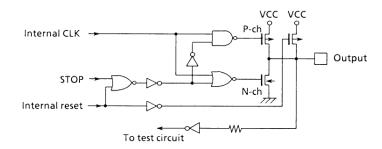

#### 3.4.4 STOP Mode

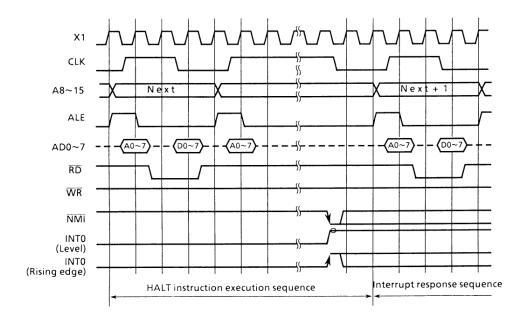

The timing for releasing the halt with state by interrupts in the STOP mode is shown in Figure 3.4 (4).

In the STOP mode, all internal circuits stop, including the internal oscillator. When the STOP mode is activated, all but certain pins are isolated from the MCU by being set to high impedance.

The state of each pin in the STOP mode is shown in Table 3.4 (1). The status in effect before the halt state continues if WDMOD <DRVE> (drive enable: bit 0 of memory address FFD2H) of the built-in I/O register is set to "1". This register is

cleared to "0" by resetting.

The internal oscillator starts first when the CPU receives an interrupt request; however, to allow oscillation to stabilize, the system clock starts its output after the time set by the warming-up counter. WDMOD <WARM> (warming-up: bit 4 at the memory address FFD2H) is used to set the warming-up time. Clearing this bit to "0" sets the warming-up time to the time required for  $2^{14}$  clock oscillations. Setting this bit to "1" sets the warming-up time to the time required for  $2^{16}$  clock oscillations. This bit is initialized to "0" by resetting.

Figure 3.4 (4). HALT Release Timing Using Interrupt in STOP Mode

The internal oscillator can be also restarted by the input of the RESET signal "0" to the CPU; however, the warming-up counter does not operate to permit operation to start quickly immediately after power-on. The normal operation may not be

performed due to the unstable clock supplied immediately after restarting the internal oscillator. To avoid this, it is necessary to keep the RESET signal must at "0" long enough to release the halt state in the STOP mode.

TOSHIBA CORPORATION 25/98

Table 3.4 (1) STOP Mode Pin Status

|                         | In/Out                                | DRVE = 0          | DRVE = 1            |

|-------------------------|---------------------------------------|-------------------|---------------------|

| P0                      | Input mode<br>Output mode             |                   | –<br>Output         |

| P1                      | Input mode<br>Output mode             |                   | –<br>Output         |

| P20                     | Input mode<br>Output mode             | Input<br>–        | Input<br>Output     |

| P21 ~ 23                | Input mode<br>Output mode             |                   | Input<br>Output     |

| P24 ~ 25                | Input pin<br>Output pin               |                   | Input*<br>Output    |

| P26 (NMI)<br>P27 (INTO) | Input pin<br>Output pin               | Input<br>–        | Input<br>Output     |

| P30 ~ P31               | Output mode                           | _                 | Output              |

| P32 ~ P33               | Output mode                           | -                 | Output              |

| D - A0, D - A1          | Output mode                           | 0V                | 0V                  |

| ALE<br>CLK<br>RESET     | Output pin<br>Output pin<br>Input pin | "O"<br>—<br>Input | "0"<br>"1"<br>Input |

| X1<br>X2                | Input pin<br>Output pin               | _<br>"1"          | _<br>"1"            |

This pin remains intermediately biased in the zero-cross detect mode.

Input mode/input pin indicates that input is invalid. -:

Input: Input is enabled.

The input gate is working. Fix the input voltage at "0" or "1" to

prevent the pin floating.

Output: Output status.

Table 3.4 (2) I/O Operation and Cancel during Halt Mode

|           | Halt m                                                                                  | ode      | RUN     | IDLE2                         | IDLE1 | STOP               |  |  |  |

|-----------|-----------------------------------------------------------------------------------------|----------|---------|-------------------------------|-------|--------------------|--|--|--|

|           | WDMOD <ha< td=""><td>LTM1, 0&gt;</td><td>00</td><td>11</td><td>10</td><td>01</td></ha<> | LTM1, 0> | 00      | 11                            | 10    | 01                 |  |  |  |

|           | CPU                                                                                     |          | Stopped |                               |       |                    |  |  |  |

|           | I/O port                                                                                |          | Hol     | ds status before HALT instruc | tion. | See Table 3.4 (2). |  |  |  |

|           | 8-bit timer                                                                             |          |         |                               |       |                    |  |  |  |

| Operation | 16-bit timer                                                                            |          | Ope     | ration                        |       | _                  |  |  |  |

| Block     | Watchdog time                                                                           | er       |         |                               |       | Stopped            |  |  |  |

|           | A/D converter                                                                           |          |         |                               |       | _                  |  |  |  |

|           | D/A converter                                                                           |          | Hol     | ds status before HALT instruc | tion. | See Table 3.4 (2). |  |  |  |

|           | Interrupts con                                                                          | troller  |         | Oper                          | ating |                    |  |  |  |

|           |                                                                                         | NMI      | 0       | 0                             | 0     | 0                  |  |  |  |

|           |                                                                                         | INTWD    | 0       | 0                             | _     | _                  |  |  |  |

|           |                                                                                         | INT0     | 0       | 0                             | 0     | 0                  |  |  |  |

|           |                                                                                         | INTT0    | 0       | 0                             | _     | -                  |  |  |  |

|           |                                                                                         | INTT1    | 0       | 0                             | _     | -                  |  |  |  |

| Halt      | Interrupt                                                                               | INTAD    | 0       | _                             | _     | _                  |  |  |  |

| Releasing | Intorrupt                                                                               | INTT2    | 0       | 0                             | _     | -                  |  |  |  |

| Source    |                                                                                         | INTT3    | 0       | 0                             | _     | -                  |  |  |  |

|           |                                                                                         | INTT4    | 0       | 0                             | -     | -                  |  |  |  |

|           |                                                                                         | INT1     | 0       | 0                             | _     | -                  |  |  |  |

|           |                                                                                         | INTT5    | 0       | 0                             | _     | _                  |  |  |  |

|           |                                                                                         | INT2     | 0       | 0                             | -     | -                  |  |  |  |

|           | RESET                                                                                   |          | 0       | 0                             | 0     | 0                  |  |  |  |

O: Can be used for HALT release.

-: Cannot be used for HALT release.

## 3.5 Port Functions

The TMP90C846 has a total of 28 I/O port pins. These ports pins can be used not only for the general-purpose I/O function

but also for the I/O function of the internal CPU and I/O. The functions of each port pin are shown in Table 3.5.

**Table 3.5 Port Functions**

| Port name | Pin name                                             | No. of pins                | Direction                                     | Direction set unit                            | Resetting status                   | Internal function pin name                                      |

|-----------|------------------------------------------------------|----------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------|-----------------------------------------------------------------|

| Port 0    | P00 ~ P07                                            | 8                          | 1/0                                           | Bit                                           | Input                              | ADO ~ AD7                                                       |

| Port 1    | P10 ~ P17                                            | 8                          | 1/0                                           | Bit                                           | Input                              | A8 ~ A15                                                        |

| Port 2    | P20<br>P21<br>P22<br>P23<br>P24<br>P25<br>P26<br>P27 | 1<br>1<br>1<br>1<br>1<br>1 | 1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0 | Bit<br>Bit<br>Bit<br>Bit<br>Bit<br>Bit<br>Bit | Input                              | ADS<br>T01<br>T03<br>T04<br>INT1/TI4<br>INT2/TI5<br>NMI<br>INT0 |

| Port 3    | P30<br>P31<br>P32<br>P33                             | 1<br>1<br>1<br>1           | Input<br>Input<br>Output<br>Output            | -<br>-<br>-<br>-                              | Input<br>Input<br>Output<br>Output | AN0<br>AN1<br>RD<br>WR                                          |

These port pins function as the general-purpose input/output pins by resetting. All port pins that can be programmed for

input or output are set as input ports. The port pins must be set for the internal functions by a program.

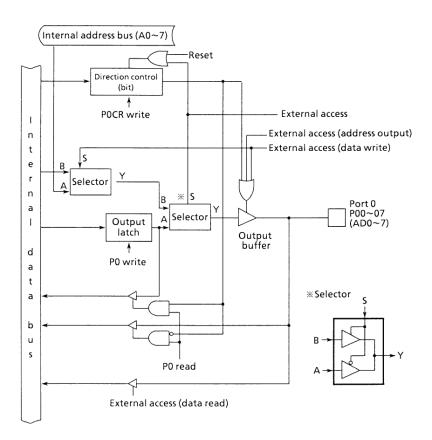

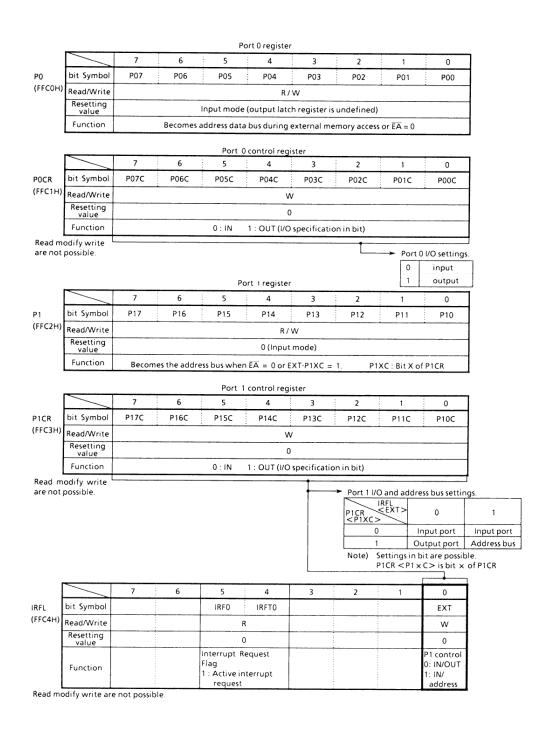

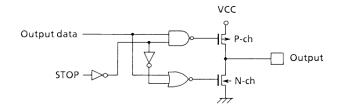

## 3.5.1 Port 0 (P00 ~ P07)

Port 0 is the 8-bit general-purpose I/O port whose I/O function is specified by the control register P0CR in bit basis. A reset operation clears all bits of the control register (P0) to "0" and sets Port 0 to the input mode. The contents of the output latch register become undefined.

In addition to the general-purpose I/O port function, Port 0 also functions as an address/data bus (AD0  $\sim$  AD7). When the external memory is accessed, Port 0 automatically functions as the address/data bus and P0CR is cleared to "0". Therefore, to use port 0 as an output port again after the external access, it is necessary to set the P0CR to "1" again.

Figure 3.5 (1). Port 0

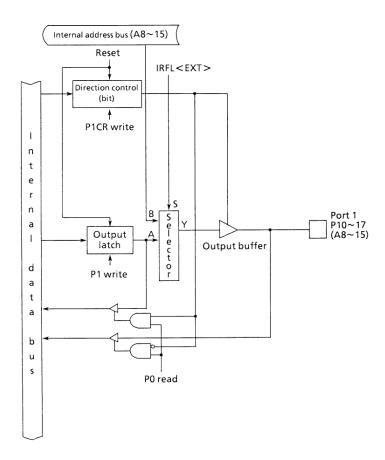

## 3.5.2 Port 1 (P10 ~ P17)

Port 1 is the 8-bit general-purpose I/O port whose I/O function is specified by the control register P1CR in bit basis.

A reset operation clears all bits of the output latch (P1) and the control register (P1CR) to "0" and sets Port 1 to the input mode.

In addition to the general-purpose I/O port function, Port 1

also functions as the address bus (A8 ~ A15). The function is selected by setting the external extension control register IRFL<EXT> to "1" and setting P1CR to the output mode. When the P1CR cleared to "0", Port 1 is set to the input mode, regardless of the external extension control register <EXT> value. Resetting clears <EXT> to "0" and sets Port 1 to the general-purpose I/O port mode.

Figure 3.5 (2). Port 1

Figure 3.5 (3). Registers for Port 0/1

TOSHIBA CORPORATION 31/98

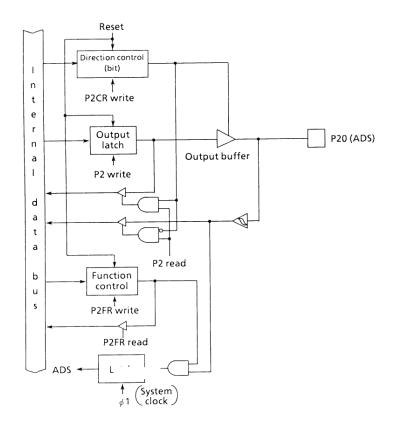

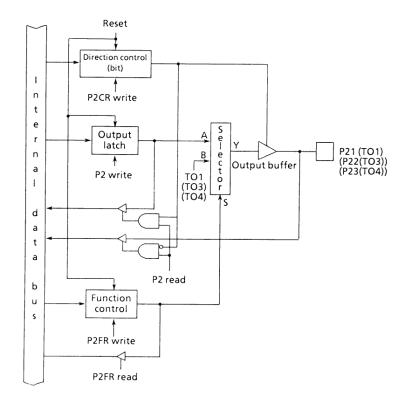

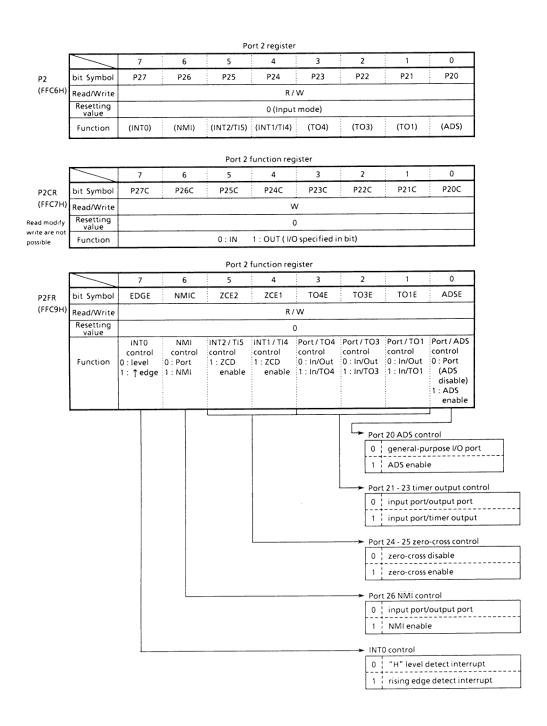

## 3.5.3 Port 2 (P20 ~ P27)

Port 2 is a 8-bit general-purpose I/O port whose I/O function is specified by the control register P2CR in bit basis.

A reset operation clears all bits of the output latch (P2) and control register (P2CR) to "0" and sets Port 2 to the input mode.

In addition to its I/O port function, Port 2 also functions as an external A/D conversion start pin, timer output pin, timer/event counter clock input pin and external interrupt request pin.

#### (1) P20 (ADS)

P20 is a general-purpose I/O port used both as the external A/D conversion start: ADS pin.

The Port 2 function register P2FR <ADSE> is used to set P20 to function as the ADS pin.

P20 is set as the ADS input pin by writing <ADSE>= "1".

P20 is set as the ADS input pin by writing <ADSE> = "1". A reset operation clears P2CR <P20C> and P2FR <ADSE> to "0" and sets P20 to input port.

## (2) P21 (TO1), P22 (TO3), P23 (TO4)

P21 - P23 are general-purpose I/O ports also used as timer output pins.

The port 2 function register P2FR <T01E, T03E, T04E> and port 2 control register P2CR <P21C,

P22C, P23C> are used to set the timer output pin.

The timer output pin is set by writing "1" to both the control

The timer output pin is set by writing "1" to both the control register and function register.

A reset operation clears P2CR <P21C, P22C, P23C> and P2FR <T01E, T03E, T04E> to "0" and sets P21 - P23 to the input port.

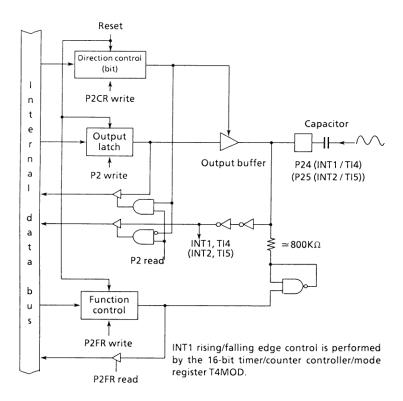

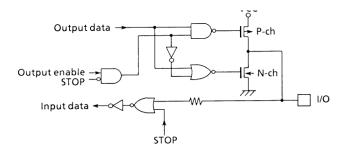

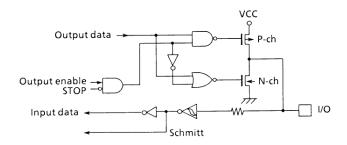

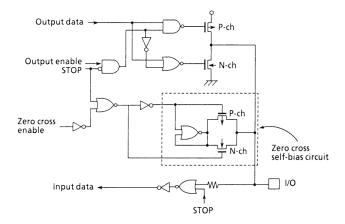

## (3) P24 (INT1/TI4), P25 (INT2/TI5)

P24 and P25 are general-purpose I/O ports, also used both as external interrupt request input pins (INT1, INT2) and timer/event counter clock input pins (TI4, TI5).

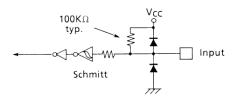

These ports have built-in zero cross detection circuits

and can be used for zero cross detection by connecting an external capacitor. The zero cross detection function is enabled by writing "1" to <ZCE1, ZCE2> of the Port 2 function register P2FR.

A reset operation clears P2CR <P24C, P25C> and P2FR <ZCE1, ZCE2> to "0" and sets P24 - P25 to the input port.

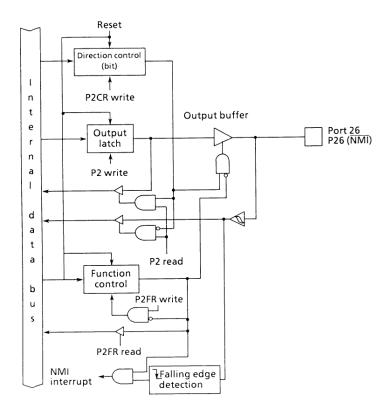

# (4) P26 (NMI)

P26 is a general-purpose I/O port, also used as the non-maskable interrupt  $\overline{\text{NMI}}$  input pin. The Port 2 function register P2FR <NMIC> is used to set the  $\overline{\text{NMI}}$  pin mode.

It is necessary to write "1" to <NMIC> when P26 is

used as the  $\overline{\text{NMI}}$  input pin (this does not depend on the Port 2 control register P2CR <P26C>).

Once set the  $\overline{\text{NMI}}$  input pin mode, P26 can only be returned to the general-purpose I/O port mode by resetting.

A reset operation clears P2CR <P26C> and P2FR <NMIC> to "0" and sets P26 to the input port.

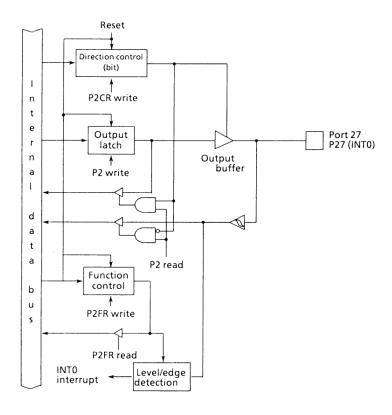

# (5) P27 (INTO)

P27 is a general-purpose I/O port, also used as the external interrupt request input pin INTO.

INTO can be set for either "H" level interrupt or rising edge interrupt with the Port 2 function register P2FR <EDGE>.

Figure 3.5 (6). Registers for Port 2

TOSHIBA CORPORATION 37/98

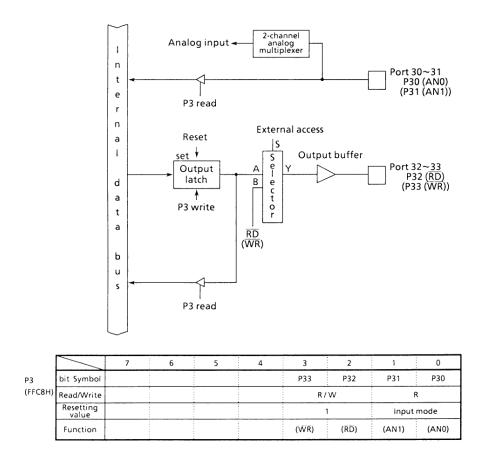

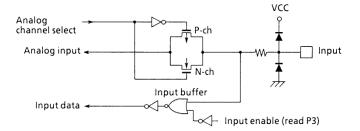

## 3.5.4 Port 3 (P30 ~ P33)

Port 3 is the 4-bit general-purpose I/O port. P30 and P31 are used for input only; P32 and P33 are used for output only.

P30 and P31 function both as a 2-bit input port and A/D converter analog input pins AN0 and AN1.

P32 and P33 are used both as a 2-bit output port and for the external memory control functions  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$ . The output latch for P32 and P33 is set to "1" by resetting and outputs "1".

When the external memory is accessed, P32 and P33

automatically function as the memory control pins  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$ . When the external memory is accessed, P32 and P33 automatically function as the memory control pins  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$ . When the internal memory is accessed, P32 and P33 function as the output port. Therefore, for accessing the external memory, leave the output latch register of P32 ( $\overline{\text{RD}}$ ) and P33 ( $\overline{\text{WR}}$ ) to "1", a value immediately set after resetting.

Figure 3.5 (7). Port 3

#### 3.6 Timers

The TMP90C846 has four 8-bit timers and one multi-function 16-bit timer/event counter.

These four 8-bit timers can be operated independently or cascade connected to form two 16-bit timers. The 8-bit timers have the following four operating modes.

- 8-bit interval timer modes (4)

- 16-bit interval timer modes (2)

- The two above can be combined (8 bits x 2, 16 bits x 1)

- 8-bit Programmable Pulse Generation (PPG; variable duty at variable interval) output modes (2)

- 8-bit PWM (pulse width modulation: variable duty at fixed interval) output mode (2)

The multi-function 16-bit timer/event counter has the following six operating modes.

- 16-bit interval timer mode

- 16-bit event counter mode

- 16-bit PPG (variable duty at variable interval) output mode

- Frequency measurement mode

- Pulse width measurement mode

- Time deviation measurement mode

#### 3.6.1 8-bit Timers

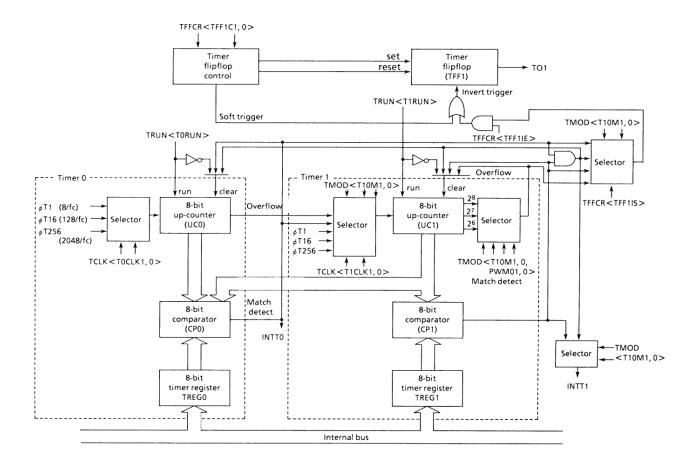

The TMP90C846 has four 8-bit interval timers (timer 0, 1, 2 and 3), each of which can be operated independently. Timer 0 and 1, or Timer 2 and 3 can be cascade-connected and used as 16-bit interval timers.

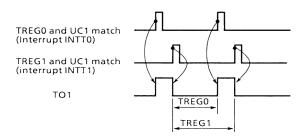

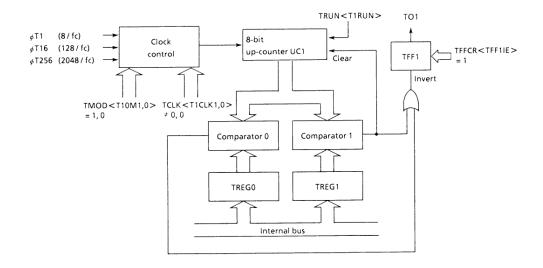

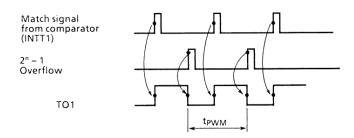

The block diagram of the 8-bit timers (Timers 0 and 1) is shown in Figure 3.6 (1).

Timers 2 and 3 have the same circuit configuration as Timers 0 and 1 respectively.

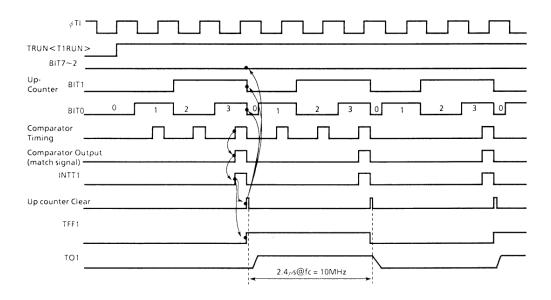

Each interval timer comprises an 8-bit up-counter, an 8-bit comparator, and an 8-bit timer register. One timer flip-flop (TFF1, TFF3) is provided for each pair of Timer 0/1 and Timer 2/3.

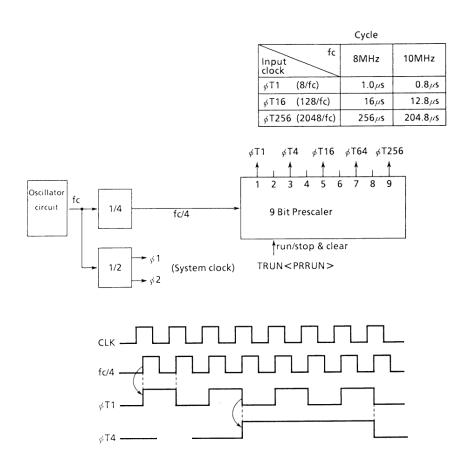

The internal clocks øT1, øT16, and øT256 used as the input clocks to the interval timers are obtained from the 9-bit prescaler shown in Figure 3.6 (2).

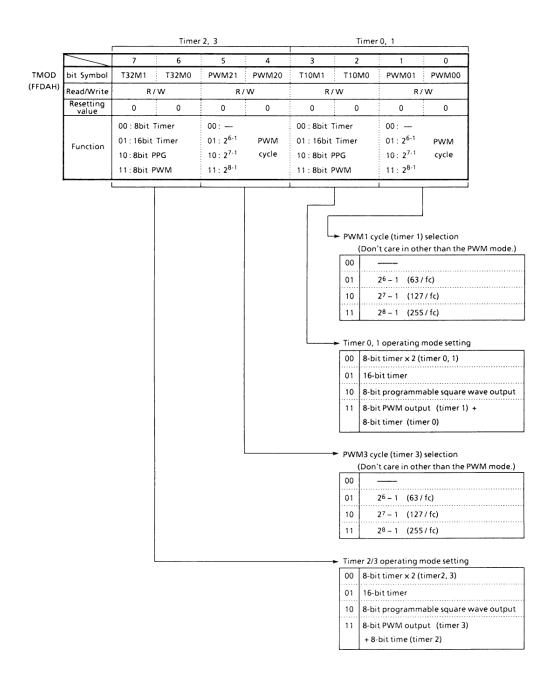

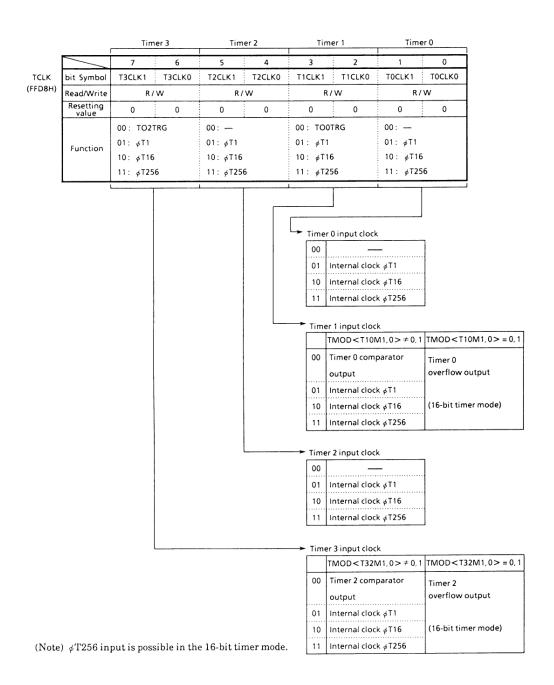

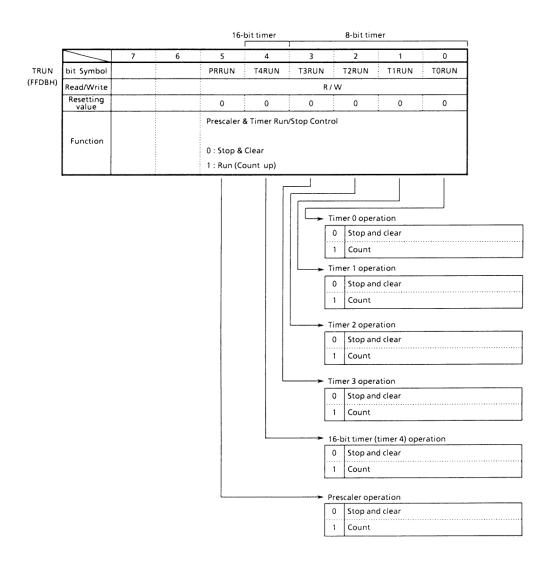

The operating modes and timer flip-flops for the 8-bit timers are controlled by four control registers (TCLK, TFFCR, TMOD and TRUN).

Figure 3.6 (1). 8-bit Timers Block Diagram (Timers 0 and 1)

## ① Prescaler

This 9-bit prescaler generates the clock input to the 8-bit timers and 16-bit timer/event counters by further dividing the fundamental clock after it has been divided by 4 (fc/4).

The three clocks  $\emptyset T1$ ,  $\emptyset T16$  and  $\emptyset T256$  are used for the 8-bit timers.

This prescaler is run and stopped with the timer operation control register TRUN <PRRUN>. Setting <PRRUN> to "1"starts counting and setting <PRRUN> to "0" stops and clears the prescaler to "0" and stops. Resetting clears <PRRUN> to "0", which clears and stops the prescaler.

Figure 3.6 (2). Prescaler

2 Up-counter

This is an 8-bit binary counter that counts up the input clock specified by the 8-bit timer clock control register TCLK and 8-bit timer mode register TMOD.

The input clock of Timers 0 and 2 can be selected from the three internal clocks  $\emptyset$ T1 (8/fc),  $\emptyset$ T16 (128/fc),  $\emptyset$ T256 (2048/fc) in accordance with the TCLK setting value.

Example: Setting TCLK <T0CLK1, 0> = 0, 1 selects  $\emptyset$ T1 as the input clock for Timer 0.

The input clock selection for Timers1 and 3 differs depending on the operating mode. When the 16-bit timer mode is set, the overflow output of Timer 0 or 2 is used as the input cock, regardless of the TCLK register setting.

In the other modes, the input clock is selected among the internal clocks øT1, øT16, øT256, and the output

of the Timers 0 and 2 comparator (match detection) by setting the TCLK register.

Example: If TMOD <T10M1, 0> = 0, 1, the overflow output of Timer 0 is used as the input clock to

Timer 1 (16-bit timer).

If TMOD <T10M1, 0> = 00 and T01MOD <T1CLK1, 0> = 0, 0, and <T1CLK1, 0> = 0, 1,  $\emptyset$ T1 is used as the input clock to Timer 1 (8-bit timer).

The TMOD register is also used to set the operating mode. Resetting initializes to TMOD <T10M1, 0 > 0, 0/TMOD < T32M1, 0 > 0, therefore, 8-bit timer mode is set.

Each up-counter can be run, stopped and cleared with the timer control register TRUN. Resetting stops all timers and clears all up-counters.

Figure 3.6 (3). 8-bit Timer Mode Register TMOD

TOSHIBA CORPORATION 43/98

Figure 3.6 (4). 8-bit Timer Clock Control Register TCLK

44/98 TOSHIBA CORPORATION

Figure 3.6 (5). Timer Control Register TRUN

Figure 3.6 (6). 8-bit Timer Flip-flop Control Register TFFCR

46/98

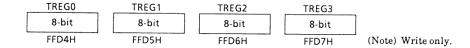

# 3 Timer registers

This is an 8-bit register used to set the interval time. When the set value of a timer register matches to that of an up-counter, the match signal of comparators becomes active. When the set value is 00H, the match signal becomes active when an up-counter overflows. When a new value is written to this register, it is immediately input to the comparator.

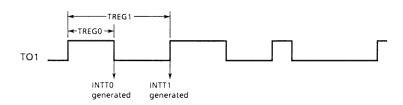

#### Comparators

When a comparison of an up-counter value and a timer register value show a match, the up-counter is cleared to "0" and an interrupt signal (INTTO ~ INTT3) is generated. If the timer flip-flop inversion is enabled, the timer flip-flop value is inverted at the same time.

#### ⑤ Timer flip-flop (Timer F/Fs)

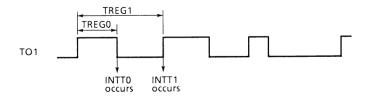

This flip-flop is inverted by the match signals (comparator output) of the interval timer. The value can be output to the timer output pins TO1 (also used as P21) and TO3 (also used as P22).

A Timer F/F is provided to each of the Timer 0/1 pair (TFF1) and Timer 2/3 pair (TFF3). The TFF1 value is

output to the TO1 pin and the TFF3 value to the TO3 pin.

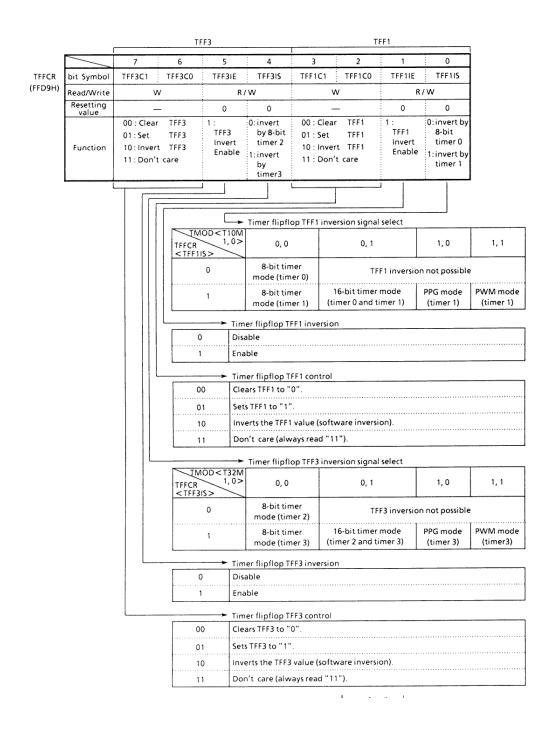

The timer F/F is controlled by the timer flip-flop control register TFFCR.

TFF1 (Timer 0/1 timer flip-flop) is used below for explanatory purposes. (Refer to Figure 3.6 (6).)

• TFFCR <FF1IS> is a selection bit for the TFF1 invert signal. In the 8-bit timer mode, <FF1IS> should be to "0" when the match signal from Timer 0 is used, and should be set to "1" when the match signal from Timer 1 is used.

In any other mode, always keep <FF1IS> set to "1". Resetting clears <FF1IS> to "0".

• TFFCR1 <FF1IS> is the TFF1 invert enable bit. Set this bit to "1" to enable inversion and clear to "0" to disable inversion.

Resetting clears <FF1IS> to "0".

• TFFCR <TFF1C 1, 0> is the TFF1 set/reset and software inversion bit. Writing "0, 0" resets TFF1, writing "0, 1" sets TFF1 and writing "1, 0" inverts the TFF1 value. Similarly, the TFF3 is controlled by the upper four bits TFFCR <TFF2C1, 0, TFF3IE, S>.

The following is an explation of the 8-bit timer operation:

## (1) 8-bit timer mode

The four interval timers 0, 1, 2 and 3 can be used independently as an 8-bit interval timers. The operation is the same as for all of the timers. Thus, Timer 1 will be used here for explanatory purposes.

① Generating interrupts in a fixed cycle

To use Timer 1 for generating Timer 1 interrupts (INTT1) in a fixed cycle, first stop Timer 1 and then set the operation mode, input clock and cycle to the TMOD, TCLK and TREG1 registers. Next, enable the interrupt INTT1 and then start Timer 1 counting.

Example: Use the following procedure to set the registers to generate Timer 1 interrupts every  $40\mu s$  (fc = 10MHz).

```

MSR

7 6 5 4 3 2 1 0

Stops Timer 1 and clears it to "0"

TRUN

Sets the 8-bit timer mode.

TMOD

----00XX

Sets the input clock to \phi T1 (0.8 \mus @ fc = 10MHz).

----01--

TCLK ←

Sets 40 \mus ÷ \phiT1 = 32H to the timer register.

TREG1 ←

0 0 1 1 0 0 1 0

INTEH ←

Enables INTT 1.

Starts Timer 1.

TRUN ←

--1--1-

```

(Note) × ; don't care -; no change

Refer to the table below for selecting the input clock:

Table 3.6 (1) Interrupt Cycle and Input Clock Using 8-bit Timer

| Interrupt cycle<br>@fc = 10MHz | Resolution | Input clock     |  |

|--------------------------------|------------|-----------------|--|

| 8µs ~ 204.8µs                  | 8µs        | øT1 (8/fc)      |  |

| 12.8µs ~ 3.2768ms              | 12.8µs     | øT16 (128/fc)   |  |

| 204.8µs ~ 52.42ms              | 204.8µs    | øT256 (2048/fc) |  |

# ② Generating pulse at 50% duty

Invert the timer flipflop at a fixed cycle and output the timer flipflop value to the timer output pin (TO1).

Example: Use the following procedure to set the register to output a pulse from the TO1 pin in a 4.8µs cycle at fc = 10MHz. Timer 0 or 1 is used in this case, but Timer 1 will be used for explanatory purposes.

```

MSB

LSB

7 6 5 4 3 2 1 0

TRUN

Stops Timer 1 and clears it to "0".

TMOD

Sets the 8-bit timer mode.

TCLK

---01--

Sets the input clock to \phi T1.

TREG1 ←

0 0 0 0 0 0 1 1

Sets (4.8 \mus ÷ \phiT1) ÷ 2 = 3 to the timer register.

Clears TFF1 to "0" and sets inversion with the match

TFFCR ←

--0011

signal from Timer 1.

Sets P21 as the TO1 pin.

P2CR

P2FR

Starts Timer 1.

TRUN

```

(Note) × ; don't care -; no change

Figure 3.6 (7). Pulse (50% duty) Output Timing Chart

Starting Timer 1 counting up with Timer 0 match output

Set the 8-bit timer mode and set the comparator output of Timer 0 as the Timer 1 input clock.

Figure 3.6 (8)

#### 4 Output inversion with software

The timer flip-flop value can be inverted regardless of the timer operation.

Writing "1, 0" to TFFCR <TFF1C1, 0> inverts the TFF1 value; writing "0, 1" into TFFCR <FF3C1, 0> inverts the TFF3 value.

⑤ Initial setting of timer flipflop

The timer flipflop initial value can be set to either "0" or "1", regardless of the timer operation.

For example, write 0, 0 to TFFCR <TFF1C1, 0> to clear TFF1 to "0", and write 0, 1 in TFFCR <TFF1C1, 0> to set TFF1 to "1".

(Note) The timer flipflopand timer register values cannot be read.

#### (2) 16-bit timer mode

16-bit interval timers can be created by using Timer 0 and 1 as a pair of Timer 2 and 3 as a pair.

The operation of Timer 0 and 1 is the same as that of Timer 2 and 3, so Timer 0 and 1 are used for explanatory purposes.

Timer 0 and 1 can be used as a 16-bit interval timer by connecting them in a cascade configuration and writing "0, 1" to TMOD <T10M1, 0>.

When the 16-bit timer mode is set, the overflow output of timer 0 is used as the Timer 1 input clock, regardless of the TCLK setting value. TCLK sets the Timer 0 input clock. The relationship between the timer (interrupt) cycle and the input clock is shown in Table 3.6 (2).

**TOSHIBA CORPORATION**

Table 3.6 (2) 16-bit Timer (Interrupt) Cycle and Input Clock

| Timer (interrupt) cycle<br>@fc = 10MHz | Resolution | Input clock to<br>Timer 0 |  |

|----------------------------------------|------------|---------------------------|--|

| 8µs ~ 52.43ms                          | 8µs        | øT1 (8/fc)                |  |

| 12.8µs ~ 838.86ms                      | 12.8µs     | øT16 (128/fc)             |  |

| 204.8µs ~ 13.42s                       | 204.8µs    | øT256 (2048/fc)           |  |

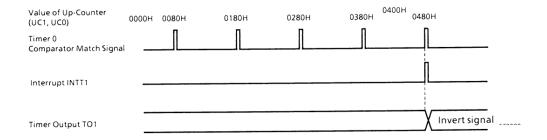

The timer (interrupt) cycle is set by loading the lower eight bits to the timer register TREGO and the upper eight bits to the timer register TREG1. In this case, always set TREGO first. (A comparison is temporarily halted by writing data to TREGO and a comparison is started by writing data into TREG1).

Example: To generate interrupts INTT1 every 1second (at fc = 8MHz, set the following values for timer register TREG0 and TREG1.

When counting by using øT16 (16µs @8MHz),

$1s \div 16\mu s = 62500 = F424H$

Therefore, set TREG1 = F4H and TREG0 = 24H.

The match signal of timer 0 comparator is output each time the up-counter UC0 matches TREGO. The up-counter UC0 is not cleared bit INTTO is generated.

The match signal of timer 1 comparator is output at each comparator timing cycle, if the up-counter UC1 matches TREG1. When the match signals of both the Timer 0 and Timer 1 comparators are output at the same time, the up-counters UC0 and UC1 are cleared to "0", and the interrupt INTT1 is generated. If the inversion is enabled, the value of the timer flipflop TFF1 is inverted then.

|                                                                | Timer 0             |                                                     |                              | Timer 1             |                                                                         |                                                                   |

|----------------------------------------------------------------|---------------------|-----------------------------------------------------|------------------------------|---------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------|

|                                                                | INTT0               | T01                                                 | Match                        | INTT1               | T01                                                                     | Match value                                                       |

| 16-bit Timer Mode<br>(count-up Timer 1 by Timer 0<br>overflow) | Interrupt generated | Output disabled<br>(cannot output a<br>TREG0 match) | TREG0<br>(continue count-up) | Interrupt generated | Output enable<br>(can output when both<br>Timer 0 and Timer 1<br>match) | TREG1 * 2 <sup>8</sup> + TREG0<br>16-bit)<br>(Cleared both match) |

| 8-bit Timer Mode<br>(count-up Timer 1 by Timer 0<br>match)     | Interrupt generated | Output enable<br>(either Timer 0<br>or Timer 1)     | TREGO<br>(clears on match)   | Interrupt generated | Output enable<br>(either Timer 0 or<br>Timer 1)                         | TREG1*TREG0<br>(multiplication value)<br>(clears on match)        |

Example: When TREG1 = 04H and TREG0 = 80H

Figure 3.6 (9)

(3) 8-bit PPG (Programmable Pulse Generation) Mode

Timer 1 or Timer 3 can be used to output pulse at any frequency and duty rate. The output pulse can be either low-active or high-active.

Timer 0 and/or Timer 2 cannot be used in this mode. For Timer 1, pulse is output to TO1 (also used as P21); for Timer 3, it is output to TO3 (also used as P22).

Timer 1 is used for explanatory purposes (operation is the same for Timer 3).

This mode outputs a programmable pulse by inverting the timer output each time the 8-bit up-counter 1 (UC1) matches the timer register TREG0 or TREG1.

It is necessary, however, to satisfy the condition (TREGO set value) < (TREG1 set value).

The up-counter (UC0) of Timer 0 cannot be used in this mode. Timer 0 can be used for counting by setting TRUN <TORUN> to "1".

Figure 3.6 (10) shows the block diagram of the PPG mode.

Figure 3.6 (10). 8-bit PPG Mode Block Diagram

Example: Outputting pulse at 1/4 duty rate and 50kHz @fc = 8MHz)

• Determine the set values of the timer registers.

t = 1/50kHz = 20 $\mu$ spulse cycle. When  $\phi$ T1 = 1 $\mu$ s (@ 8MHz) is used,  $20\mu$ s ÷ 1 $\mu$ s = 20 Therefore, the timer register 1 (TREG1) is set to TREG1 = 20 = 14H Next, to set a duty to 1/4, t x 1/4 = 20 $\mu$ s x 1/4 = 5 $\mu$ s

The frequency is set to 50kHz, by making a

$5\mu s \div 1\mu s = 5$

Therefore, set timer register 0 (TREG0) to TREG0 = 5 = 05H.

```

Stops Timer 0 and Timer 1, and clears them to "0".

TRUN

- - - - 0 1 x x

Sets the input clock to \phi T1.

TCLK

Sets the 8-bit PPG mode.

TMOD

Clears the output and enables the inversion by Timer 1.

TFFCR ←

When set to 00, a negative logic pulse is obtained.

Writes 5H.

TREGO + 0 0 0 0 0 1 0 1

Writes 14H.

TREG1 + 0 0 0 1 0 1 0 0

Sets P21 as the TO1 pin.

TRUN + - - 1 - - - 1 1

Starts Timer 1.

(iii) ×; don't care

-; no change

```

TOSHIBA CORPORATION 53/98

## **Cautions for PPG Output**

The PPG output is possible by updating the contents of TREG (Timer Register); however, a caution is required concerning the

TREG update timing in relation to the PPG pulse width setting.

Example: PPG output by 8-bit Timer 0, 1

TREG0 = pulse width TREG1 = cycle

The pulse width is normally changed with the interrupt (INTT1) processing routine for each timer cycle. When a next pulse width (value written to TREG0) is small, a problem will occur if the timer has already exceeded the TREG0 value. Thus, it is recommended that the following decision be made during INTT0 and INTT1 interrupt processing.

INTTO processing routine: Update the current TREGO

value only when writing a

smaller value.

INTT1 processing routine: Update the current TREGO

value only when writing a

larger value.

The TREG contents cannot be read; therefore, when making decisions as the above, it is necessary to store the TREG contents in RAM or a register.

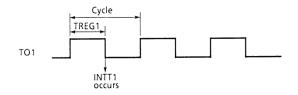

(4) 8-bit PWM (Pulse Width Modulation) Mode

This mode is only available for timer 1 and timer 3, and is used for two 8-bit resolution PWM (PWM1 and PWM3).

Timer 1 outputs to the TO1 pin (also used as P21); Timer 3 outputs to the TO3 pin (also used as P22).

Timer 0 and Timer 2 can be used as 8-bit timers.

Timer 1 (PWM1) is used for explanatory purposes (The operation for timer 3 is the same.)

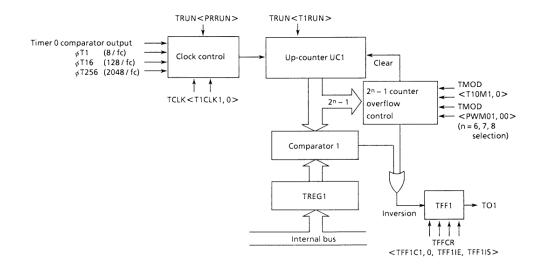

The timer output is inverted when up-counter (UC1) value matches the set value of timer register TREG1, and when a counter overflow of  $2^n$  - 1 (specify n = 6, 7 or 8 with TMOD <PWM01,00>) occurs. The up-counter UC1 is cleared by a counter overflow of  $2^n$  - 1.

The following conditions must be satisfied when the PWM mode is used.

(Set value of timer register) < ( $2^{n}$  - 1 counter overflow setting value)

(Set value of timer register) ≠ 0

(For example, n = 6: 6-bit PWM; n = 7: 7-bit PWM.)

Figure 3.6 (11) shows the block diagram of this mode.

Figure 3.6 (11). 8-bit PWM Mode Block Diagram

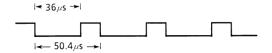

Example: Outputting the PWM shown below to the TO3 pin (P22) by using Timer 3 at fc = 10MHz.

```

Setting a PWM cycle of 50.4\mus with T1 = 0.8\mus (@fc = 10MHz), 50.4\mus ÷ 0.8\mus = 63 = 2<sup>6</sup> - 1 Therefore, n = 6 is set. (TMOD1, 0 = 01)

```

The "Low" level cycle is 36 $\mu$ s; therefore, at ØT1 = 0.8 $\mu$ s, 36 $\mu$ s ÷ 0.8 $\mu$ s = 45 = 2DH is set to TREG3.

```

TRUN ← - - - 0 - - -

Stops Timer 3.

Sets the input clock to \phi T1.

TCLK ← 0 1 - - - - -

TMOD ← 1 1 0 1 - - - -

Sets the PWM mode cycle = 26 - 1.

TFFCR ← 0 0 1 1 - - - -

Sets the output initial value to 0 ("L" level).

Writes 2DH.

TREG3 \leftarrow 0 0 1 0 1 1 0 1

P2CR ← - - - - 1 - -

Sets P22 as the TO3 pin.

P2FR

Starts Timer 3.

TRUN

(Note) × ; don't care

-; no change

```

TOSHIBA CORPORATION 55/98

Table 3.6 (3) PWM Cycle and 2<sup>n</sup> - 1 Counter Setting

|                    |                            | PWM cycle (@fc = 10Mhz) |                  |                  |  |

|--------------------|----------------------------|-------------------------|------------------|------------------|--|

| Expression         |                            | øT1<br>(8/fc)           | øT16<br>(128/fc) | øT16<br>(128/fc) |  |

| 2 <sup>6</sup> - 1 | (2 <sup>6</sup> - 1) x øTn | 50.4µs                  | 806.4µs          | 12.9µs           |  |

| 2 <sup>7</sup> - 1 | (2 <sup>7</sup> - 1) x øTn | 101.6µs                 | 1625.6µs         | 26.0ms           |  |

| 2 <sup>8</sup> - 1 | (2 <sup>8</sup> - 1) x øTn | 204.0µs                 | 3264.0µs         | 52.2ms           |  |

# **Cautions for PWM Output**

The TMP90C846 is capable of the PWM output with a 8-bit timer; however, it is necessary to pay a caution when the

PWM pulse width is changed. The following example is used for explanatory purposes.

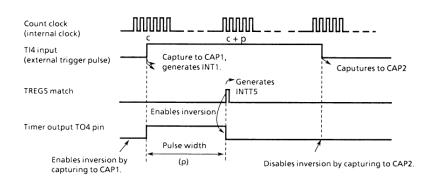

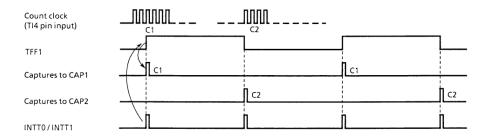

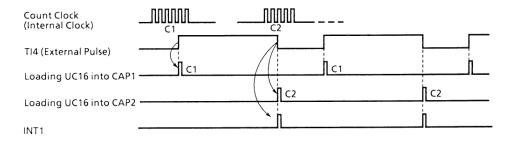

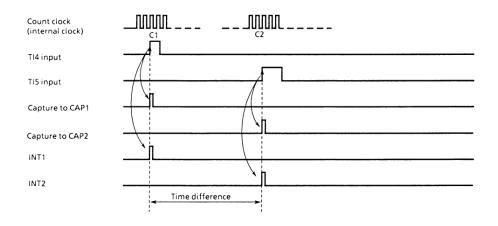

Example: Using an 8-bit timer for PWM output. TREG1 = pulse width Cycle: fixed  $(2^6 - 1, 2^7 - 1, 2^8 - 1)$