- Highest Performance Floating-Point Digital Signal Processor (DSP)

- TMS320C44-60:

33-ns Instruction Cycle Time,

330 MOPS, 60 MFLOPS,

30 MIPS, 336M Bytes/s

- TMS320C44-50:

40-ns Instruction Cycle Time

- Four Communication Ports

- Six-Channel Direct Memory Address (DMA) Coprocessor

- Single-Cycle Conversion to and From IEEE-754 Floating-Point Format

- Single Cycle, 1/x,  $1/\sqrt{x}$

- Source-Code Compatible With C3x and C4x

- Single-Cycle 40-Bit Floating-Point,

32-Bit Integer Multipliers

- Twelve 40-Bit Registers, Eight Auxiliary Registers, 14 Control Registers, and Two Timers

- IEEE-1149.1<sup>†</sup> (JTAG) Boundary-Scan Compatible

- Two Identical External Data and Address Buses Supporting Shared Memory Systems and High Data-Rate, Single-Cycle Transfers

- High Port-Data Rate of 120M Bytes/s (TMS320C44-60) (Each Bus)

- 128M-Byte Program/Data/Peripheral Address Space

- Memory-Access Request for Fast, Intelligent Bus Arbitration

- Separate Address-Bus, Data-Bus, and Control-Enable Pins

- Four Sets of Memory-Control Signals Support Different Speed Memories in Hardware

- Fabricated Using 0.72-μm Enhanced Performance Implanted CMOS (EPIC™) Technology by Texas Instruments (TI™)

- Separate Internal Program-, Data-, and DMA-Coprocessor Buses for Support of Massive Concurrent I/O of Program and Data, Thereby Maximizing Sustained CPU Performance

- IDLE2 Clock-Stop Power-Down Mode

- Communication-Port-Direction Pin

- On-Chip Program Cache and Dual-Access/Single-Cycle RAM for Increased Memory-Access Performance

- 512-Byte Instruction Cache

- 8K Bytes of Single-Cycle Dual-Access Program or Data RAM

- ROM-Based Boot Loader Supports

Program Bootup Using 8-, 16-, or 32-Bit

Memories or One of the Communication

Ports

- Software-Communication-Port Reset

- NMI With Bus-Grant Feature

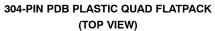

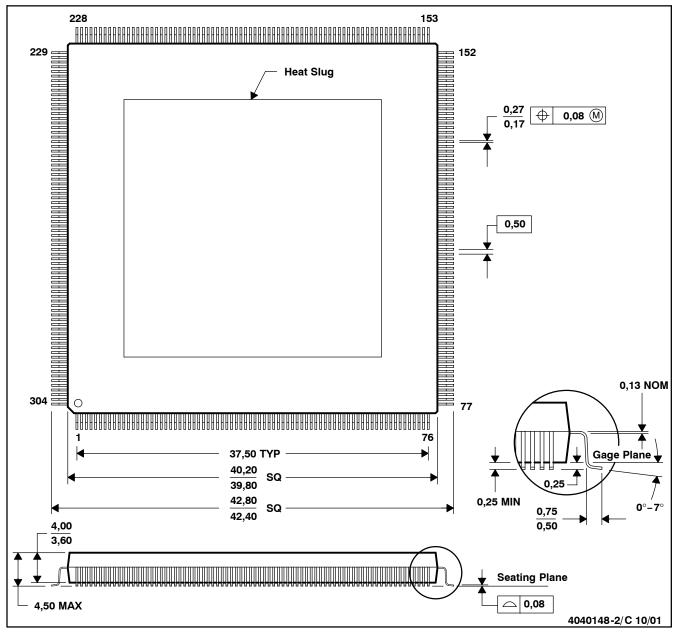

- 304-Pin Plastic Quad Flatpack (PDB Suffix) (Commercial Temperature)

- 388-Pin Plastic Ball Grid Array (GFW Suffix) (Commercial Temperature)

- 388-Pin Plastic Ball Grid Array (GFW Suffix) (Industrial Temperature)

### description

The TMSC44 DSP is a 32-bit, floating-point processor manufactured in 0.72-μm double-level-metal CMOS technology. The TMSC44 is part of the TMS320C4x generation of DSPs from Texas Instruments. The on-chip parallel-processing capabilities of the C44 make the immense floating-point performance required by many applications achievable.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup> IEEE Standard 1149.1–1990 Standard Test-Access Port and Boundary-Scan Architecture. EPIC and TI are trademarks of Texas Instruments.

All trademarks are the property of their respective owners.

### operation

The C44 has four on-chip communication ports for processor-to-processor communication with no external hardware and simple communication software. This allows connectivity with no external-glue logic. The communication ports remove input/output bottlenecks, and the independent smart 6-channel DMA coprocessor is able to handle the CPU input/output burden.

To fit the C40 into a 304-pin PQFP package (thermally enhanced plastic quad flatpack), two communication ports are removed and the external local and global address buses are reduced to 24 address lines each. In this case, both the bond pads and driver circuits are removed, decreasing die size and power consumption. Otherwise, functionality remains the same as the rest of the C4x family.

The communication-port token and data-strobe control lines are internally connected to avoid spurious data, boot-up, and power consumption problems.

#### **functions**

This section lists signal descriptions for the C44 device: each signal, number of pins, operating mode(s) (that is, input, output, or high-impedance state as indicated by I, O, or Z, respectively), and function. The signals are grouped according to function.

#### **Pin Functions**

| SIGNAL NAME        | NO. OF                                  | TYPE† | DESCRIPTION                                                     |  |  |  |  |  |  |

|--------------------|-----------------------------------------|-------|-----------------------------------------------------------------|--|--|--|--|--|--|

| OIGNAL NAME        | PINS                                    |       | DESCRIPTION                                                     |  |  |  |  |  |  |

|                    | GLOBAL-BUS EXTERNAL INTERFACE (73 pins) |       |                                                                 |  |  |  |  |  |  |

| D31 – D0           | 32                                      | I/O/Z | 32-bit data port of the global-bus external interface           |  |  |  |  |  |  |

| DE                 | 1                                       | I     | Data-bus-enable signal for the global-bus external interface    |  |  |  |  |  |  |

| A23-A0             | 24                                      | O/Z   | 24-bit address port of the global-bus external interface        |  |  |  |  |  |  |

| ĀĒ                 | 1                                       | I     | Address-bus-enable signal for the global-bus external interface |  |  |  |  |  |  |

| STAT3-STAT0        | 4                                       | 0     | Status signals for the global-bus external interface            |  |  |  |  |  |  |

| LOCK               | 1                                       | 0     | Lock signal for the global-bus external interface               |  |  |  |  |  |  |

| STRB0 <sup>‡</sup> | 1                                       | O/Z   | Access strobe 0 for the global-bus external interface           |  |  |  |  |  |  |

| R/W0 <sup>‡</sup>  | 1                                       | O/Z   | Read/write signal for STRB0 accesses                            |  |  |  |  |  |  |

| PAGE0 <sup>‡</sup> | 1                                       | O/Z   | Page signal for STRB0 accesses                                  |  |  |  |  |  |  |

| RDY0 <sup>‡</sup>  | 1                                       | I     | Ready signal for STRB0 accesses                                 |  |  |  |  |  |  |

| CE0 <sup>‡</sup>   | 1                                       | I     | Control enable for the STRBO, PAGEO, and R/WO signals           |  |  |  |  |  |  |

| STRB1 <sup>‡</sup> | 1                                       | O/Z   | Access strobe 1 for the global-bus external interface           |  |  |  |  |  |  |

| R/W1 <sup>‡</sup>  | 1                                       | O/Z   | Read/write signal for STRB1 accesses                            |  |  |  |  |  |  |

| PAGE1 <sup>‡</sup> | 1                                       | O/Z   | Page signal for STRB1 accesses                                  |  |  |  |  |  |  |

| RDY1 <sup>‡</sup>  | 1                                       | I     | Ready signal for STRB1 accesses                                 |  |  |  |  |  |  |

| CE1 <sup>‡</sup>   | 1                                       | I     | Control enable for the STRB1, PAGE1, and R/W1 signals           |  |  |  |  |  |  |

|                    |                                         | LOC   | AL-BUS EXTERNAL INTERFACE (73 pins)                             |  |  |  |  |  |  |

| LD31 - LD0         | 32                                      | I/O/Z | 32-bit data port of the local-bus external interface            |  |  |  |  |  |  |

| LDE                | 1                                       | I     | Data-bus-enable signal for the local-bus external interface     |  |  |  |  |  |  |

| LA23-LA0           | 24                                      | O/Z   | 24-bit address port of the local-bus external interface         |  |  |  |  |  |  |

| LAE                | 1                                       | I     | Address-bus-enable signal for the local-bus external interface  |  |  |  |  |  |  |

| LSTAT3-LSTAT0      | 4                                       | 0     | Status signals for the local-bus external interface             |  |  |  |  |  |  |

| LLOCK              | 1                                       | 0     | Lock signal for the local-bus external interface                |  |  |  |  |  |  |

$<sup>^{\</sup>dagger}$  I = input, O = output, Z = high impedance

<sup>&</sup>lt;sup>‡</sup> The effective address range is defined by the local/global STRB ACTIVE bits in the memory interface-control registers.

# **Pin Functions (Continued)**

| SIGNAL NAME         | NO. OF<br>PINS                                     | TYPE† | DESCRIPTION                                                |  |  |  |  |  |  |  |

|---------------------|----------------------------------------------------|-------|------------------------------------------------------------|--|--|--|--|--|--|--|

|                     | LOCAL-BUS EXTERNAL INTERFACE (73 pins) (Continued) |       |                                                            |  |  |  |  |  |  |  |

| LSTRB0 <sup>‡</sup> | 1                                                  | O/Z   | Access strobe 0 for the local-bus external interface       |  |  |  |  |  |  |  |

| LR/W0               | 1                                                  | O/Z   | Read/write signal for LSTRB0 accesses                      |  |  |  |  |  |  |  |

| LPAGE0              | 1                                                  | O/Z   | Page signal for LSTRB0 accesses                            |  |  |  |  |  |  |  |

| LRDY0               | 1                                                  | I     | Ready signal for LSTRB0 accesses                           |  |  |  |  |  |  |  |

| LCE0                | 1                                                  | ı     | Control enable for the LSTRBO, LPAGEO, and LR / WO signals |  |  |  |  |  |  |  |

| LSTRB1‡             | 1                                                  | O/Z   | Access strobe 1 for the local-bus external interface       |  |  |  |  |  |  |  |

| LR/W1               | 1                                                  | O/Z   | Read/write signal for LSTRB1 accesses                      |  |  |  |  |  |  |  |

| LPAGE1              | 1                                                  | O/Z   | Page signal for LSTRB1 accesses                            |  |  |  |  |  |  |  |

| LRDY1               | 1                                                  | I     | Ready signal for LSTRB1 accesses                           |  |  |  |  |  |  |  |

| LCE1                | 1                                                  | I     | Control enable for the LSTRB1, LPAGE1, and LR/W1 signals   |  |  |  |  |  |  |  |

|                     |                                                    | СОМ   | MUNICATION PORT 1 INTERFACE (13 pins)                      |  |  |  |  |  |  |  |

| C1D7-C1D0           | 8                                                  | I/O   | Communication port 1 data bus                              |  |  |  |  |  |  |  |

| CREQ1               | 1                                                  | I/O   | Communication port 1 token-request signal                  |  |  |  |  |  |  |  |

| CACK1               | 1                                                  | I/O   | Communication port 1 token-request-acknowledge signal      |  |  |  |  |  |  |  |

| CSTRB1              | 1                                                  | I/O   | Communication port 1 data-strobe signal                    |  |  |  |  |  |  |  |

| CRDY1               | 1                                                  | I/O   | Communication port 1 data-ready signal                     |  |  |  |  |  |  |  |

| CDIR1               | 1                                                  | 0     | Communication port 1 direction signal                      |  |  |  |  |  |  |  |

|                     |                                                    | СОМ   | MUNICATION PORT 2 INTERFACE (13 pins)                      |  |  |  |  |  |  |  |

| C2D7-C2D0           | 8                                                  | I/O   | Communication port 2 data bus                              |  |  |  |  |  |  |  |

| CREQ2               | 1                                                  | I/O   | Communication port 2 token-request signal                  |  |  |  |  |  |  |  |

| CACK2               | 1                                                  | I/O   | Communication port 2 token-request-acknowledge signal      |  |  |  |  |  |  |  |

| CSTRB2              | 1                                                  | I/O   | Communication port 2 data-strobe signal                    |  |  |  |  |  |  |  |

| CRDY2               | 1                                                  | I/O   | Communication port 2 data-ready signal                     |  |  |  |  |  |  |  |

| CDIR2               | 1                                                  | 0     | Communication port 2 direction signal                      |  |  |  |  |  |  |  |

|                     |                                                    | COM   | MUNICATION PORT 4 INTERFACE (13 pins)                      |  |  |  |  |  |  |  |

| C4D7-C4D0           | 8                                                  | I/O   | Communication port 4 data bus                              |  |  |  |  |  |  |  |

| CREQ4               | 1                                                  | I/O   | Communication port 4 token-request signal                  |  |  |  |  |  |  |  |

| CACK4               | 1                                                  | I/O   | Communication port 4 token-request-acknowledge signal      |  |  |  |  |  |  |  |

| CSTRB4              | 1                                                  | I/O   | Communication port 4 data-strobe signal                    |  |  |  |  |  |  |  |

| CRDY4               | 1                                                  | I/O   | Communication port 4 data-ready signal                     |  |  |  |  |  |  |  |

| CDIR4               | 1                                                  | 0     | Communication port 4 direction signal                      |  |  |  |  |  |  |  |

|                     |                                                    | СОМ   | MUNICATION PORT 5 INTERFACE (13 pins)                      |  |  |  |  |  |  |  |

| C5D7-C5D0           | 8                                                  | I/O   | Communication port 5 data bus                              |  |  |  |  |  |  |  |

| CREQ5               | 1                                                  | I/O   | Communication port 5 token-request signal                  |  |  |  |  |  |  |  |

| CACK5               | 1                                                  | I/O   | Communication port 5 token-request-acknowledge signal      |  |  |  |  |  |  |  |

| CSTRB5              | 1                                                  | I/O   | Communication port 5 data-strobe signal                    |  |  |  |  |  |  |  |

| CRDY5               | 1                                                  | I/O   | Communication port 5 data-ready signal                     |  |  |  |  |  |  |  |

| CDIR5               | 1                                                  | 0     | Communication port 5 direction signal                      |  |  |  |  |  |  |  |

$<sup>^{\</sup>dagger}$  I = input, O = output, Z = high impedance

<sup>†</sup> The effective address range is defined by the local/global STRB ACTIVE bits in the memory interface-control registers.

# **Pin Functions (Continued)**

| SIGNAL NAME                                   | NO. OF<br>PINS | TYPE† | DESCRIPTION                                                  |  |  |  |  |  |

|-----------------------------------------------|----------------|-------|--------------------------------------------------------------|--|--|--|--|--|

| INTERRUPTS, I/O FLAGS, RESET, TIMER (12 pins) |                |       |                                                              |  |  |  |  |  |

| IIOF3-IIOF0                                   | 4              | I/O   | Interrupt and I/O flags                                      |  |  |  |  |  |

| NMI                                           | 1              | I     | Nonmaskable interrupt. NMI is sensitive to a low-going edge. |  |  |  |  |  |

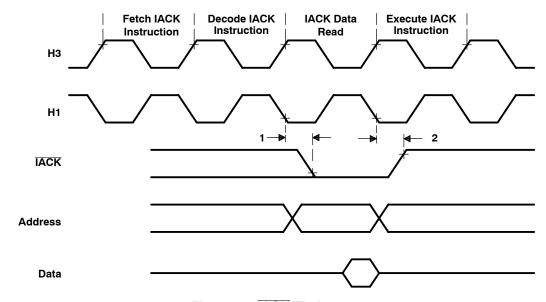

| IACK                                          | 1              | 0     | Interrupt acknowledge                                        |  |  |  |  |  |

| RESET                                         | 1              | I     | Reset signal                                                 |  |  |  |  |  |

| RESETLOC1<br>RESETLOC0                        | 2              | ı     | Reset-vector location                                        |  |  |  |  |  |

| ROMEN                                         | 1              | I     | On-chip ROM enable (0 = disable, 1 = enable)                 |  |  |  |  |  |

| TCLK0                                         | 1              | I/O   | Timer 0                                                      |  |  |  |  |  |

| TCLK1                                         | 1              | I/O   | Timer 1                                                      |  |  |  |  |  |

|                                               |                |       | CLOCK (4 pins)                                               |  |  |  |  |  |

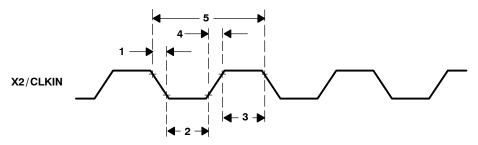

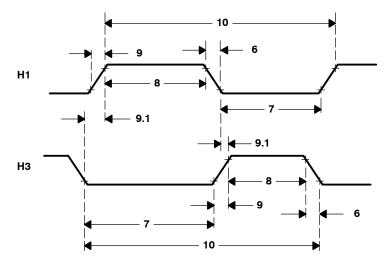

| X1                                            | 1              | 0     | Crystal                                                      |  |  |  |  |  |

| X2 / CLKIN                                    | 1              | I     | Crystal/oscillator                                           |  |  |  |  |  |

| H1                                            | 1              | 0     | H1 clock                                                     |  |  |  |  |  |

| H3                                            | 1              | 0     | H3 clock                                                     |  |  |  |  |  |

|                                               |                |       | POWER (71 pins)                                              |  |  |  |  |  |

| CV <sub>SS</sub>                              | 17             | I     | Ground                                                       |  |  |  |  |  |

| DV <sub>SS</sub>                              | 17             | I     | Ground                                                       |  |  |  |  |  |

| IV <sub>SS</sub>                              | 6              | I     | Ground                                                       |  |  |  |  |  |

| $DV_DD$                                       | 22             | I     | 5-V <sub>DC</sub> supply                                     |  |  |  |  |  |

| VSUBS                                         | 1              | I     | Substrate (tie to ground)                                    |  |  |  |  |  |

| $V_{DDL}$                                     | 4              | I     | 5-V <sub>DC</sub> supply                                     |  |  |  |  |  |

| $V_{SSL}$                                     | 4              | I     | Ground                                                       |  |  |  |  |  |

|                                               |                |       | EMULATION (7 pins)                                           |  |  |  |  |  |

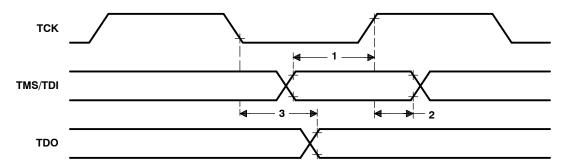

| TCK                                           | 1              | I     | IEEE 1149.1 test port clock                                  |  |  |  |  |  |

| TDI                                           | 1              | I     | IEEE 1149.1 test port data in                                |  |  |  |  |  |

| TDO                                           | 1              | O/Z   | IEEE 1149.1 test port data out                               |  |  |  |  |  |

| TMS                                           | 1              | I     | IEEE 1149.1 test port mode select                            |  |  |  |  |  |

| TRST                                          | 1              | I     | IEEE 1149.1 test port reset                                  |  |  |  |  |  |

| EMU0                                          | 1              | I/O   | Emulation pin 0                                              |  |  |  |  |  |

| EMU1                                          | 1              | I/O   | Emulation pin 1                                              |  |  |  |  |  |

<sup>†</sup> I = input, O = output, Z = high impedance ‡ The effective address range is defined by the local/global STRB ACTIVE bits in the memory interface-control registers.

## PDB Package Pin Assignments — Alphabetical Listing

|      | T DD T ackage Fin Assignments — Alphabetical Listing |       |     |                  |     |                  |     |  |  |  |

|------|------------------------------------------------------|-------|-----|------------------|-----|------------------|-----|--|--|--|

| PI   |                                                      | PIN   |     | PI               |     | PI               |     |  |  |  |

| NAME | NO.                                                  | NAME  | NO. | NAME             | NO. | NAME             | NO. |  |  |  |

| A0   | 149                                                  | C2D7  | 34  | CV <sub>SS</sub> | 134 | D24              | 137 |  |  |  |

| A1   | 150                                                  | C4D0  | 87  | CV <sub>SS</sub> | 117 | D25              | 138 |  |  |  |

| A2   | 151                                                  | C4D1  | 88  | CV <sub>SS</sub> | 102 | D26              | 140 |  |  |  |

| A3   | 152                                                  | C4D2  | 90  | CV <sub>SS</sub> | 78  | D27              | 141 |  |  |  |

| A4   | 154                                                  | C4D3  | 92  | CV <sub>SS</sub> | 62  | D28              | 142 |  |  |  |

| A5   | 155                                                  | C4D4  | 94  | CV <sub>SS</sub> | 44  | D29              | 143 |  |  |  |

| A6   | 156                                                  | C4D5  | 97  | CV <sub>SS</sub> | 25  | D30              | 144 |  |  |  |

| A7   | 157                                                  | C4D6  | 99  | CV <sub>SS</sub> | 7   | D31              | 145 |  |  |  |

| A8   | 158                                                  | C4D7  | 100 | CV <sub>SS</sub> | 282 | DE               | 89  |  |  |  |

| A9   | 159                                                  | C5D0  | 37  | CV <sub>SS</sub> | 262 | $DV_DD$          | 139 |  |  |  |

| A10  | 160                                                  | C5D1  | 39  | CV <sub>SS</sub> | 247 | $DV_DD$          | 124 |  |  |  |

| A11  | 162                                                  | C5D2  | 41  | CV <sub>SS</sub> | 230 | $DV_DD$          | 109 |  |  |  |

| A12  | 165                                                  | C5D3  | 42  | CV <sub>SS</sub> | 218 | DV <sub>DD</sub> | 96  |  |  |  |

| A13  | 166                                                  | C5D4  | 45  | CV <sub>SS</sub> | 202 | DV <sub>DD</sub> | 83  |  |  |  |

| A14  | 167                                                  | C5D5  | 46  | CV <sub>SS</sub> | 182 | DV <sub>DD</sub> | 67  |  |  |  |

| A15  | 168                                                  | C5D6  | 47  | CV <sub>SS</sub> | 164 | DV <sub>DD</sub> | 51  |  |  |  |

| A16  | 169                                                  | C5D7  | 48  | D0               | 104 | $DV_DD$          | 40  |  |  |  |

| A17  | 170                                                  | CACK1 | 13  | D1               | 105 | $DV_DD$          | 28  |  |  |  |

| A18  | 171                                                  | CACK2 | 21  | D2               | 106 | $DV_DD$          | 17  |  |  |  |

| A19  | 174                                                  | CACK4 | 73  | D3               | 107 | $DV_DD$          | 302 |  |  |  |

| A20  | 175                                                  | CACK5 | 50  | D4               | 108 | $DV_DD$          | 288 |  |  |  |

| A21  | 176                                                  | CDIR1 | 19  | D5               | 110 | $DV_DD$          | 272 |  |  |  |

# PDB Package Pin Assignments — Alphabetical Listing (Continued)

| PI               |     | PIN              |     | PI     | N   | PIN                |     |

|------------------|-----|------------------|-----|--------|-----|--------------------|-----|

| NAME             | NO. | NAME             | NO. | NAME   | NO. | NAME               | NO. |

| A22              | 177 | CDIR2            | 18  | D6     | 111 | $DV_DD$            | 256 |

| A23              | 178 | CDIR4            | 16  | D7     | 112 | $DV_DD$            | 244 |

| ĀĒ               | 57  | CDIR5            | 15  | D8     | 113 | $DV_DD$            | 236 |

| C1D0             | 269 | CE0              | 93  | D9     | 114 | $DV_DD$            | 223 |

| C1D1             | 271 | CE1              | 101 | D10    | 115 | $DV_DD$            | 207 |

| C1D2             | 274 | CRDY1            | 8   | D11    | 118 | $DV_DD$            | 188 |

| C1D3             | 276 | CRDY2            | 23  | D12    | 120 | $DV_DD$            | 172 |

| C1D4             | 278 | CRDY4            | 85  | D13    | 122 | $DV_DD$            | 161 |

| C1D5             | 280 | CRDY5            | 53  | D14    | 123 | $DV_DD$            | 153 |

| C1D6             | 283 | CREQ1            | 11  | D15    | 125 | DV <sub>SS</sub>   | 147 |

| C1D7             | 286 | CREQ2            | 20  | D16    | 127 | DV <sub>SS</sub>   | 133 |

| C2D0             | 26  | CREQ4            | 71  | D17    | 128 | DV <sub>SS</sub>   | 116 |

| C2D1             | 27  | CREQ5            | 49  | D18    | 129 | DV <sub>SS</sub>   | 103 |

| C2D2             | 29  | CSTRB1           | 14  | D19    | 130 | DV <sub>SS</sub>   | 79  |

| C2D3             | 30  | CSTRB2           | 22  | D20    | 131 | DV <sub>SS</sub>   | 63  |

| C2D4             | 31  | CSTRB4           | 84  | D21    | 132 | DV <sub>SS</sub>   | 43  |

| C2D5             | 32  | CSTRB5           | 52  | D22    | 135 | DV <sub>SS</sub>   | 24  |

| C2D6             | 33  | CV <sub>SS</sub> | 148 | D23    | 136 | DV <sub>SS</sub>   | 6   |

| DV <sub>SS</sub> | 281 | LA17             | 253 | LD30   | 228 | STAT0              | 68  |

| DV <sub>SS</sub> | 261 | LA18             | 254 | LD31   | 229 | STAT1              | 66  |

| DV <sub>SS</sub> | 246 | LA19             | 255 | LDE    | 291 | STAT2              | 64  |

| DV <sub>SS</sub> | 231 | LA20             | 257 | LLOCK  | 284 | STAT3              | 61  |

| DV <sub>SS</sub> | 217 | LA21             | 258 | LOCK   | 95  | STRB0              | 58  |

| DV <sub>SS</sub> | 201 | LA22             | 259 | LPAGE0 | 299 | STRB1              | 69  |

| DV <sub>SS</sub> | 179 | LA23             | 260 | LPAGE1 | 294 | TCK                | 86  |

| DV <sub>SS</sub> | 163 | LAE              | 287 | LRDY0  | 298 | TCLK0              | 290 |

| EMU0             | 75  | LCE0             | 297 | LRDY1  | 293 | TCLK1              | 289 |

| EMU1             | 74  | LCE1             | 292 | LR/W0  | 300 | TDI                | 76  |

| H1               | 266 | LD0              | 183 | LR/W1  | 295 | TDO                | 80  |

| H3               | 268 | LD1              | 184 | LSTAT0 | 279 | TMS                | 82  |

| TACK             | 270 | LD2              | 185 | LSTAT1 | 277 | TRST               | 81  |

| IIOF0            | 10  | LD3              | 186 | LSTAT2 | 275 | $V_{ m DDL}$       | 38  |

| IIOF1            | 9   | LD4              | 187 | LSTAT3 | 273 | $V_{ m DDL}$       | 121 |

| IIOF2            | 5   | LD5              | 192 | LSTRB0 | 301 | $V_{\mathrm{DDL}}$ | 191 |

| IIOF3            | 4   | LD6              | 194 | LSTRB1 | 296 | $V_{\mathrm{DDL}}$ | 267 |

| IV <sub>SS</sub> | 126 | LD7              | 195 | NC     | 1   | $V_{\rm SSL}$      | 36  |

| IV <sub>SS</sub> | 65  | LD8              | 196 | NC     | 77  | $V_{SSL}$          | 119 |

| IV <sub>SS</sub> | 35  | LD9              | 197 | NC     | 173 | $V_{SSL}$          | 193 |

| IV <sub>SS</sub> | 2   | LD10             | 200 | NC     | 180 | $V_{\rm SSL}$      | 265 |

| IV <sub>SS</sub> | 285 | LD11             | 203 | NC     | 181 | VSUBS              | 146 |

| IV <sub>SS</sub> | 209 | LD12             | 204 | NC     | 189 | X1                 | 264 |

| LA0              | 232 | LD13             | 205 | NC     | 190 | X2/CLKIN           | 263 |

| LA1              | 233 | LD14             | 206 | NC     | 198 |                    |     |

# PDB Package Pin Assignments — Alphabetical Listing (Continued)

| PII  | N   | PIN  | N   | PIN       |     | PIN  | 1   |

|------|-----|------|-----|-----------|-----|------|-----|

| NAME | NO. | NAME | NO. | NAME      | NO. | NAME | NO. |

| LA2  | 234 | LD15 | 208 | NC        | 199 |      |     |

| LA3  | 235 | LD16 | 210 | NC        | 214 |      |     |

| LA4  | 237 | LD17 | 211 | NC        | 303 |      |     |

| LA5  | 238 | LD18 | 212 | NC        | 304 |      |     |

| LA6  | 239 | LD19 | 213 | NMI       | 3   |      |     |

| LA7  | 240 | LD20 | 215 | PAGE0     | 60  |      |     |

| LA8  | 241 | LD21 | 216 | PAGE1     | 72  |      |     |

| LA9  | 242 | LD22 | 219 | RDY0      | 91  |      |     |

| LA10 | 243 | LD23 | 220 | RDY1      | 98  |      |     |

| LA11 | 245 | LD24 | 221 | RESET     | 54  |      |     |

| LA12 | 248 | LD25 | 222 | RESETLOC0 | 55  |      |     |

| LA13 | 249 | LD26 | 224 | RESETLOC1 | 56  |      |     |

| LA14 | 250 | LD27 | 225 | ROMEN     | 12  |      |     |

| LA15 | 251 | LD28 | 226 | R/W0      | 59  |      |     |

| LA16 | 252 | LD29 | 227 | R/W1      | 70  |      |     |

# PDB Package Pin Assignments — Numerical Listing

|     | PIN              | <u> </u> | PIN              | I   | PIN              | PIN |                  |

|-----|------------------|----------|------------------|-----|------------------|-----|------------------|

| NO. | NAME             | NO.      | NAME             | NO. | NAME             | NO. | NAME             |

| 1   | NC               | 41       | C5D2             | 81  | TRST             | 121 | $V_{DDL}$        |

| 2   | $IV_{SS}$        | 42       | C5D3             | 82  | TMS              | 122 | D13              |

| 3   | NMI              | 43       | $DV_SS$          | 83  | $DV_DD$          | 123 | D14              |

| 4   | ĪIOF3            | 44       | CV <sub>SS</sub> | 84  | CSTRB4           | 124 | $DV_DD$          |

| 5   | ĪIOF2            | 45       | C5D4             | 85  | CRDY4            | 125 | D15              |

| 6   | $DV_SS$          | 46       | C5D5             | 86  | TCK              | 126 | IV <sub>SS</sub> |

| 7   | CV <sub>SS</sub> | 47       | C5D6             | 87  | C4D0             | 127 | D16              |

| 8   | CRDY1            | 48       | C5D7             | 88  | C4D1             | 128 | D17              |

| 9   | ĪIOF1            | 49       | CREQ5            | 89  | DE               | 129 | D18              |

| 10  | ĪIOF0            | 50       | CACK5            | 90  | C4D2             | 130 | D19              |

| 11  | CREQ1            | 51       | $DV_DD$          | 91  | RDY0             | 131 | D20              |

| 12  | ROMEN            | 52       | CSTRB5           | 92  | C4D3             | 132 | D21              |

| 13  | CACK1            | 53       | CRDY5            | 93  | CE0              | 133 | DV <sub>SS</sub> |

| 14  | CSTRB1           | 54       | RESET            | 94  | C4D4             | 134 | CV <sub>SS</sub> |

| 15  | CDIR5            | 55       | RESETLOC0        | 95  | LOCK             | 135 | D22              |

| 16  | CDIR4            | 56       | RESETLOC1        | 96  | $DV_DD$          | 136 | D23              |

| 17  | $DV_DD$          | 57       | ĀĒ               | 97  | C4D5             | 137 | D24              |

| 18  | CDIR2            | 58       | STRB0            | 98  | RDY1             | 138 | D25              |

| 19  | CDIR1            | 59       | R/₩0             | 99  | C4D6             | 139 | $DV_DD$          |

| 20  | CREQ2            | 60       | PAGE0            | 100 | C4D7             | 140 | D26              |

| 21  | CACK2            | 61       | STAT3            | 101 | CE1              | 141 | D27              |

| 22  | CSTRB2           | 62       | CV <sub>SS</sub> | 102 | CV <sub>SS</sub> | 142 | D28              |

| 23  | CRDY2            | 63       | $DV_SS$          | 103 | DV <sub>SS</sub> | 143 | D29              |

| 24  | $DV_SS$          | 64       | STAT2            | 104 | D0               | 144 | D30              |

# PDB Package Pin Assignments — Numerical Listing (Continued)

| PIN PIN |                    |     | PIN              | PIN |                  |     |                  |

|---------|--------------------|-----|------------------|-----|------------------|-----|------------------|

| NO.     | NAME               | NO. | NAME             | NO. | NAME             | NO. | NAME             |

| 25      | CV <sub>SS</sub>   | 65  | IV <sub>SS</sub> | 105 | D1               | 145 | D31              |

| 26      | C2D0               | 66  | STAT1            | 106 | D2               | 146 | VSUBS            |

| 27      | C2D1               | 67  | DV <sub>DD</sub> | 107 | D3               | 147 | DV <sub>SS</sub> |

| 28      | DV <sub>DD</sub>   | 68  | STAT0            | 108 | D4               | 148 | CV <sub>SS</sub> |

| 29      | C2D2               | 69  | STRB1            | 109 | $DV_DD$          | 149 | A0               |

| 30      | C2D3               | 70  | R/₩1             | 110 | D5               | 150 | A1               |

| 31      | C2D4               | 71  | CREQ4            | 111 | D6               | 151 | A2               |

| 32      | C2D5               | 72  | PAGE1            | 112 | D7               | 152 | A3               |

| 33      | C2D6               | 73  | CACK4            | 113 | D8               | 153 | DV <sub>DD</sub> |

| 34      | C2D7               | 74  | EMU1             | 114 | D9               | 154 | A4               |

| 35      | IV <sub>SS</sub>   | 75  | EMU0             | 115 | D10              | 155 | A5               |

| 36      | $V_{SSL}$          | 76  | TDI              | 116 | DV <sub>SS</sub> | 156 | A6               |

| 37      | C5D0               | 77  | NC               | 117 | CV <sub>SS</sub> | 157 | A7               |

| 38      | $V_{\mathrm{DDL}}$ | 78  | CV <sub>SS</sub> | 118 | D11              | 158 | A8               |

| 39      | C5D1               | 79  | DV <sub>SS</sub> | 119 | $V_{SSL}$        | 159 | A9               |

| 40      | DV <sub>DD</sub>   | 80  | TDO              | 120 | D12              | 160 | A10              |

| 161     | $DV_DD$            | 201 | DV <sub>SS</sub> | 241 | LA8              | 281 | DV <sub>SS</sub> |

| 162     | A11                | 202 | CV <sub>SS</sub> | 242 | LA9              | 282 | CV <sub>SS</sub> |

| 163     | DV <sub>SS</sub>   | 203 | LD11             | 243 | LA10             | 283 | C1D6             |

| 164     | CV <sub>SS</sub>   | 204 | LD12             | 244 | $DV_DD$          | 284 | LLOCK            |

| 165     | A12                | 205 | LD13             | 245 | LA11             | 285 | IV <sub>SS</sub> |

| 166     | A13                | 206 | LD14             | 246 | DV <sub>SS</sub> | 286 | C1D7             |

| 167     | A14                | 207 | DV <sub>DD</sub> | 247 | CV <sub>SS</sub> | 287 | LAE              |

| 168     | A15                | 208 | LD15             | 248 | LA12             | 288 | DV <sub>DD</sub> |

| 169     | A16                | 209 | $IV_SS$          | 249 | LA13             | 289 | TCLK1            |

| 170     | A17                | 210 | LD16             | 250 | LA14             | 290 | TCLK0            |

| 171     | A18                | 211 | LD17             | 251 | LA15             | 291 | LDE              |

| 172     | $DV_DD$            | 212 | LD18             | 252 | LA16             | 292 | LCE1             |

| 173     | NC                 | 213 | LD19             | 253 | LA17             | 293 | LRDY1            |

| 174     | A19                | 214 | NC               | 254 | LA18             | 294 | LPAGE1           |

| 175     | A20                | 215 | LD20             | 255 | LA19             | 295 | LR/₩1            |

| 176     | A21                | 216 | LD21             | 256 | $DV_DD$          | 296 | LSTRB1           |

| 177     | A22                | 217 | DV <sub>SS</sub> | 257 | LA20             | 297 | LCE0             |

| 178     | A23                | 218 | CV <sub>SS</sub> | 258 | LA21             | 298 | LRDY0            |

| 179     | $DV_SS$            | 219 | LD22             | 259 | LA22             | 299 | LPAGE0           |

| 180     | NC                 | 220 | LD23             | 260 | LA23             | 300 | LR/W0            |

| 181     | NC                 | 221 | LD24             | 261 | DV <sub>SS</sub> | 301 | LSTRB0           |

| 182     | CV <sub>SS</sub>   | 222 | LD25             | 262 | CV <sub>SS</sub> | 302 | $DV_DD$          |

| 183     | LD0                | 223 | $DV_DD$          | 263 | X2 / CLKIN       | 303 | NC               |

| 184     | LD1                | 224 | LD26             | 264 | X1               | 304 | NC               |

| 185     | LD2                | 225 | LD27             | 265 | $V_{SSL}$        |     |                  |

| 186     | LD3                | 226 | LD28             | 266 | H1               |     |                  |

| 187     | LD4                | 227 | LD29             | 267 | $V_{DDL}$        |     |                  |

# PDB Package Pin Assignments — Numerical Listing (Continued)

| P   | PIN       | Р   | IN               | ı   | PIN     | P   | PIN  |

|-----|-----------|-----|------------------|-----|---------|-----|------|

| NO. | NAME      | NO. | NAME             | NO. | NAME    | NO. | NAME |

| 188 | $DV_DD$   | 228 | LD30             | 268 | H3      |     |      |

| 189 | NC        | 229 | LD31             | 269 | C1D0    |     |      |

| 190 | NC        | 230 | CV <sub>SS</sub> | 270 | IACK    |     |      |

| 191 | $V_{DDL}$ | 231 | $DV_SS$          | 271 | C1D1    |     |      |

| 192 | LD5       | 232 | LA0              | 272 | $DV_DD$ |     |      |

| 193 | $V_{SSL}$ | 233 | LA1              | 273 | LSTAT3  |     |      |

| 194 | LD6       | 234 | LA2              | 274 | C1D2    |     |      |

| 195 | LD7       | 235 | LA3              | 275 | LSTAT2  |     |      |

| 196 | LD8       | 236 | $DV_DD$          | 276 | C1D3    |     |      |

| 197 | LD9       | 237 | LA4              | 277 | LSTAT1  |     |      |

| 198 | NC        | 238 | LA5              | 278 | C1D4    |     |      |

| 199 | NC        | 239 | LA6              | 279 | LSTAT0  |     |      |

| 200 | LD10      | 240 | LA7              | 280 | C1D5    |     |      |

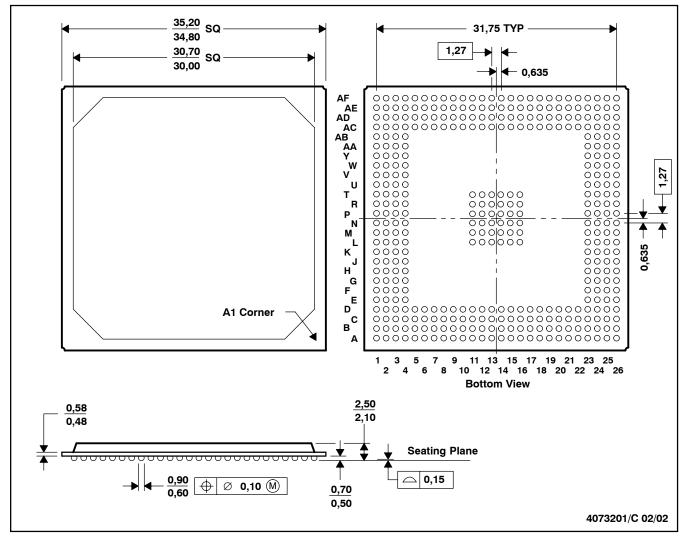

## 388-PIN GFW BALL GRID ARRAY (BOTTOM VIEW)

| AF<br>AE       | 000000000000000000000000000000000000000     |

|----------------|---------------------------------------------|

| AE<br>AD<br>AC | 000000000000000000000000000000000000000     |

| AB<br>AA       | 0000 0000                                   |

| Y<br>W         | 0000                                        |

| v<br>U         | 0000 0000                                   |

| T<br>R         | 0000 T 000000 0000<br>0000 R 000000 0000    |

| P<br>N         | 0000 P 000000 0000<br>0000 N 000000 0000    |

| M<br>L         | 0000 M 000000 0000<br>0000 L 000000 0000    |

| K<br>J         | 0000 11 16 0000                             |

| H<br>G         | 0000                                        |

| F<br>E<br>D    | 0000<br>  0000<br>  00000000000000000000000 |

| C<br>B         | 000000000000000000000000000000000000000     |

| A              | 000000000000000000000000000000000000000     |

NOTES: A. N/C = No connection to this frame pin

- B. Numbers around the detail in this figure are ball pin numbers.

- C. V<sub>SS</sub> ground potential ring is connected to the BGA ball pins as listed: A1, A2, A26, B2, B25, B26, C3, C24, D4, D9, D14, D19, D23, H4, J23, L11 - L16, M11 - M16, N4, P23, V4, W23, AC4, AC8, AC13, AC18, AC23, AD3, AD24, AE1, AE2, AE25, AF1, AF25, AF26. (The following V<sub>SS</sub> pins are also thermal connections) L11 - L16, T11 - T16, M11 - M16, N11 - N16, P11 - P16, R11 - R16.

26

D.  $\ensuremath{\text{V}_{\text{DD}}}$  power potential ring is connected to the BGA ball pins as listed: D6, D11, D16, D21, F4, F23, L4, L23, T4, T23, AA4, AA23, AC6, AC11, AC16, AC21.

## **GFW Package Pin Assignments Numerical Listing by Ball Pin Number**

|     | PIN      |     | PIN             |     | PIN      |     | PIN             |

|-----|----------|-----|-----------------|-----|----------|-----|-----------------|

| NO. | NAME     | NO. | NAME            | NO. | NAME     | NO. | NAME            |

| A1  | $V_{SS}$ | B17 | LD13            | D7  | N/C      | G25 | N/C             |

| A2  | $V_{SS}$ | B18 | N/C             | D8  | A15      | G26 | N/C             |

| А3  | N/C      | B19 | LD16            | D9  | $V_{SS}$ | H1  | N/C             |

| A4  | A7       | B20 | LD19            | D10 | A21      | H2  | D22             |

| A5  | N/C      | B21 | N/C             | D11 | $V_{DD}$ | H3  | D21             |

| A6  | N/C      | B22 | LD25            | D12 | N/C      | H4  | $V_{SS}$        |

| A7  | A14      | B23 | LD27            | D13 | N/C      | H23 | LA11            |

| A8  | A18      | B24 | LD29            | D14 | $V_{SS}$ | H24 | LA10            |

| A9  | N/C      | B25 | $V_{SS}$        | D15 | LD6      | H25 | LA13            |

| A10 | A22      | B26 | $V_{SS}$        | D16 | $V_{DD}$ | H26 | LA12            |

| A11 | N/C      | C1  | A1              | D17 | N/C      | J1  | D19             |

| A12 | LD1      | C2  | A2              | D18 | N/C      | J2  | D20             |

| A13 | N/C      | СЗ  | V <sub>SS</sub> | D19 | $V_{SS}$ | J3  | D17             |

| A14 | N/C      | C4  | A4              | D20 | N/C      | J4  | N/C             |

| A15 | LD9      | C5  | A6              | D21 | $V_{DD}$ | J23 | V <sub>SS</sub> |

<sup>&</sup>lt;sup>†</sup> Thermal connection

# GFW Package Pin Assignments Numerical Listing by Ball Pin Number (Continued)

|     | PIN                          |     | PIN               | PIN |                    | PIN  |                    |

|-----|------------------------------|-----|-------------------|-----|--------------------|------|--------------------|

| NO. | NAME                         | NO. | NAME              | NO. | NAME               | NO.  | NAME               |

| A16 | N/C                          | C6  | A10               | D22 | LD24               | J24  | N/C                |

| A17 | LD11                         | C7  | N/C               | D23 | $V_{SS}$           | J25  | LA16               |

| A18 | LD14                         | C8  | A13               | D24 | N/C                | J26  | LA14               |

| A19 | LD15                         | C9  | A17               | D25 | LA3                | K1   | D16                |

| A20 | LD18                         | C10 | A19               | D26 | LA1                | K2   | D18                |

| A21 | LD20                         | C11 | A23               | E1  | D29                | K3   | N/C                |

| A22 | LD22                         | C12 | N/C               | E2  | V <sub>(SUB)</sub> | K4   | N/C                |

| A23 | N/C                          | C13 | LD2               | E3  | D30                | K23  | LA17               |

| A24 | LD28                         | C14 | LD4               | E4  | D31                | K24  | LA15               |

| A25 | LD30                         | C15 | LD5               | E23 | LA2                | K25  | N/C                |

| A26 | $V_{SS}$                     | C16 | LD8               | E24 | LA0                | K26  | LA18               |

| B1  | A3                           | C17 | N/C               | E25 | LA5                | L1   | D14                |

| B2  | V <sub>SS</sub>              | C18 | LD12              | E26 | LA4                | L2   | D15                |

| В3  | A5                           | C19 | N/C               | F1  | N/C                | L3   | D12                |

| B4  | A9                           | C20 | LD17              | F2  | D28                | L4   | $V_{DD}$           |

| B5  | A11                          | C21 | LD21              | F3  | D26                | L11  | $V_{SS}^{\dagger}$ |

| B6  | A12                          | C22 | LD23              | F4  | $V_{DD}$           | L12  | $V_{SS}^{\dagger}$ |

| В7  | A16                          | C23 | LD26              | F23 | $V_{DD}$           | L13  | $V_{SS}^{\dagger}$ |

| B8  | N/C                          | C24 | $V_{SS}$          | F24 | N/C                | L14  | V <sub>SS</sub> †  |

| B9  | A20                          | C25 | N/C               | F25 | LA9                | L15  | $V_{SS}^{\dagger}$ |

| B10 | N/C                          | C26 | LD31              | F26 | LA7                | L16  | $V_{SS}^{\dagger}$ |

| B11 | LD0                          | D1  | N/C               | G1  | D24                | L23  | $V_{DD}$           |

| B12 | LD3                          | D2  | A0                | G2  | D25                | L24  | LA19               |

| B13 | N/C                          | D3  | N/C               | G3  | D23                | L25  | LA23               |

| B14 | LD7                          | D4  | $V_{SS}$          | G4  | D27                | L26  | LA21               |

| B15 | LD10                         | D5  | A8                | G23 | LA8                | M1   | N/C                |

| B16 | N/C                          | D6  | $V_{DD}$          | G24 | LA6                | M2   | D13                |

| МЗ  | N/C                          | R3  | D3                | W1  | N/C                | AC11 | $V_{DD}$           |

| M4  | D11                          | R4  | D1                | W2  | C4D5               | AC12 | C5D3               |

| M11 | V <sub>SS</sub> †            | R11 | V <sub>SS</sub> † | W3  | RDY0               | AC13 | V <sub>SS</sub>    |

| M12 | V <sub>SS</sub> †            | R12 | V <sub>SS</sub> † | W4  | CE0                | AC14 | N/C                |

| M13 | V <sub>SS</sub> †            | R13 | V <sub>SS</sub> † | W23 | V <sub>SS</sub>    | AC15 | C2D2               |

| M14 | V <sub>SS</sub> †            | R14 | V <sub>SS</sub> † | W24 | LLOCK              | AC16 | $V_{DD}$           |

| M16 | V <sub>SS</sub> †            | R15 | V <sub>SS</sub> † | W25 | ĪĀĒ                | AC17 | N/C                |

| M15 | V <sub>SS</sub> <sup>†</sup> | R16 | V <sub>SS</sub> † | W26 | N/C                | AC18 | V <sub>SS</sub>    |

| M23 | LA20                         | R23 | IACK              | Y1  | C4D3               | AC19 | N/C                |

| M24 | LA22                         | R24 | H3                | Y2  | C4D4               | AC20 | CACK1              |

| M25 | X2CLKIN                      | R25 | C1D2              | Y3  | C4D0               | AC21 | V <sub>DD</sub>    |

| M26 | N/C                          | R26 | LSTAT3            | Y4  | DE                 | AC22 | N/C                |

| N1  | N/C                          | T1  | D2                | Y23 | LRDY1              | AC23 | V <sub>SS</sub>    |

| N2  | N/C                          | T2  | D4                | Y24 | N/C                | AC24 | LRW0               |

| N3  | D7                           | T3  | N/C               | Y25 | TCLK0              | AC25 | LSTRB0             |

| N3  | D7                           | T3  | N/C               | Y25 | TCLK0              | AC25 | LSTRB0             |

<sup>&</sup>lt;sup>†</sup> Thermal connection

# **GFW Package Pin Assignments Numerical Listing by Ball Pin Number (Continued)**

|      | PIN                |      | PIN                | PIN  |                 |      | PIN             |

|------|--------------------|------|--------------------|------|-----------------|------|-----------------|

| NO.  | NAME               | NO.  | NAME               | NO.  | NAME            | NO.  | NAME            |

| N4   | $V_{SS}$           | T4   | $V_{DD}$           | Y26  | TCLK1           | AC26 | LPAGE0          |

| N11  | $V_{SS}^{\dagger}$ | T11  | V <sub>SS</sub> †  | AA1  | C4D1            | AD1  | N/C             |

| N12  | $V_{SS}^{\dagger}$ | T12  | V <sub>SS</sub> †  | AA2  | C4D2            | AD2  | N/C             |

| N13  | V <sub>SS</sub> †  | T13  | $V_{SS}^{\dagger}$ | AA3  | CSTRB4          | AD3  | $V_{SS}$        |

| N14  | V <sub>SS</sub> †  | T14  | V <sub>SS</sub> †  | AA4  | $V_{DD}$        | AD4  | PAGE1           |

| N15  | $V_{SS}^{\dagger}$ | T15  | $V_{SS}^{\dagger}$ | AA23 | $V_{DD}$        | AD5  | STAT0           |

| N16  | $V_{SS}^{\dagger}$ | T16  | $V_{SS}^{\dagger}$ | AA24 | LCE1            | AD6  | STAT2           |

| N23  | H1                 | T23  | $V_{DD}$           | AA25 | LPAGE1          | AD7  | PAGE0           |

| N24  | N/C                | T24  | N/C                | AA26 | LDE             | AD8  | RESETLOC1       |

| N25  | N/C                | T25  | LSTAT1             | AB1  | CRDY4           | AD9  | CSTRB5          |

| N26  | N/C                | T26  | LSTAT2             | AB2  | TCK             | AD10 | C5D7            |

| P1   | D8                 | U1   | N/C                | AB3  | TDO             | AD11 | N/C             |

| P2   | D10                | U2   | D0                 | AB4  | TMS             | AD12 | N/C             |

| P3   | D5                 | U3   | C4D6               | AB23 | LCE0            | AD13 | N/C             |

| P4   | D9                 | U4   | CE1                | AB24 | LSTRB1          | AD14 | C2D7            |

| P11  | $V_{SS}^{\dagger}$ | U23  | C1D4               | AB25 | LRDY0           | AD15 | C2D4            |

| P12  | V <sub>SS</sub> †  | U24  | C1D3               | AB26 | LRW1            | AD16 | C2D1            |

| P13  | $V_{SS}^{\dagger}$ | U25  | N/C                | AC1  | TRST            | AD17 | CRDY2           |

| P14  | $V_{SS}^{\dagger}$ | U26  | LSTAT0             | AC2  | N/C             | AD18 | CDIR1           |

| P15  | VSS <sup>†</sup>   | V1   | RDY1               | AC3  | N/C             | AD19 | CDIR5           |

| P16  | V <sub>SS</sub> †  | V2   | C4D7               | AC4  | $V_{SS}$        | AD20 | CREQ1           |

| P23  | $V_{SS}$           | V3   | LOCK               | AC5  | STRB1           | AD21 | CRDY1           |

| P24  | X1                 | V4   | $V_{SS}$           | AC6  | $V_{DD}$        | AD22 | IIOF3           |

| P25  | C1D1               | V23  | C1D7               | AC7  | N/C             | AD23 | N/C             |

| P26  | C1D0               | V24  | C1D5               | AC8  | $V_{SS}$        | AD24 | $V_{SS}$        |

| R1   | N/C                | V25  | C1D6               | AC9  | STRB0           | AD25 | N/C             |

| R2   | D6                 | V26  | N/C                | AC10 | CACK5           | AD26 | N/C             |

| AE1  | $V_{SS}$           | AE14 | C5D1               | AF1  | V <sub>SS</sub> | AF14 | C5D0            |

| AE2  | V <sub>SS</sub>    | AE15 | N/C                | AF2  | TD1             | AF15 | C2D6            |

| AE3  | EMU0               | AE16 | C2D5               | AF3  | EMU1            | AF16 | C2D3            |

| AE4  | CACK4              | AE17 | N/C                | AF4  | CREQ4           | AF17 | C2D0            |

| AE5  | RW1                | AE18 | N/C                | AF5  | N/C             | AF18 | CSTRB2          |

| AE6  | STAT1              | AE19 | CACK2              | AF6  | N/C             | AF19 | CREQ2           |

| AE7  | N/C                | AE20 | CDIR2              | AF7  | STAT3           | AF20 | CDIR4           |

| AE8  | RW0                | AE21 | CSTRB1             | AF8  | ĀĒ              | AF21 | ROMEN           |

| AE9  | RESETLOC0          | AE22 | IIOF0              | AF9  | RESET           | AF22 | IIOF1           |

| AE10 | CRDY5              | AE23 | N/C                | AF10 | N/C             | AF23 | IIOF2           |

| AE11 | CREQ5              | AE24 | NMI                | AF11 | C5D6            | AF24 | N/C             |

| AE12 | C5D5               | AE25 | V <sub>SS</sub>    | AF12 | C5D4            | AF25 | V <sub>SS</sub> |

| AE13 | N/C                | AE26 | N/C                | AF13 | C5D2            | AF26 | V <sub>SS</sub> |

<sup>&</sup>lt;sup>†</sup> Thermal connection

# GFW Package Pin Assignments Alphabetical Listing by Ball Pin Function

| <u> </u> |                 | 1 7 (30.9 | PIN      | i e  | PIN      | İ    | PIN      |

|----------|-----------------|-----------|----------|------|----------|------|----------|

| NO.      | PIN<br>FUNCTION | NO.       | FUNCTION | NO.  | FUNCTION | NO.  | FUNCTION |

| D2       | A0              | AA1       | C4D1     | P3   | D5       | E25  | LA5      |

| C1       | A1              | AA2       | C4D2     | R2   | D6       | G24  | LA6      |

| C2       | A2              | Y1        | C4D3     | N3   | D7       | F26  | LA7      |

| B1       | АЗ              | Y2        | C4D4     | P1   | D8       | G23  | LA8      |

| C4       | A4              | W2        | C4D5     | P4   | D9       | F25  | LA9      |

| В3       | A5              | U3        | C4D6     | P2   | D10      | H24  | LA10     |

| C5       | A6              | V2        | C4D7     | M4   | D11      | H23  | LA11     |

| A4       | A7              | AF14      | C5D0     | L3   | D12      | H26  | LA12     |

| D5       | A8              | AE14      | C5D1     | M2   | D13      | H25  | LA13     |

| B4       | A9              | AF13      | C5D2     | L1   | D14      | J26  | LA14     |

| C6       | A10             | AC12      | C5D3     | L2   | D15      | K24  | LA15     |

| B5       | A11             | AF12      | C5D4     | K1   | D16      | J25  | LA16     |

| B6       | A12             | AE12      | C5D5     | J3   | D17      | K23  | LA17     |

| C8       | A13             | AF11      | C5D6     | K2   | D18      | K26  | LA18     |

| A7       | A14             | AD10      | C5D7     | J1   | D19      | L24  | LA19     |

| D8       | A15             | AC20      | CACK1    | J2   | D20      | M23  | LA20     |

| В7       | A16             | AE19      | CACK2    | H3   | D21      | L26  | LA21     |

| C9       | A17             | AE4       | CACK4    | H2   | D22      | M24  | LA22     |

| A8       | A18             | AC10      | CACK5    | G3   | D23      | L25  | LA23     |

| C10      | A19             | AD18      | CDIR1    | G1   | D24      | W25  | LAE      |

| В9       | A20             | AE20      | CDIR2    | G2   | D25      | AB23 | LCE0     |

| D10      | A21             | AF20      | CDIR4    | F3   | D26      | AA24 | LCE1     |

| A10      | A22             | AD19      | CDIR5    | G4   | D27      | B11  | LD0      |

| C11      | A23             | W4        | CE0      | F2   | D28      | A12  | LD1      |

| AF8      | ĀĒ              | U4        | CE1      | E1   | D29      | C13  | LD2      |

| P26      | C1D0            | AD21      | CRDY1    | E3   | D30      | B12  | LD3      |

| P25      | C1D1            | AD17      | CRDY2    | E4   | D31      | C14  | LD4      |

| R25      | C1D2            | AB1       | CRDY4    | Y4   | DE       | C15  | LD5      |

| U24      | C1D3            | AE10      | CRDY5    | AE3  | EMU0     | D15  | LD6      |

| U23      | C1D4            | AD20      | CREQ1    | AF3  | EMU1     | B14  | LD7      |

| V24      | C1D5            | AF19      | CREQ2    | N23  | H1       | C16  | LD8      |

| V25      | C1D6            | AF4       | CREQ4    | R24  | H3       | A15  | LD9      |

| V23      | C1D7            | AE11      | CREQ5    | R23  | ĪACK     | B15  | LD10     |

| AF17     | C2D0            | AE21      | CSTRB1   | AE22 | IIOF0    | A17  | LD11     |

| AD16     | C2D1            | AF18      | CSTRB2   | AF22 | IIOF1    | C18  | LD12     |

| AC15     | C2D2            | AA3       | CSTRB4   | AF23 | IIOF2    | B17  | LD13     |

| AF16     | C2D3            | AD9       | CSTRB5   | AD22 | IIOF3    | A18  | LD14     |

| AD15     | C2D4            | U2        | D0       | E24  | LA0      | A19  | LD15     |

| AE16     | C2D5            | R4        | D1       | D26  | LA1      | B19  | LD16     |

| AF15     | C2D6            | T1        | D2       | E23  | LA2      | C20  | LD17     |

| AD14     | C2D7            | R3        | D3       | D25  | LA3      | A20  | LD18     |

| Y3       | C4D0            | T2        | D4       | E26  | LA4      | B20  | LD19     |

<sup>&</sup>lt;sup>†</sup> Thermal connection

# **GFW Package Pin Assignments Alphabetical Listing by Ball Pin Function (Continued)**

|      | PIN PIN           |      | PIN             | 1    | PIN               | -    | PIN                          |

|------|-------------------|------|-----------------|------|-------------------|------|------------------------------|

| NO.  | FUNCTION          | NO.  | FUNCTION        | NO.  | FUNCTION          | NO.  | FUNCTION                     |

| A21  | LD20              | AC7  | N/C             | G25  | N/C               | AB2  | TCK                          |

| C21  | LD21              | AD1  | N/C             | G26  | N/C               | Y25  | TCLK0                        |

| A22  | LD22              | AD11 | N/C             | H1   | N/C               | Y26  | TCLK1                        |

| C22  | LD23              | AD12 | N/C             | J24  | N/C               | AF2  | TD1                          |

| D22  | LD24              | AD13 | N/C             | J4   | N/C               | AB3  | TDO                          |

| B22  | LD25              | AD2  | N/C             | K25  | N/C               | AB4  | TMS                          |

| C23  | LD26              | AD23 | N/C             | K3   | N/C               | AC1  | TRST                         |

| B23  | LD27              | AD25 | N/C             | K4   | N/C               | AA23 | $V_{\mathrm{DD}}$            |

| A24  | LD28              | AD26 | N/C             | M1   | N/C               | AA4  | $V_{\mathrm{DD}}$            |

| B24  | LD29              | AE13 | N/C             | M26  | N/C               | AC11 | $V_{\mathrm{DD}}$            |

| A25  | LD30              | AE15 | N/C             | МЗ   | N/C               | AC16 | $V_{\mathrm{DD}}$            |

| C26  | LD31              | AE17 | N/C             | N1   | N/C               | AC21 | $V_{DD}$                     |

| AA26 | LDE               | AE18 | N/C             | N2   | N/C               | AC6  | $V_{\mathrm{DD}}$            |

| W24  | LLOCK             | AE23 | N/C             | N24  | N/C               | D11  | $V_{\mathrm{DD}}$            |

| V3   | LOCK              | AE26 | N/C             | N25  | N/C               | D16  | $V_{\mathrm{DD}}$            |

| AC26 | LPAGE0            | AE7  | N/C             | N26  | N/C               | D21  | $V_{DD}$                     |

| AA25 | LPAGE1            | AF10 | N/C             | R1   | N/C               | D6   | $V_{DD}$                     |

| AB25 | LRDY0             | AF24 | N/C             | T24  | N/C               | F23  | $V_{DD}$                     |

| Y23  | LRDY1             | AF5  | N/C             | Т3   | N/C               | F4   | $V_{DD}$                     |

| AC24 | LRW0              | AF6  | N/C             | U1   | N/C               | L23  | V <sub>DD</sub>              |

| AB26 | LRW1              | B10  | N/C             | U25  | N/C               | L4   | $V_{DD}$                     |

| U26  | LSTAT0            | B13  | N/C             | V26  | N/C               | T23  | $V_{DD}$                     |

| T25  | LSTAT1            | B16  | N/C             | W1   | N/C               | T4   | $V_{\mathrm{DD}}$            |

| T26  | LSTAT2            | B18  | N/C             | W26  | N/C               | A1   | V <sub>SS</sub>              |

| R26  | LSTAT3            | B21  | N/C             | Y24  | N/C               | A2   | V <sub>SS</sub>              |

| AC25 | LSTRB0            | B8   | N/C             | AE24 | NMI               | A26  | V <sub>SS</sub>              |

| AB24 | LSTRB1            | C12  | N/C             | AD7  | PAGE0             | B2   | V <sub>SS</sub>              |

| A11  | N/C               | C17  | N/C             | AD4  | PAGE1             | B25  | V <sub>SS</sub>              |

| A13  | N/C               | C19  | N/C             | W3   | RDY0              | B26  | V <sub>SS</sub>              |

| A14  | N/C               | C25  | N/C             | V1   | RDY1              | C24  | V <sub>SS</sub>              |

| A16  | N/C               | C7   | N/C             | AF9  | RESET             | C3   | V <sub>SS</sub>              |

| A23  | N/C               | D1   | N/C             | AE9  | RESETLOC0         | D14  | V <sub>SS</sub>              |

| A3   | N/C               | D12  | N/C             | AD8  | RESETLOC1         | D19  | V <sub>SS</sub>              |

| A5   | N/C               | D13  | N/C             | AF21 | ROMEN             | D23  | V <sub>SS</sub>              |

| A6   | N/C               | D17  | N/C             | AE8  | RW0               | D4   | V <sub>SS</sub>              |

| A9   | N/C               | D18  | N/C             | AE5  | RW1               | D9   | V <sub>SS</sub>              |

| AC14 | N/C               | D20  | N/C             | AD5  | STAT0             | H4   | V <sub>SS</sub>              |

| AC17 | N/C               | D24  | N/C             | AE6  | STAT1             | J23  | V <sub>SS</sub>              |

| AC19 | N/C               | D3   | N/C             | AD6  | STAT2             | L11  | V <sub>SS</sub> <sup>†</sup> |

| AC2  | N/C               | D7   | N/C             | AF7  | STAT3             | L12  | V <sub>SS</sub> †            |

| AC22 | N/C               | F1   | N/C             | AC9  | STRB0             | L13  | V <sub>SS</sub> †            |

| AC3  | N/C               | F24  | N/C             | AC5  | STRB1             | L14  | V <sub>SS</sub> <sup>†</sup> |

| L15  | V <sub>SS</sub> † | N4   | V <sub>SS</sub> | T11  | V <sub>SS</sub> † | AD24 | V <sub>SS</sub>              |

<sup>†</sup> Thermal connection

# GFW Package Pin Assignments Alphabetical Listing by Ball Pin Function (Continued)

|     | PIN                |     | PIN                          | F    | PIN                          | ı    | PIN                |

|-----|--------------------|-----|------------------------------|------|------------------------------|------|--------------------|

| NO. | FUNCTION           | NO. | FUNCTION                     | NO.  | FUNCTION                     | NO.  | FUNCTION           |

| L16 | $V_{SS}^{\dagger}$ | P11 | $V_{SS}^{\dagger}$           | T12  | $V_{SS}^{\dagger}$           | AE1  | $V_{SS}$           |

| M11 | $V_{SS}^{\dagger}$ | P12 | $V_{SS}^{\dagger}$           | T13  | V <sub>SS</sub> †            | AE2  | $V_{SS}$           |

| M12 | $V_{SS}^{\dagger}$ | P13 | $V_{SS}^{\dagger}$           | T14  | V <sub>SS</sub> <sup>†</sup> | AE25 | $V_{SS}$           |

| M13 | $V_{SS}^{\dagger}$ | P14 | $V_{SS}^{\dagger}$           | T15  | V <sub>SS</sub> <sup>†</sup> | AF1  | $V_{SS}$           |

| M14 | $V_{SS}^{\dagger}$ | P15 | VSS <sup>†</sup>             | T16  | $V_{SS}^{\dagger}$           | AF25 | $V_{SS}$           |

| M15 | $V_{SS}^{\dagger}$ | P16 | $V_{SS}^{\dagger}$           | V4   | $V_{SS}$                     | AF26 | $V_{SS}$           |

| M16 | $V_{SS}^{\dagger}$ | P23 | $V_{SS}$                     | W23  | $V_{SS}$                     | E2   | V( <sub>SUB)</sub> |

| N11 | $V_{SS}^{\dagger}$ | R11 | $V_{SS}^{\dagger}$           | AC4  | $V_{SS}$                     | P24  | X1                 |

| N12 | $V_{SS}^{\dagger}$ | R12 | $V_{SS}^{\dagger}$           | AC8  | $V_{SS}$                     | M25  | X2CLKIN            |

| N13 | $V_{SS}^{\dagger}$ | R13 | $V_{SS}^{\dagger}$           | AC13 | $V_{SS}$                     |      |                    |

| N14 | $V_{SS}^{\dagger}$ | R14 | $V_{SS}^{\dagger}$           | AC18 | $V_{SS}$                     |      |                    |

| N15 | V <sub>SS</sub> †  | R15 | V <sub>SS</sub> <sup>†</sup> | AC23 | V <sub>SS</sub>              |      |                    |

| N16 | V <sub>SS</sub> †  | R16 | V <sub>SS</sub> †            | AD3  | V <sub>SS</sub>              |      |                    |

<sup>&</sup>lt;sup>†</sup> Thermal connection

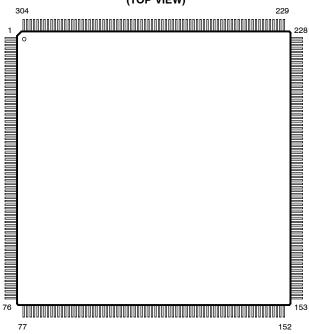

## block diagram

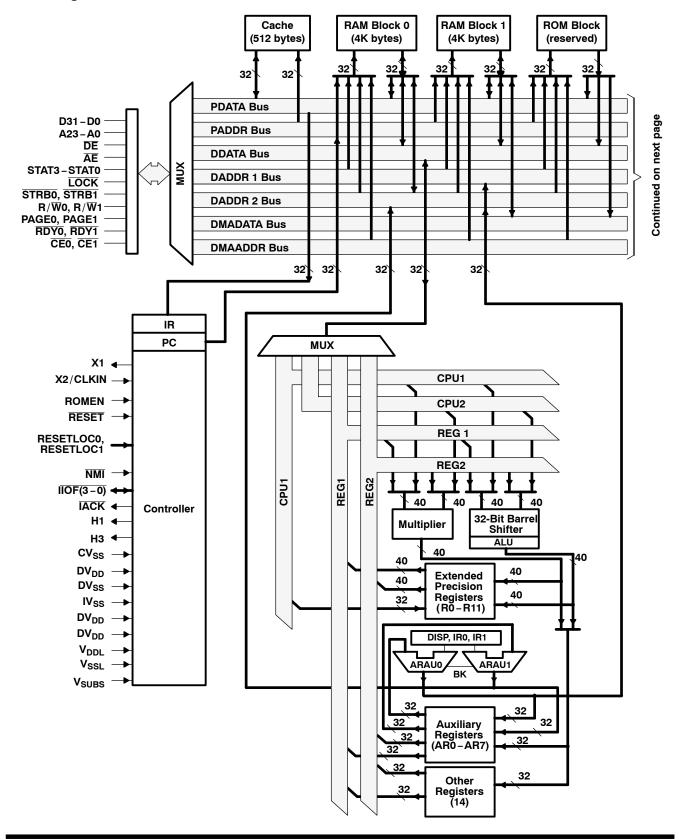

## block diagram (continued)

<sup>&</sup>lt;sup>†</sup> Communication ports 0 and 3 are not connected.

#### memory map

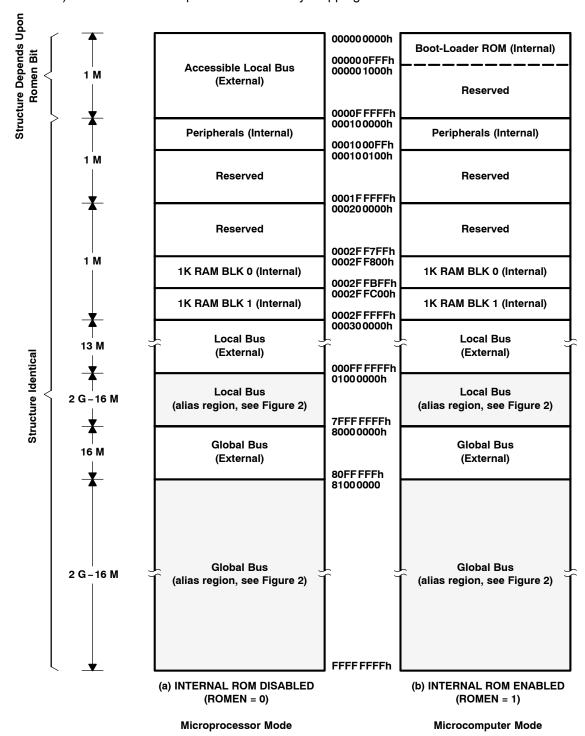

Figure 1 shows the memory map for the C44. Refer to the *TMS320C4x User's Guide* (literature number SPRU063) for a detailed description of this memory mapping.

Figure 1. Memory Map for TMS320C44

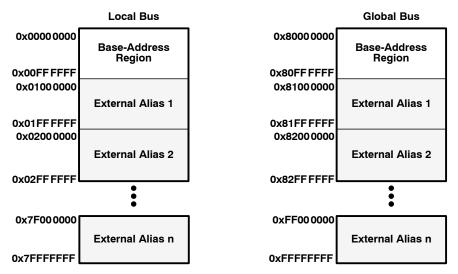

#### memory aliasing

The C44 offers global and local addresses of A0-A23 and LA0-LA23, giving an external address reach of (2 buses)  $\times$  (2<sup>24</sup>) = 2<sup>25</sup> words. Since the internal address span of the C44 is 2<sup>32</sup> words, reading or writing to memory outside of the base-address region causes memory aliasing. Figure 2 shows how the memory pages overlap each other.

Figure 2. Memory Alias

#### central processing unit

The C44 CPU is configured for high-speed internal parallelism for the highest sustained performance. The key features of the CPU are:

- Eight operations/cycle:

- 40-/32-bit floating-point/integer multiply

- 40-/32-bit floating-point/integer ALU operation

- Two data accesses

- Two address-register updates

- Floating-point conversion

- Divide and square-root support

- C3x and C4x assembly-language compatibility

- Byte and halfword accessibility

#### **DMA** coprocessor

The DMA coprocessor allows concurrent I/O and CPU processing for the highest sustained CPU performance. The key features of the DMA coprocessor are:

- Link pointers to allow DMA channels to autoinitialize without CPU intervention

- Parallel CPU operation and DMA transfers

- Six DMA channels to support memory-to-memory data transfers

- Split-mode operation which doubles the available channels to twelve when data transfers to and from a communication port are required

#### communication ports

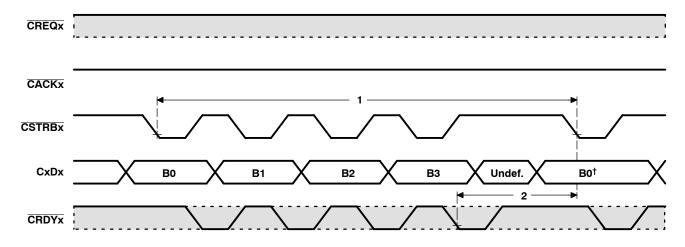

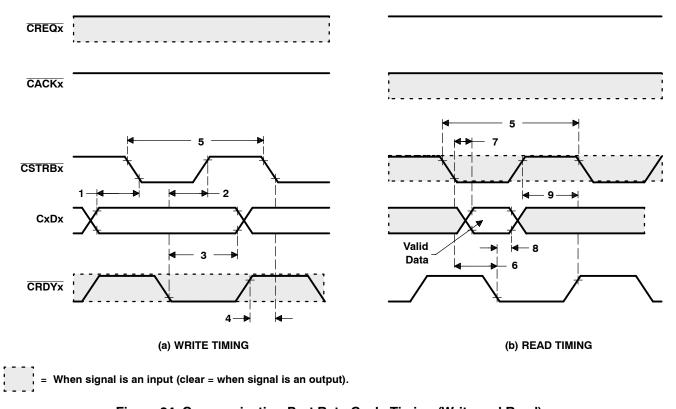

The C44 contains four identical high-speed communication ports, each of which provides a bidirectional-communication interface to other C4x devices and external peripherals. The key features of the communication ports are:

- Direct interprocessor communication and processor I/O

- 20M-byte/s bidirectional interface on each communication port for high-speed multiprocessor interface

- Port direction pin (CDIR) to ease interfacing

- Separate input and output 8-word-deep FIFO buffers for processor-to-processor communication and I/O

- Automatic arbitration and handshaking for direct processor-to-processor connection

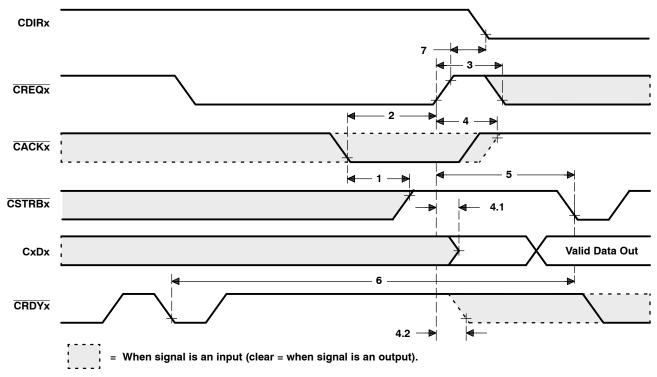

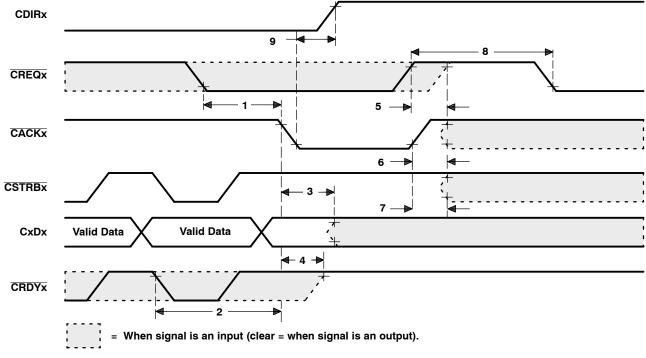

## communication-port direction pin

A port-direction pin (CDIR1, CDIR2, CDIR4, CDIR5) is available for each C44 communication port. When the communication port is in the output mode, CDIRx is driven low. When the communication port is in the input mode, CDIRx is driven high. The truth table for two C44 devices is shown in Table 1. Communication port 1 of CPUA is connected to communication port 4 of CPUB.

CDIR<sub>1</sub> CDIR4 **DESCRIPTION** 0 0 Token error 0 1 CPUA is configured to transmit to CPUB. 1 0 CPUB is configured to transmit to CPUA. 1 1

Token exchange overlap, if > 1H then token error

Table 1. Truth Table for Two C44 Devices

#### communication-port-software reset

The input and output FIFO levels for a communication port can be flushed by writing at least two back-to-back values to its communication-port software-reset address as specified in Table 2. This software reset flushes any word or byte already present in the FIFOs, but it does not affect the status of the communication-port pins.

Table 2. Communication-Port Software-Reset Address

| COMMUNICATION PORT | SOFTWARE-RESET ADDRESS |

|--------------------|------------------------|

| 1                  | 0x0100053              |

| 2                  | 0x0100063              |

| 4                  | 0x0100083              |

| 5                  | 0x0100093              |

#### communication-port-software reset (continued)

When used in conjunction with the communication-port direction pins and NMI bus-grant, an effective method of error detection and correction can be achieved. A subroutine showing how to reset communication port 1 is given in Figure 3.

```

; RESET1:Flushes FIFOs data for communication port 1;

; ----;

; Save registers

RESET1 push AR0

push R0

push RC

ldhi 010h,ARO ; Set ARO to base address of COM 1

or 050h,AR0

1

; Flush FIFO data with back-to-back write

FLUSH: rpts

sti R0,*+AR0(3);

rpts 10

; Wait

nop

*+ARO(0),RO ; Check for new data from other port

ldi

01FE0h,R0 ;

and

bnz

FLUSH

pop

RC

; Restore registers

pop

R0

ARO

pop

rets

; Return

```

Figure 3. Example of Communication-Port-Software Reset

#### NMI with bus-grant feature

The C44 devices have a software-configurable feature that allows forcing the internal-peripheral bus ready when the  $\overline{\text{NMI}}$  signal is asserted. The  $\overline{\text{NMI}}$  bus-grant feature is enabled when bits 19 and 18 of the status register (ST) are set to 10b. When enabled, a peripheral bus-grant signal is generated on the falling edge of  $\overline{\text{NMI}}$ . If  $\overline{\text{NMI}}$  is asserted and this feature is not enabled, the CPU stalls on access to the peripheral bus if it is not ready. A stall condition occurs when writing to a full output FIFO or reading an empty input FIFO. This feature is useful in correcting communication-port errors when used in conjunction with the communication-port software-reset feature.

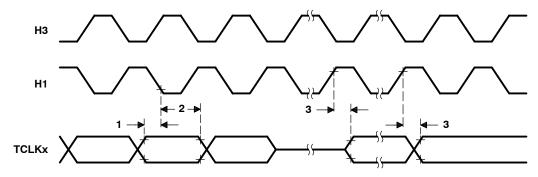

#### IDLE2 clock-stop power-down mode

The C44 has a clock-stop mode, or power-down mode (IDLE2) to achieve extremely low power consumption. When an IDLE2 instruction is executed, the clocks are halted with H1 held high. (Exiting IDLE2 requires asserting one of the  $\overline{\text{IIOF3}}$ – $\overline{\text{IIOF0}}$  pins configured as an external interrupt.) A macro showing how to generate the IDLE2 opcode is given in Figure 4. During this power-down mode:

- No instructions are executed.

- The CPU, peripherals, and internal memory retain their previous state.

- The external-bus outputs are idle. The address lines remain in their previous state; the data lines are in the high-impedance state; and the output-control signals are inactive.

## IDLE2 clock-stop power-down mode (continued)

```

; IDLE2: Macro to generate idle2 opcode

; ------

IDLE2 .macro

.word 06000001h

.endm

```

Figure 4. Example Software Subroutine Using IDLE2

IDLE2 is exited when one of the five external interrupts (NMI and IIOF3 – IIOF0) is asserted low for at least four input clocks (two H1 cycles). The clocks then start after a delay of two input clocks (one H1 cycle). The clocks can start in the opposite phase; that is, H1 can be high when H3 was high before the clocks were stopped. However, the H1 and H3 clocks remain 180 degrees out of phase with each other.

During IDLE2 operation, an external interrupt can be recognized and serviced by the CPU if it is enabled before entering IDLE2 and asserted for at least two H1 cycles. For the processor to recognize only one interrupt, the interrupt pin must be configured for edge-trigger mode or asserted less than three cycles in level-trigger mode. Any external interrupt pin can wake up the device from IDLE2, but for the CPU to recognize that interrupt, it must also be enabled. If an interrupt is recognized and executed by the CPU, the instruction following the IDLE2 instruction is not executed until after a return opcode is executed.

When the device is in emulation mode, the CPU executes an IDLE2 instruction as if it were an IDLE instruction. The clocks continue to run for correct operation of the emulator.

#### boot-loader mode selection

Table 3. Boot-Loader Mode Selection Using Pins IIOF3 – IIOF0

|       | EXTER | NAL PIN |       | COURCE PROCRAM LOCATION                                  |  |  |

|-------|-------|---------|-------|----------------------------------------------------------|--|--|

| IIOF3 | IIOF2 | IIOF1   | IIOF0 | SOURCE PROGRAM LOCATION                                  |  |  |

| 1     | 1     | 0       | 1     | Load source program from address 0030 0000h              |  |  |

| 1     | 0     | 1       | 1     | Load source program from address 4000 0000h (see Note 1) |  |  |

| 1     | 0     | 0       | 1     | Load source program from address 80 0000h                |  |  |

| 0     | 1     | 1       | 1     | Load source program from address 8000 0000h (see Note 2) |  |  |

| 0     | 1     | 0       | 1     | Load source program from address 8040 0000h (see Note 3) |  |  |

| 0     | 0     | 1       | 1     | Load source program from address 8080 0000h (see Note 4) |  |  |

| 0     | 0     | 0       | 1     | Reserved (boot-loader program terminates)                |  |  |

| 1     | 1     | 1       | 1     | Load source program from communication port              |  |  |

NOTES: 1. This selection cause the C44 to drive 0 in the 24 external local address pins and activates the LSTRB0 signal.

- 2. This selection cause the C44 to drive 0 in the 24 external global address pins ando activates the STRB0 signal.

- 3. This selection cause the C44 to drive 0x40 0000 in the 24 external global address pins and activates the STRB0 signal.

- 4. This selection cause the C44 to drive 0x80 0000 in the 24 external global address pins and to activate the STRBO signal.

#### development tools

A key aspect to a parallel-processing implementation is the development tools available. The C44 is supported by a host of parallel-processing tools for developing and simulating code easily and for debugging parallel-processing systems. The code-generation tools include:

- An optimizing ANSI C compiler with a runtime-support library that supports use of communication ports and DMA

- Third party support for C, C++, and Ada compilers

- Several operating systems available for parallel-processing support as well as DMA and communication-port drivers

- Assembler and linker with support for mapping program and data to parallel processors

The simulation tools include a TI software-simulator with a high-level-language debugger interface for simulating a single processor. The hardware development and verification tools consist of the XDS510<sup>™</sup> (parallel-processor in-circuit emulator and high-level-language debugger).

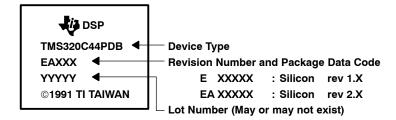

#### silicon revision identification

## silicon revision identification (continued)

**Table 4. Device Descriptions**

| DEVICE PART NUMBER | VOLTAGE | OPERATING FREQUENCY | COMM<br>PORTS | PACKAGE                                    |

|--------------------|---------|---------------------|---------------|--------------------------------------------|

| TMS320C40GFL       | 5 V     | 50 MHz/40 ns        | 6             | 325-pin ceramic PGA                        |

| TMS320C40GFL60     | 5 V     | 60 MHz/33 ns        | 6             | 325-pin ceramic PGA                        |

| TMS320C44PDB50     | 5 V     | 50 MHz/40 ns        | 4             | 304-pin PQFP                               |

| TMS320C44PDB60     | 5 V     | 60 MHz/33 ns        | 4             | 304-pin PQFP                               |

| TMS320C44GFW       | 5 V     | 50 MHz/40 ns        | 4             | 388-pad ball grid array                    |