# Am26LS32/Am26LS33

### **Quad Differential Line Receivers**

Advanced Micro Devices

#### DISTINCTIVE CHARACTERISTICS

- Input voltage range of 15 V (differential or common mode) on Am26LS33; 7 V (differential or common mode) on Am26LS32

- 200 mV sensitivity over the input voltage range on Am26LS32;

- 500 mV sensitivity on Am26LS33

- 6k minimum input impedance with 30 mV input hysteresis

- The Am26LS32 meets all the requirements of RS-422 and RS-423

- Operation from single +5 V supply

- Fail safe input-output relationship. Output always high when inputs are open

- Three-state drive, with choice of complementary output enables, for receiving directly onto a data bus

#### **GENERAL DESCRIPTION**

The Am26LS32 is a quad line receiver designed to meet the requirements of RS-422 and RS-423, and Federal Standards 1020 and 1030 for balanced and unbalanced digital data transmission.

The Am26LS32 features an input sensitivity of 200 mV over the input voltage range of  $\pm 7$  V.

The Am26LS33 features an input sensitivity of 500 mV over the input voltage range of  $\pm 15$  V.

The Am26LS32 and Am26LS33 provide an enable and disable function common to all four receivers. Both parts feature 3-state outputs with 8 mA sink capability and incorporate a fail safe input-output relationship which keeps the outputs high when the inputs are open.

The Am26LS32 and Am26LS33 are constructed using Advanced Low-Power Schottky processing.

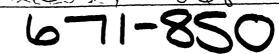

#### **BLOCK DIAGRAM**

#### 05393-0018

#### **RELATED AMD PRODUCTS**

| Part No. | Description                                                              |

|----------|--------------------------------------------------------------------------|

| 26LS29   | Quad Three-State Single Ended RS-423 Line Driver                         |

| 26LS30   | Dual Differential RS-422 Party Line/Quad Single Ended RS-423 Line Driver |

| 26LS31   | Quad High Speed Differential Line Driver                                 |

Publication# 05393 Rev. B. Amendment/0 issue Date: Mey 1991

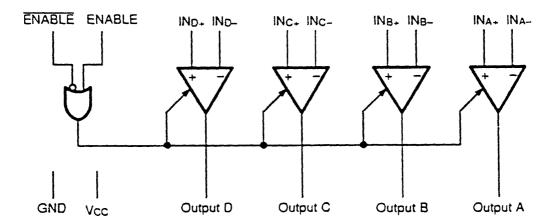

# CONNECTION DIAGRAMS

Top View

DIP

05393-002B

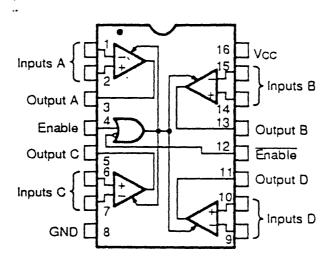

# LCC

#### Note:

Pin 1 is marked for orientation.

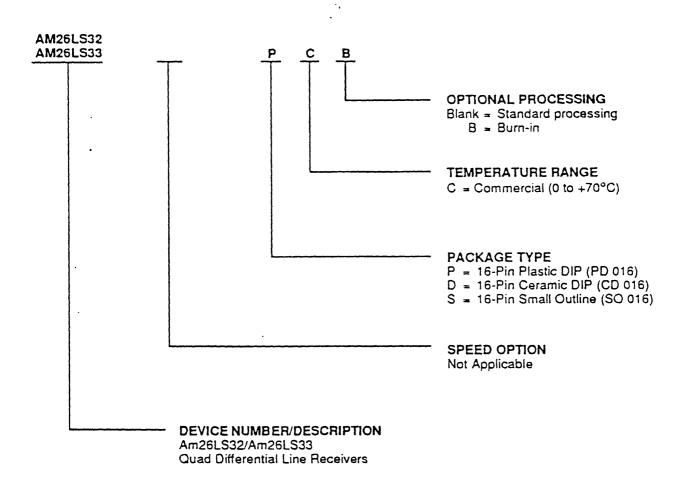

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |              |  |  |  |

|--------------------|--------------|--|--|--|

| AM26LS32           | PC, PCB, DC, |  |  |  |

| AM26LS33           | DCB, SC      |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

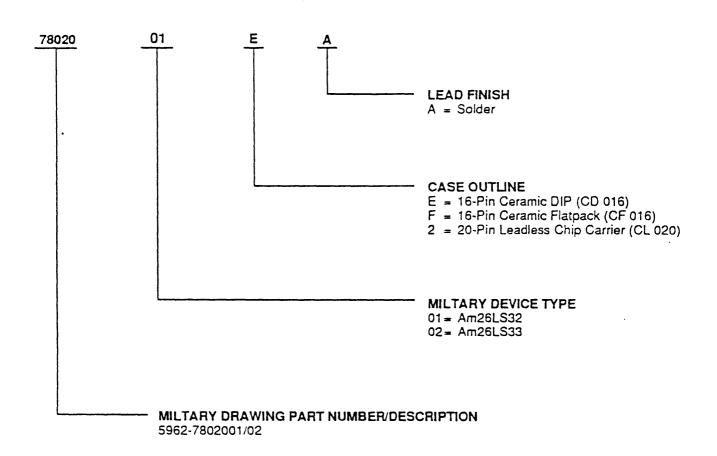

# MILITARY ORDERING INFORMATION Standard Military Drawing (SMD)/DESC Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. Standard Military Drawing (SMD)/DESC products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for SMD/DESC products is formed by a combination of:

| Valid Combinations |           |  |  |  |  |  |

|--------------------|-----------|--|--|--|--|--|

| 5962-7802001       | MEA. MFA. |  |  |  |  |  |

| 5962-7802002       | M2A       |  |  |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, or to check on newly released combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

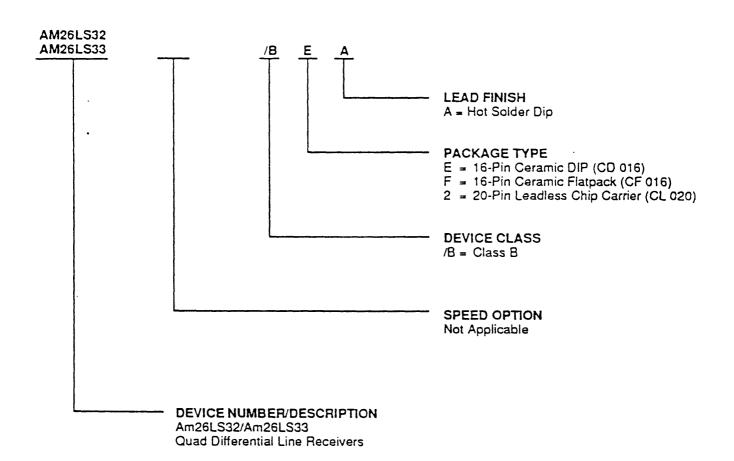

# MILITARY ORDERING INFORMATION APL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |                  |  |  |  |  |

|--------------------|------------------|--|--|--|--|

| AM26LS32           | (054 (054 (064   |  |  |  |  |

| AM26LS33           | /BEA, /BFA, /B2A |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, or to check on newly released combinations.

### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### **OPERATING RANGES** ABSOLUTE MAXIMUM RATINGS Commercial (C) Devices 7.0 V Supply Voltage Temperature 0 to +70°C ±25 V Common Mode Range Supply Voltage +4.75 V to +5.25 V ±25 V Differential Input Voltage 7.0 V Military (M) Devices Enable Voltage -55 to +125°C Temperature Output Sink Current 50 mA

Supply Voltage

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

Storage Temperature Range

Operating ranges define those limits between which the functionality of the device is guaranteed.

+4.5 V to +5.5 V

### DC CHARACTERISTICS over operating ranges unless otherwise specified

-65 to +165°C

| Parameter<br>Symbol | Parameter Description        | Test Conditions                                                         |                                      | Min. | Typ.<br>(Note 1) | Max.  | Unit  |      |    |

|---------------------|------------------------------|-------------------------------------------------------------------------|--------------------------------------|------|------------------|-------|-------|------|----|

| Vтн                 | Differential Input Voltage   |                                                                         | Am26LS32, -                          | 7 V  | ≤                | -0.2  | ±0.06 | +0.2 |    |

|                     |                              | Vout = Vol<br>or Voh<br>(Note 5)                                        | Vcм ≤ +7 V                           |      |                  |       |       |      |    |

|                     |                              |                                                                         | Am26LS33, -15 V ≤                    |      | -0.5             | ±0.12 | +0.5  | V    |    |

|                     |                              | (14016-5)                                                               | Vcм ≤ +15 V                          |      |                  | ·s.   |       |      |    |

| RIN                 | Input Resistance             | -15 V ≤ Vcм ≤ +15 V<br>(One input AC ground) (Note 4)                   |                                      |      | 6.0              | 9.8   |       | kΩ   |    |

| tin                 | Input Current (Under Test)   | V <sub>IN</sub> = +15 V, Other Input -15 V ≤ V <sub>IN</sub> ≤ +15 V    |                                      |      |                  | 2.3   | mA    |      |    |

| lin                 | Input Current (Under Test)   | V <sub>IN</sub> = −15 V, Other Input −15 V ≤ V <sub>IN</sub> ≤<br>+15 V |                                      |      | ·· .             | -2.8  | mA    |      |    |

| Voн                 | Output HIGH Voltage          | Vcc = Min.,                                                             | $\Delta V_{IN} = +1.0 V$             |      | COM'L            | 2.7   | 3.4   |      |    |

|                     |                              | VENABLE = 0.                                                            | 8  V, loh = -440                     | μА   | MIL              | 2.5   | 3.4   |      | V  |

| Vol                 | Output LOW Voltage           | Vcc = Min., ΔVIN = -1.0 V                                               |                                      |      |                  | 0.4   | ,, ,  |      |    |

|                     |                              |                                                                         |                                      |      |                  | 0.45  | V     |      |    |

| VIL                 | Enable LOW Voltage           | (Note 2)                                                                |                                      |      |                  | 0.8   | ٧     |      |    |

| ViH                 | Enable HIGH Voltage          | (Note 2)                                                                |                                      | 2.0  |                  |       | V     |      |    |

| Vic                 | Enable Clamp Voltage         | Vcc = Min.,                                                             | Vcc = Min., I <sub>IN</sub> = -18 mA |      |                  |       | -1.5  | ٧    |    |

| lo                  | Off-state (High Impedance)   | Vcc = Max.                                                              |                                      | Vo   | = 2.4 V          |       |       | 20   | μΑ |

|                     | Output Current               |                                                                         |                                      | Vo   | = 0.4 V          |       |       | -20  | μΛ |

| lıL                 | Enable LOW Current           | Vin = 0.4 V, Vcc = Max.                                                 |                                      |      | -0.2             | -0.36 | mA    |      |    |

| lıн                 | Enable HIGH Current          | Vin = 2.7 V, Vcc = Max.                                                 |                                      |      |                  | 20    | μА    |      |    |

| ſı                  | Enable Input High Current    | Vin = 5.5 V, Vcc = Max.                                                 |                                      |      |                  | 100   | μА    |      |    |

| Isc                 | Output Short Circuit Current | Vo = 0 V, Vcc = Max., ΔVin = +1.0 V<br>(Note 3)                         |                                      | -15  | 50               | -85   | mA    |      |    |

| lcc                 | Power Supply Current         | Vcc = Max., All V <sub>IN</sub> = GND,<br>Outputs Disabled              |                                      |      | 52               | 70    | mA    |      |    |

| VHYST               | Input Hysteresis             | TA = 25°C, Vcc = 5.0 V, Vcm = 0 V                                       |                                      |      | 30               |       | m۷    |      |    |

#### Notes:

- 1. All typical values are Vcc = 5.0 V, TA = 25°C.

- 2. Input thresholds are tested during DC tests and may be done in combination with testing of other DC parameters.

- 3. Not more than one output should be shorted at a time. Duration of short circuit test should not exceed one second.

- 4. Rin is not directly tested but is correlated. (See Attachment I)

- 5. Input voltage is not tested directly due to tester accuracy limitation but is threshold correlated. (See Attachment II)

# **SWITCHING CHARACTERISTICS**

| Parameter<br>Symbol | Parameter Description                      | Test Conditions                                                                                   | Min. | Typ.<br>(Note 1) | Max. | Unit |

|---------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|------|------------------|------|------|

| AC Parame           | eters (TA = +25°C)                         |                                                                                                   |      | ·                | ,    |      |

| tplH                | Propagation Delay From Input to Output     | C <sub>L</sub> 15 pF, R <sub>L1</sub> = 5 k $\Omega$ , R <sub>L2</sub> = 2 k $\Omega$ , Vcc = 5.0 |      | 17               | 25   | ns   |

| <b>TPHL</b>         | Propagation Delay From Input to Output     | C <sub>L</sub> 15 pF, R <sub>L1</sub> = 5 k $\Omega$ , R <sub>L2</sub> = 2 k $\Omega$ , Vcc = 5.0 |      | 17               | 25   | ns   |

| tız                 | Enable to Output                           | $V_{CC}$ = 5.0, C <sub>L</sub> 5 pF, R <sub>L1</sub> = 5 kΩ, R <sub>L2</sub> = 2 kΩ               |      | 20               | 30   | ns   |

| tHZ                 | Enable to Output                           | $V_{CC}$ = 5.0, C <sub>L</sub> 5 pF, R <sub>L1</sub> = 5 kΩ, R <sub>L2</sub> = 2 kΩ               |      | 15               | 22   | ns   |

| tzı                 | Enable to Output                           | Vcc = 5.0, CL 15 pF, RL <sub>1</sub> = 5 kΩ, RL <sub>2</sub> = 2 kΩ                               |      | 15               | 22   | ns   |

| tzн                 | Enable to Output                           | Vcc = 5.0, CL 15 pF, RL <sub>1</sub> = 5 k $\Omega$ , RL <sub>2</sub> = 2 k $\Omega$              |      | 15               | 22   | ns   |

| AC Param            | eters (-55°C to +125°C)                    |                                                                                                   |      |                  |      |      |

| tры                 | Propagation Delay From Input to Output     | C <sub>L</sub> 15 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$ ,        |      | 23               | 38   | ns   |

| tphL                | Propagation Delay From Input to Output     | CL 15 pF, RL <sub>1</sub> = 5 k $\Omega$ ,<br>RL <sub>2</sub> = 2 k $\Omega$                      |      | 22               | 38   | ns   |

| tpzH                | Propagation Delay From<br>Enable to Output | $C_L$ 15 pF, $R_{L1}$ = 5 k $\Omega$ , $R_{L2}$ = 2 k $\Omega$                                    |      | 17               | 33   | ns   |

| tpzL                | Propagation Delay From<br>Enable to Output | C <sub>L</sub> 15 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$          | ,    | 25               | 33   | ns   |

| tpHZ                | Propagation Delay From<br>Enable to Output | C <sub>L</sub> 5 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$           |      | 18               | 33   | ns   |

| tplz                | Propagation Delay From<br>Enable to Output | C <sub>L</sub> 5 pF, $R_{L1} = 5 k\Omega$ , $R_{L2} = 2 k\Omega$                                  |      | 24               | 45   | ns   |

| Tristate D          | elays for Enable (TA = +25°C               | C)                                                                                                |      |                  |      |      |

| tрzн                | Propagation Delay From Enable to Output    | CL 15 pF, RL <sub>1</sub> = 5 k $\Omega$ ,<br>RL <sub>2</sub> = 2 k $\Omega$                      |      | 16               | 32   | ns   |

| tpzL                | Propagation Delay From Enable to Output    | C <sub>L</sub> 15 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$          |      | 23               | 33   | ns   |

| tpHZ                | Propagation Delay From Enable to Output    | C <sub>L</sub> 5 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$           |      | 14               | 24   | ns   |

| tplz                | Propagation Delay From Enable to Output    | C <sub>L</sub> 5 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$           |      | 14               | 32   | ns   |

| Tristate D          | elays for Enable (-55°C to                 | -125°C)                                                                                           |      |                  |      |      |

| tezh                | Propagation Delay From Enable to Output    | C <sub>L</sub> 15 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$          |      | 23               | 48   | ns   |

| tezl                | Propagation Delay From Enable to Output    | C <sub>L</sub> 15 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$          |      | 35               | 50   | ns   |

| tpHZ                | Propagation Delay From Enable to Output    | C <sub>L</sub> 5 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$           |      | 20               | 36   | ns   |

| tplz                | Propagation Delay From Enable to Output    | C <sub>L</sub> 5 pF, R <sub>L1</sub> = 5 k $\Omega$ ,<br>R <sub>L2</sub> = 2 k $\Omega$           |      | 22               | 48   | ns   |

#### Note:

<sup>1.</sup> All typical values are Vcc = 5.0 V, Ta = 25°C,

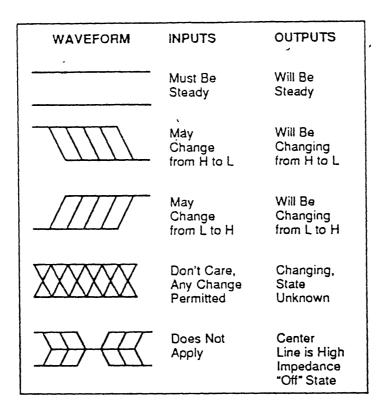

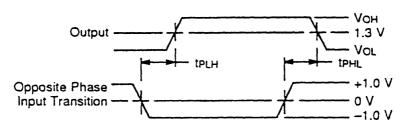

# **(EY TO SWITCHING WAVEFORMS**

KS000010

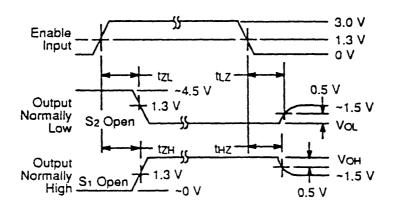

#### SWITCHING WAVEFORMS

Propagation Delay (Notes 1 and 3)

05393-004B

### Enable and Disable Times (Notes 2 and 3)

05393-005B

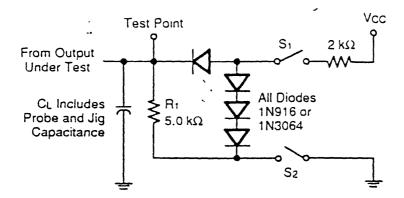

- 1. Diagram shown for ENABLE LOW.

- 2. S1 and S2 of Load Circuit are closed except where shown.

- 3. Pulse Generator for All Pulses: Rate  $\leq$  1.0 MHz; Zo = 50  $\Omega$ ; tr  $\leq$  15 ns; tr  $\leq$  6.0 ns.

Notes:

# SWITCHING TEST CIRCUIT FOR THREE-STATE OUTPUTS

05393-006B

# Am26LS32/32B/33/34 Input Resistance and Input Current (Attachment I)

Input resistance measurement for differential inputs on line receivers are generally not measured directly. Instead they are correlated to an input current measurement and to the process resistor temperature coefficient. The assumptions made include 1) Process resistor temperature coefficient is known and 2) The open input bias voltage for the input is known or measured within the same test sequence.

Under the above assumptions R<sub>IN</sub> can be correlated to the input current measured. The expression

$$R_{IN} = \frac{(V_{ICM} - V_{IN}) (R_T)}{(I_{IN}) (R25)}$$

where V<sub>ICM</sub> is the open input bias voltage of the Line Receiver. When applying this correlation to the 26LS32 die, the following criteria have been set.

- 1) Vicm and lin are the values screened at wafer sort.

- 2) Temperature coefficients are for 800 ohm/square which gives 0.96 at 0°C and 0.93 at -55°C.

When setting limits, characterized values for  $V_{ICM}$  have been used instead of the test programmed limit value.  $R_{IN}$  (dif) is  $R_{IN}$  (dif) = 2  $R_{IN}$ .

For the Am26LS32/32B/33/34

RIN Min. =

$$\frac{(2.56 - -15) \ 0.96}{\text{lin (Max.)}} = 16.8/\text{lin (Max.)}$$

Comm.,

and

RIN Min. = 16.3/lin (Max.) Mil.

# Worst Case Measurement for Input Current

Two considerations have been used to determine the test condition for input current of the data path for the Am26LS32 Line Receiver.

- 1) Input current is tested on the 26LS32 with the pin under test at one end of the range (+15 V for example) and the untested pin at the opposite extreme of the input range under test. If both pins were at the same test voltage the internal bias generator would have a lower output voltage for tests at -15 V VIN and a higher output voltage at +15 V VIN. This would produce test currents less than maximum.

- 2) For the 26LS32, breakdown of the differential inputs is the primary failure to the data sheet specification. Hence, both breakdown voltage and input current are tested during the input current tests.

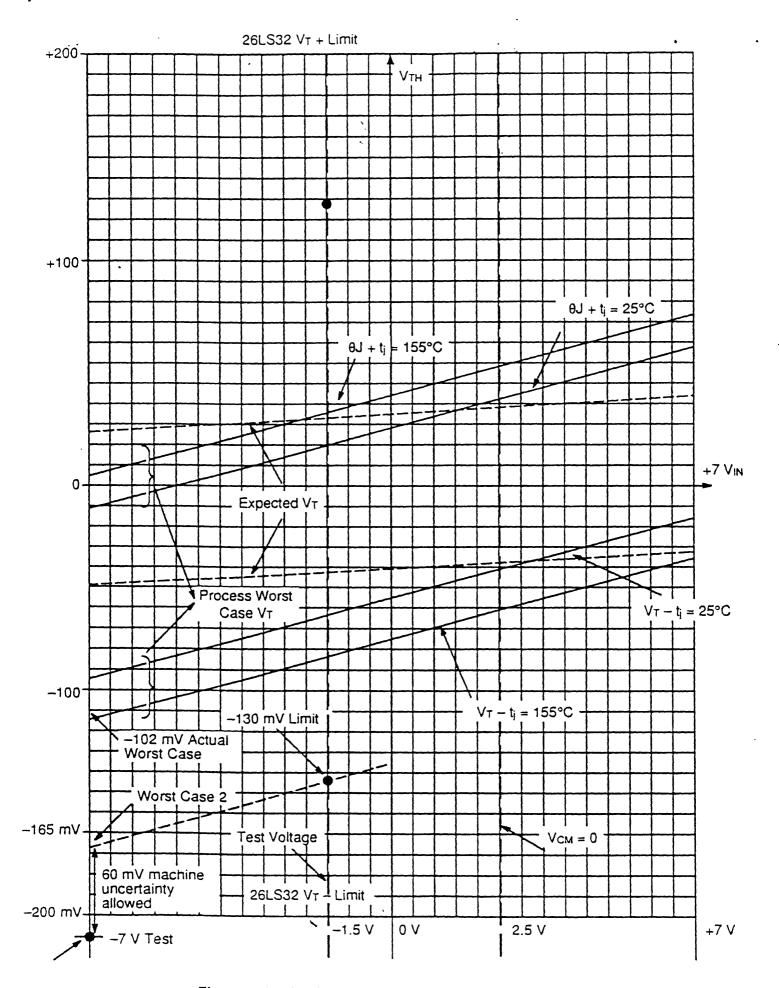

# Test Documentation For Am26LS32/32B/34 V<sub>TH</sub> (Attachment II)

nput threshold (VTH) for the Am26LS32/32B/34 is described by the equation,

$V_{TH} = (N+1) (1+R1/R) K^*T/Q ((1+Rh/(m (Rc+Rh))) (1-Rh/(M(Rc+Rh))).$

Where N+1 is the attenuator ratio, R1/R is the attenuator, ratio mismatch, M is the ratio of the input stage current to hysteresis stage current, and Rh and Rc are input stage oads. For Am26LS32 – 34 devices which pass function tests, VoH and VoL tests, thresholds for all inputs within the operating range of the circuit.

The Test system is unable to force input thresholds within the accuracy required for the Am26LS32 - 34 specifications. Figure 1 plots the expected values for V<sub>TH</sub>, the worst case values at 25°C and 155°C. Also shown are the test values for V<sub>TH</sub> at the -1.5 V input (V<sub>IN</sub>). In addition, the test voltage at -7 V V<sub>IN</sub> is shown. For the figure it is seen that the worst case value for the test limit shown would be +/-165 mV, where +/-102 mV

is expected for process parameters and the equation for  $V_{TH}$ . Further the 25 mV negative guardband used for -7 V testing is less than half the machine uncertainty of 60 mV.

When QA testing for Am26LS32/32B/34 is done, thresholds are screened for Vcm other than -1.5 V. These additional tests are considered functional tests only, and the precision threshold tests which insure compliance with data sheet limits are those tests performed where the inputs are tested near -1.5 V.

The actual threshold tests are done as a sequence where a setup is performed which preconditions the DUT to a logic one state, then the threshold correlation for a logic zero is tested followed by a threshold correlation for logic one to complete the sequence. The limit values for the setup (Vt SET), logic zero test (Vt "–"), and logic one test (Vt "+") are listed under VTH for supply value of 5.0 V.

Figure 1. 26LS32 Input Threshold  $V_{T}$  vs. Input Voltage  $V_{IN}$