# Am29C660/A/B/C/D/E

# CMOS Cascadable 32-Bit Error Detection and Correction Circuit

#### DISTINCTIVE CHARACTERISTICS

- **■** Improves memory reliability

- Corrects all single-bit errors. Detects all double- and some triple-bit errors

- Very high-speed error detection and correction

- Down to 9 ns data-in to error detection

- Low-power CMOS process

- Cascadable for data words up to 64 bits

- Simplified byte operations

- Separate byte enables on the Data Output Latch for fast byte writes

- Built-in diagnostics

- Proper EDC operation can be verified by the CPU via software control

- Detects gross error conditions of all 1's or all 0's

#### **GENERAL DESCRIPTION**

The Am29C660 CMOS Cascadable 32-Bit Error Detection and Correction Circuit (EDC) contains the logic necessary to generate check bits on a 32-bit data field according to a modified Hamming Code, and to correct the data word when check bits are supplied. Operating on data read from memory, the Am29C660 detects and corrects all single-bit errors and detects all double- and some triple-bit errors. For 32-bit words, 7 check bits are used.

The Am29C660 is expandable to operate on 64-bit data words (8 check bits). In both configurations, the device

makes error syndromes available on separate outputs for error logging.

The Am29C660 also features two diagnostic modes in which diagnostic data can be forced into portions of the chip to simplify device testing and to execute system diagnostic functions.

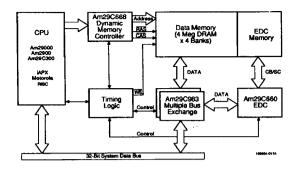

When used with the Am29C668 Dynamic Memory Controller, the Am29C660 can perform AMD's invented memory "scrubbing" operation to provide highest data integrity.

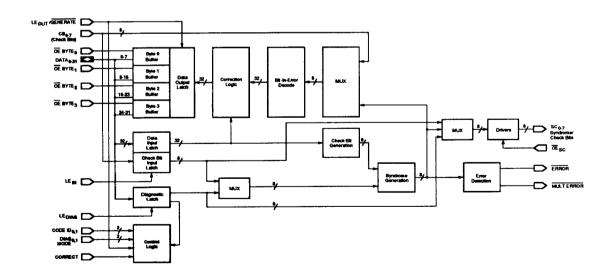

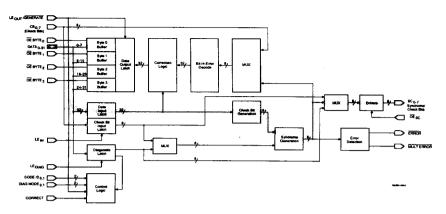

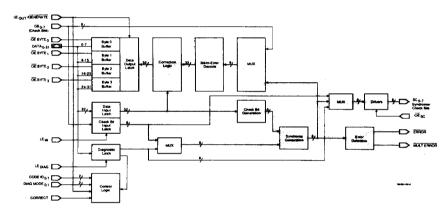

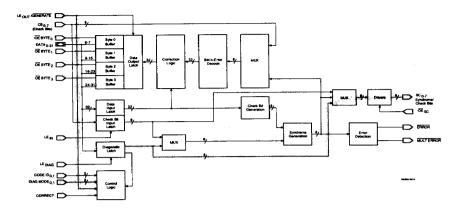

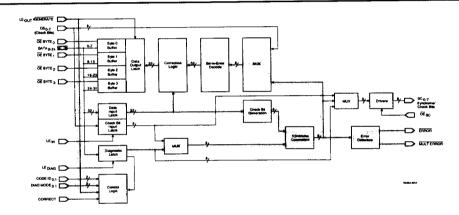

#### **BLOCK DIAGRAM**

10565-001A

Publications 10565 Rev. C Amendment/0 lesue Date: August 1991

6-29

# **RELATED AMD PRODUCTS**

| Part No.  | Description                                      |

|-----------|--------------------------------------------------|

| Am29C668  | 4M Configurable Dynamic Memory Controller/Driver |

| Am29C983A | 9-Bit x 4-Port Multiple Bus Exchange, High Speed |

| Am29C985  | 9-Bit x 4-Port Multiple Bus Exchange w/Parity    |

| Am29C60A  | 16-Bit Cascadable EDC, High Speed                |

| Am29C676  | 11-Bit Driver for 4M x 1 and 4M x 4 DRAMs        |

| Am2965/6  | 8-Bit DRAM Driver (Inverting, Non-inverting)     |

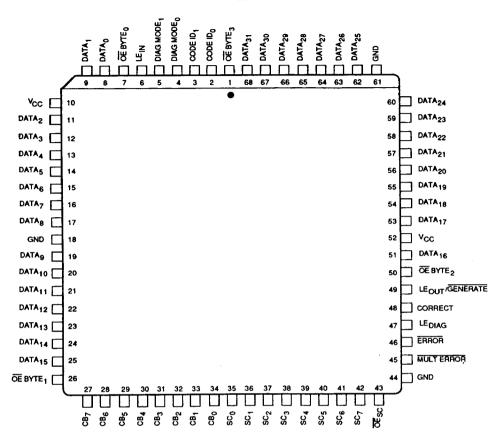

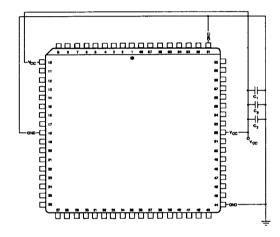

# CONNECTION DIAGRAMS Top View

Note: Pin 1 is marked for orientation (PLCC only).

10565-002A

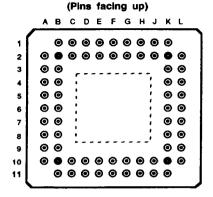

# **CONNECTION DIAGRAMS (Continued) Bottom View**

**PGA**

10565-003A

# PGA PIN DESIGNATIONS (Sorted by Pin No.)

| PIN<br>NO.  | PIN NAME               | PIN<br>NO. | PIN NAME           | PIN<br>NO. | PIN NAME                        | PIN<br>NO.          | PIN NAME        |  |

|-------------|------------------------|------------|--------------------|------------|---------------------------------|---------------------|-----------------|--|

| A-2         | DATA <sub>1</sub>      | B-9        | DATA <sub>26</sub> | F-10       | Vcc                             | K-4                 | CB <sub>3</sub> |  |

| A-3         | DATA <sub>0</sub>      | B-10       | GND                | F-11       | DATA <sub>17</sub>              | K-5                 | CB <sub>1</sub> |  |

| A-4         | LEIN                   | B-11       | DATA <sub>24</sub> | G-1        | DATA <sub>11</sub>              | K-6                 | SC <sub>0</sub> |  |

| A-5         | DIAG MODE <sub>0</sub> | C-1        | DATA <sub>4</sub>  | G-2        | DATA <sub>10</sub>              | K-7                 | SC <sub>2</sub> |  |

| A-6         | CODE IDo               | C-2        | DATA <sub>3</sub>  | G-10       | OE BYTE2                        | K-8                 | SC <sub>4</sub> |  |

| A-7         | DATA <sub>31</sub>     | C-10       | DATA <sub>22</sub> | G-11       | DATA <sub>16</sub>              | K-9                 | SC <sub>6</sub> |  |

| A-8         | DATA <sub>29</sub>     | C-11       | DATA <sub>23</sub> | H-1        | DATA <sub>13</sub>              | K-10                | GND             |  |

| A-9         | DATA <sub>27</sub>     | D-1        | DATA <sub>6</sub>  | H-2        | DATA <sub>12</sub>              | K-11                | MULT ERROR      |  |

| A-10        | DATA <sub>25</sub>     | D-2        | DATA <sub>5</sub>  | H-10       | CORRECT                         | L-2 CB <sub>6</sub> |                 |  |

| B-1         | DATA <sub>2</sub>      | D-10       | DATA <sub>20</sub> | H-11       | LE <sub>OUT</sub> /<br>GENERATE | L-3                 | CB <sub>4</sub> |  |

| B-2         | Vcc                    | D-11       | DATA <sub>21</sub> | J-1        | DATA <sub>15</sub>              | L-4                 | CB <sub>2</sub> |  |

| B-3         | OE BYTEO               | E-1        | DATA <sub>8</sub>  | J-2        | DATA <sub>14</sub>              | L-5                 | CB <sub>0</sub> |  |

| B-4         | DIAG MODE1             | E-2        | DATA <sub>7</sub>  | J-10       | ERROR                           | L-6                 | SC <sub>1</sub> |  |

| <b>B</b> -5 | CODE ID1               | E-10       | DATA <sub>18</sub> | J-11       | LEDIAG                          | L-7                 | SC <sub>3</sub> |  |

| B-6         | OE BYTE3               | E-11       | DATA <sub>19</sub> | K-1        | ŌĒ BYTE₁                        | L-8                 | SC <sub>5</sub> |  |

| B-7         | DATA <sub>30</sub>     | F-1        | DATAg              | K-2        | CB <sub>7</sub>                 | L-9                 | SC <sub>7</sub> |  |

| B-8         | DATA <sub>28</sub>     | F-2        | GND                | K-3        | CB <sub>5</sub> L-10            |                     | ŌĒSC            |  |

### (Sorted by Pin Name)

| PIN<br>NO. | PIN NAME             | PIN<br>NO. | PIN NAME           | PIN<br>NO. | PIN NAME               | PIN<br>NO.          | PIN NAME                        |  |

|------------|----------------------|------------|--------------------|------------|------------------------|---------------------|---------------------------------|--|

| L-5        | CB <sub>0</sub>      | D-1        | DATA <sub>6</sub>  | C-11       | DATA <sub>23</sub>     | H-11                | LE <sub>OUT</sub> /<br>GENERATE |  |

| K-5        | CB <sub>1</sub>      | E-2        | DATA <sub>7</sub>  | B-11       | DATA <sub>24</sub>     | K-11                | MULT ERROR                      |  |

| L-4        | CB <sub>2</sub>      | E-1        | DATA <sub>8</sub>  | A-10       | DATA <sub>25</sub>     | B-3                 | OE BYTE0                        |  |

| K-4        | CB <sub>3</sub>      | F-1        | DATA <sub>9</sub>  | B-9        | DATA <sub>26</sub>     | K-1                 | OE BYTE <sub>1</sub>            |  |

| L-3        | CB <sub>4</sub>      | G-2        | DATA <sub>10</sub> | A-9        | DATA <sub>27</sub>     | G-10                | OE BYTE2                        |  |

| К-3        | CB <sub>5</sub>      | G-1        | DATA <sub>11</sub> | B-8        | DATA <sub>28</sub>     | B-6                 | OE BYTE3                        |  |

| L-2        | CB <sub>6</sub>      | H-2        | DATA <sub>12</sub> | A-8        | DATA <sub>29</sub>     | L-10                | ŌĒSC                            |  |

| K-2        | CB <sub>7</sub>      | H-1        | DATA <sub>13</sub> | B-7        | DATA <sub>30</sub>     | K-6                 | SC <sub>0</sub>                 |  |

| A-6        | CODE ID <sub>0</sub> | J-2        | DATA <sub>14</sub> | A-7        | DATA <sub>31</sub>     | L-6                 | SC <sub>1</sub>                 |  |

| B-5        | CODE ID <sub>1</sub> | J-1        | DATA <sub>15</sub> | A-5        | DIAG MODE <sub>0</sub> | K-7                 | SC <sub>2</sub>                 |  |

| H-10       | CORRECT              | G-11       | DATA <sub>16</sub> | B-4        | DIAG MODE <sub>1</sub> | L-7                 | SC <sub>3</sub>                 |  |

| A-3        | DATA <sub>0</sub>    | F-11       | DATA <sub>17</sub> | J-10       | ERROR                  | K-8                 | SC <sub>4</sub>                 |  |

| A-2        | DATA <sub>1</sub>    | E-10       | DATA <sub>18</sub> | B-10       | GND                    | L-8                 | SC <sub>5</sub>                 |  |

| <b>B-1</b> | DATA <sub>2</sub>    | E-11       | DATA <sub>19</sub> | F-2        | GND                    | K-9                 | SC <sub>6</sub>                 |  |

| C-2        | DATA <sub>3</sub>    | D-10       | DATA <sub>20</sub> | K-10       | GND                    | L-9                 | SC <sub>7</sub>                 |  |

| C-1        | DATA <sub>4</sub>    | D-11       | DATA <sub>21</sub> | J-11       | LEDIAG                 | B-2 V <sub>CC</sub> |                                 |  |

| D-2        | DATA <sub>5</sub>    | C-10       | DATA <sub>22</sub> | A-4        | LEIN                   | F-10                | Vcc                             |  |

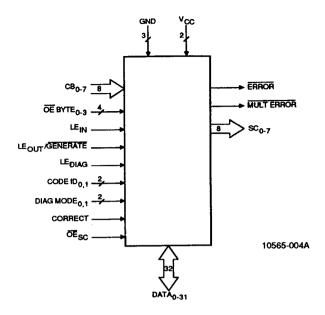

# **LOGIC SYMBOL**

Die Size: 0.174" x 0.176" Gate Count: 1670

## Package Information

| Parameter     | PGA | PLCC | Unit |

|---------------|-----|------|------|

| $\theta_{JA}$ | 34  | 35   | °C/W |

| θic           | _   | N/A  | °C/W |

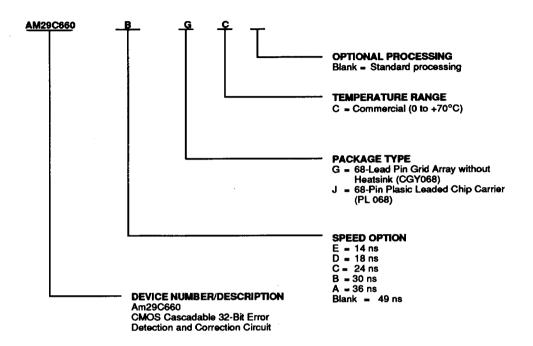

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the following elements:

Device Number

Speed Option (if applicable)

Speed Option (if applica Package Type Temperature Range Optional Processing

| Valid Combinations |        |  |  |  |  |  |  |  |

|--------------------|--------|--|--|--|--|--|--|--|

| AM29C660           |        |  |  |  |  |  |  |  |

| AM29C660A          |        |  |  |  |  |  |  |  |

| AM29C660B          | GC, JC |  |  |  |  |  |  |  |

| AM29C660C          | 40,00  |  |  |  |  |  |  |  |

| AM29C660D          |        |  |  |  |  |  |  |  |

| AM29C660E          |        |  |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

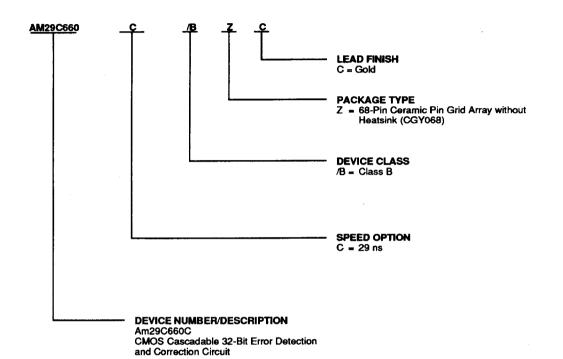

# MILITARY ORDERING INFORMATION APL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of the following elements:

Device Number

Speed Option (if applicable)

Device Class

Package Type

Lead Finish

| Valid Combinations |      |  |  |  |  |  |  |  |

|--------------------|------|--|--|--|--|--|--|--|

| AM29C660C          | /BZC |  |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

#### CB<sub>0-7</sub> Check Bits (Inputs)

These eight check bit lines are used to input bits for error detection. They are also used to input syndrome bits for error correction in the 64-bit configuration.

# CODE ID<sub>0, 1</sub> Code Identification (Inputs)

These two code identification inputs identify the size of the total data word to be processed. The two allowable data word sizes are 32 and 64 bits and their respective modified Hamming Codes are designated 32/39 and 64/72. The CODE ID inputs are also used to instruct the EDC that the CODE IDo, 1, DIAG MODEo, 1, and CORRECT signals are to be taken from the Diagnostic Latch, rather than from the input control lines (Reference Table 1).

### CORRECT Correct (Input; Active HIGH)

This signal allows the correction network to correct any single-bit error in the Data Input Latch before putting it into the Data Output Latch by complementing the bit-in-error. When the signal is LOW, the EDC routes data directly from the Data Input Latch to the Data Output Latch without correction.

# DATA<sub>0-31</sub> Data (Inputs/Outputs; Three-State)

These bidirectional data lines provide input to the Data Input Latch and Diagnostic Latch, and receive output from the Data Output Latch. DATA<sub>0</sub> is the least significant bit and DATA<sub>31</sub> is the most significant bit.

#### DIAG MODE<sub>0, 1</sub> Diagnostic Mode Select (Inputs; Active HIGH)

These two lines control the initialization and diagnostic operation of the EDC circuit (Reference Table 2).

# ERROR Error Detection Flag (Output; Active LOW)

When the EDC is in the Detect or Detect/Correct Mode, this output goes LOW if one or more syndrome bits are nonzero, indicating one or more data and/or check bits are in error. If all syndrome bits are zero, there are no errors detected and the output will be HIGH. In the Generate Mode, ERROR is forced HIGH.

#### GND (3) 0-V Power Supply

These pins are the 0-V power supply to the EDC circuit. All grounds must be connected during device operation.

# LE<sub>DIAG</sub> Diagnostic Latch Enable (Input)

This is the latch enable for the Diagnostic Latch. When HIGH, the Diagnostic Latch follows the 32-bit data on

the input lines. When LOW, the outputs of the Diagnostic Latch are latched to their previous states. The Diagnostic Latch holds diagnostic check bits and internal control signals for CODE ID0, 1, DIAG MODE0, 1, and CORRECT.

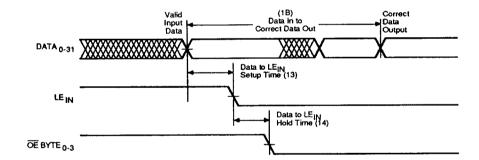

# LE<sub>IN</sub> Latch Enable Data Input Latch (Input)

This input controls latching of the input data. When HIGH, the Data Input Latch and Check Bit Input Latch follow the input data and input check bits, respectively. When LOW, the Data Input Latch and Check Bit Input Latch are latched to their previous states.

# LE<sub>OUT</sub>/GENERATE Latch Enable – Data Output Latch (input)/Generate Check Bits (input; Active LOW)

This is a multifunction pin. When it is LOW, it operates in the Check Bit Generate Mode. In this mode, the device generates the check bits or partial check bits specific to the data in the Data Input Latch. The generated check bits are placed on the syndrome/check bit outputs. The Data Output Latch is latched to its previous state when this pin is LOW.

When HIGH, the device is in the Detect or Detect/Correct Mode. In the Detect Mode, the device detects single and multiple errors, and generates syndrome bits specific to the data in the Data Input Latch and Check Bit Input Latch. In the Detect/Correct Mode, single-bit errors are automatically corrected, with the corrected data placed at the inputs of the Data Output Latch. The syndrome result is placed on the syndrome/check bit outputs and indicates, in a coded form, the number of errors and the specific bit in error. When HIGH, the Data Output Latch follows the output of the Data Input Latch as modified by the correction logic network.

In the Detect/Correct Mode, single-bit errors are corrected by the network before being loaded into the Data Output Latch. In the Detect Mode, the contents of the Data Input Latch are passed through the correction network unchanged into the Data Output Latch. The Data Output Latch is disabled with its contents unchanged if the EDC is in the Generate Mode.

# **MULT ERROR**

#### Multiple Error Detection Flag (Output; Active LOW)

When LOW in the Detect or Detect/Correct Mode, this output indicates that two or more bit errors have been detected. If HIGH, either one or no errors have been detected. In the Generate Mode, MULT ERROR is forced HIGH.

## OE BYTE₀-₃ Output Enable Bytes 0–3 (Inputs; Active LOW)

These lines control the three-state output buffers for each of the four bytes of the Data Output Latch. When LOW, they enable the output buffer of the Data Output

Latch. When HIGH, they force the Data Output Latch buffer into the high impedance state. Any number of bytes of the Data Output Latch is easily activated by separately selecting any of the four enable lines.

OEsc Output Enable, Syndrome/Check Bits (Input; Active LOW)

When in the LOW state, the three-state output lines SC<sub>0-7</sub> are enabled. When this input is HIGH, the syndrome/check bit outputs are in the high-impedance state.

SC₀, 7 Syndrome/Check Bits (Outputs; Three-State)

These eight three-state outputs contain the check/partial check bits when the EDC is in the Generate Mode.

They also contain the syndrome/partial-syndrome bits when the device is in the Detect or Detect/Correct Modes.

$V_{CC}$  (2) + 5-V Positive Power Supply Voltage

These pins are the positive + 5-V power supply to the EDC Circuit. All Vcc pins must be connected during device operation.

# FUNCTIONAL DESCRIPTION EDC Architecture

The Am29C660 EDC Circuit is a powerful 32-bit cascadable slice used for check bit generation, error detection, error correction, and diagnostics.

As shown in the block diagram, the device consists of the following:

- Data Input Latch

- · Check Bit Input Latch

- Check Bit Generation Logic

- Syndrome Generation Logic

- Error Detection Logic

- Error Correction Logic

- Data Output Latch and Output Buffers

- Diagnostics Latch

- Control Logic

## **Data Input Latch**

The Latch Enable Input, LEin, controls the loading of 32 bits of data into the Data Input Latch. Depending upon the control mode, the input data is either used for check bit generation or error detection/correction.

#### Check Bit Input Latch

Eight check bits are loaded under the control of LE<sub>IN</sub> Check bits are used in the Error Detection and Error Detection/ Correction Modes.

# **Check Bit Generation Logic**

This block generates the appropriate check bits for the 32 bits of data in the Data Input Latch. The check bits are generated according to a modified Hamming Code.

#### Syndrome Generation Logic

In both the Error Detection and Error Detection/Correction Modes, this logic block compares the check bits read from the memory against a newly generated set of check bits produced for the data read in from the memory. If both sets of check bits match, then there are no errors. If there is a mismatch, then one or more of the data and/or check bits is in error.

The syndrome bits are produced by an Exclusive-OR of the two sets of check bits. If the two sets of check bits are identical (meaning there are no errors), the syndrome bits will be all zeros. If there is a single-bit error, the syndrome bits can be decoded to determine the bit-in-error.

This logic block decodes the syndrome bits generated by the Syndrome Generation Logic. If there are no errors in either the input data or check bits, the ERROR and MULTERROR outputs remain HIGH. If one or more errors are detected, ERROR goes LOW. If two or more errors are detected, both ERROR and MULTERROR go LOW.

## **Error Correction Logic**

For single-bit errors, the Error Correction Logic corrects (by complementing) the single data bit in error. This corrected data is loaded into the Data Output Latch, which can then be read onto the bidirectional data lines. If the single-bit error is one of the check bits, the correction logic does not place corrected check bits on the syndrome/check bit outputs. If the corrected check bits are needed, the EDC must be switched to the Generate Mode

#### **Data Output Latch and Output Buffers**

The Data Output Latch is used for storing the result of an error correction operation. The latch is loaded from the correction logic under control of the Data Output Latch Enable, LEour/GENERATE. The Data Output Latch may also be directly loaded from the Data Input Latch while in the Pass-Thru Mode.

Four data bytes in the Data Output Latch may be end independently (by  $\overline{OE}$  BYTE<sub>0-3</sub>) for reading onto the bidirectional data bus. This feature facilitates byte operations.

#### Diagnostics Latch

This is a 32-bit latch loadable from the bidirectional data lines under the control of the Diagnostic Latch Enable, LEDIAG The Diagnostic Latch contains check bit information in one byte and control information in the other bytes. The Diagnostic Latch is used for driving the device when in the Internal Control Mode, or for supplying check bits when in one of the Diagnostic Modes.

#### **Control Logic**

The Control Logic specifies the mode in which the EDC is operating. Normally, the control logic is driven by the external control inputs. However, in the Internal Control Mode, the control signals are taken from the Diagnostic Latch. Since LEour and GENERATE are controlled by the same pin, the latching action (LEour from HIGH to LOW) of the Data Output Latch causes the EDC to go into the Generate Mode.

# **Detailed Operational Description**

The Am29C660 contains the logic necessary to generate check bits on a 32-bit data field according to a modified Hamming Code. Operating on data read from memory, the EDC will correct any single-bit error, and will detect all double and some triple-bit errors. The Am29C660 may be configured to operate on 32-bit data words (with 7 check bits) and 64-bit data words (with 8 check bits). In either configuration, the device makes the error syndrome bits available on separate outputs for error logging.

## Code and Byte Specification

The EDC Circuit may be configured in several different ways, and operates differently in each configuration. It is necessary to indicate to the device what size data word is involved and which bytes of the data word it is proc-

essing. This is done with the input lines CODE IDo. 1 as shown in Table 1. The two modified Hamming codes referred to in Table 1 are:

- 1, 32/39 Code: 32 data bits, 7 check bits (39 bits in total)

- 2, 64/72 Code: 64 data bits, 8 check bits (72 bits in total)

#### Control Mode Selection

There are nine operating modes of the Am29C660. Eight of these modes are selected as shown in Tables 2 and 3. Table 2 is the Diagnostic Mode Control Decode Table, and Table 3 is the Mode Control Decode Table. The Diagnostic Mode pins, DIAG MODEo, 1, define the five basic areas of operation. GENERATE and COR-RECT further divide the operations into eight functions. The ninth mode is the Internal Control Mode which is selected by the CODE ID inputs as shown in Table 1.

Table 1. CODE ID Decode

| CODE<br>ID <sub>1</sub> | CODE<br>ID <sub>0</sub> | Hamming Code and<br>Slice Selected     |

|-------------------------|-------------------------|----------------------------------------|

| 0                       | 0                       | Code 32/39, 32-Bit Data Word           |

| 0                       | 1                       | Internal Control Mode                  |

| 1                       | ٥                       | Code 64/72, Lower 32-Bit Slice (0-31)  |

| 1                       | 1                       | Code 64/72, Upper 32-Bit Slice (32-63) |

**Table 2. Diagnostic Mode Control Decode**

| DIAG MODE | DIAG MODE | CORRECT | Diagnostic Mode Selected                                  |

|-----------|-----------|---------|-----------------------------------------------------------|

| . 0       | 0         | Х       | Normal EDC Function Mode or Non-Diagnostic Mode           |

| 0         | 1         | х       | Diagnostic Generate Mode                                  |

| 1         | 0         | X       | Diagnostic Detect Mode and Diagnostic Detect/Correct Mode |

| 1         | 1         | 1       | Initialize Mode                                           |

| 1         | 1         | 0       | Pass-Thru Mode                                            |

Table 3. Mode Control Decode

| Operating                        | DIAG N | ODE    |                                                |         | Contents of                                           | SCo-7 and                                         | ERROR and  |

|----------------------------------|--------|--------|------------------------------------------------|---------|-------------------------------------------------------|---------------------------------------------------|------------|

| Mode                             | 1      | 0      | LEOUT/GENERATE                                 | CORRECT | Data Output Latch                                     | OEsc = LOW                                        | MULT ERROR |

| Generate                         | 0      | 0      | 0                                              | ×       | •                                                     | Check bits<br>generated from<br>Data Input Latch  | High       |

| Detect                           | 0      | 0<br>1 | 1                                              | 0       | Data Input Latch                                      | Generated from<br>Data Input/Check<br>Bit Latches | Valid      |

| Detect/<br>Correct               | 0      | 0<br>1 | 1                                              | 1       | Data Input Latch<br>with single bit<br>error detected | Generated from<br>Data Input/Check<br>Bit Latches | Valid      |

| Pass-Thru                        | 1      | 1      | 1 or ↓                                         | 0       | Data Input Latch                                      | Check Bit Latch                                   | HIGH       |

| Diagnostic<br>Generate           | 0      | 1      | 0                                              | Х       | -                                                     | Check bits from<br>Diagnostic Latch               | _          |

| Diagnostic<br>Detect             | 1      | 0      | 1                                              | 0       | Data Input Latch                                      | Data Input<br>check bits from<br>Diagnostic Latch | Valid      |

| Diagnostic<br>Detect/<br>Correct | 1      | 0      | 1                                              | 1       | Data Input Latch<br>with single-bit<br>error detected | Data Input<br>check bits from<br>Diagnostic Latch | Valid      |

| Initialize                       | 1      | 1      | 1 or ↓                                         | 1       | Data Input Latch<br>set to all "0"s                   | Check bits<br>generated from<br>Data Input Latch  | _          |

| internal<br>Control              |        |        | = 10 Control Signals C<br>T are taken from the |         | ·                                                     |                                                   |            |

<sup>\*</sup> In the Generate Mode, data is read into the EDC circuit and the check bits are generated. The same data is written to the memory along with the check bits. Since the Data Output Latch is not used in the Generate Mode, LEOUT, being LOW (since it is tied to Generate) does not affect the writing of check bits.

The Generate Mode is used to display the check bits on the  $SC_{0-7}$  outputs. The Error Detect Mode provides an indication of an error or multiple errors on the ERROR and MULTERROR outputs. Single-bit errors are not corrected in this mode. The syndrome bits are provided on the  $SC_{0-7}$  outputs. In the Diagnostic Detect Mode, the syndrome bits are generated by comparing the internally generated check bits from the Data Input Latch with check bits stored in the Diagnostic Latch (as opposed to those in the Check Bit Latch).

The Detect/Correct Mode is similar to the Detect Mode except that single-bit errors will be corrected (by complementing) and made available as input to the Data Output Latch. In the Diagnostic Detect/Correct Mode, single-bit errors will be corrected as determined by the syndrome bits, which are in turn generated from the check bits corresponding to the data in the Data Input Latch and the check bits in the Diagnostic Latch.

In the Initialize Mode check bits are generated for all zero data bits. The Data Input Latch is held to a logic zero and is made available as input to the Data Output Latch.

In the Internal Control Mode, the control signals CODE IDo, 1 DIAG MODEo, 1, and CORRECT are taken from the Diagnostic Latch and their respective control inputs are disregarded.

#### Check and Syndrome Bits

The Am29C660 provides either check or syndrome bits on the three-state outputs SC<sub>0-7</sub>. Check bits are generated from the Data Input Bits. Syndrome bits are an Exclusive-OR of the check bits generated from the data read from the memory and the check bits read from the memory with the stored data.

Syndrome bits can be decoded to determine the single bit-in-error or to indicate a double- or triple-bit error.

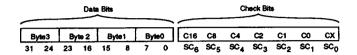

The check bits generated by the Am29C660 are designated as follows:

- 32-bit configuration: CX, C0, C1, C2, C4, C8, C16

- 64-bit configuration: CX, C0, C1, C2, C4, C8, C16, C32

- Pin Name: SC<sub>0</sub>, SC<sub>1</sub>, SC<sub>2</sub>, SC<sub>3</sub>, SC<sub>4</sub>, SC<sub>5</sub>, SC<sub>6</sub>, SC<sub>7</sub>.

The syndrome bits generated by the Am29C660 are designated as follows:

•32-bit configuration: SX, S0, S1, S2, S4, S8, S16

•64-bit configuration: SX, S0, S1, S2, S4, S8, S16, S32

•Pin Name: SC<sub>0</sub>, SC<sub>1</sub>, SC<sub>2</sub>, SC<sub>3</sub>, SC<sub>4</sub>, SC<sub>5</sub>, SC<sub>6</sub>, SC<sub>7</sub>.

#### 32-Bit Word Configuration

#### **Data Field Format**

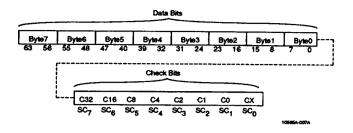

The 32-bit format consists of 32 data bits and 7 check bits and is referred to as the 32/39 code. The format is shown in Figure 1.

10565-005A

Figure 1. 32-Bit Data Word Format

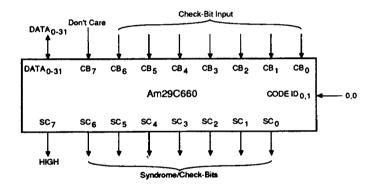

# **Chip Configuration**

A single Am29C660 EDC Circuit connected as shown in Figure 2 is all that is necessary to perform single-bit error correction and double-bit error detection on a 32-bit

data field. In this configuration, only seven check bits are required. Therefore, CB<sub>7</sub> is a "don't care" and CODE ID<sub>0.1</sub> = 00.

10565-006A

Figure 2. 32-Bit Configuration

## **Generate Mode**

In this mode, check bits will be generated that correspond to the contents of the Data Input Latch. The check bits generated are placed on the outputs SC<sub>0-6</sub>. SC<sub>7</sub> is a logic "1" or HIGH.

Check bits are generated according to a modified Hamming Code. Details of the code for check bit generation

are shown in Tables 4-1 and 4-2. Check bits are generated as either an XOR or XNOR of 16 of the 32 bits as indicated in the table. The XOR function results in an even parity check bit, the XNOR in an odd parity check bit.

Figure 3 shows the data flow in the Generate Mode.

Table 4-1. 32-Bit Configuration Check Bit Encoding (Data Bits 0-15)

| Generated<br>Check | Parity     | Participating Data Bits |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

|--------------------|------------|-------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| Bits               |            | 0                       | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| СХ                 | Even (XOR) | х                       |   |   |   | Х |   | Х | Х | X | × |    | Х  |    |    | х  |    |

| Co                 | Even (XOR) | Х                       | Х | Х |   | Х |   | Х |   | Х |   | X  |    | Х  |    |    |    |

| C <sub>1</sub>     | Odd (XNOR) | х                       |   |   | Х | Х |   |   | Х |   | X | Х  |    |    | Х  |    | X  |

| C <sub>2</sub>     | Odd (XNOR) | Х                       | Χ |   |   |   | X | X | Χ |   |   |    | Х  | Х  | Х  |    |    |

| C <sub>4</sub>     | Even (XOR) |                         |   | X | Х | х | Х | X | Х |   |   |    |    |    |    | Χ  | Х  |

| C <sub>8</sub>     | Even (XOR) |                         |   |   |   |   |   |   |   | Х | X | Х  | Х  | х  | Х  | Х  | Х  |

| C <sub>16</sub>    | Even (XOR) | X                       | Х | Х | Х | x | Х | Х | Х |   |   |    |    |    |    |    |    |

Table 4-2. 32-Bit Configuration Check Bit Encoding (Data Bits 16–31)

| Generated<br>Check |            | Participating Data Bits |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|--------------------|------------|-------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Bits               | Parity     | 16                      | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| СХ                 | Even (XOR) |                         | Х  | Х  | X  |    | Х  |    |    |    |    | Х  |    | х  | Х  |    | Х  |

| Co                 | Even (XOR) | X                       | Х  | Х  |    | Х  |    | Х  |    | х  |    | Х  |    | х  |    |    |    |

| C <sub>1</sub>     | Odd (XNOR) | X                       |    |    | Х  | X  |    |    | Х  |    | Х  | X  |    |    | Х  |    | Х  |

| C <sub>2</sub>     | Odd (XNOR) | х                       | Х  |    |    |    | Х  | Х  | Х  |    |    |    | Х  | x  | Х  |    |    |

| C4                 | Even (XOR) |                         |    | Х  | Х  | х  | Х  | Х  | Х  |    |    |    |    |    |    | Х  | Х  |

| Св                 | Even (XOR) |                         |    |    |    |    |    |    |    | X  | X  | X  | Х  | Х  | X  | Х  | Х  |

| C <sub>16</sub>    | Even (XOR) |                         |    |    |    |    |    |    |    | Х  | X  | X  | Х  | Х  | Х  | Х  | X  |

The check bit is generated as either an XOR or XNOR of the sixteen data bits noted by an "X" in the table.

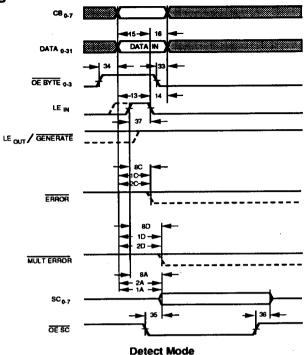

#### **Detect Mode**

In this mode the device will compare the check bits generated from the contents of the Data Input Latch with the contents of the Check Bit Latch, and will detect all single- and double-bit errors and some triple-bit errors. If one or more errors are detected, ERROR goes LOW. If two or more errors are detected, MULTERROR and ERROR go LOW. Both error indicators are HIGH if there is no error.

The syndrome bits which are generated during error detection are available on the outputs SC<sub>0-6</sub>. SC<sub>7</sub> remains HIGH. The syndrome bits may be decoded to determine if a bit error was detected and for a single-bit error, which of the data or check bits is in error. Table 5 shows the syndrome bit decoding for the 32-bit data word configuration. If no error is detected, the syndrome bits will all be zeros (except SC<sub>7</sub> which is tied to a logical "1").

**Table 5. Syndrome Bit Decoding Matrix**

| S  | Syndrome<br>Bits |    |    |  |    | S16<br>S8<br>S4 | 0 0 0 | 1<br>0<br>0 | 0<br>1<br>0 | 1<br>1<br>0 | 0<br>0<br>1 | 1<br>0<br>1 | 0<br>1<br>1 | 1<br>1<br>1 |

|----|------------------|----|----|--|----|-----------------|-------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| SX | <b>\$0</b>       | S1 | S2 |  |    |                 |       |             |             |             |             |             |             |             |

| 0  | 0                | 0  | 0  |  | *  | C16             | œ     | Ŧ           | C4          | Т           | Т           | 30          |             |             |

| 0  | 0                | 0  | 1  |  | C2 | Т               | ۲     | 27          | Т           | 5           | M           | T           |             |             |

| 0  | 0                | .1 | 0  |  | C1 | _               | Т     | 25          | ۲           | თ           | 15          | Т           |             |             |

| 0  | 0                | 1  | 1  |  | T  | M               | 13    | Т           | 23          | ۲           | Т           | Σ           |             |             |

| 0  | 1                | 0  | 0  |  | C0 | Т               | T     | 24          | ۲           | ٩           | Σ           | ۲           |             |             |

| 0  | 1                | 0  | 1  |  | T  | 1               | 12    | 1           | 22          | ۲           | ۲           | Μ           |             |             |

| 0  | 1                | 1  | 0  |  | T  | 7               | 10    | _           | 20          | ۲           | Т           | Μ           |             |             |

| 0  | 1                | 1  | 1  |  | 16 | 1               | Ŧ     | М           | T           | Σ           | M           | ۲           |             |             |

| 1  | 0                | 0  | 0  |  | СХ | _               | T     | X           | T           | Σ           | 14          | т           |             |             |

| 1  | 0                | 0  | 1  |  | T  | ×               | 11    | T           | 21          | Т           | T           | 4           |             |             |

| 1  | 0                | 1  | 0  |  | T  | М               | 9     | Т           | 19          | ۲           | ۲           | 31          |             |             |

| 1  | 0                | 1  | 1  |  | М  | Т               | T     | 29          | Т           | 7           | Δ           | ۲           |             |             |

| 1  | 1                | 0  | 0  |  | T  | М               | 8     | Т           | 18          | Т           | Т           | М           |             |             |

| 1  | 1                | 0  | 1  |  | 17 | Т               | T     | 28          | Т           | 6           | М           | Т           |             |             |

| 1  | 1                | 1  | 0  |  | М  | Т               | Т     | 26          | T           | 4           | М           | T           |             |             |

| 1  | 1                | 1  | 1  |  | Т  | 0               | М     | Т           | м           | Т           | T           | М           |             |             |

<sup>\* =</sup> No errors detected

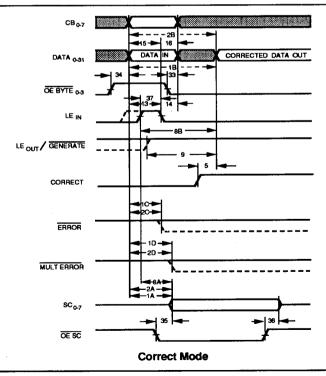

#### **Detect/Correct Mode**

In this mode, the EDC functions the same way as in the Detect Mode except that the correction network is enabled to correct, by complementing, any single-bit error in the Data Input Latch before placing the data on the inputs of the Data Output Latch. If a multiple error is detected, the output of the correction network is undefined. If a single-bit error occurs to a check bit, there is no automatic correction. If a check bit correction is desired, it can be done by placing the device in the Generate Mode to produce the correct check bit sequence for the data in the Data Input Latch.

#### Pass-Thru Mode

In this mode, the unmodified contents of the Data Input Latch are placed on the inputs of the Data Output Latch, and the contents of the Check bit Latch are placed on the output SC<sub>0-6</sub> (SC<sub>7</sub> is a logical "1"). ERROR and MULT ERROR are forced HIGH in this mode (inactive).

#### **Diagnostic Generate Mode**

This is one of the three special Diagnostic Modes selected by the control inputs DIAG MODE<sub>0, 1</sub>. This mode is similar to the normal Generate Mode except that the check bits are not generated from the contents of the Data Input Latch. They are instead taken directly from the contents of the Diagnostic Latch. Table 6 shows the Diagnostic Latch coding format. Figures 5 and 6 illustrate the flow of data during the two diagnostic modes.

# Diagnostic Detect, Diagnostic Detect/ Correct Modes

These two special Diagnostic Modes are also selected by the control inputs DIAG MODE<sub>0, 1</sub>. These modes are similar to the normal Detect and Detect/Correct Modes except that the check bits are taken from the Diagnostic Latch, rather than from the Check Bit Input Latch.

#### Initialize Mode

In this mode the inputs of the Data Output Latch are forced to all zeros. The syndrome bit outputs SCo-6 are generated to correspond to the all-zero data on the Data Output Latch. SC7 is tied high. The ERROR and MULT ERROR outputs are forced HIGH in this mode. The Initialize Mode is useful after power-up when RAM contents are random. The EDC may be placed in this mode and its outputs written into all memory addresses under processor control.

#### Internal Control Mode

This mode is selected by the external control inputs CODE ID<sub>0-1</sub>. When in the Internal Control Mode, the Am29C660 takes the CODE ID<sub>0-1</sub>, DIAG MODE<sub>0-1</sub>, and CORRECT control signals from the Diagnostic Latch rather than from the external input lines.

Table 6. 32-Bit Diagnostic Latch Coding Format

| Data Bit | Internal Function       |

|----------|-------------------------|

| 0        | Diagnostic Check Bit X  |

| 1        | Diagnostic Check Bit 0  |

| 2        | Diagnostic Check Bit 1  |

| 3        | Diagnostic Check Bit 2  |

| 4        | Diagnostic Check Bit 4  |

| 5        | Diagnostic Check Bit 8  |

| 6        | Diagnostic Check Bit 16 |

| 7        | Don't Care              |

| 8        | COD€ ID <sub>0</sub>    |

| 9        | CODE ID1                |

| 10       | DIAG MODEO              |

| 11       | DIAG MODE <sub>1</sub>  |

| 12       | CORRECT                 |

| 13-31    | Don't Care              |

Number = The bit number of the single bit-in-error

T = Two errors detected

M = More than two errors detected

Figure 3. Check Bit Generation Data Path

Figure 4. Error Detection and Correction Data Path

Figure 5. Diagnostic Check Bit Generation Data Path

Figure 6. Diagnostic Detect and Correct Data Path

# 64-Bit Data Word Configuration

#### **Data Field Format**

The 64-bit format consists of 64 data bits and 8 check bits and is referred to as the 64/72 code. The format is shown in Figure 7.

Figure 7. 64-Blt Data Word Format

#### **Chip Configuration**

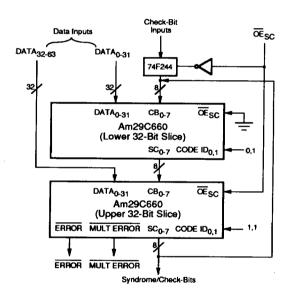

Two Am29C660 EDC Circuits connected as shown in Figure 8, provide all the necessary logic for all single-bit error detection correction, all double-bit error detection.

and some triple-bit error detection on a 64-bit data field. In this configuration, eight check bits are required. CODE IDo, 1 control signal inputs distinguish the upper 32 bits from the lower 32 bits as shown in Table 1.

10565-008A

Figure 8. 64-Bit Configuration

The valid syndrome bits and the ERROR and MULT ERROR output signals are taken from the upper EDC slice. The lower EDC slice has its OEsc input tied to ground (logic "0") and its SCo-routputs connected to the respective CBo-r inputs of the upper EDC slice. The 32 most significant data bits, DATA32-63, are connected to the data lines of the upper EDC slice. All the latch enables and control signals must be input to both the upper and the lower EDC slices.

In the Detect/Correct Mode, the valid syndrome bits from the upper EDC slice must be read into the lower EDC slice via the check bit inputs of the lower EDC slice. They are selected by an internal MUX as inputs to the bit-in-error decoder (see Block Diagram). External buffering and output enabling of the check bit lines is required as shown in Figure 8. The OEsc signal to the upper EDC slice can be used to control the enabling of the check bits to the lower EDC slice. The external check bits to the lower EDC slice are disabled.

#### **Generate Mode**

In this mode, check bits will be generated that correspond to the contents of the Data Input Latch. The generated check bits are placed on the  $SC_{0-7}$  outputs of the upper EDC slice.

Check bits are generated according to a modified Hamming Code. Details of the code for check bit generation are shown in Tables 7-1 through 7-4. Check bits are generated as either an XOR or XNOR of 32 of the 64 bits. The XOR function results in an even parity check bit, the XNOR in an odd parity check bit.

Table 7-1. 64-Bit Configuration Check Bit Encoding (Data Bits 0-15)

| Generated       |            |   |   |   |   | ı | Par | tici | pat | ing | Da | ata | Bits | S  |    |    |    |

|-----------------|------------|---|---|---|---|---|-----|------|-----|-----|----|-----|------|----|----|----|----|

| Check<br>Bits   | Parity     | 0 | 1 | 2 | 3 | 4 | 5   | 6    | 7   | 8   | 9  | 10  | 11   | 12 | 13 | 14 | 15 |

| СХ              | Even (XOR) |   | х | х | Х |   | Х   |      |     | Х   | X  |     | Х    |    |    | Χ  |    |

| Co              | Even (XOR) | X | X | X |   | Х |     | X    |     | X   |    | Х   |      | X  |    |    |    |

| C <sub>1</sub>  | Odd (XNOR) | × |   |   | Х | Х |     |      | Х   |     | Х  | Х   |      |    | Х  |    | Χ  |

| C <sub>2</sub>  | Odd (XNOR) | X | Х |   |   |   | X   | Х    | Х   |     |    |     | X    | X  | Х  |    |    |

| C4              | Even (XOR) | T |   | Х | Х | Х | Х   | Х    | Х   |     |    |     |      |    |    | Χ  | Х  |

| C <sub>8</sub>  | Even (XOR) |   |   |   |   | Г |     |      |     | Х   | Х  | Х   | Х    | X  | Х  | Χ  | X  |

| C <sub>16</sub> | Even (XOR) | х | Х | Х | Х | X | Х   | Х    | Х   |     |    |     |      |    |    |    |    |

| C <sub>32</sub> | Even (XOR) | x | Х | Х | Х | X | Х   | Х    | Х   |     |    |     |      |    |    |    |    |

Table 7-2. 64-Bit Configuration Check Bit Encoding (Data Bits 16-31)

| Generated       |            | Participating Data Bits |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-----------------|------------|-------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Check<br>Bits   | Parity     | 16                      | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| СХ              | Even (XOR) | Г                       | Х  | Х  | Х  | Г  | Х  |    |    | х  | X  |    | Х  |    |    | X  |    |

| Co              | Even (XOR) | х                       | Х  | Х  |    | Х  |    | Х  |    | Х  |    | Х  |    | Х  |    |    |    |

| C <sub>1</sub>  | Odd (XNOR) | х                       |    |    | Х  | Х  |    |    | Х  |    | Х  | Х  |    |    | Х  |    | Χ  |

| C <sub>2</sub>  | Odd (XNOR) | х                       | Х  |    |    |    | Х  | X  | Х  |    |    | ٠  | X  | X  | Χ  |    |    |

| C4              | Even (XOR) |                         |    | Х  | Х  | Х  | Х  | Х  | X  |    |    |    |    |    |    | Х  | X  |

| Св              | Even (XOR) | Г                       |    |    |    |    |    |    |    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | X  |

| C <sub>16</sub> | Even (XOR) |                         |    |    |    |    |    |    |    | Х  | Х  | Х  | Х  | х  | X  | Х  | Х  |

| C <sub>32</sub> | Even (XOR) | Г                       |    |    |    | Γ  |    |    |    | х  | Х  | Х  | Х  | X  | Х  | Х  | Х  |

Table 7-3. 64-Bit Configuration Check Bit Encoding (Data Bits 32-47)

| Generated       |            | Participating Data Bits |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-----------------|------------|-------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Check<br>Bits   | Parity     | 32                      | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

| СХ              | Even (XOR) | х                       |    |    |    | x  |    | Х  | Х  | Г  |    | Х  |    | Х  | Х  |    | Х  |

| Co              | Even (XOR) | X                       | X  | Х  |    | Х  |    | Х  |    | Х  |    | Х  |    | Х  |    |    |    |

| C <sub>1</sub>  | Odd (XNOR) | X                       |    |    | Х  | Х  |    |    | Х  |    | Χ  | Χ  |    |    | X  |    | Х  |

| C <sub>2</sub>  | Odd (XNOR) | X                       | Х  |    |    |    | Х  | Х  | X  |    |    |    | X  | х  | X  |    |    |

| C <sub>4</sub>  | Even (XOR) |                         |    | Х  | Х  | х  | Х  | Х  | Х  |    |    |    |    |    |    | Х  | Х  |

| C <sub>8</sub>  | Even (XOR) |                         |    |    |    |    |    |    |    | X  | X  | Х  | Х  | X  | X  | X  | Х  |

| C <sub>16</sub> | Even (XOR) | X                       | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |    |    |    |    |    |    |    |

| C <sub>32</sub> | Even (XOR) | П                       |    |    |    | Γ  |    |    |    | Х  | X  | Х  | Х  | Х  | X  | X  | Х  |

Table 7-4, 64-Bit Configuration Check Bit Encoding (Data Bits 48-63)

| Generated<br>Check |            | Participating Data Bits |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|--------------------|------------|-------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Bits               | Parity     | 48                      | 49 | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

| СХ                 | Even (XOR) | x                       |    |    |    | x  |    | Х  | Х  | Г  |    | Х  |    | х  | Х  |    | Х  |

| Co                 | Even (XOR) | х                       | Х  | Х  |    | х  |    | Х  |    | X  |    | Х  |    | х  |    |    |    |

| C <sub>1</sub>     | Odd (XNOR) | x                       |    |    | X  | Х  |    |    | X  |    | Х  | Х  |    |    | X  |    | Х  |

| C <sub>2</sub>     | Odd (XNOR) | х                       | Х  |    |    |    | Χ  | X  | Х  |    |    |    | X  | х  | Х  |    |    |

| C4                 | Even (XOR) | Π                       |    | Х  | Х  | X  | Х  | X  | Х  |    |    |    |    |    |    | Х  | Х  |

| Св                 | Even (XOR) |                         |    |    |    |    |    |    |    | х  | Х  | X  | Х  | х  | X  | X  | Х  |

| C <sub>16</sub>    | Even (XOR) |                         |    |    |    |    |    |    |    | Х  | Х  | Х  | Х  | Х  | Х  | X  | Х  |

| C <sub>32</sub>    | Even (XOR) | X                       | Х  | Х  | X  | х  | Х  | Х  | Х  |    |    |    |    |    |    |    |    |

The check bit is generated as either an XOR or XNOR of the 32 data bits noted by an "X" in the table.

#### **Detect Mode**

In this mode, the device will compare the check bits generated from the contents of the Data Input Latch with the contents of the Check Bit Latch. All single- and double-bit errors and some triple-bit errors will be detected. If one or more errors are detected, ERROR goes LOW. If two or more errors are detected, both ERROR and MULT ERROR will go LOW. Both error indicators will be HIGH if no errors are detected. The valid ERROR and MULT ERROR signals are from the upper EDC slice.

The syndrome bits which are generated during error detection are available on the outputs SC<sub>0-7</sub> of the upper EDC slice. The syndrome bits may be decoded to determine if a bit error was detected, and for a single-bit error, which of the data or check bits is in error. Table 8 shows the syndrome bit decoding for the 64-bit data word configuration. If no error is detected, the syndrome bits will all be zeros.

In the Detect Mode, the contents of the Data Input Latch are driven directly into the inputs of the Data Output Latch without correction.

Table 8. 64-Bit Syndrome Bit Decoding Matrix

| -  | Synd |    |    | S32       | 0  | 1   | 0   | 1 | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1 | 0  | 1  | 0   | 1  |

|----|------|----|----|-----------|----|-----|-----|---|----|----|----|----|----|----|----|---|----|----|-----|----|

|    | BI   | ts |    | S16<br>S8 | 0  | 0   | 1 0 | 0 | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0 | 0  | 0  | 1 1 | 1  |

|    |      |    |    | 56<br>S4  | 0  | 0   | 0   | 0 | 0  | ò  | o  | Ó  | 1  | 1  | 1  | 1 | 1  | i  | 1   | 1  |

| SX | SO   | S1 | S2 |           |    |     |     |   |    |    |    |    |    |    |    |   |    |    |     |    |

| 0  | 0    | 0  | 0  |           | •  | C32 | C16 | Т | C8 | Т  | Т  | М  | C4 | Т  | T  | М | Т  | 46 | 62  | Т  |

| 0  | 0    | 0  | 1  |           | C2 | Т   | Т   | М | Ŧ  | 43 | 59 | Т  | T  | 53 | 37 | Т | М  | Т  | Т   | М  |

| 0  | 0    | 1  | 0  |           | C1 | Т   | T   | М | Т  | 41 | 57 | Т  | Т  | 51 | 35 | T | 15 | Т  | Т   | 31 |

| 0  | 0    | 1  | 1  |           | Т  | М   | м   | Т | 13 | T  | Т  | 29 | 23 | Т  | Т  | 7 | Т  | М  | М   | Т  |

| 0  | 1    | 0  | 0  |           | co | Т   | Т   | М | Т  | 40 | 56 | T  | Т  | 50 | 34 | T | М  | Т  | Т   | М  |

| 0  | 1    | 0  | 1  |           | Т  | 49  | 33  | Т | 12 | Т  | T  | 28 | 22 | Т  | Т  | 6 | Т  | М  | М   | Ť  |

| 0  | 1    | 1  | 0  |           | Т  | М   | М   | Т | 10 | Т  | T  | 26 | 20 | Т  | Т  | 4 | Т  | М  | М   | Т  |

| 0  | 1    | 1  | 1  |           | 16 | Т   | Т   | 0 | Т  | М  | М  | Т  | Т  | м  | М  | Т | M. | Т  | T   | М  |

| 1  | 0    | 0  | 0  |           | СХ | Т   | Т   | М | T  | М  | М  | T  | Т  | М  | м  | Т | 14 | T  | Т   | 30 |

| 1  | 0    | 0  | 1  |           | T  | М   | М   | T | 11 | Т  | Т  | 27 | 21 | Т  | Т  | 5 | Т  | м  | М   | Т  |

| 1  | 0    | 1  | 0  |           | Т  | М   | М   | Т | 9  | Т  | T  | 25 | 19 | Т  | T  | 3 | Т  | 47 | 63  | T  |

| 1  | 0    | 1  | 1  |           | м  | Т   | Т   | М | Т  | 45 | 61 | T  | Ŧ  | 55 | 39 | T | М  | Т  | T   | М  |

| 1  | 1    | 0  | 0  |           | Т  | м   | м   | T | 8  | Т  | Т  | 24 | 18 | Т  | Т  | 2 | Ŧ  | м  | М   | Т  |

| 1  | 1    | 0  | 1  |           | 17 | Ŧ   | Т   | 1 | T  | 44 | 60 | Т  | Т  | 54 | 38 | Т | М  | T  | Т   | М  |

| 1  | 1    | 1  | 0  |           | м  | T   | T   | М | Т  | 42 | 58 | Т  | Т  | 52 | 36 | Т | М  | T  | T   | м  |

| 1  | 1    | 1  | 1  |           | Т  | 48  | 32  | Т | М  | Т  | Т  | м  | М  | T  | Т  | М | Т  | м  | М   | T  |

<sup>\* =</sup> No errors detected

Number = The bit number of the single bit-in-error

T - Two errors detected

M = More than two errors detected

#### Detect/Correct Mode

In this mode, the EDC functions the same way as in the Detect Mode except that the correction network is enabled to correct, by complementing, any single-bit error in the Data Input Latch before placing the data on the inputs of the Data Output Latch. If a multiple error is detected, the output of the correction network is undefined. If a single-bit error occurs to a check bit, there is no automatic correction. If a check bit correction is desired, it can be done by placing the device in the Generate Mode to produce the correct check bit sequence for the data in the Data Input Latch.

For data correction, both the upper EDC slice and the lower EDC slice require access to the syndrome bits SC<sub>0-7</sub> of the upper EDC slice, the EDC slice has access to these syndrome bits through an internal data path. The syndrome bits must be read through the CB<sub>0-7</sub> inputs for the lower EDC slice as shown in Figure 8. In the Detect/Correct Mode, the valid SC<sub>0-7</sub> outputs of the up-

per EDC slice must be enabled so that they are available for reading in through the CBo-7 inputs of the lower EDC slice.

#### Pass-Thru Mode

In this mode, the unmodified contents of the Data Input Latch are placed on the inputs of the Data Output Latch, and the contents of the Check bit Latch are placed on the output SCo-6 (SC<sub>7</sub> is a logical"1"). ERROR and MULT ERROR are forced HIGH in this mode (inactive).

#### Diagnostic Generate Mode

This is one of the three special Diagnostic Modes selected by the control inputs DIAG MODE<sub>0,1</sub>. This mode is similar to the normal Generate Mode except that the check bits are not generated from the contents of the Data Input Latch. They are instead taken directly from the contents of the Diagnostic Latch. Table 9 shows the Diagnostic Latch coding format.

Table 9, 64-Bit Diagnostic Latch Coding Format

| Data Bit | Internal Function                           |

|----------|---------------------------------------------|

| 0        | Diagnostic Check Bit X                      |

| 1        | Diagnostic Check Bit 0                      |

| 2        | Diagnostic Check Bit 1                      |

| 3        | Diagnostic Check Bit 2                      |

| 4        | Diagnostic Check Bit 4                      |

| 5        | Diagnostic Check Bit 8                      |

| 6        | Diagnostic Check Bit 16                     |

| 7        | Diagnostic Check Bit 32                     |

| 8        | CODE ID <sub>0</sub> , Lower 32-Bit Slice   |

| 9        | CODE ID1, Lower 32-Bit Slice                |

| 10       | DIAG MODE <sub>0</sub> , Lower 32-Bit Slice |

| 11       | DIAG MODE <sub>1</sub> , Lower 32-Bit Slice |

| 12       | CORRECT, Lower 32-Bit Slice                 |

| 13-31    | Don't Care                                  |

| 32-39    | Don't Care                                  |

| 40       | CODE ID <sub>0</sub> , Upper 32-Bit Slice   |

| 41       | CODE ID <sub>1</sub> , Upper 32-Bit Slice   |

| 42       | DIAG MODE <sub>0</sub> , Upper 32-Bit Slice |

| 43       | DIAG MODE <sub>1</sub> , Upper 32-Bit Slice |

| 44       | CORRECT, Upper 32-Bit Slice                 |

| 45-63    | Don't Care                                  |

# Diagnostic Detect, Diagnostic Detect /Correct Modes

These two special Diagnostic Modes are also selected by the control inputs DIAG MODE<sub>0</sub>, 1. These modes are similar to the normal Detect and Detect/Correct Modes except that the check bits are taken from the Diagnostic Latch, rather than from the Check Bit Input Latch.

#### Initialize Mode

In this mode the inputs of the Data Output Latch are forced to all zeros. The syndrome bit outputs SCo-6 are generated to correspond to the all-zero data on the Data Output Latch. SC7 is tied high. The ERROR and MULT ERROR outputs are forced HIGH in this mode. The Initialize Mode is useful after power-up when RAM contents are random. The EDC may be placed in this mode

and its outputs written into all memory addresses under processor control.

#### Internal Control Mode

This mode is selected by the external control inputs CODE ID<sub>0-1</sub>. When in the Internal Control Mode, the Am29C660 takes the CODE ID<sub>0-1</sub>, DIAG MODE<sub>0-1</sub>, and CORRECT control signals from the Diagnostic Latch rather than from the external input lines.

Table 10. Key AC Calculations For The 64-Bit Configuration

| Pro                  | 64-Bit<br>opagation Delay | Component Delays from Am29C660<br>AC Specifications                                          | Example for<br>Am29C660E |

|----------------------|---------------------------|----------------------------------------------------------------------------------------------|--------------------------|

| From                 | То                        |                                                                                              |                          |

| DATA0-31             | Check Bit Outputs         | (Data to SC, CODE ID 10) + (Check Bit to SC, CODE ID 11)                                     | 11 + 9 = 20 ns           |

| DATA <sub>0-31</sub> | Corrected Data<br>Outputs | (Data to SC, + CODE ID 10) + (Check Bit to SC, CODE ID 11) + (Check Bit to Data, CODE ID 10) | 11 + 9 + 10 = 30 ns      |

| DATA <sub>0-31</sub> | Syndrome Outputs          | (Data to SC, CODE ID 10) + (Check Bit to SC, CODE ID 11)                                     | 11 + 9 = 20 ns           |

| DATA <sub>0-31</sub> | ERROR Outputs             | (Data to SC, CODE ID 10) + (Check Bit to ERROR, CODE ID 11)                                  | 11 + 7 = 18 ns           |

| DATA <sub>0-31</sub> | MULT ERROR Outputs        | (Data to SC, CODE ID 10) + (Check Bit to MULT ERROR, CODE ID 11)                             | 11 + 9 = 20 ns           |

#### **APPLICATIONS**

# System Design Considerations

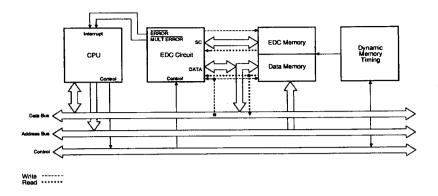

To obtain optimum performance and maximum design flexibility, AMD's Dynamic Memory Management System has been divided into functional building blocks. For 32-bit error detecting/correcting systems, these building blocks include the Am29C660 EDC Circuit, Am29C668 4M Configurable Dynamic Memory Controller/Driver, and the Am2971A 100-MHz Enhanced Programmable Event Generator or delay lines as the timing reference. Together these chips can perform traditional EDC, Flow-Thru or Fly-By, or AMD's Scrubbing EDC cycle.

# **High-Performance Parallel Operation**

For maximum memory system performance, the EDC should be used in the Check-Only (or Fly-By) configuration shown in Figure 9. With this configuration, the memory system operates as fast with EDC as it would without.

On reads from memory, data is read out from the DRAMs directly to the data bus (same as in a non-EDC system). At the same time, the data is read into the EDC to check for errors. If an error exists, the EDC's error flags (ERROR, MULT ERROR) are used to interrupt the CPU and/or to stretch the memory cycle. If no error is detected, no slowdown is required.

If an error is detected, the EDC generates corrected data for the processor. At the designer's option, the correct data may be written back into memory; error logging

and diagnostic routines may also be run under processor control.

The Check-Only configuration allows data reads to proceed as fast with EDC as without. Only if an error is detected is there any slowdown, but even if the memory system had an error every hour this would mean only one error every 3 – 4 billion memory cycles. Therefore, even with a very high error rate, EDC in a Check-Only configuration has essentially zero impact on memory system speed.

On writes to memory, check bits must be generated before the full memory word can be written into memory. Using the Am29C983 Multiple Bus Exchange allows the data word to be buffered on the memory board while check bits are generated. This makes the check bit generate time transparent to the processor.

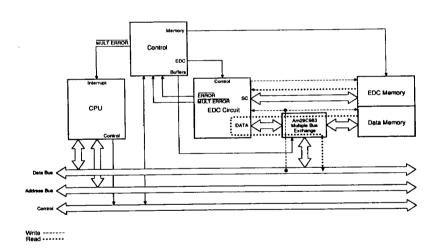

#### EDC in the Data Path

The simplest configuration for the Am29C660 is to have the EDC circuit directly in the data path, as shown in Figure 10 (Flow-Thru configuration). In this configuration, data read from memory is always corrected prior to putting the data on the data bus. The advantages are simpler operation and no need for mid-cycle interrupts. The disadvantage is that memory system speed is slowed by the amount of time it takes for error correction on every cycle.

Usually the Flow-Thru configuration will be used with MOS microprocessors which have ample memory timing budgets. Most high-performance processors will use the high-performance parallel configuration shown in Figure 9 (Fly-By).

# **Memory Scrubbing During Refresh**

Scrubbing is an error correction technique that examines the entire memory during system refresh cycles. thus causing little or no impact on performance yet providing high data reliability since errors cannot accumu-

Single-bit errors are by far the most common in a dynamic memory system, and are always correctable by the EDC. Double-bit errors occur far less frequently than single-bit errors (100-to-1 or greater) and are always detected by the EDC, but not corrected.

In a memory system, soft errors occur only one at a time. A double-bit error in a data word occurs when a single soft error is left uncorrected and is followed by another error in the data word within hours, days, or weeks after the first occurrence.

Scrubbing the memory periodically avoids almost all double-bit errors. In the scrubbing operation, every data word in memory is periodically checked by the EDC for single-bit errors. If one is found, it is corrected and the correct data word is written back into memory. Errors are not allowed to accumulate, and thus most double-bit errors are avoided.

The scrubbing operation is generally done as a background routine when the memory is not being used by the processor. If memory is scrubbed frequently, errors that are detected and corrected during processor accesses need not be immediately written back into memory. Instead, the error will be corrected in memory during scrubbing. This reduces the time delay involved in a processor access of an incorrect memory word.

On each refresh-with-scrub cycle, one memory location is read, checked for errors, and if necessary, corrected before being written back into memory. For a sixteenmegaword memory (224 locations) with one refresh every 16 microseconds, the AMD Memory Management chip set will scrub the entire memory of single-bit errors every minute. If multiple-bit errors are encountered during a scrub cycle, WE is suppressed.

With the occurrence of an error, a read/modify/write (R/ M/W) cycle is performed. The duration of a R/M/W cycle is typically longer than a normal read or write cycle. During refresh operations, a row in each bank is accessed by energizing the RAS line. This refreshes all the locations in that row. If an error is detected, a write operation is performed in that bank at the location of the error. This is accomplished by energizing the CAS line in that bank for that location. The entire checking operation is performed within the refresh cycle. A wait state may need to be issued to extend the cycle should an error be discovered. However, the system reliability will be increased because soft errors will not be able to accumulate in areas of memory that are not frequently accessed.

When performing refresh without scrubbing, all four RAS lines go LOW but the CAS lines remain HIGH or inactive. A refresh with scrubbing will activate all four RAS lines as before and a single CAS line. Errors that are detected during scrubbing cycles do not cause interrupts or bus-error (BERR) signal assertions.

Figure 11 shows a sixteen-megaword memory system with error detection and correction.

#### Check Bit Correction

The EDC detects single bit errors whether the error is a data bit or a check bit. Data bit errors are automatically corrected by the EDC. To generate corrected check bits once a single check bit error is detected, the EDC need only be switched to GENERATE mode (data in the DATA INPUT LATCH is valid).

The syndromes generated by the EDC may be decoded to determine whether the single bit error is a check bit.

In many memory systems, a check bit error will be ignored on the memory read and corrected during a periodic "scrubbing" of memory (see section in System Design Considerations).

#### **Multiple Errors**

The bit-in-error decode logic uses syndrome bit S0 through S32 to correct errors, SX is only used in developing the multiple error signal. This means that some multiple errors will cause a data bit to be inverted.

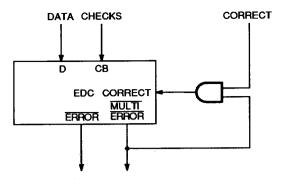

For example, in the 16-bit mode if data bits 8 and 13 are in error the syndrome 111100 (SX, S0, S1, S4, S8) is produced. This is flagged a double error by the error detection logic, but the bit-in-error decoder only receives syndrome 11100 (S0, S1, S2, S4, S8), which it decodes as a single error in data bit 0 and inverts that bit. If it is desired to inhibit this version the multiple error output may be connected to the correct input as in Figure 13. This will inhibit correction when a multiple error occurs. Extra time delay may be introduced in the data to correct data path when this is done.

10565-009A

Figure 9. Check-Only Configuration

10565-010A

Figure 10. Correct-Always Configuration

10565-011A

Figure 11. Sixteen-Megaword Memory System with EDC

10565-012A

#### Note:

$C_1 = 1.0 \mu F$ ,  $C_2 = 0.1 \mu F$ ,  $C_3 = 0.01 \mu F$ .

The C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> capacitors should be used to shunt low- and high-frequency noise from Vcc. Do not replace with one capacitor. Place capacitors as close to the device as possible.

Figure 12. Device Decoupling-Vcc and Ground Pin Connections

Table 11. 32-Bit Word/Check Bit Examples

| D <sub>31</sub> |      |      | Example | e 32-Bit W | ord  |      |      |     | responding<br>neck Bits<br>C <sub>16</sub> |

|-----------------|------|------|---------|------------|------|------|------|-----|--------------------------------------------|

| 0101            | 0101 | 0101 | 0101    | 0101       | 0101 | 0101 | 0101 |     | 0011000                                    |

| 1010            | 1010 | 1010 | 1010    | 1010       | 1010 | 1010 | 1010 | 1 1 | 0011000                                    |

| 0001            | 0000 | 1100 | 0111    | 0111       | 1101 | 0111 | 1111 |     | 1101110                                    |

| 0000            | 0011 | 0011 | 1101    | 1000       | 0101 | 0100 | 0000 |     | 1110011                                    |

| 1111            | 1111 | 1111 | 0000    | 0000       | 0000 | 1111 | 1110 |     | 0101001                                    |

Figure 13. Inhibition of Data Modification

10565-013A

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage Temperature65 to +150°C                                                                                                                                                                                                               |

| Temperature (Case)                                                                                                                                                                                                                            |

| Under Bias55 to +125°C                                                                                                                                                                                                                        |

| Supply Voltage to Ground Potential                                                                                                                                                                                                            |

| Continous                                                                                                                                                                                                                                     |

| DC Voltage Applied to Outputs For                                                                                                                                                                                                             |

| HIGH Output State0.5 V to Vcc Max.                                                                                                                                                                                                            |

| DC Input Voltage0.5 to +5.5 V                                                                                                                                                                                                                 |

| DC Input Current30 mA to +5.0 mA                                                                                                                                                                                                              |

| Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied Exposure to absolute maximum ratings for extended periods may affect device reliability. |

| OPERATING RANGES                                                                |                      |

|---------------------------------------------------------------------------------|----------------------|

| Commercial (C) Devices                                                          |                      |

| Ambient Temperature (T <sub>A</sub> )                                           | 0 to + 70°C          |

| Supply Voltage                                                                  | . +4.75 to +5.25 V   |

| Military (M) Devices                                                            |                      |

| Case Temperature (Tc)                                                           | 55 to +125°C         |

| Supply Voltage                                                                  | +4.5 to +5.5 V       |

| Operating ranges define those limits bet tionality of the device is guaranteed. | ween which the func- |

# DC CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description                                             | ,                                                                                         | Test Conditions                       | (Note 1)                                | Min.                 | Max. | Uni       |

|---------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------|----------------------|------|-----------|

| VIH                 | Input HIGH Voltage                                                   | Guaranteed Inpu<br>Voltage for all I                                                      |                                       |                                         | 2.0                  |      | ٧         |

| VIL                 | Input LOW Voltage                                                    | Guaranteed Inpu<br>Voltage for all I                                                      | ut Logical LOW<br>nputs (Note 3)      |                                         |                      | 0.8  | ٧         |

| hн                  | Input HIGH Current                                                   | V <sub>CC</sub> = Max.,<br>V <sub>IN</sub> = V <sub>CC</sub>                              |                                       |                                         |                      | 5.0  | μΑ        |

| ŧ <sub>IL</sub>     | Input LOW Current                                                    | V <sub>CC</sub> = Max.,<br>V <sub>IN</sub> = GND                                          |                                       |                                         |                      | -5.0 | μА        |

|                     |                                                                      |                                                                                           | I <sub>OH</sub> = -300 μ              | A                                       | V <sub>CC</sub> -0.2 |      |           |

| V <sub>OH</sub>     | Output HIGH Voltage                                                  | V <sub>CC</sub> = Min.                                                                    | MIL IOH = -8                          | mA                                      | 2.4                  |      | V         |

|                     |                                                                      |                                                                                           | COM'L IOH =                           | -15 mA                                  | 2.4                  |      |           |

|                     |                                                                      |                                                                                           | l <sub>OL</sub> = 300 μA              |                                         |                      | 0.2  |           |

| VOL                 | Output LOW Voltage                                                   | V <sub>CC</sub> = Min.                                                                    | MIL IOL = 8 r                         |                                         |                      | 0.5  | l۷        |

|                     |                                                                      |                                                                                           | COM'L IOL =                           |                                         |                      | 0.5  |           |

| loz                 | Off-State (High-Impedance)                                           | V <sub>CC</sub> = Max.                                                                    |                                       | V <sub>O</sub> = 0 V                    |                      | -10  | μ,        |

| -02                 | Output Current                                                       |                                                                                           |                                       | V <sub>O</sub> = V <sub>CC</sub> (Max.) |                      | 10   | <u> </u>  |

| los                 | Output Short-Circuit Current                                         |                                                                                           | 0 = 0 V (Note 2)                      |                                         | -30                  |      | m/        |

| Icca                | Quiescent Power<br>Supply Current<br>(CMOS Inputs)                   | V <sub>CC</sub> = Max.,<br>V <sub>CC</sub> -0.2 V ≤ V <sub>I</sub><br>f <sub>OP</sub> = 0 | <sub>IN</sub> ,V <sub>IN</sub> ≤ 0.2V |                                         |                      | 5.0  | m         |