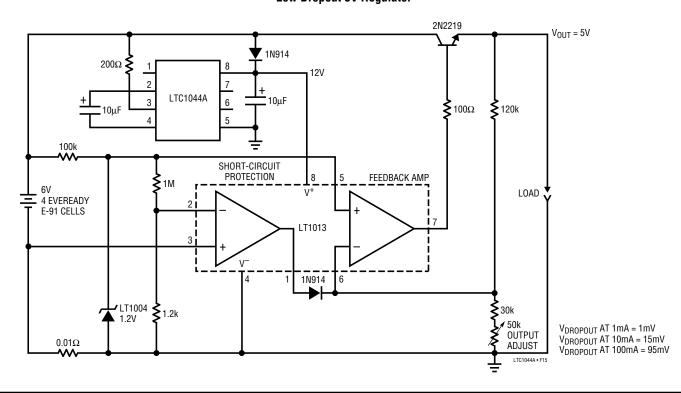

## Switched-Capacitor Voltage Converter with Regulator

### **FEATURES**

- Available in Space Saving SO-8 Package

- **Output Current: 100mA**

- Low Loss: 1.1V at 100mA

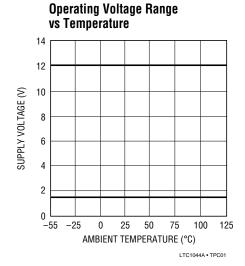

- Operating Range: 3.5V to 15V

- Reference and Error Amplifier for Regulation

- External Shutdown

- External Oscillator Synchronization

- Can Be Paralleled

- Pin Compatible with the LTC®1044/LTC7660

### **APPLICATIONS**

- Voltage Inverter

- Voltage Regulator

- Negative Voltage Doubler

- Positive Voltage Doubler

DESCRIPTION

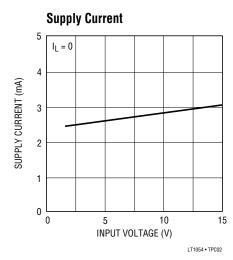

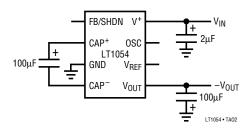

The LT®1054 is a monolithic, bipolar, switched-capacitor voltage converter and regulator. The LT1054 provides higher output current than previously available converters with significantly lower voltage losses. An adaptive switch driver scheme optimizes efficiency over a wide range of output currents. Total voltage loss at 100mA output current is typically 1.1V. This holds true over the full supply voltage range of 3.5V to 15V. Quiescent current is typically 2.5mA.

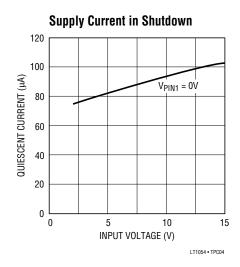

The LT1054 also provides regulation, a feature not previously available in switched-capacitor voltage converters. By adding an external resistive divider a regulated output can be obtained. This output will be regulated against changes in both input voltage and output current. The LT1054 can also be shut down by grounding the feedback pin. Supply current in shutdown is less than 100µA.

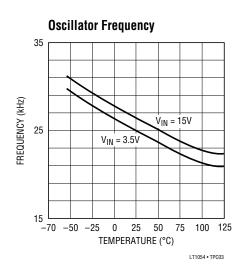

The internal oscillator of the LT1054 runs at a nominal frequency of 25kHz. The oscillator pin can be used to adjust the switching frequency or to externally synchronize the LT1054.

The LT1054 is pin compatible with previous converters such the LTC1044/LTC7660.

17, LTC and LT are registered trademarks of Linear Technology Corporation.

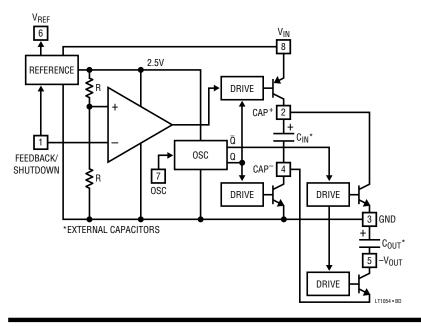

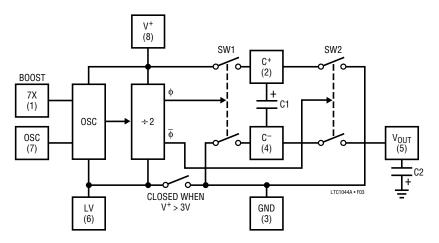

### **BLOCK DIAGRAM**

## **Voltage Loss** $3.5V \le V_{IN} \le 15V$ C<sub>IN</sub> = C<sub>OUT</sub> = 100μF • INDICATES GUARANTEED TEST POINT /OLTAGE LOSS (V) = 25°C 30 40 50 60 70 90 100 OUTPUT CURRENT (mA) I T1054 • TA01

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (Note 1)Input Voltage | 16V                            |

|--------------------------------------|--------------------------------|

| Pin 1                                | $0V \le V_{PIN1} \le V^+$      |

| Pin 3 (S Package)                    | $0V \le V_{PIN3} \le V^+$      |

| Pin 7                                | $0V \le V_{PIN7} \le V_{REF}$  |

| Pin 13 (S Package)                   | $0V \le V_{PIN13} \le V_{REF}$ |

| Operating Temperature Range          |                                |

| LT1054C                              | 0°C to 70°C                    |

| LT1054I                              | 40°C to 85°C                   |

| LT1054M                              | 55°C to 125°C                  |

| Junction Temperature Range (Note 2)  |                          |       |

|--------------------------------------|--------------------------|-------|

| LT1054C                              |                          | 125°C |

| LT1054I                              |                          | 125°C |

| LT1054M                              |                          | 150°C |

| Storage Temperature Range            |                          |       |

| H, J8, N8 and S8 Packages            | . –55°C to               | 150°C |

| S Package                            | $-65^{\circ}\text{C to}$ | 150°C |

| Lead Temperature (Soldering, 10 sec) |                          | 300°C |

|                                      |                          |       |

## PACKAGE/ORDER INFORMATION (Note 6)

| TOP VIEW  V <sup>+</sup> 8  7  OSC  CAP <sup>+</sup> (2)  6  V <sub>REF</sub> GND (3)  4  5  V <sub>OUT</sub> CASE  IS  CAP <sup>-</sup> VOUT  H PACKAGE  8-LEAD TO-5 METAL CAN  T <sub>JMAX</sub> = 150°C, $\theta_{JA}$ = 150°C, $\theta_{JC}$ = 45°C/W | ORDER PART<br>NUMBER<br>LT1054CH<br>LT1054MH                             | TOP VIEW  FB/SHDN 1  CAP+ 2  GND 3  CAP- 4  S8 PACKAGE 8-LEAD PLASTIC SO  T <sub>JMAX</sub> = XXX°C, θ <sub>JA</sub> = XXX°C/W  SEE REGULATION AND CAPACITOR SELECTION SECTIONS IN THE APPLICATIONS INFORMATION FOR IMPORTANT INFORMATION ON THE S8 DEVICE | ORDER PART<br>NUMBER<br>LT1054CS8<br>S8 PART<br>MARKING<br>1054 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| TOP VIEW  FB/SHDN 1  CAP+ 2  GND 3  CAP- 4  J8 PACKAGE 8-LEAD CERAMIC DIP  T <sub>JMAX</sub> = 150°C, θ <sub>JA</sub> = 100°C/W (J8)  T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 130°C/W (N8)                                                           | ORDER PART<br>NUMBER<br>LT1054CJ8<br>LT1054CN8<br>LT1054IN8<br>LT1054MJ8 | TOP VIEW  NC 1  NC 2  FB/SHDN 3  CAP* 4  GND 5  CAP 111 V <sub>OUT</sub> 10 NC  9 NC  S PACKAGE 16-LEAD PLASTIC SOL  T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 150°C/W                                                                                  | ORDER PART<br>NUMBER<br>LT1054CS<br>LT1054IS                    |

### **ELECTRICAL CHARACTERISTICS** (Note 6)

| PARAMETER                                            | CONDITIONS                                                                                  |   | MIN          | TYP          | MAX          | UNITS    |

|------------------------------------------------------|---------------------------------------------------------------------------------------------|---|--------------|--------------|--------------|----------|

| Supply Current                                       | $I_{LOAD} = 0mA$ $V_{IN} = 3.5V$ $V_{IN} = 15V$                                             | • |              | 2.5<br>3.0   | 4.0<br>5.0   | mA<br>mA |

| Supply Voltage Range                                 |                                                                                             | • | 3.5          |              | 15           | V        |

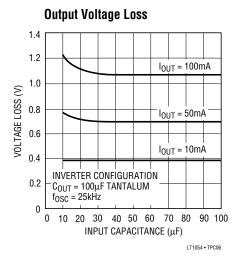

| Voltage Loss (V <sub>IN</sub> – IV <sub>OUT</sub> I) | $C_{IN} = C_{OUT} = 100 \mu F$ Tantalum (Note 3)<br>$I_{OUT} = 10 mA$<br>$I_{OUT} = 100 mA$ | • |              | 0.35<br>1.10 | 0.55<br>1.60 | V        |

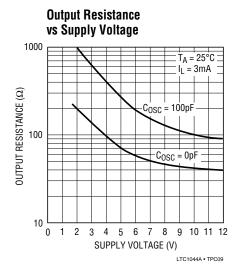

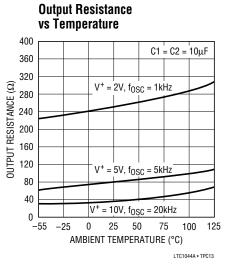

| Output Resistance                                    | $\Delta I_{OUT} = 10$ mA to 100mA (Note 4)                                                  | • |              | 10           | 15           | Ω        |

| Oscillator Frequency                                 | $3.5V \le V_{IN} \le 15V$                                                                   | • | 15           | 25           | 35           | kHz      |

| Reference Voltage                                    | I <sub>REF</sub> = 60μA, T <sub>J</sub> = 25°C                                              | • | 2.35<br>2.25 | 2.50         | 2.65<br>2.75 | V        |

| Regulated Voltage                                    | $V_{IN} = 7V$ , $T_J = 25^{\circ}C$ , $R_L = 500\Omega$ (Note 5)                            |   | -4.70        | -5.00        | -5.20        | V        |

| Line Regulation                                      | $7V \le V_{IN} \le 12V$ , $R_L = 500\Omega$ (Note 5)                                        | • |              | 5            | 25           | mV       |

| Load Regulation                                      | $V_{IN}$ = 7V, $100\Omega \le R_L \le 500\Omega$ (Note 5)                                   | • |              | 10           | 50           | mV       |

| Maximum Switch Current                               |                                                                                             |   |              | 300          |              | mA       |

| Supply Current in Shutdown                           | V <sub>PIN1</sub> = 0V                                                                      | • |              | 100          | 200          | μΑ       |

The ● denotes specifications which apply over the full operating temperature range. For C grade parts these specifications also apply up to a junction temperature of 100°C.

**Note 1:** The absolute maximum supply voltage rating of 16V is for unregulated circuits. For regulation mode circuits with  $V_{OUT} \le 15V$  at pin 5, (pin 11 S package) this rating may be increased to 20V.

**Note 2:** The devices are guaranteed by design to be functional up to the absolute maximum junction temperature.

**Note 3:** For voltage loss tests, the device is connected as a voltage inverter, with pins 1, 6, and 7 (3, 12, and 13 S package) unconnected. The voltage losses may be higher in other configurations.

**Note 4:** Output resistance is defined as the slope of the curve,  $(\Delta V_{OUT})$  vs  $\Delta I_{OUT}$ ), for output currents of 10mA to 100mA. This represents the linear portion of the curve. The incremental slope of the curve will be higher at currents <10mA due to the characteristics of the switch transistors.

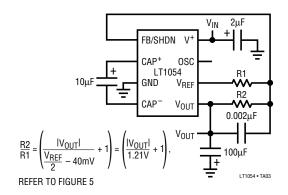

**Note 5:** All regulation specifications are for a device connected as a positive-to-negative converter/regulator with R1 = 20k, R2 = 102.5k, C1 =  $0.002\mu F$ , (C1 =  $0.05\mu F$  S package)  $C_{IN}$  =  $10\mu F$  tantalum,  $C_{OUT}$  =  $100\mu F$  tantalum.

**Note 6:** The S8 package uses a different die than the H, J8, N8 and S packages. The S8 device will meet all the existing data sheet parameters. See Regulation and Capacitor Selection in the Applications Information section for differences in application requirements.

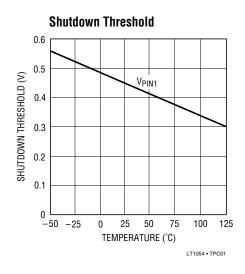

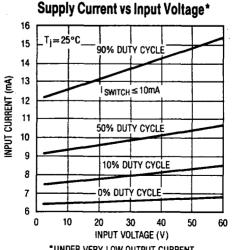

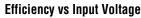

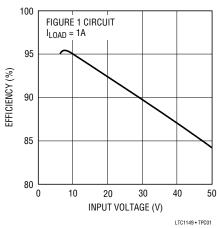

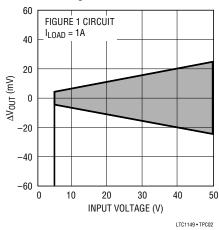

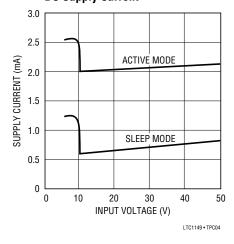

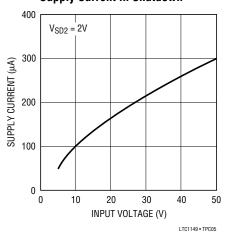

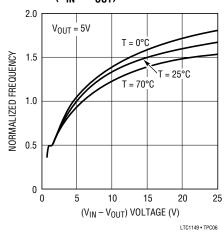

### TYPICAL PERFORMANCE CHARACTERISTICS

### TYPICAL PERFORMANCE CHARACTERISTICS

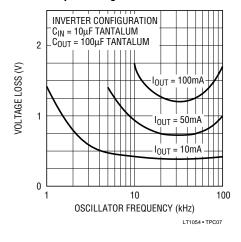

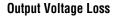

#### **Output Voltage Loss**

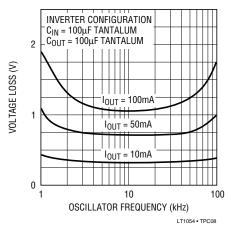

### **Regulated Output Voltage**

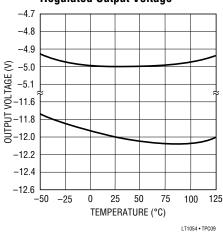

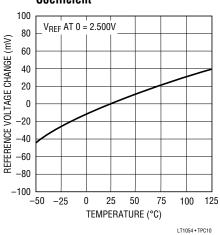

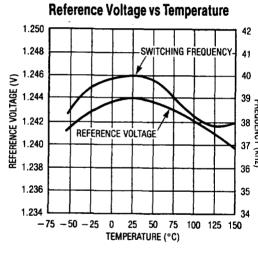

## Reference Voltage Temperature Coefficient

### PIN FUNCTIONS

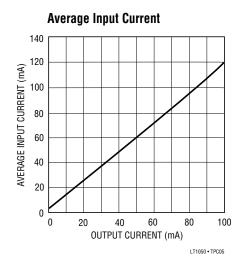

V+ (Pin 8): Input Supply. The LT1054 alternately charges  $C_{IN}$  to the input voltage when  $C_{IN}$  is switched in parallel with the input supply and then transfers charge to  $C_{OUT}$  when  $C_{IN}$  is switched in parallel with  $C_{OIIT}$ . Switching occurs at the oscillator frequency. During the time that C<sub>IN</sub> is charging, the peak supply current will be approximately equal to 2.2 times the output current. During the time that  $C_{IN}$  is delivering charge to C<sub>OUT</sub> the supply current drops to approximately 0.2 times the output current. An input supply bypass capacitor will supply part of the peak input current drawn by the LT1054 and average out the current drawn from the supply. A minimum input supply bypass capacitor of 2µF, preferably tantalum or some other low ESR type is recommended. A larger capacitor may be desirable in some cases, for example, when the actual input supply is connected to the LT1054 through long leads, or when the pulse current drawn by the LT1054 might affect other circuitry through supply coupling.

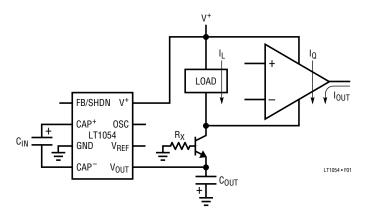

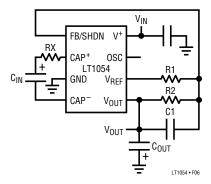

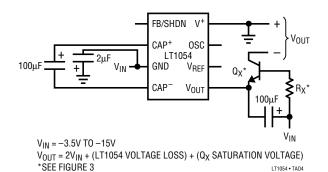

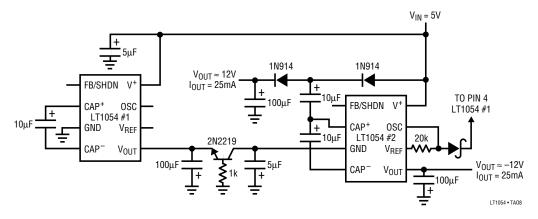

**V<sub>OUT</sub>** (**Pin 5**): In addition to being the output pin the pin is also tied to the substrate of the device. Special care must be taken in LT1054 circuits to avoid pulling this pin positive with respect to any of the other pins. Pulling pin 5 positive with respect to pin 3 (GND) will forward bias the substrate diode which will prevent the device from starting. This condition can occur when the output load driven by the LT1054 is referred to its positive supply (or to some other positive voltage). Note that most op amps present just such a load since their supply currents flow from their V<sup>+</sup> terminals to their V<sup>-</sup> terminals. To prevent start-up problems with this type of load an external transistor must be added as shown in Figure 1. This will prevent V<sub>OUT</sub> (pin 5) from being pulled above the ground pin (pin 3) during startup. Any small, general purpose transistor such as 2N2222 or 2N2219 can be used. Rx should be chosen to provide enough base drive to the external transistor so that it is saturated under nominal output voltage and maximum output current conditions. In some cases an N-channel enhancement mode MOSFET can be used in place of the transistor.

$$R_X \le \frac{(|V_{OUT}|)\beta}{I_{OUT}}$$

Figure 1

**V<sub>RFF</sub>** (**Pin 6**): Reference Output. This pin provides a 2.5V reference point for use in LT1054-based regulator circuits. The temperature coefficient of the reference voltage has been adjusted so that the temperature coefficient of the regulated output voltage is close to zero. This requires the reference output to have a positive temperature coefficient as can be seen in the typical performance curves. This nonzero drift is necessary to offset a drift term inherent in the internal reference divider and comparator network tied to the feedback pin. The overall result of these drift terms is a regulated output which has a slight positive temperature coefficient at output voltages below 5V and a slight negative TC at output voltages above 5V. Reference output current should be limited, for regulator feedback networks, to approximately 60µA. The reference pin will draw ≈100µA when shorted to ground and will not affect the internal reference/regulator, so that this pin can also be used as a pull-up for LT1054 circuits that require synchronization.

**CAP**+/**CAP**- (**Pin 2/Pin 4**): Pin 2, the positive side of the input capacitor ( $C_{IN}$ ), is alternately driven between V+ and ground. When driven to V+, pin 2 sources current from V+. When driven to ground pin 2 sinks current to ground. Pin 4, the negative side of the input capacitor, is driven alternately between ground the  $V_{OUT}$ . When driven to ground, pin 4 sinks current to ground. When driven to  $V_{OUT}$  pin 4 sources current from  $C_{OUT}$ . In all cases current flow in the switches is unidirectional as should be expected using bipolar switches.

### PIN FUNCTIONS

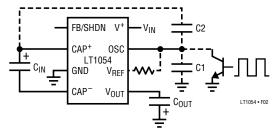

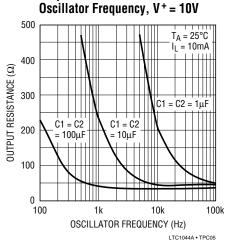

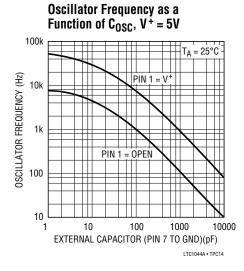

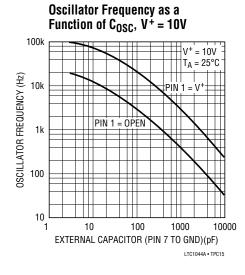

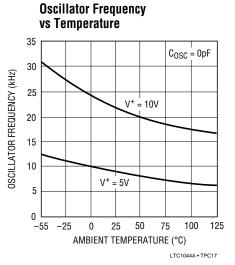

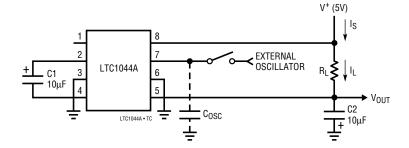

**OSC (Pin 7):** Oscillator Pin. This pin can be used to raise or lower the oscillator frequency or to synchronize the device to an external clock. Internally pin 7 is connected to the oscillator timing capacitor ( $C_t \approx 150 \text{pF}$ ) which is alternately charged and discharged by current sources of  $\pm 7 \mu \text{A}$  so that the duty cycle is  $\approx 50\%$ . The LT1054 oscillator is designed to run in the frequency band where switching losses are minimized. However the frequency can be raised, lowered, or synchronized to an external system clock if necessary.

The frequency can be lowered by adding an external capacitor (C1, Figure 2) from pin 7 to ground. This will increase the charge and discharge times which lowers the oscillator frequency. The frequency can be increased by adding an external capacitor (C2, Figure 2, in the range of 5pF to 20pF) from pin 2 to pin 7. This capacitor will couple charge into C<sub>t</sub> at the switch transitions, which will shorten the charge and discharge time, raising the oscillator frequency. Synchronization can be accomplished by adding an external resistive pull-up from pin 7 to the reference pin (pin 6). A 20k pull-up is recommended. An open collector gate or an NPN transistor can then be used to drive the oscillator pin at the external clock frequency as shown in Figure 2. Pulling up pin 7 to an external voltage is **not recommended**. For circuits that require both fre-

Figure 2

quency synchronization and regulation, an external reference can be used as the reference point for the top of the R1/R2 divider allowing pin 6 to be used as a pull-up point for pin 7.

FB/SHDN (Pin 1): Feedback/Shutdown Pin. This pin has two functions. Pulling pin 1 below the shutdown threshold  $(\approx 0.45 \text{V})$  puts the device into shutdown. In shutdown the reference/regulator is turned off and switching stops. The switches are set such that both CIN and COUT are discharged through the output load. Quiescent current in shutdown drops to approximately 100µA (see Typical Performance Characteristics). Any open-collector gate can be used to put the LT1054 into shutdown. For normal (unregulated) operation the device will start back up when the external gate is shut off. In LT1054 circuits that use the regulation feature, the external resistor divider can provide enough pull-down to keep the device in shutdown until the output capacitor (C<sub>OUT</sub>) has fully discharged. For most applications where the LT1054 would be run intermittently, this does not present a problem because the discharge time of the output capacitor will be short compared to the offtime of the device. In applications where the device has to start up before the output capacitor (COUT) has fully discharged, a restart pulse must be applied to pin 1 of the LT1054. Using the circuit of Figure 5, the restart signal can be either a pulse  $(t_p > 100 \mu s)$  or a logic high. Diode coupling the restart signal into pin 1 will allow the output voltage to come up and regulate without overshoot. The resistor divider R3/R4 in Figure 5 should be chosen to provide a signal level at pin 1 of 0.7V to 1.1V.

Pin 1 is also the inverting input of the LT1054's error amplifier and as such can be used to obtain a regulated output voltage.

### APPLICATIONS INFORMATION

### **Theory of Operation**

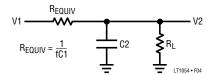

To understand the theory of operation of the LT1054, a review of a basic switched-capacitor building block is helpful.

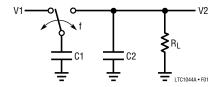

In Figure 3 when the switch is in the left position, capacitor C1 will charge to voltage V1. The total charge on C1 will be q1 = C1V1. The switch then moves to the right, discharging C1 to voltage V2. After this discharge time the charge on C1 is q2 = C1V2. Note that charge has been transferred from the source V1 to the output V2. The amount of charge transferred is:

$$\Delta q = q1 - q2 = C1(V1 - V2)$$

If the switch is cycled f times per second, the charge transfer per unit time (i.e., current) is:

$$I = f \times \Delta q = f \times C1(V1 - V2)$$

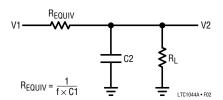

To obtain an equivalent resistance for the switched-capacitor network we can rewrite this equation in terms of voltage and impedance equivalence:

$$I = \frac{V1 - V2}{(1/fC1)} = \frac{V1 - V2}{REQUIV}$$

$$V1 - C1 - C2 - R_{L}$$

$$V2 - C1 - C2 - R_{L}$$

Figure 3. Switched-Capacitor Building Block

A new variable  $R_{EQUIV}$  is defined such that  $R_{EQUIV} = 1/fC1$ . Thus the equivalent circuit for the switched-capacitor network is as shown in Figure 4. The LT1054 has the same switching action as the basic switched-capacitor building block. Even though this simplification doesn't include finite switch on-resistance and output voltage ripple, it provides an intuitive feel for how the device works.

These simplified circuits explain voltage loss as a function of frequency (see Typical Performance Characteristics). As frequency is decreased, the output impedance will eventually be dominated by the 1/fC1 term and voltage losses will rise.

Figure 4. Switched-Capacitor Equivalent Circuit

Note that losses also rise as frequency increases. This is caused by internal switching losses which occur due to some finite charge being lost on each switching cycle. This charge loss per-unit-cycle, when multiplied by the switching frequency, becomes a current loss. At high frequency this loss becomes significant and voltage losses again rise.

The oscillator of the LT1054 is designed to run in the frequency band where voltage losses are at a minimum.

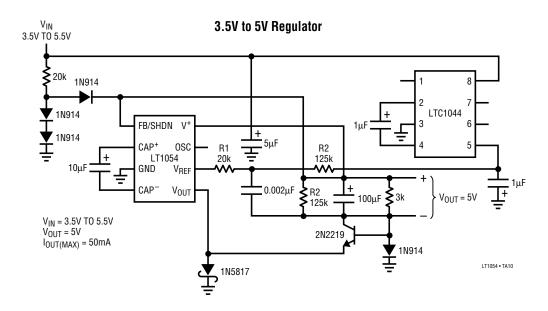

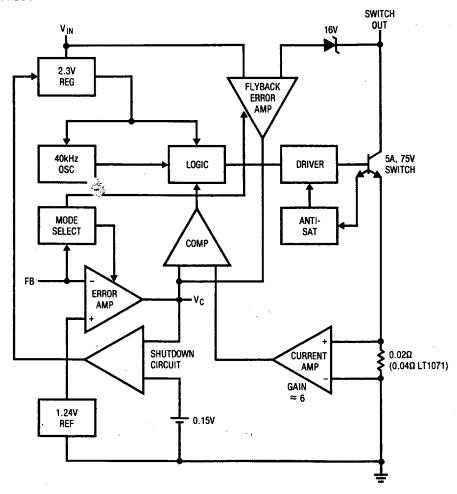

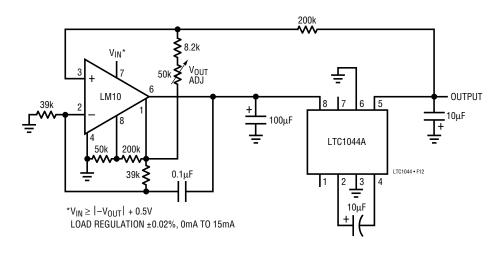

### Regulation

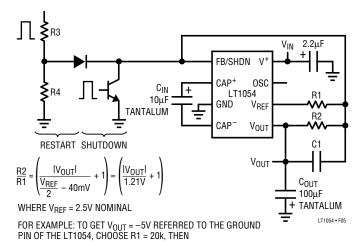

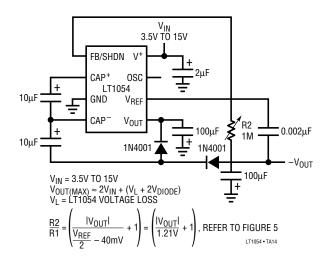

The error amplifier of the LT1054 servos the drive to the PNP switch to control the voltage across the input capacitor ( $C_{IN}$ ) which in turn will determine the output voltage. Using the reference and error amplifier of the LT1054, an external resistive divider is all that is needed to set the regulated output voltage. Figure 5 shows the basic regulator configuration and the formula for calculating the appropriate resistor values. R1 should be chosen to be

R2 =

$$20k \left( \frac{|-5V|}{\frac{2.5V}{2} - 40mV} + 1 \right) = 102.6k$$

\*CHOOSE THE CLOSEST 1% VALUE

Figure 5

### APPLICATIONS INFORMATION

20k or greater because the reference output current is limited to  $\approx 100 \mu A$ . R2 should be chosen to be in the range of 100k to 300k. For optimum results the ratio of  $C_{IN}/C_{OUT}$  is recommended to be 1/10. C1, required for good load regulation at light load currents, should be 0.002  $\mu F$  for all output voltages.

A new die layout was required to fit into the physical dimensions of the S8 package. Although the new die of the LT1054CS8 will meet all the specifications of the existing LT1054 data sheet, subtle differences in the layout of the new die require consideration in some application circuits. In regulating mode circuits using the 1054CS8 the nominal values of the capacitors, C<sub>IN</sub> and C<sub>OUT</sub>, must be approximately equal for proper operation at elevated junction temperatures. This is different from the earlier part. Mismatches within normal production tolerances for the capacitors are acceptable. Making the nominal capacitor values equal will ensure proper operation at elevated junction temperatures at the cost of a small degradation in the transient response of regulator circuits. For unregulated circuits the values of  $C_{IN}$  and  $C_{OUT}$ are normally equal for all packages. For S8 applications assistance in unusual applications circuits, please consult the factory.

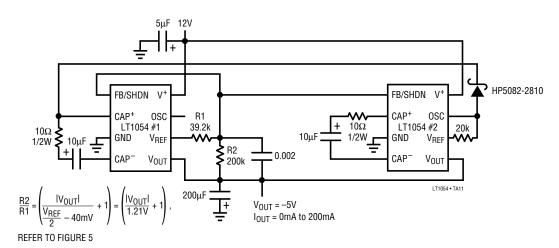

It can be seen from the circuit block diagram that the maximum regulated output voltage is limited by the supply voltage. For the basic configuration,  $|V_{OUT}|$  referred to the ground pin of the LT1054 must be less than the total of the supply voltage minus the voltage loss due to the switches. The voltage loss versus output current due to the switches can be found in Typical Performance Characteristics. Other configurations such as the negative doubler can provide higher output voltages at reduced output currents (see Typical Applications).

### **Capacitor Selection**

For unregulated circuits the nominal values of  $C_{IN}$  and  $C_{OUT}$  should be equal. For regulated circuits see the section on Regulation. While the exact values of  $C_{IN}$  and  $C_{OUT}$  are noncritical, good quality, low ESR capacitors such as solid tantalum are necessary to minimize voltage losses at high currents. For  $C_{IN}$  the effect of the ESR of the capacitor will be multiplied by four due to the fact that switch currents are approximately two times higher than output current and

losses will occur on both the charge and discharge cycle. This means that using a capacitor with  $1\Omega$  of ESR for  $C_{IN}$ will have the same effect as increasing the output impedance of the LT1054 by  $4\Omega$ . This represents a significant increase in the voltage losses. For  $C_{OUT}$  the affect of ESR is less dramatic. Cour is alternately charged and discharged at a current approximately equal to the output current and the ESR of the capacitor will cause a step function to occur in the output ripple at the switch transitions. This step function will degrade the output regulation for changes in output load current and should be avoided. Realizing that large value tantalum capacitors can be expensive, a technique that can be used is to parallel a smaller tantalum capacitor with a large aluminum electrolytic capacitor to gain both low ESR and reasonable cost. Where physical size is a concern some of the newer chip type surface mount tantalum capacitors can be used. These capacitors are normally rated at working voltages in the 10V to 20V range and exhibit very low ESR (in the range of  $0.1\Omega$ ).

### **Output Ripple**

The peak-to-peak output ripple is determined by the value of the output capacitor and the output current. Peak-to-peak output ripple may be approximated by the formula:

$$dV = \frac{I_{OUT}}{2fC_{OUT}}$$

where dV = peak-to-peak ripple and f = oscillator frequency.

For output capacitors with significant ESR a second term must be added to account for the voltage step at the switch transitions. This step is approximately equal to:

### **Power Dissipation**

The power dissipation of any LT1054 circuit must be limited such that the junction temperature of the device does not exceed the maximum junction temperature ratings. The total power dissipation must be calculated from two components, the power loss due to voltage drops in the switches and the power loss due to drive current losses. The total power dissipated by the LT1054 can be calculated from:

### APPLICATIONS INFORMATION

$$P \approx (V_{IN} - |V_{OUT}|)(I_{OUT}) + (V_{IN})(I_{OUT})(0.2)$$

where both  $V_{IN}$  and  $V_{OUT}$  are referred to the ground pin (pin 3) of the LT1054. For LT1054 regulator circuits, the power dissipation will be equivalent to that of a linear regulator. Due to the limited power handling capability of the LT1054 packages, the user will have to limit output current requirements or take steps to dissipate some power external to the LT1054 for large input/output differentials. This can be accomplished by placing a resistor in series with  $C_{IN}$  as shown in Figure 6. A portion of the input voltage will then be dropped across this resistor without affecting the output regulation. Because switch current is approximately 2.2

Figure 6

times the output current and the resistor will cause a voltage drop when  $C_{\text{IN}}$  is both charging and discharging, the resistor should be chosen as:

$$R_X = V_X/(4.4 I_{OUT})$$

where

$$V_X \approx V_{IN} - [(LT1054 \text{ Voltage Loss})(1.3) + |V_{OUT}|]$$

and  $I_{OUT}$  = maximum required output current. The factor of 1.3 will allow some operating margin for the LT1054.

For example: assume a 12V to -5V converter at 100mA output current. First calculate the power dissipation without an external resistor:

$$P = (12V - |-5V|)(100mA) + (12V)(100mA)(0.2)$$

$P = 700mW + 240mW = 940mW$

At  $\theta_{JA}$  of 130°C/W for a commercial plastic device this would cause a junction temperature rise of 122°C so that the device would exceed the maximum junction temperature at an ambient temperature of 25°C. Now calculate the power dissipation with an external resistor (R<sub>X</sub>). First find how much voltage can be dropped across R<sub>X</sub>. The maximum voltage loss of the LT1054 in the standard regulator configuration at 100mA output current is 1.6V, so

$$V_X = 12V - [(1.6V)(1.3) + |-5V|] = 4.9V$$

and  $R_X = 4.9V/(4.4)(100\text{mA}) = 11\Omega$

This resistor will reduce the power dissipated by the LT1054 by (4.9V)(100mA) = 490mW. The total power dissipated by the LT1054 would then be = (940 mW -490mW) = 450mW. The junction temperature rise would now be only 58°C. Although commercial devices are guaranteed to be functional up to a junction temperature of 125°C, the specifications are only guaranteed up to a junction temperature of 100°C, so ideally you should limit the junction temperature to 100°C. For the above example this would mean limiting the ambient temperature to 42°C. Other steps can be taken to allow higher ambient temperatures. The thermal resistance numbers for the LT1054 packages represent worst case numbers with no heat sinking and still air. Small clip-on type heat sinks can be used to lower the thermal resistance of the LT1054 package. In some systems there may be some available airflow which will help to lower the thermal resistance. Wide PC board traces from the LT1054 leads can also help to remove heat from the device. This is especially true for plastic packages.

#### **Basic Voltage Inverter**

#### **Basic Voltage Inverter/Regulator**

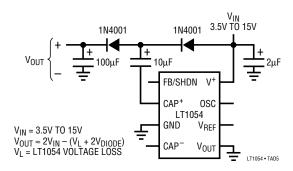

#### **Negative Voltage Doubler**

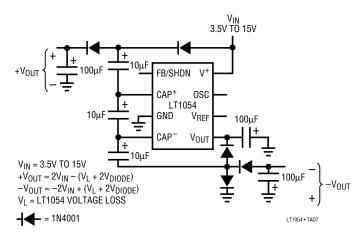

#### **Positive Doubler**

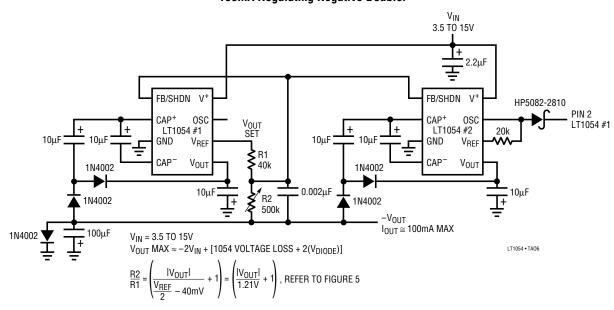

#### **100mA Regulating Negative Doubler**

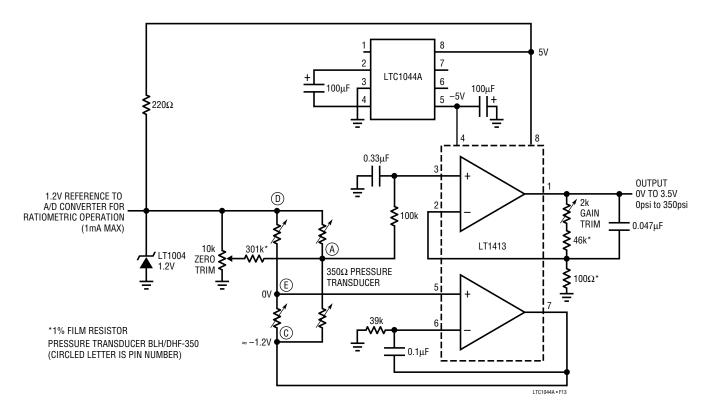

#### Strain Gauge Bridge Signal Conditioner

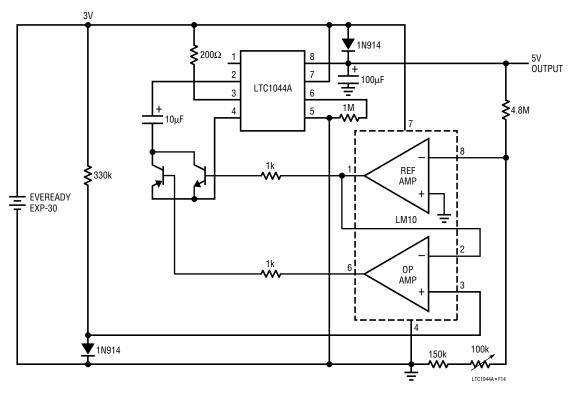

#### 5V to $\pm 12V$ Converter

#### 5V to $\pm 12V$ Converter INPUT TTL OR CMOS $10 \mu \text{F}$ 2N2907 40Ω **§** ZER0 LOW FOR ON TRIM GAIN TRIM 100k 0.022µF A1 1/2 LT1013 A2 1/2 LT1013 100k 10k $350\Omega$ **₹**200k LT1054 • TA09 FB/SHDN V+ 3k A = 125 FOR OV TO 3V OUT FROM FULL-SCALE CAP+ OSC 2N2222 BRIDGE OUTPUT OF 24mV LT1054 GND 100μF $V_{\mathsf{REF}}$ TANTALUM CAP. $V_{OUT}$

#### Regulating 200mA, 12V to -5V Converter

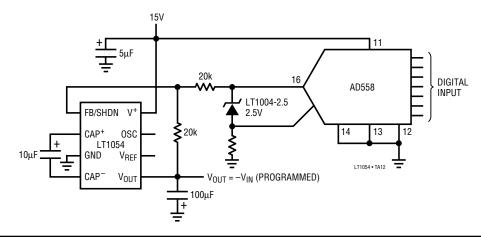

### **Digitally Programmable Negative Supply**

## Positive Doubler with Regulation (5V to 8V Converter)

#### $V_{IN} = 5V$ FB/SHDN 1N5817 10μF $V_{OUT}$ CAP+ OSC LT1054 1N5817 0.03μF GND $V_{\mathsf{REF}}$ 100μF $v_{\text{OUT}}$ CAP 5V **≨**10k LT1006 LT1054 • TA13

### **Negative Doubler with Regulator**

THE TYPICAL APPLICATIONS CIRCUITS WERE VERIFIED USING THE STANDARD LT1054. FOR S8 APPLICATIONS ASSISTANCE IN ANY OF THE UNUSUAL APPLICATIONS CIRCUITS PLEASE CONSULT THE FACTORY

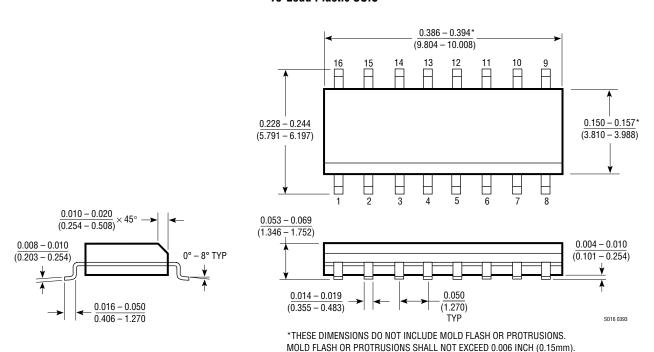

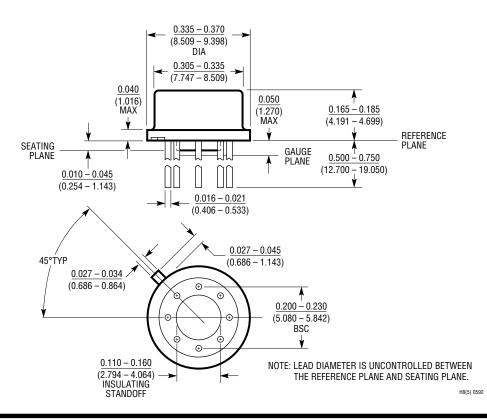

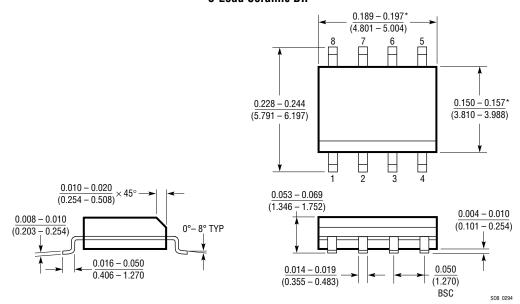

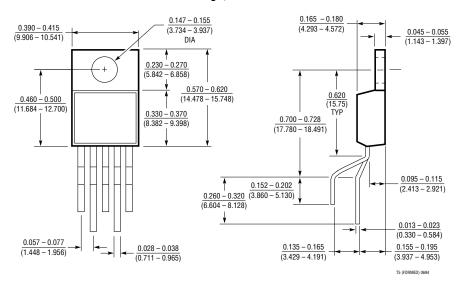

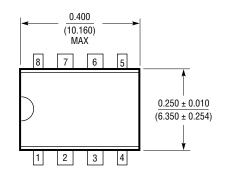

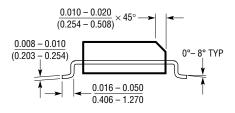

### PACKAGE DESCRIPTION D

Dimension in inches (millimeters) unless otherwise noted.

#### H Package 8-Lead TO-5 Metal Can

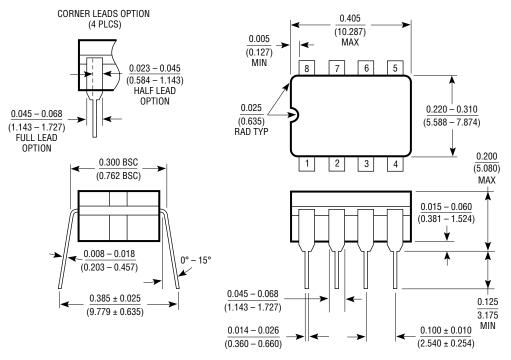

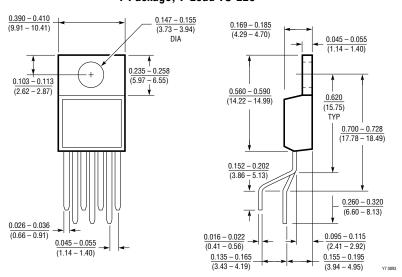

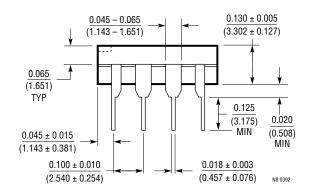

### PACKAGE DESCRIPTION

Dimension in inches (millimeters) unless otherwise noted.

#### J8 Package 8-Lead Ceramic DIP

NOTE: LEAD DIMENSIONS APPLY TO SOLDER DIP OR TIN PLATE LEADS.

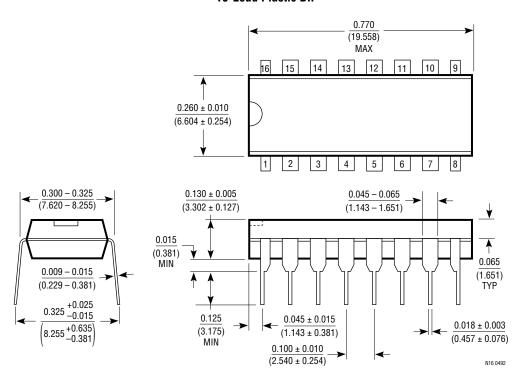

#### N8 Package 8-Lead Plastic DIP

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTURSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm). J8 0694

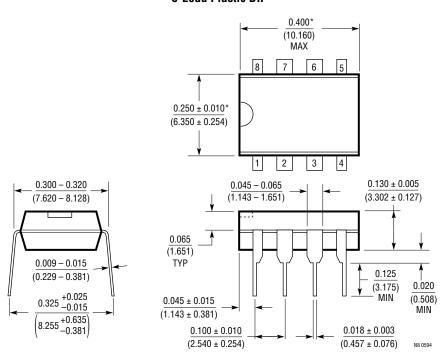

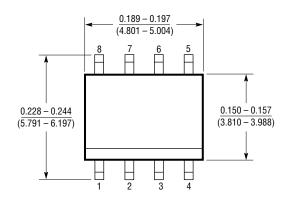

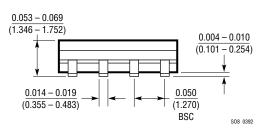

### PACKAGE DESCRIPTION

$\label{lem:decomposition} \textbf{Dimension in inches (millimeters) unless otherwise noted.}$

#### S8 Package 8-Lead Ceramic DIP

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 INCH (0.15mm).

#### S Package 16-Lead Plastic SOL

1. PIN 1 IDENT, NOTCH ON TOP AND CAVITIES ON THE BOTTOM OF PACKAGES ARE THE MANUFACTURING OPTIONS. THE PART MAY BE SUPPLIED WITH OR WITHOUT ANY OF THE OPTIONS.

<sup>2.</sup> THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 INCH (0.15mm).

SOL16 0392

### NORTHEAST REGION

**Linear Technology Corporation** 3220 Tillman Drive, Suite 120

Bensalem, PA 19020 Phone: (215) 638-9667 FAX: (215) 638-9764

#### **Linear Technology Corporation**

266 Lowell St., Suite B-8 Wilmington, MA 01887 Phone: (508) 658-3881 FAX: (508) 658-2701

#### **FRANCE**

#### Linear Technology S.A.R.L.

Immeuble "Le Quartz" 58 Chemin de la Justice 92290 Chatenay Malabry France

Phone: 33-1-41079555 FAX: 33-1-46314613

#### **GERMANY**

#### Linear Technology GmbH

Untere Hauptstr. 9 D-85386 Eching Germany

Phone: 49-89-3197410 FAX: 49-89-3194821

#### **JAPAN**

### Linear Technology KK

5F NAO Bldg.

1-14 Shin-Ogawa-cho Shinjuku-ku

Tokyo, 162 Japan Phone: 81-3-3267-7891 FAX: 81-3-3267-8510

#### **U.S. Area Sales Offices**

#### **SOUTHEAST REGION**

#### **Linear Technology Corporation**

17000 Dallas Parkway Suite 219 Dallas, TX 75248 Phone: (214) 733-3071 FAX: (214) 380-5138

#### **CENTRAL REGION**

#### **Linear Technology Corporation**

Chesapeake Square 229 Mitchell Court, Suite A-25

Addison, IL 60101 Phone: (708) 620-6910 FAX: (708) 620-6977

### **NORTHWEST REGION**

**SOUTHWEST REGION**

Woodland Hills, CA 91364

Phone: (818) 703-0835 FAX: (818) 703-0517

22141 Ventura Blvd.

Suite 206

### **Linear Technology Corporation**

**Linear Technology Corporation**

782 Sycamore Dr. Milpitas, CA 95035 Phone: (408) 428-2050 FAX: (408) 432-6331

#### International Sales Offices

#### **KOREA**

#### **Linear Technology Korea Branch**

Namsong Building, #505 Itaewon-Dong 260-199 Yongsan-Ku, Seoul

Korea

Phone: 82-2-792-1617 FAX: 82-2-792-1619

#### **SINGAPORE**

#### Linear Technology Pte. Ltd.

507 Yishun Industrial Park A

Singapore 2776 Phone: 65-753-2692 FAX: 65-754-4113

#### **TAIWAN**

#### **Linear Technology Corporation**

Rm. 801, No. 46, Sec. 2 Chung Shan N. Rd. Taipei, Taiwan, R.O.C. Phone: 886-2-521-7575 FAX: 886-2-562-2285

### UNITED KINGDOM

#### Linear Technology (UK) Ltd.

The Coliseum, Riverside Way Camberley, Surrey GU15 3YL

United Kingdom

Phone: 44-1276-677676 FAX: 44-1276-64851

#### World Headquarters

#### **Linear Technology Corporation**

1630 McCarthy Blvd. Milpitas, CA 95035-7487 Phone: (408) 432-1900 FAX: (408) 434-0507

0295

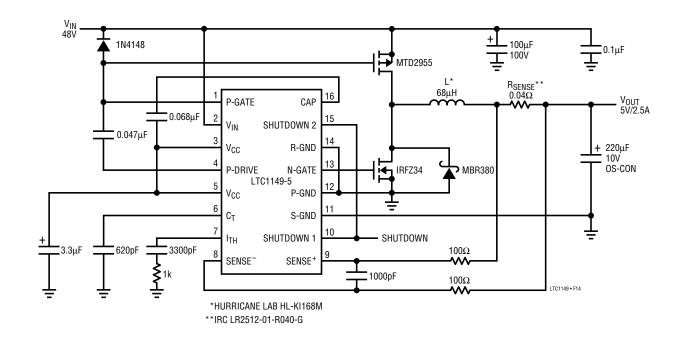

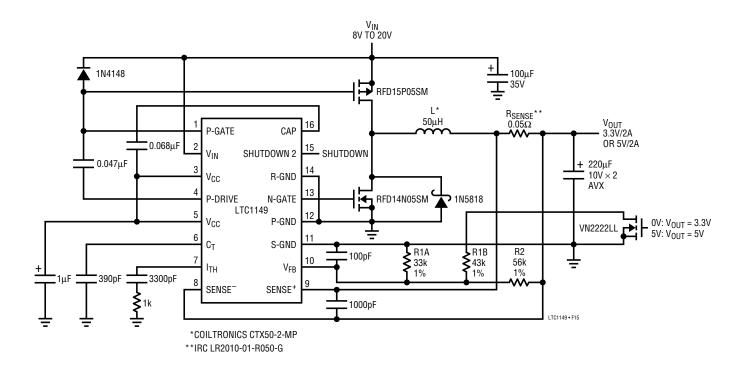

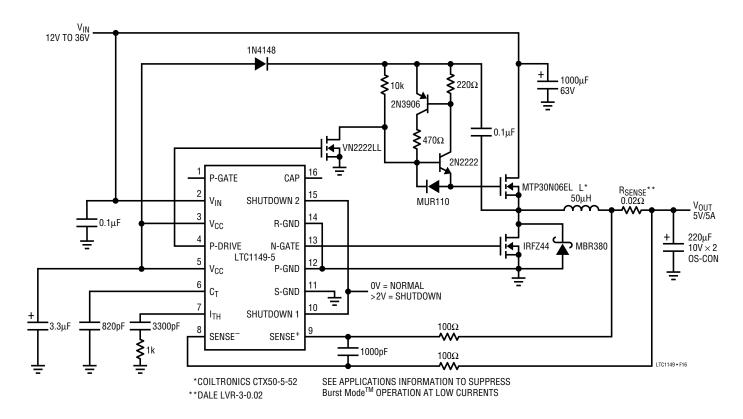

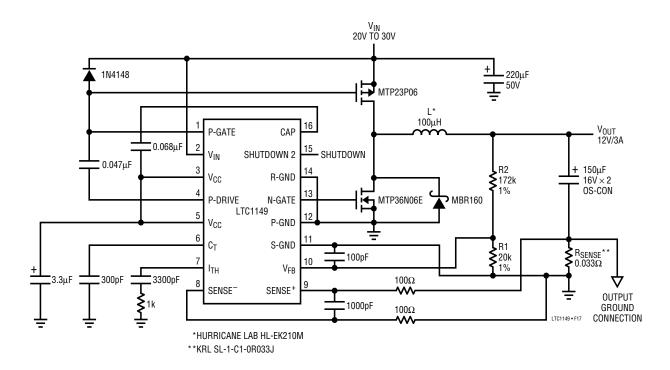

## 5A and 2.5A High Efficiency Switching Regulators

### **FEATURES**

- Wide Input Voltage Range 3V-60V

- Low Quiescent Current—6mA

- Internal 5A Switch (2.5A for LT1071)

- Very Few External Parts Required

- Self-Protected Against Overloads

- Operates in Nearly All Switching Topologies

- Shutdown Mode Draws Only 50µA Supply Current

- Flyback-Regulated Mode has Fully Floating Outputs

- Comes in Standard 5-Pin Packages

- Can be Externally Synchronized (Consult Factory)

### **APPLICATIONS**

- Logic Supply 5V @ 10A

- 5V Logic to ± 15V Op Amp Supply

- Offline Converter up to 200W

- Battery Upconverter

- Power Inverter (+ to -) or (- to +)

- Fully Floating Multiple Outputs

- For Lower Current Applications see LT1072

#### USER NOTE:

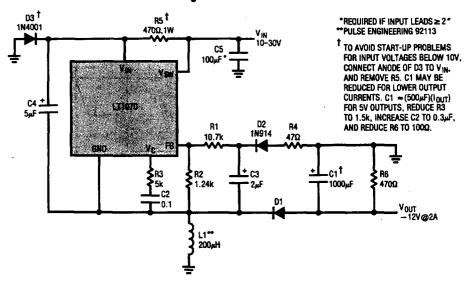

This data sheet is only intended to provide specifications, graphs, and a general functional description of the LT1070/LT1071. Application circuits are included to show the capability of the LT1070/LT1071. A complete design manual (AN-19) should be obtained to assist in developing new designs. This manual contains a comprehensive discussion of both the LT1070 and the external components used with it, as well as complete formulas for calculating the values of these components. The manual can also be used for the LT1071 by factoring in the lower switch current rating. A second application note, AN-25, which details off-line applications is available.

### DESCRIPTION

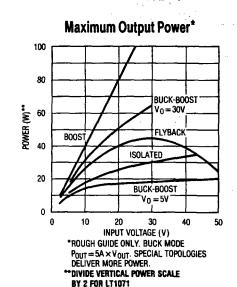

The LT1070 and LT1071 are monolithic high power switching regulators. They can be operated in all standard switching configurations including buck, boost, flyback, forward, inverting and "Cuk". A high current, high efficiency switch is included on the die along with all oscillator, control, and protection circuitry. Integration of all functions allows the LT1070/LT1071 to be built in a standard 5-pin TO-3 or TO-220 power package. This makes it extremely easy to use and provides "bust proof" operation similar to that obtained with 3-pin linear regulators.

The LT1070/LT1071 operates with supply voltages from 3V to 60V, and draws only 6mA quiescent current. It can deliver load power up to 100 watts with no external power devices. By utilizing current-mode switching techniques, it provides excellent AC and DC load and line regulation.

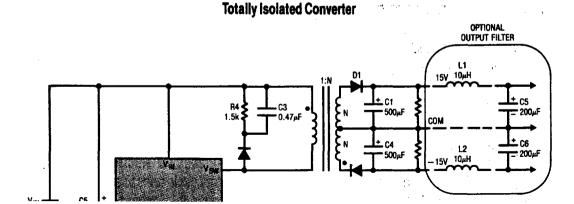

The LT1070/LT1071 has many unique features not found even on the vastly more difficult to use low power control chips presently available. It uses adaptive anti-sat switch drive to allow very wide ranging load currents with no loss in efficiency. An externally activated shutdown mode reduces total supply current to  $50\mu A$  typical for standby operation. Totally isolated and regulated outputs can be generated by using the optional "flyback regulation mode" built into the LT1070/LT1071, without the need for opto-couplers or extra transformer windings.

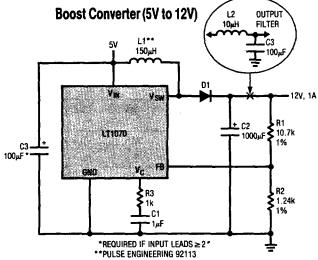

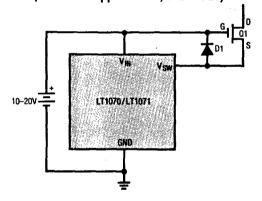

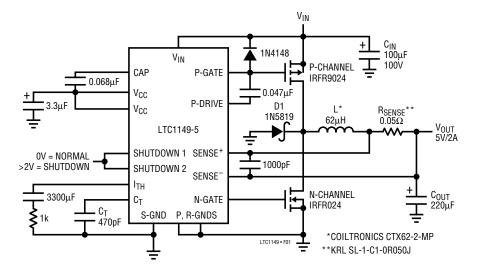

# TYPICAL APPLICATION Boost Converter (5V to 12V)

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                                     |

|----------------------------------------------------|

| LT1070/71HV (See Note 1)                           |

| LT1070/71 (See Note 1)                             |

| Switch Output Voltage                              |

| LT1070/71HV75V                                     |

| LT1070/7165V                                       |

| Feedback Pin Voltage (Transient, 1ms) ± 15V        |

| Operating Junction Temperature Range               |

| LT1070/71HVM, LT1070/71M – 55°C to + 150°C         |

| LT1070/71HVC, LT1070/71C (Oper.) 0°C to + 100°C    |

| LT1070/71HVC, LT1070/71C (Sh. Ckt.) 0°C to + 125°C |

| Storage Temperature Range – 65°C to + 150°C        |

| Lead Temperature (Soldering, 10sec)                |

Note 1: Minimum switch "on" time for the LT1070/LT1071 in current limit is  $\approx 1.0 \mu \text{sec}$ . This limits the maximum input voltage during short circuit conditions, in the buck and inverting modes only, to  $\approx 35 \text{V}$ . Normal (unshorted) conditions are not affected. Mask changes are being implemented which will reduce minimum "on" time to  $\leq 1 \mu \text{sec}$ , increasing maximum short circuit input voltage above 40V. If the present LT1070/LT1071 (contact factory for package date code) is being operated in the buck or inverting mode at high input voltages and short circuit conditions are expected, a resistor must be placed in series with the inductor, as follows:

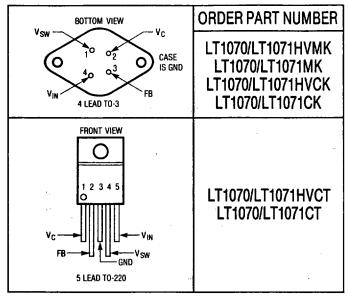

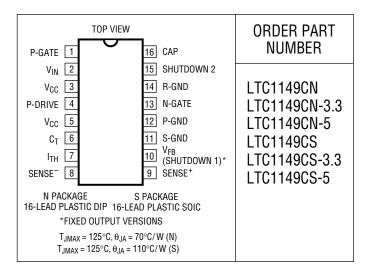

### PACKAGE/ORDER INFORMATION

The value of the resistor is given by:

$$R = \frac{t \bullet f \bullet V_{IN} - Vf}{I_{(LIMIT)}} - R_{L}$$

t = Minimum "on" time of LT1070/LT1071 in current limit, ≈ 1µs

f = Operating frequency (40kHz)

Vf = Forward voltage of external catch diode at I(LIMIT)

$I_{(LIMIT)}$  = Current limit of LT1070 ( $\approx$ 8A), LT1071 ( $\approx$ 4A)

R<sub>L</sub> = Internal series resistance of inductor

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified,  $V_{IN} = 15V$ ,  $V_C = 0.5V$ ,  $V_{FB} = V_{REF}$ , output pin open.

| SYMBOL           | PARAMETER                                   | CONDITIONS                                                         |   | MIN            | TYP            | MAX            | UNITS    |

|------------------|---------------------------------------------|--------------------------------------------------------------------|---|----------------|----------------|----------------|----------|

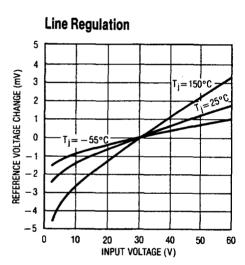

| V <sub>REF</sub> | Reference Voltage                           | Measured at Feedback Pin                                           | • | 1.224<br>1.214 | 1.244<br>1.244 | 1.264<br>1.274 | V        |

| l <sub>B</sub>   | Feedback Input Current                      | V <sub>FB</sub> = V <sub>REF</sub>                                 |   |                | 350            | 750<br>1100    | nA<br>·  |

| gm               | Error Amplifier<br>Transconductance         | $\Delta I_C = \pm 25 \mu A$                                        |   | 3000<br>2400   | 4400           | 6000<br>7000   | μmho     |

|                  | Error Amplifier Source or<br>Sink Current   | V <sub>C</sub> = 1.5V                                              | • | 150<br>120     | 200            | 350<br>400     | μΑ<br>Αμ |

|                  | Error Amplifier Clamp<br>Voltage            | Hi Clamp, V <sub>FB</sub> = 1V<br>Lo Clamp, V <sub>FB</sub> = 1.5V |   | 1.8<br>0.25    | 0.38           | 2.3<br>0.52    | V        |

|                  | Reference Voltage Line<br>Regulation        | 3V≤V <sub>IN</sub> ≤V <sub>MAX</sub>                               | • |                |                | 0.03           | %/V      |

| Av               | Error Amplifier Voltage<br>Gain             | 0.7V≤V <sub>C</sub> ≤1.4V                                          |   | 500            | 800            | 2000           | . V/V    |

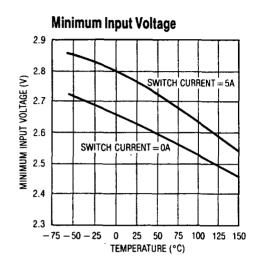

|                  | Minimum Input Voltage                       |                                                                    | • | · · ·          | 2.6            | 3.0            | V        |

| lq               | Supply Current                              | $3V \le V_{IN} \le V_{MAX}$ , $V_C = 0.6V$                         |   |                | 6              | 9              | mA       |

|                  | Control Pin Threshold                       | Duty Cycle = 0                                                     | • | 0.8<br>0.6     | 0.9            | 1.08<br>1.25   | ٧        |

|                  | Normal/Flyback Threshold<br>on Feedback Pin |                                                                    |   | 0.4            | 0.45           | 0.54           | ٧        |

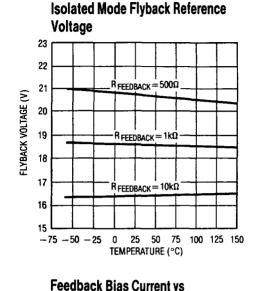

| V <sub>FB</sub>  | Flyback Reference Voltage                   | I <sub>FB</sub> = 50μA                                             | • | 15<br>14       | 16.3           | 17.6<br>18     | ٧        |

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified,  $V_{IN} = 15V$ ,  $V_C = 0.5V$ ,  $V_{FB} = V_{REF}$ , output pin open.

| SYMBOL                               | PARAMETER                                                                  | CONDITIONS                                                                                       | T | MIN             | TYP         | MAX                                      | UNITS      |

|--------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---|-----------------|-------------|------------------------------------------|------------|

| V <sub>FB</sub>                      | Change in Flyback<br>Reference Voltage                                     | 0.05≤I <sub>FB</sub> ≤1mA                                                                        |   | 4.5             | 6.8         | 8.5                                      | ٧          |

|                                      | Flyback Reference Voltage<br>Line Regulation                               | I <sub>FB</sub> = 50µA<br>3V ≤ V <sub>IN</sub> ≤ V <sub>MAX</sub>                                |   |                 | 0.01        | 0.03                                     | %/V        |

|                                      | Flyback Amplifier<br>Transconductance (gm)                                 | $\Delta I_C = \pm 10 \mu A$                                                                      |   | 150             | 300         | 500                                      | μmho       |

|                                      | Flyback Amplifier Source and Sink Current                                  | V <sub>C</sub> =1.5V Source<br>I <sub>FB</sub> =50µA Sink                                        | • | 15<br>25        | 32<br>40    | 70<br>70                                 | μΑ<br>μΑ   |

| BV                                   | Output Switch Breakdown<br>Voltage                                         | 3V ≤ V <sub>IN</sub> ≤ V <sub>MAX</sub> LT1070/LT1071<br>I <sub>SW</sub> = 5mA LT1070HV/LT1071HV | • | 65<br>75        | 90<br>90    |                                          | V          |

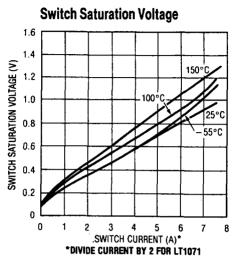

| V <sub>SAT</sub>                     | Output Switch (Note 1) "On" Resistance                                     | LT1070<br>LT1071                                                                                 | • |                 | 0.15<br>0.3 | 0.24<br>0.5                              | Ω          |

|                                      | Control Voltage to Switch Current Transconductance                         | LT1070<br>LT1071                                                                                 |   |                 | 8           |                                          | A/V<br>A/V |

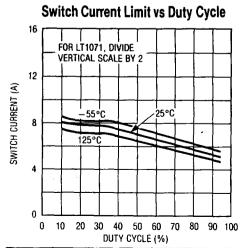

| I <sub>LIM</sub>                     | Switch Current Limit (LT1070)                                              | Duty Cycle ≤ 50% Tj ≥ 25°C  Duty Cycle ≤ 50% Tj < 25°C  Duty Cycle = 80% (Note 2)                | • | 5<br>5<br>4     |             | 10<br>11<br>10                           | A          |

| LIM                                  | Switch Current Limit (LT1071)                                              | Duty Cycle ≤ 50% Tj ≥ 25°C  Duty Cycle ≤ 50% Tj < 25°C  Duty Cycle = 80% (Note 2)                | • | 2.5<br>2.5<br>2 |             | 5<br>5.5<br>5                            | A          |

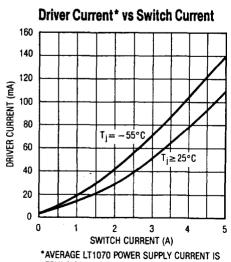

| ΔI <sub>IN</sub><br>ΔI <sub>SW</sub> | Supply Current Increase<br>During Switch On-Time                           |                                                                                                  |   |                 | 25          | 35                                       | mA/A       |

| f                                    | Switching Frequency                                                        |                                                                                                  | • | 35<br>33        | 40          | 45<br>47                                 | kHz        |

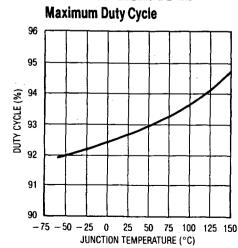

| DC (max)                             | Maximum Switch Duty Cycle                                                  |                                                                                                  |   | 90              | 92          | 97                                       | %          |

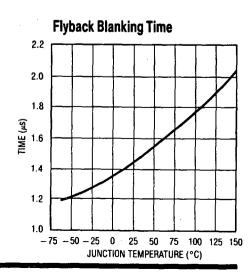

|                                      | Flyback Sense Delay Time                                                   |                                                                                                  |   |                 | 1.5         | 44 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - | μS         |

|                                      | Shutdown Mode<br>Supply Current                                            | $3V \le V_{\text{IN}} \le V_{\text{MAX}}$ $V_{\text{C}} = 0.05V$                                 |   |                 | 100         | 250                                      | ДА         |

|                                      | Shutdown Mode Threshold Voltage es the specifications which apply over the | 3V≤V <sub>IN</sub> ≤V <sub>MAX</sub>                                                             | • | 100<br>50       | 150         | 250<br>300                               | mV<br>mV   |

The denotes the specifications which apply over the full operating temperature range.

Note 1: Measured with  $V_C$  in hi clamp,  $V_{FB} = 0.8V$ .  $I_{SW} = 4A$  for LT1070 and 2A for LT1071.

**Note 2:** For duty cycles (DC) between 50% and 80%, minimum guaranteed switch current is given by  $I_{LIM}$  = 3.33 (2 – DC) for the LT1070 and  $I_{LIM}$  = 1.67 (2 – DC) for the LT1071.

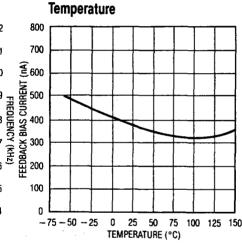

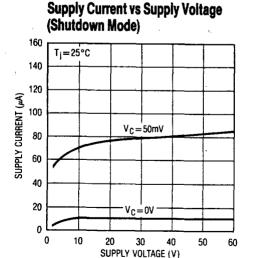

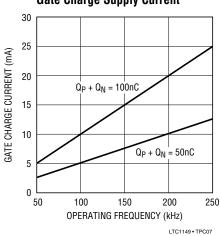

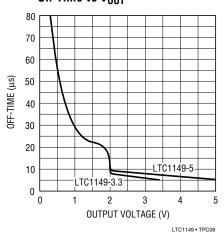

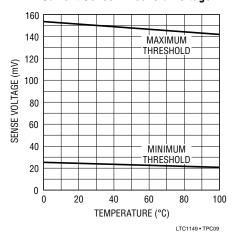

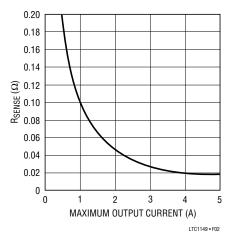

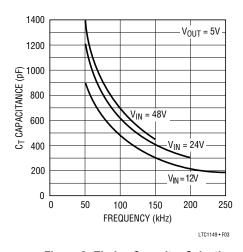

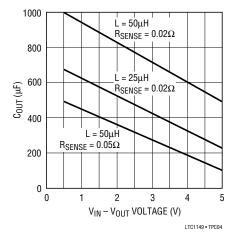

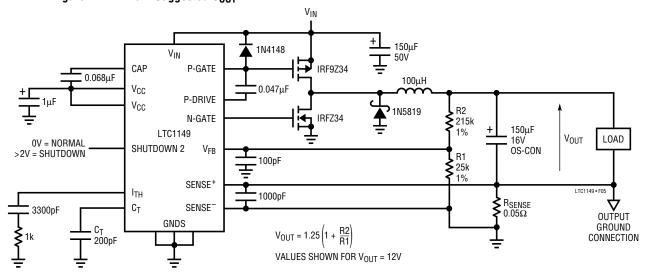

### TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

\*UNDER VERY LOW OUTPUT CURRENT CONDITIONS, DUTY CYCLE FOR MOST CIRCUITS WILL APPROACH 10% OR LESS.

## TYPICAL PERFORMANCE CHARACTERISTICS

20 10 0

30 40 50 60

SWITCH VOLTAGE (V)

70 80 90 100 0

VC PIN VOLTAGE (V)

FREQUENCY (Hz)

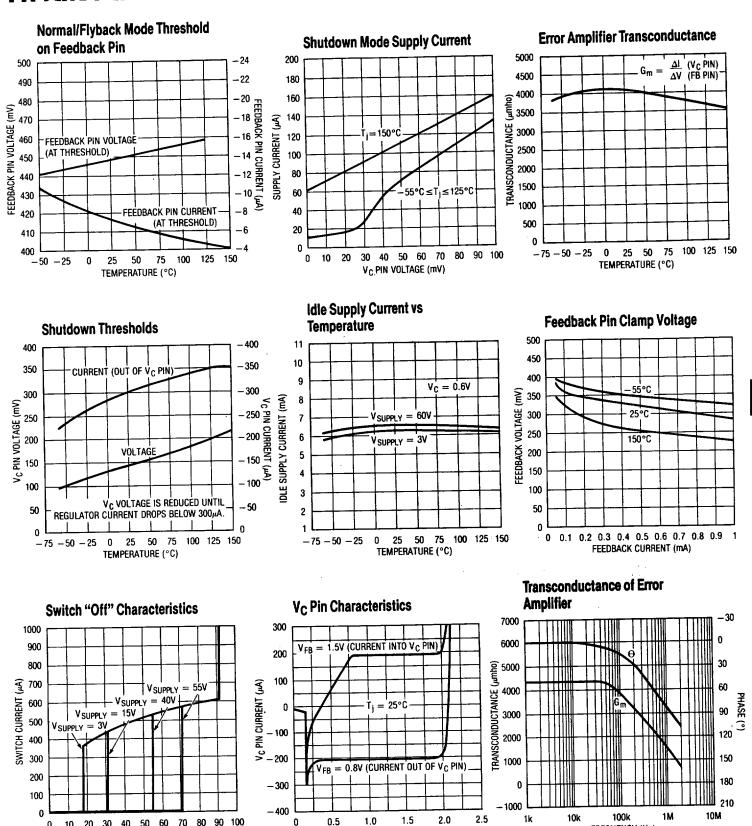

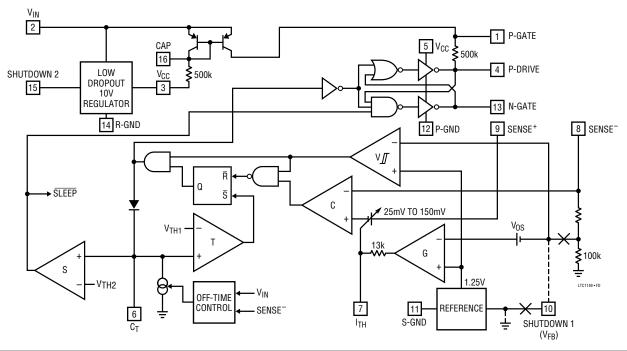

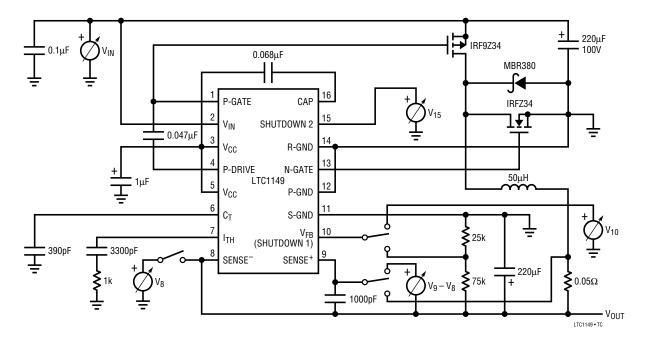

### **BLOCK DIAGRAM**

### LT1070/LT1071 OPERATION

The LT1070/LT1071 is a current mode switcher. This means that switch duty cycle is directly controlled by switch current rather than by output voltage. Referring to the block diagram, the switch is turned "on" at the start of each oscillator cycle. It is turned "off" when switch current reaches a predetermined level. Control of output voltage is obtained by using the output of a voltage sensing error amplifier to set current trip level. This technique has several advantages. First, it has immediate response to input voltage variations, unlike ordinary switchers which have notoriously poor line transient response. Second, it reduces the 90° phase shift at midfrequencies in the energy storage inductor. This greatly simplifies closed loop frequency compensation under widely varying input voltage or output load conditions. Finally, it allows simple pulse-by-pulse current limiting to provide maximum switch protection under output overload or short conditions. A low-dropout internal regulator provides a 2.3V supply for all internal circuitry on the LT1070/LT1071. This low-dropout design allows input voltage to vary from 3V to 60V with virtually no change in device performance. A 40kHz oscillator is the basic clock for all internal timing. It turns "on" the output switch via the logic and driver circuitry. Special adaptive anti-sat circuitry detects onset of saturation in the power switch and adjusts driver current instantaneously to limit switch saturation. This minimizes driver dissipation and provides very rapid turn-off of the switch.

A 1.2V bandgap reference biases the positive input of the error amplifier. The negative input is brought out for output voltage sensing. This feedback pin has a second function; when pulled low with an external resistor, it programs the LT1070/LT1071 to disconnect the main error amplifier output

### LT1070/LT1071 OPERATION

and connects the output of the flyback amplifier to the comparator input. The LT1070/LT1071 will then regulate the value of the flyback pulse with respect to the supply voltage. This flyback pulse is directly proportional to output voltage in the traditional transformer coupled flyback topology regulator. By regulating the amplitude of the flyback pulse, the output voltage can be regulated with no direct connection between input and output. The output is fully floating up to the breakdown voltage of the transformer windings. Multiple floating outputs are easily obtained with additional windings. A special delay network inside the LT1070/LT1071 ignores the leakage inductance spike at the leading edge of the flyback pulse to improve output regulation.

The error signal developed at the comparator input is brought out externally. This pin (V<sub>C</sub>) has four different functions. It is used for frequency compensation, current limit adjustment, soft starting, and total regulator shutdown. During normal regulator operation this pin sits at a voltage between 0.9V (low output current) and 2.0V (high output current). The error amplifiers are current output (gm) types, so this voltage can be externally clamped for adjusting current limit. Likewise, a capacitor coupled external clamp will provide soft start. Switch duty cycle goes to zero if the V<sub>C</sub> pin is pulled to ground through a diode, placing the LT1070/LT1071 in an idle mode. Pulling the V<sub>C</sub> pin below 0.15V causes total regulator shutdown, with only 50<sub>µ</sub>A supply current for shutdown circuitry biasing. See AN-19 for full application details.

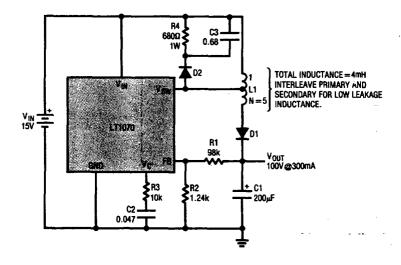

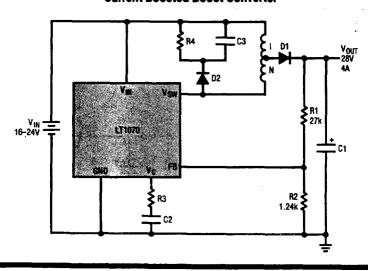

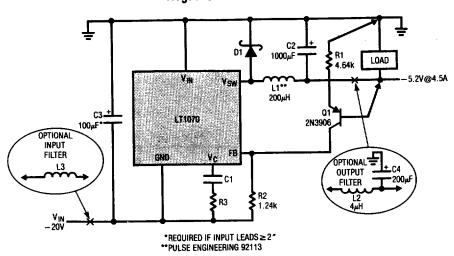

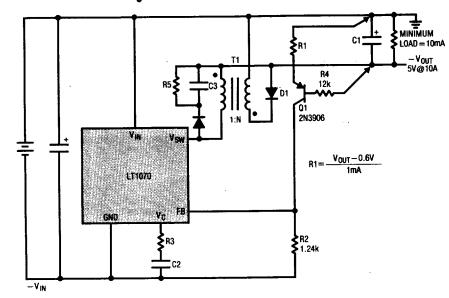

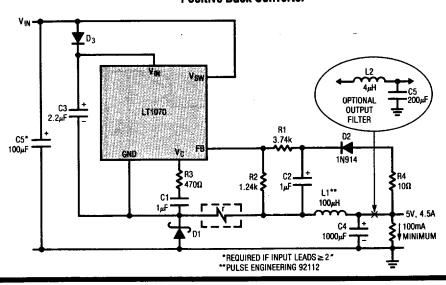

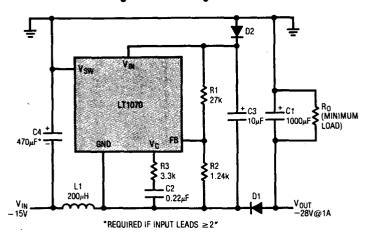

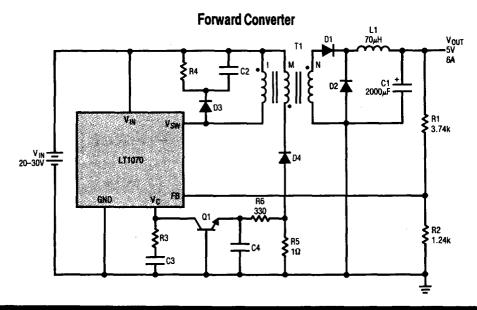

## TYPICAL APPLICATIONS (Note that maximum output currents are divided by 2 for LT1071.)

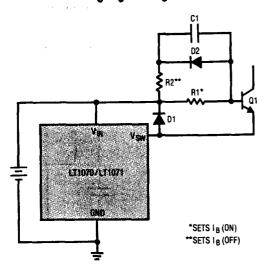

## Driving High Voltage FET (for Offline Applications, See AN-25)

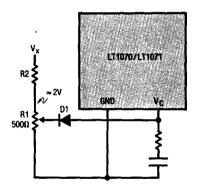

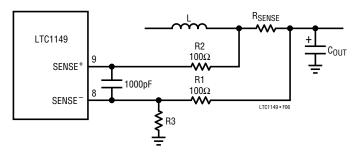

### **External Current Limit**

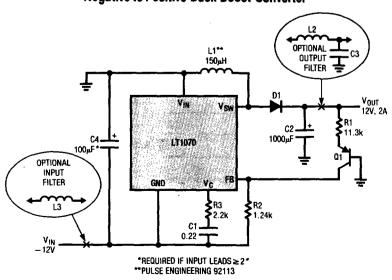

#### **Negative to Positive Buck-Boost Converter**

#### **External Current Limit**

## LT1070/LT1071

### TYPICAL APPLICATIONS

### Positive to Negative Buck-Boost Converter

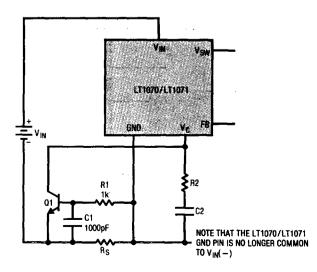

### **Voltage Boosted Boost Converter**

#### **Current Boosted Boost Converter**

### **Negative Buck Converter**

### **Negative Current Boosted Buck Converter**

#### **Positive Buck Converter**

### **Negative Boost Regulator**

### **Driving High Voltage NPN**

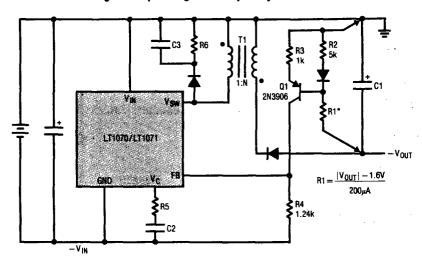

### **Negative Input-Negative Output Flyback Converter**

#### **Positive Current Boosted Buck Converter** 470Ω R6 0.47µF 470Ω C6 0.002 V<sub>BN</sub> N ≈ 0.25 LT1070 D1 1.24k FB C5 100µF R3 680Ω Ç4 R5 0.01µF COMP 200pl 0.33 V<sub>OUT</sub> 5V@10A C2 5k 5000μF

\*REQUIRED IF INPUT LEADS ≥ 2"

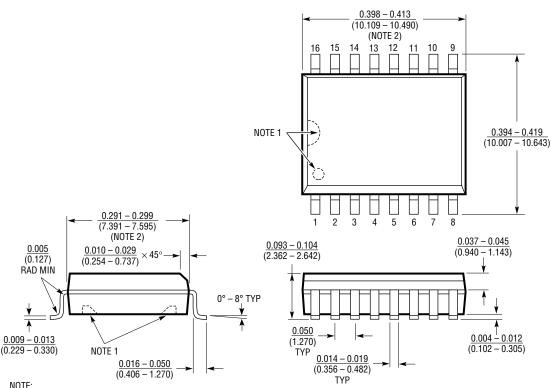

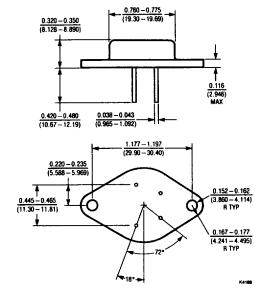

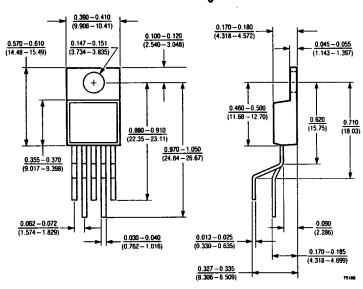

## PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

### TO-3 Type Metal Can (Steel) K Package

### TO-220 Type Plastic T Package

|                      | TJMAX  | θJC   | θJA    |

|----------------------|--------|-------|--------|

| LT1070MK, LT1070HVMK | 150°C  | 2°C/W | 35°C/W |

| LT1070CK, LT1070HVCK | 100°C. | 2°CW  | 35°C/W |

| LT1071MK, LT1071HVMK | 150°C  | 4°C/W | 35°C/W |

| LT1071CK, LT1071HVCK | 100°C  | 4°C/W | 35°C/W |

|                      | TJMAX | θJC   | θJA    |

|----------------------|-------|-------|--------|

| LT1070CT, LT1070HVCT | 100°C | 2°C/W | 75°C/W |

| LT1071CT, LT1071HVCT | 100°C | 4°CW  | 75°C/W |

## 5V Step-Down Switching Regulator

### **FEATURES**

- Fixed 5V Output

- 2A On-Board Switch

- 100kHz Switching Frequency

- 2% Output Voltage Tolerance Over Temperature

- Greatly Improved Dynamic Behavior

- Available in Low Cost 5-Lead Package

- Only 9.5mA Quiescent Current

- Operates Up to 60V Input

### **APPLICATIONS**

- 5V Output Buck Converter

- Tapped Inductor Buck Converter with 4A Output at 5V

- Positive-to-Negative Converter

### DESCRIPTION

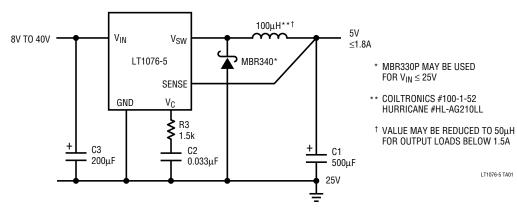

The LT1076-5 is a 2A fixed 5V output monolithic bipolar switching regulator which requires only a few external parts for normal operation. The power switch, all oscillator and control circuitry, all current limit components, and an output monitor are included on the chip. The topology is a classic positive "buck" configuration but several design innovations allow this device to be used as a positive-to-negative converter, a negative boost converter, and as a flyback converter. The switch output is specified to swing 40V below ground, allowing the LT1076-5 to drive a tapped inductor in the buck mode with output currents up to 4A.

The LT1076-5 uses a true analog multiplier in the feedback loop. This makes the device respond nearly instantaneously to input voltage fluctuations and makes loop gain independent of input voltage. As a result, dynamic behavior of the regulator is significantly improved over previous designs.

On-chip pulse by pulse current limiting makes the LT1076-5 nearly bust-proof for output overloads or shorts. The input voltage range as a buck converter is 8V to 60V, but a self-boot feature allows input voltages as low as 5V in the inverting and boost configurations.

The LT1076-5 is available in a low cost 5-lead T0-220 package with frequency pre-set at 100kHz and current limit at 2.6A. See Application Note 44 for design details.

### TYPICAL APPLICATION

#### **Basic Positive Buck Converter**

### **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage                                |      |

|----------------------------------------------|------|

| LT1076-5                                     | 45V  |

| LT1076HV-5                                   | 64V  |

| Switch Voltage with Respect to Input Voltage |      |

| LT1076-5                                     | 64V  |

| LT1076HV-5                                   | 75V  |

| Switch Voltage with Respect to Ground Pin    |      |

| (V <sub>SW</sub> Negative)                   |      |

| LT1076-5 (Note 5)                            | 35V  |

| LT1076HV-5 (Note 5)                          | 45V  |

| Sense Pin Voltage –2V,                       | 10V  |

| Maximum Operating Ambient Temperature Range  |      |

| LT1076C-5, LT1076HVC-5 0°C to 7              | 70°C |

| LT1076I-5, LT1076HVI-540°C to 8              | 35°C |

| Maximum Operating Junction Temperature Range |      |

| LT1076C-5, LT1076HVC-5 0°C to 12             | 25°C |

| LT1076I-5, LT1076HVI-540°C to 12             | 25°C |

| Maximum Storage Temperature −65°C to 15      | 50°C |

| Lead Temperature (Soldering, 10 sec)30       | )0°C |

|                                              |      |

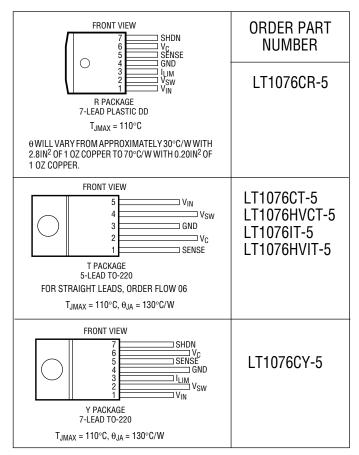

### PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

## **ELECTRICAL CHARACTERISTICS** $T_J = 25^{\circ}C$ , $V_{IN} = 25V$ , unless otherwise noted.

| PARAMETER                     | CONDITIONS                                                                                                 |   | MIN | TYP               | MAX             | UNITS          |

|-------------------------------|------------------------------------------------------------------------------------------------------------|---|-----|-------------------|-----------------|----------------|

| Switch "On" Voltage (Note 1)  | I <sub>SW</sub> = 0.5A<br>I <sub>SW</sub> = 2A                                                             | • |     |                   | 1.2<br>1.7      | V              |

| Switch "Off" Leakage          | $V_{IN} = 25V, V_{SW} = 0$<br>$V_{IN} = V_{MAX}, V_{SW} = 0$ (Note 6)                                      |   |     |                   | 150<br>250      | μA<br>μA       |

| Supply Current (Note 2)       | $V_{OUT}$ = 5.5V, $V_{IN} \le 40V$<br>$40V < V_{IN} < 60V$<br>$V_{SHDN}$ = 0.1V (Device Shutdown) (Note 8) | • |     | 8.5<br>9.0<br>140 | 11<br>12<br>300 | mA<br>mA<br>μA |

| Minimum Supply Voltage        | Normal Mode<br>Start-Up Mode (Note 3)                                                                      | • |     | 7.3<br>3.5        | 8.0<br>4.8      | V              |

| Switch Current Limit (Note 4) | I <sub>LIM</sub> = Open<br>R <sub>LIM</sub> = 10k (Note 9)<br>R <sub>LIM</sub> = 7k (Note 9)               | • | 2   | 2.6<br>1.8<br>1.2 | 3.2             | A<br>A<br>A    |

| Maximum Duty Cycle            |                                                                                                            | • | 85  | 90                |                 | %              |

## **ELECTRICAL CHARACTERISTICS** $T_J = 25^{\circ}C$ , $V_{IN} = 25V$ , unless otherwise noted.

| PARAMETER                                 | CONDITIONS                                                                                                          |   | MIN        | TYP          | MAX        | UNITS             |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---|------------|--------------|------------|-------------------|

| Switching Frequency                       | $T_J \le 125$ °C $V_{OUT} = V_{SENSE} = 0V$ (Note 4)                                                                | • | 90<br>85   | 100<br>20    | 110<br>120 | kHz<br>kHz<br>kHz |

| Switching Frequency Line Regulation       | $8V \le V_{IN} \le V_{MAX}$ (Note 7)                                                                                | • |            | 0.03         | 0.1        | %/V               |

| Error Amplifier Voltage Gain (Note 7)     | $1V \le V_C \le 4V$                                                                                                 |   |            | 2000         |            | V/V               |

| Error Amplifier Transconductance (Note 7) |                                                                                                                     |   | 3700       | 5000         | 8000       | μmho              |

| Error Amplifier Source and Sink Current   | Source ( $V_{SENSE} = 4.5V$ )<br>Sink ( $V_{SENSE} = 5.5V$ )                                                        |   | 100<br>0.7 | 140<br>1.0   | 225<br>1.6 | μA<br>mA          |

| Sense Pin Divider Resistance              |                                                                                                                     |   | 3          | 5            | 8          | kΩ                |

| Sense Voltage                             | V <sub>C</sub> = 2V                                                                                                 | • | 4.85       | 5            | 5.15       | V                 |

| Output Voltage Tolerance                  | V <sub>OUT</sub> (Nominal) = 5V<br>All Conditions of Input Voltage, Output Voltage,<br>Temperature and Load Current | • |            | ±0.5<br>±1.0 | ±2<br>±3   | %<br>%            |

| Output Voltage Line Regulation            | $8V \le V_{IN} \le V_{MAX}$ (Note 6)                                                                                | • |            | 0.005        | 0.02       | %/V               |

| V <sub>C</sub> Voltage at 0% Duty Cycle   | Over Temperature                                                                                                    | • |            | 1.5<br>-4.0  |            | V<br>mV/°C        |

| Multiplier Reference Voltage              |                                                                                                                     |   |            | 24           |            | V                 |

| Shutdown Pin Current                      | $V_{SHDN} = 5V$<br>$V_{SHDN} \le V_{THRESHOLD} (\cong 2.5V)$                                                        |   | 5          | 10           | 20<br>50   | μA<br>μA          |

| Shutdown Thresholds                       | Switch Duty Cycle = 0<br>Fully Shut Down                                                                            |   | 2.2<br>0.1 | 2.45<br>0.30 | 2.7<br>0.5 | V                 |

| Thermal Resistance Junction to Case       |                                                                                                                     |   |            |              | 4          | °C/W              |

The ● denotes specifications which apply over the full operating temperature range.

**Note 1:** To calculate maximum switch "on" voltage at currents between low and high conditions, a linear interpolation may be used.

**Note 2:** A sense pin voltage ( $V_{SENSE}$ ) of 5.5V forces the  $V_C$  pin to its low clamp level and the switch duty cycle to zero. This approximates the zero load condition where duty cycle approaches zero.

**Note 3:** Total voltage from  $V_{IN}$  pin to ground pin must be  $\geq$  8V after start-up for proper regulation. For  $T_A < 25^{\circ}C$ , limit = 5V.

**Note 4:** Switch frequency is internally scaled down when the sense pin voltage is less than 2.6V to avoid extremely short switch on times. During current limit testing,  $V_{SENSE}$  is adjusted to give a minimum switch on time of  $1\mu s$ .

Note 5: Switch to input voltage limitation must also be observed.

**Note 6:**  $V_{MAX} = 40V$  for the LT1076-5 and 60V for the LT1076HV-5.

**Note 7:** Error amplifier voltage gain and transconductance are specified relative to the internal feedback node. To calculate gain and transconductance from the Sense pin (Output) to the  $V_{C}$  pin, multiply by 0.44

Note 8: Does not include switch leakage.

Note 9:

$$I_{LIM} \approx \frac{R_{LIM} - 1k}{5k}$$

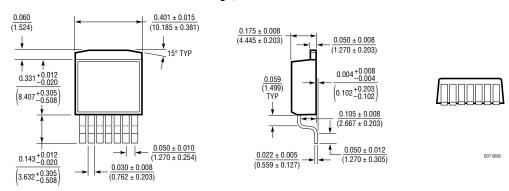

## PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

#### R Package, 7-Lead Plastic DD

#### T Package, 5-Lead TO-220

#### Y Package, 7-Lead TO-220

## 12V CMOS Voltage Converter

### **FEATURES**

- 1.5V to 12V Operating Supply Voltage Range

- 13V Absolute Maximum Rating

- 200µA Maximum No Load Supply Current at 5V

- Boost Pin (Pin 1) for Higher Switching Frequency

- 97% Minimum Open Circuit Voltage Conversion Efficiency

- 95% Minimum Power Conversion Efficiency

- $I_S = 1.5\mu A$  with 5V Supply When OSC Pin = 0V or V<sup>+</sup>

- High Voltage Upgrade to ICL7660/LTC1044

### **APPLICATIONS**

- Conversion of 10V to ±10V Supplies

- Conversion of 5V to ±5V Supplies

- Precise Voltage Division: V<sub>OLIT</sub> = V<sub>IN</sub>/2 ±20ppm

- Voltage Multiplication: V<sub>OUT</sub> = ±nV<sub>IN</sub>

- Supply Splitter: V<sub>OUT</sub> = ±V<sub>S</sub>/2

- Automotive Applications

- Battery Systems with 9V Wall Adapters/Chargers

### DESCRIPTION

The LTC1044A is a monolithic CMOS switched-capacitor voltage converter. It plugs in for ICL7660/LTC1044 in applications where higher input voltage (up to 12V) is needed. The LTC1044A provides several conversion functions without using inductors. The input voltage can be inverted ( $V_{OUT} = -V_{IN}$ ), doubled ( $V_{OUT} = 2V_{IN}$ ), divided ( $V_{OUT} = V_{IN}/2$ ) or multiplied ( $V_{OUT} = \pm nV_{IN}$ ).

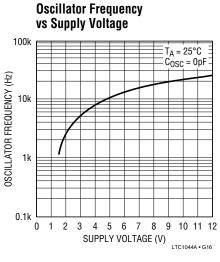

To optimize performance in specific applications, a boost function is available to raise the internal oscillator frequency by a factor of 7. Smaller external capacitors can be used in higher frequency operation to save board space. The internal oscillator can also be disabled to save power. The supply current drops to  $1.5\mu A$  at 5V input when the OSC pin is tied to GND or V<sup>+</sup>.

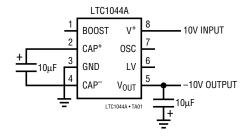

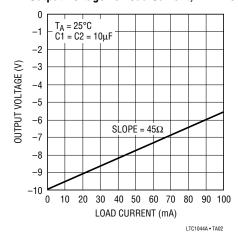

### TYPICAL APPLICATION

#### Generating – 10V from 10V

#### Output Voltage vs Load Current, V+ = 10V

### **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                         |                               |

|----------------------------------|-------------------------------|

| Supply Voltage                   | 13V                           |

| Input Voltage on Pins 1, 6 and 7 | 7                             |

| (Note 2)                         | $-0.3V < V_{IN} < V^+ + 0.3V$ |

| Current into Pin 6               | 20μΑ                          |

| Output Short-Circuit Duration    |                               |

| V <sup>+</sup> ≤ 6.5V            | Continuous                    |

| Operating Temperature Range      |                               |

| LTC1044AC                        | 0°C to 70°C                   |

| LTC1044AI                        | 40°C to 85°C                  |

| Storage Temperature Range        |                               |

| Lead Temperature (Soldering, 1   | 0 sec) 300°C                  |

|                                  |                               |

### PACKAGE/ORDER INFORMATION

| BOOST 1                                            | ORDER PART<br>NUMBER    |                            |  |  |  |

|----------------------------------------------------|-------------------------|----------------------------|--|--|--|

| CAP <sup>+</sup> 2<br>GND 3<br>CAP <sup>-</sup> 4  | 7 osc<br>6 LV<br>5 Vout | LTC1044ACN8<br>LTC1044AIN8 |  |  |  |

| N8 PAC<br>8-LEAD PL/<br>T <sub>JMAX</sub> = 110°C, |                         |                            |  |  |  |

| TOP V                                              | 8 V+                    | ORDER PART<br>NUMBER       |  |  |  |

| CAP <sup>+</sup> 2<br>GND 3                        | 7 OSC<br>6 LV           | LTC1044ACS8<br>LTC1044AIS8 |  |  |  |

| CAP- 4                                             | 5 V <sub>OUT</sub>      | S8 PART MARKING            |  |  |  |

| S8 PAC<br>8-LEAD PLA<br>T <sub>JMAX</sub> = 110°C, | 1044A<br>1044AI         |                            |  |  |  |

Consult factory for Military grade parts

## **ELECTRICAL CHARACTERISTICS** $V^+ = 5V$ , $C_{OSC} = 0pF$ , $T_A = 25^{\circ}C$ , See Test Circuit, unless otherwise noted.

| SYMBOL           | PARAMETER                            | CONDITIONS                                                                                            |   | MIN    | TC1044A<br>TYP | C<br>MAX          | MIN    | TC1044 <i>P</i><br>Typ | MAX               | UNITS       |

|------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------|---|--------|----------------|-------------------|--------|------------------------|-------------------|-------------|

| I <sub>S</sub>   | Supply Current                       | $R_L = \infty$ , Pins 1 and 7, No Connection $R_L = \infty$ , Pins 1 and 7, No Connection, $V^+ = 3V$ |   |        | 60<br>15       | 200               |        | 60<br>15               | 200               | μA<br>μA    |

|                  | Minimum Supply Voltage               | R <sub>L</sub> = 10k                                                                                  | • | 1.5    |                |                   | 1.5    |                        |                   | V           |

|                  | Maximum Supply Voltage               | R <sub>L</sub> = 10k                                                                                  | • |        |                | 12                |        |                        | 12                | V           |

| R <sub>OUT</sub> | Output Resistance                    | $I_L = 20 \text{mA}, f_{OSC} = 5 \text{kHz}$<br>$V^+ = 2V, I_L = 3 \text{mA}, f_{OSC} = 1 \text{kHz}$ | • |        |                | 100<br>120<br>310 |        |                        | 100<br>130<br>325 | Ω<br>Ω<br>Ω |

| f <sub>OSC</sub> | Oscillator Frequency                 | V <sup>+</sup> = 5V, (Note 3)<br>V <sup>+</sup> = 2V                                                  | • | 5<br>1 |                |                   | 5<br>1 |                        |                   | kHz<br>kHz  |

| P <sub>EFF</sub> | Power Efficiency                     | $R_L = 5k$ , $f_{OSC} = 5kHz$                                                                         |   | 95     | 98             |                   | 95     | 98                     |                   | %           |

|                  | Voltage Conversion Efficiency        | R <sub>L</sub> = ∞                                                                                    |   | 97     | 99.9           |                   | 97     | 99.9                   |                   | %           |

|                  | Oscillator Sink or Source<br>Current | V <sub>OSC</sub> = 0V or V <sup>+</sup><br>Pin 1 (B00ST) = 0V<br>Pin 1 (B00ST) = V <sup>+</sup>       | • |        |                | 3<br>20           |        |                        | 3<br>20           | μA<br>μA    |

The  $\bullet$  denotes specifications which apply over the full operating temperature range; all other limits and typicals  $T_A = 25^{\circ}C$ .

**Note 1:** Absolute maximum ratings are those values beyond which the life of a device may be impaired.

**Note 2:** Connecting any input terminal to voltages greater than V<sup>+</sup> or less than ground may cause destructive latch-up. It is recommended that no

inputs from sources operating from external supplies be applied prior to power-up of the LTC1044A.

**Note 3:**  $f_{OSC}$  is tested with  $C_{OSC} = 100$ pF to minimize the effects of test fixture capacitance loading. The 0pF frequency is correlated to this 100pF test point, and is intended to simulate the capacitance at pin 7 when the device is plugged into a test socket and no external capacitor is used.

## TYPICAL PERFORMANCE CHARACTERISTICS Using the Test Circuit

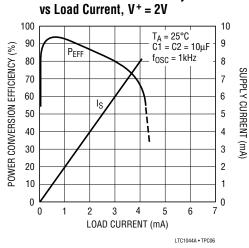

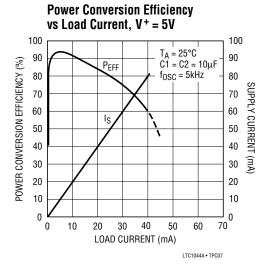

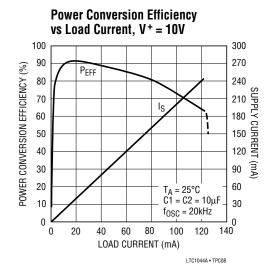

**Power Conversion Efficiency**

## TYPICAL PERFORMANCE CHARACTERISTICS Using the Test Circuit

# **TEST CIRCUIT**

# APPLICATIONS INFORMATION

#### **Theory of Operation**

To understand the theory of operation of the LTC1044A, a review of a basic switched-capacitor building block is helpful.

In Figure 1, when the switch is in the left position, capacitor C1 will charge to voltage V1. The total charge on C1 will be q1 = C1V1. The switch then moves to the right, discharging C1 to voltage V2. After this discharge time, the charge on C1 is q2 = C1V2. Note that charge has been transferred from the source, V1, to the output, V2. The amount of charge transferred is:

$$\Delta q = q1 - q2 = C1(V1 - V2)$$

If the switch is cycled f times per second, the charge transfer per unit time (i.e., current) is:

$$I = f \times \Delta q = f \times C1(V1 - V2)$$

Figure 1. Switched-Capacitor Building Block

Rewriting in terms of voltage and impedance equivalence,

$$I = \frac{V1 - V2}{1/(f \times C1)} = \frac{V1 - V2}{R_{EQUIV}}$$

A new variable,  $R_{EQUIV}$ , has been defined such that  $R_{EQUIV} = 1/(f \times C1)$ . Thus, the equivalent circuit for the switched-capacitor network is as shown in Figure 2.

Figure 2. Switched-Capacitor Equivalent Circuit

Examination of Figure 3 shows that the LTC1044A has the same switching action as the basic switched-capacitor building block. With the addition of finite switch-on resistance and output voltage ripple, the simple theory although not exact, provides an intuitive feel for how the device works.

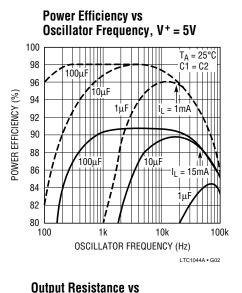

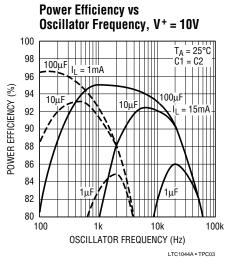

For example, if you examine power conversion efficiency as a function of frequency (see typical curve), this simple theory will explain how the LTC1044A behaves. The loss, and hence the efficiency, is set by the output impedance. As frequency is decreased, the output impedance will eventually be dominated by the  $1/(f \times C1)$  term, and power efficiency will drop. The typical curves for Power Efficiency vs Frequency show this effect for various capacitor values.

Note also that power efficiency decreases as frequency goes up. This is caused by internal switching losses which occur due to some finite charge being lost on each switching cycle. This charge loss per unit cycle, when multiplied by the switching frequency, becomes a current loss. At high frequency this loss becomes significant and the power efficiency starts to decrease.

Figure 3. LTC1044A Switched-Capacitor Voltage Converter Block Diagram

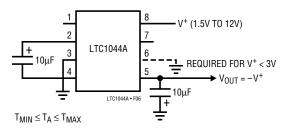

# LV (Pin 6)

The internal logic of the LTC1044A runs between V $^+$  and LV (pin 6). For V $^+$  greater than or equal to 3V, an internal switch shorts LV to GND (pin 3). For V $^+$  less than 3V, the LV pin should be tied to GND. For V $^+$  greater than or equal to 3V, the LV pin can be tied to GND or left floating.

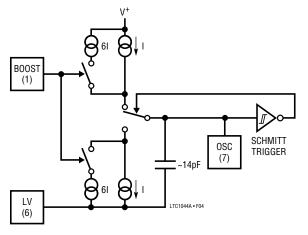

# OSC (Pin 7) and Boost (Pin 1)

The switching frequency can be raised, lowered, or driven from an external source. Figure 4 shows a functional diagram of the oscillator circuit.

By connecting the boost pin (pin 1) to  $V^+$ , the charge and discharge current is increased and hence, the frequency is increased by approximately 7 times. Increasing the

frequency will decrease output impedance and ripple for higher load currents.

Loading pin 7 with more capacitance will lower the frequency. Using the boost (pin 1) in conjunction with external capacitance on pin 7 allows user selection of the frequency over a wide range.

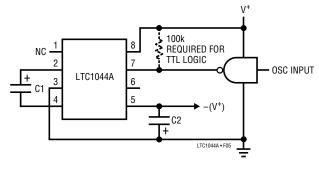

Driving the LTC1044A from an external frequency source can be easily achieved by driving pin 7 and leaving the boost pin open as shown in Figure 5. The output current from pin 7 is small (typically  $0.5\mu A$ ) so a logic gate is capable of driving this current. The choice of using a CMOS logic gate is best because it can operate over a wide supply voltage range (3V to 15V) and has enough voltage swing to drive the internal Schmitt trigger shown in Figure 4. For 5V applications, a TTL logic gate can be used by simply adding an external pull-up resistor (see Figure 5).

Figure 4. Oscillator

Figure 5. External Clocking

#### **Capacitor Selection**

External capacitors C1 and C2 are not critical. Matching is not required, nor do they have to be high quality or tight tolerance. Aluminum or tantalum electrolytics are excellent choices with cost and size being the only consideration.

#### **Negative Voltage Converter**

Figure 6 shows a typical connection which will provide a negative supply from an available positive supply. This circuit operates over full temperature and power supply ranges *without* the need of any external diodes. The LV pin (pin 6) is shown grounded, but for  $V^+ \ge 3V$  it may be "floated", since LV is internally switched to ground (pin 3) for  $V^+ \ge 3V$ .

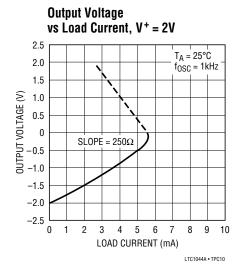

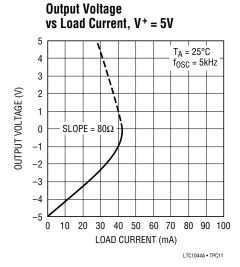

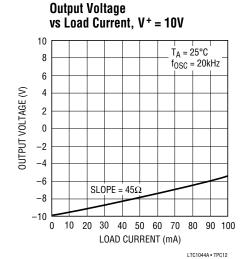

The output voltage (pin 5) characteristics of the circuit are those of a nearly ideal voltage source in series with an  $80\Omega$  resistor. The  $80\Omega$  output impedance is composed of two terms:

- 1. The equivalent switched-capacitor resistance (see Theory of Operation).

- 2. A term related to the on-resistance of the MOS switches.

At an oscillator frequency of 10kHz and C1 =  $10\mu F$ , the first term is:

$$\begin{split} R_{EQUIV} &= \frac{1}{(f_{OSC}/2) \times C1} \\ &= \frac{1}{5 \times 10^3 \times 10 \times 10^{-6}} = 20 \Omega \end{split}$$

Notice that the above equation for  $R_{EQUIV}$  is *not* a capacitive reactance equation  $(X_C = 1/\omega C)$  and does not contain a  $2\pi$  term.

Figure 6. Negative Voltage Converter

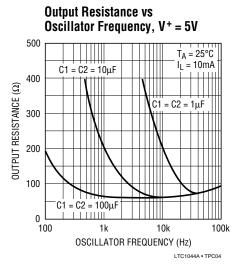

The exact expression for output resistance is extremely complex, but the dominant effect of the capacitor is clearly shown on the typical curves of Output Resistance and Power Efficiency vs Frequency. For C1 = C2 =  $10\mu F$ , the output impedance goes from  $60\Omega$  at  $f_{OSC}$  = 10kHz to  $200\Omega$  at  $f_{OSC}$  = 1kHz. As the  $1/(f \times C)$  term becomes large compared to the switch-on resistance term, the output resistance is determined by  $1/(f \times C)$  only.

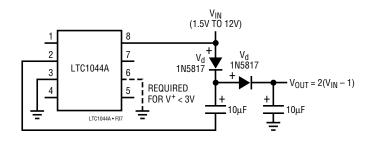

#### **Voltage Doubling**

Figure 7 shows a two-diode capacitive voltage doubler. With a 5V input, the output is 9.93V with no load and 9.13V with a 10mA load. With a 10V input, the output is 19.93V with no load and 19.28V with a 10mA load.

Figure 7. Voltage Doubler

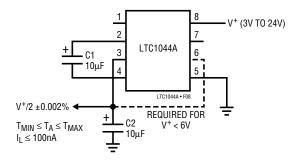

#### **Ultra-Precision Voltage Divider**

An ultra-precision voltage divider is shown in Figure 8. To achieve the 0.0002% accuracy indicated, the load current should be kept below 100nA. However, with a slight loss in accuracy the load current can be increased.

Figure 8. Ultra-Precision Voltage Divider

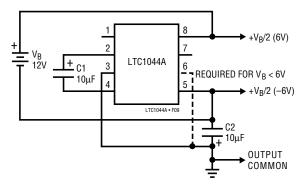

#### **Battery Splitter**

A common need in many systems is to obtain (+) and (-) supplies from a single battery or single power supply system. Where current requirements are small, the circuit shown in Figure 9 is a simple solution. It provides symmetrical  $\pm$  output voltages, both equal to one half input voltage. The output voltages are both referenced to pin 3

Figure 9. Battery Splitter

(output common). If the input voltage between pin 8 and pin 5 is less than 6V, pin 6 should also be connected to pin 3 as shown by the dashed line.

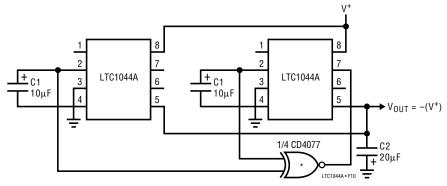

#### **Paralleling for Lower Output Resistance**

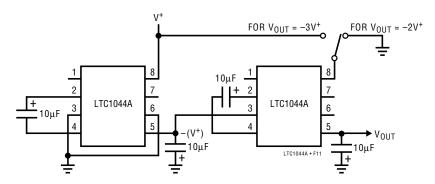

Additional flexibility of the LTC1044A is shown in Figures 10 and 11.

Figure 10 shows two LTC1044As connected in parallel to provide a lower effective output resistance. If, however, the output resistance is dominated by  $1/(f \times C1)$ , increasing the capacitor size (C1) or increasing the frequency will be of more benefit than the paralleling circuit shown.

Figure 11 makes use of "stacking" two LTC1044As to provide even higher voltages. A negative voltage doubler or tripler can be achieved, depending upon how pin 8 of the second LTC1044A is connected, as shown schematically by the switch. The available output current will be dictated/decreased by the product of the individual power conversion efficiencies and the voltage step-up ratio.

\*THE EXCLUSIVE NOR GATE SYNCHRONIZES BOTH LTC1044As TO MINIMIZE RIPPLE

Figure 10. Paralleling for Lower Output Resistance

Figure 11. Stacking for Higher Voltage