**AN1120**

## Basic Servo Loop Motor Control Using the MC68HC05B6 MCU

## By Jim Gray

This application note describes a basic circuit and software implementing proportional derivative (PD) closed-loop speed control for a brush motor using four integrated circuits (ICs), two opto discretes, and less than 200 bytes of code.

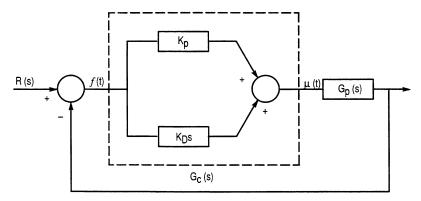

Feedback control systems using digital algorithms implemented on microcontroller units (MCUs) are becoming increasingly commonplace. The use of an MCU in this type of control application is justified when system flexibility is needed, such as varying drive motors or storing wear parameters in electrically erasable programmable read-only memory (EEPROM). Typically, the system would be modeled mathematically in the discrete time domain due to the use of sampled rather than continuous data. The linear difference equations describing the transfer function of the system are solved using z-transforms, allowing, in the case of proportional-integral-derivative (PID) control, the determination of constants for proper system performance and stability. However, this level of analysis is not necessary to illustrate how straightforward the implementation is using the MC68HC05B6 and the MPM3004 TMOSTM H-bridge. The generalized flow of a PD loop is shown in Figure 1. The transfer function of  $G_C(s)$  consists of the PD control, and  $G_p(s)$  represents the power amplifier, motor, and load. Here s is a complex variable having both real and imaginary parts. The proportional term  $K_p$  can be accomplished with shifting operations, at least to the resolution of powers of 2. The derivative term,  $K_{DS}$ , of f(t) is approximately

$$\frac{df(t)}{dt}\Big|_{t=kT} \cong \frac{1}{T}[f(kT) - f(k-1)T]$$

where f(kT) is the current value of the controlled parameter, and f(k-1)T is the value of the same parameter at the previous sampling time. In this example, kDs is realized as the rate of change of the difference between the measured and the desired period of motor-shaft rotation.

Figure 1. PD Loop Flow

TMOS is a trademark of Motorola Inc.

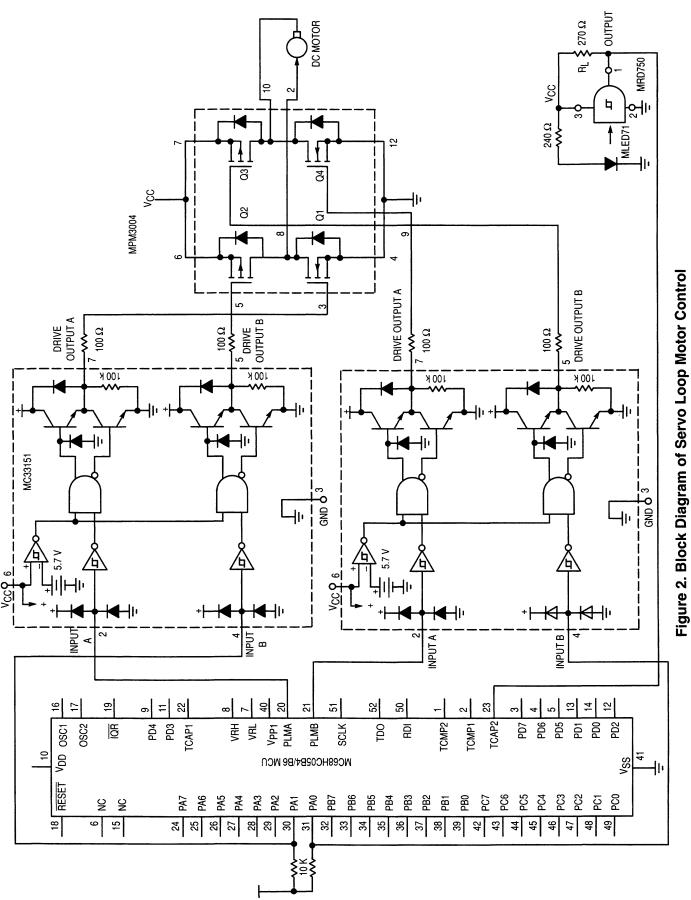

The MC68HC05B6 is an M68HC05 MCU Family member with two channels of programmable pulse-length modulation on-chip. When used with an H-bridge device such as the MPM3004, these channels can control bidirectional currents of up to 10-A continuous (25-A peak) at 60 V (see Figure 2). Two I/O pins and both pulse-length modulation (PLM) channels are used to control the MPM3004. Proper gate drive and level conversion is provided by the MC34151 dual inverting gate drivers. Input to the control loop consists of the MLED71 infrared emitter and MRD750 photo Schmitt trigger detector coupled through a slotted disc on the motor shaft. The TCAP2 pin and associated input capture registers are used to convert the optical index marks into a time measurement. Great care must be taken to ensure an adequate current source for the MPM3004 and to isolate the supply for the MC34151s. Separate circuit runs and 0.1-μF bypass capacitors on the MC34151 ICs were used in this case.

The justification for adding a derivative term to a proportional controller can be easily understood by examining the reasons for the overshoot and ringing typical of an underdamped proportional-only controller. When proportional control applies additional power to correct an underspeed condition, it does so continuously until the error term is zero, resulting in a power setting that ensures an overspeed condition. The converse occurs when reducing motor speed. The rate of change of the error signal as excessive power is being applied to correct underspeed will be a relatively large negative value (the error term is being rapidly reduced). Thus, the derivative of the error term is of the correct sign to compensate the proportional gain term. One effect of this compensation is to retard the loop's response time, but the proportional gain can be increased to offset this.

The listing (see Figure 3) shows the assembly source code for speed measurement and the PD control of PLMA, which drives the power H-bridge in one direction. The opposite direction of rotation is obtained by complementing bits 0 and 1 of port A and driving the opposite lower leg of the H-bridge with PLMB. Eight-bit arithmetic was used exclusively in this example for space and clarity. Although this approach is functional, 16-bit routines for multiply and divide, given in Reference 2, are better for finer control. Routines to set initial values, control direction of rotation, and check for motor stall are also necessary, although they are not shown in this application note.

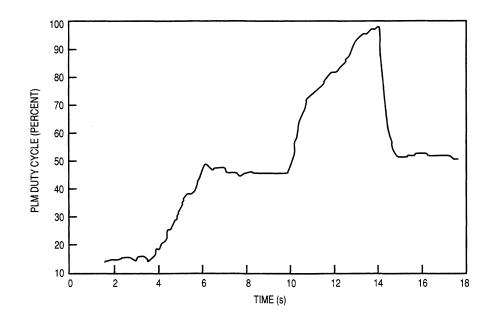

Figure 4 shows the response of the system to various changes in load. The data was captured in an emulator trace buffer (Motorola CDS8 Jewelbox) and plotted using a data base program. Beginning from a no-load condition at 4 s, loading (an uncalibrated friction brake) was ramped to cause approximately a 50-percent duty cycle. Starting at 10 s, the load was then increased again until the system was at the limit of compliance — i.e., at full power and still maintaining the desired speed. Next, at 14 s, approximately half the load was rapidly (0.1 s) removed. The gain of the proportional term was 2, and the derivative constant was 1. In systems where a low-pass filter would be beneficial or the steady state error is potentially large, an integral term could be added for full PID control.

## REFERENCES

- 1. Kuo, Benjamin C., Automatic Control Systems, New Jersey: Prentice-Hall, 1987.

- 2. M6805UM/AD2, M6805 HMOS/M146805 CMOS Family User's Manual, New Jersey: Prentice-Hall, 1983.

- 3. MC68HC05B6/D, MC68HC05B6 Data Sheet, Motorola, 1988.

- 4. M68HC05AG/AD, M68HC05 Applications Guide, Motorola, 1989.

Figure 2. Block Diagram of Servo Loop Motor Control

```

MC68HC05B6 SERVO LOOP MOTOR CONTROL EXAMPLE

^{\star} This program performs a closed loop servo speed control using PLMA for

3

* output. Speed is measured optically with a slotted disk. The optically

5

* detected index mark, controls TCAP2 which allows calculation of the

* period of revolution for the loop input.

6

8

9 0000

org .$0

10

cycles off

11 0000

12 0000

PADR

RMB

13 0001

PBDR

RMB

14 0002

PCDR

RMB

15 0003

PDIDR

RMB

16 0004

PADDR

RMB

1

17 0005

PBDDR

RMB

18 0006

PCDDR

RMB

19

20 000A

ORG

$0A

21

22 000A

PLMA

RMB

1

23 000B

PLMB

RMB

1

24 000C

MISC

RMB

7

25

26 0012

ORG

$12

27

28 0012

TCR

RMB

1

29 0013

TSR

RMB

1

30 0014

CAHR1

RMB

31 0015

RMB

CALR1

32 0016

COHR1

RMB

1

33 0017

COLR1

RMB

1

34 0018

CNTHR

RMB

35 0019

CNTLR

RMB

1

36 001A

ACNTHR RMB

37 001B

ACNTLR RMB

1

38 001C

CAHR2

RMB

1

39 001D

CALR2

RMB

1

40

41 0050

ORG

$50

42

BCNTH

43 0050

RMB

1

44 0051

BCNTL

RMB

45 0052

ECNTH

RMB

1

46 0053

ECNTL

RMB

1

47 0054

PERIOD RMB

MUST BE INITIALIZED WITH STARTING VALUE

48 0055

PLMTMP

RMB

MUST BE INITIALIZED WITH DESIRED PERIOD COUNT

49 0056

DESPRD

RMB

50 0057

DELTAN

RMB

51 0058

DELTAO

RMB

52 0059

DELTADC RMB

53 005A

54 OF00

ORG

$F00

55

56 OF00 A604

SELECT SLOW PLM REPETION RATE

BEGIN

LDA

#$4

57 OF02 B70C

SPEED

STA

MISC

58 OF04 B655

PLMTMP

LOAD PLM VALUE

59 OF06 B70A

STA

PLMA

CLEAR FLAG AND ANY PENDING INT.

60 OF08 B613

KEYS

LDA

TSR

61 OFOA B61C

LDA

CAHR2

62 OFOC B61D

CALR2

LDA

63 OFOE 1E12

BSET 7,TCR

SET INPUT CAPTURE INTERRUPT ENABLE

64 OF10 9A

CLI

CLEAR I BIT ALLOWING TIMER INTERRUPTS

WAIT

WAIT FOR OPTO INDEX TCIC INTERRUPT

65 OF11 20FE

BRA

WAIT

66 OF13 B613

CLR TSR BIT 4 TO ENSURE

RPM

LDA

TSR

67 OF15 B61C

LDA

CAHR2

SYNCHRONIZATION TO INDEX

68 0F17 B61D

LDA

CALR2

```

Figure 3. MC68HC05B6 Servo Loop Motor Control Example

|     |              | 081302 | TFLAG1 | BRSET      | 4, TSR, INDEX1    | TEST FLAG FOR INDEX1                          |

|-----|--------------|--------|--------|------------|-------------------|-----------------------------------------------|

|     | 0F1C<br>0F1E |        | INDEX1 | BRA<br>LDA | TFLAG1<br>CAHR2   | STORE COUNT                                   |

| 72  | 0F20         | B750   |        | STA        | BCNTH             |                                               |

| 73  | 0F22         | B61D   |        | LDA        | CALR2             |                                               |

|     | 0F24         |        |        | STA        | BCNTL             |                                               |

|     | 0F26         |        | 5501   | CLRA       |                   | DELAY TO AVOID RETRIGGER ON SAME INDEX        |

|     | 0F27<br>0F28 |        | DEC1   | DECA       | DEC1              |                                               |

|     | OF2A         |        |        | BNE<br>LDA | DEC1<br>TSR       | CLEAR FLAG AND WAIT                           |

|     | 0F2C         |        |        | LDA        | CAHR2             | FOR INDEX2                                    |

| 80  | 0F2E         | B61D   |        | LDA        | CALR2             |                                               |

| 81  | 0F30         | 081302 | TFLAG2 | BRSET      | 4,TSR,INDEX2      |                                               |

|     | 0F33         |        |        | BRA        | TFLAG2            |                                               |

|     | 0F35         |        | INDEX2 | LDA        | CAHR2             | STORE SECOND COUNT                            |

|     | 0F37<br>0F39 |        |        | STA<br>LDA | ECNTH             |                                               |

|     | 0F3B         |        |        | STA        | CALR2<br>ECNTL    |                                               |

|     | OF3D         |        |        | LDA        | ECNTH             | CALCULATE PERIOD                              |

| 88  | 0F3F         | B050   |        | SUB        | BCNTH             | THEN                                          |

| 89  | 0F41         | B754   |        | STA        | PERIOD            | STORE.                                        |

|     | 0F43         |        |        | LDA        | DELTAN            | GET PREVIOUS ERROR AND                        |

|     | 0F45         |        |        | STA        | DELTAO            | STORE IT.                                     |

|     | 0F47         |        |        | LDA        | DESPRD            | LOAD DESIRED PERIOD, SUBTRACT ACTUAL          |

|     | 0F49<br>0F4B |        |        | SUB<br>BLO | PERIOD<br>INCSPD  | TO FORM DELTAN. GO TO INCREMENTING PLM        |

|     | OF4D         |        |        | LSLA       | INCSED            | MULTIPLY ERROR BY 2.                          |

|     | OF4E         |        |        | STA        | DELTAN            | OR FALL THRU TO DECREMENTING HERE.            |

| 97  | 0F50         | B658   |        | LDA        | DELTAO            | FORM RATE OF CHANGE                           |

|     | 0F52         |        |        | SUB        | DELTAN            | OF ERROR                                      |

|     | 0F54         |        |        | STA        | DELTADC           | AND STORE.                                    |

|     | 0F56         |        |        | LDA        | DELTAN            | GET CURRENT ERROR                             |

|     | 0F58<br>0F5A |        |        | SUB<br>STA | DELTADO           | AND APPLY DE/DT CORRECTION                    |

|     | 0F5C         |        |        | LDA        | DELTADC<br>PLMTMP | THEN STORE. GET CURRENT PLM                   |

|     | OF5E         |        |        | SUB        | DELTAN            | AND APPLY CORRECTION.                         |

| 105 | 0F60         | 2208   |        | BHI        | ADJDN             | BRANCH TO DECREMENT IF RESULT POSITIVE        |

| 106 | 0F62         | A610   | PLMMIN | LDA        | #\$10             | OTHERWISE IN LOW SATURATION SO                |

|     | 0F64         |        |        | STA        | PLMA              | KEEP PLM AT MINIMUM.                          |

|     | 0F66         |        |        | STA        | PLMTMP            |                                               |

|     | 0F68<br>0F6A |        | ADJDN  | BRA<br>CMP | DONE<br>#\$10     | SEE IF PLM AT MINIMUM                         |

|     | OF6C         |        | ADODN  | BHI        | DECSPD            | SEE II FEM AT MINIMOM                         |

|     | OF6E         |        |        | BRA        | PLMMIN            |                                               |

| 113 | 0F70         | B70A   | DECSPD | STA        | PLMA              | DECREMENT PLMA                                |

|     | 0F72         |        |        | STA        | PLMTMP            | UPDATE PLMA TEMPORARY LOCATION                |

|     | 0F74         |        |        | BRA        | DONE              |                                               |

|     | 0F76<br>0F77 |        | INCSPD | LSLA       | DET MAN           | MULTIPLY ERROR BY 2                           |

|     | 0F77         |        |        | STA<br>LDA | DELTAN<br>DELTAO  | INCREMENT WITH SATURATION FORM RATE OF CHANGE |

|     | 0F7B         |        |        | SUB        | DELTAN            | OF ERROR.                                     |

|     | 0F7D         |        |        | ADD        | DELTAN            | NOW ADD IT TO CURRENT DELTA                   |

| 121 | 0F7F         | B759   |        | STA        | DELTADC           | TO FORM RATE OF CHANGE COMPENSATED ERROR.     |

|     | 0F81         |        |        | LDA        | PLMTMP            | GET CURRENT PLM                               |

|     | 0F83         |        |        | SUB        | DELTADC           | AND APPLY CORRECTION.                         |

|     | 0F85<br>0F87 |        |        | BLO        | ADJUP             | THE CAMPIDATION OF CORRECTION FOUNDS          |

|     | 0F89         |        | ADJUP  | BRA<br>STA | DONE<br>PLMA      | IN SATURATION OR CORRECTION EQUALS 0          |

|     | 0F8B         |        | 110001 | STA        | PLMTMP            |                                               |

|     | 0F8D         |        | DONE   | RTI        |                   | RETURN TO WAIT                                |

| 129 |              |        |        |            |                   |                                               |

| 130 | 1 0 0 0 ∩    |        |        | OPC        | ¢1ppn             | set westers                                   |

|     | 1FF0<br>1FF0 | 0F00   |        | ORG<br>FDB | \$1FF0<br>BEGIN   | set vectors<br>R                              |

|     | 1FF2         |        |        | FDB        | BEGIN             | SCI                                           |

|     | 1FF4         |        |        | FDB        | BEGIN             | TOV                                           |

| 135 | 1FF6         | 0F00   |        | FDB        | BEGIN             | TOC                                           |

|     | 1FF8         |        |        | FDB        | RPM               | TIC                                           |

|     | 1FFA         |        |        | FDB        | BEGIN             | IRQ                                           |

| 138 | 1FFC         | UF'UU  |        | FDB        | BEGIN             | SWI                                           |

MOTOROLA 5 AN1120/D

MOTOROLA AN1120/D

Figure 4. Step Response of PLM Motor Control

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products or any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

## **Literature Distribution Centers:**

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Center; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.