# 0.1 GHz to 18 GHz, GaAs SP4T Switch

HMC641A **Data Sheet**

### **FEATURES**

Broadband frequency range: 0.1 GHz to 18 GHz Nonreflective 50  $\Omega$  design Low insertion loss: 2.1 dB to 12 GHz High isolation: 42 dB to 12 GHz **High input linearity** P1dB: 25 dBm typical at  $V_{SS} = -5 \text{ V}$ IP3: 41 dBm typical High power handling at  $V_{SS} = -5 \text{ V}$ 24 dBm through path 23 dBm terminated path Integrated 2 to 4 line decoder 8-pad, 1.92 mm × 1.60 mm × 0.102 mm, CHIP

### **APPLICATIONS**

**Test instrumentation** Microwave radios and very small aperture terminals (VSATs) Military radios, radars, and electronic counter measures (ECMs) **Broadband telecommunications systems**

### **GENERAL DESCRIPTION**

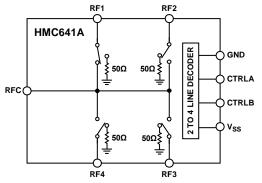

The HMC641A is a nonreflective, single-pole, four-throw (SP4T) switch, manufactured using a gallium arsenide (GaAs) process. This switch typically provides low insertion loss of 2.1 dB and high isolation of 42 dB in broadband frequency range from 0.1 GHz to 18 GHz.

The HMC641A includes an on-chip, binary 2 to 4 line decoder that provides control from two logic input lines.

Trademarks and registered trademarks are the property of their respective owners.

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The switch operates with a negative supply voltage of -5 V to -3 V and requires two negative logic control voltages.

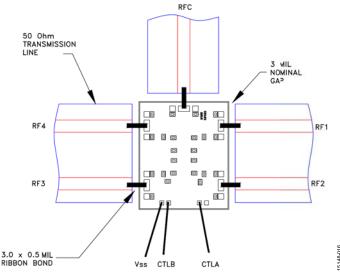

All electrical performance data is acquired with the HMC641A that all RFx pads are connected to by the 50  $\Omega$  transmission lines via one 3.0 mil  $\times$  0.5 mil ribbon bond of minimal length.

### **TABLE OF CONTENTS**

| Features                                                                                                                 |  |

|--------------------------------------------------------------------------------------------------------------------------|--|

| Applications                                                                                                             |  |

| Functional Block Diagram                                                                                                 |  |

| General Description1                                                                                                     |  |

| Revision History                                                                                                         |  |

| Specifications                                                                                                           |  |

| Absolute Maximum Ratings                                                                                                 |  |

| Power Derating Curve4                                                                                                    |  |

| ESD Caution4                                                                                                             |  |

| Pin Configuration and Function Descriptions5                                                                             |  |

| REVISION HISTORY                                                                                                         |  |

| This Hittite Microwave Products data sheet has been reformatted to meet the styles and standards of Analog Devices, Inc. |  |

| 3/2017—Rev. 02.0316 to Rev. C                                                                                            |  |

| Updated FormatUniversal                                                                                                  |  |

| Changes to Features Section, Figure 1, and General Description                                                           |  |

| Section                                                                                                                  |  |

| Changed $V_{SS} = -5 \text{ V}$ to $V_{SS} = -5 \text{ V}$ to $-3 \text{ V}$ , Table 1                                   |  |

| Changes to Table 1                                                                                                       |  |

Added Power Derating Curve Section and Figure 2;

| Interface Schematics5                                         |

|---------------------------------------------------------------|

| Typical Performance Characteristics6                          |

| Insertion Loss, Return Loss, and Isolation6                   |

| Input Power Compression and Third-Order Intercept7            |

| Theory of Operation8                                          |

| Applications Information9                                     |

| Mounting and Bonding Techniques9                              |

| Assembly Diagram9                                             |

| Outline Dimensions                                            |

| Ordering Guide                                                |

| C                                                             |

|                                                               |

| Added Figure 45                                               |

| Deleted GND Interface Schematic Figure and TTL Interface      |

| Circuit Figure5                                               |

| Changes to Table 3 and Figure 55                              |

| Added Table 4; Renumbered Sequentially8                       |

| Added Theory of Operation Section8                            |

| Added Applications Information Section, Figure 14, Figure 15, |

| and Assembly Diagram Section9                                 |

| Updated Outline Dimensions                                    |

| Updated Ordering Guide                                        |

## **SPECIFICATIONS**

$V_{SS} = -5 \text{ V to } -3 \text{ V}, V_{CTL} = 0 \text{ V or } V_{SS}, T_{DIE} = 25^{\circ}\text{C}, 50 \Omega$  system, unless otherwise noted.

Table 1.

| Parameter                    | Symbol           | Test Conditions/Comments                 | Min | Тур | Max  | Unit |

|------------------------------|------------------|------------------------------------------|-----|-----|------|------|

| BROADBAND FREQUENCY RANGE    | f                |                                          | 0.1 |     | 18   | GHz  |

| INSERTION LOSS               |                  | 0.1 GHz to 12 GHz                        |     | 2.1 | 2.4  | dB   |

|                              |                  | 0.1 GHz to 18 GHz                        |     | 2.3 | 3.0  | dB   |

| ISOLATION                    |                  |                                          |     |     |      |      |

| Between RFC and RF1 to RF4   |                  | 0.1 GHz to 12 GHz                        | 39  | 42  |      | dB   |

|                              |                  | 0.1 GHz to 18 GHz                        | 36  | 38  |      | dB   |

| RETURN LOSS                  |                  |                                          |     |     |      |      |

| RFC                          |                  | 0.1 GHz to 18 GHz                        |     | 15  |      | dB   |

| RF1 to RF4                   |                  |                                          |     |     |      |      |

| On State                     |                  | 0.1 GHz to 18 GHz                        |     | 15  |      | dB   |

| Off State                    |                  | 0.1 GHz to 18 GHz                        |     | 15  |      | dB   |

| SWITCHING CHARACTERISTICS    |                  |                                          |     |     |      |      |

| Rise and Fall Time           | trise, trall     | 10% to 90% of RF output                  |     | 15  |      | ns   |

| On and Off Time              | ton, toff        | 50% V <sub>CTL</sub> to 90% of RF output |     | 95  |      | ns   |

| INPUT LINEARITY <sup>1</sup> |                  | 250 MHz to 18 GHz                        |     |     |      |      |

| 1 dB Compression             | P1dB             | $V_{SS} = -5 \text{ V}$                  | 22  | 25  |      | dBm  |

|                              |                  | $V_{SS} = -3 \text{ V}$                  |     | 22  |      | dBm  |

| Third-Order Intercept        | IP3              | 10 dBm per tone, 1 MHz spacing           |     |     |      |      |

|                              |                  | $V_{SS} = -5 \text{ V}$                  | 38  | 41  |      | dBm  |

|                              |                  | $V_{SS} = -3 \text{ V}$                  |     | 41  |      | dBm  |

| SUPPLY                       |                  | V <sub>SS</sub> pin                      |     |     |      |      |

| Voltage                      | $V_{SS}$         |                                          | -5  |     | -3   | V    |

| Current                      | Iss              |                                          |     | 1.9 | 6    | mA   |

| DIGITAL CONTROL INPUTS       |                  | CTRLA and CTRLB pins                     |     |     |      |      |

| Voltage                      | $V_{CTL}$        |                                          |     |     |      |      |

| Low                          | $V_{INL}$        | $V_{SS} = -5 \text{ V}$                  | -3  |     | 0    | V    |

|                              |                  | $V_{SS} = -3 \text{ V}$                  | -1  |     | 0    | V    |

| High                         | V <sub>INH</sub> | $V_{SS} = -5 \text{ V}$                  | -5  |     | -4.2 | V    |

|                              |                  | $V_{SS} = -3 \text{ V}$                  | -3  |     | -2.2 | V    |

| Current                      | I <sub>CTL</sub> |                                          |     |     |      |      |

| Low                          | I <sub>INL</sub> |                                          |     | 50  |      | μΑ   |

| High                         | I <sub>INH</sub> |                                          |     | 0.2 |      | μΑ   |

<sup>&</sup>lt;sup>1</sup> Input linearity performance degrades at frequencies less than 250 MHz; see Figure 10, Figure 11, Figure 12, and Figure 13.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Table 2.                                                                 |                                   |  |  |  |  |  |  |

|--------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|--|

| Parameter                                                                | Rating                            |  |  |  |  |  |  |

| Supply Voltage                                                           | -7 V                              |  |  |  |  |  |  |

| Digital Control Input Voltage                                            | $V_{SS} - 0.5 V \text{ to } +1 V$ |  |  |  |  |  |  |

| RF Input Power <sup>1</sup>                                              |                                   |  |  |  |  |  |  |

| $(f = 250 \text{ MHz to } 18 \text{ GHz}, T_{DIE} = 85^{\circ}\text{C})$ |                                   |  |  |  |  |  |  |

| $V_{SS} = -5 V$                                                          |                                   |  |  |  |  |  |  |

| Through Path                                                             | 24 dBm                            |  |  |  |  |  |  |

| Terminated Path                                                          | 23 dBm                            |  |  |  |  |  |  |

| Hot Switching                                                            | 20 dBm                            |  |  |  |  |  |  |

| $V_{SS} = -3 V$                                                          |                                   |  |  |  |  |  |  |

| Through Path                                                             | 21 dBm                            |  |  |  |  |  |  |

| Terminated Path                                                          | 20 dBm                            |  |  |  |  |  |  |

| Hot Switching                                                            | 17 dBm                            |  |  |  |  |  |  |

| Temperature                                                              |                                   |  |  |  |  |  |  |

| Junction Temperature, T <sub>J</sub>                                     | 150°C                             |  |  |  |  |  |  |

| Die Bottom Temperature Range, TDIE                                       | −55°C to +85°C                    |  |  |  |  |  |  |

| Storage Temperature Range                                                | −65°C to +150°C                   |  |  |  |  |  |  |

| Junction to Die Bottom Thermal Resistance                                |                                   |  |  |  |  |  |  |

| Through Path                                                             | 201°C/W                           |  |  |  |  |  |  |

| Terminated Path                                                          | 322°C/W                           |  |  |  |  |  |  |

| ESD Sensitivity                                                          |                                   |  |  |  |  |  |  |

| Human Body Model (HBM)                                                   | 250 V (Class 1A)                  |  |  |  |  |  |  |

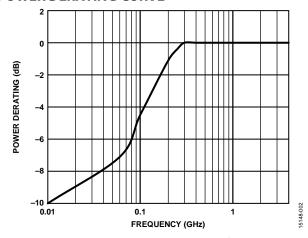

$<sup>^{\</sup>rm 1}\,\text{For power derating}$  at frequencies less than 250 MHz, see Figure 2.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **POWER DERATING CURVE**

Figure 2. Power Derating at Frequencies Less Than 250 MHz

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

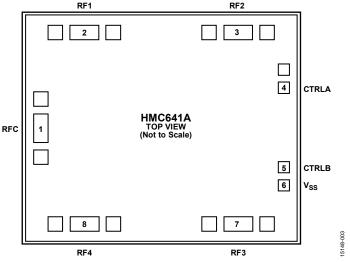

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

Table 3. Pad Function Descriptions<sup>1</sup>

| Pad No.    | Mnemonic | Description                                                                                                                                                                                                  |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

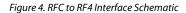

| 1          | RFC      | RF Common Pad. This pad is dc-coupled to 0 V and ac matched to 50 $\Omega$ . No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 4 for the interface schematic.  |

| 2          | RF1      | RF Throw Pad 1. This pad is dc-coupled to 0 V and ac matched to 50 $\Omega$ . No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 4 for the interface schematic. |

| 3          | RF2      | RF Throw Pad 2. This pad is dc-coupled to 0 V and ac matched to 50 $\Omega$ . No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 4 for the interface schematic. |

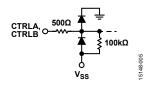

| 4          | CTRLA    | Control Input A; see Table 4. See Figure 5 for the interface schematic.                                                                                                                                      |

| 5          | CTRLB    | Control Input B; see Table 4. See Figure 5 for the interface schematic.                                                                                                                                      |

| 6          | $V_{SS}$ | Negative Supply Voltage.                                                                                                                                                                                     |

| 7          | RF3      | RF Throw Pad 3. This pad is dc-coupled to 0 V and ac matched to 50 $\Omega$ . No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 4 for the interface schematic. |

| 8          | RF4      | RF Throw Pad 4. This pad is dc-coupled to 0 V and ac matched to 50 $\Omega$ . No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 4 for the interface schematic. |

| Die Bottom | GND      | Ground. Die bottom must be attached directly to the ground plane eutectically or with conductive epoxy.                                                                                                      |

<sup>&</sup>lt;sup>1</sup> No connection is required for the unlabeled grounds.

### **INTERFACE SCHEMATICS**

Figure 5. CTRLA and CTRLB Interface Schematic

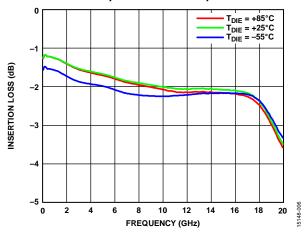

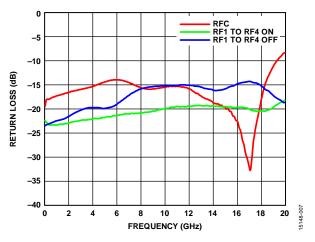

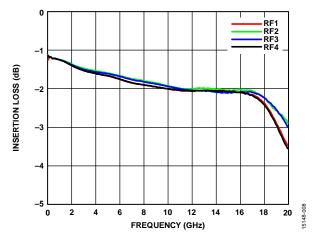

# TYPICAL PERFORMANCE CHARACTERISTICS INSERTION LOSS, RETURN LOSS, AND ISOLATION

Figure 6. Insertion Loss Between RFC and RF1 vs. Frequency over Temperature

Figure 7. Return Loss for RFC, RF1 to RF4 On and RF1 to RF4 Off vs. Frequency

Figure 8. Insertion Loss Between RFC and RF1 to RF4 vs. Frequency

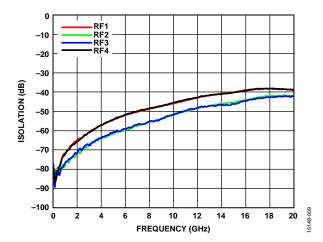

Figure 9. Isolation Between RFC and RF1 to RF4 vs. Frequency

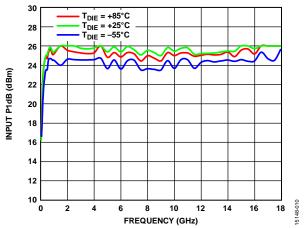

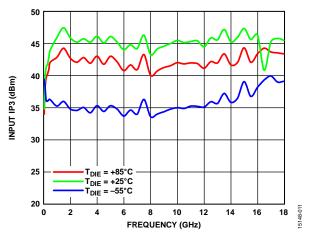

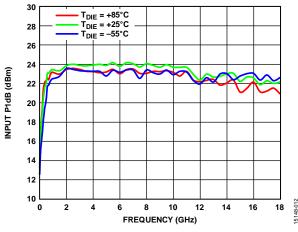

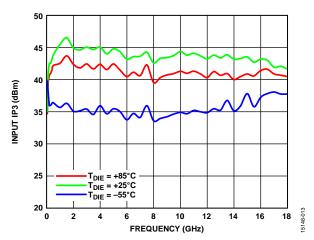

### INPUT POWER COMPRESSION (P1dB) AND THIRD-ORDER INTERCEPT (IP3)

Figure 10. Input P1dB vs. Frequency over Temperature,  $V_{SS} = -5 V$

Figure 11. Input IP3 vs. Frequency over Temperature,  $V_{SS} = -5 V$

Figure 12. Input P1dB vs. Frequency over Temperature,  $V_{SS} = -3 V$

Figure 13. Input IP3 vs. Frequency over Temperature,  $V_{SS} = -3 V$

### THEORY OF OPERATION

The HMC641A requires a negative supply voltage at the  $V_{SS}$  pad and two logic control inputs at the CTRLA and CTRLB pads to control the state of the RF paths.

Depending on the logic level applied to the CTRLA and CTRLB pads, one RF path is in the insertion loss state while the other three paths are in an isolation state (see Table 4). The insertion loss path conducts the RF signal between the RF throw pad and RF common pad while the isolation paths provide high loss between RF throw pads terminated to internal 50  $\Omega$  resistors and the insertion loss path.

The ideal power-up sequence is as follows:

- 1. Ground to the die bottom.

- 2. Power up V<sub>SS</sub>.

- Power up the digital control inputs. The relative order of the logic control inputs is not important. However, powering the digital control inputs before the V<sub>SS</sub> supply can inadvertently become forward-biased and damage the internal electrostatic discharge (ESD) protection structures.

- 4. Apply an RF input signal. The design is bidirectional; the RF input signal can be applied to the RFC pad while the RF throw pads are the outputs or the RF input signal can be applied to the RF throw pads while the RFC pad is the output. All of the RF pads are dc-coupled to 0 V, and no dc blocking is required at the RF pads when the RF line potential is equal to 0 V.

The power-down sequence is the reverse of the power-up sequence.

**Table 4. Control Voltage Truth Table**

| Digital | Control Input | RF Paths            |                     |                     |                     |

|---------|---------------|---------------------|---------------------|---------------------|---------------------|

| CTRLA   | CTRLB         | RF1 to RFC          | RF2 to RFC          | RF3 to RFC          | RF4 to RFC          |

| High    | High          | Insertion loss (on) | Isolation (off)     | Isolation (off)     | Isolation (off)     |

| Low     | High          | Isolation (off)     | Insertion loss (on) | Isolation (off)     | Isolation (off)     |

| High    | Low           | Isolation (off)     | Isolation (off)     | Insertion loss (on) | Isolation (off)     |

| Low     | Low           | Isolation (off)     | Isolation (off)     | Isolation (off)     | Insertion loss (on) |

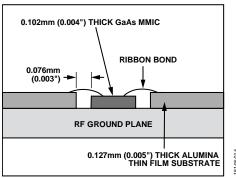

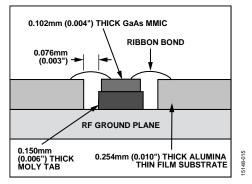

# APPLICATIONS INFORMATION MOUNTING AND BONDING TECHNIQUES

The HMC641A is back metallized and must be attached directly to the ground plane with gold tin (AuSn) eutectic preforms or with electrically conductive epoxy.

The die thickness is 0.102 mm (4 mil). The 50  $\Omega$  microstrip transmission lines on 0.127 mm (5 mil) thick alumina thin film substrates are recommended for bringing RF to and from the HMC641A (see Figure 14).

Figure 14. Bonding RF Pads to 5 mil Substrate

When using 0.254 mm (10 mil) thick alumina thin film substrates, theHMC641A must be raised 0.150 mm (6 mil) so the surface of the HMC641A is coplanar with the surface of the substrate. One way to accomplish this is by attaching the 0.102 mm (4 mil) thick die to a 0.150 mm (6 mil) thick molybdenum heat spreader (moly tab), which is then attached to the ground plane (see Figure 15).

Figure 15. Bonding RF Pads to 10 mil Substrate

Microstrip substrates are placed as close to the HMC641A as possible to minimize bond length. Typical die to substrate spacing is 0.076 mm (3 mil).

RF bonds made with 3 mil  $\times$  5 mil ribbon are recommended. DC bonds made with 1 mil diameter wire are recommended. All bonds must be as short as possible.

### **ASSEMBLY DIAGRAM**

An assembly diagram of the HMC641A is shown in Figure 16.

Figure 16. Die Assembly Diagram

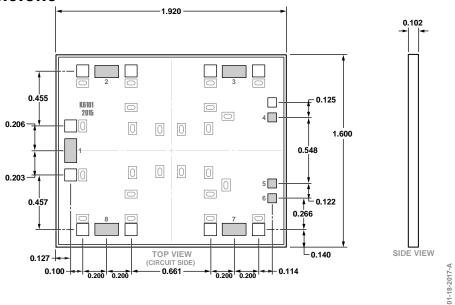

## **OUTLINE DIMENSIONS**

Figure 17. 8-Pad Bare Die [CHIP] (C-8-9) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Package Description   | Package Option |

|-----------------------|-------------------|-----------------------|----------------|

| HMC641A               | −55°C to +85°C    | 8-Pad Bare Die [CHIP] | C-8-9          |

| HMC641A-SX            | −55°C to +85°C    | 8-Pad Bare Die [CHIP] | C-8-9          |

<sup>&</sup>lt;sup>1</sup> The HMC641A is a RoHS Compliant Part.

<sup>&</sup>lt;sup>2</sup> The HMC641A-SX is a sample order model.