±1LSB\*

# **μP Compatible High-Speed 10-Bit A/D Converter with S/H**

## **GENERAL DESCRIPTION**

The ML2271 is a high speed,  $\mu P$  compatible 10-bit A/D converter. A three step flash technique is used to achieve a conversion time of 1.65 $\mu$ s.\* The ML2271 operates from a single 5V supply and has an analog input range from GND to  $V_{CC}$ .

The ML2271 has a true internal sample and hold and can digitize sinusoid signals as high as 150kHz without conversion errors.

The ML2271 digital interface has been designed so that the device appears as a memory location or I/O port to a  $\mu$ P, eliminating the need for external interfacing logic. The data outputs are latched and have three state control, allowing direct connection to a  $\mu$ P bus or I/O port. The addition of an internal timing generator also allows the device to easily operate in stand alone applications.

The ML2271 is pin and function compatible with the ADC1061.

\* For higher speed and higher accuracy versions, contact the factory

## **FEATURES**

- Conversion time over temperature and supply voltage tolerance

Linearity error

±1LSB\*

Full scale error

- Capable of digitizing a 5V, 150kHz sine wave

- No missing codes

Zero error

- 0V to 5V analog input range with single 5V power supply

- Analog input protection 25mA min

- Operates ratiometrically or with up to 5V voltage reference

- No external clock required

- Easy interface to μP, or operates stand-alone

- Latched, 3-state data outputs

- Power-on reset circuitry

- Low power 175mW max

- Standard 20-pin DIP or surface mount SOIC

- 0°C to 70°C, -40°C to +85°C operating temperature range

# **PIN CONFIGURATION**

#### 20-Pin SOIC D VCC III 1 20 III DB0 INT III 2 19 III DB1 $\overline{WR} \square \square 3$ 18 III DB2 RD III 4 17 III DB3 16 III DB4 A VCC III 6 15 III DB5 -VREF Ⅲ 7 14 III DB6 VIN III 8 13 III DB7 +VREF III 9 12 III DB8 GND Ⅲ 10 11 III DB9 **TOP VIEW**

# PIN DESCRIPTION

| PIN#              | NAME              | FUNCTION                                                                      | PIN#       | NAME              | FUNCTION                                            |

|-------------------|-------------------|-------------------------------------------------------------------------------|------------|-------------------|-----------------------------------------------------|

| 1                 | D V <sub>CC</sub> | Digital supply. $+5V \pm 5\%$ .<br>Connect to A $V_{CC}$ .                    | 7          | $-V_{REF}$        | Negative reference input voltage for A/D converter. |

| 2                 | ĪNT               | Interrupt output. This output signals                                         | 8          | $V_{IN}$          | Analog input.                                       |

|                   |                   | the end of a conversion and indicates that data is valid on the data outputs. | 9          | +V <sub>REF</sub> | Positive reference input voltage for A/D converter. |

|                   |                   | See Digital Interface section.                                                | 10         | GND               | Ground.                                             |

| 3 W               | WR                | Write input. Input which initiates a conversion. See Digital Interface        | 11         | DB9               | Data output — bit 9 (MSB)                           |

|                   |                   | section.                                                                      | 12         | DB8               | Data output — bit 8                                 |

| $4 \overline{RD}$ | $\overline{RD}$   | Read input. This input latches data                                           | 13         | DB7               | Data output — bit 7                                 |

|                   |                   | into the output latches. See Digital                                          | 14         | DB6               | Data output — bit 6                                 |

| _                 | <del></del>       | Interface section.                                                            | 15         | DB5               | Data output — bit 5                                 |

| 5                 | CS                | Chip select input. This input must be held low during WR and RD for the       | 16         | DB4               | Data output — bit 4                                 |

|                   |                   | device to perform a conversion.                                               | 1 <i>7</i> | DB3               | Data output — bit 3                                 |

| 6                 | $AV_{CC}$         | $V_{CC}$ Analog supply. +5V ±5%. Connect to                                   | 18         | DB2               | Data output — bit 2                                 |

|                   |                   | D V <sub>CC</sub> .                                                           | 19         | DB1               | Data output — bit 1                                 |

|                   |                   |                                                                               | 20         | DB0               | Data output — bit 0 (LSB)                           |

|                   |                   |                                                                               |            |                   |                                                     |

# **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltage, A V <sub>CC</sub> , D V <sub>CC</sub> |

|-------------------------------------------------------|

| Voltage                                               |

| Logic Inputs–0.3V to V <sub>CC</sub> + 0.3V           |

| Analog Inputs $-0.3$ V to $V_{CC}$ + 0.3              |

| Input Current per Pin (Note 2) ±25mA                  |

| Storage Temperature –65°C to +150°C                   |

| Package Dissipation                                   |

| at $T_A = 25$ °C (Board Mount) 875mW                  |

| Lead Temperature (Soldering 10 sec.)                  |

| Dual-In-Line Package (Molded) 260°C                   |

| Molded Small Outline IC Package                       |

| Vapor Phase (60 sec.)                                 |

| Infrared (15 sec.)                                    |

|                                                       |

# **OPERATING CONDITIONS**

| Temperature Range (Note 3) | $T_{MIN} \le T_A \le T_{MAX}$ |

|----------------------------|-------------------------------|

| ML2271CCS                  | 0°C to +70°C                  |

| ML2271CCP                  | 0°C to +70°C                  |

| ML2271CIS                  | 40°C to +85°C                 |

| ML2271CIP                  | 40°C to +85°C                 |

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified,  $T_A = T_{MIN}$  to  $T_{MAX}$ , D  $V_{CC} = A V_{CC} = +V_{REF} = 5V \pm 5\%$ , and  $-V_{REF} = GND$

|                                           |                                                                                   | ML2271CCX         |                 |                      | ML2271CIX         |                 |                      |       |

|-------------------------------------------|-----------------------------------------------------------------------------------|-------------------|-----------------|----------------------|-------------------|-----------------|----------------------|-------|

| PARAMETER                                 | CONDITIONS                                                                        | MIN               | TYP<br>(Note 4) | MAX                  | MIN               | TYP<br>(Note 4) | MAX                  | UNITS |

| Converter                                 |                                                                                   |                   |                 |                      |                   |                 |                      |       |

| Integral Linearity Error<br>ML2271CXX     | $V_{REF} = V_{CC} $ (Notes 5,7)                                                   |                   |                 | ±1                   |                   |                 | ±1.5                 | LSB   |

| Differential Linearity Error<br>ML2271CXX | $V_{REF} = V_{CC} $ (Note 5)                                                      |                   |                 | ±1                   |                   |                 | ±1                   | LSB   |

| Full Scale Error<br>ML2271CXX             | (Note 5)                                                                          |                   |                 | ±1                   |                   |                 | ±1                   | LSB   |

| Zero Scale Error<br>ML2271CXX             | (Note 5)                                                                          |                   |                 | ±1                   |                   |                 | ±1                   | LSB   |

| Total Unadjusted Error<br>ML2271CXX       | (Note 5)                                                                          |                   |                 | ±1.5                 |                   |                 | ±2.0                 | LSB   |

| +V <sub>REF</sub> Voltage Range           | (Note 6)                                                                          | -V <sub>REF</sub> |                 | V <sub>CC</sub> +0.1 | –V <sub>REF</sub> |                 | V <sub>CC</sub> +0.1 | V     |

| -V <sub>REF</sub> Voltage Range           | (Note 6)                                                                          | GND-0.1           |                 | +V <sub>REF</sub>    | GND-0.1           |                 | +V <sub>REF</sub>    | V     |

| Reference Input Resistance                | (Note 5)                                                                          | 0.9               | 1.3             | 1.7                  | 0.9               | 1.3             | 1.7                  | kΩ    |

| Analog Input Range                        | (Notes 5,8)                                                                       | -V <sub>REF</sub> |                 | +V <sub>REF</sub>    | –V <sub>REF</sub> |                 | +V <sub>REF</sub>    | V     |

| Power Supply Sensitivity                  | DC $V_{CC} = 5V \pm 5\%$ , $V_{REF} = 4.75V$ (Note 5)                             |                   | ±1/32           | ±1/4                 |                   | ±1/32           | ±1/4                 | LSB   |

|                                           | $100 \text{mV}_{P-P}$ , $100 \text{kHz}$ sine on $V_{CC}$ , $V_{IN} = 0$ (Note 5) |                   | ±1/16           |                      |                   | ±1/16           |                      | LSB   |

| Analog Input Leakage Current              | Converter Idle (Notes 5,9)                                                        | -2                |                 | +2                   | -2                |                 | +2                   | μΑ    |

| Analog Input Capacitance                  | During Acquisition Period                                                         |                   | 25              |                      |                   | 25              |                      | рF    |

# **ELECTRICAL CHARACTERISTICS** (continued)

Unless otherwise specified,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $D\ V_{CC} = A\ V_{CC} = +V_{REF} = 5V\ \pm 5\%$ , and  $-V_{REF} = GND$

|                                                          | CONDITIONS                                                                                                                                                   | ML2271CCX |                 |      | ML2271CIX |                 |     |       |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|------|-----------|-----------------|-----|-------|

| PARAMETER                                                |                                                                                                                                                              | MIN       | TYP<br>(Note 4) | MAX  | MIN       | TYP<br>(Note 4) | MAX | UNITS |

| Digital and DC                                           |                                                                                                                                                              |           |                 |      |           |                 |     |       |

| V <sub>IN(1)</sub> , Logical "1"<br>Input Voltage        | (Note 5)                                                                                                                                                     | 2.0       |                 |      | 2.0       |                 |     | V     |

| V <sub>IN(0)</sub> , Logical "0"<br>Input Voltage        | (Note 5)                                                                                                                                                     |           |                 | 0.8  |           |                 | 0.8 | V     |

| I <sub>IN(1)</sub> , Logical "1"<br>Input Current        | $V_{IN} = V_{CC} $ (Note 5)                                                                                                                                  |           |                 | 1    |           |                 | 1   | μА    |

| I <sub>IN(0)</sub> , Logical "0"<br>Input Current        | $V_{IN} = 0V \text{ (Note 5)}$                                                                                                                               | -1        |                 |      | -1        |                 |     | μА    |

| V <sub>OUT(1)</sub> , Logical "1"<br>Output Voltage      | $I_{OUT} = -2mA \text{ (Note 5)}$                                                                                                                            | 4.0       |                 |      | 4.0       |                 |     | V     |

| V <sub>OUT(0)</sub> , Logical "0"<br>Output Voltage      | I <sub>OUT</sub> = 2mA (Note 5)                                                                                                                              |           |                 | 0.4  |           |                 | 0.4 | V     |

| I <sub>OUT</sub> , Three-State                           | V <sub>OUT</sub> = 0V (Note 5)                                                                                                                               | -1        |                 |      | -1        |                 |     | μА    |

| Output Current                                           | $V_{OUT} = V_{CC}$ (Note 5)                                                                                                                                  |           |                 | 1    |           |                 | 1   | μА    |

| C <sub>OUT</sub> , Logic<br>Output Capacitance           |                                                                                                                                                              |           | 5               |      |           | 5               |     | pF    |

| C <sub>IN</sub> , Logic Input Capacitance                |                                                                                                                                                              |           | 5               |      |           | 5               |     | рF    |

| I <sub>CC</sub> , Supply Current,<br>Analog Plus Digital | $\overline{\text{CS}} = \overline{\text{WR}} = \overline{\text{RD}} = 0$<br>No Output Load (Note 5)                                                          |           |                 | 32   |           |                 | 35  | mA    |

| AC and Dynamic Performanc                                | e (Note 9)                                                                                                                                                   |           | <u>.</u>        |      |           |                 |     | •     |

| t <sub>CONV</sub> , Conversion Time,<br>Interrupt Mode   | Figure 2 t <sub>WR</sub> = 250ns<br>(Note 6)                                                                                                                 |           |                 | 1.65 |           |                 | 1.8 | μs    |

| t <sub>CWRD</sub> , Conversion Time,<br>Write-Read Mode  | Figure 3<br>(Note 5)                                                                                                                                         |           |                 | 1.9  |           |                 | 2.0 | μs    |

| t <sub>CRD</sub> , Conversion Time,<br>Write-Read Mode   | Figure 4<br>(Note 6)                                                                                                                                         |           |                 | 1.9  |           |                 | 2.0 | μs    |

| SNR, Signal to Noise Ratio                               | V <sub>IN</sub> = 5V, 150kHz Noise is sum of all nonfundamental components from 0–300kHz. f <sub>SAMPLING</sub> = 600kHz                                     |           | 60              |      |           | 60              |     | dB    |

| HD, Harmonic Distortion                                  | V <sub>IN</sub> = 5V, 150kHz<br>THD is sum of 2–5th harmonics<br>or aliases relative to fundamental.<br>f <sub>SAMPLING</sub> = 600kHz                       |           | -60             |      |           | -60             |     | dB    |

| IMD, Intermodulation<br>Distortion                       | fa = 2.5V, 150kHz<br>fb = 2.5V, 148kHz<br>IMB is (fa + fb), (fa – fb),<br>(2fa + fb), (2fa – fb), relative to<br>fundamental. f <sub>SAMPLING</sub> = 600kHz |           | -60             |      |           | -60             |     | dB    |

| FR, Frequency Response                                   | $V_{IN} = 5V$ , 0–150kHz<br>Relative to 1kHz<br>$f_{SAMPLING} = 600kHz$                                                                                      |           | ±0.1            |      |           | ±0.1            |     | dB    |

| SR, Slew Rate Tracking                                   |                                                                                                                                                              |           | 2.36            |      |           | 2.36            |     | V/µs  |

## **ELECTRICAL CHARACTERISTICS** (continued)

Unless otherwise specified,  $T_A = T_{MIN}$  to  $T_{MAX}$ , D  $V_{CC} = A V_{CC} = +V_{RFF} = 5V \pm 5\%$ , and  $-V_{RFF} = GND$

|                                                                                                            |                      | 1   | ML2271CCX       |      | ML2271CIX |                 |      |       |  |

|------------------------------------------------------------------------------------------------------------|----------------------|-----|-----------------|------|-----------|-----------------|------|-------|--|

| PARAMETER                                                                                                  | CONDITIONS           | MIN | TYP<br>(Note 4) | MAX  | MIN       | TYP<br>(Note 4) | MAX  | UNITS |  |

| AC Performance, Figures 2, 3, 4, and 5                                                                     |                      |     |                 |      |           |                 |      |       |  |

| t <sub>CSS</sub> , $\overline{\text{CS}}$ to $\overline{\text{RD}}$ , $\overline{\text{WR}}$<br>Setup Time | (Note 5)             | 0   |                 |      | 0         |                 |      | ns    |  |

| $\overline{t_{CSH}}$ , $\overline{CS}$ to $\overline{RD}$ , $\overline{WR}$<br>Hold Time                   | (Note 5)             | 0   |                 |      | 0         |                 |      | ns    |  |

| t <sub>WR</sub> , WR Pulse Width                                                                           | (Note 5)             | 250 |                 | 50K  | 250       |                 | 50K  | ns    |  |

| t <sub>ACC2</sub> , WR to Data Valid                                                                       | (Note 5)             |     |                 | 2.05 |           |                 | 2.05 | μs    |  |

| t <sub>RD</sub> , Read Pulse Width                                                                         | (Note 5)             | 100 |                 |      | 100       |                 |      | ns    |  |

| $t_{WRL}$ , $\overline{WR}$ to $\overline{RD}$ $\downarrow$                                                | (Note 6)             | 0   |                 |      | 0         |                 |      | ns    |  |

| t <sub>INTH</sub> , RD↑ to INT↑                                                                            | (Note 5)             | 10  |                 | 55   | 10        |                 | 55   | ns    |  |

| t <sub>ACC1</sub> , Data Access Time,<br>RD↓ to Data Valid                                                 | (Note 5)             | 0   |                 | 55   | 0         |                 | 55   | ns    |  |

| t <sub>ID</sub> , Data Access Time,<br>INT↓ to Data Valid                                                  | (Note 5)             | 0   |                 | 50   | 0         |                 | 50   | ns    |  |

| t <sub>1H</sub> , t <sub>0H</sub> , RD↑ to Data High<br>Impedance State                                    | Figure 1<br>(Note 5) | 10  |                 | 50   | 10        |                 | 60   | ns    |  |

| t <sub>P</sub> , Delay From End of<br>Conversion to<br>Next Conversion                                     | (Note 6)             |     |                 | 20   |           |                 | 20   | ns    |  |

| t <sub>IC</sub> , INT↓ to Start of Next<br>Conversion                                                      | (Note 5)             | 500 |                 |      | 500       |                 |      | ns    |  |

- Note 1: Absolute maximum ratings are limits beyond which the life of the integrated circuit may be impaired. All voltages unless otherwise specified are measured with

- When the voltage at any pin exceeds the power supply rails ( $V_{IN}$  < or GND or  $V_{IN}$  >  $V_{CC}$ ) the absolute value of current at that pin should be limited to 25mA or less. Note 2:

- 0°C to +70°C and -40°C to +85°C operating temperature range devices are 100% tested with temperature limits guaranteed by 100% testing, sampling, or by Note 3: correlation with worst-case test conditions.

- Note 4: Typicals are parametric norm at 25°C.

- Parameter guaranteed and 100% production tested. Note 5:

- Parameter guaranteed. Parameters not 100% tested are not in outgoing quality level calculation. Note 6:

- Total unadjusted error includes offset, full scale, linearity, and sample and hold errors. Note 7:

- Total unadjusted error includes offset, full scale, linearity, and sample and note errors.

For  $-V_{REF} \ge V_{IN}$  the digital output code will be 0000 0000. Two on-chip diodes are tied to the analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the  $V_{CC}$  supply. Be careful, during testing at low  $V_{CC}$  levels (4.5V), as high level analog inputs (5V) cause this input diode to conduct especially at elevated temperatures, and cause errors for analog inputs near full scale. The spec allows 100mV forward bias of Note 8: either diode. This means that as long as the analog  $V_{IN}$  or  $V_{REF}$  does not exceed the supply voltage by more than 100mV, the output code will be correct. To achieve an absolute  $0V_{DC}$  to  $5V_{DC}$  input voltage range will therefore require a minimum supply voltage of  $4.900V_{DC}$  over temperature variations, initial tolerance and

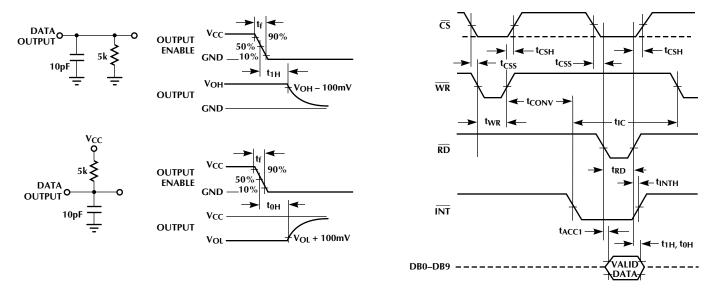

Figure 1. High Impedance Test Circuits and Waveforms

**Figure 2. Interrupt Mode Timing**

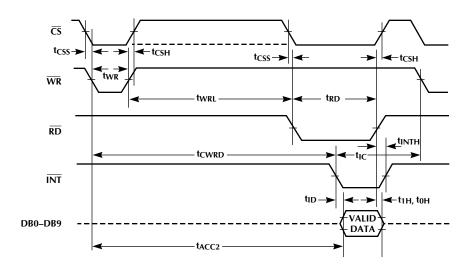

Figure 3. WR-RD Mode Timing

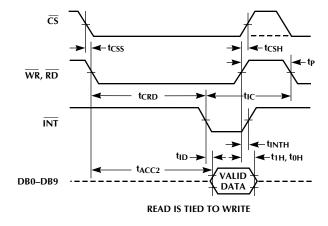

**Figure 4. RD Mode Timing**

## 1.0 FUNCTIONAL DESCRIPTION

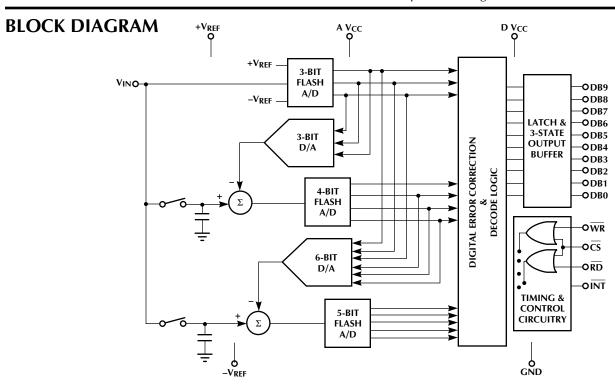

The ML2271 uses a three step flash technique for A/D conversion. This technique first performs a 3 bit flash conversion on  $V_{\rm IN}$  to determine the 3 most significant bits (MSB decision). These 3 MSB's are then cycled through an internal DAC to recreate the analog input. This reconstructed analog input signal from the DAC is then subtracted from the input, and the difference voltage is converted by a second 3 bit flash conversion providing the next 3 significant bits, called intermediate significant bits (ISB decision). This procedure is then performed again to provide the final 4 least significant bits (LSB decision).

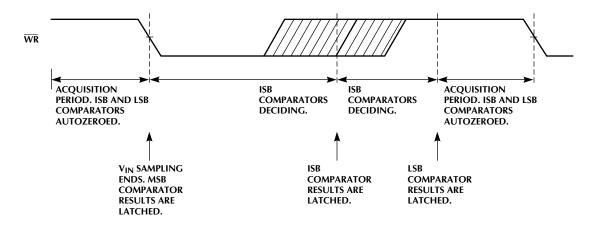

The ML2271 has a true internal sample and hold. The internal operating sequence is shown in Figure 5. The falling edge of WR opens the S/H sampling switch, ends the acquisition time for the analog input, and starts the conversion on the internally sample and held signal. Then the MSB, ISB, and LSB decisions are made. INT goes low at end of conversion and RD controls the data outputs. This falling edge of INT also closes the sampling switch and starts the acquisition period for the next conversion.

Figure 5. Operating Sequence

#### 1.1 ANALOG INPUT

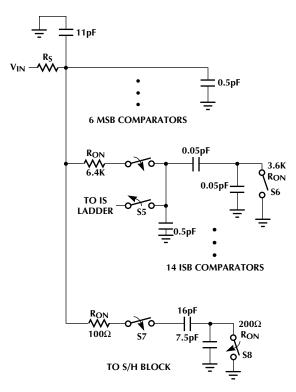

The analog input on the ML2271 behaves differently than inputs on conventional converters. The analog input current requirements change while the conversion is in progress, and the amount of input current depends on what cycle the converter is in.

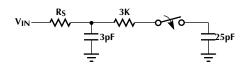

The input circuit for the converter is shown in Figure 6A with the equivalent input circuit shown in Figure 6B. The acquisition period for the S/H starts on INT falling edge and ends on WR falling edge.

The critical period for charging up the analog input occurs during the acquisition period and the source of the external signal on  $V_{\text{IN}}$  must adequately charge up the analog voltage during this time. To do this, the input must settle within the required analog accuracy tolerance 100ns before the end of the acquisition period so that the sampling capacitors have adequate time to store the input signal. If more time is needed due to finite charging or settling time of the external source, the  $\overline{\text{WR}}$  high period can be extended as long as is required.

#### 1.2 SAMPLE AND HOLD

The ML2271 does not have the limitation of an equivalent circuit implemented with a track/hold. An internal sample and hold acquires the analog signal, holds it internally, and then a conversion is performed on the sample and held signal. Since this is a true sample and hold function, the ML2271 can sample and hold signals with frequencies as high as  $150 \text{kHz} \otimes 5 \text{V}$  (slew rates as high as  $2.36 \text{V/}\mu\text{s}$ ) without sacrificing conversion accuracy.

#### 1.3 REFERENCE

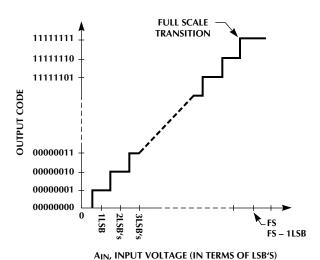

The  $+V_{REF}$  and  $-V_{REF}$  inputs are the reference voltages that determine the full scale and zero input voltages, respectively, for the A/D converter. Thus,  $+V_{REF}$  defines the analog input which produces a full scale output and  $-V_{REF}$  defines the analog input which produces an output code of all zeroes. The transfer function for the A/D converter is shown in Figure 7.

$+V_{REF}$  and  $-V_{REF}$  can be set to any voltage between GND and  $V_{CC}$ . This means that the reference voltages can be offset from GND and the difference between  $+V_{REF}$  and  $-V_{REF}$  can be made small to increase the resolution of the conversion. Note that the linearity error increases when  $[+V_{REF} - (-V_{REF})]$  decreases.

Figure 6A. Converter Input Circuit

Figure 6B. Converter Equivalent Input Circuit

Figure 7. A/D Transfer Characteristic

#### 1.4 POWER SUPPLY AND REFERENCE DECOUPLING

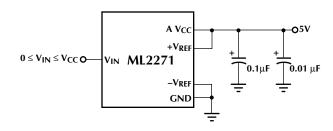

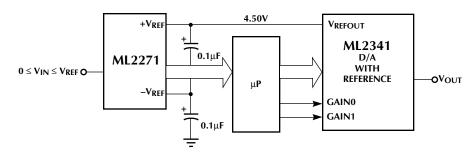

$0.1\mu F$  in parallel with  $0.01\mu F$  ceramic disc capacitors are recommended to bypass A  $V_{CC}$  to GND, as well as D  $V_{CC}$  to GND, using the shortest lead lengths possible.

If  $+V_{REF}$  and  $-V_{REF}$  inputs are driven by long lines, they should be bypassed by  $0.1\mu F$  in parallel with  $0.01\mu F$  ceramic disc capacitors at the reference input pins.

#### 1.5 DYNAMIC PERFORMANCE

### 1.5.1 Sinusoidal Inputs

Since the ML2271 has an internal sample and hold, the device can digitize high frequency sinusoids with little or no signal degradations. Using the Nyquist criteria, the highest frequency input to the converter could theoretically by 1/2 the sampling rate ( $f_S$ ). Any frequency components above  $f_S/2$  will be aliased below  $f_S/2$ . In most applications, these aliased components cause unacceptable distortion and must be filtered out of the input. If the input frequency is too close to  $f_S/2$ , then the requirements on the antialias filter become difficult or impossible to realize with standard component and tolerances. In most practical applications, the highest input frequency has to be limited to 1/3 to 1/4 of  $f_S$  in order to relax the filtering requirements enough to make a realizable antialias filter.

The maximum sampling rate (f<sub>MAX</sub>) for the ML2271 can be calculated as follows:

$$f_{MAX} = \frac{1}{t_{CONT} + t_P}$$

$$f_{MAX} = \frac{1}{1.45\mu s + 0.300\mu s}$$

$f_{MAX} = 570kHz$

t<sub>WR</sub> = Write Pulse Width

t<sub>WRD</sub> = Write to Data Delay

t<sub>P</sub> = Delay Time Between Conversions

Note that the dynamic performance specifications (SNR, HD, IMD and FR) for the ML2271 are all specified at 150kHz, which is less than 1/3 of the sampling rate, f<sub>S</sub>. This allows adequate margin between the input frequency and the aliased components to allow antialias filtering if needed.

In applications where aliased frequency components are acceptable and filtering of the input signal is not needed, the user can apply an input sinusoid higher than 150kHz to the device. Note, however, that as the input frequency increases above 150kHz, dynamic performance degradation will occur due to the finite bandwidth of the internal sample and hold.

## 1.5.2 Signal-to-Noise Ratio

Signal-to-noise ratio (SNR) is the measured signal to noise at the output of the converter. The signal is the rms magnitude of the fundamental. Noise is the rms sum of all the nonfundamental signals up to half the sampling

frequency. SNR is dependent on the number of quantization levels used in the digitization process; the more the levels, the smaller the quantization noise. The theoretical SNR for a sine wave is given by

$$SNR = (6.02N + 1.76) dB$$

where N is the number of bits. Thus for ideal 10-bit converter, SNR = 61.96 dB.

#### 1.5.3 Harmonic Distortion

Harmonic distortion is the ratio of the rms sum of harmonics to the fundamental. Total harmonic distortion (THD) of the ML2271 is defined as

$$20 \log \frac{(V_2^2 + V_3^2 + V_4^2 + V_5^2)^{1/2}}{V_1}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  are the rms amplitudes of the individual harmonics.

#### 1.5.4 Intermodulation Distortion

With inputs consisting of sine waves at two frequencies,  $f_A$  and  $f_B$ , any active device with nonlinearities will create distortion products, of order (m+n), at sum and difference frequencies of  $mf_A+nf_B$ , where  $m,n=0,1,2,3\ldots$  Intermodulation terms are those for which m or n is not equal to zero. The (IMD) intermodulation distortion specification includes the second order terms  $(f_A+f_B)$  and  $(f_A-f_B)$  and the third order terms  $(2f_A+f_B)$ ,  $(2f_A-f_B)$ , and  $(f_A-2f_B)$  only.

#### 1.6 DIGITAL INTERFACE

Depending on the way the external signals are applied to the ML2271, the timing of the conversion and resultant digital interface can be configured in three different modes.

While the operation for each mode is described below, there are some general rules that dictate the general relationships between  $\overline{CS}$ ,  $\overline{WR}$ ,  $\overline{RD}$ ,  $\overline{INT}$ , and DB0–DB9. The falling edge of  $\overline{WR}$  terminates the acquisition period and initiates a conversion.  $\overline{INT}$  is forced low when a conversion is internally completed.  $\overline{INT}$  is reset high by the  $\overline{RD}$  rising edge. DB0–DB9 is in the high impedance state except when both  $\overline{RD}$  and  $\overline{INT}$  are low.  $\overline{RD}$  low period does not affect the internal conversion but only determines when the digital signals DB0–DB9 are active; thus,  $\overline{RD}$  can occur anytime.  $\overline{CS}$  is used to select the device and needs to be low only while  $\overline{WR}$  is low or when  $\overline{RD}$  is low.

### 1.6.1 Interrupt Mode

Timing for the Interrupt Mode is shown in Figure 2. To do a conversion,  $\overline{CS}$  must be low to select the device.  $\overline{INT}$  falling edge starts the acquisition period. The falling edge of  $\overline{WR}$  ends the acquisition period and the MSB comparison is made. Then, the (Intermediate Significant

Bits) ISB and LSB decisions are made with internal timing signals. After the conversion is complete,  $\overline{\text{INT}}$  goes low indicating end of conversion. When  $\overline{\text{RD}}$  goes low, DB0–DB9 goes from high impedance to the active state with the digital result of the conversion.  $\overline{\text{INT}}$  is rest high and DB0–DB9 is reset to high impedance on the rising edge of  $\overline{\text{RD}}$ .

Interrupt Operation is intended to be used in interrupt driven systems or applications where  $\overline{\text{INT}}$  signals the transfer of data.

#### 1.6.2 Write-Read Mode

Write-Read Operation is the same as Interrupt Operation except that RD is brought low before the internal conversion is completed (before INT goes low).

Timing for Write-Read Operation is shown in Figure 3. To perform a conversion,  $\overline{CS}$  must be low to select the device.  $\overline{INT}$  falling edge starts the acquisition period. The falling edge of  $\overline{WR}$  ends the acquisition period and the MSB decision is made. Then, the ISB and LSB decisions are made by internal timing signals. In this mode,  $\overline{RD}$  is brought low before the internal conversion is completed. When the internal conversion is completed,  $\overline{INT}$  will be forced low and data will appear on DB0–DB9 as long as  $\overline{RD}$  is still low.  $\overline{INT}$  is reset high and DB0–DB9 is reset to high impedance on the rising edge of  $\overline{RD}$ .

Write-Read Operation is intended for applications where RD controls the transfer of data to a microprocessor.

#### 1.6.3 Read Mode

Read Mode Operation is implemented by tying  $\overline{RD}$  to  $\overline{WR}$  and keeping  $\overline{RD}$  and  $\overline{WR}$  low long enough so that the conversion time is totally determined by the internal timing signals.

Timing for the Read Mode is shown in Figure 4. To do a conversion,  $\overline{CS}$  must be low to select the device. The  $\overline{RD}$  and  $\overline{WR}$  falling edge starts the conversion.  $\overline{RD}$  and  $\overline{WR}$  is held low for the entire internal conversion. Thus, the MSB, ISB, and LSB comparisons along with the end of the acquisition period are made by internally generated timing signals. After the conversion is complete,  $\overline{INT}$  goes low. Since  $\overline{RD}$  is fixed low, DB0–DB9 will go from high impedance to active state as soon as  $\overline{INT}$  goes low.  $\overline{INT}$  is reset high and  $\overline{DB0}$ –DB9 is reset to high impedance on rising edge of  $\overline{WR}$  and  $\overline{RD}$ .

Read Mode Operation allows a conversion to be done with the device's own internal timing and thus, no eternal timing is needed.

## 1.6.4 Power-On Reset

When power is first applied, an internal power-on reset and timer circuit inhibits the  $\overline{CS}$  input and resets the internal circuitry to prevent the ML2271 from starting in an unknown state. During this period of approximately 5 $\mu$ s,  $\overline{INT}$  remains high and the data bus is in the high-impedance state.

# 2.0 TYPICAL APPLICATIONS

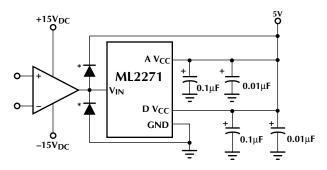

\*PROTECTION IS REQUIRED IF INPUT CURRENT > 25mA

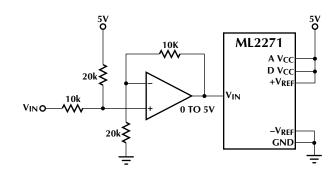

**Figure 8. Protecting the Input**

Figure 9. Using V<sub>CC</sub> as Reference for Ratiometric Operation

Figure 10. Using External Reference of D/A

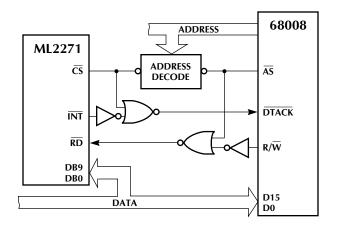

Figure 11. 68000 Type Interface to ML2271

Figure 12. ±2.5V Analog Input Range

# 2.0 TYPICAL APPLICATIONS (Continued)

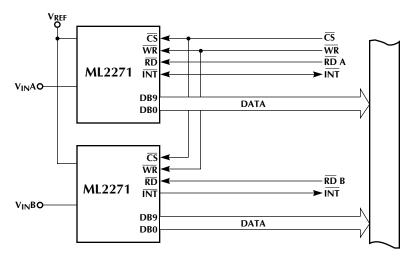

Figure 13. Simultaneous Sampling of Two Variables

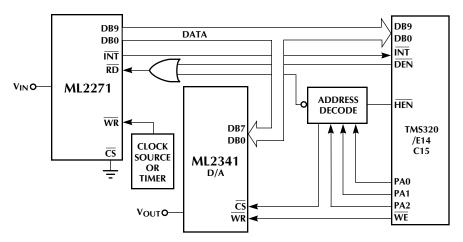

Figure 14. TMS320 Interface with D/A Output

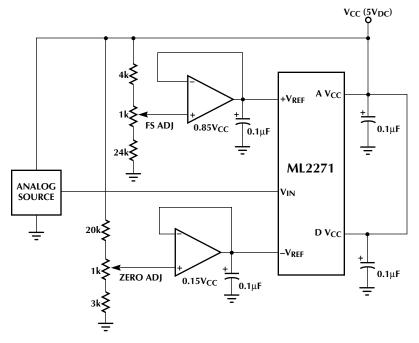

Figure 15. Operating with a Ratiometric Analog Signal of 15% of  $V_{CC}$  to 85% of  $V_{CC}$

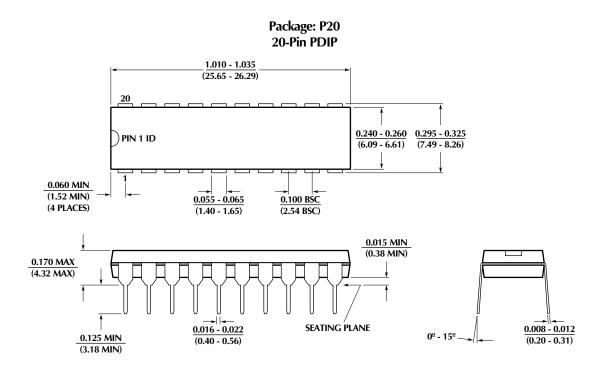

## PHYSICAL DIMENSIONS inches (millimeters)

## ORDERING INFORMATION

| PART NUMBER | LINEARITY ERROR | TEMPERATURE RANGE | PACKAGE           |

|-------------|-----------------|-------------------|-------------------|

| ML2271CIP   | ±1 LSB          | –40°C TO +85°C    | MOLDED DIP (P20)  |

| ML2271CIS   |                 | –40°C TO +85°C    | MOLDED SOIC (S20) |

| ML2271CCP   | ±1 LSB          | 0°C TO +70°C      | MOLDED DIP (P20)  |

| ML2271CCS   |                 | 0°C TO +70°C      | MOLDED SOIC (S20) |

© Micro Linear 1997 Micro Linear is a registered trademark of Micro Linear Corporation

Products described in this document may be covered by one or more of the following patents, U.S.: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; Japan: 2598946; 2619299. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others. The circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility or liability for use of any application herein. The customer is urged to consult with appropriate legal counsel before deciding on a particular application.

2092 Concourse Drive San Jose, CA 95131 Tel: 408/433-5200 Fax: 408/432-0295

To receive a price quote or to request a product sample, call or send e-mail to your local representative.

When sending e-mail, be sure to include the Micro Linear part number and whether you want a price quote or a sample in the subject line.

(i.e. subject: Sample request - ML part#xxxx)

Click here to find your local representative