### VND670SP

# Dual high-side switch with dual Power MOSFET gate driver (bridge configuration)

#### **Features**

| Туре     | R <sub>DS(on)</sub>         | I <sub>OUT</sub>   | V <sub>CC</sub> |

|----------|-----------------------------|--------------------|-----------------|

| VND670SP | $30 \mathrm{m}\Omega^{(1)}$ | 15A <sup>(1)</sup> | 40V             |

- 1. Per each channel.

- 5V logic level compatible inputs

- Gate drive for two external power MOSFET

- Undervoltage and overvoltage shutdown

- Overvoltage clamp

- Thermal shutdown

- Cross-conduction protection

- Current limitation

psolete

- Very low standby power consumption

- PWM operation up to 10 KHz

- Protection against loss of ground and loss of V<sub>CC</sub>

- Reverse battery protection:

#### **Description**

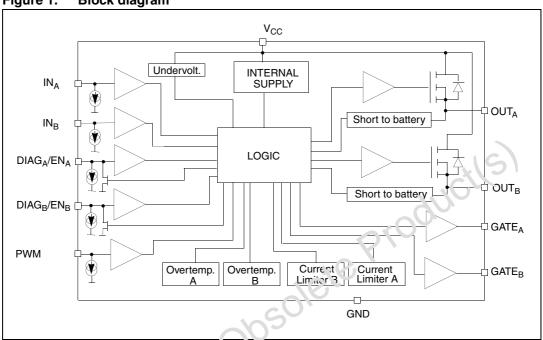

The VNL67J3P is a monolithic device made using \$1 Nicroelectronics VIPower technology M0-3. intended for driving motors in full bridge configuration. The device integrates two 30 mW Power MOSFET in high-side configuration, and provides gate drive for two external Power MOSFET used as low side switches. INA and INB allow to select clockwise or counter clockwise drive or brake; DIAGA/ENA, DIAGB/ENB allow to disable one half bridge and feedback diagnostic. Built-in thermal shutdown, combined with a current limiter, protects the chip in overtemperature and short circuit conditions. Short to battery protects the external connected low-side Power MOSFET.

Table 1. Device summary

| Package    | Order codes |               |  |  |

|------------|-------------|---------------|--|--|

|            | Tube        | Tape and reel |  |  |

| PowerSO-10 | VND670SP    | VND670SP13TR  |  |  |

Contents VND670SP

### **Contents**

| 1        | Bloc | ck diagram and pin description                                                                                              | 5    |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------|------|

| 2        | Elec | ctrical specifications                                                                                                      | 6    |

|          | 2.1  | Absolute maximum ratings                                                                                                    | 6    |

|          | 2.2  | Thermal data                                                                                                                | 7    |

|          | 2.3  | Electrical characteristics                                                                                                  | 7    |

| 3        | Арр  | olication information                                                                                                       | 11   |

|          | 3.1  | Normal operating conditions                                                                                                 | . 12 |

|          | 3.2  | Fault conditions                                                                                                            | . 13 |

|          | 3.3  | Normal operating conditions                                                                                                 | . 13 |

| 4        | Pacl | kage and packing information                                                                                                | . 16 |

|          | 4.1  | ECOPACK® packages                                                                                                           | . 16 |

|          | 4.2  | PowerSO-10 mechanical data                                                                                                  | . 16 |

|          | 4.3  | PowerSO-10 packing information                                                                                              | . 18 |

| 5<br>005 | Revi | kage and packing information  ECOPACK® packages  PowerSO-10 mechanical data  PowerSO-10 packing information  rision history | . 19 |

|          |      |                                                                                                                             |      |

VND670SP List of tables

### List of tables

| Table 1.  | Device summary                                                  |

|-----------|-----------------------------------------------------------------|

| Table 2.  | Suggested connections for unused and not connected pins5        |

| Table 3.  | Absolute maximum ratings                                        |

| Table 4.  | Thermal data (per island)                                       |

| Table 5.  | Power                                                           |

| Table 6.  | Switching                                                       |

| Table 7.  | Protection and diagnostic                                       |

| Table 8.  | PWM8                                                            |

| Table 9.  | Logic inputs8                                                   |

| Table 10. | Enable                                                          |

| Table 11. | Truth table in normal operating conditions                      |

| Table 12. |                                                                 |

| Table 13. | Electrical transient requirements                               |

| Table 14. | PowerSO-10 mechanical data                                      |

| Table 15. | Document revision history                                       |

|           |                                                                 |

|           |                                                                 |

|           | *6                                                              |

|           | 18                                                              |

|           |                                                                 |

|           | 5                                                               |

|           |                                                                 |

|           |                                                                 |

|           | Fruth table in fault conditions (detected on OUT <sub>A</sub> ) |

|           | 16                                                              |

|           |                                                                 |

|           |                                                                 |

|           | AU.                                                             |

|           |                                                                 |

|           |                                                                 |

|           |                                                                 |

|           |                                                                 |

| 16        |                                                                 |

| 2011      |                                                                 |

| -105      |                                                                 |

| Uh.       |                                                                 |

|           | ste Product(s)                                                  |

|           |                                                                 |

|           |                                                                 |

|           |                                                                 |

List of figures VND670SP

## **List of figures**

| Figure 1.<br>Figure 2.<br>Figure 3.<br>Figure 4.<br>Figure 5.<br>Figure 6. | Block diagram                                              |

|----------------------------------------------------------------------------|------------------------------------------------------------|

| Figure 7. Figure 8. Figure 9. Figure 10. Figure 11. Figure 12. Figure 13.  | Typical application circuit for DC to 10 KHz PWM operation |

| Figure 14.                                                                 | SO-28 tape and reel shipment (suffix "TR")                 |

| Obsoli                                                                     | Block diagram                                              |

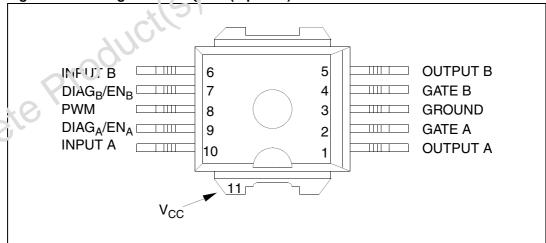

### 1 Block diagram and pin description

Figure 1. Block diagram

Figure 2. Configuration diagram (top view)

Table 2. Suggested connections for unused and not connected pins

| Connection / pin | Status | N.C. | Output | Input                 |

|------------------|--------|------|--------|-----------------------|

| Floating         | X      | X    | Х      | Х                     |

| To ground        |        | Х    |        | Through 10KΩ resistor |

### 2 Electrical specifications

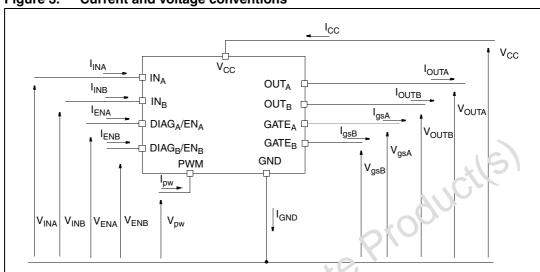

Figure 3. Current and voltage conventions

#### 2.1 Absolute maximum ratings

Stressing the device above the rating listed in the "Absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality document.

| Table 2.  | Absolute   | maximum        | ratings |

|-----------|------------|----------------|---------|

| I GOIO JI | / .DOO!GLO | IIIWAAIIIIWIII | utiligo |

|     | Symbo!            | Parameter                                                  | Value       | Unit |

|-----|-------------------|------------------------------------------------------------|-------------|------|

| 10  | $v_{cc}$          | Supply voltage                                             | -0.340      | V    |

| 60/ | I <sub>max1</sub> | Maximum output current (continuous)                        | 15          | Α    |

| 002 | I <sub>max2</sub> | Maximum output current (250ms pulse duration)              | 20          | Α    |

| 0.  | I <sub>R</sub>    | Reverse DC output current                                  | - 15        | Α    |

|     | I <sub>IN</sub>   | Input current                                              | +/- 10      | mA   |

|     | I <sub>EN</sub>   | Enable pin current                                         | +/- 10      | mA   |

|     | $I_{pw}$          | PWM pin current                                            | +/- 10      | mA   |

|     | I <sub>gs</sub>   | Output gate current                                        | +/- 20      | mA   |

|     | $V_{ESD}$         | Electrostatic discharge ( $R = 1.5K\Omega$ ; $C = 100pF$ ) | 2000        | V    |

|     | Tj                | Junction operating temperature                             | - 40 to 150 | °C   |

|     | T <sub>stg</sub>  | Storage temperature                                        | - 55 to 150 | °C   |

#### 2.2 Thermal data

Table 4. Thermal data (per island)

| Symbol                | Parameter                           | Max. value        | Unit |

|-----------------------|-------------------------------------|-------------------|------|

| R <sub>thj-case</sub> | Thermal resistance junction-case    | 1.4               | °C/W |

| R <sub>thj-amb</sub>  | Thermal resistance junction-ambient | 50 <sup>(1)</sup> | °C/W |

<sup>1.</sup> When mounted using the recommended pad size on FR-4 board (see AN515 Application Note).

#### 2.3 Electrical characteristics

Values specified in this section are for 9V <  $V_{CC}$  < 18V; -40°C <  $T_j$  < 150°C, unless otherwise stated.

Table 5. Power

| Symbol            | Parameter                  | Test conditions                                                 | Mn. | Гур. | Max.     | Unit     |

|-------------------|----------------------------|-----------------------------------------------------------------|-----|------|----------|----------|

| V <sub>CC</sub>   | Operating supply voltage   |                                                                 | 5.5 |      | 36       | V        |

| R <sub>ON</sub>   | On-state resistance        | I <sub>LOAD</sub> = 12,<br>I <sub>LOAD</sub> = 12A<br>Ti = 25°C |     | 26   | 50<br>30 | mΩ<br>mΩ |

| Is                | Supply current             | On-state<br>Off-state                                           |     |      | 15<br>40 | mΑ<br>μΑ |

| V <sub>gate</sub> | Gate output voltaçe        |                                                                 | 5.0 |      | 8.5      | V        |

| $V_{\rm gs,cl}$   | Gate output clarip voltage | I <sub>gs</sub> = - 1 mA                                        | 6.0 | 6.8  | 8.0      | V        |

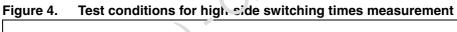

Table 6. Switching ( $V_{CC} = 13V$ ,  $R_{LOAD} = 1.1\Omega$ )

|     | Synibal                               | Parameter                           | Test conditions        | Min. | Тур. | Max. | Unit  |

|-----|---------------------------------------|-------------------------------------|------------------------|------|------|------|-------|

|     | <sup>‡</sup> D(on)                    | Turn-on delay time                  |                        |      | 50   | 150  | μs    |

| 16  | t <sub>D(off)</sub>                   | Turn-off delay time                 |                        |      | 45   | 135  | μs    |

| 60, | t <sub>r</sub>                        | Output voltage rise time            | Input rise time < 1µs  |      | 50   | 150  | μs    |

| 000 | t <sub>f</sub>                        | Output voltage fall time            | (see Figure 4)         |      | 40   | 120  | μs    |

|     | (dV <sub>OUT</sub> /dt) <sub>on</sub> | Turn-on voltage slope               |                        |      | 160  | 500  | V/ ms |

|     | $(dV_{OUT}/dt)_{off}$                 | Turn-off voltage slope              |                        |      | 230  | 1200 | V/ ms |

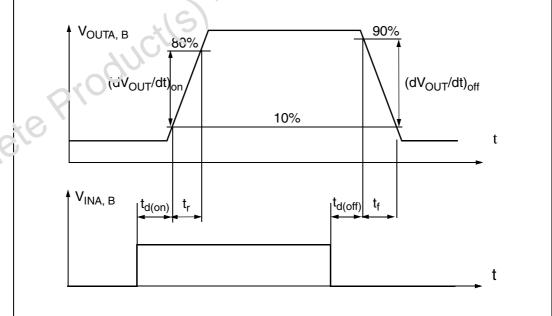

|     | t <sub>dong</sub>                     | V <sub>gs</sub> turn-on delay time  | C1=4.7nF               |      | 0.5  | 2    | μs    |

|     | t <sub>rg</sub>                       | V <sub>gs</sub> rise time           | Break to ground        |      | 2.6  | 10   | μs    |

|     | t <sub>doffg</sub>                    | V <sub>gs</sub> turn-off delay time | configuration          |      | 1.0  | 5.0  | μs    |

|     | t <sub>fg</sub>                       | V <sub>gs</sub> fall time           | (see <i>Figure 5</i> ) |      | 2.2  | 10   | μs    |

|     | t <sub>del</sub>                      | External MOSFET turn-on dead time   | (see Figure 6)         |      | 600  | 1800 | μs    |

Table 7. Protection and diagnostic

| Symbol           | Parameter                                              | Test conditions                  | Min.                    | Тур. | Max.                    | Unit |

|------------------|--------------------------------------------------------|----------------------------------|-------------------------|------|-------------------------|------|

| V <sub>USD</sub> | Undervoltage shutdown                                  |                                  |                         |      | 5.5                     | V    |

| V <sub>OV</sub>  | Overvoltage shutdown                                   |                                  | 36                      | 43   |                         | V    |

| I <sub>LIM</sub> | Current limitation                                     |                                  | 30                      | 45   |                         | Α    |

| T <sub>TSD</sub> | Thermal shutdown temperature                           | V <sub>IN</sub> = 3.25 V         | 150                     | 170  | 200                     | °C   |

| V <sub>ocl</sub> | Output turn-off clamp voltage                          | I <sub>LOAD</sub> = 12A, L = 6mH | V <sub>CC</sub> -<br>55 |      | V <sub>CC</sub> -<br>41 | V    |

| V <sub>sat</sub> | External MOSFET saturation voltage detection threshold |                                  | 2.5                     | 4.2  | 5.5                     | ٧    |

#### Table 8. PWM

| Symbol               | Parameter                 | Test conditions                                     | Mi 1.                        | īур.                         | Max.                         | Unit   |

|----------------------|---------------------------|-----------------------------------------------------|------------------------------|------------------------------|------------------------------|--------|

| $V_{pwl}$            | PWM low level voltage     | *                                                   | 6,                           |                              | 1.5                          | V      |

| I <sub>pwl</sub>     | PWM pin current           | $V_{pw} = 1.5V$                                     | 1                            |                              |                              | μA     |

| $V_{pwh}$            | PWM high level voltage    | 50                                                  | 3.25                         |                              |                              | V      |

| I <sub>pwh</sub>     | PWM pin current           | `' <sub>p.v.</sub> :: 3.25V                         |                              |                              | 10                           | μΑ     |

| $V_{pwhhyst}$        | PWM hysteresis voltage    |                                                     | 0.5                          |                              |                              | ٧      |

| V <sub>pwcl</sub>    | PWM clamp voltage         | $I_{pw} = 1 \text{ mA}$<br>$I_{pw} = -1 \text{ mA}$ | V <sub>CC</sub> +0.3<br>-5.0 | V <sub>CC</sub> +0.7<br>-3.5 | V <sub>CC</sub> +1.0<br>-2.0 | V<br>V |

| V <sub>pwtest</sub>  | Test nicae PWM pin        |                                                     | -3.5                         | -2.0                         | -0.5                         | ٧      |

| I <sub>pwte 3t</sub> | Test mode PWM pin current | V <sub>pwtest</sub> = -2.0 V                        | -2000                        | -500                         |                              | μΑ     |

## Table 9. Logic inputs

| Symbol             | Parameter                | Test conditions                               | Min.        | Тур.        | Max.        | Unit   |

|--------------------|--------------------------|-----------------------------------------------|-------------|-------------|-------------|--------|

| V <sub>IL</sub>    | Input low level voltage  |                                               |             |             | 1.5         | V      |

| I <sub>INL</sub>   | Input current            | V <sub>IN</sub> = 1.5 V                       | 1           |             |             | μΑ     |

| V <sub>IH</sub>    | Input high level voltage |                                               | 3.25        |             |             | ٧      |

| I <sub>INH</sub>   | Input current            | V <sub>IN</sub> = 3.25 V                      |             |             | 10          | μΑ     |

| V <sub>IHYST</sub> | Input hysteresis voltage |                                               | 0.5         |             |             | ٧      |

| V <sub>ICL</sub>   | Input clamp voltage      | I <sub>IN</sub> =1mA<br>I <sub>IN</sub> =-1mA | 6.0<br>-1.0 | 6.8<br>-0.7 | 8.0<br>-0.3 | V<br>V |

Table 10. Enable

| Symbol             | Parameter                       | Test conditions                                                                                         | Min.        | Тур.        | Max.        | Unit   |

|--------------------|---------------------------------|---------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|--------|

| V <sub>ENL</sub>   | Enable low level voltage        | Normal operation (DIAG <sub>X</sub> /EN <sub>X</sub> pin acts as an input pin)                          |             |             | 1.5         | V      |

| I <sub>ENL</sub>   | Enable pin current              | V <sub>EN</sub> = 1.5 V                                                                                 | 1           |             |             | μΑ     |

| V <sub>ENH</sub>   | Enable high level voltage       | Normal operation<br>(DIAG <sub>X</sub> /EN <sub>X</sub> pin acts<br>as an input pin)                    | 3.25        |             |             | V      |

| I <sub>ENH</sub>   | Enable pin current              | V <sub>EN</sub> = 3.25 V                                                                                |             |             | 10          | μΑ     |

| V <sub>EHYST</sub> | Enable hysteresis voltage       | Normal operation (DIAG <sub>X</sub> /EN <sub>X</sub> pin acts as an input pin)                          | 0.5         | (           | 115         | V      |

| V <sub>ENCL</sub>  | Enable clamp voltage            | I <sub>EN</sub> = 1mA<br>I <sub>EN</sub> = -1mA                                                         | 6.0<br>-1.0 | 3.3<br>-0.7 | 8.0<br>-0.3 | V<br>V |

| V <sub>DIAG</sub>  | Enable output low level voltage | Fault operation (DIAG <sub>X</sub> /EN <sub>X</sub> pin acts as an input pin) $I_{EN} = 1.6 \text{ me}$ |             |             | 0.4         | V      |

V<sub>gsA, B</sub> 80% 20% t

Figure 5. Test conditions for external Power MOSFET switching times measurement

### 3 Application information

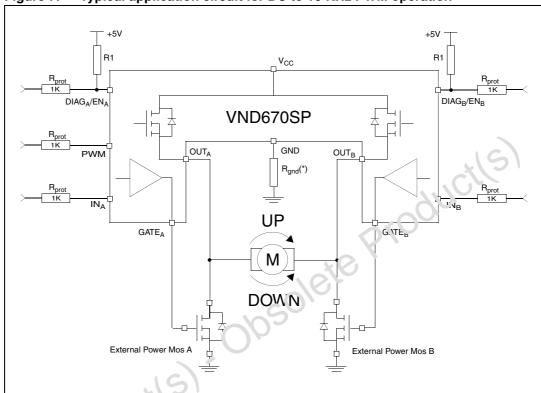

Figure 7. Typical application circuit for DC to 10 KHz PWM operation

Note: 1 Reverse battery protection: series relay in  $V_{CC}$  line:  $R_{gnd}$ =0 Ohms; series fuse in  $V_{CC}$  line with antiparallel 2.049 between ground and  $V_{CC}$ :  $R_{gnd}$ =10 Ohms.

2 Layout hints, the connection between GND pin of the VN670SP and the Power MOSFET SOUF.CL connections should be kept short enough to ensure that the dynamic difference between these two points never exceed 1V for the bridge to operate properly.

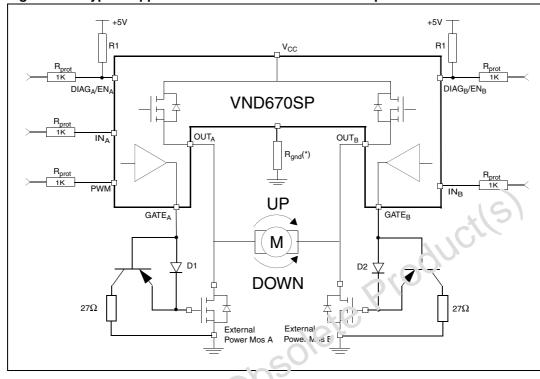

Figure 8. Typical application circuit for a 20 KHz PWM operation

Note: 1 Reverse battery protection: series relay in  $V_{CC}$  line:  $R_{gnd} = 0$  Ohms; series fuse in  $V_{CC}$  line with antiparallel diode between ground and  $V_{CC}$ :  $R_{gnd} = 10$  Ohms.

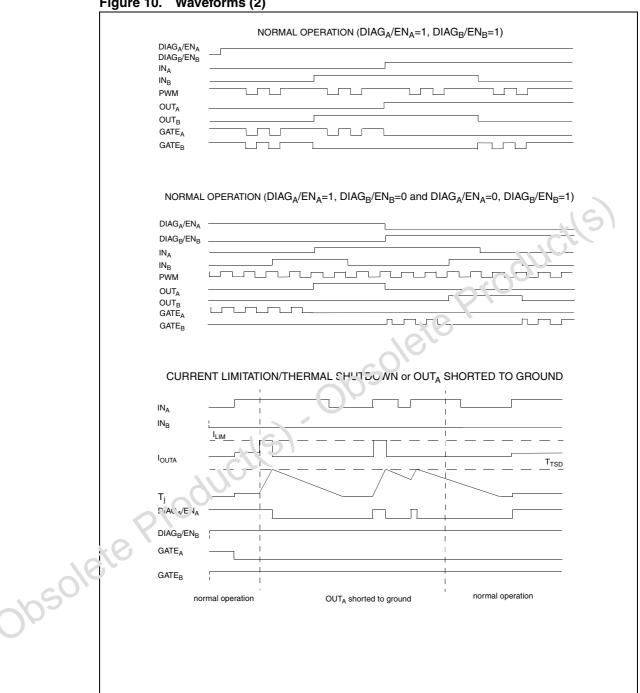

#### 3.1 Normal operating conditions

Table 11. Truth table in normal operating conditions

|        | INA | I.V <sub>B</sub> | DIAG <sub>A</sub> /EN <sub>A</sub> | DIAG <sub>B</sub> /EN <sub>B</sub> | OUTA | OUTB | GATEA | GATEB | Comment                  |

|--------|-----|------------------|------------------------------------|------------------------------------|------|------|-------|-------|--------------------------|

|        | .0, | 1                | 1                                  | 1                                  | Н    | Н    | L     | L     | Brake to V <sub>CC</sub> |

| 76     | 1   | 0                | 1                                  | 1                                  | Н    | L    | L     | Н     | Clockwise                |

| 1050\\ | 0   | 1                | 1                                  | 1                                  | L    | Н    | Н     | L     | Counter cw               |

| 002    | 0   | 0                | 1                                  | 1                                  | L    | L    | Н     | Н     | Brake to GND             |

|        | Χ   | Х                | 0                                  | 0                                  | L    | L    | L     | L     | Stand by                 |

|        | 1   | Х                | 1                                  | 0                                  | Н    | L    | L     | L     | HS <sub>A</sub> only     |

|        | 0   | Х                | 1                                  | 0                                  | L    | L    | Н     | L     | MOS <sub>A</sub> only    |

|        | Χ   | 1                | 0                                  | 1                                  | L    | Н    | L     | L     | HS <sub>B</sub> only     |

|        | Х   | 0                | 0                                  | 1                                  | L    | L    | L     | Н     | MOS <sub>B</sub> only    |

Note: 1 In normal operating conditions the  $DIAG_X/EN_X$  pin is considered as an input pin by the device. This pin must be externally pulled high.

2 PWM pin usage:

In all cases, a "0" on the PWM pin will turn-off both  $GATE_A$  and  $GATE_B$  outputs. When PWM rises back to "1",  $GATE_A$  or  $GATE_B$  turn on again depending on the input pin state.

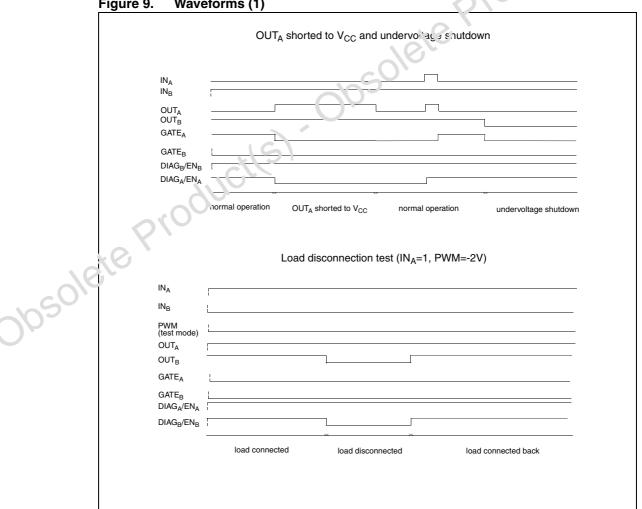

#### 3.2 Fault conditions

In case of a fault conditions the  $\mathsf{DIAG}_X/\mathsf{EN}_X$  pin is considered as an output pin by the device. The fault conditions are:

- overtemperature on one or both high-sides;

- short to battery condition on the output (saturation detection on the external connected Power MOSFET).

Possible origins of fault conditions may be:

- OUT<sub>A</sub> is shorted to ground ---> overtemperature detection on high-side A.

- OUT<sub>A</sub> is shorted to  $V_{CC}$  ---> external Power MOSFET saturation detection (driven by  $GATE_A$ ).

When a fault condition is detected, the user can know which power element is in fault by monitoring the IN<sub>A</sub>, IN<sub>B</sub>, DIAG<sub>A</sub>/EN<sub>A</sub> and DIAG<sub>B</sub>/EN<sub>B</sub> pins.

In any case, when a fault is detected, the faulty half bridge is latched off. To  $t_{CIT}$ -on the respective output (GATE<sub>X</sub> or OUT<sub>X</sub>) again, the input signal must rise from low to high level.

|     |                 |                                    |                                    |      | A/                | ~     |       |

|-----|-----------------|------------------------------------|------------------------------------|------|-------------------|-------|-------|

| INA | IN <sub>B</sub> | DIAG <sub>A</sub> /EN <sub>A</sub> | DIAG <sub>B</sub> /EN <sub>B</sub> | OUTA | o∕JT <sub>B</sub> | GATEA | GATEB |

| 1   | 1               | 0                                  | 1                                  | Open | Н                 | L     | L     |

| 1   | 0               | 0                                  | 1                                  | Onen | Open              | L     | L     |

| 0   | 1               | 0                                  | 1                                  | Open | Н                 | L     | L     |

| 0   | 0               | 0                                  | 1,                                 | Open | Open              | L     | L     |

| Х   | Х               | 0                                  | 0                                  | Open | Open              | L     | L     |

| 1   | Х               | 0                                  | 0                                  | Open | Open              | L     | L     |

| 0   | Х               | 7/7                                | 0                                  | Open | Open              | L     | L     |

| Х   | -1C             | 0                                  | 1                                  | Open | Н                 | L     | L     |

| X   | 0               | 0                                  | 1                                  | Open | Open              | L     | L     |

Table 12. Truth table in fault conditions (detected on  $CU_{\Delta}$ )

#### 3.3 Test mode

The PWM pin allows to test the load connection between two half-bridges. In the test mode ( $V_{pwm}$ =-2V) the external Power Mos gate drivers are disabled. The IN<sub>A</sub> or IN<sub>B</sub> inputs allow to turn-on the high-side A or B, respectively, in order to connect one side of the load at  $V_{CC}$  voltage. The check of the voltage on the other side of the load allow to verify the continuity of the load connection. In case of load disconnection the DIAD<sub>X</sub>/EN<sub>X</sub> pin corresponding to the faulty output is pulled down.

100ms,  $0.01\Omega$

400ms,  $2\Omega$

| ISO T/R              |                      | Test level           |                       |                       |                      |  |  |

|----------------------|----------------------|----------------------|-----------------------|-----------------------|----------------------|--|--|

| 7637/1<br>Test pulse | ı                    | II                   | III                   | IV                    | Delays and impedance |  |  |

| 1                    | - 25V <sup>(1)</sup> | - 50V <sup>(1)</sup> | - 75V <sup>(1)</sup>  | - 100V <sup>(1)</sup> | 2ms, $10\Omega$      |  |  |

| 2                    | + 25V <sup>(1)</sup> | + 50V <sup>(1)</sup> | + 75V <sup>(1)</sup>  | + 100V <sup>(1)</sup> | $0.2 ms, 10 \Omega$  |  |  |

| 3a                   | - 25V <sup>(1)</sup> | - 50V <sup>(1)</sup> | - 100V <sup>(1)</sup> | - 150V <sup>(1)</sup> | 0.1μs, 50Ω           |  |  |

| 3b                   | + 25V <sup>(1)</sup> | + 50V <sup>(1)</sup> | + 75V <sup>(1)</sup>  | + 100V <sup>(1)</sup> | 0.1μs, 50Ω           |  |  |

- 6V<sup>(1)</sup>

$+66.5V^{(2)}$

- 7V<sup>(1)</sup>

+ 86.5V<sup>(2)</sup>

Table 13. **Electrical transient requirements**

- 4V<sup>(1)</sup>

$+ 26.5V^{(1)}$

1. All functions of the device are performed as designed after exposure to disturbance.

- 5V<sup>(1)</sup>

$+46.5V^{(2)}$

One or more functions of the device is not performed as designed after exposure and cannot be returned to proper operation without replacing the device.

Figure 9. Waveforms (1)

4

Figure 10. Waveforms (2)

### 4 Package and packing information

## 4.1 ECOPACK® packages

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

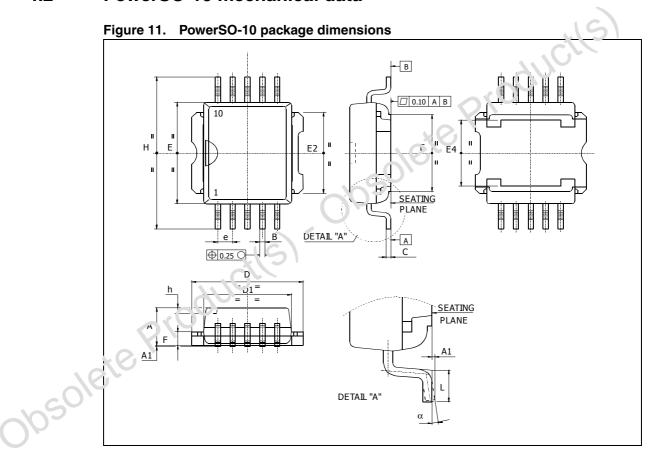

#### 4.2 PowerSO-10 mechanical data

Table 14. PowerSO-10 mechanical data

|      | Dim               | mm    |       |       |  |  |

|------|-------------------|-------|-------|-------|--|--|

|      | Dim.              | Min.  | Тур.  | Max.  |  |  |

|      | А                 | 3.35  |       | 3.65  |  |  |

|      | A <sup>(1)</sup>  | 3.4   |       | 3.6   |  |  |

|      | A1                | 0     |       | 0.10  |  |  |

|      | В                 | 0.40  |       | 0.60  |  |  |

|      | B <sup>(1)</sup>  | 0.37  |       | 0.53  |  |  |

|      | С                 | 0.35  |       | 0.55  |  |  |

|      | C <sup>(1)</sup>  | 0.23  |       | 0.32  |  |  |

|      | D                 | 9.40  | . (   | 9.60  |  |  |

|      | D1                | 7.40  | 01    | 7.60  |  |  |

|      | Е                 | 9.30  | .xe   | 9.50  |  |  |

|      | E2                | 7.20  | 7/8,0 | 7.60  |  |  |

|      | E2 <sup>(1)</sup> | 7.30  |       | 7.50  |  |  |

|      | E4                | 5.90  |       | 6.10  |  |  |

|      | E4 <sup>(1)</sup> | 5.90  |       | 6.30  |  |  |

|      | е                 | 1/3   | 1.27  |       |  |  |

|      | F AU              | 1.25  |       | 1.35  |  |  |

|      | F <sup>(1</sup> ) | 1.20  |       | 1.40  |  |  |

|      | H                 | 13.80 |       | 14.40 |  |  |

| 10   | H <sup>(1)</sup>  | 13.85 |       | 14.35 |  |  |

| COIL | h                 |       | 0.50  |       |  |  |

| 002  | L                 | 1.20  |       | 1.80  |  |  |

|      | L <sup>(1)</sup>  | 0.80  |       | 1.10  |  |  |

|      | α                 | 0°    |       | 8°    |  |  |

|      | o <sup>(1)</sup>  | 2°    |       | 8°    |  |  |

<sup>1.</sup> Muar only POA P013P.

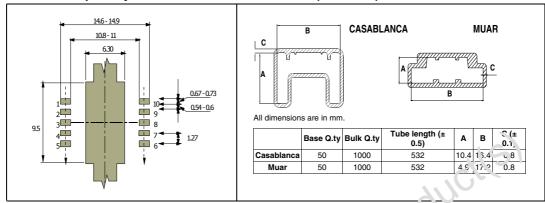

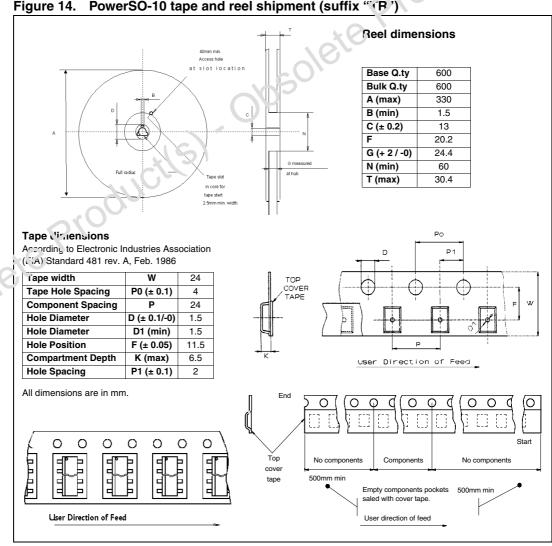

#### PowerSO-10 packing information 4.3

Figure 12. PowerSO-10 suggested Figure 13. PowerSO-10 tube shipment (no suffix) pad layout

PowerSO-10 tape and reel shipment (suffix "(P')

VND670SP Revision history

## 5 Revision history

Table 15. Document revision history

| Date        | Revision | Changes                                                                                                                          |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------|

| 03-May-2006 | 1        | Initial release.                                                                                                                 |

| 11-Dec-2008 | 2        | Document reformatted and restructured.  Added contents, list of tables and figures.  Added <i>ECOPACK® packages</i> information. |

Obsolete Product(s). Obsolete Product(s)

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its sulhsidia. 'eu ('ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and sen ices described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and solvices described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property Liquis is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a trainant covering the use in any manner whatsoever of such third party products or services or any intellectual property containe 2 to 3 in 3 in 3.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE ANCION BALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNE'SE FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN VIRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCT'S OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PF OP ENTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of S. p. or ucts with provisions different from the statements and/or technical features set forth in this document shall immediately void any war and granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liabi. To T.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics:

VND670SP-E VND670SPTR-E