# AN8725FH

## Semiconductor laser power control IC

### ■ Overview

The AN8725FH is a laser driver IC that can set a laser emitting level to a maximum precision in recording and playback of an optical recording equipment such as PD, and can modulate a laser light in tune with the external signal.

### ■ Features

- Digital setting of playback current, peak current, bias current and abnormal light emitting level

- Peak current and bias current can be modulated by the external signal.

- Driving current set-up (digital set-up)

- For playback: 8-bit + 4-bit (0 mA to 80 mA)

- 5-bit + 4-bit (0 mA to 150 mA)

- For peak: 4-bit + 8-bit (0 mA to 150 mA)

- For bias: 4-bit + 8-bit (0 mA to 150 mA)

- Laser output light monitoring circuit built-in

- Abnormal light emitting detecting function built-in:

- Possible to set up excessive and insufficient light emitting levels with 4-bit DAC for playback and recording, respectively.

- Supply voltage abnormality detection:

- Voltage down (3.9 V or less), voltage up (6.1 V or more)

### ■ Applications

- Optical disk drive

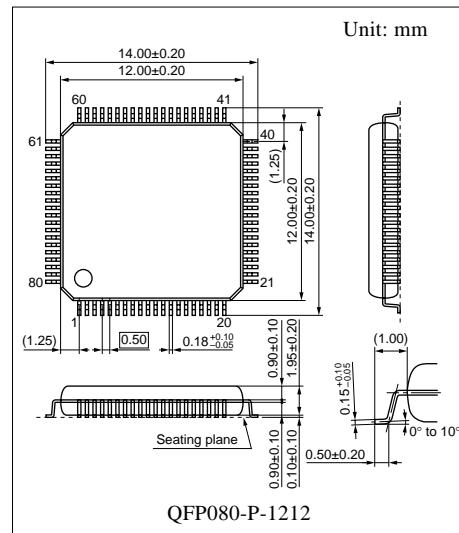

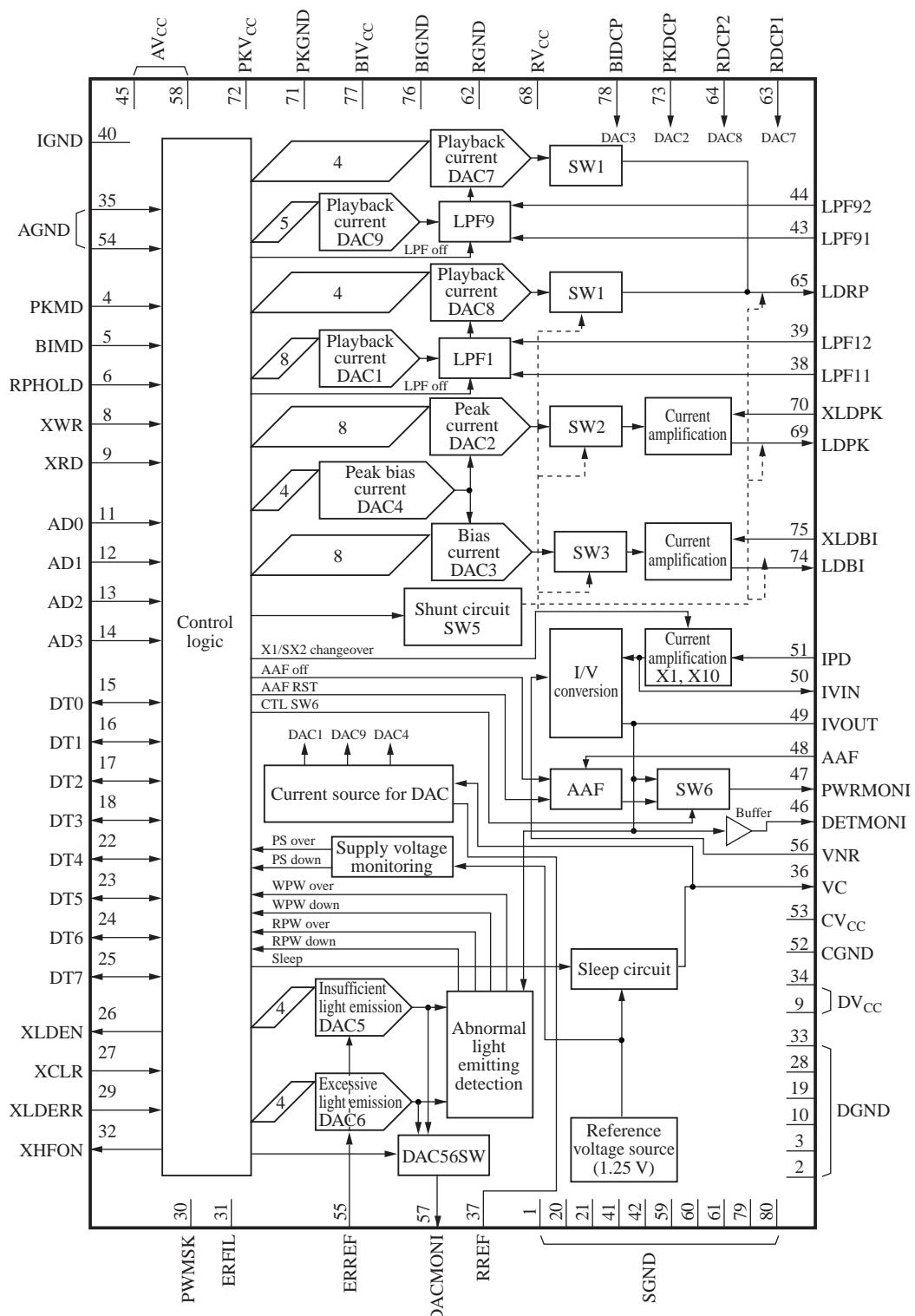

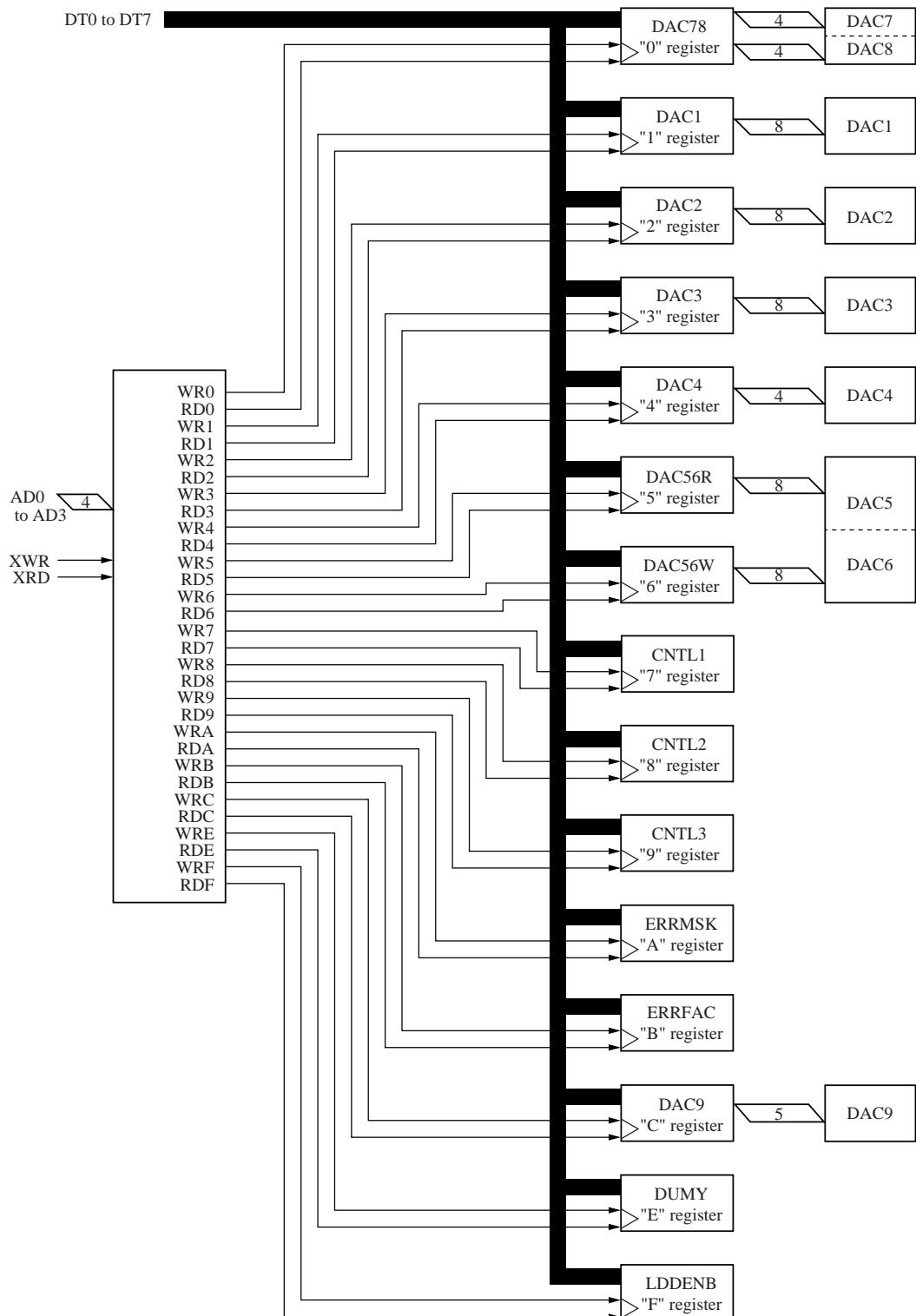

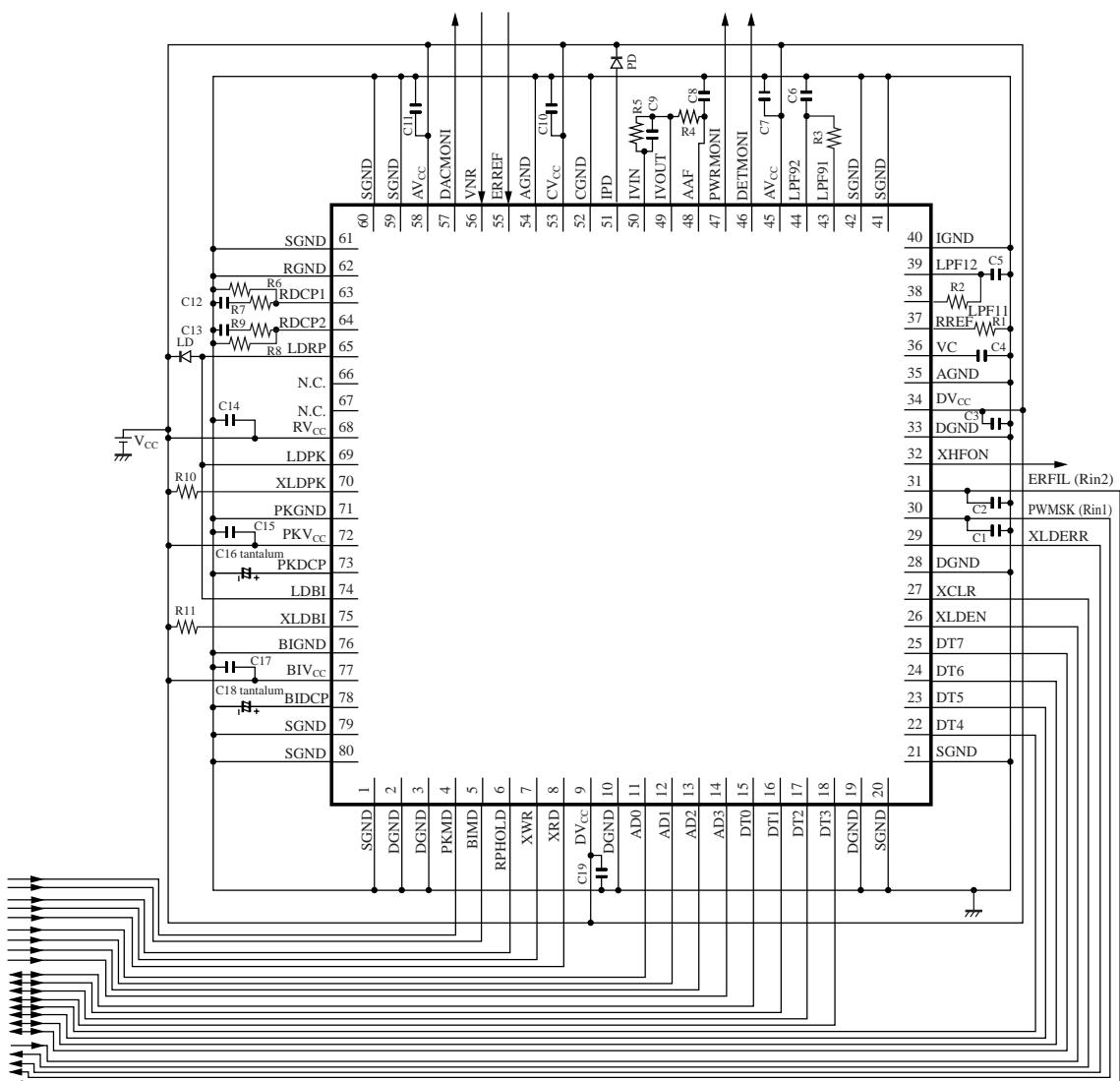

## ■ Block Diagram

## ■ Pin Descriptions

Note) Description on notations of "Category" in the following list:

IN : Input pin I/O : Input/output pin (pull-down with  $100\text{ k}\Omega$ )

IND : Input pin (pull-down with 100 k $\Omega$ ) PS : Power supply/GND pin

INU : Input pin (pull-up with 100 k $\Omega$ )      MSC : Parts connecting pin, etc.

OUT: Output pins

### A: Analog function

## D: Digital functions

| Pin No. | Symbol           | Category | Description |                                                                                                                                                                                                                  |

|---------|------------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SGND             | PS       | D           | Pin connected to the chip substrate.<br>Must be used in the same potential as other GND pins.                                                                                                                    |

| 2       | DGND             | PS       | D           | GND pin exclusive for a logic circuit.                                                                                                                                                                           |

| 3       | DGND             | PS       | D           | Must be used in the same potential as other GND pins.                                                                                                                                                            |

| 4       | PKMD             | IND      | D           | Peak current modulation signal input pin.<br>In high-level, the current set up with DAC2 is superimposed on LD.                                                                                                  |

| 5       | BIMD             | IND      | D           | Bias current modulation signal input pin.<br>In high-level, the current set up with DAC3 is superimposed on LD.                                                                                                  |

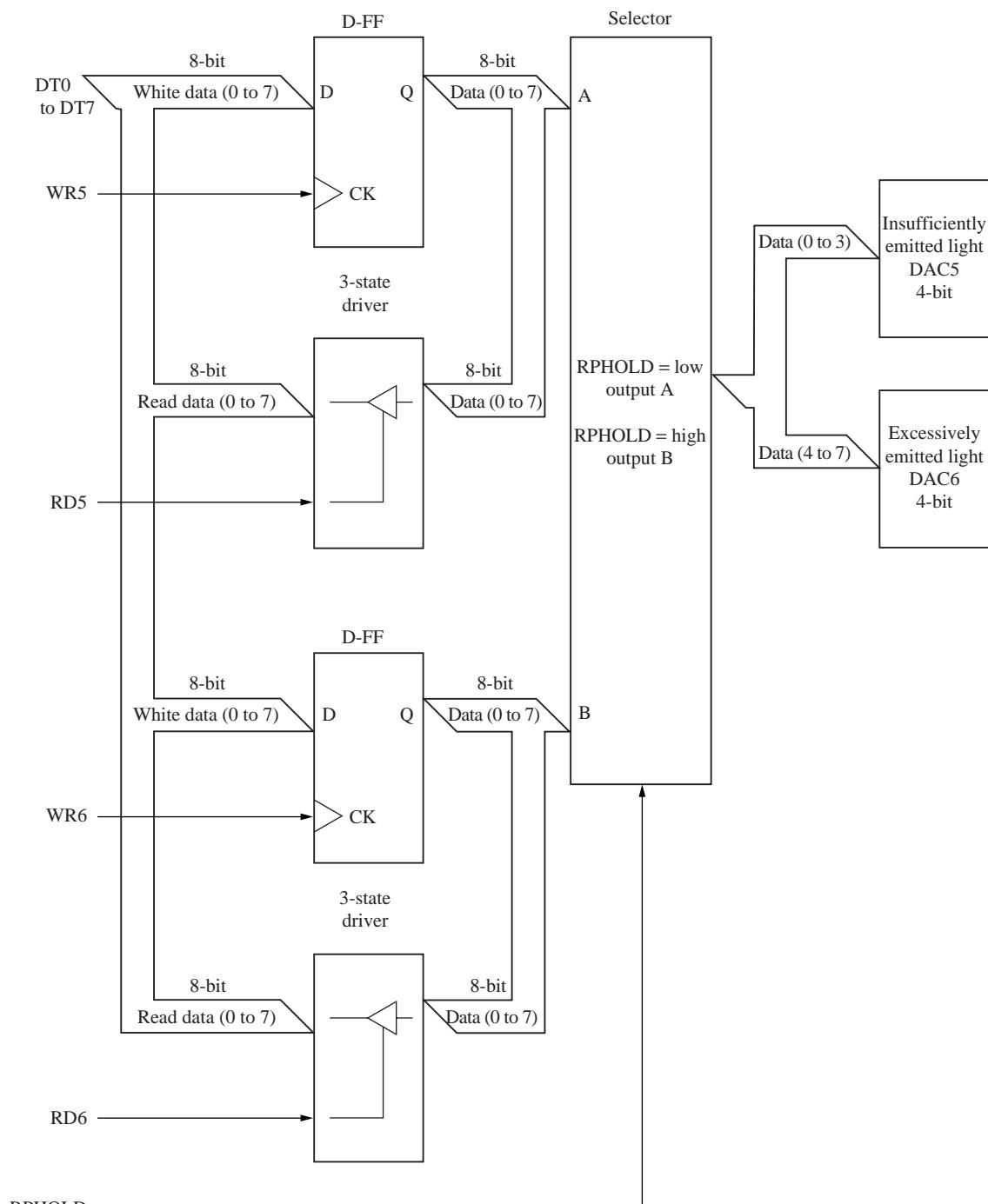

| 6       | RPHOLD           | IND      | D           | Record gate signal input pin.<br>Inputs a low-level in playback and a high-level in recording.<br>Switches an amp. of light monitoring signal, abnormally emitted light detection level and on/off of HF module. |

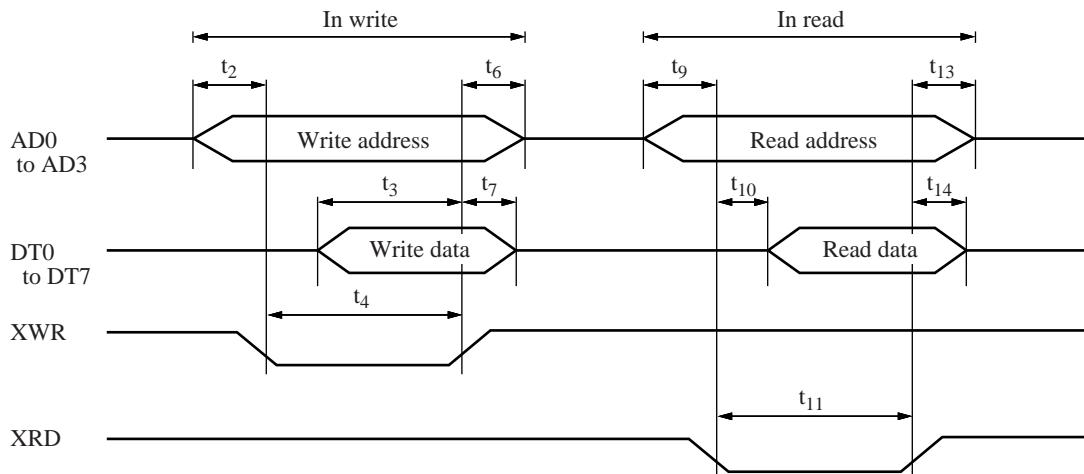

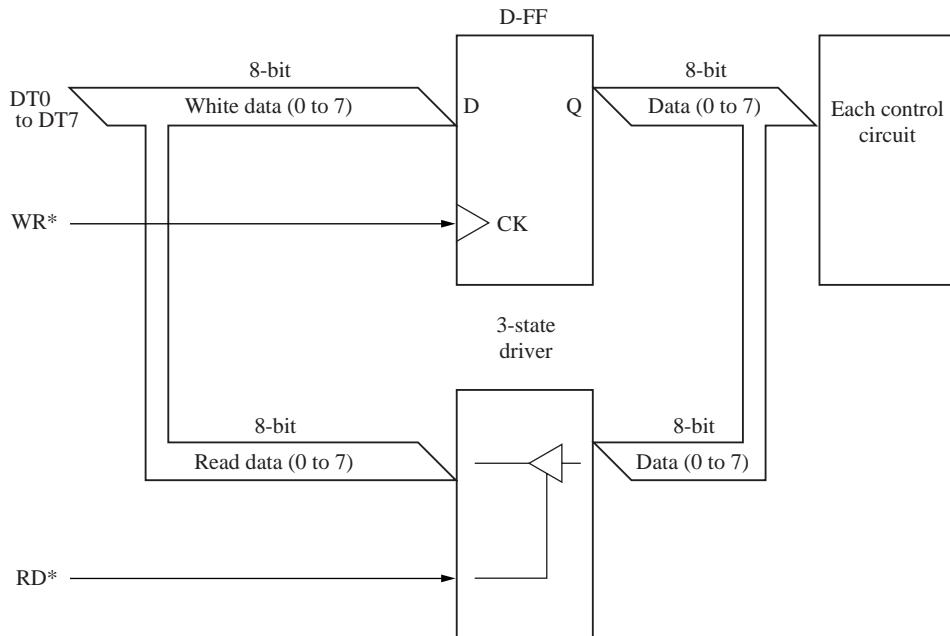

| 7       | XWR              | INU      | D           | Register writing signal pin.<br>Selects a register specified by address in a fall edge and writes a bus data on the register of the address specified in the rise edge.                                          |

| 8       | XRD              | INU      | D           | Register read-out signal pin.<br>Register data of the address specified in low appears on the bus.                                                                                                               |

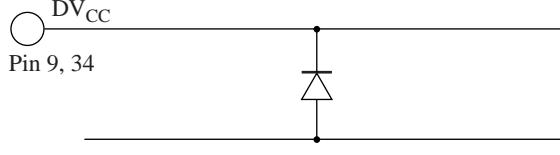

| 9       | DV <sub>CC</sub> | PS       | D           | Power supply pin exclusive for a logic circuit.<br>Must be used in the same potential as other power supply pins.                                                                                                |

| 10      | DGND             | PS       | D           | GND pin exclusive for a logic circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                  |

| 11      | AD0              | IND      | D           | 4-bit address pin for registers.<br>Selects the register to be accessed.                                                                                                                                         |

| 12      | AD1              | IND      | D           |                                                                                                                                                                                                                  |

| 13      | AD2              | IND      | D           |                                                                                                                                                                                                                  |

| 14      | AD3              | IND      | D           |                                                                                                                                                                                                                  |

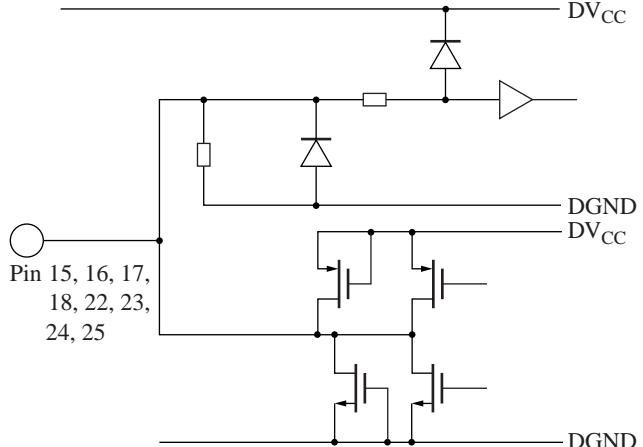

| 15      | DT0              | I/O      | D           | Data I/O 8-bit bus pin.<br>The bus to set the data to be written on a register and to read out the data of a register.                                                                                           |

| 16      | DT1              | I/O      | D           |                                                                                                                                                                                                                  |

| 17      | DT2              | I/O      | D           |                                                                                                                                                                                                                  |

| 18      | DT3              | I/O      | D           |                                                                                                                                                                                                                  |

| 19      | DGND             | PS       | D           | GND pin exclusive for a logic circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                  |

## ■ Pin Descriptions (continued)

| Pin No. | Symbol | Category | Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20      | SGND   | PS       | D           | Pin connected to the chip substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21      | SGND   | PS       |             | Must be used in the same potential as other GND pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 22      | DT 4   | I/O      | D           | Data I/O 8-bit bus pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 23      | DT 5   | I/O      |             | The bus to set the data to be written on a register and to read out the data of a register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24      | DT 6   | I/O      | D           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25      | DT 7   | I/O      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 26      | XLDEN  | INU      | D           | LD enable input pin.<br>In a high-level or open mode, LD becomes off and open. This state is suited to check the LD characteristics in keeping a connection to the IC. At the time power off, both ends of LD are short-circuited by the IC for protection. In the low-level, it returns to a normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27      | XCLR   | IND      |             | Clear signal input pin.<br>Sets an LDDENB register to "0" in the low-level and presets the status of each DAC and each switch to an initial state as defined separately. But six registers for an abnormal detection are not cleared. In this state, each output of a current amplification 1, 2, 3 are in the off state and a shunt circuit becomes on to continue to protect LD.<br>Setting this pin to the high-level and the LDDENB register to "1", it returns to a normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 28      | DGND   | PS       | D           | GND pin exclusive for a logic circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

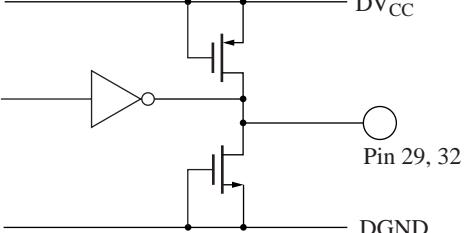

| 29      | XLDERR | OUT      |             | Laser abnormality detection output pin.<br>When a supply voltage or a laser light emission exceeds a fixed range, it goes to low-level. A supply voltage abnormality is detected for the voltage drop (3.9 V or less) or voltage rise (6.1 V or more). And an abnormal light emission is detected for an excessive or weaker light emission set up by 4-bit DAC5 and DAC6. This abnormality detection is latched so as to prevent it from being reset until ERRCLR register is set to "1".<br>Further, each DAC output of a playback current, a peak current and a bias current can be set to off, a shunt circuit be set to on and LD between anode and GND be short-circuited by $100\ \Omega$ so that LD can be protected. This protection function is latched to keep it from being reset until ERRCLR is set to "1". Selection of either operation or non-operation for this operation can be made by an STPMSK register. |

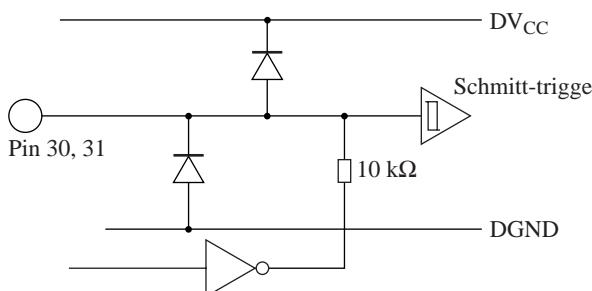

| 30      | PWMSK  | MSC      | D           | The pin to set up the mask time for a transitional response output that comes out at switching a detection level of excessive or insufficient light emission by RPHOLD. Set a mask time by an external capacitor between PWMSK and DGND and the resistor (10 k $\Omega$ ) inside the IC. This pin is for a schmitt-trigger input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## ■ Pin Descriptions (continued)

| Pin No. | Symbol           | Category |   | Description                                                                                                                                                                                                                                                       |

|---------|------------------|----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | ERFIL            | MSC      | D | Filter setting pin to avoid a detection error of laser abnormality caused by noise.<br>Connect an external capacitor between ERFIL and DGND, and set a filter together with a resistor (10 kΩ) inside the IC. This pin is for schmitt-trigger input.              |

| 32      | XHFON            | OUT      | D | HF module on/off control signal output pin.<br>High corresponds to off and low to on.                                                                                                                                                                             |

| 33      | DGND             | PS       | D | GND pin exclusive to a logic circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                    |

| 34      | DV <sub>CC</sub> | PS       | D | Power supply pin exclusive to a logic circuit.<br>Must be used in the same potential as other power supply pins.                                                                                                                                                  |

| 35      | AGND             | PS       | A | GND pin exclusive to a analog circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                   |

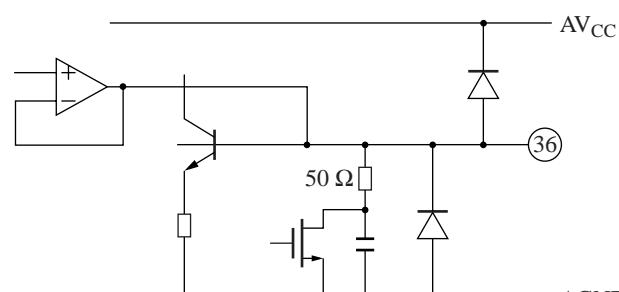

| 36      | VC               | MSC      | A | Output pin for reference voltage (1.25 V).<br>Connects a capacitor C between this pin and AGND for de-coupling.                                                                                                                                                   |

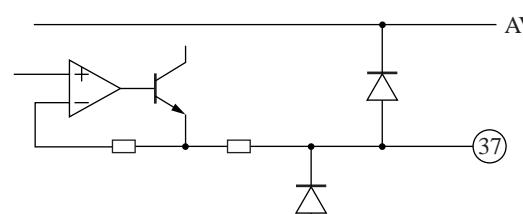

| 37      | RREF             | MSC      | A | Reference resistor connecting pin to determine an output current for each DAC.<br>Connect a resistor of 10 kΩ between RREF and AGND.                                                                                                                              |

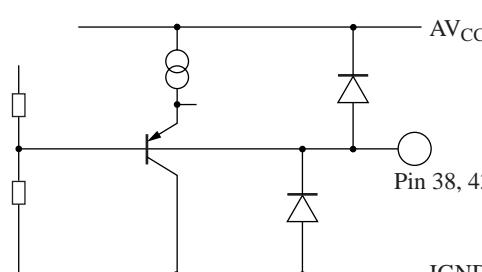

| 38      | LPF11            | MSC      | A | LPF characteristic setting pin for DAC1 and DAC8.                                                                                                                                                                                                                 |

| 39      | LPF12            | MSC      | A | Connect an external resistor between LPF11 and LPF12, and then capacitor between LPF12 and IGND to set up a cutoff frequency.                                                                                                                                     |

| 40      | IGND             | PS       | A | GND pin for playback power supply setting DAC1, DAC9 and disturbance reduction LPF.<br>Must be used in the same potential as other GND pins.                                                                                                                      |

| 41      | SGND             | PS       | D | Pin connected to the chip substrate.                                                                                                                                                                                                                              |

| 42      | SGND             | PS       | D | Must be used in the same potential as other GND pins.                                                                                                                                                                                                             |

| 43      | LPF91            | MSC      | A | LPF characteristic setting pin for DAC9 and DAC7.                                                                                                                                                                                                                 |

| 44      | LPF92            | MSC      | A | Connect an external resistor between LPF91 and LPF92 and then capacitor between LPF92 and IGND to set a cutoff frequency.                                                                                                                                         |

| 45      | AV <sub>CC</sub> | PS       | A | Power supply pin for an analog circuit, a reference supply voltage circuit, etc.<br>Must be used in the same potential as other power supply pins.                                                                                                                |

| 46      | DETMONI          | OUT      | A | Pin to monitor a signal for detecting abnormally emitted light.<br>In a playback mode, the signal output is five times that in recording (ten times is possible by a register setting). Has offset to VNR due to being outputted through a buffer of transistors. |

| 47      | PWRMONI          | OUT      | A | Laser emitting light monitor signal.<br>In a low-level of RPHOLD, the amplifier output has 10 times gain compared with recording, and is equipped with AFF.                                                                                                       |

## ■ Pin Descriptions (continued)

| Pin No. | Symbol           | Category |   | Description                                                                                                                                                                                                                                                                           |

|---------|------------------|----------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

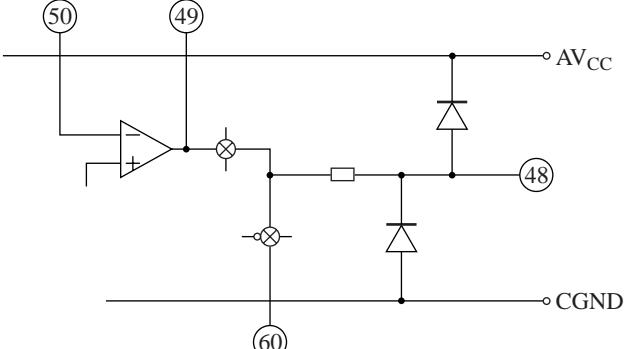

| 48      | AAF              | MSC      | A | AAF characteristic setting pin for optical monitor circuit.<br>Connect an external resistor, capacitor between AAF and IVOOUT and set up a cutoff frequency.                                                                                                                          |

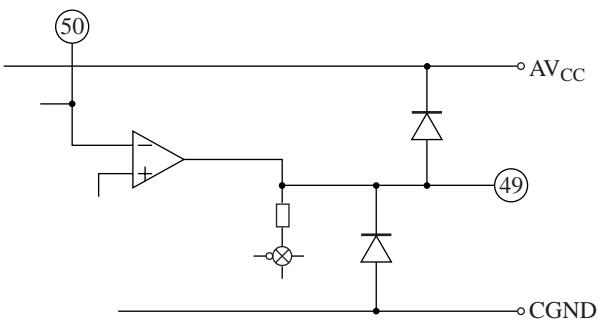

| 49      | IVOOUT           | OUT      | A | I to V conversion signal output pin.<br>Connect an external variable resistor between IVIN and IVOOUT.                                                                                                                                                                                |

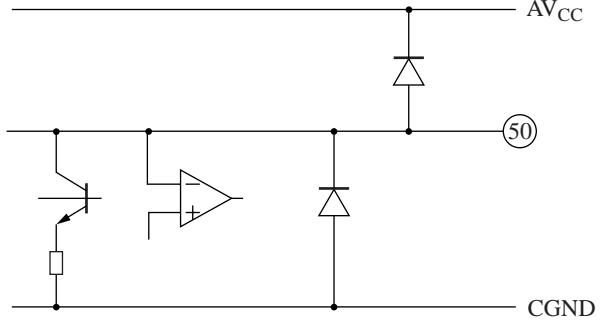

| 50      | IVIN             | MSC      | A | I to V conversion resistor connection pin.<br>Connect an external variable resistor between IVIN and IVOOUT.                                                                                                                                                                          |

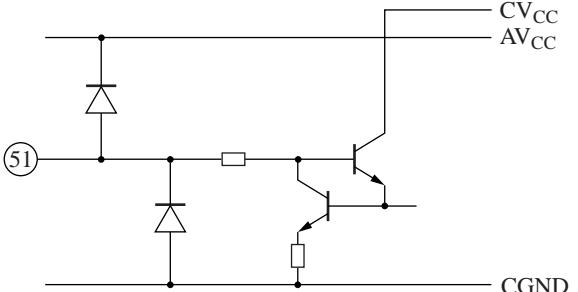

| 51      | IPD              | MSC      | A | Pin photo diode (PD) connection pin.<br>Connect a pin photo diode for detecting a semiconductor laser emitting light. Connect anode to this pin.<br>Applicable to a source-type PD which has a typical value of 40 $\mu$ A to 160 $\mu$ A output in object lens output power of 1 mW. |

| 52      | CGND             | PS       | A | GND pin in an optical monitor circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                                       |

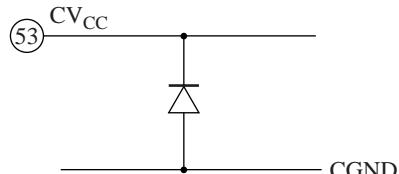

| 53      | CV <sub>CC</sub> | PS       | A | Power supply pin in an optical monitor circuit.<br>Must be used in the same potential as other power supply pins.                                                                                                                                                                     |

| 54      | AGND             | PS       | A | GND pin exclusive to a analog circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                                       |

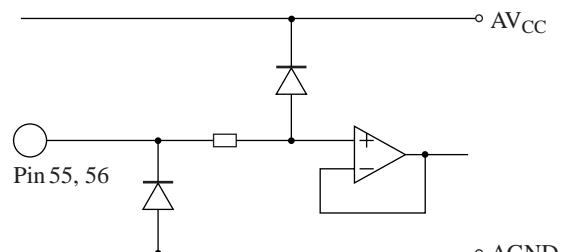

| 55      | ERREF            | IN       | A | Abnormally emitting light detecting range setting pin.<br>Sets a full scale voltage of DAC5 and DAC6.<br>A setting range is VNR or more and input range of an external ADC or less.                                                                                                   |

| 56      | VNR              | IN       | A | Reference level input pin for PWRMONI output.<br>Input a reference voltage of 1.25 V of an external ADC.                                                                                                                                                                              |

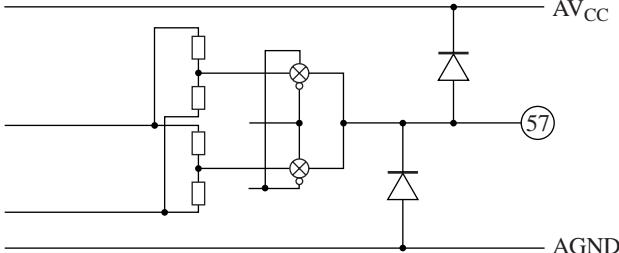

| 57      | DACMONI          | OUT      | A | DAC5, DAC6 monitor pin.<br>DAC5 voltage is outputted when DAC56 SW register is low, DAC6 voltage is outputted when DAC6 voltage is high.                                                                                                                                              |

| 58      | AV <sub>CC</sub> | PS       | A | Power supply pin for an analog circuit, a reference supply voltage circuit, etc.<br>Must be used in the same potential as other power supply pins.                                                                                                                                    |

| 59      | SGND             | PS       | D | Pin connected to the chip substrate.                                                                                                                                                                                                                                                  |

| 60      | SGND             | PS       | D | Must be used in the same potential as other GND pins.                                                                                                                                                                                                                                 |

| 61      | SGND             | PS       | D |                                                                                                                                                                                                                                                                                       |

| 62      | RGND             | PS       | A | GND pin for the lead current setting DAC7 and DAC8.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                          |

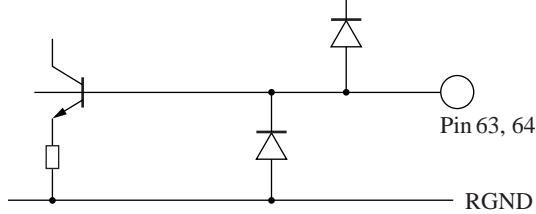

| 63      | RDCP1            | MSC      | A | Pin to connect a de-coupling capacitor to protect the output current of DAC7, the read current setting circuit, from disturbance by a switching noise such as peak current.<br>(Connects a capacitor between RDCP1 and RGND.)                                                         |

## ■ Pin Descriptions (continued)

| Pin No. | Symbol            | Category |   | Description                                                                                                                                                                                                                         |

|---------|-------------------|----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64      | RDCP2             | MSC      | A | Pin to connect a de-coupling capacitor to protect the output current of DAC7, the read current setting circuit, from disturbance by a switching noise such as peak current.<br>(Connects a capacitor between RDCP2 and RGND.)       |

| 65      | LDRP              | OUT      | A | Source type read current (DAC1, DAC7, DAC8, DAC9) output pin.<br>Possible to set up the range of 0 mA to 150 mA in the precision of 8-bit + 4-bit + 5-bit + 4-bit.<br>Output voltage range is 1.0 V to 3.5 V.                       |

| 66      | N.C.              | —        | — | N.C. pin.                                                                                                                                                                                                                           |

| 67      | N.C.              | —        | — | Open the pin or connect to GND.                                                                                                                                                                                                     |

| 68      | RV <sub>CC</sub>  | PS       | A | Power supply pin for read current setting DAC7, DAC8.<br>Consumes approximately a quarter of the necessary read current.<br>Must be used in the same potential as other power supply pins.                                          |

| 69      | LDPK              | OUT      | A | Source-type peak current (DAC2) output pin.<br>Possible to set the range of 0 mA to 150 mA in the accuracy of 8-bit.<br>The output voltage range is 1.0 V to 3.2 V.                                                                 |

| 70      | XLDPK             | IN       | A | Sink-type peak current output pin.<br>Approximately three fourths of LDRK output current are outputted from this pin.                                                                                                               |

| 71      | PKGND             | PS       | A | GND pin of DAC2 in the peak current setting circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                       |

| 72      | PKV <sub>CC</sub> | PS       | A | DAC2 power supply pin in the peak current setting circuit.<br>Consumes approximately a quarter of the setting current.<br>Must be used in the same potential as other power supply pins.                                            |

| 73      | PKDCP             | MSC      | A | Pin to connect a de-coupling capacitor to avoid the output current disturbance, which is caused by a switching noise such as peak current, in peak current setting circuit DAC2.<br>(Connects a capacitor between PKDCP and PKGND.) |

| 74      | LDBI              | OUT      | A | Source-type bias current (DAC3) output pin.<br>Possible to set the range of 0 mA to 150 mA in the accuracy of 8-bit.<br>Output voltage range is 1.0 V to 3.2 V.                                                                     |

| 75      | XLDBI             | IN       | A | Sink-type peak current output pin.<br>Approximately three fourths of LDBI output current are outputted from this pin.                                                                                                               |

| 76      | BIGND             | PS       | A | GND pin of a bias current setting circuit DAC3.<br>Must be used in the same potential as other GND pins.                                                                                                                            |

| 77      | BIV <sub>CC</sub> | PS       | A | Power supply pin of a bias current setting circuit DAC3.<br>Consumes approximately one fourth of a setting current.<br>Must be used in the same potential as other power supply pins.                                               |

### ■ Pin Descriptions (continued)

| Pin No. | Symbol | Category |   | Description                                                                                                                                                                                                                           |

|---------|--------|----------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78      | BIDCP  | MSC      | A | Pin to connect a de-coupling capacitor to avoid the output current disturbance, which is caused by a switching noise such as bias current, of a bias current setting circuit DAC3.<br>(Connects a capacitor between BIDCP and BIGND.) |

| 79      | SGND   | PS       | D | Pin connected to the chip substrate.                                                                                                                                                                                                  |

| 80      | SGND   | PS       | D | Must be used in the same potential as other GND pins.                                                                                                                                                                                 |

### ■ Absolute Maximum Ratings

| Parameter                                   | Symbol           | Rating                       | Unit |

|---------------------------------------------|------------------|------------------------------|------|

| Supply voltage                              | V <sub>CC</sub>  | 7.0                          | V    |

| Input voltage                               | V <sub>IN</sub>  | –0.4 to V <sub>CC</sub> +0.4 | V    |

| Output voltage                              | V <sub>OUT</sub> | –0.4 to V <sub>CC</sub> +0.4 | V    |

| Parts connecting pin voltage                | V <sub>MSC</sub> | –0.4 to V <sub>CC</sub> +0.4 | V    |

| Supply current                              | I <sub>CC</sub>  | 80                           | mA   |

| Pin current                                 | I <sub>PIN</sub> | –100 to +100                 | mA   |

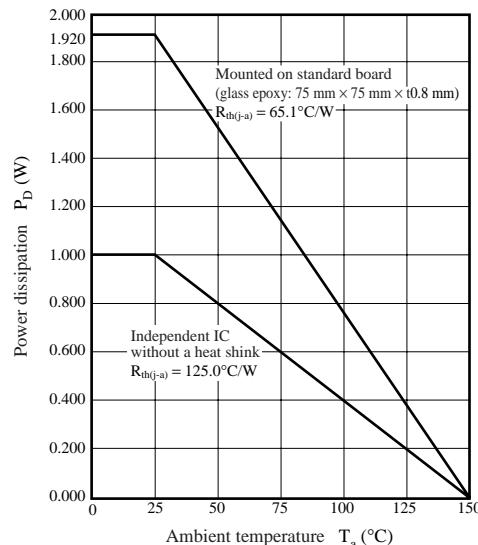

| Power dissipation <sup>*2</sup>             | P <sub>D</sub>   | 600                          | mW   |

| Operating ambient temperature <sup>*1</sup> | T <sub>opr</sub> | –20 to +75                   | °C   |

| Storage temperature <sup>*1</sup>           | T <sub>stg</sub> | –55 to +150                  | °C   |

Note) <sup>\*1</sup>: Except for the operating ambient temperature and storage temperature, all ratings are for T<sub>a</sub> = 25°C.

<sup>\*2</sup>: The power dissipation shown is for the IC package in single unit at T<sub>a</sub> = 75°C.

Refer to "■ Application Notes, 1. P<sub>D</sub>—T<sub>a</sub> curves of QFP080-P-1212".

### ■ Recommended Operating Range

| Parameter      | Symbol          | Range        | Unit |

|----------------|-----------------|--------------|------|

| Supply voltage | V <sub>CC</sub> | 4.50 to 5.50 | V    |

### ■ Electrical Characteristics at V<sub>CC</sub> = 5.0 V, T<sub>a</sub> = 25°C

| Parameter                   | Symbol            | Conditions                                                             | Min  | Typ  | Max  | Unit |

|-----------------------------|-------------------|------------------------------------------------------------------------|------|------|------|------|

| Supply current              |                   |                                                                        |      |      |      |      |

| Supply current              | I <sub>CC</sub>   | XCLR = low, digital I/O pin = open,<br>I <sub>PD</sub> = 0 μA          | —    | 20   | 30   | mA   |

| Sleep mode supply current   | I <sub>SLP</sub>  | Sleep = 1, I <sub>PD</sub> = 0 μA                                      | —    | 3    | 4    | mA   |

| Reference voltage block     |                   |                                                                        |      |      |      |      |

| Reference voltage output    | V <sub>REF</sub>  |                                                                        | 1.20 | 1.25 | 1.30 | V    |

| Reference voltage variation | ΔV <sub>REF</sub> | V <sub>CC</sub> = 4.5 V to 5.5 V, I <sub>REF</sub> = 0 mA              | —    | —    | ± 15 | mV   |

|                             |                   | V <sub>CC</sub> = 4.5 V to 5.5 V<br>I <sub>REF</sub> = –1 mA to +1 mA  | —    | —    | ± 20 |      |

| Maximum output current      | ΔV <sub>OM</sub>  | I <sub>REF</sub> = –1.5 mA,<br>difference from I <sub>REF</sub> = 0 mA | —    | —    | ± 50 | mV   |

■ Electrical Characteristics at  $V_{CC} = 5.0$  V,  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                                           | Symbol              | Conditions                                                                                                 | Min                  | Typ                  | Max                 | Unit          |

|-----------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------|----------------------|----------------------|---------------------|---------------|

| Digital block                                       |                     |                                                                                                            |                      |                      |                     |               |

| High-level input voltage                            | $V_{IH}$            | To be applied to a digital input pin                                                                       | $0.8 \times V_{CC}$  | —                    | —                   | V             |

| Low-level input voltage                             | $V_{IL}$            | To be applied to a digital input pin                                                                       | —                    | —                    | $0.2 \times V_{CC}$ | V             |

| High-level input voltage<br>(Schmitt-trigger input) | $V_{IHSCH}$         | To be applied to PWMSK, ERFIL pin                                                                          | $0.8 \times V_{CC}$  | —                    | —                   | V             |

| Low-level input voltage<br>(Schmitt-trigger input)  | $V_{ILSCH}$         | To be applied to PWMSK, ERFIL pin                                                                          | —                    | —                    | $0.2 \times V_{CC}$ | V             |

| High-level output voltage                           | $V_{OH}$            | $I_{OH} = -2$ mA                                                                                           | $0.8 \times V_{CC}$  | —                    | —                   | V             |

| Low-level output voltage                            | $V_{OL1}$           | $I_{OL} = +2$ mA                                                                                           | —                    | —                    | $0.2 \times V_{CC}$ | V             |

|                                                     | $V_{OL2}$           | $I_{OL} = +0.5$ mA                                                                                         | —                    | —                    | 0.4                 |               |

| Input pull-up, pull-down resistance                 | $R_{PD}$            | Pull-up: $V_{IL} = 0$ V<br>Pull-down: $V_{IH} = 5.0$ V                                                     | 75                   | 100                  | 125                 | k $\Omega$    |

| Input leak                                          | $I_{LKH}$           | To be applied to a digital input pin,<br>$V_{OH} = 5.25$ V                                                 | —                    | —                    | 80                  | $\mu\text{A}$ |

|                                                     | $I_{LKL}$           | To be applied to a digital input pin,<br>$V_{OL} = 0$ V                                                    | —                    | —                    | 10                  |               |

| Entire optical monitor                              |                     |                                                                                                            |                      |                      |                     |               |

| Offset voltage at playback                          | $V_{PMOFR}$         | VR1 = 1 k $\Omega$ , $I_{PD} = 0$ mA                                                                       | -15                  | —                    | 15                  | mV            |

|                                                     |                     | VR1 = 1 k $\Omega$ , difference from an ideal value at $I_{PD} = 100$ $\mu\text{A}$ to 200 $\mu\text{A}$   | -40                  | 0                    | 40                  |               |

| Offset voltage at recording                         | $V_{PMOFW}$         | VR1 = 1 k $\Omega$ , $I_{PD} = 0$ mA                                                                       | -15                  | —                    | 15                  | mV            |

|                                                     |                     | VR1 = 1 k $\Omega$ , difference from an ideal value at $I_{PD} = 100$ $\mu\text{A}$ to 2 000 $\mu\text{A}$ | -20                  | 0                    | 20                  |               |

| Gain ratio                                          | GR                  | $G_{PMR}/G_{PMW}$ ,<br>output = VNR +0.6 V to 2.0 V                                                        | 9.0                  | 10.0                 | 11.0                | times         |

| Maximum output voltage                              | $V_{PM\ max}$       |                                                                                                            | $V_{CC} \times 0.73$ | $V_{CC} \times 0.78$ | —                   | V             |

| Minimum output voltage                              | $V_{PM\ min}$       |                                                                                                            | —                    | —                    | $VNR - 0.015$       | V             |

| f characteristics at playback                       | $f_{PMR\ AAF\ OFF}$ | AAF-off VR1 = 1 k $\Omega$ ,<br>-3 dB, $I_{PD} = 100$ $\mu\text{A}$ to 200 $\mu\text{A}$                   | 4                    | 6                    | —                   | MHz           |

| f characteristics at recording                      | $f_{PMW}$           | VR1 = 1 k $\Omega$ ,<br>-3 dB, $I_{PD} = 100$ $\mu\text{A}$ to 2 000 $\mu\text{A}$                         | 6                    | 7.5                  | —                   | MHz           |

| Settling time at playback                           | $t_{PMSETR}$        | VR1 = 1 k $\Omega$ , error $\pm 0.5\%$ ,<br>output variation: Range of 0 V to 2 V                          | —                    | 200                  | 400                 | ns            |

| Settling time at recording                          | $t_{PMSETW}$        | VR1 = 1 k $\Omega$ , error $\pm 0.5\%$ ,<br>output variation: Range of 0 V to 2 V                          | —                    | 200                  | 400                 | ns            |

■ Electrical Characteristics at  $V_{CC} = 5.0$  V,  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                        | Symbol     | Conditions                                                                                                                       | Min  | Typ  | Max  | Unit          |

|----------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------------|

| Current amplification changeover |            |                                                                                                                                  |      |      |      |               |

| Gain at playback                 | $G_{IPDR}$ | Reg7 = "80h", $I_{PD} = 40 \mu\text{A}$ to $240 \mu\text{A}$                                                                     | 9.0  | 10.0 | 11.0 | times         |

| Gain at recording                | $G_{IPDW}$ | Reg7 = "C0h", $I_{PD} = 200 \mu\text{A}$ to $3200 \mu\text{A}$                                                                   | 0.9  | 1.0  | 1.1  | times         |

| Gain ratio                       | $GR_{IPD}$ | $G_{IPDR}/G_{IPDW}$                                                                                                              | 9.0  | 10.0 | 11.0 | times         |

| I to V conversion block          |            |                                                                                                                                  |      |      |      |               |

| Offset voltage                   | $V_{IVOF}$ | $VR1 = 0 \Omega$ , $I_{PD} = 0 \text{ mA}$                                                                                       | -15  | —    | 15   | mV            |

| DAC1 block                       |            |                                                                                                                                  |      |      |      |               |

| Resolution                       | RES1       |                                                                                                                                  | —    | 8    | —    | bit           |

| Integral linearity error         | EL1        |                                                                                                                                  | -1.0 | —    | 10.0 | LSB           |

| Differential linearity error     | ED1        |                                                                                                                                  | -1.0 | —    | 1.5  | LSB           |

| Maximum output current           | $I_{1max}$ | DAC1 = "FFh", DAC8 [Fh], DAC7 [0h], DAC9 [00h]                                                                                   | 70   | 80   | 90   | mA            |

| Offset current                   | $I_{1OF1}$ | "00h" LPF-on, DAC8 [Fh], DAC7 [0h], DAC9 [00h], DAC7, DAC8 characteristics included                                              | -1   | —    | 1    | mA            |

|                                  | $I_{1OF2}$ | "00h" LPF-off, DAC8 [Fh], DAC7 [0h], DAC9 [00h]                                                                                  | -250 | —    | 250  | $\mu\text{A}$ |

| LPF on/off gain ratio            | $GR_{DAL}$ | $G_{LPFON}/G_{LPFOFF}$ , input amplitude 0 V to 2 V                                                                              | 0.95 | 1    | 1.05 | times         |

| Settling time                    | $t_{SDA1}$ | XWR $\uparrow$ to DAC1 [10h to 8Fh], $\pm 2$ LSB range, DAC7 [0h], DAC8 [Fh], DAC9 [00h] LPF-off, LPF11 pin open, RDGP2 pin open | —    | 400  | 800  | ns            |

| DAC7 block                       |            |                                                                                                                                  |      |      |      |               |

| Resolution                       | RES7       |                                                                                                                                  | —    | 4    | —    | bit           |

| Integral linearity error         | EL7        |                                                                                                                                  | -1.0 | —    | 1.0  | LSB           |

| Differential linearity error     | ED7        |                                                                                                                                  | -0.5 | —    | 0.5  | LSB           |

| Maximum output current           | $I_{7max}$ | Set to DAC7 = "Fh", DAC9 [1Fh], DAC1 [00h], DAC8 [0h]                                                                            | 133  | 150  | 170  | mA            |

| Minimum output current           | $I_{7min}$ | Set to DAC7 = "0h", DAC9 [1Fh], DAC1 [00h], DAC8 [0h]                                                                            | -0.1 | 0    | 0.1  | mA            |

| Settling time                    | $t_{SDA7}$ | XWR $\uparrow$ to DAC7 [0h to Fh], DAC9 [1Fh], $\pm 0.5$ LSB, DAC1 [00h], DAC8 [0h]                                              | —    | 50   | 500  | ns            |

| DAC8 block                       |            |                                                                                                                                  |      |      |      |               |

| Resolution                       | RES8       |                                                                                                                                  | —    | 4    | —    | bit           |

| Integral linearity error         | EL8        |                                                                                                                                  | -1.0 | —    | 1.0  | LSB           |

| Differential linearity error     | ED8        |                                                                                                                                  | -0.5 | —    | 0.5  | LSB           |

■ Electrical Characteristics at  $V_{CC} = 5.0$  V,  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                    | Symbol      | Conditions                                                                          | Min  | Typ | Max | Unit |

|------------------------------|-------------|-------------------------------------------------------------------------------------|------|-----|-----|------|

| DAC8 block (continued)       |             |                                                                                     |      |     |     |      |

| Maximum output current       | $I_{8\max}$ | Set to DAC8 = "Fh", DAC1 [FFh], DAC9 [1Fh], DAC7 [0h]                               | 70   | 80  | 90  | mA   |

| Minimum output current       | $I_{8\min}$ | Set to DAC8 = "0h", DAC1 [FFh], DAC9 [1Fh], DAC7 [0h]                               | 4    | 5   | 6   | mA   |

| Settling time                | $t_{SDA8}$  | XWR $\uparrow$ to DAC8 [0h to Fh], DAC1 [80h], $\pm 0.5$ LSB, DAC9 [00h], DAC7 [0h] | —    | 50  | 250 | ns   |

| DAC2 block                   |             |                                                                                     |      |     |     |      |

| Resolution                   | RES2        |                                                                                     | —    | 8   | —   | bit  |

| Integral linearity error     | EL2         |                                                                                     | -1.0 | —   | 5.0 | LSB  |

| Differential linearity error | ED2         |                                                                                     | -1.0 | —   | 1.0 | LSB  |

| Maximum output current       | $I_{2\max}$ | DAC2 = "FFh", DAC4 [Fh]                                                             | 133  | 150 | 170 | mA   |

| Offset current               | $I_{2OF}$   | DAC2 = "00h", DAC4 [Fh]                                                             | -0.1 | —   | 0.1 | mA   |

| Settling time                | $t_{SDA2}$  | XWR $\uparrow$ to DAC2 [10h to FFh], $\pm 2.0$ LSB, DAC4 [Fh]                       | —    | 100 | 250 | ns   |

| DAC3 block                   |             |                                                                                     |      |     |     |      |

| Resolution                   | RES3        |                                                                                     | —    | 8   | —   | bit  |

| Integral linearity error     | EL3         |                                                                                     | -1.0 | —   | 5.0 | LSB  |

| Differential linearity error | ED3         |                                                                                     | -1.0 | —   | 1.0 | LSB  |

| Maximum output current       | $I_{3\max}$ | DAC3 = "FFh", DAC4 [Fh]                                                             | 133  | 150 | 170 | mA   |

| Offset current               | $I_{3OF}$   | DAC3 = "00h", DAC4 [Fh]                                                             | -0.1 | —   | 0.1 | mA   |

| Settling time                | $t_{SDA3}$  | XWR $\uparrow$ to DAC3 [10h to FFh], $\pm 2.0$ LSB, DAC4 [Fh]                       | —    | 200 | 450 | ns   |

| DAC4 block                   |             |                                                                                     |      |     |     |      |

| Resolution                   | RES4        |                                                                                     | —    | 4   | —   | bit  |

| Integral linearity error     | EL4         |                                                                                     | -1.0 | —   | 1.0 | LSB  |

| Differential linearity error | ED4         |                                                                                     | -1.0 | —   | 1.0 | LSB  |

| Maximum output current       | $I_{4\max}$ | DAC2 = "FFh", DAC4 [Fh]                                                             | 133  | 150 | 170 | mA   |

| Offset current               | $I_{4OF}$   | DAC2 = "00h", DAC4 [Fh]                                                             | -0.1 | —   | 0.1 | mA   |

| Settling time                | $t_{SDA4}$  | XWR $\uparrow$ to DAC4 [0h to Fh], $\pm 0.5$ LSB, DAC2 [FFh]                        | —    | 300 | 600 | ns   |

| DAC9 block                   |             |                                                                                     |      |     |     |      |

| Resolution                   | RES9        |                                                                                     | —    | 5   | —   | bit  |

| Integral linearity error     | EL9         |                                                                                     | -1.0 | —   | 1.0 | LSB  |

| Differential linearity error | ED9         |                                                                                     | -1.0 | —   | 1.0 | LSB  |

| Maximum output current       | $I_{9\max}$ | DAC9 = "1Fh", DAC7 [Fh], DAC1 [00h], DAC8 [0h]                                      | 133  | 150 | 170 | mA   |

■ Electrical Characteristics at  $V_{CC} = 5.0$  V,  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                               | Symbol     | Conditions                                                                                                                          | Min   | Typ | Max  | Unit          |

|-----------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|---------------|

| DAC9 block (continued)                  |            |                                                                                                                                     |       |     |      |               |

| Offset current                          | $I_{9OF1}$ | "00h" LPF-on, DAC7 [Fh], DAC8 [0h], DAC1 [00h], DAC7, DAC8 characteristics included                                                 | -2.0  | —   | 2.0  | mA            |

|                                         | $I_{9OF2}$ | "00h" LPF-off, DAC7 [Fh], DAC8 [0h], DAC9 [00h], DAC7, DAC8 characteristics included                                                | -0.85 | —   | 0.85 |               |

| LPF on/off gain ratio                   | $GR_{DA9}$ | $G_{LPFON} / G_{LPFOFF}$ , input amplitude 0 V to 2 V                                                                               | 0.95  | 1   | 1.05 | times         |

| Settling time                           | $t_{SDA9}$ | XWR $\uparrow$ to DAC9 [00h to 1Fh]<br>$\pm 2$ LSB range,<br>DAC7[Fh], DAC8 [0h],<br>LPF9-off,<br>LPF91 pin open,<br>RDCP1 pin open | —     | 400 | 800  | ns            |

| Supply voltage monitoring block         |            |                                                                                                                                     |       |     |      |               |

| Abnormality release supply voltage      | $V_{PSDL}$ | Sweep $V_{CC}$ from low to high                                                                                                     | 3.9   | 4.2 | 4.5  | V             |

|                                         | $V_{PSOL}$ | Sweep $V_{CC}$ from high to low                                                                                                     | 5.5   | 5.8 | 6.1  |               |

| Abnormality supply voltage              | $V_{PSDH}$ | Sweep $V_{CC}$ from high to low                                                                                                     | 3.6   | 3.9 | 4.2  | V             |

|                                         | $V_{PSOH}$ | Sweep $V_{CC}$ from low to high                                                                                                     | 5.8   | 6.1 | 6.4  |               |

| Abnormally emitted light detection DAC5 |            |                                                                                                                                     |       |     |      |               |

| Resolution                              | RES5       |                                                                                                                                     | —     | 4   | —    | bit           |

| Integral linearity error                | EL5        |                                                                                                                                     | -0.5  | —   | 0.5  | LSB           |

| Differential linearity error            | ED5        |                                                                                                                                     | -0.5  | —   | 0.5  | LSB           |

| Offset voltage                          | $V_{5OF1}$ | DAC5 = set to "Fh" and difference to ERREF pin                                                                                      | -20   | —   | 20   | mV            |

|                                         | $V_{5OF2}$ | DAC5 = set to "0h" and difference to VNR pin, at ERREF - VNR = 2.0 V                                                                | 105   | 125 | 145  |               |

| Settling time                           | $t_{SDA5}$ | XWR $\uparrow$ to DAC5 [0h to Fh], $\pm 0.5$ LSB                                                                                    | —     | 0.5 | 1.5  | $\mu\text{s}$ |

| Abnormally emitted light detection DAC6 |            |                                                                                                                                     |       |     |      |               |

| Resolution                              | RES6       |                                                                                                                                     | —     | 4   | —    | bit           |

| Integral linearity error                | EL6        |                                                                                                                                     | -0.5  | —   | 0.5  | LSB           |

| Differential linearity error            | ED6        |                                                                                                                                     | -0.5  | —   | 0.5  | LSB           |

| Offset voltage                          | $V_{6OF1}$ | DAC6 = set to "Fh" and difference to ERREF pin                                                                                      | -20   | —   | 20   | mV            |

|                                         | $V_{6OF2}$ | DAC6 = set to "0h" and difference to VNR pin, at ERREF - VNR = 2.0 V                                                                | 105   | 125 | 145  |               |

| Settling time                           | $t_{SDA6}$ | XWR $\uparrow$ to DAC6 [0h to Fh], $\pm 0.5$ LSB                                                                                    | —     | 0.5 | 1.5  | $\mu\text{s}$ |

■ Electrical Characteristics at  $V_{CC} = 5.0$  V,  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                                                | Symbol                     | Conditions                                                                             | Min | Typ  | Max  | Unit  |

|----------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|-----|------|------|-------|

| Abnormally emitted light detection optical monitor block |                            |                                                                                        |     |      |      |       |

| Offset voltage                                           | $V_{EROFR}$                | In playback, DETMONI pin,<br>$I_{PD} = 0 \mu\text{A}$                                  | -40 | —    | 60   | mV    |

|                                                          | $V_{EROFW}$                | In recording, DETMONI pin,<br>$I_{PD} = 0 \mu\text{A}$                                 | -50 | —    | 50   |       |

| Gain                                                     | $G_{ERR1}$                 | In playback, addr. "9": D4 = "0",<br>$I_{PD} = 100 \mu\text{A}$ to $200 \mu\text{A}$   | 9.0 | 10.0 | 11.0 | times |

|                                                          | $G_{ERR2}$                 | In playback, addr. "9": D4 = "1",<br>$I_{PD} = 100 \mu\text{A}$ to $200 \mu\text{A}$   | 4.5 | 5.0  | 5.5  |       |

|                                                          | $G_{ERW}$                  | In recording, DETMONI pin,<br>$I_{PD} = 100 \mu\text{A}$ to $2000 \mu\text{A}$         | 0.9 | 1.0  | 1.1  |       |

| Gain ratio                                               | $\frac{G_{ERR1}}{G_{ERW}}$ |                                                                                        | 9.0 | 10.0 | 11.0 | times |

|                                                          | $\frac{G_{ERR2}}{G_{ERW}}$ |                                                                                        | 4.5 | 5.0  | 5.5  |       |

| f characteristics at playback                            | $f_{ERR}$                  | $VR1 = 1 \text{ k}\Omega$ , -3 dB,<br>$I_{PD} = 100 \mu\text{A}$ to $200 \mu\text{A}$  | 2.5 | —    | —    | MHz   |

| f characteristics at recording                           | $f_{ERW}$                  | $VR1 = 1 \text{ k}\Omega$ , -3 dB,<br>$I_{PD} = 100 \mu\text{A}$ to $2000 \mu\text{A}$ | 5.0 | —    | —    | MHz   |

| Control operation response                               |                            |                                                                                        |     |      |      |       |

| Data write to XLDERR ↓                                   | $t_{203}$                  | XWR ↑ to XLDERR ↓                                                                      | —   | 20   | 60   | ns    |

| Data write to XLDERR ↑                                   | $t_{204}$                  | XWR ↑ to XLDERR ↑                                                                      | —   | 25   | 60   | ns    |

| Data write to sleep mode                                 | $t_{205}$                  | XWR ↑ to sleep mode                                                                    | —   | 4    | 9    | μs    |

| Data write to normal mode                                | $t_{206}$                  | XWR ↑ to normal mode                                                                   | —   | 3    | 8    | μs    |

| RPHOLD ↑ to DAC5 R → W                                   | $t_{39}$                   | RPHOLD ↑ to DAC5 W,<br>at having reached $\pm 0.5$ LSB                                 | —   | 0.40 | 2.5  | μs    |

| RPHOLD ↓ to DAC5 W → R                                   | $t_{40}$                   | RPHOLD ↓ to DAC5 R,<br>at having reached $\pm 0.5$ LSB                                 | —   | 0.40 | 2.5  | μs    |

| RPHOLD ↑ to DAC6 R → W                                   | $t_{41}$                   | RPHOLD ↑ to DAC6 W,<br>at having reached $\pm 0.5$ LSB                                 | —   | 0.40 | 2.5  | μs    |

| RPHOLD ↓ to DAC6 W → R                                   | $t_{42}$                   | RPHOLD ↓ to DAC6 R,<br>at having reached $\pm 0.5$ LSB                                 | —   | 0.40 | 2.5  | μs    |

| RPHOLD ↑ to HF module signal                             | $t_{43}$                   | RPHOLD ↑ to XHFON ↑                                                                    | —   | 18   | 30   | ns    |

| RPHOLD ↓ to HF module signal                             | $t_{44}$                   | RPHOLD ↓ to XHFON ↓                                                                    | —   | 17   | 30   | ns    |

■ Electrical Characteristics at  $V_{CC} = 5.0$  V,  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                                     | Symbol    | Conditions                                       | Min           | Typ           | Max           | Unit |

|-----------------------------------------------|-----------|--------------------------------------------------|---------------|---------------|---------------|------|

| Recording Modulation                          |           |                                                  |               |               |               |      |

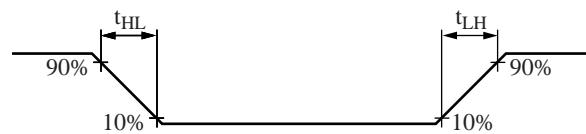

| Peak modulation signal response <sup>*1</sup> | $t_{113}$ | PKMD $\uparrow$ to LDPK $\uparrow$ 50% delay     | —             | 18            | 30            | ns   |

|                                               | $t_{114}$ | PKMD $\downarrow$ to LDPK $\downarrow$ 50% delay | —             | 17            | 30            |      |

|                                               | $t_{115}$ | LDPK $\uparrow$ 50% to LDPK $\downarrow$ 50%     | $t_{112} - 3$ | $t_{112} - 1$ | $t_{112} + 1$ |      |

|                                               | $t_{116}$ | LDPK $\uparrow$ 10% to LDPK $\uparrow$ 90%       | —             | 6             | 9             |      |

|                                               | $t_{117}$ | LDPK $\downarrow$ 90% to LDPK $\downarrow$ 10%   | —             | 4             | 6             |      |

| Bias modulation signal response <sup>*1</sup> | $t_{123}$ | BIMD $\uparrow$ to LDBI $\uparrow$ 50% delay     | —             | 18            | 30            | ns   |

|                                               | $t_{124}$ | BIMD $\downarrow$ to LDBI $\downarrow$ 50% delay | —             | 17            | 30            |      |

|                                               | $t_{125}$ | LDBI $\uparrow$ 50% to LDBI $\downarrow$ 50%     | $t_{122} - 3$ | $t_{122} - 1$ | $t_{122} + 1$ |      |

|                                               | $t_{126}$ | LDBI $\uparrow$ 10% to LDBI $\uparrow$ 90%       | —             | 6             | 9             |      |

|                                               | $t_{127}$ | LDBI $\downarrow$ 90% to LDBI $\downarrow$ 10%   | —             | 5             | 8             |      |

Note) \*1: Resistive load (at 15  $\Omega$ )Conditions of  $t_{113}$  to  $t_{117}$

Measure at approximately 1.75 V of LDPK pin voltage.

DAC1 [FFh], DAC8 [7h]

DAC9 [1Fh], DAC7 [7h], DAC4 [Fh]

DAC2 [00h to 80f]

Conditions of  $t_{123}$  to  $t_{127}$

Measure at approximately 1.75 V of LDPK pin voltage.

DAC1 [FFh], DAC8 [7h]

DAC9 [1Fh], DAC7 [7h], DAC4 [Fh]

DAC3 [00h to 80f]

## • Design reference data

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                                       | Symbol                              | Conditions                                                                                                                                    | Min | Typ | Max      | Unit                                 |

|-----------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|--------------------------------------|

| Reference voltage block                                         |                                     |                                                                                                                                               |     |     |          |                                      |

| Reference voltage temperature characteristics <sup>*2</sup>     | $\Delta V_{TEM}$                    | $V_{REF} = 0$ V, $T_a = -20^\circ\text{C}$ to $+75^\circ\text{C}$                                                                             | —   | —   | $\pm 30$ | mV                                   |

| Digital block                                                   |                                     |                                                                                                                                               |     |     |          |                                      |

| Low $\rightarrow$ high input hysteresis (Schmidt trigger input) | $V_{LHHYS}$                         | To be applied to PWMSK, ERFIL pin                                                                                                             | —   | 1.0 | —        | V                                    |

| High $\rightarrow$ low input hysteresis (Schmidt trigger input) | $V_{HLHYS}$                         | To be applied to PWMSK, ERFIL pin                                                                                                             | —   | 1.0 | —        | V                                    |

| Entire optical monitor                                          |                                     |                                                                                                                                               |     |     |          |                                      |

| Offset voltage temperature variation                            | $\frac{\Delta V_{PMOFR}}{\Delta T}$ | In playback, $VR1 = 1$ k $\Omega$<br>$I_{PD} = 10$ $\mu\text{A}$ to 200 $\mu\text{A}$<br>$T_a = -20^\circ\text{C}$ to $+75^\circ\text{C}$     | —   | 55  | 200      | $\frac{\mu\text{V}}{^\circ\text{C}}$ |

|                                                                 | $\frac{\Delta V_{PMOFW}}{\Delta T}$ | In recording, $VR1 = 1$ k $\Omega$<br>$I_{PD} = 100$ $\mu\text{A}$ to 2 000 $\mu\text{A}$<br>$T_a = -20^\circ\text{C}$ to $+75^\circ\text{C}$ | —   | 30  | 150      |                                      |

Note) \*2: Difference between  $V_{REF}$  min. and  $V_{REF}$  max. within the range of  $T_a = -20^\circ\text{C}$  to  $+75^\circ\text{C}$ .

■ Electrical Characteristics at  $V_{CC} = 5.0$  V,  $T_a = 25^\circ\text{C}$  (continued)

## • Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                               | Symbol                       | Conditions                                                                                                                                                                         | Min | Typ  | Max | Unit                                 |

|-----------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------------------------------------|

| Entire optical monitor (continued)      |                              |                                                                                                                                                                                    |     |      |     |                                      |

| Gain ratio variation to temperature     | $\frac{dG_{PMR}}{dG_{PMW}}$  | $T_a = -20^\circ\text{C}$ to $+75^\circ\text{C}$                                                                                                                                   | -3  | —    | 3   | %                                    |

| Slew rate                               | $S1_{PMR}$                   | In playback, AAF-off rise                                                                                                                                                          | 13  | 18   | —   | V/ $\mu$ s                           |

|                                         | $S1_{PMW}$                   | In recording, rise                                                                                                                                                                 | 35  | 45   | —   |                                      |

| Signal changeover response              | $t_{PMSW1}$                  | $\times 10 \rightarrow \times 1$ , at having reached $\pm 0.5\%$                                                                                                                   | —   | 100  | 300 | ns                                   |