# **SMPS IC**

Smartrectifier<sup>™</sup> IR11688S

## **DUAL SYNCHRONOUS RECTIFICATION CONTROL IC**

## **Features**

- Secondary-side high speed synchronous rectification controller for resonant half bridge converters

- Direct sensing of MOSFET drain voltage up to 200V

- Operates up to 400kHz switching frequency

- Programmable Minimum On Time

- Anti-bounce logic and UVLO protection

- Linear turn-off phase to compensate for premature switch off due to parasitic inductance

- 4A peak turn off drive current

- Micropower start-up & ultra-low quiescent current

- 50ns turn-off propagation delay

- Wide Vcc operating range 4.75V to 18V

- Cycle by Cycle MOT Protection

- Auto low power mode standby mode

- Improved noise immunity

- Compatible with Energy Star low standby power

- Lead-free

## **Product Summary**

| Topology                          | LLC Half-bridge |

|-----------------------------------|-----------------|

| VD                                | 200V            |

| V <sub>OUT</sub>                  | Vcc             |

| I <sub>0+</sub> & I <sub>0-</sub> | +1A & -4A       |

**Package Options**

# **Typical Applications**

Desktop SMPS, Server SMPS, AC-DC adapters, LCD & PDP TV, Telecom SMPS

# **Ordering Information**

| Daga Bart Namahar | Daalaa wa Tawa | Standard F    | Pack     | Complete Part Number |  |

|-------------------|----------------|---------------|----------|----------------------|--|

| Base Part Number  | Package Type   | Form          | Quantity | Complete Part Number |  |

| IR11688S          | SOIC8N         | Tape and Reel | 2500     | IR11688STRPBF        |  |

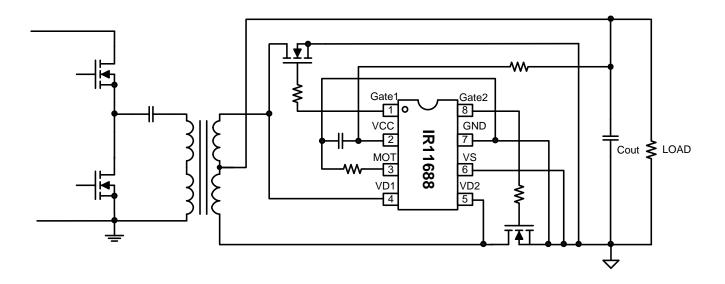

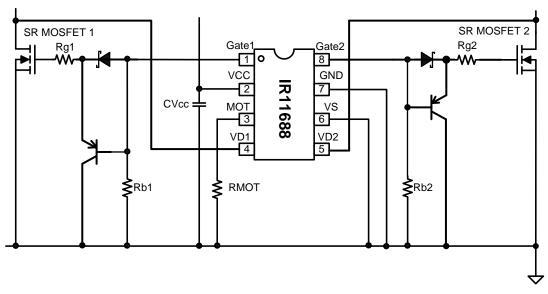

# **Typical Connection Diagram**

# IR11688S

| Table of Contents                              | Page |  |  |  |  |

|------------------------------------------------|------|--|--|--|--|

| Ordering Information                           | 1    |  |  |  |  |

| Description                                    | 4    |  |  |  |  |

| Absolute Maximum Ratings                       | 5    |  |  |  |  |

| Electrical Characteristics                     | 6    |  |  |  |  |

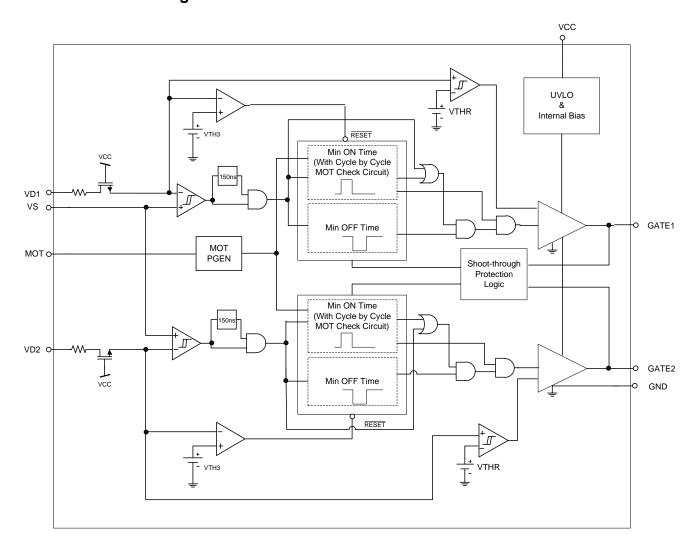

| Functional Block Diagram                       | 8    |  |  |  |  |

| Input/Output Pin Equivalent Circuit Diagram    |      |  |  |  |  |

| Pin Definitions                                | 10   |  |  |  |  |

| Pin Assignments                                | 10   |  |  |  |  |

| Application Information and Additional Details | 12   |  |  |  |  |

| Package Details                                | 23   |  |  |  |  |

| Tape and Reel Details                          | 24   |  |  |  |  |

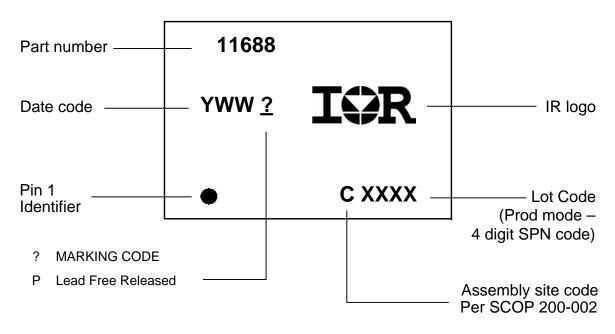

| Part Marking Information                       | 25   |  |  |  |  |

| Qualification Information                      | 26   |  |  |  |  |

# **Description**

The IR11688 is a dual smart secondary-side controller IC optimized to drive two N-Channel power MOSFETs configured for synchronous rectification in resonant converter applications. Each channel can drive one or multiple parallel MOSFETs to emulate the behavior of Schottky diode rectifiers, bypassing the body diodes for the majority of each conduction period to minimize power dissipation and remaining off during the blocking period.

The drain to source voltage of each rectifier MOSFET is sensed to determine the source to drain current and turn each gate on rapidly at the start of each conduction cycle and off in close proximity to the zero current transitions for each branch of the output rectifier circuit. Ruggedness and noise immunity are accomplished using an advanced blanking scheme and double-pulse suppression that allows reliable operation in fixed and variable frequency applications.

The programmable minimum on time (MOT) function provides flexibility to work over a wide range of switching frequencies. The cycle-by-cycle MOT protection circuit is able to automatically detect a light or no load condition so that the gate drives may be disabled to avoid unwanted reverse currents flowing through the MOSFETs.

The IR11688 has a wide Vcc supply voltage range from 4.75V to 18V, enabling its supply to be derived from the output and eliminating the need for an auxiliary supply circuit in systems with output voltage as low as 5V.

The IR11688 also has very low quiescent current when the gate drives are not switching to offer minimal power consumption in standby mode.

# **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any pin. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Parameters                     | Symbol               | Min. | Max.    | Units | Remarks                        |

|--------------------------------|----------------------|------|---------|-------|--------------------------------|

| Supply Voltage                 | $V_{CC}$             | -0.3 | 20      | V     |                                |

| Cont. Drain Sense Voltage      | $V_{D1,2}$           | -1   | 200     | V     |                                |

| Pulse Drain Sense Voltage      | $V_{D1,2}$           | -3   | 200     | V     |                                |

| Source Sense Voltage           | Vs                   | -1   | 5       | V     |                                |

| Gate Voltage                   | V <sub>GATE1,2</sub> | -0.3 | Vcc+0.3 | V     |                                |

| MOT Voltage                    | $V_{MOT}$            | -0.3 | 3.5     | V     |                                |

| Operating Junction Temperature | $T_J$                | -40  | 150     | °C    |                                |

| Storage Temperature            | Ts                   | -55  | 150     | °C    |                                |

| Thermal Resistance             | $R_{\theta JA}$      |      | 128     | °C/W  | SOIC-8                         |

| Package Power Dissipation      | $P_D$                |      | 970     | mW    | SOIC-8, T <sub>AMB</sub> =25°C |

# **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions.

| Symbol          | Definition           | Min.            | Max. | Units |

|-----------------|----------------------|-----------------|------|-------|

| V <sub>CC</sub> | Supply voltage       | 4.75            | 18   | \ /   |

| $V_{D}$         | Drain Sense Voltage  | -3 <sup>①</sup> | 200  | V     |

| T <sub>J</sub>  | Junction Temperature | -40             | 125  | °C    |

| Fsw             | Switching Frequency  |                 | 400  | kHz   |

V<sub>D</sub> -3V negative spike width ≤100ns

# **Recommended Component Values**

| Symbol           | Component              | Min. | Max. | Units |  |

|------------------|------------------------|------|------|-------|--|

| R <sub>MOT</sub> | MOT pin resistor value | 20   | 150  | kΩ    |  |

# **Electrical Characteristics**

VCC=12V,  $T_A$  = 25°C unless otherwise specified. The output voltage and current ( $V_O$  and  $I_O$ ) parameters are referenced to GND (pin7).

**Supply Section**

| Paramatana                             | 0                     | N.4.* | <b>T</b> |      | 11    | D                                                  |

|----------------------------------------|-----------------------|-------|----------|------|-------|----------------------------------------------------|

| Parameters                             | Symbol                | Min.  | Тур.     | Max. | Units | Remarks                                            |

| Supply Voltage Operating               |                       |       |          |      |       |                                                    |

| Range                                  | $V_{CC}$              | 4.75  |          | 18   | V     |                                                    |

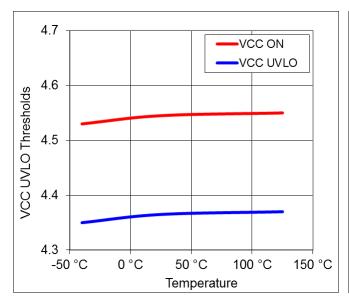

| V <sub>CC</sub> Turn On Threshold      | V <sub>CC ON</sub>    | 4.35  | 4.55     | 4.75 | V     |                                                    |

| V <sub>CC</sub> Turn Off Threshold     |                       | 4 4 5 | 4.05     | 4.55 | 1/    |                                                    |

| (Under Voltage Lock Out)               | V <sub>CC UVLO</sub>  | 4.15  | 4.35     | 4.55 | V     |                                                    |

| V <sub>CC</sub> Turn On/Off Hysteresis | V <sub>CC HYST</sub>  |       | 0.2      |      | V     |                                                    |

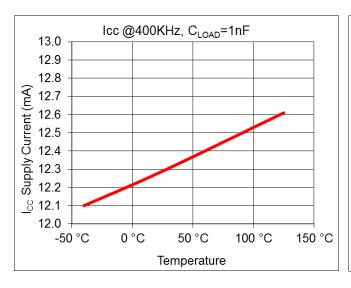

| Operating Current                      |                       |       |          |      |       | $C_{LOAD} = 1 \text{nF}, f_{SW} = 400 \text{kHz},$ |

| Operating Current                      | I <sub>CC</sub>       |       | 13       | 15   | mA    | $R_{MOT}=50k\Omega$                                |

|                                        |                       |       |          |      |       | No switching at VD pins and after                  |

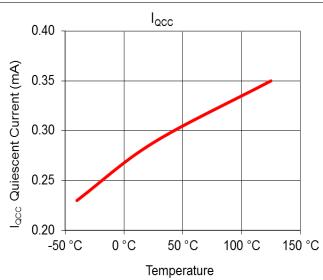

| Quiescent Current                      |                       |       |          |      |       | T <sub>WAIT</sub> is exceeded, VD=2V,              |

|                                        | I <sub>QCC</sub>      |       | 320      | 500  | μΑ    | $R_{MOT}=50k\Omega$                                |

| Start-up Current                       | I <sub>CC START</sub> |       | 40       | 80   | μΑ    | V <sub>CC</sub> =V <sub>CC ON</sub> - 0.1V         |

| Quiescent waiting time                 | T <sub>WAIT</sub>     | 340   | 570      | 800  | μS    |                                                    |

**Comparator Section**

| Parameters            | Symbol              | Min. | Тур. | Max. | Units | Remarks                       |

|-----------------------|---------------------|------|------|------|-------|-------------------------------|

| Turn-off Threshold    | $V_{TH1}$           | -7   | -4   | 0    | mV    | V <sub>S</sub> =0V            |

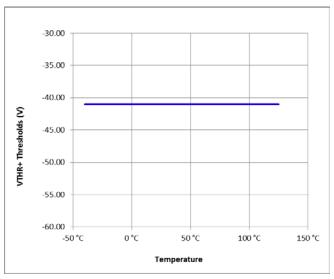

| Regulation Threshold  | $V_{THR}$           | -50  | -40  | -30  | mV    | 10mV hysteresis (-50mV/-40mV) |

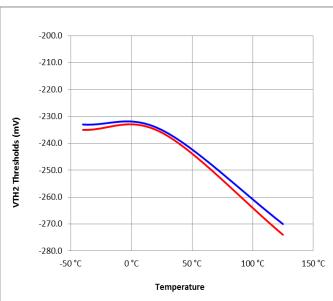

| Turn-on Threshold     | $V_{TH2}$           | -263 | -230 | -197 | mV    |                               |

| Hysteresis            | $V_{HYST}$          |      | 230  |      | mV    | GBD                           |

| Input Bias Current    | I <sub>IBIAS1</sub> | -7.5 | -5   |      | μA    | $V_D = -50 \text{mV}$         |

| Input Bias Current    | I <sub>IBIAS2</sub> |      | 7    | 10   | μA    | $V_D = 200V$                  |

| Turn-on Blanking time | $T_Bon$             |      | 150  |      | ns    | GBD                           |

## **One-Shot Section**

| 0.10 0.101 000.101      |                    |      |      |      |       |         |

|-------------------------|--------------------|------|------|------|-------|---------|

| Parameters              | Symbol             | Min. | Тур. | Max. | Units | Remarks |

| Blanking pulse duration | t <sub>BLANK</sub> | 8    | 15   | 24   | μs    |         |

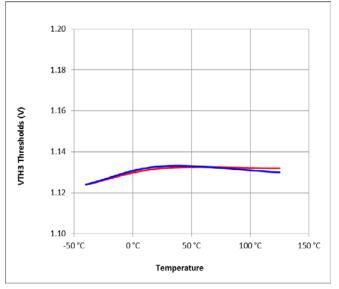

| Reset Threshold         | $V_{TH3}$          | 1.06 | 1.18 | 1.31 | V     |         |

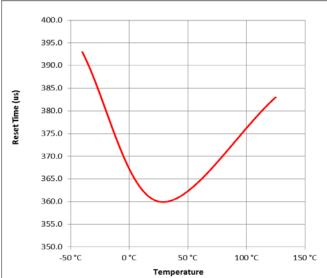

| Reset Delay             | t <sub>BRST</sub>  |      | 400  |      | ns    |         |

| Hysteresis              | $V_{HYST3}$        |      | 40   |      | mV    | GBD     |

## **Minimum On Time Section**

| Parameters      | Symbol  | Min. | Тур. | Max. | Units | Remarks                             |

|-----------------|---------|------|------|------|-------|-------------------------------------|

| Minimum on time | _       | 375  | 500  | 625  | ns    | $R_{MOT} = 24k\Omega, V_{CC} = 5V$  |

|                 | I Onmin | 0.75 | 1    | 1.25 | μs    | $R_{MOT} = 50 k\Omega, V_{CC} = 5V$ |

# **Electrical Characteristics**

VCC=12V,  $T_A$  = 25°C unless otherwise specified. The output voltage and current ( $V_O$  and  $I_O$ ) parameters are referenced to GND (pin7).

## **Gate Driver Section**

| Parameters                 | Symbol                | Min. | Тур. | Max. | Units | Remarks                                                  |

|----------------------------|-----------------------|------|------|------|-------|----------------------------------------------------------|

| Gate Low Voltage           | $V_{GLO}$             |      | 0.15 | 0.25 | V     | $I_{GATE} = 100 \text{mA}$                               |

| Gate High Voltage          | \/                    |      | 11.9 |      | V     | GBD                                                      |

| Gate High Voltage          | $V_{GTH}$             |      | 4.9  |      | V     | GBD                                                      |

| Rise Time                  | t <sub>r</sub>        |      | 20   | 38   | ns    | $C_{LOAD} = 1nF$                                         |

| Fall Time                  | t <sub>f</sub>        |      | 10   | 22   | ns    | $C_{LOAD} = 1nF$                                         |

| Turn on Propagation Delay  | t <sub>Don</sub>      |      | 200  | 250  | ns    | $V_{DS}$ to $V_{GATE} - V_{DS}$ goes down from 6V to -1V |

| Turn off Propagation Delay | t <sub>Doff</sub>     |      | 42   | 60   | ns    | $V_{DS}$ to $V_{GATE} - V_{DS}$ goes up from -1V to 6V   |

| Pull up Resistance         | $r_{up}$              |      | 6    |      | Ω     | GBD                                                      |

| Pull down Resistance       | r <sub>down</sub>     |      | 1.5  |      | Ω     | $I_{GATE} = -100 \text{mA}$                              |

| Output Peak Current        |                       |      |      |      |       |                                                          |

| (source)                   | I <sub>O source</sub> |      | 1    |      | Α     | GBD                                                      |

| Output Peak Current (sink) | I <sub>O sink</sub>   |      | 4    |      | Α     | GBD                                                      |

GBD – parameter is guaranteed by design and is not tested.

# **Functional Block Diagram**

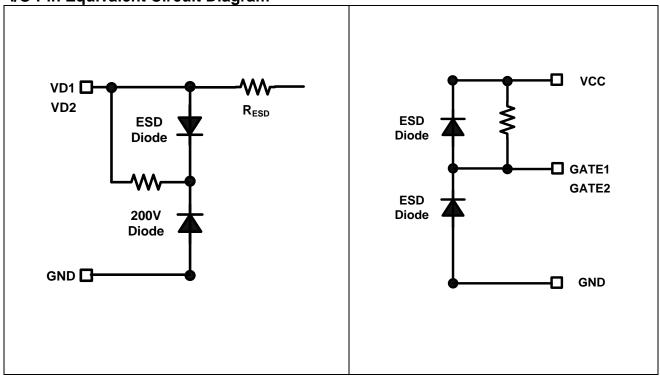

I/O Pin Equivalent Circuit Diagram

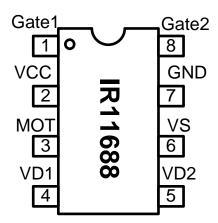

# **Pin Definitions**

| PIN# | Symbol | Description                      |

|------|--------|----------------------------------|

| 1    | GATE1  | Gate Drive Output 1              |

| 2    | VCC    | Supply Voltage                   |

| 3    | MOT    | Minimum On Time Programmable pin |

| 4    | VD1    | Sync FET 1 Drain Voltage Sense   |

| 5    | VD2    | Sync FET 2 Drain Voltage Sense   |

| 6    | VS     | Sync FET Source Voltage Sense    |

| 7    | GND    | Analog and Power Ground          |

| 8    | GATE2  | Gate Drive Output 2              |

# **Pin Assignments**

# **Detailed Pin Description**

## **VCC: Power Supply**

This is the supply voltage pin of the IC, monitored by the under voltage lockout circuit. It is possible to turn off the IC entering UVLO mode by pulling this pin below the minimum turn off threshold voltage for micro power consumption.

To prevent noise interfering with operation, a ceramic decoupling capacitor should be connected from Vcc to GND and located as close to the IC as possible. A low value series resistor may also be added to the Vcc supply circuit for filtering if required. Vcc is internally clamped at around 20V.

#### **GND: Ground**

This is power ground connection to the IC. Internal circuit blocks and gate drivers are referenced to this point.

#### **MOT: Minimum On Time**

The MOT programming pin controls the amount of minimum on time. Once  $V_{TH2}$  is crossed at either VD input, the corresponding gate drive output will transition high to turn on the SR MOSFET. Spurious ringing and oscillations can falsely trigger the input comparator to prematurely switch the output off. During the MOT period the input comparator is disabled maintaining conduction through the MOSFET on for this preset minimum period.

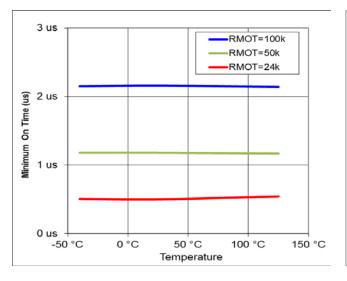

The MOT is typically programmed between 500ns and 2us by means of an external resistor referenced to GND.

## VD1 and VD2: Drain Voltage Sense

The VD pins are the voltage sensing inputs for the SR MOSFET drains. These are high voltage inputs therefore particular care must be taken in properly routing the connections. Additional RC filters can be placed at these inputs to improve noise immunity, however only a small resistor ( $\leq 1 \text{k}\Omega$ ) and capacitor value (in the pF range) may be used to avoid introducing excessive delay to the control input.

#### **VS: Source Voltage Sense**

This is the signal ground for the sources of the two SR power MOSFETs to provide an accurate differential voltage measurement. Kelvin connect this pin to the source of MOSFET2 (channel 2 MOSFET) is recommended if the two MOSFETs are far apart to each other.

#### **GATE1 and GATE2: Gate Drive Outputs**

Each gate driver output has +1A/-4A peak drive capability. Although these pins can be directly connected to the SR MOSFET gates the use of gate resistors is recommended, especially when using several MOSFETs in parallel. Care must be taken to keep the gate loop as short and as tight as possible in order to achieve optimal switching performance.

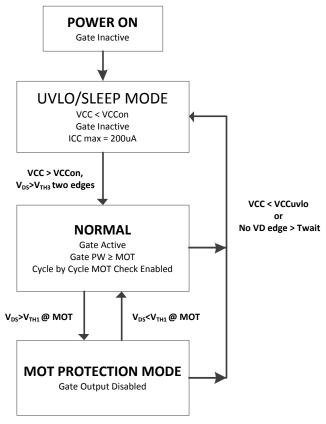

# Application Information and Additional Details State Diagram

#### **UVLO/SLEEP Mode**

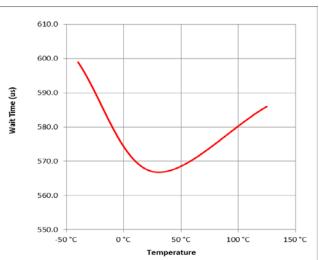

The IC remains in the UVLO/SLEEP condition until the voltage at the VCC pin first exceeds the VCC turn on threshold voltage,  $V_{\text{CC ON}}$ . While in the UVLO/SLEEP state, the gate drive outputs are inactive and only a very small quiescent current of  $I_{\text{CC START}}$  is drawn. UVLO mode is accessible from any other state of operation whenever the IC supply voltage condition of Vcc <  $V_{\text{CC UVLO}}$  occurs. If during normal operation, the drain inputs remain inactive such that no edges are detected for a period longer than  $T_{\text{WAIT}}$  the IC enters SLEEP mode. It remains in a low power state until woken up by a voltage transition at either VD input.

#### **Normal Mode**

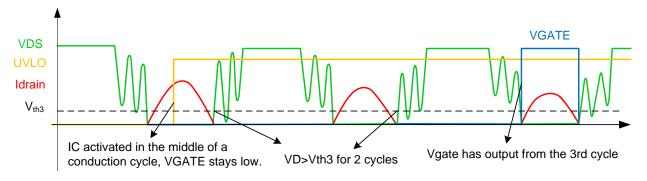

The IC enters into normal operating mode when the  $V_{\text{CC ON}}$  threshold has been exceeded. On entering Normal Mode from the UVLO Mode the GATE outputs remain disabled until  $V_{DS}$  transitions above  $V_{TH3}$  two times. This ensures that the GATE output cannot be enabled in the middle of a switching cycle since this can cause undesired reverse conduction. The cycle by cycle minimum on time (MOT) protection circuit also becomes activated to prevent reverse currents occurring when conduction time is short, which may also happen during system power up and down. The gate drives will continuously drive the MOSFETs after this startup sequence is completed.

#### **MOT Protection Mode**

If secondary current conduction time in either rectifier circuit branch is shorter than the set MOT, the subsequent gate driver output pulse is skipped. This function avoids reverse current from occurring when the system is switching at very low duty-cycles under very light or zero load conditions. The cycle by cycle MOT check circuit always remains active in Normal Mode and MOT Protection Mode so that the IC will automatically resume normal operation only after the load increases to a level where the secondary current conduction time exceeds MOT. System standby power consumption is significantly reduced in this mode while the gate outputs are inactive.

# **General Description**

The IR11688 dual *SMART RECTIFIER*<sup>TM</sup> controller is a high-voltage IC for synchronous rectification designed for resonant converter applications. As stated, it emulates the operation of two diodes configured with a center tapped transformer secondary by correctly switching on and off the synchronous rectifier MOSFETs in the two rectifier circuit branches.

The core of this device consists of two high-voltage drain sensing inputs feeding high speed comparators to differentially sense the drain to source voltage at each SR MOSFET. The SR MOSFET source to drain current is detected from the voltage across the conducting body diode or the R<sub>DSON</sub> resistance when switched on. Internal control logic allows the corresponding gate drive output to be switched on and off at the correct time to bypass the body diode for the majority of the conduction period.

The IR11688 further simplifies synchronous rectifier control by offering the following power management features:

- Wide VCC operating range allows the IC to be supplied from the converter output

- Shoot through protection logic that prevents both GATE outputs from ever being high at the same time

- Turn-off phase regulation to compensate for power device package inductance and avoid premature turn-off

- Optimized negative turn on voltage threshold detection and leading edge noise filter to minimize false triggering due to ringing oscillations

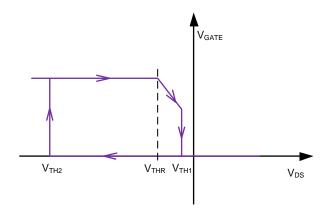

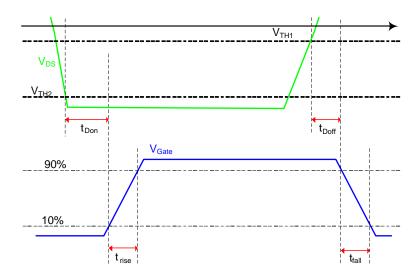

The IR11688 control technique senses SR MOSFET source to drain voltages comparing them with three different negative thresholds ( $V_{TH1}$ ,  $V_{TH2}$  and  $V_{TH2}$ ) to precisely control gate turn on and off as shown in figure 1:

Figure 1: Input comparator thresholds

#### **Turn-on phase**

When the conduction phase of each SR MOSFET begins, the device is off so therefore current starts to flow through the body diode producing a negative  $V_{DS}$  voltage across it. The body diode has a much higher voltage drop than the one resulting from the MOSFET on resistance and is therefore sufficient to trigger the turn-on threshold  $V_{TH2}$ .

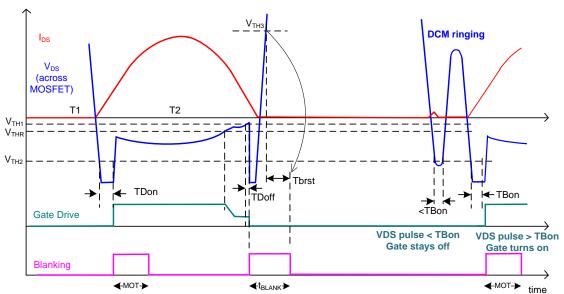

When either  $V_{DS}$  input remains below  $V_{TH2}$  for more than  $T_{Bon}$  (150ns), the gate of the corresponding SR MOSFET is driven high, which causes  $V_{DS}$  to reduce rapidly to  $I_D$  x  $R_{DSON}$ . The internal delay timer will be reset if  $V_{DS}$  rises above  $V_{TH2}$  before  $T_{Bon}$  times out. This turn-on blanking time helps to avoid misfiring that could be triggered by high frequency ringing in DCM operation. The voltage drop at switch on is usually accompanied by some amount of ringing, which could potentially trigger the input comparator to turn off the gate drive very quickly. However the minimum on time (MOT) blanking period prevents this. The turn-on blanking time ( $T_{Bon}$ ) and the MOT limit the minimum conduction time for the secondary rectifiers determining the switching frequency upper limit that the IR11688 may effectively operate at.

#### Regulation phase

After the gate has been driven high at switch on, the SR MOSFET remains on until the source to drain current falls to the level where  $V_{DS}$  reaches the regulation threshold  $V_{THR}$ . At the end of the MOT, the gate output is no longer driven high and reverts to a high impedance state. When  $V_{DS} < V_{THR}$  a weak pull down gradually discharges the gate voltage held by the SR MOSFET input capacitance. As the gate voltage drops, the MOSFET channel resistance increases as it enters the linear region. This causes  $V_{DS}$  to once again exceed  $V_{THR}$  so that weak pull down will cease until the conduction current falls to the point where  $V_{DS}$  again drops below  $V_{THR}$ . This regulating process continues so that the conduction period is extended until the current has fallen to a very low level. In this way premature turn off, which can arise due to parasitic inductances in PCB traces and the MOSFET package, is prevented. This period of conduction through the SR MOSFET body diodes is thereby reduced to a minimum improving overall system efficiency.

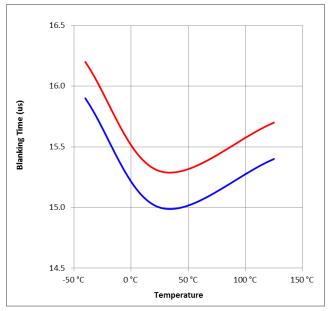

#### Turn-off and reset phases

At the end of the switching cycle the conduction rectifier current reduces to zero so the  $V_{DS}$  voltage will cross the turn-off threshold  $V_{TH1}$ . When this happens the gate is driven low to switch off the SR MOSFET. Any residual current will again start flowing through the body diode causing a negative step in  $V_{DS}$ . When this occurs  $V_{DS}$  could potentially trigger turn-on once again by crossing  $V_{TH2}$ . To prevent this possibility, turn on is blanked for a time period,  $t_{BLANK}$  after turn off has occurred. The blanking time is internally set and can be reset only when  $V_{DS}$  crosses the positive threshold  $V_{TH3}$ . Reset occurs only when  $V_{DS}$  remains higher than  $V_{TH3}$  for more than the reset blanking time,  $t_{BRST}$ . This protects against false triggering due to ringing after the turn-off phase. Once reset the IR11688 is re-armed so that turn on may be triggered for the next conduction cycle.

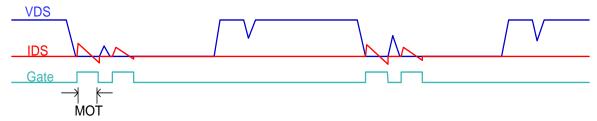

Figure 2: Secondary currents and voltages

#### **Programmable Minimum On Time**

The minimum on time is set by an external resistor (RMOT) connected between the MOT pin and ground. The minimum on time can be calculated based on below equation:

$$T_{MOT} = R_{MOT} \times 2 \times 10^{-11} + 20 \text{ns}$$

where 20ns is the typical internal comparator propagation delay.

RMOT value should remain within the upper and lower limits specified under recommended operating conditions.

### **MOT** protection

Under very light load or zero load conditions, the current in the SR MOSFETs becomes discontinuous and may be shorter than the MOT time in some cases. If this happens, reverse current will flow from the drain to source at the end of the MOT since the gate drive has been kept on. This reverse current discharges the converter output capacitor sending energy back to the transformer and resonating to cause voltage ringing at  $V_{DS}$  at switch off. Such ringing may potentially trigger gate turn on leading to further reverse current and subsequent multiple falsely triggered erroneous gate pulses as illustrated below in Figure 4:

Figure 3: Waveform without MOT protection

The cycle-by-cycle MOT protection function detects reverse current at the end of the MOT period and disables the following gate output pulse preventing further reverse current. The internal comparator and MOT pulse generator continue to operate under the protection mode even when the gate drive is disabled. This enables the circuit to continuously monitor the system load current and automatically revert to normal operating mode once the load current conduction time has again increased to be longer than the MOT. This protection function reduces standby power losses and can also prevent voltage spikes caused by false triggering at light load.

Figure 4: Waveform under MOT protection mode

## **Synchronized Enable Function**

Sync Enable function ensures that gate turn on always occurs at the beginning of a switching cycle.

Figure 5: Synchronized Enable Function

## **Driving Logic Level MOSFET**

An external gate clamping circuit is recommended when driving logic level SR MOSFETs. The clamping circuit keeps the gate voltage below 1V during system power up when the IR11688 is not fully biased in UVLO mode, especially when Vcc is less than 2V. It is not recommended to drive logic level MOSFETs with the IR11688 without a safety clamping circuit.

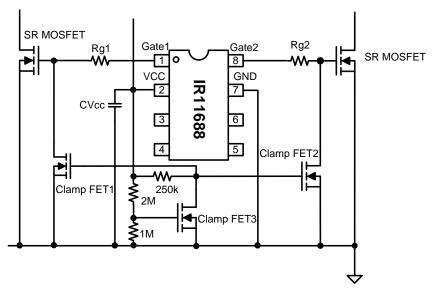

Note the gate regulation feature will be lost when using PNP transistor clamping circuit. Use MOSFET clamping circuit (figure 7) if regulation function is needed.

Figure 6: PNP transistor gate clamping circuit for driving logic level MOSFET

Figure 7: Signal MOSFET gate clamping circuit for driving logic level MOSFET

Figure 8: VD and gate drive output timing

Figure 9: Undervoltage Lockout vs. Temperature

Figure 10: Icc Quiescent Current vs. Temperature

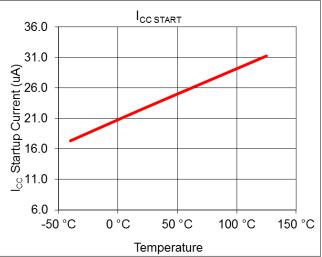

Figure 11: Icc supply current at 1nF load vs. Temperature Figure 12: Icc Startup Current vs. Temperature

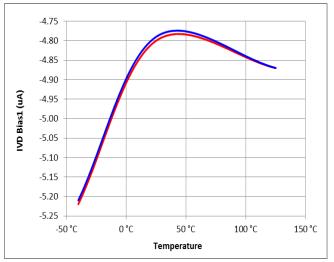

Figure 13: VD bias at -50mV vs. Temperature

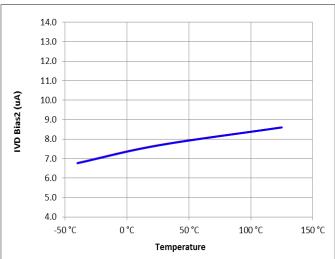

Figure 14: VD bias at 200V vs. Temperature

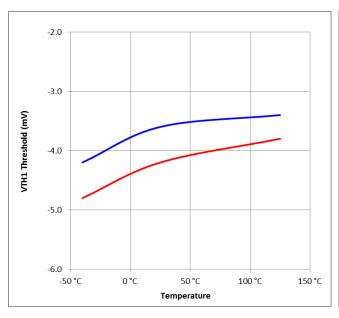

Figure 15: V<sub>TH1</sub> Threshold vs. Temperature

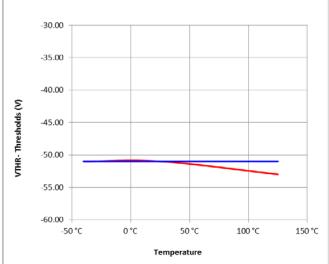

Figure 16: V<sub>TH2</sub> Threshold vs. Temperature

(Red curve channel 1, Blue curve channel 2)

Figure 17: V<sub>TH3</sub> Threshold vs. Temperature

Figure 18: T<sub>BRST</sub> Reset Time vs. Temperature

Figure 19: V<sub>THR+</sub> Threshold vs. Temperature

Figure 20: V<sub>THR</sub>. Threshold vs. Temperature

Figure 21: Minimum On Time vs. Temperature

Figure 22: T<sub>WAIT</sub> Wait Time vs. Temperature

Figure 23: T<sub>BLANK</sub> Blanking Time vs. Temperature

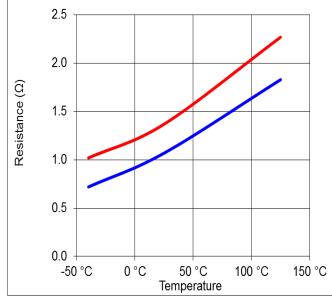

Figure 24: Gate Pull Down Resistance vs. Temperature

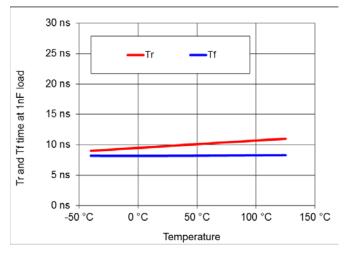

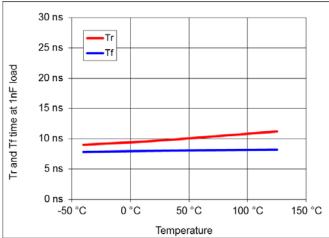

Figure 25: Gate Rise and Fall Time vs. Temperature (CH1) Figure 26: Gate Rise and Fall Time vs. Temperature (CH2)

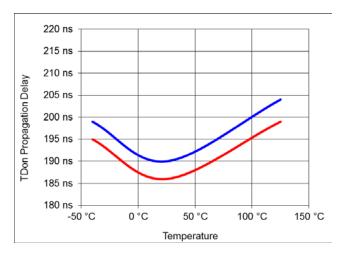

Figure 27: TD<sub>ON</sub> Propagation Delay vs. Temperature

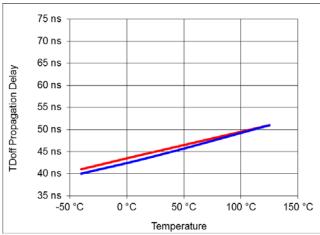

Figure 28: TD<sub>OFF</sub> Propagation Delay vs. Temperature

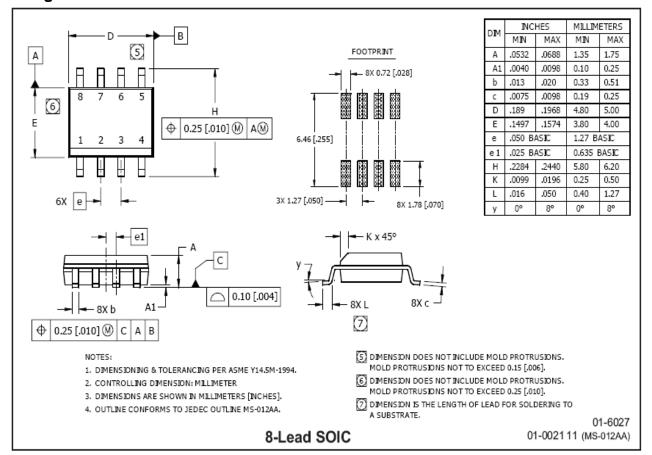

# Package Details: SOIC8N

# Tape and Reel Details: SOIC8N

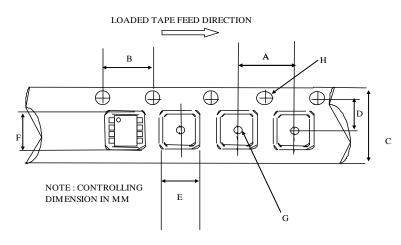

#### CARRIER TAPE DIMENSION FOR 8SOICN

|      | Metric |       | Imperial |       |

|------|--------|-------|----------|-------|

| Code | Min    | Max   | Min      | Max   |

| Α    | 7.90   | 8.10  | 0.311    | 0.318 |

| В    | 3.90   | 4.10  | 0.153    | 0.161 |

| С    | 11.70  | 12.30 | 0.46     | 0.484 |

| D    | 5.45   | 5.55  | 0.214    | 0.218 |

| E    | 6.30   | 6.50  | 0.248    | 0.255 |

| F    | 5.10   | 5.30  | 0.200    | 0.208 |

| G    | 1.50   | n/a   | 0.059    | n/a   |

| Н    | 1.50   | 1.60  | 0.059    | 0.062 |

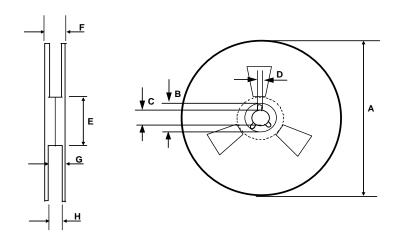

# REEL DIMENSIONS FOR 8SOICN

|      | Metric |        | Imperial |        |

|------|--------|--------|----------|--------|

| Code | Min    | Max    | Min      | Max    |

| Α    | 329.60 | 330.25 | 12.976   | 13.001 |

| В    | 20.95  | 21.45  | 0.824    | 0.844  |

| С    | 12.80  | 13.20  | 0.503    | 0.519  |

| D    | 1.95   | 2.45   | 0.767    | 0.096  |

| E    | 98.00  | 102.00 | 3.858    | 4.015  |

| F    | n/a    | 18.40  | n/a      | 0.724  |

| G    | 14.50  | 17.10  | 0.570    | 0.673  |

| Н    | 12.40  | 14.40  | 0.488    | 0.566  |

# **Part Marking Information**

# Qualification Information<sup>†</sup>

| Qualification Level        |                  | Industrial <sup>††</sup>                                       |                           |  |

|----------------------------|------------------|----------------------------------------------------------------|---------------------------|--|

|                            |                  | Comments: This family of ICs has passed JEDEC's Industrial     |                           |  |

|                            |                  | qualification. IR's Consumer qualification level is granted by |                           |  |

|                            |                  | extension of the higher Industrial level.                      |                           |  |

| Moisture Sensitivity Level |                  | SOIC8N                                                         | MSL2 <sup>†††</sup> 260°C |  |

|                            |                  |                                                                | (per IPC/JEDEC J-STD-020) |  |

| ESD                        | Machine Model    | Class A                                                        |                           |  |

|                            |                  | (per JEDEC standard JESD22-A115)                               |                           |  |

|                            | Human Body Model | Class 1C                                                       |                           |  |

|                            |                  | (per EIA/JEDEC standard EIA/JESD22-A114)                       |                           |  |

| IC Latch-Up Test           |                  | Class I Level A                                                |                           |  |

|                            |                  | (per JESD78)                                                   |                           |  |

| RoHS Compliant             |                  | Yes                                                            |                           |  |

- † Qualification standards can be found at International Rectifier's web site: <a href="http://www.irf.com/product-info/reliability/">http://www.irf.com/product-info/reliability/</a>

- †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

- ††† Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2015 All Rights Reserved.

#### **IMPORTANT NOTICE**

The information given in this document shall in <u>no event</u> be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may <u>not</u> be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.