# ISM RF SYNTHESIZER WITH INTEGRATED VCOS FOR WIRELESS COMMUNICATIONS

#### **Features**

- Dual-band RF synthesizers

- RF1: 2300 MHz to 2500 MHz

- RF2: 2025 MHz to 2300 MHz

- IF synthesizer

- 62.5 MHz to 1000 MHz

- Integrated VCOs, loop filters, varactors, and resonators

- Minimal external components required

- Low phase noise

- 5 µA standby current

- 25.7 mA typical supply current

- 2.7 V to 3.6 V operation

- Packages: 24-pin TSSOP, 28-lead QFN

- Lead-free/RoHS-compliant options available

# Ordering Information: See page 29.

#### **Applications**

- ISM and MMDS band communications

- Wireless LAN and WAN

- Dual-band communications

#### **Description**

The Si4136 is a monolithic integrated circuit that performs both IF and RF synthesis for wireless communications applications. The Si4136 includes three VCOs, loop filters, reference and VCO dividers, and phase detectors. Divider and powerdown settings are programmable through a three-wire serial interface.

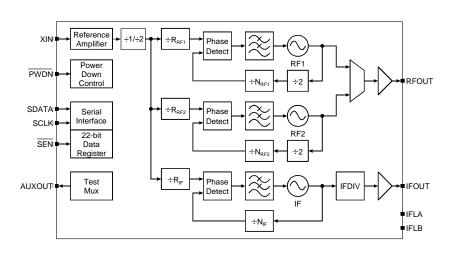

#### **Functional Block Diagram**

# TABLE OF CONTENTS

| <u>Section</u>                             | <u>Page</u> |

|--------------------------------------------|-------------|

| 1. Electrical Specifications               |             |

| 2. Functional Description                  |             |

| 2.1. Serial Interface                      |             |

| 2.2. Setting the IF VCO Center Frequencies |             |

| 2.3. Self-Tuning Algorithm                 |             |

| 2.4. Output Frequencies                    |             |

| 2.5. PLL Loop Dynamics                     |             |

| 2.6. RF and IF Outputs (RFOUT and IFOUT)   |             |

| 2.7. Reference Frequency Amplifier         |             |

| 2.8. Powerdown Modes                       |             |

| 2.9. Auxiliary Output (AUXOUT)             |             |

| 3. Control Registers                       |             |

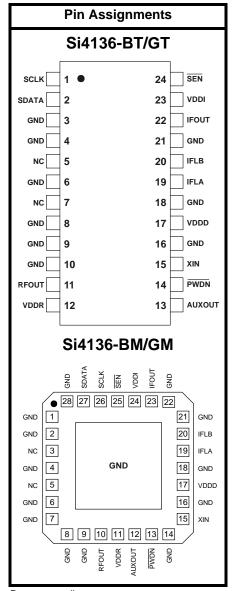

| 4. Pin Descriptions: Si4136-BT/GT          |             |

| 5. Pin Descriptions: Si4136-BM/GM          |             |

| 6. Ordering Guide                          |             |

| 7. Si4136 Derivative Devices               |             |

| 8. Package Outline: Si4136-BT/GT           |             |

| 9. Package Outline: Si4136-BM/GM           |             |

| Document Change List                       |             |

| Contact Information                        |             |

## 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter                  | Symbol         | Test Condition                                  | Min  | Тур | Max | Unit |

|----------------------------|----------------|-------------------------------------------------|------|-----|-----|------|

| Ambient Temperature        | T <sub>A</sub> |                                                 | -40  | 25  | 85  | °C   |

| Supply Voltage             | $V_{DD}$       |                                                 | 2.7  | 3.0 | 3.6 | V    |

| Supply Voltages Difference | $V_{\Delta}$   | $(V_{DDR} - V_{DDD}),$<br>$(V_{DDI} - V_{DDD})$ | -0.3 | _   | 0.3 | V    |

**Note:** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25°C unless otherwise stated.

Table 2. Absolute Maximum Ratings<sup>1,2</sup>

| Parameter                  | Symbol           | Value                        | Unit |

|----------------------------|------------------|------------------------------|------|

| DC Supply Voltage          | V <sub>DD</sub>  | -0.5 to 4.0                  | V    |

| Input Current <sup>3</sup> | I <sub>IN</sub>  | ±10                          | mA   |

| Input Voltage <sup>3</sup> | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage Temperature Range  | T <sub>STG</sub> | -55 to 150                   | °C   |

#### Notes:

- 1. Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. This device is a high performance RF integrated circuit with an ESD rating of < 2 kV. Handling and assembly of this device should only be done at ESD-protected workstations.

- 3. For signals SCLK, SDATA, SEN, PWDN, and XIN.

#### **Table 3. DC Characteristics**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                              | Symbol          | Test Condition                                        | Min                  | Тур  | Max                 | Unit |

|----------------------------------------|-----------------|-------------------------------------------------------|----------------------|------|---------------------|------|

| Total Supply Current <sup>1</sup>      |                 | RF1 and IF operating                                  |                      | 25.7 | 31                  | mA   |

| RF1 Mode Supply Current <sup>1</sup>   |                 |                                                       |                      | 15.7 | 19                  | mA   |

| RF2 Mode Supply Current <sup>1</sup>   |                 |                                                       | _                    | 15   | 18                  | mA   |

| IF Mode Supply Current <sup>1</sup>    |                 |                                                       | _                    | 10   | 12                  | mA   |

| Standby Current                        |                 | PWDN = 0                                              | _                    | 1    | _                   | μΑ   |

| High Level Input Voltage <sup>2</sup>  | V <sub>IH</sub> |                                                       | 0.7 V <sub>DD</sub>  | _    | _                   | V    |

| Low Level Input Voltage <sup>2</sup>   | V <sub>IL</sub> |                                                       | _                    | _    | 0.3 V <sub>DD</sub> | V    |

| High Level Input Current <sup>2</sup>  | I <sub>IH</sub> | $V_{IH} = 3.6 \text{ V},$<br>$V_{DD} = 3.6 \text{ V}$ | -10                  | _    | 10                  | μΑ   |

| Low Level Input Current <sup>2</sup>   | I <sub>IL</sub> | V <sub>IL</sub> = 0 V,<br>V <sub>DD</sub> = 3.6 V     | -10                  | _    | 10                  | μΑ   |

| High Level Output Voltage <sup>3</sup> | V <sub>OH</sub> | I <sub>OH</sub> = -500 μA                             | V <sub>DD</sub> -0.4 | _    | _                   | V    |

| Low Level Output Voltage <sup>3</sup>  | V <sub>OL</sub> | I <sub>OH</sub> = 500 μA                              | _                    | 1    | 0.4                 | V    |

#### Notes:

- RF1 = 2.4 GHz, RF2 = 2.1 GHz, IFOUT = 800 MHz, LPWR = 0.

For signals SCLK, SDATA, SEN, and PWDN.

- 3. For signal AUXOUT.

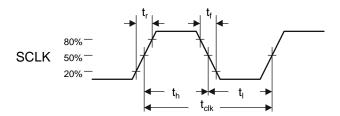

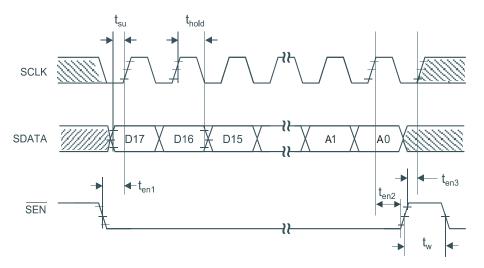

#### **Table 4. Serial Interface Timing**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter <sup>1</sup>                 | Symbol            | Test Condition | Min | Тур | Max | Unit |

|----------------------------------------|-------------------|----------------|-----|-----|-----|------|

| SCLK Cycle Time                        | t <sub>clk</sub>  | Figure 1       | 40  | _   | _   | ns   |

| SCLK Rise Time                         | t <sub>r</sub>    | Figure 1       | _   | _   | 50  | ns   |

| SCLK Fall Time                         | t <sub>f</sub>    | Figure 1       | _   | _   | 50  | ns   |

| SCLK High Time                         | t <sub>h</sub>    | Figure 1       | 10  | _   | _   | ns   |

| SCLK Low Time                          | t <sub>i</sub>    | Figure 1       | 10  | _   | _   | ns   |

| SDATA Setup Time to SCLK <sup>↑2</sup> | t <sub>su</sub>   | Figure 2       | 5   | _   | _   | ns   |

| SDATA Hold Time from SCLK <sup>2</sup> | t <sub>hold</sub> | Figure 2       | 0   | _   |     | ns   |

| SEN↓ to SCLK↑ Delay Time²              | t <sub>en1</sub>  | Figure 2       | 10  | _   | _   | ns   |

| SCLK↑ to SEN↑ Delay Time²              | t <sub>en2</sub>  | Figure 2       | 12  | _   | _   | ns   |

| SEN↑ to SCLK↑ Delay Time²              | t <sub>en3</sub>  | Figure 2       | 12  | _   | _   | ns   |

| SEN Pulse Width                        | t <sub>w</sub>    | Figure 2       | 10  | _   | _   | ns   |

#### Notes:

- 1. All timing is referenced to the 50% level of the waveform, unless otherwise noted.

- 2. Timing is not referenced to 50% level of the waveform. See Figure 2.

Figure 1. SCLK Timing Diagram

Figure 2. Serial Interface Timing Diagram

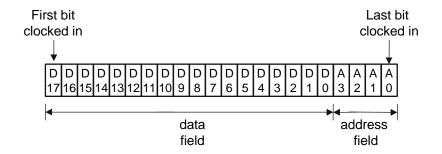

Figure 3. Serial Word Format

# Si4136/Si4126

#### **Table 5. RF and IF Synthesizer Characteristics**

(V<sub>DD</sub> = 2.7 to 3.6 V,  $T_A$  = -40 to 85 °C)

| Parameter <sup>1</sup>                       | Symbol                                                                                                                                  | Test Condition    | Min   | Тур   | Max                       | Unit            |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------|---------------------------|-----------------|

| XIN Input Frequency                          | f <sub>REF</sub>                                                                                                                        | XINDIV2 = 0       | 2     | _     | 25                        | MHz             |

| XIN Input Frequency                          | f <sub>REF</sub>                                                                                                                        | XINDIV2 = 1       | 25    | _     | 50                        | MHz             |

| Reference Amplifier Sensitivity              | $V_{REF}$                                                                                                                               |                   | 0.5   | _     | V <sub>DD</sub><br>+0.3 V | V <sub>PP</sub> |

| Phase Detector Update Frequency              | Detector Update Frequency $f_{\varphi} = f_{REF}/R \text{ for } \\ XINDIV2 = 0 \\ f_{\varphi} = f_{REF}/2R \text{ for } \\ XINDIV2 = 1$ |                   | 0.010 | _     | 1.0                       | MHz             |

| RF1 VCO Tuning Range <sup>2</sup>            |                                                                                                                                         |                   | 2300  | _     | 2500                      | MHz             |

| RF2 VCO Tuning Range <sup>2</sup>            |                                                                                                                                         |                   | 2025  | _     | 2300                      | MHz             |

| IF VCO Center Frequency Range                | f <sub>CEN</sub>                                                                                                                        |                   | 526   | _     | 952                       | MHz             |

| IFOUT Tuning Range from f <sub>CEN</sub>     |                                                                                                                                         | with IFDIV        | 62.5  | _     | 1000                      | MHz             |

| IFOUT VCO Tuning Range from f <sub>CEN</sub> |                                                                                                                                         | Note: L ±10%      | -5    | _     | 5                         | %               |

| RF1 VCO Pushing                              |                                                                                                                                         | Open loop         | _     | 0.75  | _                         | MHz/V           |

| RF2 VCO Pushing                              |                                                                                                                                         |                   | _     | 0.65  | _                         | MHz/V           |

| IF VCO Pushing                               |                                                                                                                                         |                   | _     | 0.10  | _                         | MHz/V           |

| RF1 VCO Pulling                              |                                                                                                                                         | VSWR = 2:1, all   | _     | 0.250 | _                         | MHz p-p         |

| RF2 VCO Pulling                              |                                                                                                                                         | phases, open loop | _     | 0.100 | _                         | MHz p-p         |

| IF VCO Pulling                               |                                                                                                                                         |                   | _     | 0.025 | _                         | MHz p-p         |

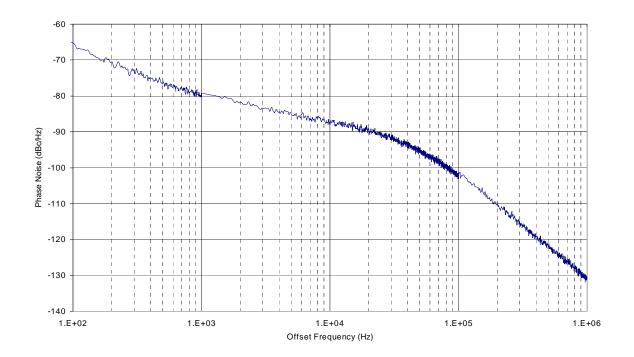

| RF1 Phase Noise                              |                                                                                                                                         | 1 MHz offset      | _     | -130  | _                         | dBc/Hz          |

| RF1 Integrated Phase Error                   |                                                                                                                                         | 100 Hz to 100 kHz | _     | 1.2   | _                         | degrees<br>rms  |

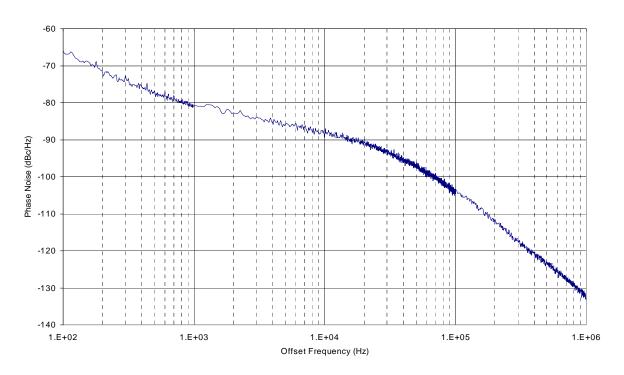

| RF2 Phase Noise                              |                                                                                                                                         | 1 MHz offset      | _     | -131  | _                         | dBc/Hz          |

| RF2 Integrated Phase Error                   |                                                                                                                                         | 100 Hz to 100 kHz | _     | 1.0   | _                         | degrees<br>rms  |

| IF Phase Noise at 800 MHz                    |                                                                                                                                         | 100 kHz offset    | _     | -104  | _                         | dBc/Hz          |

| IF Integrated Phase Error                    |                                                                                                                                         | 100 Hz to 100 kHz | _     | 0.4   | _                         | degrees<br>rms  |

#### Notes:

- 1.  $f_{\phi}(RF) = 1$  MHz,  $f_{\phi}(IF) = 1$  MHz, RF1 = 2.4 GHz, RF2 = 2.1 GHz, IFOUT = 800 MHz, LPWR = 0, for all parameters unless otherwise noted.

- 2. RF VCO tuning range limits are fixed by inductance of internally bonded wires.

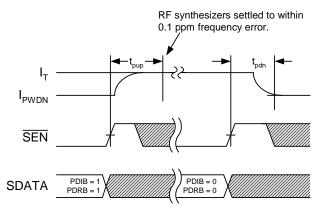

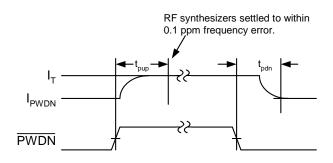

- 3. From powerup request (PWDN↑ or SEN↑ during a write of 1 to bits PDIB and PDRB in Register 2) to RF and IF synthesizers ready (settled to within 0.1 ppm frequency error).

- **4.** From powerdown request (PWDN↓, or SEN↑ during a write of 0 to bits PDIB and PDRB in Register 2) to supply current equal to I<sub>PWDN</sub>.

#### Table 5. RF and IF Synthesizer Characteristics (Continued)

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, T_A = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter <sup>1</sup>                                 | Symbol           | Test Condition                              | Min        | Тур                  | Max               | Unit |

|--------------------------------------------------------|------------------|---------------------------------------------|------------|----------------------|-------------------|------|

| RF1 Harmonic Suppression                               |                  | Second Harmonic                             | _          | -28                  | -20               | dBc  |

| RF2 Harmonic Suppression                               |                  |                                             | _          | -23                  | -20               | dBc  |

| IF Harmonic Suppression                                |                  |                                             | -          | -26                  | -20               | dBc  |

| RFOUT Power Level                                      |                  | $Z_L = 50 \Omega$ , RF1 active              | -7         | -3.5                 | -0.5              | dBm  |

| RFOUT Power Level                                      |                  | $Z_L = 50 \Omega$ , RF2 active              | <b>-</b> 7 | -3.5                 | -0.5              | dBm  |

| IFOUT Power Level                                      |                  | $Z_L = 50 \Omega$                           | -7         | -4                   | 0                 | dBm  |

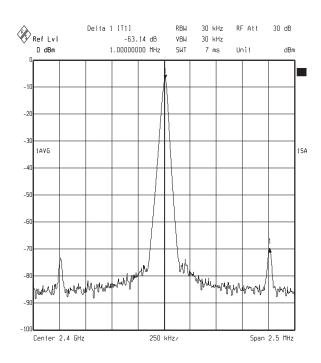

| RF1 Output Reference Spurs                             |                  | Offset = 1 MHz                              | _          | -63                  | _                 | dBc  |

|                                                        |                  | Offset = 2 MHz                              |            | -68                  | _                 | dBc  |

|                                                        |                  | Offset = 3 MHz                              |            | -70                  | _                 | dBc  |

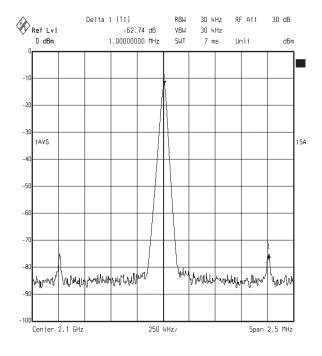

| RF2 Output Reference Spurs                             |                  | Offset = 1 MHz                              | _          | -63                  | _                 | dBc  |

|                                                        |                  | Offset = 2 MHz                              |            | -68                  | _                 | dBc  |

|                                                        |                  | Offset = 3 MHz                              |            | -70                  | _                 | dBc  |

| Powerup Request to Synthesizer Ready <sup>3</sup> Time | t <sub>pup</sub> | Figures 4, 5 $f_{\phi}$ > 500 kHz           | _          | 80                   | 100               | μS   |

| Powerup Request to Synthesizer Ready <sup>3</sup> Time | t <sub>pup</sub> | Figures 4, 5 $f_{\phi} \le 500 \text{ kHz}$ | _          | 40/f <sub>\phi</sub> | 50/f <sub>φ</sub> |      |

| Powerdown Request to Synthesizer Off <sup>4</sup> Time | t <sub>pdn</sub> | Figures 4, 5                                | _          | _                    | 100               | ns   |

#### Notes:

- 1.  $f_{\phi}(RF) = 1$  MHz,  $f_{\phi}(IF) = 1$  MHz, RF1 = 2.4 GHz, RF2 = 2.1 GHz, IFOUT = 800 MHz, LPWR = 0, for all parameters unless otherwise noted.

- 2. RF VCO tuning range limits are fixed by inductance of internally bonded wires.

- **3.** From powerup request (PWDN↑ or SEN↑ during a write of 1 to bits PDIB and PDRB in Register 2) to RF and IF synthesizers ready (settled to within 0.1 ppm frequency error).

- **4.** From powerdown request (PWDN↓, or SEN↑ during a write of 0 to bits PDIB and PDRB in Register 2) to supply current equal to I<sub>PWDN</sub>.

Figure 4. Software Power Management Timing Diagram

Figure 5. Hardware Power Management Timing Diagram

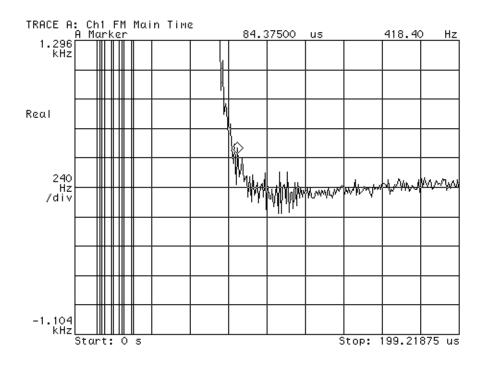

Figure 6. Typical Transient Response RF1 at 2.4 GHz with 1 MHz Phase Detector Update Frequency

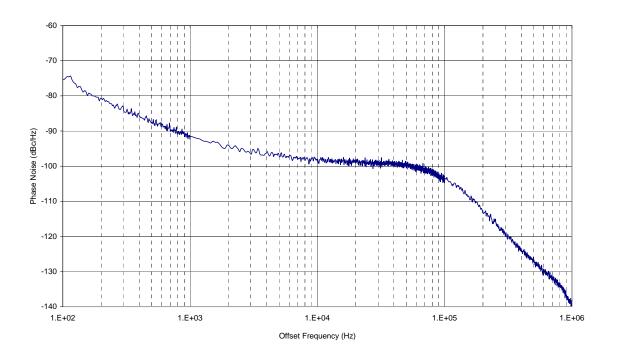

Typical RF1 Phase Noise at 2.4 GHz

Figure 7. Typical RF1 Phase Noise at 2.4 GHz with 1 MHz Phase Detector Update Frequency

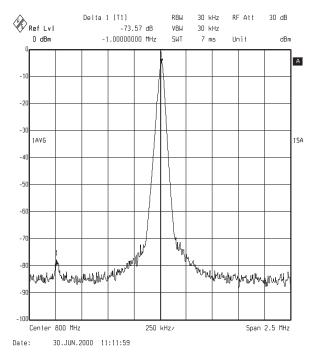

Figure 8. Typical RF1 Spurious Response at 2.4 GHz with 1 MHz Phase Detector Update Frequency

s

Typical RF2 Phase Noise at 2.1 GHz

Figure 9. Typical RF2 Phase Noise at 2.1 GHz with 1 MHz Phase Detector Update Frequency

Figure 10. Typical RF2 Spurious Response at 2.1 GHz with 1 MHz Phase Detector Update Frequency

Typical IF Phase Noise at 800 MHz

Figure 11. Typical IF Phase Noise at 800 MHz with 1 MHz Phase Detector Update Frequency

Figure 12. IF Spurious Response at 800 MHz with 1 MHz Phase Detector Update Frequency

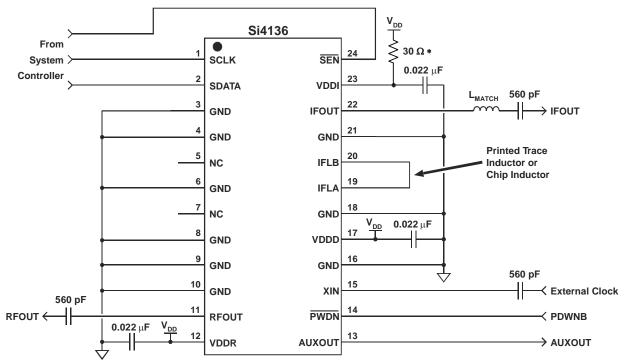

\*Add 30  $\Omega$  series resistor if using IF output divide values 2, 4, or 8 and f  $_{\rm CEN}\,$  < 600 MHz.

Figure 13. Typical Application Circuit: Si4136-BT/GT

## 2. Functional Description

The Si4136 is a monolithic integrated circuit that performs IF and dual-band RF synthesis for many wireless communications applications. This integrated circuit (IC), along with a minimum number of external components, is all that is necessary to implement the frequency synthesis function in applications like W-LAN using the IEEE 802.11 standard.

The Si4136 has three complete phase-locked loops (PLLs), with integrated voltage-controlled oscillators (VCOs). The low phase noise of the VCOs makes the Si4136 suitable for use in demanding wireless communications applications. Also integrated are phase detectors, loop filters, and reference and output frequency dividers. The IC is programmed through a three-wire serial interface.

Two PLLs are provided for RF synthesis. These RF PLLs are multiplexed so that only one PLL is active at a given time (as determined by the setting of an internal register). The active PLL is the last one written. The center frequency of the VCO in each PLL is set by the internal bond wire inductance within the package. Inaccuracies in these inductances are compensated for by the self-tuning algorithm. The algorithm is run following power-up or following a change in the programmed output frequency.

The RF PLLs contain a divide-by-2 circuit before the N-divider. As a result, the phase detector frequency (f $\phi$ ) is equal to half the desired channel spacing. For example, for a 200 kHz channel spacing, f $\phi$  would equal 100 kHz. The IF PLL does not contain the divide-by-2 circuit before the N-divider. In this case, f $\phi$  is equal to the desired channel spacing. Each RF VCO is optimized for a particular frequency range. The RF1 VCO is optimized to operate from 2.3 GHz to 2.5 GHz, while the RF2 VCO is optimized to operate between 2.025 GHz and 2.3 GHz.

One PLL is provided for IF synthesis. The center frequency of this circuit's VCO is set by an external inductance. The PLL can adjust the IF output frequency by ±5% of the VCO center frequency. Inaccuracies in the value of the external inductance are compensated for by the Si4136's proprietary self-tuning algorithm. This algorithm is initiated each time the PLL is powered-up (by either the PWDN pin or by software) and/or each time a new output frequency is programmed. The IF VCO can have its center frequency set as low as 526 MHz and as high as 952 MHz. An IF output divider is provided to divide down the IF output frequencies, if needed. The divider is programmable, capable of dividing by 1, 2, 4, or 8.

In order to accommodate designs running at XIN

frequencies greater than 25 MHz, the Si4136 includes a programmable divide-by-2 option (XINDIV2 in Register 0, D6) on the XIN input. By enabling this option, the Si4136 can accept a range of TCXO frequencies from 25 MHz to 50 MHz. This feature makes the Si4136 ideal for W-LAN radio designs operating at an XIN of 44 MHz.

The unique PLL architecture used in the Si4136 produces settling (lock) times that are comparable in speed to fractional-N architectures without suffering the high phase noise or spurious modulation effects often associated with those designs.

#### 2.1. Serial Interface

A timing diagram for the serial interface is shown in Figure 2 on page 7. Figure 3 on page 7 shows the format of the serial word.

The Si4136 is programmed serially with 22-bit words comprised of 18-bit data fields and 4-bit address fields. When the serial interface is enabled (i.e., when SEN is low) data and address bits on the SDATA pin are clocked into an internal shift register on the rising edge of SCLK. Data in the shift register is then transferred on the rising edge of SEN into the internal data register addressed in the address field. The serial interface is disabled when SEN is high.

Table 11 on page 21 summarizes the data register functions and addresses. It is not necessary (although it is permissible) to clock into the internal shift register any leading bits that are "don't cares."

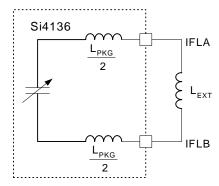

## 2.2. Setting the IF VCO Center Frequencies

The IF PLL can adjust its output frequency ±5% from the center frequency as established by the value of an external inductance connected to the VCO. The RF1 and RF2 PLLs have fixed operating ranges due to the inductance set by the internal bond wires. Each center frequency is established by the value of the total inductance (internal and/or external) connected to the respective VCO. Manufacturing tolerance of ±10% for the external inductor is acceptable for the IF VCO. The Si4136 will compensate for inaccuracies by executing a self-tuning algorithm following PLL power-up or following a change in the programmed output frequency.

Because the total tank inductance is in the low nH range, the inductance of the package needs to be considered in determining the correct external inductance. The total inductance ( $L_{TOT}$ ) presented to the IF VCO is the sum of the external inductance ( $L_{EXT}$ ) and the package inductance ( $L_{PKG}$ ). The IF VCO has a nominal capacitance ( $C_{NOM}$ ) in parallel with the total inductance, and the center frequency is as follows:

$$f_{CEN} = \frac{1}{2\pi \sqrt{L_{TOT} \cdot C_{NOM}}} = \frac{1}{2\pi \sqrt{(L_{PKG} + L_{EXT}) \cdot C_{NOM}}}$$

Table 6 summarizes the characteristics of the IF VCO.

Table 6. Si4136-BT/GT VCO Characteristics

| vco | Fcen I | _   | Cnom<br>(pF) | Lpkg<br>(nH) | Lext F<br>(n | _    |

|-----|--------|-----|--------------|--------------|--------------|------|

|     | Min    | Max |              |              | Min          | Max  |

| IF  | 526    | 952 | 6.5          | 2.1          | 2.2          | 12.0 |

Figure 14. Example of IF External Inductor

design example, suppose synthesizing frequencies in a 30 MHz band between 735 MHz and 765 MHz is desired. The center frequency should be defined as midway between the two extremes, or 750 MHz. The PLL will be able to adjust the VCO output frequency ±5% of the center frequency, or ±37.5 MHz of 750 MHz (i.e., from approximately 713 MHz to 788 MHz). The IF VCO has a  $C_{NOM}$  of 6.5 pF, and a 6.9 nH inductance (correct to two digits) in parallel with this capacitance will yield the desired center frequency. An external inductance of 4.8 nH should be connected between IFLA and IFLB, as shown in Figure 14. This, in addition to 2.1 nH of package inductance, will present the correct total inductance to the VCO. In manufacturing, the external inductance can vary ±10% of its nominal value and the Si4136 will correct for the variation with the self-tuning algorithm.

For more information on designing the external trace inductor, please refer to Application Note 31.

#### 2.3. Self-Tuning Algorithm

The self-tuning algorithm is initiated immediately following power-up of a PLL or, if the PLL is already powered, following a change in its programmed output frequency. This algorithm attempts to tune the VCO so that its free-running frequency is near the desired output frequency. In so doing, the algorithm will compensate for manufacturing tolerance errors in the value of the external inductance connected to the IF VCO. It will also reduce the frequency error for which the PLL must correct to get the precise desired output frequency. The self-tuning algorithm will leave the VCO oscillating at a frequency in error by somewhat less than 1% of the desired output frequency.

After self-tuning, the PLL controls the VCO oscillation frequency. The PLL will complete frequency locking, eliminating any remaining frequency error. Thereafter, it will maintain frequency-lock, compensating for effects caused by temperature and supply voltage variations.

The Si4136's self-tuning algorithm will compensate for component value errors at any temperature within the specified temperature range. However, the ability of the PLL to compensate for drift in component values that occur *after* self-tuning is limited. For external inductances with temperature coefficients around ±150 ppm/°C, the PLL will be able to maintain lock for changes in temperature of approximately ±30°C.

Applications where the PLL is regularly powered-down or the frequency is periodically reprogrammed minimize or eliminate the potential effects of temperature drift because the VCO is re-tuned in either case. In applications where the ambient temperature can drift substantially after self-tuning, it may be necessary to monitor the lock-detect bar (LDETB) signal on the AUXOUT pin to determine whether a PLL is about to run out of locking capability. (See "2.9. Auxiliary Output (AUXOUT)" for how to select LDETB.) The LDETB signal will be low after self-tuning has completed but will rise when either the IF or RF PLL nears the limit of its compensation range. (LDETB will also be high when either PLL is executing the self-tuning algorithm.) The output frequency will still be locked when LDETB goes high, but the PLL will eventually lose lock if the temperature continues to drift in the same direction. Therefore, if LDETB goes high both the IF and RF PLLs should promptly be re-tuned by initiating the self-tuning algorithm.

#### 2.4. Output Frequencies

The IF and RF output frequencies are set by programming the R- and N-Divider registers. Each PLL has its own R and N registers so that each can be

programmed independently. Programming either the Ror N-Divider register for RF1 or RF2 automatically selects the associated output.

When XINDIV2 = 0, the reference frequency on the XIN pin is divided by R and this signal is the input to the PLL's phase detector. The other input to the phase detector is the PLL's VCO output frequency divided by 2N for the RF PLLs or N for the IF PLL. After an initial transient

Equation 1.

$$f_{OUT} = (2N/R) \cdot f_{REF}$$

(for the RF PLLs)

Equation 2.  $f_{OUT} = (N/R) \cdot f_{REF}$  (for the IF PLL).

The integers R are set by programming the RF1 R-Divider register (Register 6), the RF2 R-Divider register (Register 7) and the IF R-Divider register (Register 8).

The integers N are set by programming the RF1 N-Divider register (register 3), the RF2 N-Divider register (Register 4), and the IF N-Divider register (Register 5).

If the optional divide-by-2 circuit on the XIN pin is enabled (XINDIV2 = 1) then after an initial transient

$$f_{OUT} = (N/R) \cdot f_{REF}$$

(for the RF PLLs)

$f_{OUT} = (N/2R) \cdot f_{REF}$  (for the IF PLL).

Each N-Divider is implemented as a conventional high speed divider. That is, it consists of a dual-modulus prescaler, a swallow counter, and a lower speed synchronous counter. However, the control of these sub-circuits is handled automatically. Only the appropriate N value should be programmed.

#### 2.5. PLL Loop Dynamics

The transient response for each PLL is determined by its phase detector update rate  $f_{\varphi}$  (equal to  $f_{REF}/R$ ) and the phase detector gain programmed for each RF1, RF2, or IF synthesizer. (See Register 1.) Four different settings for the phase detector gain are available for each PLL. The highest gain is programmed by setting the two phase detector gain bits to 00, and the lowest by setting the bits to 11. The values of the available gains, relative to the highest gain, are listed in Table 7.

Table 7. Gain Values (Register 1)

| K <sub>P</sub> Bits | Relative P.D.<br>Gain |

|---------------------|-----------------------|

| 00                  | 1                     |

| 01                  | 1/2                   |

| 10                  | 1/4                   |

| 11                  | 1/8                   |

In general, a higher phase detector gain will decrease in-band phase noise and increase the speed of the PLL

transient until the point at which stability begins to be compromised. The optimal gain depends on N. Table 8 lists recommended settings for different values of N.

Table 8. Optimal K<sub>P</sub> Settings

| N             | RF1<br>K <sub>P1</sub> <1:0> | RF2<br>K <sub>P2</sub> <1:0> | IF<br>K <sub>PI</sub> <1:0> |

|---------------|------------------------------|------------------------------|-----------------------------|

| ≤2047         | 00                           | 00                           | 00                          |

| 2048 to 4095  | 00                           | 01                           | 01                          |

| 4096 to 8191  | 01                           | 10                           | 10                          |

| 8192 to 16383 | 10                           | 11                           | 11                          |

| ≥16384        | 11                           | 11                           | 11                          |

The VCO gain and loop filter characteristics are not programmable.

The settling time for each PLL is directly proportional to its phase detector update period  $T_{\varphi}$  ( $T_{\varphi}$  equals  $1/f_{\varphi}$ ). During the first 13 update periods the Si4136 executes the self-tuning algorithm. Thereafter the PLL controls the output frequency. Because of the unique architecture of the Si4136 PLLs, the time required to settle the output frequency to 0.1 ppm error is only about 25 update periods. Thus, the total time after power-up or a change in programmed frequency until the synthesized frequency is well settled—including time for self-tuning—is around 40 update periods.

**Note:** This settling time analysis holds for  $f_{\varphi} \le 500$  kHz. For  $f_{\varphi} > 500$  kHz, the settling time can be a maximum of 100  $\mu s$  as specified in Table 5.

## 2.6. RF and IF Outputs (RFOUT and IFOUT)

The RFOUT and IFOUT pins are driven by amplifiers that buffer the RF VCOs and IF VCO, respectively. The RF output amplifier receives its input from either the RF1 or RF2 VCO, depending upon which R- or N-Divider register was last written. For example, programming the N-Divider register for RF1 automatically selects the RF1 VCO output.

Figure 13 on page 15 shows an application diagram for the Si4136. The RF output signal must be AC coupled to its load through a capacitor.

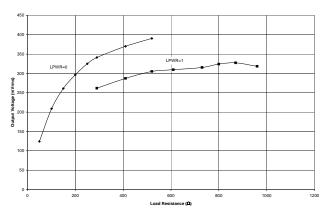

The IFOUT pin must also be AC coupled to its load through a capacitor. The IF output level is dependent upon the load. Figure 17 displays the output level versus load resistance. For resistive loads greater than 500  $\Omega$  the output level saturates and the bias currents in the IF output amplifier are higher than they need to be. The LPWR bit in the Main Configuration register

(Register 0) can be set to 1 to reduce the bias currents and therefore reduce the power dissipated by the IF amplifier. For loads less than 500  $\Omega$ , LPWR should be set to 0 to maximize the output level.

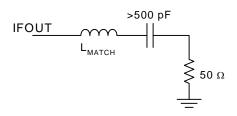

For IF frequencies greater than 500 MHz, a matching network is required in order to drive a 50  $\Omega$  load. See Figure 15 below. The value of L<sub>MATCH</sub> can be determined by Table 9.

Typical values range between 8 nH and 40 nH.

Figure 15. IF Frequencies > 500 MHz

Table 9. L<sub>MATCH</sub> Values

| Frequency   | L <sub>MATCH</sub> |

|-------------|--------------------|

| 500–600 MHz | 40 nH              |

| 600-800 MHz | 27 nH              |

| 800–1 GHz   | 18 nH              |

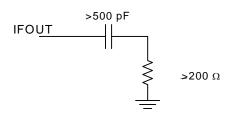

For frequencies less than 500 MHz, the IF output buffer can directly drive a 200  $\Omega$  resistive load or higher. For resistive loads greater than 500  $\Omega$  (f < 500 MHz) the LPWR bit can be set to reduce the power consumed by the IF output buffer. See Figure 16 below.

Figure 16. IF Frequencies < 500 MHz

Figure 17. Typical IF Output Voltage vs. Load Resistance at 550 MHz

### 2.7. Reference Frequency Amplifier

The Si4136 provides a reference frequency amplifier. If the driving signal has CMOS levels, it can be connected directly to the XIN pin. Otherwise, the reference frequency signal should be AC coupled to the XIN pin through a 560 pF capacitor.

#### 2.8. Powerdown Modes

Table 10 summarizes the powerdown functionality. The Si4136 can be powered down by taking the PWDN pin low or by setting bits in the Powerdown register (Register 2). When the PWDN pin is low, the Si4136 will be powered down regardless of the Powerdown register settings. When the PWDN pin is high, power management is under control of the Powerdown register bits.

The IF and RF sections of the Si4136 circuitry can be individually powered down by setting the Powerdown register bits PDIB and PDRB low. The reference frequency amplifier will also be powered up if either the PDRB and PDIB bits are high. Also, setting the AUTOPDB bit to 1 in the Main Configuration register (Register 0) is equivalent to setting both bits in the Powerdown register to 1.

The serial interface remains available and can be written in all power-down modes.

#### 2.9. Auxiliary Output (AUXOUT)

The signal appearing on AUXOUT is selected by setting the AUXSEL bits in the Main Configuration register (Register 0).

The LDETB signal can be selected by setting the AUXSEL bits to 011. This signal can be used to indicate that the IF or RF PLL is about to lose lock due to excessive ambient temperature drift and should be retuned.

**Table 10. Powerdown Configuration**

| PWDN Pin                     | AUTOPDB | PDIB | PDRB | IF Circuitry | RF<br>Circuitry |

|------------------------------|---------|------|------|--------------|-----------------|

| $\overline{\text{PWDN}} = 0$ | х       | x    | x    | OFF          | OFF             |

|                              | 0       | 0    | 0    | OFF          | OFF             |

|                              | 0       | 0    | 1    | OFF          | ON              |

| PWDN = 1                     | 0       | 1    | 0    | ON           | OFF             |

|                              | 0       | 1    | 1    | ON           | ON              |

|                              | 1       | Х    | х    | ON           | ON              |

|                              | '       |      |      | 011          |                 |

**Note:** x = don't care.

# 3. Control Registers

**Table 11. Register Summary**

| Register | Name                      | Bit<br>17 | Bit<br>16 | Bit<br>15 | Bit<br>14 | Bit<br>13        | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit<br>9 | Bit<br>8 | Bit<br>7         | Bit<br>6    | Bit<br>5        | Bit<br>4 | Bit<br>3    | Bit<br>2 | Bit<br>1 | Bit<br>0 |

|----------|---------------------------|-----------|-----------|-----------|-----------|------------------|-----------|-----------|-----------|----------|----------|------------------|-------------|-----------------|----------|-------------|----------|----------|----------|

| 0        | Main<br>Configuration     | 0         | 0         | 0         | 0         | AUX              | SEL       | IF        | ΟΙV       | 0        | 0        | 0                | XIN<br>DIV2 | LPWR            | 0        | AUTO<br>PDB | 0        | 0        | 0        |

| 1        | Phase<br>Detector<br>Gain | 0         | 0         | 0         | 0         | 0                | 0         | 0         | 0         | 0        | 0        | 0                | 0           | K               | PI       | K           | P2       | K        | P1       |

| 2        | Powerdown                 | 0         | 0         | 0         | 0         | 0                | 0         | 0         | 0         | 0        | 0        | 0                | 0           | 0               | 0        | 0           | 0        | PDIB     | PDRB     |

| 3        | RF1 N<br>Divider          |           |           |           |           | N <sub>RF1</sub> |           |           |           |          |          |                  |             |                 |          |             |          |          |          |

| 4        | RF2 N<br>Divider          | 0         |           |           |           |                  |           |           |           |          |          | N <sub>RF2</sub> | 2           |                 |          |             |          |          |          |

| 5        | IF N Divider              | 0         | 0         |           |           |                  |           |           |           |          |          | Ν                | IF          |                 |          |             |          |          |          |

| 6        | RF1 R<br>Divider          | 0         | 0         | 0         | 0         | 0                |           |           |           |          |          |                  | R           | RF1             |          |             |          |          |          |

| 7        | RF2 R<br>Divider          | 0         | 0         | 0         | 0         | 0                |           |           |           |          |          |                  | R           | RF2             |          |             |          |          |          |

| 8        | IF R Divider              | 0         | 0         | 0         | 0         | 0                |           |           |           |          |          |                  |             | R <sub>IF</sub> |          |             |          |          |          |

| 9        | Reserved                  |           |           |           |           |                  |           |           |           |          |          |                  |             |                 |          |             |          |          |          |

|          | •                         |           |           |           |           |                  |           | ,         |           |          |          | •                |             | •               |          |             |          | •        |          |

|          |                           |           |           |           |           |                  |           |           |           |          |          |                  |             |                 |          |             |          |          |          |

| 15       | Reserved                  |           |           |           |           |                  |           |           |           |          |          |                  |             |                 | _        |             |          |          |          |

**Note:** Registers 9–15 are reserved. Writes to these registers may result in unpredictable behavior.

## Register 0. Main Configuration Address Field = A[3:0] = 0000

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6          | D5   | D4 | D3          | D2 | D1 | D0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|-------------|------|----|-------------|----|----|----|

| Name | 0   | 0   | 0   | 0   | AUX | SEL | IF  | ΟIV | 0  | 0  | 0  | XIN<br>DIV2 | LPWR | 0  | AUTO<br>PDB | 0  | 0  | 0  |

| Bit   | Name     | Function                                                                                                                                                                  |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17:14 | Reserved | Program to zero.                                                                                                                                                          |

| 13:12 | AUXSEL   | Auxiliary Output Pin Definition.  00 = Reserved.  01 = Force output low.  11 = Lock Detect (LDETB).                                                                       |

| 11:10 | IFDIV    | IF Output Divider  00 = IFOUT = IFVCO Frequency 01 = IFOUT= IFVCO Frequency/2 10 = IFOUT = IFVCO Frequency/4 11 = IFOUT = IFVCO Frequency/8                               |

| 9:7   | Reserved | Program to zero.                                                                                                                                                          |

| 6     | XINDIV2  | XIN Divide-By-2 Mode.  0 = XIN not divided by 2.  1 = XIN divided by 2.                                                                                                   |

| 5     | LPWR     | Output Power-Level Settings for IF Synthesizer Circuit. $0 = R_{LOAD} < 500 \ \Omega \text{—normal power mode.}$ $1 = R_{LOAD} \geq 500 \ \Omega \text{—low power mode.}$ |

| 4     | Reserved | Program to zero.                                                                                                                                                          |

| 3     | AUTOPDB  | Auto Powerdown  0 = Software powerdown is controlled by Register 2.  1 = Equivalent to setting all bits in Register 2 = 1.                                                |

| 2:0   | Reserved | Program to zero.                                                                                                                                                          |

## Register 1. Phase Detector Gain Address Field (A[3:0]) = 0001

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Name | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | K  | PI | K  | 2  | K  | 21 |

| Bit  | Name            | Function                          |  |

|------|-----------------|-----------------------------------|--|

| 17:6 | Reserved        | Program to zero.                  |  |

| 5:4  | K <sub>PI</sub> | IF Phase Detector Gain Constant.  |  |

|      |                 | N Value K <sub>PI</sub>           |  |

|      |                 | <2048 = 00                        |  |

|      |                 | 2048–4095 = 01                    |  |

|      |                 | 4096–8191 = 10                    |  |

|      |                 | >8191 = 11                        |  |

| 3:2  | K <sub>P2</sub> | RF2 Phase Detector Gain Constant. |  |

|      |                 | N Value K <sub>P2</sub>           |  |

|      |                 | <2048 = 00                        |  |

|      |                 | 2048–4095 = 01                    |  |

|      |                 | 4096–8191 = 10                    |  |

|      |                 | >8191 = 11                        |  |

| 1:0  | K <sub>P1</sub> | RF1 Phase Detector Gain Constant. |  |

|      |                 | N Value K <sub>P1</sub>           |  |

|      |                 | <4096 = 00                        |  |

|      |                 | 4096–8191 = 01                    |  |

|      |                 | 8192–16383 = 10                   |  |

|      |                 | >16383 = 11                       |  |

## Register 2. Powerdown Address Field (A[3:0]) = 0010

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1   | D0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|------|------|

| Name | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | PDIB | PDRB |

| Bit  | Name     | Function                                                                            |

|------|----------|-------------------------------------------------------------------------------------|

| 17:2 | Reserved | Program to zero.                                                                    |

| 1    | PDIB     | Powerdown IF Synthesizer.  0 = IF synthesizer powered down.  1 = IF synthesizer on. |

| 0    | PDRB     | Powerdown RF Synthesizer.  0 = RF synthesizer powered down.  1 = RF synthesizer on. |

## Register 3. RF1 N Divider Address Field (A[3:0]) = 0011

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9             | D8  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----------------|-----|----|----|----|----|----|----|----|----|

| Name |     |     |     |     |     |     |     |     | N <sub>F</sub> | RF1 |    |    |    |    |    |    |    |    |

| Bit  | Name             | Function                       |

|------|------------------|--------------------------------|

| 17:0 | N <sub>RF1</sub> | N Divider for RF1 Synthesizer. |

|      |                  | $N_{RF1} \ge 992.$             |

## Register 4. RF2 N Divider Address Field = A[3:0] = 0100

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8               | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|------------------|----|----|----|----|----|----|----|----|

| Name | 0   |     |     |     |     |     |     |     |    | N <sub>RF2</sub> |    |    |    |    |    |    |    |    |

| Bit  | Name             | Function                                                           |

|------|------------------|--------------------------------------------------------------------|

| 17   | Reserved         | Program to zero.                                                   |

| 16:0 | N <sub>RF2</sub> | N Divider for RF2 Synthesizer. $N_{RF2} \geq 240. \label{eq:NRF2}$ |

| Register 5 | . IF N Divider | Address Field | (A[3:0]) = | 0101 |

|------------|----------------|---------------|------------|------|

|------------|----------------|---------------|------------|------|

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Name | 0   | 0   |     |     | •   |     |     |     |    | N  | IF |    | •  |    |    |    |    |    |

| Bit   | Name            | Function                                                       |

|-------|-----------------|----------------------------------------------------------------|

| 17:16 | Reserved        | Program to zero.                                               |

| 15:0  | N <sub>IF</sub> | N Divider for IF Synthesizer. $N_{IF} \geq 56. \label{eq:NIF}$ |

# Register 6. RF1 R Divider Address Field (A[3:0]) = 0110

| Bit  | D17 | D16 | D15 | D14 | D13 | D12              | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|-----|-----|-----|-----|-----|------------------|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Name | 0   | 0   | 0   | 0   | 0   | R <sub>RF1</sub> |     |     |    |    |    |    |    |    |    |    |    |    |

|       | Name             | Function                                                                                 |

|-------|------------------|------------------------------------------------------------------------------------------|

| 17:13 | Reserved         | Program to zero.                                                                         |

| 12:0  | R <sub>RF1</sub> | R Divider for RF1 Synthesizer.                                                           |

|       |                  | $R_{RF1}$ can be any value from 7 to 8189 if $K_{P1} = 00$<br>8 to 8189 if $K_{P1} = 01$ |

|       |                  | 10 to 8189 if $K_{P1} = 01$                                                              |

|       |                  | 14 to 8189 if K <sub>P1</sub> = 11                                                       |

## Register 7. RF2 R Divider Address Field (A[3:0]) = 0111

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6               | D5 | D4 | D3 | D2 | D1 | D0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|------------------|----|----|----|----|----|----|

| Name | 0   | 0   | 0   | 0   | 0   |     |     |     |    |    |    | R <sub>RF2</sub> |    |    |    |    |    |    |

| Bit   | Name             | Function                                                                                                                                      |

|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 17:13 | Reserved         | Program to zero.                                                                                                                              |

| 12:0  | R <sub>RF2</sub> | R Divider for RF2 Synthesizer.                                                                                                                |

|       |                  | $R_{RF2}$ can be any value from 7 to 8189 if $K_{P2}$ = 00 8 to 8189 if $K_{P2}$ = 01 10 to 8189 if $K_{P2}$ = 10 14 to 8189 if $K_{P2}$ = 11 |

## Register 8. IF R Divider Address Field (A[3:0]) = 1000

| Bit  | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6       | D5 | D4 | D3 | D2 | D1 | D0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----------|----|----|----|----|----|----|

| Name | 0   | 0   | 0   | 0   | 0   |     |     |     |    |    |    | $R_{IF}$ | •  | •  | •  |    |    |    |

| Bit   | Name            | Function                                                                                                                                                                   |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17:13 | Reserved        | Program to zero.                                                                                                                                                           |

| 12:0  | R <sub>IF</sub> | R Divider for IF Synthesizer. $R_{IF}$ can be any value from 7 to 8189 if $K_{P1} = 00$ 8 to 8189 if $K_{P1} = 01$ 10 to 8189 if $K_{P1} = 10$ 14 to 8189 if $K_{P1} = 11$ |

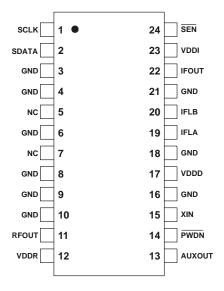

# 4. Pin Descriptions: Si4136-BT/GT

| Pin Number(s)                | Name       | Description                                        |

|------------------------------|------------|----------------------------------------------------|

| 1                            | SCLK       | Serial clock input                                 |

| 2                            | SDATA      | Serial data input                                  |

| 3, 4, 6, 8–10,<br>16, 18, 21 | GND        | Common ground                                      |

| 5, 7                         | NC         | No connect                                         |

| 11                           | RFOUT      | Radio frequency (RF) output of the selected RF VCO |

| 12                           | VDDR       | Supply voltage for the RF analog circuitry         |

| 13                           | AUXOUT     | Auxiliary output                                   |

| 14                           | PWDN       | Powerdown input pin                                |

| 15                           | XIN        | Reference frequency amplifier input                |

| 17                           | VDDD       | Supply voltage for digital circuitry               |

| 19, 20                       | IFLA, IFLB | Pins for inductor connection to IF VCO             |

| 22                           | IFOUT      | Intermediate frequency (IF) output of the IF VCO   |

| 23                           | VDDI       | Supply voltage for IF analog circuitry             |

| 24                           | SEN        | Enable serial port input                           |

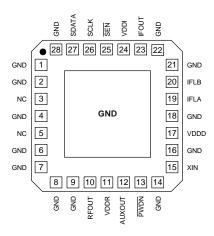

# 5. Pin Descriptions: Si4136-BM/GM

| Pin Number(s)                              | Name       | Description                                        |

|--------------------------------------------|------------|----------------------------------------------------|

| 1, 2, 4, 6, 7–9, 14,<br>16, 18, 21, 22, 28 | GND        | Common ground                                      |

| 3, 5                                       | NC         | No connect                                         |

| 10                                         | RFOUT      | Radio frequency (RF) output of the selected RF VCO |

| 11                                         | VDDR       | Supply voltage for the RF analog circuitry         |

| 12                                         | AUXOUT     | Auxiliary output                                   |

| 13                                         | PWDN       | Powerdown input pin                                |

| 15                                         | XIN        | Reference frequency amplifier input                |

| 17                                         | VDDD       | Supply voltage for digital circuitry               |

| 19, 20                                     | IFLA, IFLB | Pins for inductor connection to IF VCO             |

| 23                                         | IFOUT      | Intermediate frequency (IF) output of the IF VCO   |

| 24                                         | VDDI       | Supply voltage for IF analog circuitry             |

| 25                                         | SEN        | Enable serial port input                           |

| 26                                         | SCLK       | Serial clock input                                 |

| 27                                         | SDATA      | Serial data input                                  |

# 6. Ordering Guide

| Ordering Part<br>Number | Description                      | Lead-Free/<br>RoHS Compliant | Temperature  |

|-------------------------|----------------------------------|------------------------------|--------------|

| Si4136-F-BT             | 2.5 GHz/2.3 GHz/IF OUT           |                              | –40 to 85 °C |

| Si4136-F-GT             | 2.5 GHz/2.3 GHz/IF OUT/Lead Free | ~                            | –40 to 85 °C |

| Si4136-F-BM             | 2.5 GHz/2.3 GHz/IF OUT           |                              | –40 to 85 °C |

| Si4136-F-GM             | 2.5 GHz/2.3 GHz/IF OUT/Lead Free | ~                            | –40 to 85 °C |

| Si4126-F-BM             | 2.3 GHz/IF OUT                   |                              | –40 to 85 °C |

| Si4126-F-GM             | 2.3 GHz/IF OUT/Lead Free         | ~                            | –40 to 85 °C |

## 7. Si4136 Derivative Devices

The Si4136 performs both IF and dual-band RF frequency synthesis. The Si4126 is a derivative of this device. The Si4126 features two synthesizers, RF2 and IF; it does not include RF1. The pinouts for the Si4126 and the Si4136 are the same. Unused registers related to RF1 should be programmed to zero.

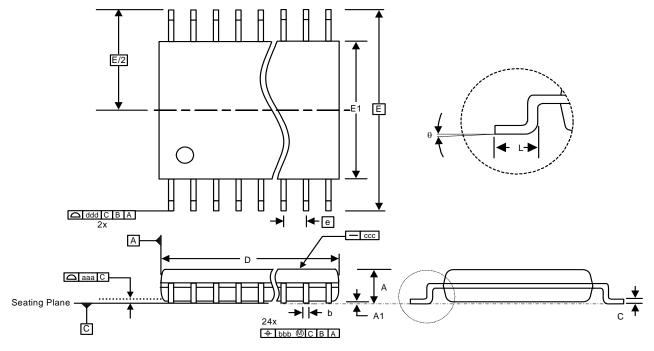

## 8. Package Outline: Si4136-BT/GT

Figure 18 illustrates the package details for the Si4136-BT/GT. Table 12 lists the values for the dimensions shown in the illustration.

Figure 18. 24-Pin Thin Shrink Small Outline Package (TSSOP)

**Table 12. Package Diagram Dimensions**

|        |          | Millimeters |      |  |  |  |  |  |

|--------|----------|-------------|------|--|--|--|--|--|

| Symbol | Min      | Nom         | Max  |  |  |  |  |  |

| Α      | _        | _           | 1.20 |  |  |  |  |  |

| A1     | 0.05     | _           | 0.15 |  |  |  |  |  |

| b      | 0.19     | _           | 0.30 |  |  |  |  |  |

| С      | 0.09     | _           | 0.20 |  |  |  |  |  |

| D      | 7.70     | 7.80        | 7.90 |  |  |  |  |  |

| е      | 0.65 BSC |             |      |  |  |  |  |  |

| Е      |          | 6.40 BSC    |      |  |  |  |  |  |

| E1     | 4.30     | 4.40        | 4.50 |  |  |  |  |  |

| L      | 0.45     | 0.60        | 0.75 |  |  |  |  |  |

| θ      | 0°       | _           | 8°   |  |  |  |  |  |

| aaa    |          | 0.10        |      |  |  |  |  |  |

| bbb    |          | 0.10        |      |  |  |  |  |  |

| ccc    | 0.05     |             |      |  |  |  |  |  |

| ddd    | 0.20     |             |      |  |  |  |  |  |

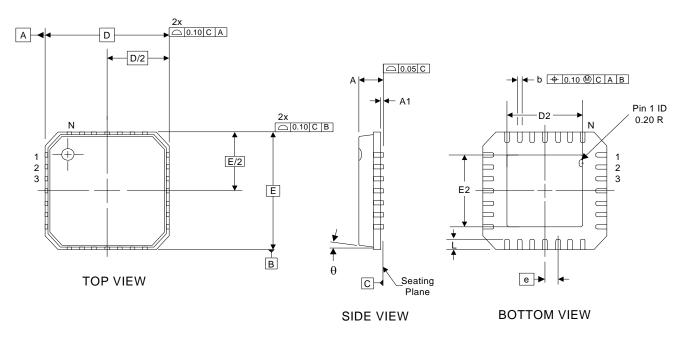

## 9. Package Outline: Si4136-BM/GM

Figure 19 illustrates the package details for the Si4136-BM/GM. Table 13 lists the values for the dimensions shown in the illustration.

Figure 19. 28-Pin Quad Flat No-Lead (QFN)

Table 13. Package Dimensions

**Controlling Dimension: mm**

| Symbol | Millimeters |      |      |

|--------|-------------|------|------|

|        | Min         | Nom  | Max  |

| Α      | _           | 0.85 | 0.90 |

| A1     | 0.00        | 0.01 | 0.05 |

| b      | 0.18        | 0.23 | 0.30 |

| D, E   | 5.00 BSC    |      |      |

| D2, E2 | 2.55        | 2.70 | 2.85 |

| N      | 28          |      |      |

| е      | 0.50 BSC    |      |      |

| L      | 0.50        | 0.60 | 0.75 |

| θ      |             |      | 12°  |

# Si4136/Si4126

## **DOCUMENT CHANGE LIST**

## **Revision 1.3 to Revision 1.4**

- Si4136-BT change to Si4136-BT/GT

- Si4136-BM change to Si4136-BM/GM

## **Revision 1.4 to Revision 1.41**

■ Updated contact information.

Notes:

# Si4136/Si4126

## **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.